# **Copyright Warning & Restrictions**

The copyright law of the United States (Title 17, United States Code) governs the making of photocopies or other reproductions of copyrighted material.

Under certain conditions specified in the law, libraries and archives are authorized to furnish a photocopy or other reproduction. One of these specified conditions is that the photocopy or reproduction is not to be "used for any purpose other than private study, scholarship, or research." If a, user makes a request for, or later uses, a photocopy or reproduction for purposes in excess of "fair use" that user may be liable for copyright infringement,

This institution reserves the right to refuse to accept a copying order if, in its judgment, fulfillment of the order would involve violation of copyright law.

Please Note: The author retains the copyright while the New Jersey Institute of Technology reserves the right to distribute this thesis or dissertation

Printing note: If you do not wish to print this page, then select "Pages from: first page # to: last page #" on the print dialog screen

The Van Houten library has removed some of the personal information and all signatures from the approval page and biographical sketches of theses and dissertations in order to protect the identity of NJIT graduates and faculty.

#### **ABSTRACT**

# CHARACTERIZATION OF LOW POWER HfO<sub>2</sub> BASED SWITCHING DEVICES FOR IN-MEMORY COMPUTING

### by Aseel Zeinati

Oxide based Resistive Random Access Memory (RRAM) devices are investigated as one of the promising non-volatile memories to be used for in-memory computing that will replace the classical von Neumann architecture and reduce the power consumption. These applications required multilevel cell (MLC) characteristics that can be achieved in RRAM devices. One of the methods to achieve this analog switching behavior is by performing an optimized electrical pulse. The RRAM device structure is basically an insulator between two metals as metal-insulator-metal (MIM) structure. Where one of the primary challenges is to assign an RRAM stack with both low power consumption and good switching performance.

This thesis investigates different HfO<sub>2</sub> based RRAM stacks and compares their electrical and MLC characteristics. By engineering the distribution of defects and oxygen vacancies in the switching layer, which have been done by exposing the dielectric with a hydrogen plasma treatment in the first device, using HfO<sub>2</sub> and Al<sub>2</sub>O<sub>3</sub> as a bilayer, or by adding Zr to the HfO<sub>2</sub>. While the plasma treated devices show a promising conductance quantization with low power consumption, the performance can be further enhanced by engineering the bottom electrode. The impact of introducing additional nitrogen at the bottom electrode, TiN, shows additional reduction in the switching power of the plasma treated devices.

# CHARACTERIZATION OF LOW POWER HfO<sub>2</sub> BASED SWITCHING DEVICES FOR IN-MEMORY COMPUTING

by Aseel Zeinati

A Thesis

Submitted to the Faculty Of

New Jersey Institute of Technology

in Partial Fulfillment of the Requirements for the Degree of

Master of Science in Electrical Engineering

Helen And John C. Hartmann Department Of Electrical And Computer Engineering

May 2023

# **APPROVAL PAGE**

# CHARACTERIZATION OF LOW POWER HfO<sub>2</sub> BASED SWITCHING DEVICES FOR IN-MEMORY COMPUTING

# **Aseel Zeinati**

| Dr. Durgamadhab Misra, Dissertation Advisor<br>Professor and Chair of Electrical and Computer Engineering, NJIT | Date |

|-----------------------------------------------------------------------------------------------------------------|------|

| Dr. Leonid Tsybeskov, Committee Member Distinguished Professor, Electrical and Computer Engineering, NJIT       | Date |

| Dr. Shaahin Angizi, Committee Member<br>Assistant Professor, Electrical and Computer Engineering, NJIT          | Date |

#### **BIOGRAPHICAL SKETCH**

Author: Aseel Zeinati

Degree: Master of Science

Date: May 2023

Date of Birth:

Place of Birth:

#### **Undergraduate and Graduate Education:**

- Master of Science in Electrical Engineering,

New Jersey Institute of Technology, Newark, NJ, 2023

- Bachelor of Science in Electrical Engineering,

Jordan University of Science and Technology, Jordan, 2013

Major: Electrical Engineering

#### Presentation and Publication:

Zeinati, A.; Misra, D.; Triyoso, D.; Clark, R.; Tapily, K.; Consiglio, S.; Wajda, C.; and Leusink, G., "Process Optimization to Reduce Power in HfO2-Based RRAM Devices for In-Memory Computing", 242<sup>nd</sup> ECS, October 10, 2022, Doi: 10.1149/MA2022-0215806mtgabs.

Zeinati, A.; Misra, D.; Triyoso, D.; Clark, R.; Tapily, K.; Consiglio, S.; Wajda, C.; and Leusink, G., "The Impact of Engineering TiN Bottom Electrode in RRAM Devices with Plasma Treated HfO2 on Reducing the Power for In Memory Computing", 243<sup>rd</sup> ECS, May 28, 2023.

Zeinati, A., and Naser, S.; "Design and Implementation of RF Energy Harvester", Bs project in JUST, January 12, 2013.

"Verily, knowledge only comes by learning and continue learning, and forbearance only comes by cultivating forbearance."

-The prophet Muhammad.

#### **ACKNOWLEDGMENT**

Words cannot express my gratitude to my advisor Dr. Durgamadhab Misra, Professor and Chair of Electrical and Computer Engineering, New Jersey Institute of Technology, Newark, New Jersey for his invaluable patience and effort to teach me and guide me throughout my research. Many thanks should also go to the defense committee members Dr. Leonid Tsybeskov, Distinguished Professor, Dr. Shaahin Angizi, Assistant Professor, Electrical and Computer Engineering, New Jersey Institute of Technology, Newark, New Jersey, who generously provided the knowledge and expertise. I also could not have undertaken this journey without the generous support from the Tokyo Electron Ltd., who financed my research.

This endeavor would not have been possible without the support of my husband Ahmed and my kids Bara and Nada. I am also grateful to my family, especially my parents Khaldoun and Rajaa, and my in-laws Ayman and Dalal. Their belief in me has kept my spirits and motivation high during this process.

Lastly, I would be remiss in not mentioning my sister Rahmah and my brothers; Mohammad, Abdelrahman, Saleh and Khaled for their emotional support.

# **TABLE OF CONTENTS**

| Cł | napte        | r                                                              |                    | Page |

|----|--------------|----------------------------------------------------------------|--------------------|------|

| 1  | INTRODUCTION |                                                                |                    | 1    |

|    | 1.1          | Background                                                     |                    | 1    |

|    | 1.2          | Emerging Nonvolatile Memory                                    |                    | 3    |

|    |              | 1.2.1 Phase-Change Memory (P                                   | CM)                | 4    |

|    |              | 1.2.2 Spin Transfer Torque Mag                                 | netic RAM (STTRAM) | 5    |

|    |              | 1.2.3 Resistive Random-Access                                  | Memory (RRAM)      | 5    |

|    | 1.3          | Motivation for the Thesis                                      |                    | 6    |

|    | 1.4          | Thesis Organization                                            |                    | 7    |

| 2  | RRA          | M TECHNOLOGY REVIEW                                            |                    | 8    |

|    | 2.1          | RRAM Switching Mechanism                                       |                    | 9    |

|    | 2.2          | RRAM Structure                                                 |                    | 11   |

|    | 2.3          | HfO <sub>2</sub> as Switching layer                            |                    | 12   |

|    |              | 2.3.1 HfO <sub>2</sub> with Hydrogen Plasm                     | a Treatment        | 13   |

|    |              | 2.3.2 HfO <sub>2</sub> /Al <sub>2</sub> O <sub>3</sub> bilayer |                    | 15   |

|    | 2.4          | Impact of Top Electrode                                        |                    | 16   |

|    | 2.5          | MLC for In-Memory Computing                                    |                    | 17   |

| 3  | EXP          | ERIMENTAL SETUP                                                |                    | 19   |

|    | 3.1          | Devices Structures                                             |                    | 19   |

|    | 3.2          | Electrical Characterizations Tools                             | and Connections    | 20   |

|    | 3.3          | Forming Process                                                |                    | 21   |

|    | 3.4          | Pulse Operation                                                |                    | 22   |

# TABLE OF CONTENTS Continued

| CI         | hapte | r       |                                      | Page |

|------------|-------|---------|--------------------------------------|------|

|            |       | 3.4.1   | Width-Varying Pulsed Operation       | 22   |

|            |       | 3.4.2   | Amplitude-Varying Pulsed Operation   | 23   |

|            |       | 3.4.3   | Endurance Test                       | 23   |

| 4          | RES   | ULTS A  | ND DISCUSSIONS                       | 25   |

|            | 4.1   | Formir  | ng Process Results                   | 25   |

|            | 4.2   | Width-  | -Varying Pulsed Operation Results    | 27   |

|            | 4.3   | Amplit  | ude-Varying Pulsed Operation Results | 30   |

|            | 4.4   | Endur   | ance Test Results                    | 35   |

|            | 4.5   | Condu   | uctance Quantization                 | 37   |

| 5          | IMP   | ACT OF  | BOTTOM ELECTRODE                     | 39   |

|            | 5.1   | Device  | e Structures                         | 39   |

|            | 5.2   | Formir  | ng Process and Results               | 40   |

|            | 5.3   | RESE    | T Pulsed Operation and Results       | 42   |

| 6          | CON   | ICLUSIO | ON AND FUTURE WORK                   | 44   |

|            | 6.1   | Conclu  | usion                                | 45   |

|            | 6.2   | Future  | Work                                 | 46   |

| REFERENCES |       |         | 47                                   |      |

# LIST OF TABLES

| Tab | le                                                                                                                                                                                                                         | Page |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 2.1 | The Materials That Have Been Used for Binary Metal Oxide RRAM. Metals of the Corresponding Binary Oxides Used for the Resistive Switching Layer Are Colored in Yellow. Metals Used for the Electrodes Are Colored in Blue. | 11   |

| 4.1 | List The Forming Voltages (V <sub>forming</sub> ), The Minimum I <sub>CC</sub> That Form The Device, And Forming Power (I <sub>CC</sub> X V <sub>forming</sub> )                                                           | 26   |

| 4.2 | Comparison Of Conductance States That Have Been Generated In The Four RRAM Devices With Width-Varying Pulsed Operation                                                                                                     | 30   |

| 4.3 | Comparison Of Conductance States That Have Been Generated In The Four RRAM Devices With Amplitude-Varying Pulsed Operation                                                                                                 | 34   |

| 5.1 | List The Forming Voltages ( $V_{forming}$ ), The Minimum I <sub>CC</sub> That Form The Device, And Forming Power (I <sub>CC</sub> X $V_{forming}$ )                                                                        | 42   |

# **LIST OF FIGURES**

| Figure |                                                                                                                                                                                                                                       |    |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.1    | In-memory computing. A, in a conventional computing system. B, in-memory computing                                                                                                                                                    | 2  |

| 1.2    | Memristor crossbar arrays for in-memory computing                                                                                                                                                                                     | 2  |

| 1.3    | The memory hierarchy                                                                                                                                                                                                                  | 3  |

| 1.4    | Phase-Change Memory (PCM) structure                                                                                                                                                                                                   | 5  |

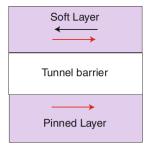

| 1.5    | STTRAM structure                                                                                                                                                                                                                      | 5  |

| 1.6    | RRAM structure                                                                                                                                                                                                                        | 6  |

| 2.1    | The four fundamental two-terminal circuit elements: resistor, capacitor, inductor and memristor                                                                                                                                       | 8  |

| 2.2    | HP first working memristor with simulated I-V curve                                                                                                                                                                                   | 9  |

| 2.3    | I-V characteristics of forming, LRS after SET and HRS after RESET of RRAM device and evolution of oxygen ions and oxygen vacancies distributions during forming (A)-(C), after RESET (D) and after SET                                | 10 |

| 2.4    | I-V curves showing the two modes of operation: (a) unipolar, (b) bipolar                                                                                                                                                              | 11 |

| 2.5    | The impact of introducing H-plasma in the $HfO_2$ layer, (a) after depositing 4 nm of $HfO_2$ then followed by 1 nm of $HfO_2$ , (b) after 2 nm of $HfO_2$ then followed by 3 nm of $HfO_2$ (c) in the midpoint of 6 nm $HfO_2$ layer | 14 |

| 2.6    | On the left the schematic of the device, on the right the I-V curves of two DC sweep of RRAM stack using HfO <sub>2</sub> with H-plasma in the midpoint and TiN as TE                                                                 | 14 |

| 2.7    | On the left the schematic of the device, on the right the I-V curves of three DC sweep of RRAM stack using 7 nm $HfO_2$ with 1 nm $Al_2O_3$ near BE                                                                                   | 15 |

| 2.8    | On the left the schematic of the device, on the right the I-V curves of four DC sweep of RRAM stack using 7 nm HfO <sub>2</sub> with 1 nm Al <sub>2</sub> O <sub>3</sub> near TE                                                      | 16 |

# LIST OF FIGURES Continued

| Figur | e                                                                                                                                                                                                                                                          | Page |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 2.9   | On the left the schematic of the device, on the right the I-V curves of three DC sweep of RRAM stack using 7nm $HfO_2$ with 0.5 nm $Al_2O_3$ near BE                                                                                                       | 16   |

| 2.10  | On the left the schematic of the device, on the right the I-V curves of two DC sweep of RRAM stack using HfO <sub>2</sub> with H-plasma in the midpoint and Ru as a TE                                                                                     | 17   |

| 2.11  | MLC Characteristics of pulse measurements data for treated HfO <sub>2</sub>                                                                                                                                                                                | 18   |

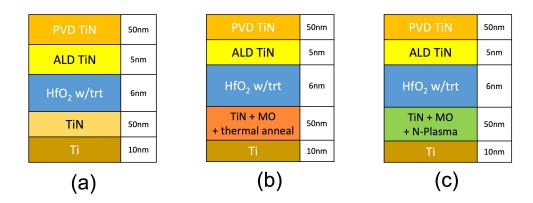

| 3.1   | Schematic of the four devices with different switching layers showing the material stack and relative thickness of each layer                                                                                                                              | 20   |

| 3.2   | Block diagram of pulse measurement set-up                                                                                                                                                                                                                  | 21   |

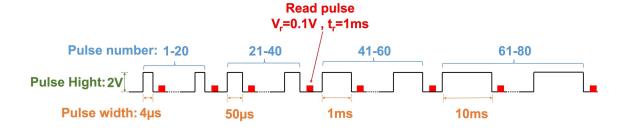

| 3.3   | Schematic diagram of programed cycle of SET width-varying pulsed operation (off scale)                                                                                                                                                                     | 22   |

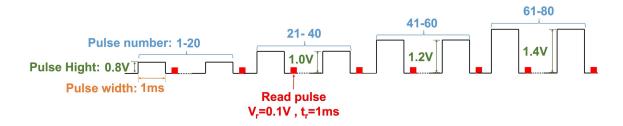

| 3.4   | Schematic diagram of programed cycle of SET amplitude-varying pulsed operation (off scale)                                                                                                                                                                 | 23   |

| 4.1   | forming I-V curves of the four RRAM devices with oxide control showing the minimum $I_{\text{CC}}$                                                                                                                                                         | 25   |

| 4.2   | treated device deposition steps, deposit 3 nm $HfO_2$ by ALD then introduce H-Plasma and after that deposit another 3 nm $HfO_2$ by ALD                                                                                                                    | 26   |

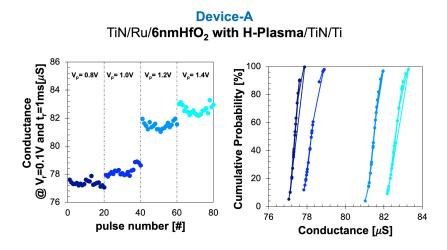

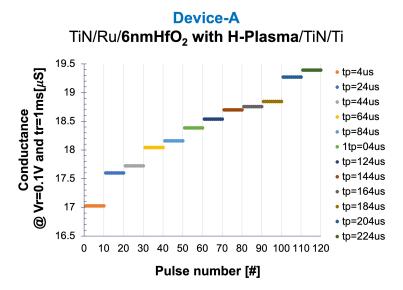

| 4.3   | Measured conductance modulation obtained by applying successive SET pulse sequences with increasing $t_{\text{p}}$ and the experimental cumulative probability distributions of the states for device-A (6nm HfO $_2$ with H-plasma treatment)             | 28   |

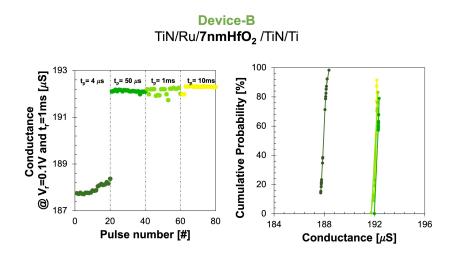

| 4.4   | Measured conductance modulation obtained by applying successive SET pulse sequences with increasing $t_{\text{p}}$ and the experimental cumulative probability distributions of the states for device-B (7 nm stochiometric $HfO_2$ )                      | 28   |

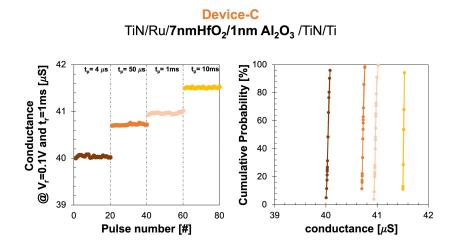

| 4.5   | Measured conductance modulation obtained by applying successive SET pulse sequences with increasing $t_p$ and the experimental cumulative probability distributions of the states for Device-C (7nm HfO <sub>2</sub> /1nm Al <sub>2</sub> O <sub>3</sub> ) | 29   |

# LIST OF FIGURES Continued

| Figur | re                                                                                                                                                                                                                                                     | Page |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

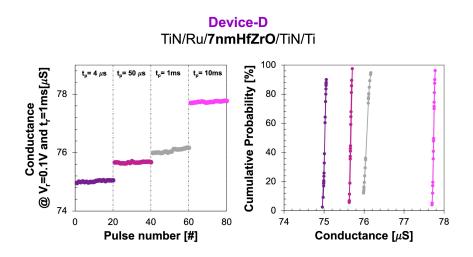

| 4.6   | Measured conductance modulation obtained by applying successive SET pulse sequences with increasing $t_{\text{p}}$ and the experimental cumulative probability distributions of the states for Device-D (7nm HfZrO).                                   | 29   |

| 4.7   | Measured conductance modulation obtained by applying successive SET pulse sequences with increasing $V_{\text{p}}$ and the experimental cumulative probability distributions of the states for device-A (6nm HfO <sub>2</sub> with H-plasma treatment) | 31   |

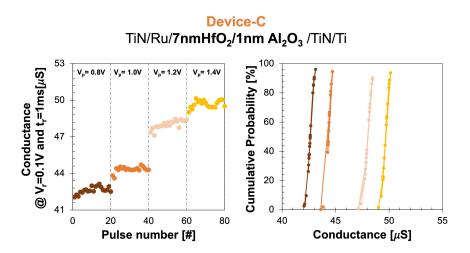

| 4.8   | Measured conductance modulation obtained by applying successive SET pulse sequences with increasing $V_p$ and the experimental cumulative probability distributions of the states for Device-C (7nm $HfO_2/1nm\ Al_2O_3$ )                             | 32   |

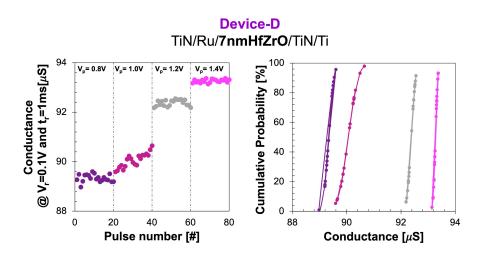

| 4.9   | Measured conductance modulation obtained by applying successive SET pulse sequences with increasing $V_{\text{p}}$ and the experimental cumulative probability distributions of the states for Device-D (7nm HfZrO).                                   | 32   |

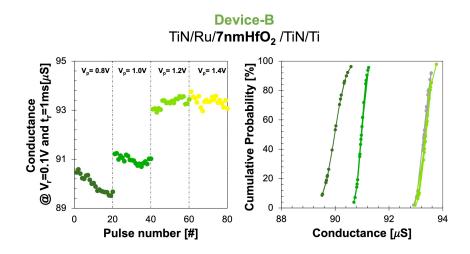

| 4.10  | Measured conductance modulation obtained by applying successive SET pulse sequences with increasing $V_p$ and the experimental cumulative probability distributions of the states for device-B (7 nm stochiometric $HfO_2$ )                           | 33   |

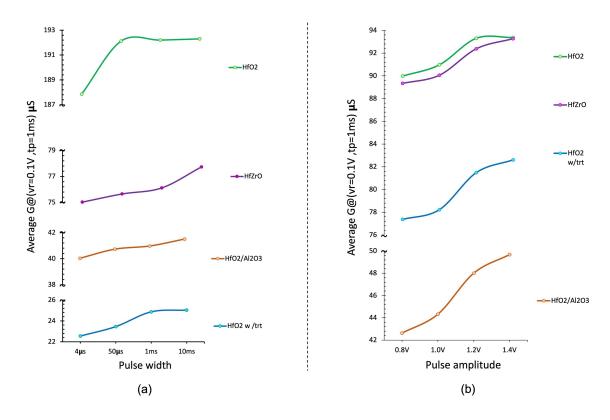

| 4.11  | Average RRAM conductance was plotted against varying (a) SET pulse width and (b) SET pulse amplitude                                                                                                                                                   | 34   |

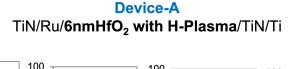

| 4.12  | Measured conductance values just after SET transition during 10k endurance cycles for every programing pulse width (tp= $4\mu s$ , $50\mu s$ , $1ms$ , $10ms$ ) for the device-A (6nm HfO <sub>2</sub> with H-plasma treatment).                       | 35   |

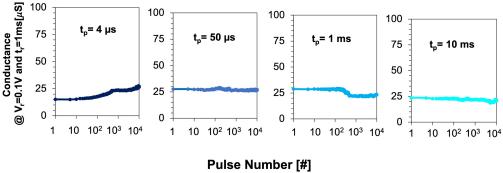

| 4.13  | Measured conductance values just after SET transition during 10k endurance cycles for every programing pulse width (tp= $4\mu s$ , $50\mu s$ , $10ms$ ) for the device-B (7 nm stochiometric HfO <sub>2</sub> )                                        | 36   |

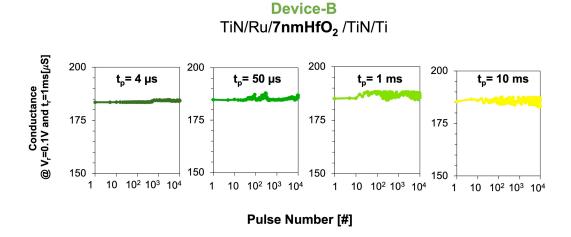

| 4.14  | Measured conductance values just after SET transition during 10k endurance cycles for every programing pulse width (tp= $4\mu$ s, $50\mu$ s, 1ms, 10ms) for the device-C (7nm HfO <sub>2</sub> /1nm Al <sub>2</sub> O <sub>3</sub> )                   | 36   |

# LIST OF FIGURES Continued

| Figur | e                                                                                                                                                                                                                                         | Page |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

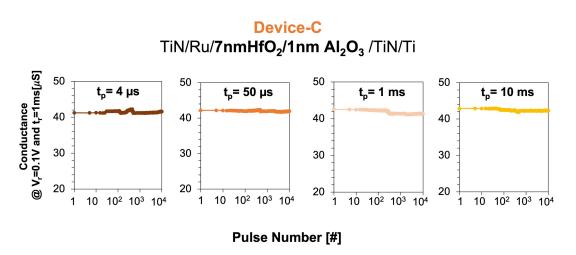

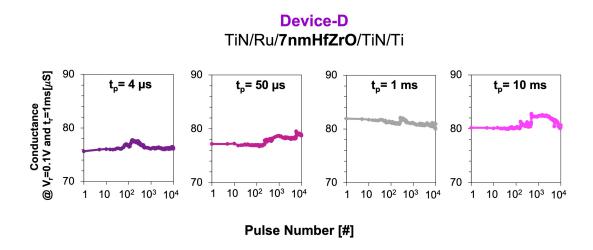

| 4.15  | Measured conductance values just after SET transition during 10k endurance cycles for every programing pulse width (tp= $4\mu s$ , $50\mu s$ , $1ms$ , $10ms$ ) for the device-D ( $7nm$ HfZrO)                                           | 37   |

| 4.16  | Quantization of measured conductance obtained by applying successive SET pulse sequences with increasing $t_{\text{p}}$ for device-A (6nm HfO <sub>2</sub> with H-plasma treatment)                                                       | 38   |

| 5.1   | Schematic of RRAM device showing the preferable $V_{\circ}$ distribution inside the oxide layer, which is more $V_{\circ}$ near the TE                                                                                                    | 39   |

| 5.2   | Schematic of RRAM stacks that have the same TE and dielectric but different BE (a) TiN (device-E (control)), (b) TiN plus Mo with thermal anneal (device F), (c) TiN plus Mo with plasma nitridation (device G)                           | 40   |

| 5.3   | Forming I-V curves of the three RRAM devices with BE control showing the minimum $I_{\text{CC}}$                                                                                                                                          | 41   |

| 5.4   | Schematic diagram of programed cycle of RESET width-varying pulsed operation (off scale)                                                                                                                                                  | 42   |

| 5.5   | Measured conductance modulation obtained by applying successive RESET pulse sequences with increasing $t_{\text{p}}$ and for (a) Device-E (TiN) (b) Device-F (TiN+ Mo+ Thermal annealing)                                                 | 43   |

| 5.6   | Measured conductance modulation obtained by applying successive RESET pulse sequences with increasing $t_{\text{p}}$ and for Device-G (TiN + Mo+ Plasma Nitridation) (a) $t_{\text{p}}$ in microseconds (b) $t_{\text{p}}$ in nanoseconds | 43   |

#### CHAPTER 1

#### INTRODUCTION

### 1.1. Background

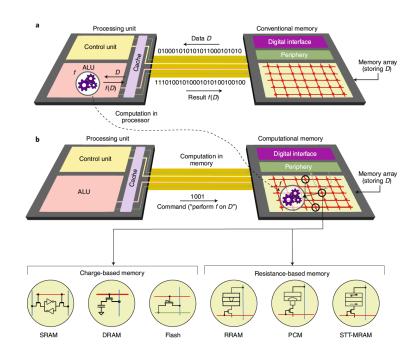

Today's computing systems are built based on the Van Neumann architecture, with a separated memory and processing units. Data must move between the processing and the memory units back and forth and cause a memory wall problem. With the development of artificial intelligent and machine learning applications, with large data the Van Neumann architecture cannot meet the demand of these applications. To overcome such a problem in-memory computing is a promising solution with large datasets, discrete and random memory access [1, 2]. Figure 1.1a shows the conventional computing system that built using Van Neumann architecture performed an operation f on data set D, D must move back and forth and this costs latency and energy, where Figure 1.1b shows the in-memory computing system using crossbar structure [1].

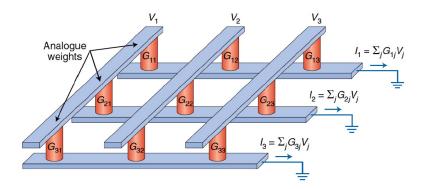

In-memory computing is an alternate approach where computing performed within the memory unit that is organized in an array as a crossbar [3] shown in Figure 1.2 [6]. Each node in this crossbar has a memory element for an extremely low power consumption and high efficiency of data movement [4]. Each memory element in the crossbar could be charge-based memory in terms of presence or absence of the charge, such as SRAM, DRAM, and flash memory [7], or resistance-based memory in terms of the differences in the atomic arrangements

or orientation of ferromagnetic metal layers, such as RRAM, PCM, FeRAM and STTRAM [8].

**Figure 1.1** In-memory computing. (a) in a conventional computing system. (b) inmemory computing. Source: [1].

**Figure 1.2** Crossbar arrays for in-memory computing. Source: [6].

### 1.2. Emerging Nonvolatile Memory

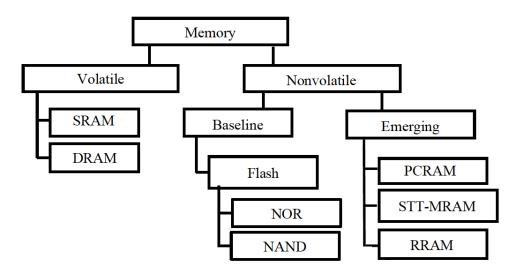

Memory devices is the core of any computing system. There are two types of memory based on their ability to hold the information after removing the power source: volatile memory such as DRAM and SRAM which lose the information once the power is off, and nonvolatile memory that also can be classify in to two groups; baseline memory like flash memory and emerging memory like RRAM. Figure 1.3 shows the memory hierarchy [5].

**Figure 1.3** The memory hierarchy. Source: [5].

SRAM consumes a large area due to its six-transistor (6T) structure which reduce its density data storage [8]. While DRAM requires large programming voltages, and capacitor leakage issues limited the data storage capacity [9]. Flash memory has high density data storage since it can be stacked in 3D structure, but requires long programming read times (around milliseconds), and that increases its programming power [10]. All these memories SRAM, DRAM and Flash are

based on complementary metal oxide semiconductor (CMOS) technology that reach its scale limit due to Moore's law [11]. This opens the way to the emerging non-volatile memory technology due to its low consuming power, high density and doesn't have the scalability issue, since it has very simple structure. Some of the types of emerging non-volatile memory devices that's active in the research area are phase change memory (PCM), spin transfer torque magnetic random-access memory (STTRAM), and resistive random-access memory (RRAM).

The emerging non-volatile memory devices are resistance-based memory, which can be programed to store information through changing in their resistance state by applying an electric field.

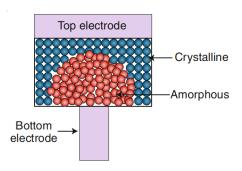

## 1.2.1. Phase-Change Memory (PCM)

This type of memory takes a mushroom cell structure which is the shape of the switching volume above a heater, as shown in Figure 1.4. By heating the material above its crystallization temperature with a sequence of longer width and lower amplitude pulses the device enter its low resistance state LRS (crystalline), while using a short width and high amplitude voltage pulses and subsequent rapid cooling will perform an abrupt melt-quench process the device enter its high resistance state HRS (amorphous). Repetitive crystallization reduces amorphous thickness gradually and led to multiple programmable states in PCM devices [12].

**Figure 1.4** Phase-Change Memory (PCM) structure. Source: [1].

## 1.2.2. Spin Transfer Torque Magnetic RAM (STTRAM)

This type of memory has a structure known as magnetic tunnel junctions as shown in Figure 1.5 which is basically two ferromagnetic layers sandwiching a spacer layer (commonly MgO). The device could be programed into two states depending on the electron spin inside the ferromagnetic layers by passing a spin-polarized current, which initiates a phenomenon called STT [13].

**Figure 1.5** STTRAM structure. Source: [1].

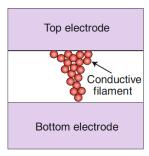

#### 1.2.3. Resistive Random-Access Memory (RRAM)

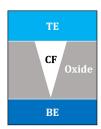

This type of memory is built as metal insulator metal structure (MIM) structure as shown in Figure 1.6. The change in its resistance state done by applying a SET electric field to the top electrode. A conductive filament (CF) is formed and let the

device enter low resistive state (LRS), while applying a RESET electric field will rupture the CF and the device will enter the high resistance state (HRS).

There are two types of RRAM based on the switching mechanisms. The conductive-bridge RAM (CBRAM), which depend on the fast-diffusing Ag or Cu ions into the oxide to form a conductive bridge [14]. The other type is the binary metal oxide RRAM, where the CF is formed by oxygen vacancies ( $V_0$ ) after the oxygen ions leave the oxide toward the top electrode.

**Figure 1.6** RRAM structure.

Source: [1].

#### 1.3. Motivation of this Work

The motivation of this work is to investigate different RRAM stack that works that will have multilevel programable devices with low power consumption, strong endurance, and a good reliability. These devices need to have an appropriate distribution of  $V_0$  to reduce power and enhance performance. This can be achieved by modifying process conditions for the switching layer deposition and for engineering the electrode materials. The characteristics can be evaluated using pulse operation. Then the promising RRAM device can be used for in memory computing with low power consumption.

### 1.4. Thesis Organization

Chapter 1 introduce the computing systems and the needs of in-memory computing approach, with list of some of non-volatile memories and their properties.

Chapter 2 presents previous studies on selecting RRAM stack materials. Comparison of the top electrode metal such as Ru and TiN and comparison of the different deposition process such as hydrogen plasma treatment in HfO<sub>2</sub>. Different position of the caping layer Al<sub>2</sub>O<sub>3</sub> in a HfO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> bilayer structure is also discussed.

Chapter 3 describe the experimental setup of this work. The electrical characterization such as the forming process, the pulse operations with width variation, amplitude variation, and the endurance test are outlined.

Chapter 4 presents the results of four devices with different switching dielectrics, HfO<sub>2</sub>-Treated, HfO<sub>2</sub>, HfO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> and hafnium-zirconium oxide (HfZrO) with same top and bottom electrodes.

Chapter 5 presents the experimental setup, the devices structures, the results of three devices that have the same top electrode and the switching dielectric but with different bottom electrodes to study the impact of controlling the nitrogen level in the bottom electrode.

Chapter 6 present the conclusion of the is work followed by the suggestion of the future work.

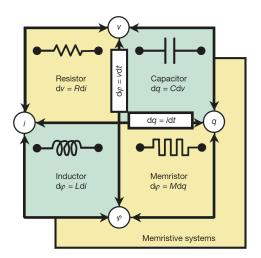

#### **CHAPTER 2**

#### RRAM TECHNOLOGY REVIEW

RRAM devices is known as memristor (short for memory and resister) was discovered by a distinguished faculty member in the Electrical Engineering and Computer Sciences Department of the University of California Berkeley Leon Chua in 1971 as the fourth fundamental element beside resistors, capacitors and inductors as shown in Figure 2.1.

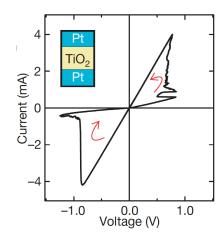

Hewlett Packard (HP) labs formulate a physics-based model of a memristor and fabricated nanoscale MIM devices in 2008 and proved the work of the memristor as a resister with memory (state). The I-V characteristics of HP's first working RRAM device is shown in Figure 2.2. The inset in Figure 2.2 shows the dielectric layer, TiO<sub>2</sub>, sandwiched between two electrodes made of Pt. [15, 16].

**Figure 2.1** The four fundamental two-terminal circuit elements: resistor, capacitor, inductor and memristor.

Source: [16].

**Figure 2.2** HP first working memristor with simulated I-V curve. Source: [16].

The properties of the memristor make it a promising device to be used for inmemory computing systems. Because of its simple structure the device is highly scalable. This device can make the memory system high speed, allow high storge density, enhance endurance and retention. It has the advantage of being compatible with the conventional CMOS fabrication environment.

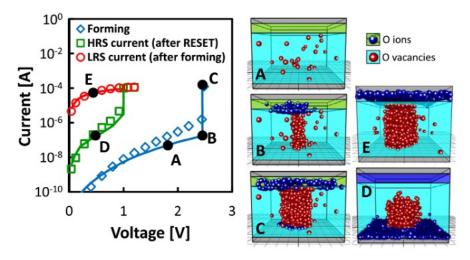

### 2.1. RRAM Switching Mechanism

The switching mechanism for the fresh RRAM devices starts with forming process. Where the device initially in the HRS with randomly distributed defects in the oxide layer, also known as the switching layer, as shown in Figure 2.3.A [18]. The bottom electrode (BE) is grounded, and a DC sweep with compliance current (I<sub>cc</sub>) is applied to the top electrode (TE). Figure 2.3.B shows how the oxygen ions move toward the TE after applying the DC sweep and a conductive filament (CF) formed inside the switching layer. The CF lowers the resistance value of the device like a dielectric soft breakdown where the device entered the LRS. This process is called

the forming process. When the electric field reversed the CF ruptured and the device entered HRS again, this process called RESET. After the forming and RESET process a SET operation is performed by applying the electric field with an  $I_{cc}$ . The  $I_{cc}$  prevents the device from being damaged. During the SET operation the CF is reconstructed, and the device entered the LRS as shown in Figure 2.3 (E).

After forming, the RRAM device consumes less power for SET process because the CF is partially ruptured during the RESET process. The top of the CF after RESET becomes a virtual BE. The I-V curve, shown in the left side of Figure 2.3 [17,18], represents the above behavior.

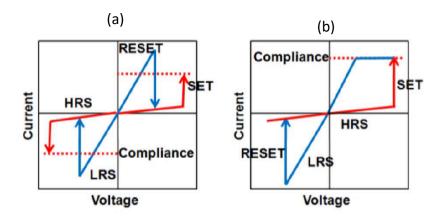

The former discussed RRAM switching mechanisms is for a mode of RRAM devices called bipolar RRAM where the RESET performed by applying electric field with an opposite polarity of the SET electric field. In the other mode of RRAM known as unipolar, the SET and RESET both have the same polarity. Figure 2.4 shows the I-V curves of the two-operations mode unipolar and bipolar.

**Figure 2.3** I-V characteristics of forming, LRS after SET and HRS after RESET of RRAM device and evolution of oxygen ions and oxygen vacancies distributions during forming (A)-(C), after RESET (D) and after SET. Source: [18].

**Figure 2.4** I-V curves showing the two modes of operation: (a) unipolar, (b) bipolar. Source: [19].

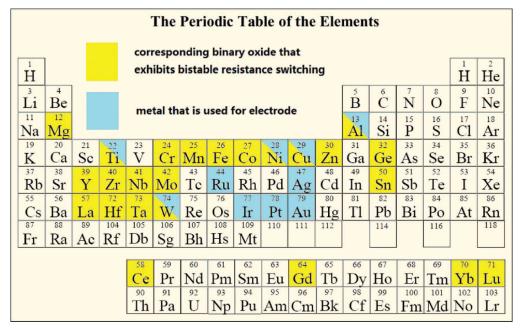

**Table 2.1** The Materials That Have Been Used for Binary Metal Oxide RRAM. Metals of the Corresponding Binary Oxides Used for the Resistive Switching Layer Are Colored in Yellow. Metals Used for the Electrodes Are Colored in Blue. Source: [17].

#### 2.2. RRAM Structure

The RRAM structure as mentioned before is basically an oxide sandwiched between two electrodes. While characterizing the RRAM devices the material of the oxide and the two electrodes impact the electrical and physical properties.

When the RRAM devices is used in the computing systems it will be integrated with conventional CMOS in a one-transistor—one-resistor (1T1R) device structure.

There are many of metal oxides that could be used as the switching layer in RRAM devices, such as HfO<sub>x</sub>, AlO<sub>x</sub>, NiO<sub>x</sub>, TiO<sub>x</sub>, and TaO, they also known as transition metal oxides. The materials for the oxide layer and the electrodes are summarized in Table 2.1 [17].

The TE, such as TiN, Pt, Ru, TaN act like an oxygen ion receiver when the electric failed is applied to it. The switching characteristics of the RRAM devices relays on the interface between TE and the switching layer that's explain the focus of several studies on the properties of this interface and how to control the oxygen ions flow on it. On the other hand, the BE properties also impact the performance of the RRAM devices.

### 2.3. HfO<sub>2</sub> as Switching layer

HfO<sub>2</sub> is a high k martial with a band gab of (~5.6 ev) that has been used in fabricating RRAM devices since 2012 [20]. It's one of the most mature oxides that have been used as a switching layer in RRAM because it is enriched with defects [18]. In addition, its computable with CMOS technology, very well understood dielectric, has a good endurance, high reliability, and consumes low power.

The functional properties of  $HfO_2$  depend on its defect structure [21], the stoichiometric  $HfO_2$  is one of the options to be used as switching layer in RRAM but due to its lack of oxygen vacancies ( $V_0$ ) it consumes large power than the non-stoichiometric  $HfO_x$ . the former  $HfO_x$  has more defects but it's very difficult to

control which led to unstable CF, in addition to complicated fabrication process of this type of oxides.

Increasing the density of  $V_0$  near the top electrode seems to streamline the switching characteristics. While controlling  $V_0$  distribution in  $HfO_2$  is, therefore, required doped  $HfO_2$ , by introducing hydrogen plasma treatment in the middle of  $HfO_2$  layer [22], or by making  $HfO_2/Al_2O_3$  bilayer structure [23].

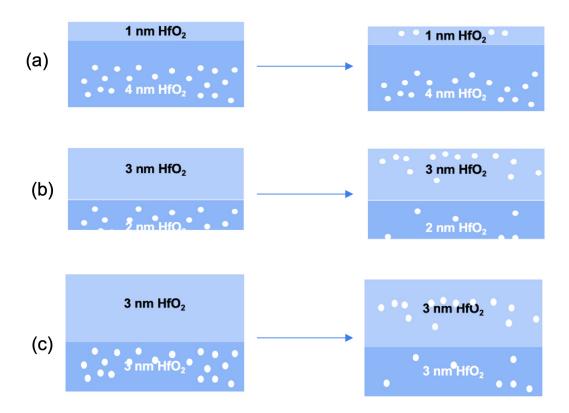

#### 2.3.1. HfO<sub>2</sub> with Hydrogen Plasma Treatment

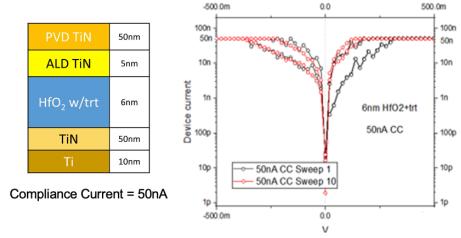

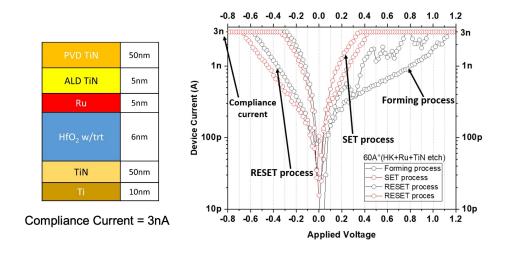

It has been reported that more  $V_0$  near the TE reduced the switching power and improve the performance of the RRAM device [22]. The study that has been done in [24] investigated the efficient position to introduce the H-plasma as shown in Figure 2.5. When the H-plasma was inserted between 4nm and 1nm of HfO<sub>2</sub> as appeared in Figure 2.5a, thinner cap layer was not able to reoxidize the defects and the distribution of  $V_0$  related defects became uniform throughout the dielectric thickness. That led to a higher forming voltage. For thicker cap layer as Figure 2.5b the reoxidation followed by  $V_0$  migration toward the top reduces the forming voltage, while introducing the H-plasma in the midpoint of the HfO<sub>2</sub> layer as shown in Figure 2.5c increases the  $V_0$  related defects close to the TE that significantly decreased the switching power for filament formation. Figure 2.6 [22] shows I-V curve of two DC sweep applied to the TE of TiN/ HfO<sub>2</sub> with H-plasma in the midpoint/TiN stack with the lowest  $I_{cc}$ = 50nA [22].

**Figure 2.5** The impact of introducing H-plasma in the  $HfO_2$  layer, (a) after depositing 4 nm of  $HfO_2$  then followed by 1 nm of  $HfO_2$ , (b) after 2 nm of  $HfO_2$  then followed by 3 nm of  $HfO_2$  (c) in the midpoint of 6 nm  $HfO_2$  layer.

**Figure 2.6** On the left the schematic of the device, on the right the I-V curves of two DC sweep of RRAM stack using  $HfO_2$  with H-plasma in the midpoint and TiN as TE.

Source of the I-V curves: [22].

### 2.3.2. HfO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> bilayer

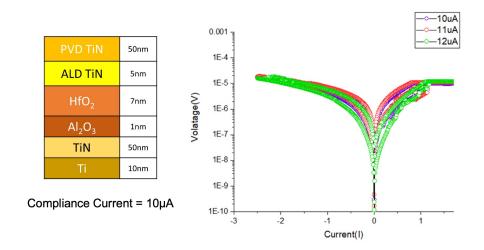

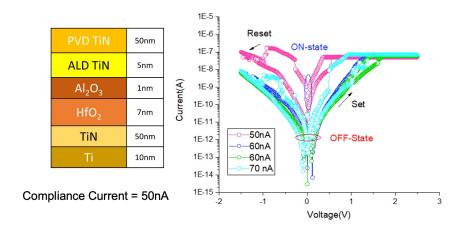

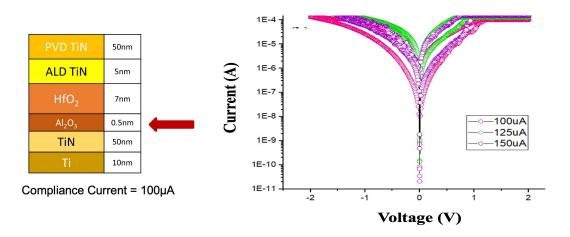

There are several methods to control the  $V_0$  distribution near the TE rather than introducing H-plasma treatment. Caping the HfO<sub>2</sub> with Al<sub>2</sub>O<sub>3</sub> showed reasonable control on  $V_0$ . The position of this caping layer has been investigated in [26]. The study shows the impact of depositing 1 nm Al<sub>2</sub>O<sub>3</sub> between the switching layer and the BE as shown in Figure 2.7, and of depositing 1 nm Al<sub>2</sub>O<sub>3</sub> between the switching layer and the TE as shown in Figure 2.8. The former device shows lower forming power because the  $V_0$  are formed relatively faster in Al<sub>2</sub>O<sub>3</sub> layer than in HfO<sub>2</sub> layer, once they are formed in Al<sub>2</sub>O<sub>3</sub> they stimulate generation for more  $V_0$  in HfO<sub>2</sub>. In addition, the study found that reducing the thickness of the Al<sub>2</sub>O<sub>3</sub> didn't improve the behavior of the device as shown in Figure 2.9 [26].

**Figure 2.7** On the left the schematic of the device, on the right the I-V curves of three DC sweep of RRAM stack using 7 nm HfO<sub>2</sub> with 1 nm Al<sub>2</sub>O<sub>3</sub> near BE. Source of the I-V curves: [26].

**Figure 2.8** On the left the schematic of the device, on the right the I-V curves of four DC sweep of RRAM stack using 7 nm  $HfO_2$  with 1 nm  $Al_2O_3$  near TE. Source of the I-V curves: [26].

**Figure 2.9** On the left the schematic of the device, on the right the I-V curves of three DC sweep of RRAM stack using 7nm  $HfO_2$  with 0.5 nm  $Al_2O_3$  near BE. Source of the I-V curves: [26].

## 2.4. Impact of Top Electrode

The properties of the TE playing a significant role in power reduction since the interface of it with the switching layer impact the  $V_0$  distribution. Higher work function determines a stable resistive switching but the change in barrier height between metal and the dielectric dominates the switching power. Figure 2.10

imported from [22] shows how using Ru as a TE with treated switching layer with H-Plasma instead of TiN with the same switching layer (Figure 2.6) reduced the  $I_{cc}$  from 50 nA to 3 nA. The work function of Ru/HfO<sub>2</sub> is (4.6 eV) which is slightly higher than TiN (4.5 eV). Also, the defects in the switching layer and metal-induced gap states control the barrier height and effect the switching behavior [22].

**Figure 2.10** on the left the schematic of the device, on the right the I-V curves of two DC sweep of RRAM stack using  $HfO_2$  with H-plasma in the midpoint and Ru as a TE.

Source of the I-V curves: [22].

#### 2.5. MLC for In-Memory Computing

The purpose of studying different RRAM stack is finding the low power device to be used for in-memory computing. Such a device should have multi-level cell characteristics (MLC) where we can store more than two bits per the device. This behavior could be achieved in RRAM devices by several method like applying different DC sweeps while changing I<sub>cc</sub>. The former method is not practical for in-memory application since it consumes large power while programing, where other method like applying programing pulses shows a reasonable characteristic that

make the RRAM devices a promising non-volatile memory to be used in a crossbar for in-memory computing [18]. The programing pulses could be a SET or RESET train of pulses, either by fixing the pulse amplitude and varying the pulse width, or by fixing the pulse width while varying the pulse amplitude, in this work we performed both methods and compared their advantages and disadvantages.

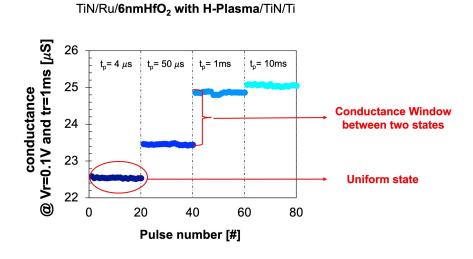

While studying the MLC for any device we are looking for enough conductance (G) window between any two states, uniformity of each conductance state, a good cycling endurance for each state, thermal stability of the stored data in each state, and good immunity of read disturbance [19], Figure 2.7 shows some MLC characteristics that have been mentioned for a pulse measurement of an RRAM device that has a dielectric of 6nm HfO<sub>2</sub> with H-Plasma treatment at the midpoint.

Figure 2.11 MLC Characteristics of pulse measurements data for treated HfO<sub>2</sub>.

#### CHAPTER 3

#### **EXPERIMENTAL SETUP**

#### 3.1. Devices Structures

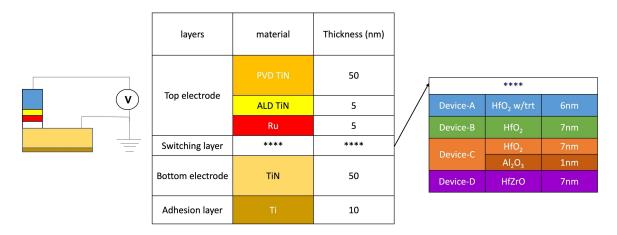

The challenges of selecting the RRAM stack are active research for better reliability, good endurance, reasonable quantization in MLC, and low power consumption. In this work we investigated seven different stacks, that have similar active area diameter of 300  $\mu$ m.

The first four devices have been compared with fixed TE as (PVD TiN/ ALD TiN/Ru), and BE as (PVD TiN/ PVD Ti), while varying the dielectric in the switching layer. All the switching layers deposited using atomic layer deposition technique (ALD) which is executed on TEL Trias<sup>+TM</sup> platform with shower-head type 300mm reactor [25].

Later in chapter 5 the other three devices will be presented. These devices have similar TE as (PVD TiN/ ALD TiN) and switching layer as HfO<sub>2</sub> with H-Plasma treatment, but different BE to study the impact of controlling TiN.

The four devices with different switching layer schematic shown in Figure 3.1, where device-A dielectric is 6nm  $HfO_2$  treated with H-Plasma in the middle, where introducing the plasma showed significant impact on the switching behavior [22] as mentioned in the previous chapter and will be prove by the results in the following chapter. Device-B dielectric is 7nm stochiometric  $HfO_2$ , which has lack of  $V_0$  that effect the switching behavior. Device-C dielectric is bilayer 7nm  $HfO_2$  followed by 1nm  $Al_2O_3$ , where the  $Al_2O_3$  cap increase the  $V_0$  near the TE [23].

Device-D dielectric is 7nm HfZrO, where introducing the Zr to the HfO<sub>2</sub> changed the filament microstructure, reduces the effect of the filament thickness [26].

**Figure 3.1** Schematic of the four devices with different switching layers showing the material stack and relative thickness of each layer.

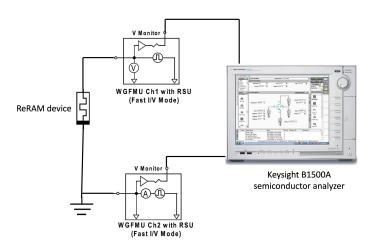

#### 3.2. Electrical Characterizations Tools and Connections

A Keysight B1500 semiconductor device parameter analyzer connected to two wave generator fast measurement units (WGFMU) were used to perform both the current-voltage (I-V) characteristics and pulsed measurements. Where Figure 3.2 shows the measurement setup. The benefit of using WGFMU is keeping the same set-up while moving from dc sweep to pulse application, where it is a mandator to start with forming the device using dc sweep before performing the pulse measurement. In the other hand the WGFMU doesn't provide a compliance current limitation which requires us to carefully select the pulse amplitudes to avoid device damaged during the experiment. One of the WGFM channels connected to the TE of the RRAM device, and the other channel connected to the grounded BE. This connection allows the analyzer to perform the voltage pulses on the TE using the

first channel. And then measure the current pulses using the second channel that connected to the BE, which will be the invers of the measurement that will be read from the analyzer since the BE is grounded.

**Figure 3.2** Block diagram of pulse measurement set-up.

Source: [27].

### 3.3. Forming Process

The conductive switching characteristics are achieved by the formation and rupture of a CF due to the  $V_o$  distribution in the switching layer. Initially, the fresh device is in a high resistance state (HRS). When the voltage is applied to the TE the oxygen ions move toward it while leaving a line of oxygen vacancies inside the oxide to form CF like the soft breakdown of the dielectric [28]. A  $I_{cc}$  limitation is required during this process to avoid irreversible permanent dielectric breakdown. Once the CF is formed the device enter the low resistance state (LRS). When a reversed voltage is applied after the formation a part of the CF will be removed due to the recombination of the oxygen ions with the oxygen vacancies which will switch the

device back from LRS to HRS [23]. We formed all the RRAM devices by applying a DC double sweep to the TE while the  $I_{cc}$  was carefully increased from 1nA to 250 $\mu$ A.

## 3.4. Pulse Operation

In this work we performed three pulse operation on the four RRAM devices (device-A, device-B, device-C, device-D) after forming and resetting each device with voltage sweep.

## 3.4.1. Width-Varying Pulsed Operation

The first experiment was by applying a train of 80 SET pulses without resting where the pulse width changed every 20 pulses ( $t_p$ = 4 $\mu$ s, 50 $\mu$ s, 1ms, 10ms) to make sure that the conductance level reaches a good saturation while keeping the pulse amplitude constant at ( $V_p$ = 2V). Figure 3.3 shows Schematic diagram of complete program cycle of width-varying pulsed operation, where we applied a non-distractive read pulse of pulse amplitude ( $V_r$ =0.1V) and pulse width (tr=1ms) after each pulse to read the conductance of the CF.

**Figure 3.3** Schematic diagram of programed cycle of SET width-varying pulsed operation (off scale).

When the pulses train is applied to the TE the potential drop across the oxide barrier reduces due to the generation of new  $V_o$  which in turns lower the probability

to generate more vacancies and reach a saturation level [18]. Increasing t<sub>p</sub> gives more time to create new vacancies within the pulse and make the oxide rich of substantial number of traps and trap-assisted tunneling contributes to additional conduction reaching higher conductance levels [18, 19].

## 3.4.2. Amplitude-Varying Pulsed Operation

In the second experiment we followed the first experiment steps, but we kept the pulse width constant at ( $t_p$ =1ms) while changing the pulse amplitude ( $V_p$ =0.8V, 1.0V, 1.2V, 1.4V) every 20 pulses. Figure 3.4 shows Schematic diagram of complete program cycle of amplitude-varying pulsed operation.

**Figure 3.4** Schematic diagram of programed cycle of SET amplitude-varying pulsed operation (off scale).

When a sequences of pulses with varying either pulse width or pulse amplitude are applied to the switching device, it will form one of these shapes of CF while increasing  $t_p$  or  $V_p$ ; a thick CF of larger diameter or multiple conducting thin filaments through the insulator stack [23].

#### 3.4.3. Endurance Test

The main factor limiting the large utilization of RRAM devices in commercial systems is regarding to variability and reliability issues that appear in RRAM devices, which are usually evaluated by performing switching endurance tests [29].

The last experiment in the pulse operation was performing 10k endurance cycles for every programing pulse width ( $t_p$ = 4 $\mu$ s, 50 $\mu$ s, 1ms, 10ms).

#### **CHAPTER 4**

### **RESULTS AND DISCUSSIONS**

# 4.1. Forming Process Results

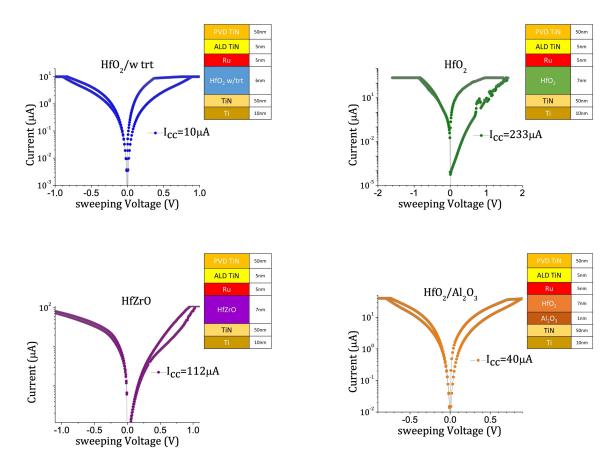

We formed all the RRAM devices by applying a dc double sweep to the TE while the  $I_{CC}$  was carefully increased from 1nA to  $250\mu A$ . Figure 4.1 shows the forming I-V curves of the four RRAM devices that were under investigation in this study, and Table 4.1 list the forming voltages ( $V_{forming}$ ), the minimum  $I_{CC}$  that form the device, and forming power ( $I_{CC} \times V_{forming}$ ).

**Figure 4.1** Forming I-V curves of the four RRAM devices with oxide control showing the minimum  $I_{\text{CC}}$ .

**Table 4.1** List The Forming Voltages ( $V_{forming}$ ), The Minimum  $I_{CC}$  That Form The Device, And Forming Power ( $I_{CC} \times V_{forming}$ )

| Device   | Device's Dielectric                                       | l <sub>cc</sub> | ${f V}_{ m forming}$ | Forming Power<br>(I <sub>cc</sub> xV <sub>forming</sub> ) |

|----------|-----------------------------------------------------------|-----------------|----------------------|-----------------------------------------------------------|

| Device-A | 6nmHfO <sub>2</sub> w/trt                                 | 10 μΑ           | 0.94 V               | 9.4 μW                                                    |

| Device-B | 7nm HfO <sub>2</sub>                                      | 233 μΑ          | 1.36 V               | 316.88 μW                                                 |

| Device-C | 7nm HfO <sub>2</sub> / 1nm Al <sub>2</sub> O <sub>3</sub> | 40 µA           | 0.89 V               | 35.6 μW                                                   |

| Device-D | 7nm HfZrO                                                 | 112 µA          | 1.04 V               | 116.48 μW                                                 |

It is clear from Table 4.1 that the device with treated HfO<sub>2</sub> denoted as device-A shows the lowest forming power which attributed to the extra oxygen vacancies due to hydrogen plasma that have been introduced during the deposition of a 6nm thick HfO<sub>2</sub> layer as shown in Figure 4.2. This process step may enrich the oxide HfO<sub>2</sub> near the top electrode with oxygen vacancies which in turn will reduce the switching power and improve the switching behavior compering to the oxide without the plasma treatment [22].

**Figure 4.2** Treated device deposition steps, deposit 3 nm HfO<sub>2</sub> by ALD then introduce H-Plasma and after that deposit another 3 nm HfO<sub>2</sub> by ALD.

Since higher concentration of oxygen vacancies near to the top electrode reduces the switching power [23], the device with bilayer HfO<sub>2</sub> and Al<sub>2</sub>O<sub>3</sub> denoted as device-C becomes the second on the low forming power list after device-A. That

attributed to the insertion of 1nm Al<sub>2</sub>O<sub>3</sub> buffer layer under the 7nm HfO<sub>2</sub>. hence the oxygen vacancies are formed relatively faster in Al<sub>2</sub>O<sub>3</sub> layer than in HfO<sub>2</sub> layer, once they are formed in Al<sub>2</sub>O<sub>3</sub> they stimulate generation for more oxygen vacancies in HfO<sub>2</sub> [23]. For the device with HfZrO denoted as device-D Therefore, the addition of Zr into HfO<sub>2</sub> mends the filament microstructure, reduces the effect of the filament thickness which will improve the reliability after stress [26]. The last on the low forming power list is the device with stochiometric HfO<sub>2</sub> denoted as device-B which prove that the lowest of oxygen vacancies near the top will consume the highest forming power.

## 4.2. Width-Varying Pulsed Operation Results

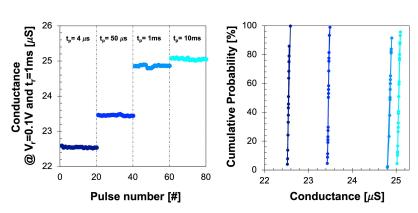

For device-A (6nm HfO<sub>2</sub> with H-plasma treatment) Figure 4.3 shows the four expected states with no overlap and a good window between states for pulse widths ( $t_P$ = 4 $\mu$ s, 50 $\mu$ s, 1ms), we noticed reduction in window between states generated from pulse widths (1ms) and (10ms) which is the opposite case with device-D (7nm HfZrO) the good window between states appeared with higher pulse widths as shown in 4.6.

While Figure 4.4 of device-B with no treatment shows two states out of four expected states, which may be caused by a formation of interfacial oxide layer between the electrode and the oxide that make the device stuck with the same LRS [19].

# **Device-A**TiN/Ru/**6nmHfO**<sub>2</sub> with **H-Plasma**/TiN/Ti

**Figure 4.3** Measured conductance modulation obtained by applying successive SET pulse sequences with increasing  $t_p$  and the experimental cumulative probability distributions of the states for device-A (6nm HfO<sub>2</sub> with H-plasma treatment).

**Figure 4.4** Measured conductance modulation obtained by applying successive SET pulse sequences with increasing  $t_p$  and the experimental cumulative probability distributions of the states for device-B (7 nm stochiometric HfO<sub>2</sub>).

Pulsed with high width gives more time during the pulse to generate more oxygen vacancies which will apply more stress to the device. That make device-D and device-C stabler than device-A under high stress as shown in Figures 4.5 and

4.6. Table 4.2 shows summary of the comparison that made in this section between the four RRAM devices.

**Figure 4.5** Measured conductance modulation obtained by applying successive SET pulse sequences with increasing  $t_p$  and the experimental cumulative probability distributions of the states for Device-C (7nm HfO<sub>2</sub>/1nm Al<sub>2</sub>O<sub>3</sub>).

**Figure 4.6** Measured conductance modulation obtained by applying successive SET pulse sequences with increasing  $t_p$  and the experimental cumulative probability distributions of the states for Device-D (7nm HfZrO).

**Table 4.2** Comparison Of Conductance States That Have Been Generated In The Four RRAM Devices With Width-Varying Pulsed Operation

| Device   | Device's dielectric                                       | Number of<br>states<br>out of 4 | Conductance Window between |          |          |  |

|----------|-----------------------------------------------------------|---------------------------------|----------------------------|----------|----------|--|

|          |                                                           |                                 | G1-G2                      | G2-G3    | G3-G4    |  |

| Device-A | 6nmHfO <sub>2</sub> w/trt                                 | 4                               | 0.927 μS                   | 1.322 µS | 0.276 μS |  |

| Device-B | 7nm HfO <sub>2</sub>                                      | 2                               | 3.993 µS                   | 0        | 0        |  |

| Device-C | 7nm HfO <sub>2</sub> / 1nm Al <sub>2</sub> O <sub>3</sub> | 4                               | 0.678 μS                   | 0.234 μS | 0.56 μS  |  |

| Device-D | 7nm HfZrO                                                 | 4                               | 0.618 μS                   | 0.318 µS | 1.716 µS |  |

# 4.3. Amplitude-Varying Pulsed Operation Results

It was found that the conductance level increased with small change while increasing the pulsed width with fixed pulse amplitude from the previous section. But for a fixed pulse width the increasing in the conductance level was found to be larger while increasing pulsed amplitude with noticeable fluctuation within the same conductance level. The fluctuation from cycle to cycle within the same device and same state level attributed to the stochastic nature of the oxygen vacancies/ions processes, as mentioned in [30], it could be smothered with low pulse width since we demonstrated the amplitude-varying with high pulse width (tp=1ms).

Device-A (6nm HfO2 with plasma treatment) Figure 4.7 shows higher range of conductance level with amplitude-varying pulsed operation than that had been achieved with width-varying pulsed operation, but with better MLC characteristics. It could be because with width-varying we use 2V amplitude (higher voltage regime) which produce Fowler–Nordheim (F–N) tunneling that cause induvial electrons to escape from the device and lower the conductance value [31] [32], but it cannot

be proved with rustles that was taken in the room temperature only. After that we perform amplitude-varying at lower voltages but with large pulse width that allow more oxygen vacancies to be generated in the oxide and make it rich of substantial number of traps and trap-assisted tunneling leads to higher conduction [32].

**Figure 4.7** Measured conductance modulation obtained by applying successive SET pulse sequences with increasing  $V_p$  and the experimental cumulative probability distributions of the states for device-A (6nm HfO<sub>2</sub> with H-plasma treatment).

While device-C (7nm HfO<sub>2</sub>/1nm Al<sub>2</sub>O<sub>3</sub>) Figure 4.8 shows settled conductance state range with both pulsed operations and has the best endurance compared to the other three devices, since it exposes stability with 10k endurance cycles with small degradation of (1ms) pulse width but with the lowest fluctuations in all states as shown in Figure 4.13. These features of device-C make it possible to obtain quasi-analog behavior, which is important for in-memory computing [33].

**Figure 4.8** Measured conductance modulation obtained by applying successive SET pulse sequences with increasing  $V_p$  and the experimental cumulative probability distributions of the states for Device-C (7nm HfO<sub>2</sub>/1nm Al<sub>2</sub>O<sub>3</sub>).

**Figure 4.9** Measured conductance modulation obtained by applying successive SET pulse sequences with increasing  $V_p$  and the experimental cumulative probability distributions of the states for Device-D (7nm HfZrO).

For device-D (7nm HfZrO) Figure 4.9 shows four conductance states that was demonstrated out of four expected states, with remarkable smoothness at pulse amplitudes (1.2V and 1.4V) due to the addition of Zr as mentioned earlier that mends the filament microstructure since the HfZrO has high dielectric constant

under processing conditions [26] [34] [35], however device-C shows more stability than device-D with 10k endurance cycles experiment as clear in Figures 4.13 and 4.14. Hence the effect of amplitude-varying is stronger than width-varying as mentioned previously the behavior of device-B was improved to demonstrate three discrete states out of four with no overlapping as shown in Figure 4.10.

**Figure 4.10** Measured conductance modulation obtained by applying successive SET pulse sequences with increasing  $V_p$  and the experimental cumulative probability distributions of the states for device-B (7 nm stochiometric HfO<sub>2</sub>).

It is clear from Figure 4.11 that the effect of changing pulse amplitude is stronger than changing the pulse width on the RRAM devices for all type of dielectrics in this study. While the width-varying leads to linearity between conductance stats the amplitude-varying shows exponential behavior [31]. The linearity eases controlling the states of the device, however a large window between states makes the amplitude-varying operation better to achieve a good MLC characteristic since it will reduce the read/write disturbance. Table 4.3 shows

summary of the comparison that made in this section between the four RRAM devices.

**Figure 4.11** Average RRAM conductance was plotted against varying (a) SET pulse width and (b) SET pulse amplitude.

**Table 4.3** Comparison Of Conductance States That Have Been Generated In The Four RRAM Devices With Amplitude-Varying Pulsed Operation

| Device   | Device's dielectric                                       | Number of states out of 4 | Conductance Window Between |          |          |  |

|----------|-----------------------------------------------------------|---------------------------|----------------------------|----------|----------|--|

|          |                                                           |                           | G1-G2                      | G2-G3    | G3-G4    |  |

| Device-A | 6nmHfO <sub>2</sub> w/trt                                 | 4                         | 0.862 μS                   | 3.255 µS | 1.123 µS |  |

| Device-B | 7nm HfO <sub>2</sub>                                      | 3                         | 0.996µS                    | 2.33µS   | 0.066µS  |  |

| Device-C | 7nm HfO <sub>2</sub> / 1nm Al <sub>2</sub> O <sub>3</sub> | 4                         | 1.699 µS                   | 3.681 µS | 1.670 μS |  |

| Device-D | 7nm HfZrO                                                 | 4                         | 0.721 μS                   | 2.320 µS | 0.891 μS |  |

#### 4.4. Endurance Test Results

A reasonable endurance was obtained with all RRAM devices that were fabricated in this study with some disparity between them. Figure 4.12 shows the endurance of device-A (6nm HfO<sub>2</sub> with plasma treatment), as with pulse width  $t_p$ =4 $\mu$ s we observed after 100 cycles a small raising in the conductance values due to new oxygen vacancies that has been generated while increasing the number of pulses. However, with pulse width  $t_p$ =1ms after 450 cycles the conductance level degraded with small amount that could be caused by overstress of the CF [33].

**Figure 4.12** Measured conductance values just after SET transition during 10k endurance cycles for every programing pulse width (tp=  $4\mu s$ ,  $50\mu s$ , 1ms, 10ms) for the device-A (6nm HfO<sub>2</sub> with H-plasma treatment).

Figure 4.13 shows the endurance of device-B (7nm HfO<sub>2</sub>) where the fluctuation starts with pulse width  $t_p$ =50 $\mu$ s which is expected with such a device with no buffer layer.

**Figure 4.13** Measured conductance values just after SET transition during 10k endurance cycles for every programing pulse width (tp=  $4\mu s$ ,  $50\mu s$ , 1ms, 10ms) for the device-B (7 nm stochiometric HfO<sub>2</sub>).

Figure 4.14 shows excellent endurance that obtained with device-C (7nm  $HfO_2/1nm Al_2O_3$ ) due to  $Al_2O_3$  below  $HfO_2$  caping which could allow more control on the formation of CF that consist of oxygen vacancies over the Al atoms that diffused form  $Al_2O_3$  layer and reduces oxygen vacancies generation energy near the Al atoms [16].

**Figure 4.14** Measured conductance values just after SET transition during 10k endurance cycles for every programing pulse width (tp=  $4\mu s$ ,  $50\mu s$ , 1ms, 10ms) for the device-C (7nm HfO<sub>2</sub>/1nm Al<sub>2</sub>O<sub>3</sub>).

Figure 4.15 shows changed in conductive value in device-D after 200 cycled for all programing pulsed widths, could be attributed to its bond structure [14].

**Figure 4.15** Measured conductance values just after SET transition during 10k endurance cycles for every programing pulse width (tp=  $4\mu s$ ,  $50\mu s$ , 1ms, 10ms) for the device-D (7nm HfZrO).

## 4.5. Conductance quantization

Since device-A (6nm HfO<sub>2</sub> with H-plasma treatment) shows the lowest forming power and a reasonable conductance quantization, we perform another pulsed operation with proper pulse width variation and pulse amplitude, by applying 120 SET pulses with fixed  $V_p$ =1V and changing tp every 10 pulses starting with  $t_p$ =4 $\mu$ s with increasing step 20 $\mu$ s.

Figure 4.16 shows the conductance quantization with no overlap between the states. Which make the treated device a promising candidate to be used as a two-terminals device in a crossbar for in-memory computing and for implementing artificial synopses for neuromorphic computing.

**Figure 4.16** Quantization of measured conductance obtained by applying successive SET pulse sequences with increasing  $t_{\text{p}}$  for device-A (6nm HfO<sub>2</sub> with H-plasma treatment).

#### **CHAPTER 5**

#### IMPACT OF BOTTOM ELECTRODE ON SWITCHING CHARACTERISTICS

#### 5.1. Device Structures

Engineering the distribution of defects or oxygen vacancies near the top and bottom electrodes has a significant impact on reducing the switching power and improving the multi-level cell (MLC) characteristics of the device. A graded distribution with higher concentration of oxygen vacancies closer to the top electrode (TE) due to hydrogen plasma treatment and lower concentration near the bottom electrode (BE) reduces switching power [22]. Figure 5.1 shows a schematic of the  $V_{\circ}$  distribution inside the oxide.

**Figure 5.1** Schematic of RRAM device showing the desirable  $V_o$  distribution inside the oxide layer, which is more  $V_o$  near the TE.

This chapter presented the results of studying three RRAM stacks as shown in Figure 5.2 that have the same TE (50nm PVD TiN/5nm ALD TiN) and dielectric (HfO<sub>2</sub> with hydrogen plasma treatment at the mid-point) but with different BE for each stack: TiN (device-E (control)), TiN plus Mo with thermal anneal (device F), and TiN plus Mo with plasma nitridation (device G).

**Figure 5.2** Schematic of RRAM stacks that have the same TE and dielectric but different BE (a) TiN (device-E (control)), (b) TiN plus Mo with thermal anneal (device-F), (c) TiN plus Mo with plasma nitridation (device-G).

## **5.2. Forming Process and Results**

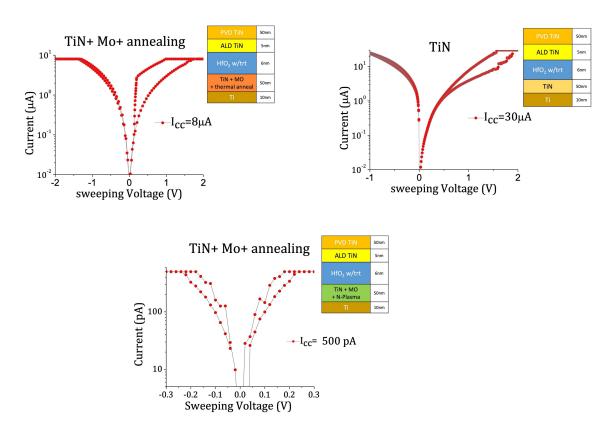

We formed all the RRAM devices by applying a DC double sweep to the TE and grounded the BE where the  $I_{CC}$  was carefully increased from 1nA to  $50\mu$ A. While forming the devices device-G with (TiN plus Mo with plasma nitridation) at the BE shows switching at 1nA, then we apply lower  $I_{CC}$  and found several devices on the wafer that switched at 500pA. Figure 5.3 shows the forming I-V curves of the three RRAM devices, and Table 5.1 list the forming voltages ( $V_{forming}$ ), the minimum  $I_{CC}$  that form the device, and forming power ( $I_{CC} \times V_{forming}$ ).

Selecting inert metal as a BE provides a lower  $V_o$  concentration at the interface between the BE and the dielectric [36]. which in turn reduces the switching power as noted with device-G (TiN plus Mo with plasma nitridation). It is possible that the presence of nitrogen prevents the decrease in  $V_o$  concentration near the BE. Where the  $N_2$  molecules reach the grain boundary then the active nitrogen atoms connect to the Hf ion dangling bonds as their lone-pair electrons.

Since the bonding energy of the Hf–N bond is very low (535ev) compared to Hf–O bond (801ev) [37], then the oxygen ions move toward the TE and reduce the forming voltage.

**Figure 5.3** Forming I-V curves of the three RRAM devices with BE control showing the minimum I<sub>CC</sub>.

On the other hand, a higher concentration of  $V_o$  at the BE and the dielectric interface leads to a larger magnitude of band bending and increases the height of Schottky barrier. This possibly leads to an increase in the switching power in device-E and device-F as compared to device-G [37]. Device-E (TiN) switched at  $I_{CC}$  =30 $\mu$ A and device-F (TiN plus Mo with thermal anneal) switched at  $I_{CC}$  =8 $\mu$ A,

which is superior compared to device-E in switching power. This suggests that the alloy of TiN with Mo is reducing the  $V_o$  near the BE.

**Table 5.1** List The Forming Voltages ( $V_{forming}$ ), The Minimum  $I_{CC}$  That Form The Device, And Forming Power ( $I_{CC} \times V_{forming}$ )

| Device   | Device's BE                   | l <sub>cc</sub> | <b>V</b> <sub>forming</sub> | Forming Power<br>(I <sub>cc</sub> xV <sub>forming</sub> ) |

|----------|-------------------------------|-----------------|-----------------------------|-----------------------------------------------------------|

| Device-E | TiN                           | 30 μΑ           | 1.8 V                       | 54 μW                                                     |

| Device-F | TiN + Mo + thermal anneal     | 8 μΑ            | 1.6 V                       | 12.8 μW                                                   |

| Device-G | TiN + Mo + plasma nitridation | 500 pA          | 0.25 V                      | 125 pW                                                    |

## 5.3. RESET Pulsed Operation and Results

To study the MLC characteristics of the devices, we performed a train of 36 RESET pulses with fixed amplitude  $V_p$ = -1V and pulse width starting at 4 $\mu$ s and increasing by 20 $\mu$ s every 3 pulses, while we applied  $V_r$ =0.1V and  $V_r$ =10 $\mu$ s after each pulse to measure the conductance Figure 5.4 shows the schematic of the pulse train.

**Figure 5.4** Schematic diagram of programed cycle of RESET width-varying pulsed operation (off scale).

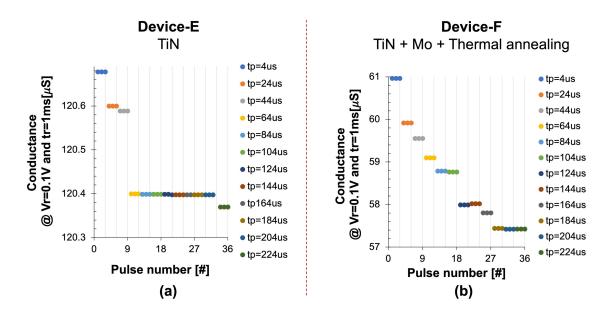

Figure 5.5a shows that device-F (TiN plus Mo with thermal anneal) has good MLC with no overlap between the states while device-E has unstable MLC behavior as shown in Figure 5.5b due to time constant variation.

**Figure 5.5** Measured conductance modulation obtained by applying successive RESET pulse sequences with increasing  $t_p$  and for (a) Device-E (TiN) (b) Device-F (TiN+ Mo+ Thermal annealing).

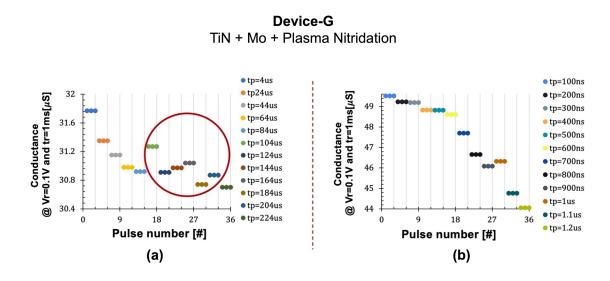

**Figure 5.6** Measured conductance modulation obtained by applying successive RESET pulse sequences with increasing  $t_p$  and for Device-G (TiN + Mo+ Plasma Nitridation) (a)  $t_p$  in microseconds (b)  $t_p$  in nanoseconds.

Figure 5.6a shows the results of device-G for the same RESET pulse train that was applied to devices-E and devices-F. Since device-G switched at a very

low current and voltage, the conductance quantization was unstable after 15 pulses due to overstress of the conductive filament. Wherefore we programed anther RESET pulse train with nanoseconds pulse width. We performed a train of 36 RESET pulses with fixed amplitude  $V_p$ = -0.5V and pulse width starting at 100ns and increasing by 100ns every 3 pulses, while we applied  $V_r$ =0.05V and  $t_r$ =100ns after each pulse to measure the conductance Figure 5.6b shows the improve conductance quantization of device-G.

#### CHAPTER 6

## **CONCLUSION AND FUTURE WORK**

#### 6.1. Conclusion

RRAM is a promising device to be used for in-memory computing due to its low power consumption, compatibility with CMOS, high density storge, high reliability, MLC characteristics and reasonable endurance. Since selecting the material of each layer of the RRAM device is impact the switching behavior and the power consumption by the device, in this work chapters 3 and 4 presented the study four different dielectrics: (a) HfO<sub>2</sub> with plasma treatment (b) HfO<sub>2</sub>, (c) HfO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> bilayer, and (d) HfZrO. By forming and characterizing the multi-level conductance behavior with pulse width variation, pulse amplitude variation and endurance test.

The H-plasma Treated HfO<sub>2</sub> showed the lowest power requirement and excellent multi-level conductance quantization for pulse width variation measurements, due to the presence of the H-plasma at the midpoint of the switching layer. In addition to the Ru as TE, where its deposition process plays a role in power reduction as found from previous studies. While proper selection of pulse width and amplitude can make the devices perform efficiently.

HfO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> bilayer showed stability in conductance range in both pulse width and amplitude variation, while the forming power is higher than the treated device, but the endurance test is showing better uniformity.

The results show how the distribution of  $V_{\circ}$  plays a significate role in conductance quantization. The more  $V_{\circ}$  near the TE and lower near the BE reduce the power consumption and improve the MLC characteristics.

After studying the impact of the dielectric, we studied tree different devices with varying the BE, while chapter 5 presented the process and the results. compared to TiN we have observed that TiN Annealed Mo devices showed much lower switching energy and conductance quantization. It can be assumed that bottom electrode metal/alloy can have some significant impact on RRAM performance.

While we are evaluating devices with TiN-Mo exposed N-plasma as bottom electrode we surprised with several devices that switched at 500 pA. The presence of N-plasma also led to better conductance quantization with nanoseconds pulse width than in microsecond pulse width.

#### 6.2. Future Work

For future work, studying the impact of different nitrogen flow in BE will be the next step in this research. In addition to the physical analysis such as High-resolution transmission electron microscopy (TEM) and X-ray photoelectron spectroscopy (XPS) that could be used to examine the structure and concentration of  $V_0$  for better understanding of the electrical analysis results.

#### REFERENCES

- [1] Sebastian, A.; Gallo, M.L.; Khaddam-Aljameh, R.; Eleftheriou, E., "Memory devices and applications for in-memory computing", Nature Nanotechnology, vol. 15, 2020, DOI: https://doi.org/10.1038/s41565-020-0655-z.

- [2] Zou, X.; Xu, Sh.; Chen, X.; Yan, L.; Han, Y., "Breaking the von Neumann bottleneck: architecture-level processing-in-memory technology", Science China, vol. 64, 2021, DOI: https://doi.org/10.1007/s11432-020-3227-1.

- [3] Mittal, S., "A Survey of ReRAM-Based Architectures for Processing-In-Memory and Neural Networks", Mach Learn Knowl Extr, 2018, DOI: https://doi.org/10.3390/make1010005.

- [4] Chen, W. H.; Li, K. X.; Lin, W. Y., "A 65 nm 1 Mb nonvolatile computing-in-memory ReRAM macro with sub-16 ns multiplyand- accumulate for binary DNN Al edge processors" In: Proceedings of IEEE International Solid-State Circuits Conference, San Francisco, 2018. DOI:10.1109/ISSCC.2018.8310400.

- [5] Chen, A., "A review of emerging non-volatile memory (NVM) technologies and applications", Solid-State Electronics 125, 2016, DOI: 10.1016/J.SSE.2016.07.006.

- [6] Ielmini, D., Wong, H.-S.; "In-memory computing with resistive switching devices", Nature Electronics, vol. 1, 2018, DOI:10.1038/s41928-018-0092-2.

- [7] Zhirnov, V. V.; Marinella, M. J.," In Emerging Nanoelectronic Devices", eds Chen, A. Ch. 3 Wiley Online Library, 2015.

- [8] Wong, H.-S. P.; Salahuddin, S., "Memory leads the way to better computing", Nature Nanotechnology, vol. 10, 2015, DOI:10.1038/nnano.2015.29.

- [9] Xie, Y.; Zhao, J, "Emerging Memory Technologies," in IEEE Micro, vol. 39, no. 1, pp. 6-

- 7, February 2019, DOI: 10.1109/MM.2019.2892165.

- [10] Banerjee, W., "Challenges and Applications of Emerging Nonvolatile Memory Devices," Electronics, vol. 9, no. 6, p. 1029, 2020, DOI: https://doi.org/10.3390/electronics9061029.