# **Copyright Warning & Restrictions**

The copyright law of the United States (Title 17, United States Code) governs the making of photocopies or other reproductions of copyrighted material.

Under certain conditions specified in the law, libraries and archives are authorized to furnish a photocopy or other reproduction. One of these specified conditions is that the photocopy or reproduction is not to be "used for any purpose other than private study, scholarship, or research." If a, user makes a request for, or later uses, a photocopy or reproduction for purposes in excess of "fair use" that user may be liable for copyright infringement,

This institution reserves the right to refuse to accept a copying order if, in its judgment, fulfillment of the order would involve violation of copyright law.

Please Note: The author retains the copyright while the New Jersey Institute of Technology reserves the right to distribute this thesis or dissertation

Printing note: If you do not wish to print this page, then select "Pages from: first page # to: last page #" on the print dialog screen

The Van Houten library has removed some of the personal information and all signatures from the approval page and biographical sketches of theses and dissertations in order to protect the identity of NJIT graduates and faculty.

#### ABSTRACT

### HIGH-PERFORMANCE LEARNING SYSTEMS USING LOW-PRECISION NANOSCALE DEVICES

#### by Nandakumar Sasidharan Rajalekshmi

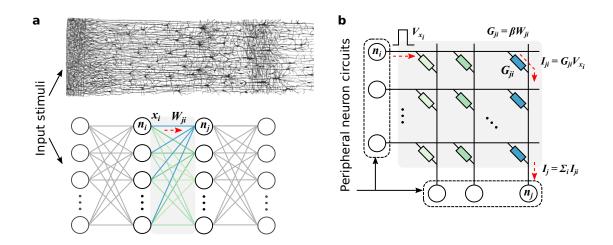

Brain-inspired computation promises a paradigm shift in information processing, both in terms of its parallel processing architecture and the ability to learn to tackle problems deemed unsolvable by traditional algorithmic approaches. The computational capability of the human brain is believed to stem from an interconnected network of 100 billion compute nodes (neurons) that interact with each other through approximately 10<sup>15</sup> adjustable memory junctions (synapses). The conductance of synapses is modifiable allowing the network to learn and perform various cognitive functions. Artificial neural networks inspired by this architecture have demonstrated even super-human performance in many complex tasks.

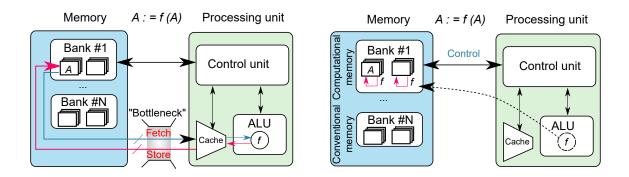

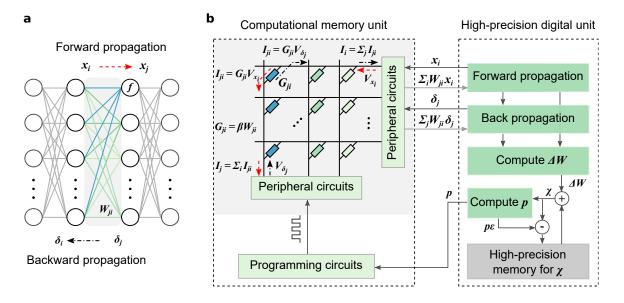

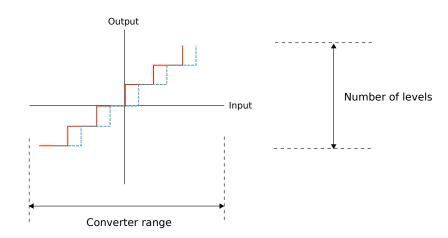

Computational systems based on the von Neumann architecture, however, are ill-suited to optimize and operate these large networks, as they have to constantly move data between the physically separated processor and memory units. Crossbar arrays of nanoscale analog memory devices could store large network weight matrices in their respective conductances and could perform matrix operations without moving the weights to a processor. While this 'in-memory computation' provides an efficient and scalable architecture, the trainability of the memory devices is constrained by their limited precision, stochasticity, and non-linearity, and therefore poses a major challenge.

In this dissertation, a mixed-precision architecture is proposed which uses a high-precision digital memory to compensate for the limited precision of the synaptic devices during the training of deep neural networks. In the architecture, the desired weight updates are accumulated in high-precision and transferred to the synaptic devices when the accumulated update exceeds a threshold representing the average device update granularity. Deep neural networks based on experimental nanoscale devices are shown to achieve performance comparable to high-precision software simulations by this approach.

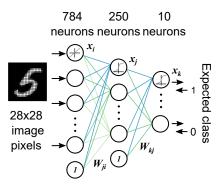

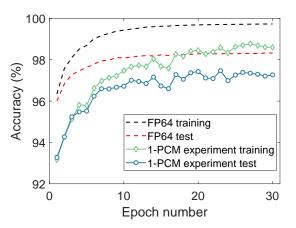

Phase-change memory devices (PCM) on a prototype chip from IBM is used to experimentally demonstrate the proposed architecture. Artificial neural networks whose synapses are realized using PCM devices are trained to classify handwritten images from the MNIST dataset and the mixed-precision approach is successful in achieving training accuracies comparable to floating-point simulations. On-chip inference experiment using the PCM devices shows that the network states are retained reliably for more than  $10^6$  s. The architecture is estimated to achieve approximately  $20 \times$  acceleration in training these networks compared to high-precision implementations and has a potential for at least  $100 \times$  efficiency gain in inference.

Supervised training and inference of third generation spiking neural networks using PCM are also demonstrated using the hardware platform. New array level conductance scaling methods are demonstrated for adaptive mapping of the device conductance to network weights and to compensate for the effect of conductance drift. During the course of the study, Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> based PCM and Cu/SiO<sub>2</sub>/W based resistive random access memories are characterized for their gradual conductance modulation behavior and statistically accurate models are created. The models are used to pre-validate the experiments and to test the efficacy of different synapse configurations in the training of neural networks.

Collectively, this work demonstrates the feasibility of realizing high-performance learning systems that use low-precision nanoscale memory devices, with accuracies comparable to those obtained from high-precision software training. Such learning systems could have widespread applications including for energy and memory constrained edge computing and internet of things.

## HIGH-PERFORMANCE LEARNING SYSTEMS USING LOW-PRECISION NANOSCALE DEVICES

by Nandakumar Sasidharan Rajalekshmi

A Dissertation Submitted to the Faculty of New Jersey Institute of Technology in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy in Electrical Engineering

Helen and John C. Hartmann Department of Electrical and Computer Engineering

May 2019

Copyright  $\bigodot$  2019 by Nandakumar Sasidharan Rajalekshmi<br/> ALL RIGHTS RESERVED

# APPROVAL PAGE

# HIGH-PERFORMANCE LEARNING SYSTEMS USING LOW-PRECISION NANOSCALE DEVICES

# Nandakumar Sasidharan Rajalekshmi

| Dr. Bipin Rajendran, Dissertation Advisor<br>Associate Professor of Electrical and Computer Engineering, NJIT    | Date |

|------------------------------------------------------------------------------------------------------------------|------|

| Dr. Abu Sebastian, Committee Member<br>Research Staff Member, IBM Research Zurich                                | Date |

| Dr. Durgamadhab Misra, Committee Member<br>Professor of Electrical and Computer Engineering, NJIT                | Date |

| Dr. Osvaldo Simeone, Committee Member<br>Professor of Electrical and Computer Engineering, NJIT                  | Date |

| Dr. Hieu Pham Trung Nguyen, Committee Member<br>Assistant Professor of Electrical and Computer Engineering, NJIT | Date |

#### **BIOGRAPHICAL SKETCH**

| Author: | Nandakumar Sasidharan Rajalekshmi |

|---------|-----------------------------------|

| Degree: | Doctor of Philosophy              |

| Date:   | May 2019                          |

#### Undergraduate and Graduate Education:

- Doctor of Philosophy in Electrical Engineering, New Jersey Institute of Technology, Newark, NJ, 2019

- Master of Technology in Microelectronics, Indian Institute of Technology Bombay, Mumbai, India, 2016

- Bachelor of Technology in Electrical and Communication Engineering, College of Engineering, Thiruvananthapuram, Kerala, India, 2013

Major: Electrical Engineering

#### **Presentations and Publications:**

- S. Nandakumar, M. Le Gallo, I. Boybat, B. Rajendran, A. Sebastian, and E. Eleftheriou, "A phase-change memory model for neuromorphic computing," *Journal of Applied Physics*, vol. 124, no. 15, p. 152135, October 2018.

- S. Nandakumar, S. R. Kulkarni, A. V. Babu, and B. Rajendran, "Building braininspired computing systems: examining the role of nanoscale devices," *IEEE Nanotechnology Magazine*, vol. 12, no. 3, pp. 19–35, September 2018.

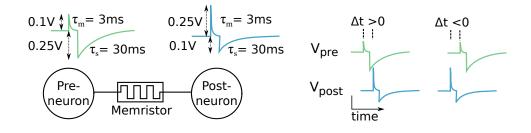

- I. Boybat, M. Le Gallo, S. Nandakumar, T. Moraitis, T. Parnell, T. Tuma, B. Rajendran, Y. Leblebici, A. Sebastian, E. Eleftheriou, "Neuromorphic computing with multi-memristive synapses," *Nature Communications*, vol. 9, no. 1, p. 2514, June 2018.

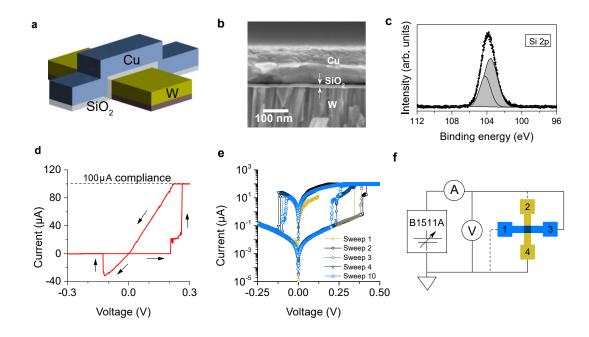

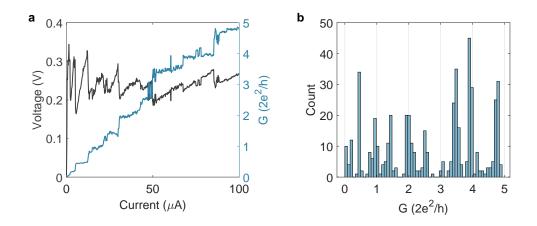

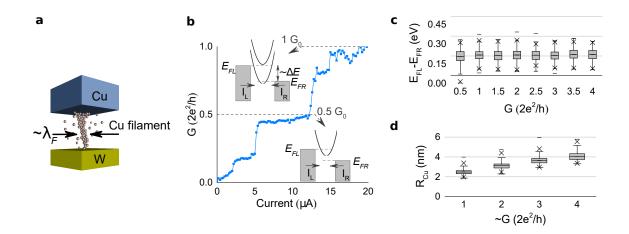

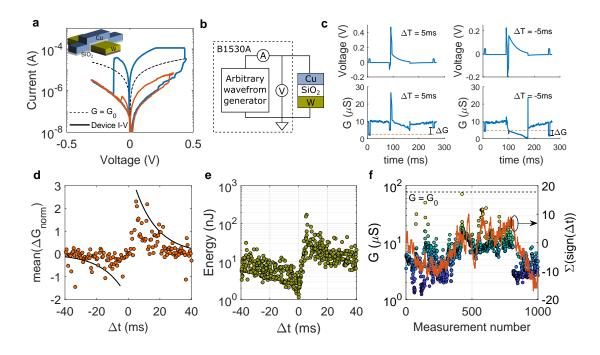

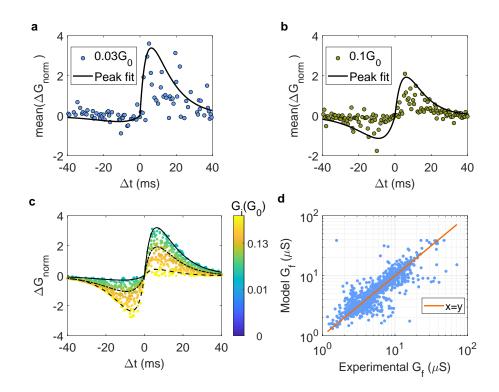

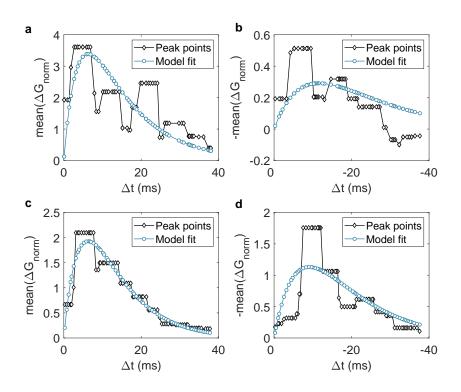

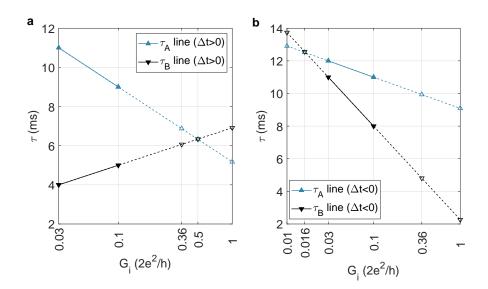

- S. Nandakumar, M. Minvielle, S. Nagar, C. Dubourdieu, and B. Rajendran, "A 250 mV Cu/SiO<sub>2</sub>/W memristor with half-integer quantum conductance states," Nano Letters, vol. 16, no. 3, pp. 1602–1608, March 2016.

- S. Nandakumar, M. Le Gallo, I. Boybat, B. Rajendran, A. Sebastian, and E. Eleftheriou, "Mixed-precision architecture based on computational memory for training deep neural networks," *In Proceedings of the IEEE International Symposium on Circuits and Systems (ISCAS)*, 2018, pp. 1–5.

- I. Boybat, S. Nandakumar, M. Le Gallo, B. Rajendran, Y. Leblebici, A. Sebastian, E. Eleftheriou, "Impact of conductance drift on multi-PCM synaptic architectures," In Proceedings of the 18th Non-Volatile Memory Technology Symposium (NVMTS), 2018, pp. 1-4.

- I. Boybat, M. Le Gallo, S. Nandakumar, B. Rajendran, Y. Leblebici, A. Sebastian, E. Eleftheriou, "Multi-PCM synapses for spiking neural networks," *European Phase-Change and Ovonic Symposium*, 2018

- S. Nandakumar, I. Boybat, M. Le Gallo, A. Sebastian, B. Rajendran, and E. Eleftheriou, "Supervised learning in spiking neural networks with MLC PCM synapses," In Proceedings of the 75th Annual Device Research Conference (DRC), 2017, vol. 22, no. 2, pp. 1–2.

- I. Boybat, M. Le Gallo, S. Nandakumar, T. Moraitis, T. Tuma, B. Rajendran, A. Sebastian, E. Eleftheriou, "An efficient synaptic architecture for artificial neural networks," *In Proceedings of the 17th Non-Volatile Memory Technology* Symposium (NVMTS), 2017, pp. 1–4.

- S. Nandakumar and B. Rajendran, "Synaptic plasticity in a memristive device below 500mV," *ECS Transactions*, vol. 77, no. 2, pp. 31–37, Apr. 2017.

- S. Nandakumar and B. Rajendran, "Verilog-A compact model for a novel Cu/SiO<sub>2</sub>/W quantum memristor," In Proceedings of the International Conference on Simulation of Semiconductor Processes and Devices (SISPAD), 2016, no. 973, pp. 169–172.

- S. Nandakumar and B. Rajendran, "Physics-based switching model for Cu/SiO<sub>2</sub>/W quantum memristor," In Proceedings of the 74th Annual Device Research Conference (DRC), 2016, vol. 16, no. 973, pp. 1–2.

- C. Shetty, Sri Nitchith, Rishabh Rawat, S. Nandakumar, Pritesh Shah, Shruti Kulkarni, and Bipin Rajendran, "Live demonstration: Spiking neural circuit based navigation inspired by C. elegans thermotaxis," In Proceedings of the IEEE International Symposium on Circuits and Systems (ISCAS), 2015, pp. 1905–1905.

For all those who let me be...

#### ACKNOWLEDGMENT

I express my sincere gratitude to my advisor Prof. Bipin Rajendran who has been a constant support and spent countless hours to improve various aspects of my Ph.D. research life. I would like to thank Dr. Abu Sebastian and Dr. Evangelos Eleftheriou for providing the many research opportunities, support, and guidance at IBM Research Zurich. I sincerely thank my dissertation committee members, Prof. Durgamadhab Misra, Prof. Osvaldo Simeone, and Prof. Hieu Pham Trung Nguyen for providing guidance, recommendations, valuable suggestions, and comments during my Ph.D. research.

I would like to express my thanks to Dr. Manuel Le Gallo, Irem Boybat, Christophe Piveteau, Vinay Joshy, Shruti Kulkarni, Anakha V. Babu for various stimulating discussions and contributions to my research.

I would like to thank IBM for the Ph.D. fellowship. I sincerely thank the NJIT ECE department for the constant support and for providing teaching assistantship opportunities.

Last, I would like to express my deepest appreciation to my parents, Sasidharan Nair and Rajalekshmi G. Their continued patience and endless support have been a key element in all my endeavors.

# TABLE OF CONTENTS

| $\mathbf{C}$ | hapt | r Pa                                                   | age |

|--------------|------|--------------------------------------------------------|-----|

| 1            | INT  | CODUCTION                                              | 1   |

|              | 1.1  | Computational Engine in the Human Brain                | 3   |

|              | 1.2  | Computational Architectures                            | 4   |

|              |      | 1.2.1 von Neumann architecture                         | 5   |

|              |      | 1.2.2 Graphics processing units                        | 6   |

|              |      | 1.2.3 Non-volatile memory arrays: computational memory | 7   |

|              |      | 1.2.4 Potential of analog memory based neural networks | 8   |

|              | 1.3  | Further in this Dissertation                           | 9   |

| 2            | NAI  | OSCALE MEMORY DEVICES AND LEARNING                     | 11  |

|              | 2.1  | Introduction                                           | 11  |

|              | 2.2  | Synaptic Devices                                       | 12  |

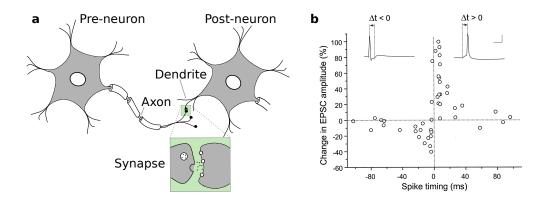

|              |      | 2.2.1 Synapse                                          | 12  |

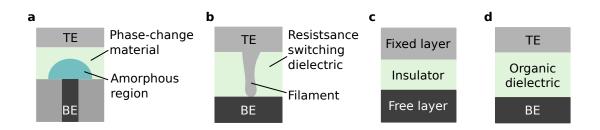

|              |      | 2.2.2 Non-volatile analog memories                     | 14  |

|              | 2.3  | Ideal Synaptic Characteristics                         | 20  |

|              |      | 2.3.1 Device level challenges                          | 21  |

|              | 2.4  | Training Neural Networks                               | 22  |

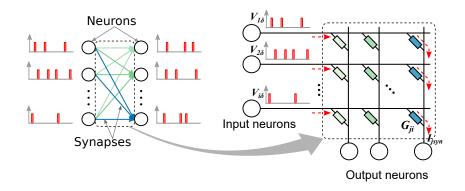

|              |      | 2.4.1 Artificial neural network                        | 22  |

|              |      | 2.4.2 Spiking neural network                           | 23  |

|              |      | 2.4.3 Precision requirement                            | 25  |

|              | 2.5  | Summary                                                | 26  |

| 3            | PHA  | SE CHANGE MEMORY MODEL                                 | 28  |

|              | 3.1  | Introduction                                           | 28  |

|              | 3.2  | Device Characterization and Modeling                   | 30  |

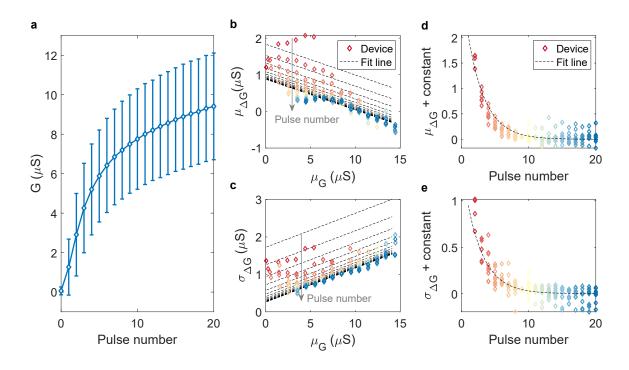

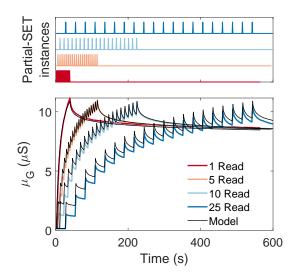

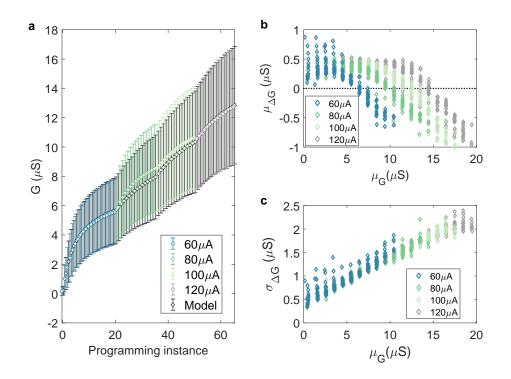

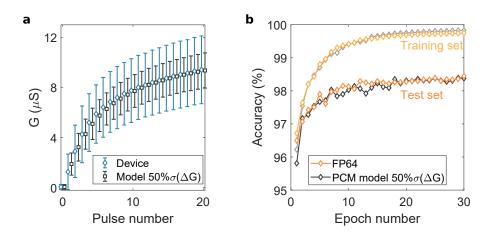

|              |      | 3.2.1 Accumulative behavior                            | 32  |

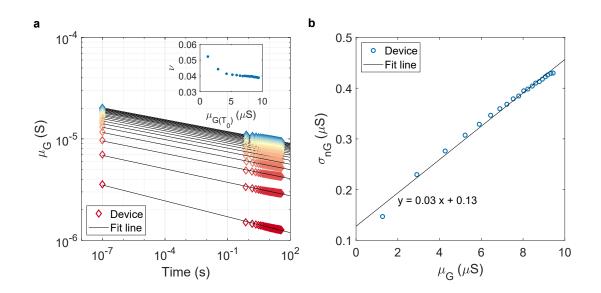

|              |      | 3.2.2 Conductance drift and read noise                 | 34  |

# TABLE OF CONTENTS (Continued)

| С | hapt | r P                                                              | age |

|---|------|------------------------------------------------------------------|-----|

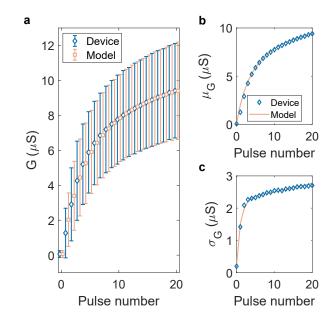

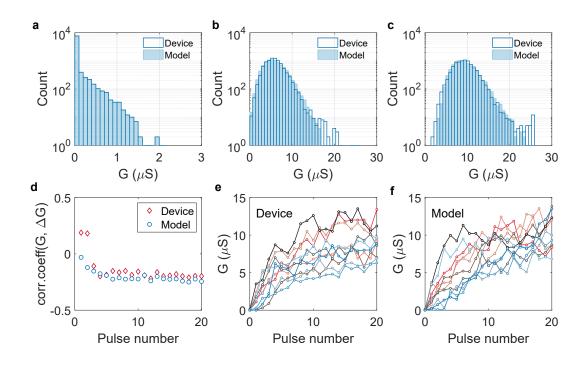

|   |      | 3.2.3 Overall model description and validation                   | 36  |

|   |      | 3.2.4 Generalizability of the PCM model                          | 40  |

|   | 3.3  | Spiking Neural Network with Modeled PCM-synapses                 | 43  |

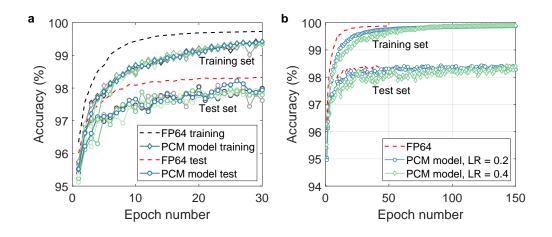

|   | 3.4  | Deep Learning with Modeled PCM-synapses                          | 47  |

|   | 3.5  | Discussion                                                       | 51  |

|   | 3.6  | Summary                                                          | 53  |

| 4 | MIX  | ED-PRECISION TRAINING ARCHITECTURE                               | 54  |

|   | 4.1  | Introduction                                                     | 54  |

|   | 4.2  | Computational Memory: Key Challenges                             | 55  |

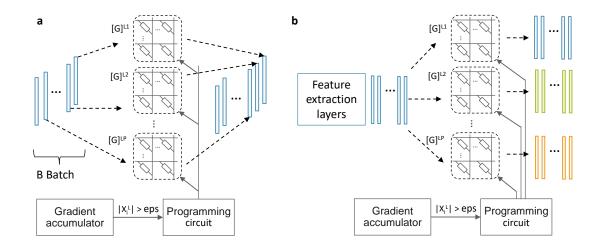

|   | 4.3  | Mixed-Precision Computational Memory Architecture                | 56  |

|   | 4.4  | Evaluation of the Mixed-Precision Architecture                   | 58  |

|   |      | 4.4.1 The simulation framework                                   | 58  |

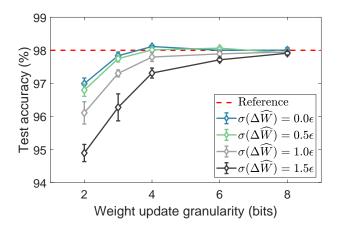

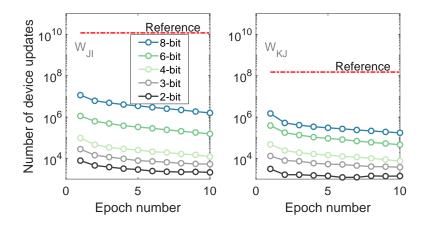

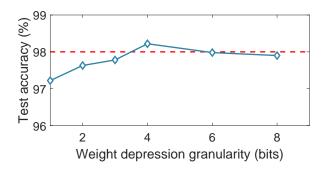

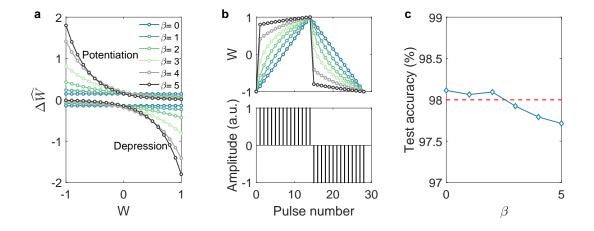

|   |      | 4.4.2 Inaccuracies arising from weight-updates                   | 59  |

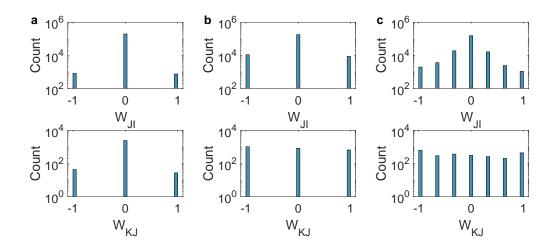

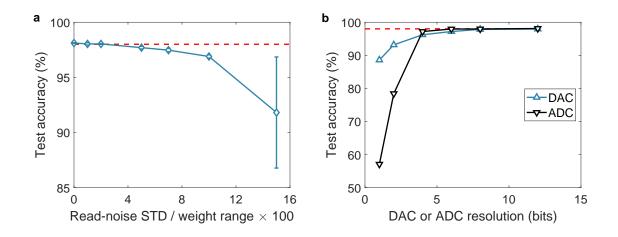

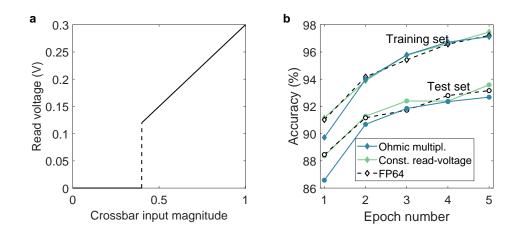

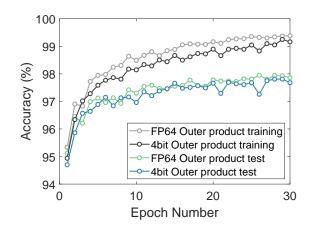

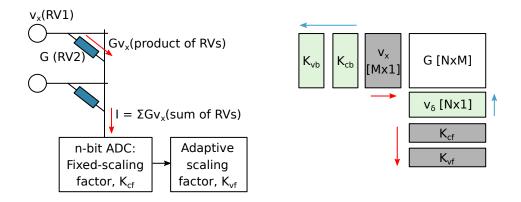

|   |      | 4.4.3 Inaccuracies arising from matrix-vector multiplication     | 65  |

|   | 4.5  | Discussion                                                       | 69  |

|   | 4.6  | Summary                                                          | 71  |

| 5 |      | ERIMENTAL VALIDATION OF MIXED-PRECISION TRAINING<br>CHITECTURE   | 73  |

|   | 5.1  | Introduction                                                     | 73  |

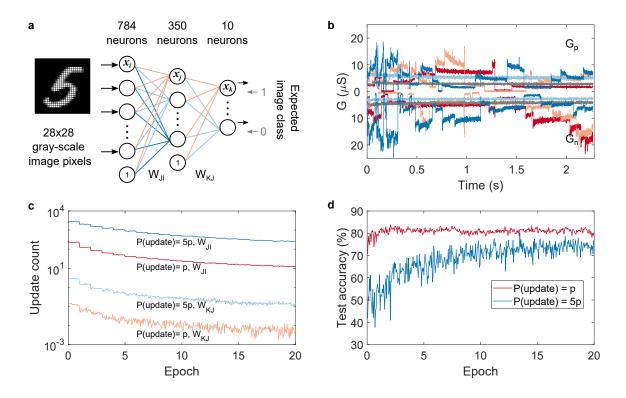

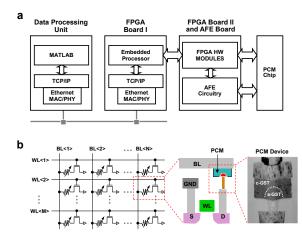

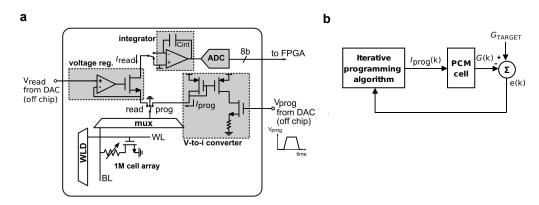

|   | 5.2  | Experiment for Training Handwritten Digit Classification Network | 73  |

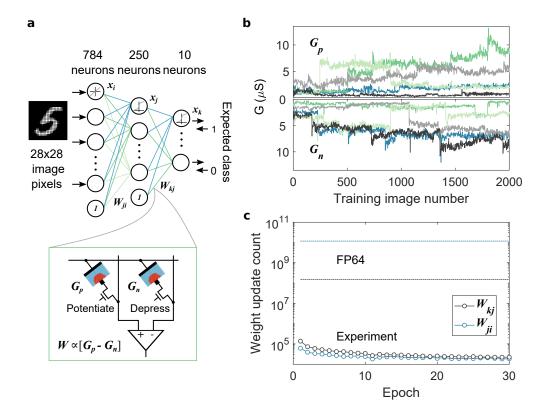

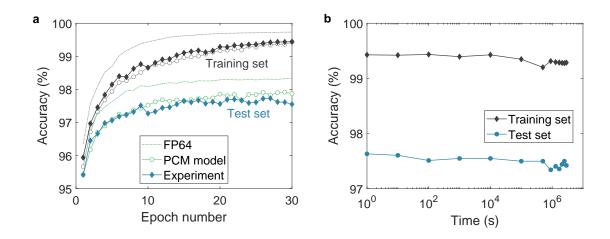

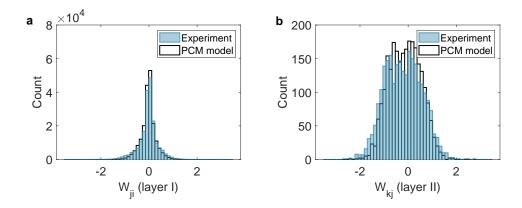

|   |      | 5.2.1 Training using differential PCM synapses                   | 73  |

|   |      | 5.2.2 On-chip inference                                          | 80  |

|   |      | 5.2.3 Training using on-chip ohmic multiplication                | 80  |

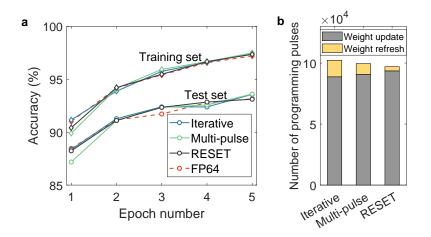

|   |      | 5.2.4 Weight refresh methods                                     | 81  |

|   |      | 5.2.5 Training experiment using non-differential PCM synapse     | 84  |

|   | 5.3  | Training Deeper Neural Networks                                  | 86  |

# TABLE OF CONTENTS (Continued)

| C | hapt | er F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Page |

|---|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|   | 5.4  | Mixed-Precision Weight Update                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 88   |

|   | 5.5  | Independent Training of Neural Networks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 90   |

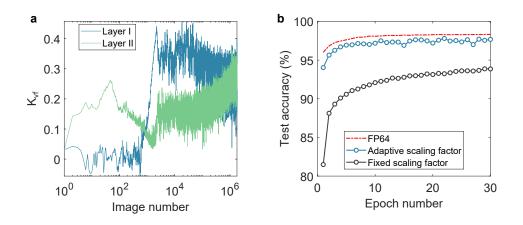

|   |      | 5.5.1 Adaptive conductance to weight mapping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 90   |

|   |      | 5.5.2 Crossbar replication for pipeline processing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 94   |

|   | 5.6  | Performance Assessment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 96   |

|   | 5.7  | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 98   |

| 6 |      | AINING OF SPIKING NEURAL NETWORK USING PHASE-CHANGE<br>EMORY ARRAYS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 100  |

|   | 6.1  | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 100  |

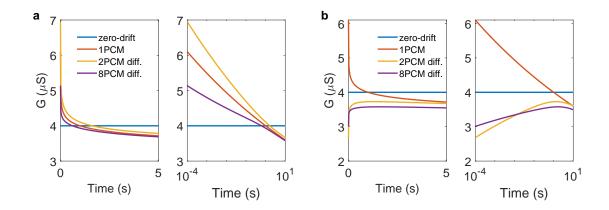

|   | 6.2  | PCM Conductance Drift                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 101  |

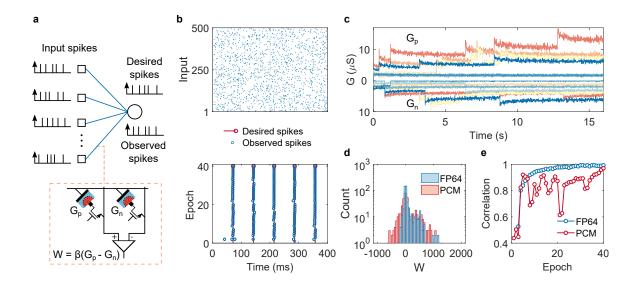

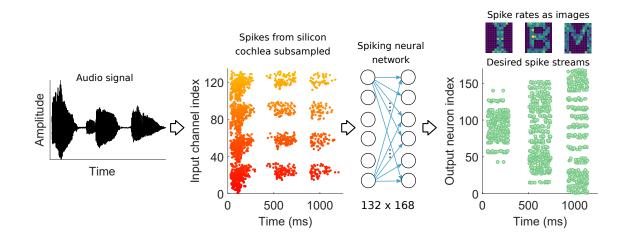

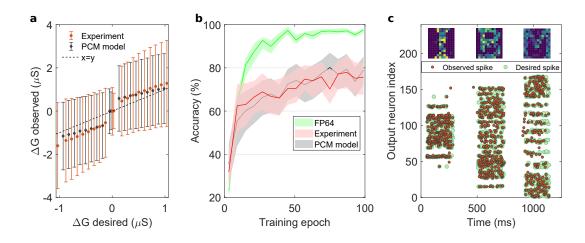

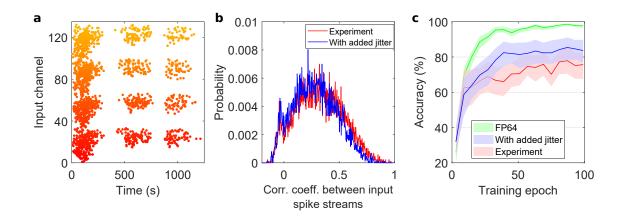

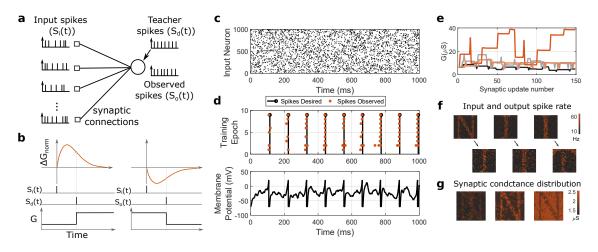

|   | 6.3  | SNN Training Experiment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 103  |

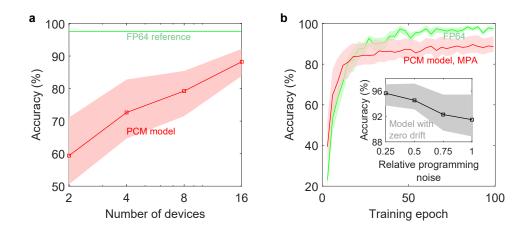

|   | 6.4  | Training Accuracy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 107  |

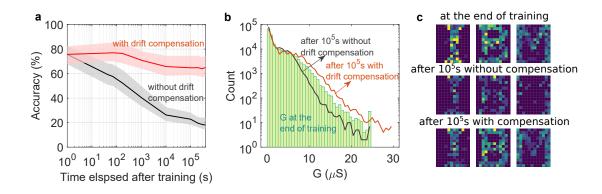

|   | 6.5  | SNN Inference on PCM Array                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 109  |

|   | 6.6  | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 111  |

| 7 | RES  | SISTIVE RANDOM ACCESS MEMORY FOR SYNAPSE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 113  |

|   | 7.1  | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 113  |

|   | 7.2  | Resistance Switching Mechanism                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 114  |

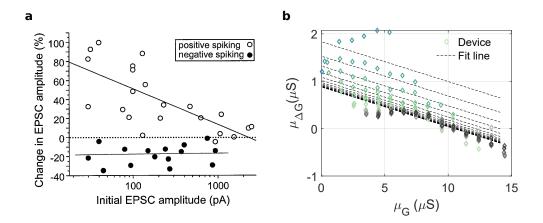

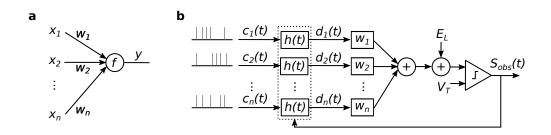

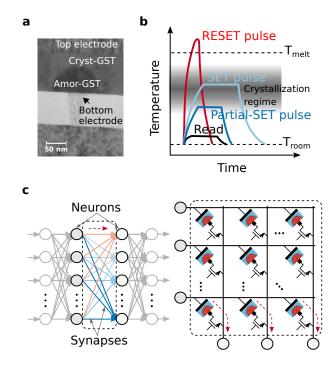

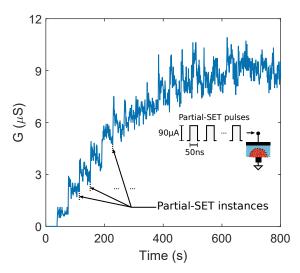

|   | 7.3  | Fabrication and Characterization of ${\rm Cu}/{\rm SiO_2}/{\rm W}$ RRAM $\ .$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 115  |