# **Copyright Warning & Restrictions**

The copyright law of the United States (Title 17, United States Code) governs the making of photocopies or other reproductions of copyrighted material.

Under certain conditions specified in the law, libraries and archives are authorized to furnish a photocopy or other reproduction. One of these specified conditions is that the photocopy or reproduction is not to be "used for any purpose other than private study, scholarship, or research." If a, user makes a request for, or later uses, a photocopy or reproduction for purposes in excess of "fair use" that user may be liable for copyright infringement,

This institution reserves the right to refuse to accept a copying order if, in its judgment, fulfillment of the order would involve violation of copyright law.

Please Note: The author retains the copyright while the New Jersey Institute of Technology reserves the right to distribute this thesis or dissertation

Printing note: If you do not wish to print this page, then select "Pages from: first page # to: last page #" on the print dialog screen

The Van Houten library has removed some of the personal information and all signatures from the approval page and biographical sketches of theses and dissertations in order to protect the identity of NJIT graduates and faculty.

#### ABSTRACT

#### CHARACTERIZATION OF SELF-HEATING EFFECTS AND ASSESSMENT OF ITS IMPACT ON RELIABILITY IN FINFET TECHNOLOGY

#### by Peter Christopher Paliwoda

The systematically growing power (heat) dissipation in CMOS transistors with each successive technology node is reaching levels which could impact its reliable operation. The emergence of technologies such as bulk/SOI FinFETs has dramatically confined the heat in the device channel due to its vertical geometry and it is expected to further exacerbate with gate-all-around transistors.

This work studies heat generation in the channel of semiconductor devices and measures its dissipation by means of wafer level characterization and predictive thermal simulation. The experimental work is based on several existing device thermometry techniques to which additional layout improvements are made in state of the art bulk FinFET and SOI FinFET 14nm technology nodes. The sensors produce excellent matching results which are confirmed through TCAD thermal simulation, differences between sensor types are quantified and error bars on measurements are established.

The lateral heat transport measurements determine that heat from the source is mostly dissipated at a distance of  $1\mu$ m and  $1.5\mu$ m in bulk FinFET and SOI FinFET, respectively. Heat additivity is successfully confirmed to prove and highlight the fact that the whole system needs to be considered when performing thermal analysis. Furthermore, an investigation is devoted to study self-heating with different layout densities by varying the number of fins and fingers per active region (RX). Fin thermal resistance is measured at different ambient temperatures to show its variation of up to 70% between -40°C to 175°C. Therefore, the Si fin has a more dominant effect in heat transport and its varying thermal conductivity should be taken into account. The effect of ambient temperature on self-heating measurement is confirmed by supplying heat through thermal chuck and adjacent heater devices themselves.

Motivation for this work is the continuous evolution of the transistor geometry and use of exotic materials, which in the recent technology nodes made heat removal more challenging. This poses reliability and performance concerns. Therefore, this work studies the impact of self-heating on reliability testing at DC conditions as well as realistic CMOS logic operating (AC) conditions. Front-end-of-line (FEOL) reliability mechanisms, such as hot carrier injection (HCI) and non-uniform time dependent dielectric breakdown (TDDB), are studied to show that self-heating effects can impact measurement results and recommendations are given on how to mitigate them. By performing an HCI stress at moderate bias conditions, this dissertation shows that the laborious techniques of heat subtraction are no longer necessary. Self-heating is also studied at more realistic device switching conditions by utilizing ring oscillators with several densities and stage counts to show that self-heating is considerably lower compared to constant voltage stress conditions and degradation is not distinguishable.

### CHARACTERIZATION OF SELF-HEATING EFFECTS AND ASSESSMENT OF ITS IMPACT ON RELIABILITY IN FINFET TECHNOLOGY

by Peter Christopher Paliwoda

A Dissertation Submitted to the Faculty of New Jersey Institute of Technology in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy in Electrical Engineering

> Helen and John C. Hartmann Department of Electrical and Computer Engineering

> > December 2018

Copyright © 2018 by Peter Christopher Paliwoda

# ALL RIGHTS RESERVED

# **APPROVAL PAGE**

### CHARACTERIZATION OF SELF-HEATING EFFECTS AND ASSESSMENT OF ITS IMPACT ON RELIABILITY IN FINFET TECHNOLOGY

Peter Christopher Paliwoda

| Dr. Durgamadhab Misra, Dissertation Co-Advisor<br>Professor of Electrical and Computer Engineering, NJIT   | Date |

|------------------------------------------------------------------------------------------------------------|------|

| Dr. Zakariae Chbili, Dissertation Co-Advisor<br>GLOBALFOUNDRIES, Inc.                                      | Date |

| Dr. Leonid Tsybeskov, Committee Member<br>Professor and Chair of Electrical and Computer Engineering, NJIT | Date |

| Dr. Marek Sosnowski, Committee Member<br>Professor of Electrical and Computer Engineering, NJIT            | Date |

| Dr. Hieu Nguyen, Committee Member<br>Professor of Electrical and Computer Engineering, NJIT                | Date |

| Dr. Andreas Kerber, Committee Member                                                                       | Date |

Former GLOBALFOUNDRIES, Inc.

Date

#### **BIOGRAPHICAL SKETCH**

**Degree:** Doctor of Philosophy

Date: December 2018

#### **Undergraduate and Graduate Education:**

- Doctor of Philosophy in Electrical Engineering, New Jersey Institute of Technology, Newark, NJ, 2018

- Master of Science in Electrical Engineering, Rensselaer Polytechnic Institute, Troy, NY, 2005

- Bachelor of Science in Electrical Engineering, Rensselaer Polytechnic Institute, Troy, NY, 2003

Major: Electrical Engineering

#### **Presentations and Publications:**

- P. Paliwoda, Z. Chbili, A. Kerber, T. Nigam, D. Singh, K. Nagahiro, P.P Manik, S. Cimino, D. Misra, "Self-heating effects on Hot carrier degradation and its impact on Ring-Oscillator reliability," *IEEE International Integrated Reliability Workshop (IIRW)*, South Lake Tahoe, CA, 2018.

- D. Singh, O. D. Restrepo, P. P. Manik, N. Rao Mavilla, H. Zhang, P. Paliwoda, S. Pinkett, Y. Deng, E. Cruz Silva, J. B. Johnson, M. Bajaj, S. Furkay, Z. Chbili, A. Kerber, C. Christiansen, S. Narasimha, E. Maciejewski, S. Samavedam, C.-H. Lin, "Bottom-up methodology for predictive simulations of self-heating in aggressively scaled process technologies," *IEEE International Reliability Physics Symposium (IRPS)*, Burlingame, CA, pp. 6F.6-1-6F.6-7, 2018.

- P. Paliwoda, Z. Chbili, A. Kerber, D. Singh, D. Misra, "Ambient temperature and layout impact on self-heating characterization in FinFET devices," *IEEE International Reliability Physics Symposium (IRPS)*, Burlingame, CA, pp. 6E.2-1-6E.2-5, 2018.

- P. Paliwoda, P.P. Manik, D. Singh, Z. Chbili, A. Kerber, J. Johnson, D. Misra, "Self-Heating assessment on bulk FinFET devices through characterization and predictive simulation," *IEEE Transactions on Device and Materials Reliability*, vol. 18, no. 2, pp. 133-138, 2018.

- L. Pantisano, P. Srinivasan, T. Kim, T. Chu, M. Ozbek, A. N. Zainuddin, M. Hasanuzzaman, S. Dag, P. Paliwoda, M. Bajaj, B. Kannan, M. Kota and K. Zhao, "Interaction of work function tuning and negative bias temperature instability for future nodes," *Microelectronic Engineering*, vol. 178, pp. 258-261, 2017.

- Kerber, P. Srinivasan, S. Cimino, P. Paliwoda, S. Chandrashekhar, Z. Chbili, S. Uppal, R. Ranjan, M. I. Mahmud, D. Singh, P. P. Manik, J. Johnson, F. Guarin, T. Nigam and B. Parameshwaran, "Device reliability metric for end-of-life performance optimization based on circuit level assessment," *IEEE International Reliability Physics Symposium (IRPS)*, Monterey, CA, pp. 2D-3.1-2D-3.5, 2017.

- P. Paliwoda, Z. Chbili, A. Kerber, A. Gondal and D. Misra, "Self-heating measurement methodologies and their assessment on bulk FinFET devices," *IEEE International Integrated Reliability Workshop (IIRW)*, Fallen Leaf Lake, CA, pp. 1-4, 2017.

- C. S. Premachandran, R. Ranjan, R. Agarwal, S.F. Yap, P. Paliwoda, T. Sarasvathi, A. Gondal, P. Justison, N. Mahadeva Iyer, "Wafer level high temperature reliability study by backside probing for a 50um thin TSV wafer," *IEEE 65th Electronic Components and Technology Conference (ECTC)*, San Diego, CA, pp. 2144-2148, 2015.

- Y. Liu, M.H. Chi, A. Mittal, G. Aluri, S. Uppal, P. Paliwoda, E. Banghart, K. Korablev, B. Liu, M. Nam, M. Eller, S. Samavedam, "Anti-fuse memory array embedded in 14nm FinFET CMOS with novel selector-less bit-cell featuring self-rectifying characteristics," *Symposium on VLSI Technology (VLSI-Technology): Digest of Technical Papers*, Honolulu, HI, pp. 1-2, 2014.

- **P. Paliwoda** and D. Misra, "Impact of constant voltage stress on high-κ gate dielectric for RF IC performance," *ECS Transactions*, vol. 41 no. 3, pp. 415-419, 2011.

- **P. Paliwoda** and M. Hella, "An optimized CMOS gilbert mixer using inter-stage inductance for ultra wideband receivers," *49th IEEE International Midwest Symposium on Circuits and Systems*, San Juan, vol. 1, pp. 362-365, 2006.

To Alicia

#### ACKNOWLEDGMENT

Firstly, I would like to thank my dissertation co-advisor, Dr. Durgamadhab Misra for his guidance, support and encouragement throughout my PhD studies. Dr. Misra was first to introduce me to the field of electronic reliability, which became my daily work and passion. I am thankful to my dissertation co-advisor, Dr. Zakariae Chbili for his great vision, wisdom and help in grasping the small and big picture of this work. Dr. Chbili helped me grow professionally and personally by teaching me how to strive for excellence both in publication preparation and presentation skills.

I would like to express my gratitude to my committee member Dr. Andreas Kerber for sharing his knowledge, brilliance, enthusiasm towards research and problem solving skills which motivated me tremendously become better at what I do. To be under Dr. Kerber's guidance was an honor and privilege. I would also like to express my special appreciation to my committee members; Dr. Leonid Tsybeskov, Dr. Marek Sosnowski, and Dr. Hieu Nguyen for their constructive knowledge and feedback throughout my doctoral studies.

I am thankful for the financial support from New Jersey Institute of Technology, National Science Foundation and GLOBALFOUNDRIES, Inc. which made the completion of this work possible.

This work would not achieve its present quality without the fruitful discussions with Tanya Nigam, Oscar Restrepo and Dhruv Singh in the areas of reliability and TCAD thermal simulation, their expertise in these fields helped me close many gaps in this dissertation. Furthermore, I am thankful for my colleagues; Kurt Nagahiro, Charles LaRow, Sing Fui Yap, Liu Yang, Maria Toledano Luque, Thomas Kauerauf, Salvatore Cimino, Amit Gupta, Iqbal Mahmud, Luigi Pantisano, Srinivasan Purushothaman and my manager Byoung Min who helped me tremendously through discussions and problem solving during this study.

I am grateful for my family, especially my parents, Elżbieta and Edward for always being supportive and loving and for my daughter Alicia, who has given me the inspiration to complete this work.

Finally, enormous thanks go to my lifelong friends; Kamil Wasilewski, Filipp Akopyan, Borjan Gagoski, Chin-Chen Lee, Marina Gritsik, Harold Henderson, Jerzy Sokol and Raymond Boullianne for always being there when I needed their advice or help.

| C | Chapter P                                           |    |

|---|-----------------------------------------------------|----|

| 1 | INTRODUCTION                                        | 1  |

|   | 1.1 Motivation                                      | 5  |

|   | 1.1.1 Self-Heating Effects on Semiconductor Devices | 5  |

|   | 1.2 Objective                                       | 7  |

|   | 1.3 Heat Conduction in Semiconductors               | 8  |

|   | 1.4 Heat Source in Semiconductors                   | 10 |

|   | 1.5 Dissertation Organization                       | 13 |

|   | 1.5.1 Chapter 2                                     | 13 |

|   | 1.5.2 Chapter 3                                     | 13 |

|   | 1.5.3 Chapter 4                                     | 14 |

|   | 1.5.4 Chapter 5                                     | 14 |

|   | 1.5.5 Chapter 6                                     | 15 |

| 2 | STATE OF THE ART                                    | 16 |

|   | 2.1 Phonon Confinement Effects                      | 16 |

|   | 2.2 Quantification of Self-Heating                  | 20 |

|   | 2.3 Layout Impact on Self-Heating                   | 22 |

|   | 2.4 Reliability Implications due to Self-Heating    | 23 |

|   | 2.5 Summary                                         | 29 |

| 3 | SELF-HEATING MEASUREMENT METHODOLOGIES              | 30 |

|   | 3.1 Introduction                                    | 30 |

# TABLE OF CONTENTS

# TABLE OF CONTENTS (Continued)

| C | hapter                                                                 | Page |

|---|------------------------------------------------------------------------|------|

|   | 3.2 Sensor Layout Design                                               | 31   |

|   | 3.3 Self-Heating Measurement Procedure and Results                     | 34   |

|   | 3.3.1 Self-Heating Measurement Results                                 | . 38 |

|   | 3.3.2 Additivity of Heat                                               | 39   |

|   | 3.4 Temperature Measurement Error                                      | 41   |

|   | 3.5 Sensor Quality Verification                                        | 47   |

|   | 3.6 Thermal Simulations                                                | 50   |

|   | 3.7 Self-Heating Comparison between SOI- and bulk-FinFET Devices       | 57   |

|   | 3.8 Summary                                                            | 59   |

| 4 | AMBIENT TEMPERATURE AND LAYOUT IMPACT ON SELF-HEATING CHARACTERIZATION | 61   |

|   | 4.1 Introduction                                                       | 61   |

|   | 4.2 Experimental                                                       | 62   |

|   | 4.3 Layout Impact on Self-Heating                                      | 64   |

|   | 4.3.1 Layout Density                                                   | 65   |

|   | 4.3.2 Lateral Heat Dissipation                                         | 66   |

|   | 4.4 Ambient Temperature Impact on Self-Heating                         | 67   |

|   | 4.4.1 Chuck Temperature Dependence                                     | 68   |

|   | 4.4.2 Adjacent Heater Transistor Dissipated Power Dependence           | 71   |

|   | 4.5 Summary                                                            | 73   |

### TABLE OF CONTENTS (Continued)

| C | hapter                                                                                                                                       | Page |

|---|----------------------------------------------------------------------------------------------------------------------------------------------|------|

| 5 | SELF-HEATING EFFECTS ON HOT CARRIER AND TIME-DEPENDENT<br>DIELECTRIC BREAKDOWN DEGRADATION AND ITS IMPACT ON RING-<br>OSCILLATOR RELIABILITY | 74   |

|   |                                                                                                                                              |      |

|   | 5.1 Introduction                                                                                                                             | 74   |

|   | 5.2 Experimental Setup                                                                                                                       | 75   |

|   | 5.3 Results and Discussion                                                                                                                   | 80   |

|   | 5.3.1 Self-Heating Characterization at DC and AC Operation                                                                                   | 80   |

|   | 5.3.2 Self-Heating Effect on Hot-Carrier at Constant Voltage Stress                                                                          | 83   |

|   | 5.3.3 Self-Heating Effect on Uniform and Non-Uniform TDDB at Constant Voltage Stress                                                         | 86   |

|   | 5.3.4 Self-Heating Impact on Ring Oscillator Reliability                                                                                     | . 89 |

|   | 5.4 Summary                                                                                                                                  | 90   |

| 6 | CONCLUSIONS AND FUTURE WORK                                                                                                                  | 91   |

|   | 6.1 Conclusions                                                                                                                              | 91   |

|   | 6.2 Future Work                                                                                                                              | 94   |

|   | 6.2.1 Type III (R <sub>G</sub> ) Sensor Test Improvement                                                                                     | 94   |

|   | 6.2.2 Self-Heating Impact on Back-End-Of-Line Interconnects                                                                                  | 96   |

|   | 6.2.3 Persistent Self-heating                                                                                                                | 97   |

|   | REFERENCES                                                                                                                                   | . 98 |

# LIST OF TABLES

| Tabl | Γable                                             |    |

|------|---------------------------------------------------|----|

| 2.1  | Transistor Parameters with Thermal Dependence     | 20 |

| 2.2  | Thermal Dependence of Reliability Mechanisms [25] | 25 |

| 3.1  | Sensing Methodologies                             | 33 |

# LIST OF FIGURES

| Figu | re                                                                                                                                                                                                                                                                                                                           | Page |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 1.1  | Historical comparison of transistor count, performance, power usage and number of logical cores over 42 years                                                                                                                                                                                                                | 2    |

| 1.2  | Thermal conductivities of common materials used in semiconductor<br>manufacturing and their modulation with respect to temperature. Reduction in<br>thermal conductivity is observed in alloy materials and dielectrics if compared<br>to bulk Si or Ge                                                                      | 3    |

| 2.1  | A summary of thermal conductivity data at 300 K for various bulk and SOI materials, showing strong scaling of thermal conductivity with Si layer thickness                                                                                                                                                                   | 17   |

| 2.2  | A normalized plot of temperature rise ( $T_{RISE}$ ) as a function of power density per transistor width across different device architectures and substrate types, demonstrating the impact of phonon confinement on local self-heating effects                                                                             | 18   |

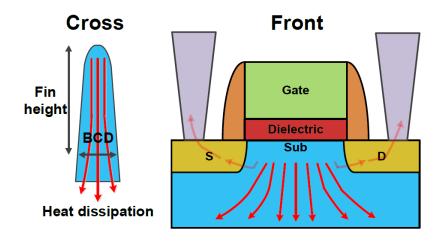

| 2.3  | FinFET self-heat, during transistor operation gets dissipated via several nano-<br>meters of Fin width to bulk substrate and also through the contacts                                                                                                                                                                       | 19   |

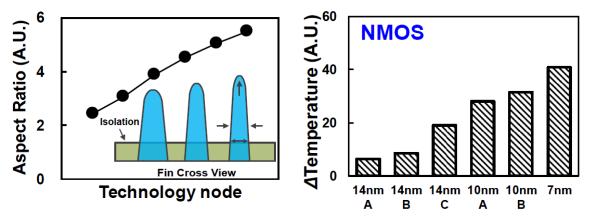

| 2.4  | With increased aspect ratio in advancing technology node (left) NMOS FinFET and PMOS (not shown) exhibits self-heating temperature increase (@same power)                                                                                                                                                                    | 19   |

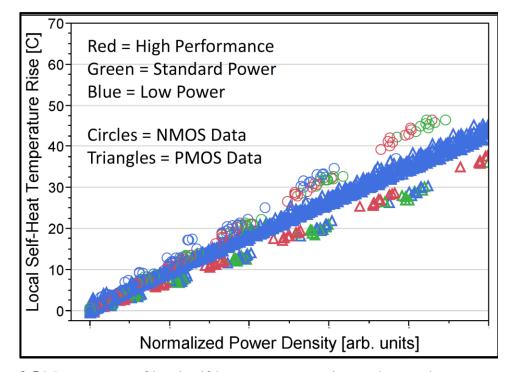

| 2.5  | Measurement of local self-heat temperature rise on the metal sensor                                                                                                                                                                                                                                                          | 22   |

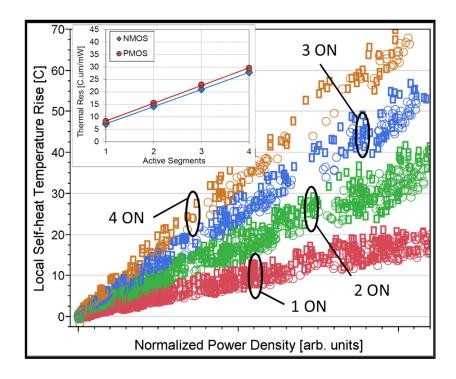

| 2.6  | Response of thermal resistance to the number of powered heater segments                                                                                                                                                                                                                                                      | 23   |

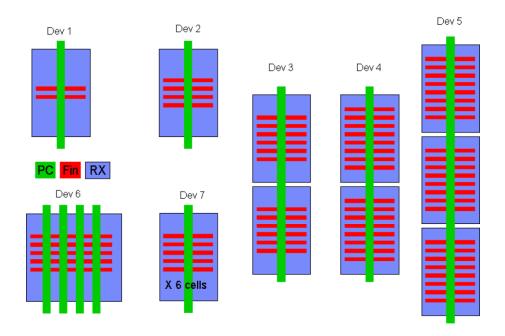

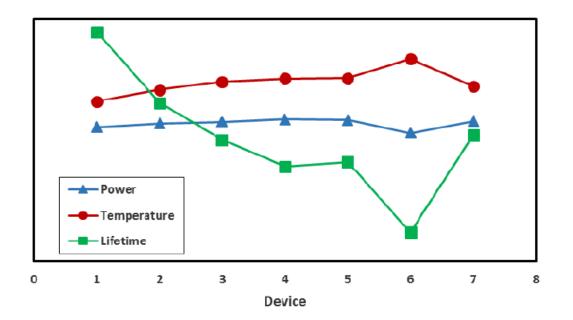

| 2.7  | FinFET device layouts studied which are referenced in Figure 2.8                                                                                                                                                                                                                                                             | 24   |

| 2.8  | Stress power per unit width, calculated device stress temperature and extracted<br>Lifetime for various layouts                                                                                                                                                                                                              | 24   |

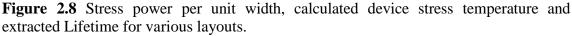

| 2.9  | IdSat recovery ratio vs. delay time; higher Idsat for lower channel length and threshold voltage exhibits more recovery due to higher temperature induced by self-heating effect (a). Since $V_T$ does not raise high temperature due to self-heating effect, degradation can be fairly compared without any disturbance (b) | 26   |

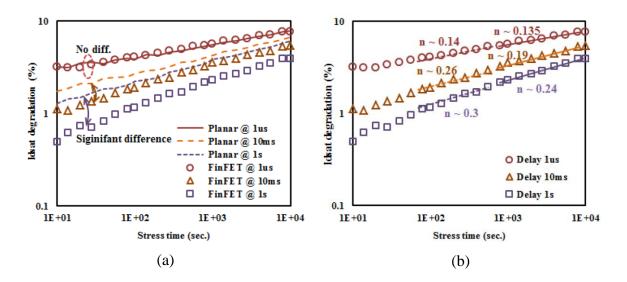

| 2.10 | Planar/FinFET Idsat degradation vs. stress time at different measurement delay (a). Degradation slope is affected by self-heating effect (b)                                                                                                                                                                                 | 27   |

| Figu | re                                                                                                                                                                                                                                                                           | Page |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

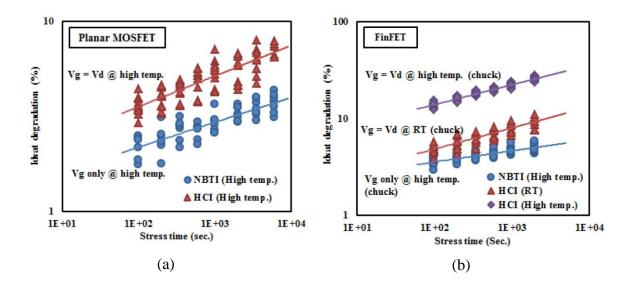

| 2.11 | Planar (a) and FinFET (b) devices PHCI & NBTI degradation vs. stress time.<br>NBTI takes significant part in HCI degradation which is shown in planar<br>devices. FinFET HCI stressed at room temperature suffers high temperature<br>NBTI effect due to self-heating effect | 28   |

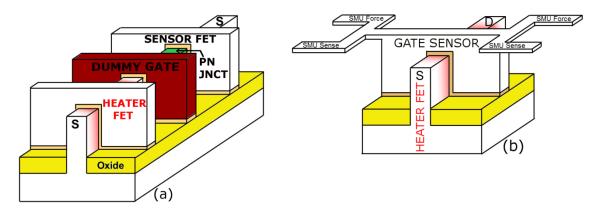

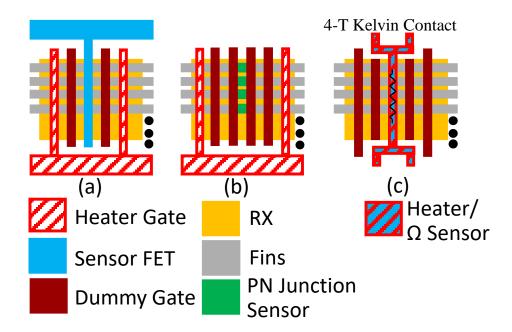

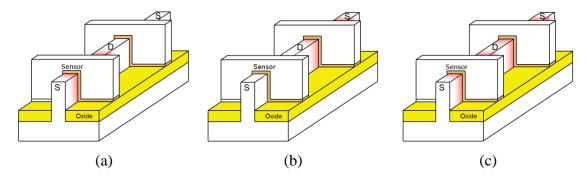

| 3.1  | Illustrative figure showing the different heat sensing schemes: a) adjacent heat sensing using the electrical characteristic of a FET device and PN-junction diode b) local heat sensing using a 4-terminal kelvin contact to measure the thermal coefficient of resistance. | 32   |

| 3.2  | Illustrative figure showing the layout design of each sensor type a) Type I: $V_{Tlin}$ sensor, b) Type II: PN-junction sensor, c) Type III: $R_G$ sensor                                                                                                                    | 32   |

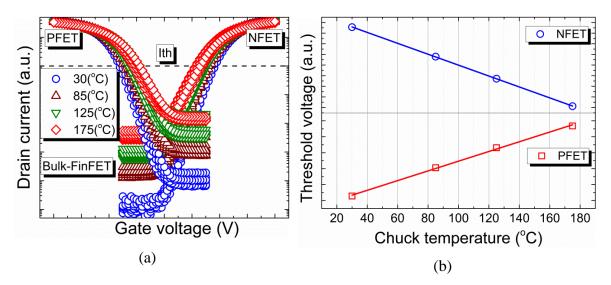

| 3.3  | I-V characteristics of the Type I FinFET sensor at different chuck temperatures showing VT thermal sensitivity (a) Type I: $V_{Tlin}$ sensor, threshold voltage (VTlin) sensitivity to temperature change for NFET and PFET devices (b)                                      | 34   |

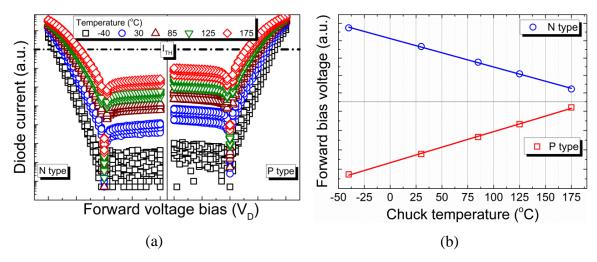

| 3.4  | I-V characteristics of the Type II pn-junction sensor at different chuck temperatures showing its thermal sensitivity (a) and forward bias ( $V_D$ ) sensitivity to temperature change for n-p and p-n diode (b)                                                             | 35   |

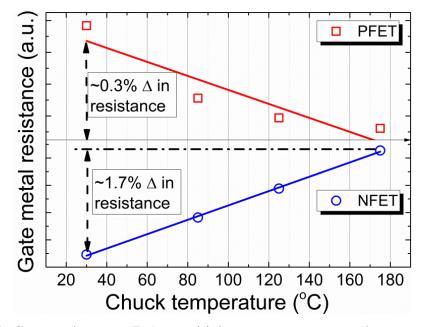

| 3.5  | Gate resistance $(R_G)$ sensitivity to temperature change showing the temperature coefficient of resistance (TCR) for NFET and PFET sensors                                                                                                                                  | 36   |

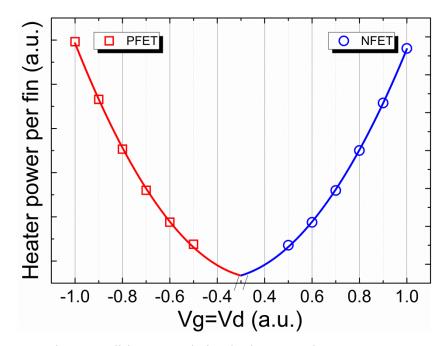

| 3.6  | Heating conditions used in logic PFET/NFET structures. Functional dependence<br>up to $V_g=V_d=\pm 1V$ can be described by Power = $A \cdot x \cdot (x \pm \Delta)$ with $\Delta$ being the<br>device threshold.                                                             | 37   |

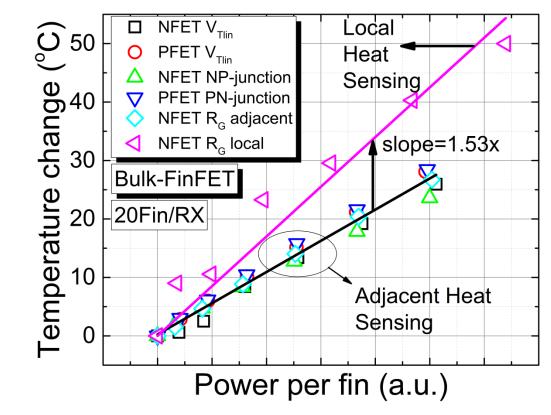

| 3.7  | Self-heating characterization compared using three different sensing methodologies. Local sensing $R_{TH}$ is ~ 1.5X higher than adjacent heat sensing                                                                                                                       | 39   |

| 3.8  | Local (a), adjacent (b) and local & adjacent (c) self-heating measurement scenarios.                                                                                                                                                                                         | 40   |

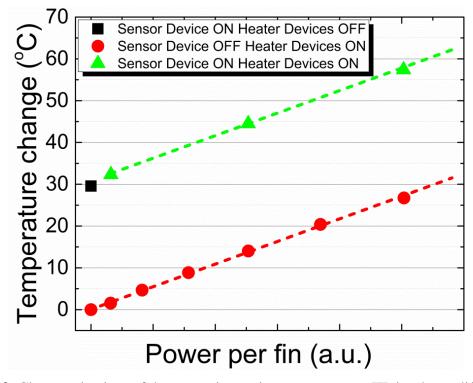

| 3.9  | Characterization of heat sensing using sensor type III in three different configurations. By turning ON the sensor, the heater, or a combination of both, the heat from the two devices is additive.                                                                         | 41   |

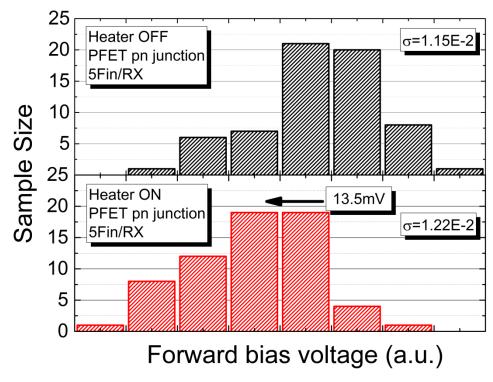

| 3.10 | Normal distribution of pn junction forward bias voltage $V_D$ , with heater OFF (upper) and ON (lower). Mean shift of $V_D$ distribution at higher temperatures is observed.                                                                                                 | 42   |

| Figu | re                                                                                                                                                                                                            | Page |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

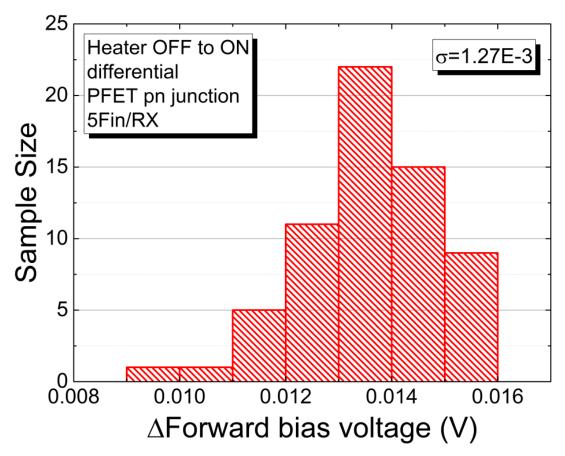

| 3.11 | Normal distribution of pn junction differential forward bias voltage $\Delta V_D$ between heater ON and heater OFF                                                                                            | 43   |

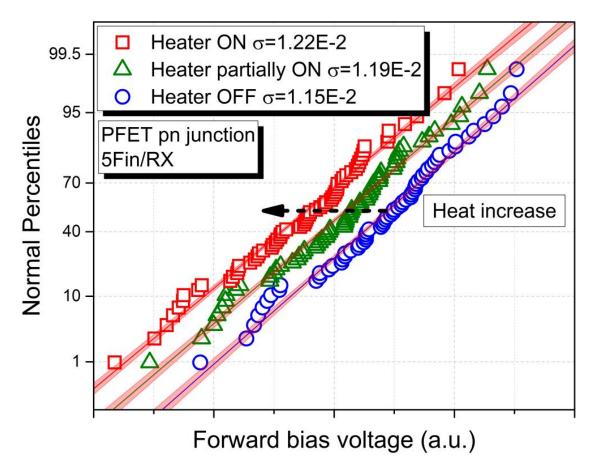

| 3.12 | Probability plot for the forward bias voltage distribution at different heater power dissipations                                                                                                             | 44   |

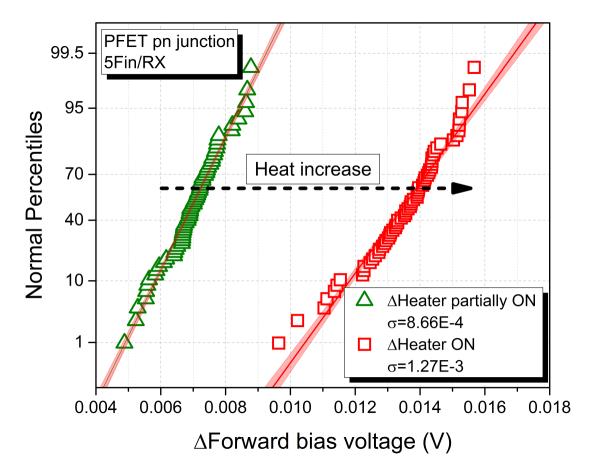

| 3.13 | Probability plot of pn junction differential forward bias voltage $\Delta V_D$ between heater ON and heater OFF                                                                                               | 45   |

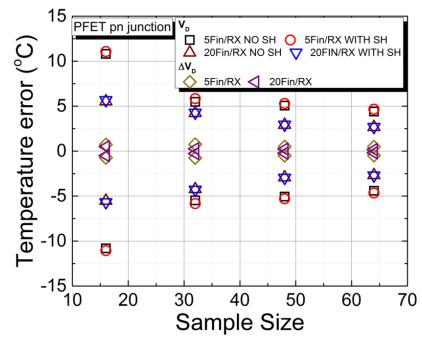

| 3.14 | Temperature error based on pn junction forward bias voltage $V_D$ and differential $\Delta V_D$ between heater ON and heater OFF for 5 & 20Fin/RX                                                             |      |

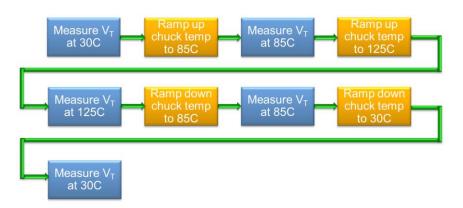

| 3.15 | Test plan to verify sensor reliability and repeatability of measurements while modulating the chuck temperature                                                                                               | 47   |

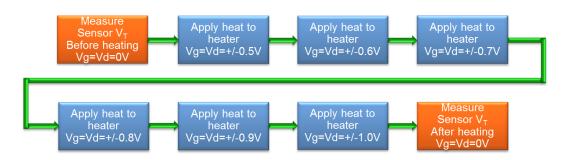

| 3.16 | Test plan to verify sensor reliability and repeatability of measurements while modulating heat in the adjacent heater structures                                                                              | 47   |

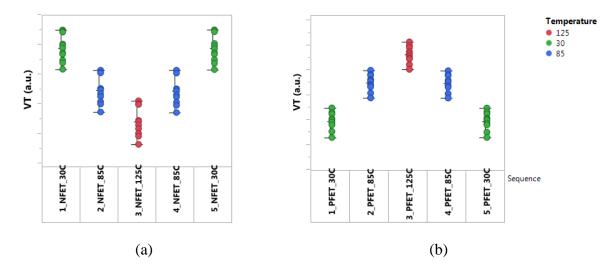

| 3.17 | Type I sensor, $V_T$ measurement while modulating the chuck temperature NFET (a) and PFET (b)                                                                                                                 | 48   |

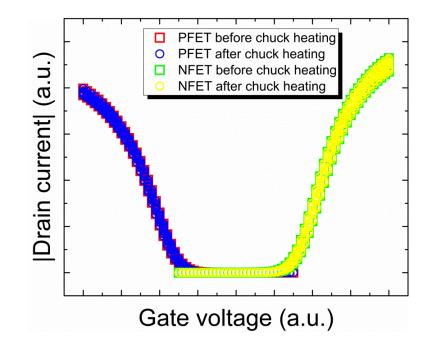

| 3.18 | Hysteresis is not observed in the drain current characteristics of the sensor structure before and after modulation of the chuck temperature                                                                  | 49   |

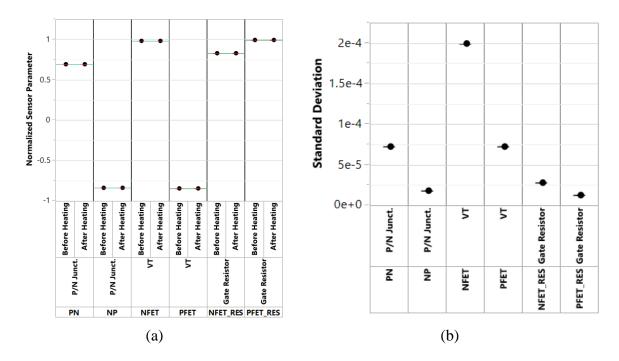

| 3.19 | No change observed in $V_D, V_T$ , or $R_G$ before and after heating the heater structure (a), also confirmed by low values of standard deviation of the thermal parameters from before and after heating (b) | 50   |

| 3.20 | Schematic of heat transfer pathways in FinFET circuit                                                                                                                                                         | 51   |

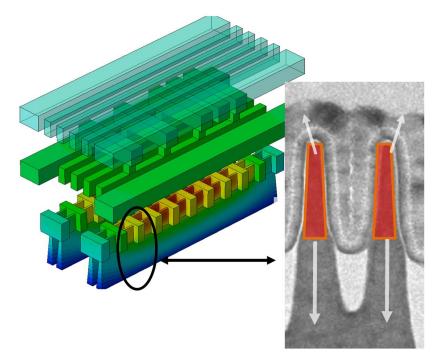

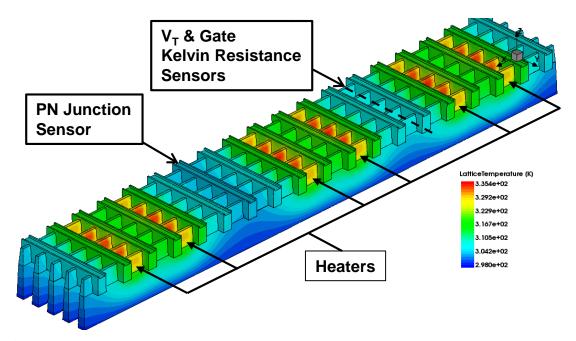

| 3.21 | Thermal contours of local self-heat effects in NFET Bulk FinFET structure with 5 fins per active region RX                                                                                                    | 53   |

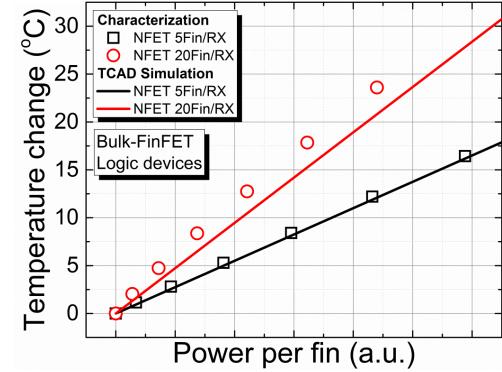

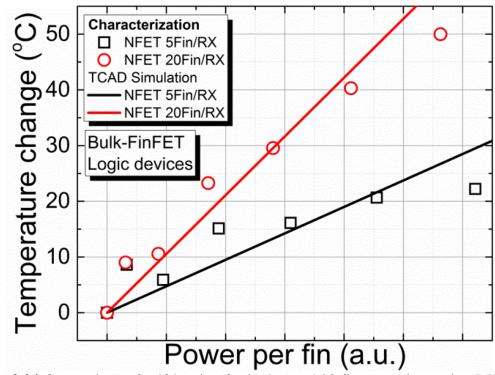

| 3.22 | Comparison of self-heating for both 5 and 20 fin per active region RX using V <sub>T</sub> (Type I) sensor                                                                                                    | 54   |

| 3.23 | Comparison of self-heating for both 5 and 20 fin per active region RX using PN junction (Type II) sensor                                                                                                      | 54   |

| 3.24 | Comparison of self-heating for both 5 and 20 fin per active region RX using gate kelvin probe (Type III) R <sub>G</sub> sensor                                                                                | 55   |

| Figu | re                                                                                                                                                                                                                                                          | Page |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

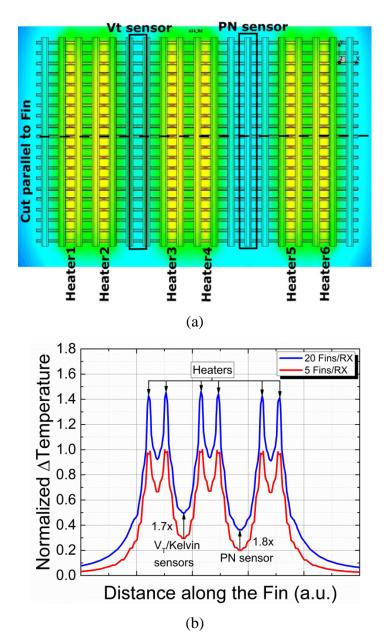

| 3.25 | Temperature profile cut (a) parallel to fins showing the difference in temperature (b) between $V_T$ /Kelvin and PN junction sensor                                                                                                                         | 56   |

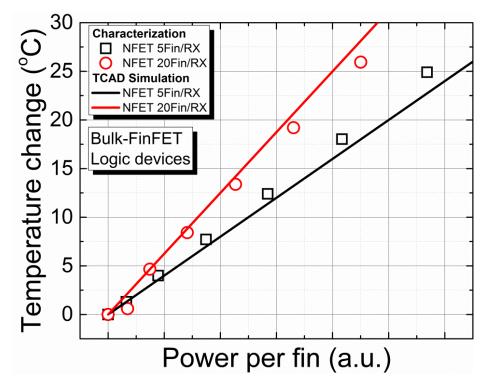

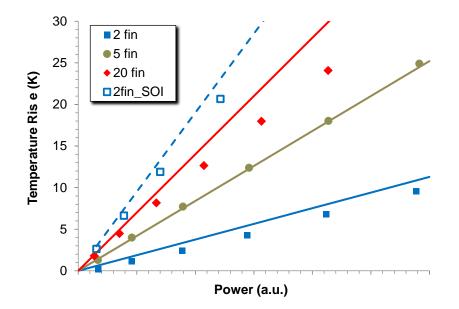

| 3.26 | Self-heating measurements (symbols) and simulations (lines) of a $V_T$ sensor with 2,5 and 20 fins in bulk FinFETs and 2 fins in SOI FinFETs                                                                                                                | 57   |

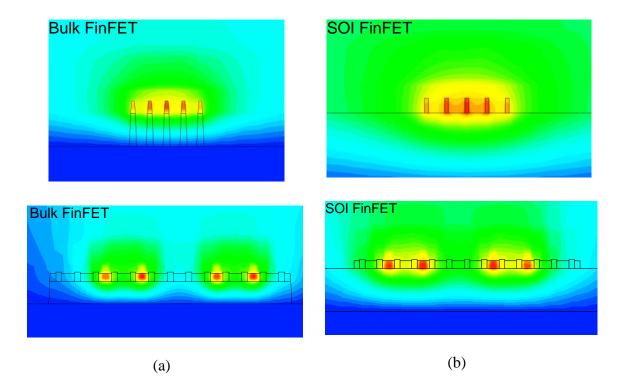

| 3.27 | TCAD thermal simulation of heat spreading in bulk FinFET (a) and SOI<br>FinFET (b)                                                                                                                                                                          | 58   |

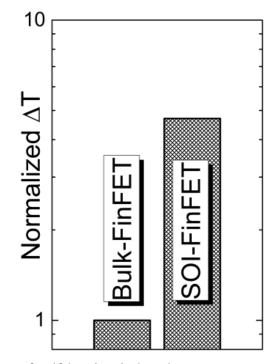

| 3.28 | Comparison of self-heating induced average temperature change in n- and pFET sensor for SOI-FinFET and bulk-FinFET devices based on hardware calibrated thermal TCAD model                                                                                  | 59   |

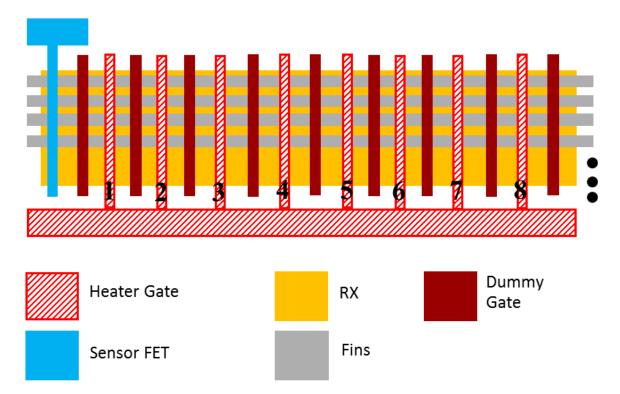

| 4.1  | Layout for the lateral heat conduction test using FinFET technology                                                                                                                                                                                         | 63   |

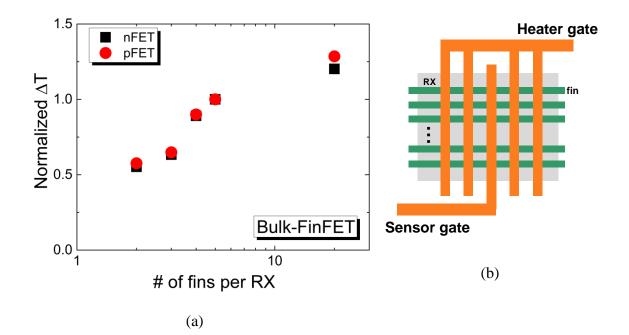

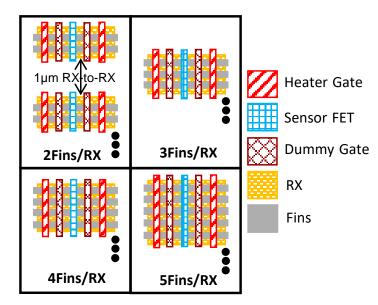

| 4.2  | Temperature change versus number of fins per active area (RX) at constant<br>power per fin for bulk-FinFETs normalized to the 5 fin device (a). Illustrative<br>figure of structure used for study, showing variation of fin count per active<br>region (b) | 65   |

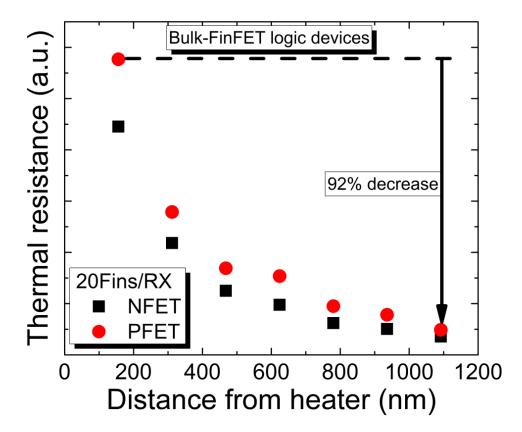

| 4.3  | Self-heating sensed at different distances from the heater in Bulk-FinFET core logic devices                                                                                                                                                                | 66   |

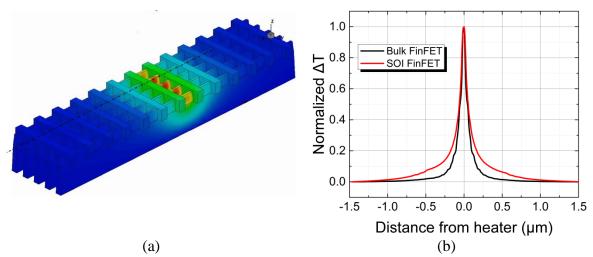

| 4.4  | Bi-directional, lateral heat dissipation through TCAD thermal simulation performed along the cut on bulk FinFET (a) and SOI FinFET. SOI FinFET shows greater lateral spreading compared to bulk FinFET technology (b)                                       |      |

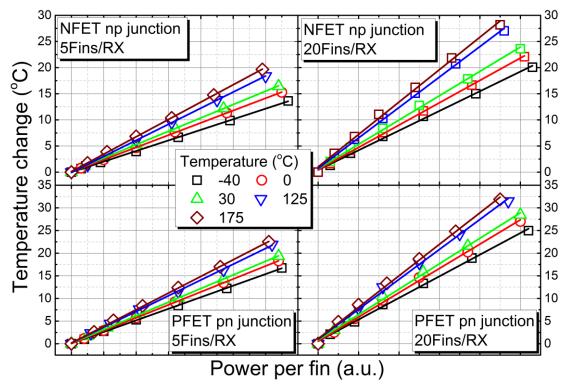

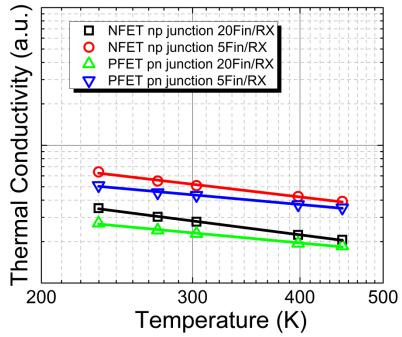

| 4.5  | Self-heating characteristics for 5 and 20 Fin FET heaters, using FET np and pn junction sensors at different prober chuck temperatures (-40 to 175°C)                                                                                                       | 68   |

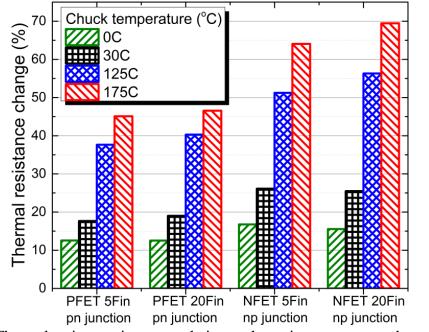

| 4.6  | Thermal resistance increase relative to the resistance measured at -40°C. Up to 70% increase is observed.                                                                                                                                                   | 69   |

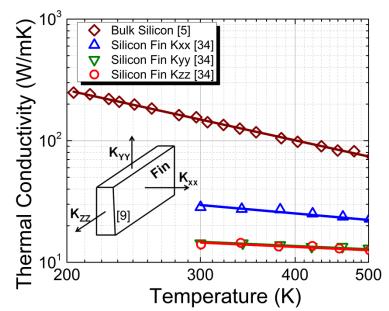

| 4.7  | Theoretical thermal conductivity of silicon bulk compared to silicon fin                                                                                                                                                                                    | 70   |

| 4.8  | Thermal conductivity of tested devices versus ambient temperature                                                                                                                                                                                           | 70   |

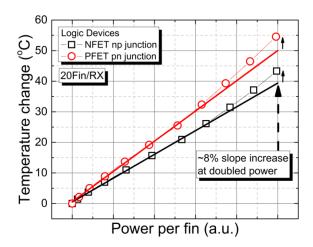

| 4.9  | Self-heating at up to twice the power applied to the heater. 8% increase in slope is observed at high temperatures/power dissipation                                                                                                                        | 72   |

| Figu | re                                                                                                                                                                                                                                                   | Page |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

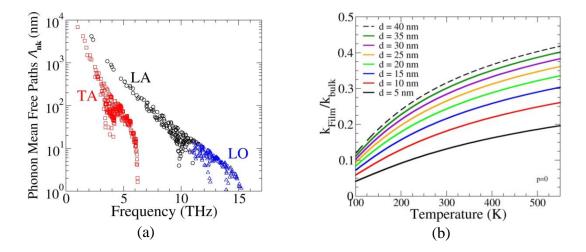

| 4.10 | (a) Phonon mean free paths (nm) in bulk silicon at 300K for longitudinal (LA) / transverse (TA) acoustic branches across the frequency range (b) Thermal conductivity (k) reduction in Si fins as a function of temperature                          | 72   |

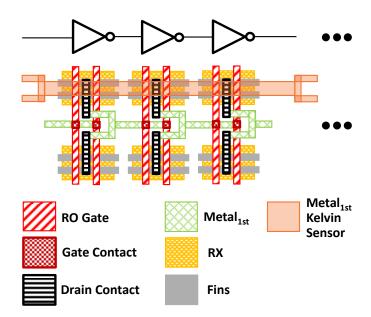

| 5.1  | Illustrative figure showing the ring oscillator layout designs with metal (M1) temperature sensor with kelvin contacts                                                                                                                               | 76   |

| 5.2  | Illustrative figure showing the layout designs of the 4 FinFET devices used                                                                                                                                                                          | 76   |

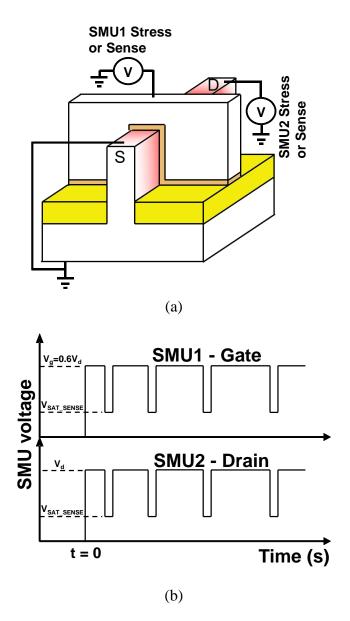

| 5.3  | SMU connections for a conventional constant voltage HC stress (a) and waveform of an applied stress (b)                                                                                                                                              | 77   |

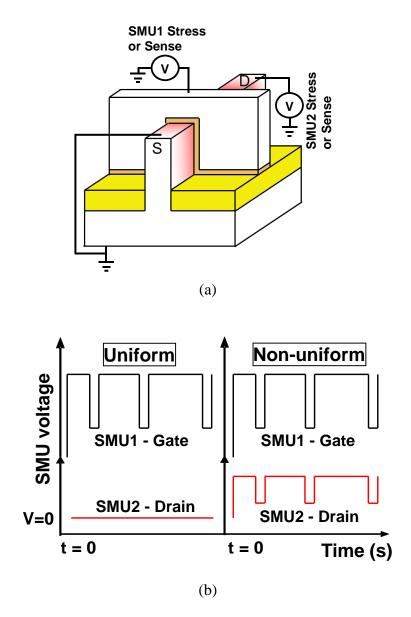

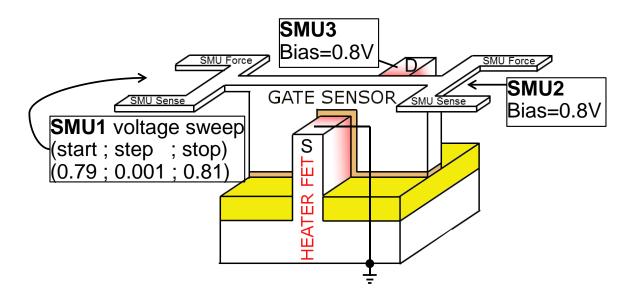

| 5.4  | SMU connections for a conventional uniform and non-uniform constant voltage TDDB stress (a). Applied gate and drain bias during stress, showing the difference between TDDB stress types. The drain is biased and monitored for non-uniform TDDB (b) | 78   |

| 5.5  | Illustrative figure showing during which times current flows through PFET and NFET devices while RO is in operation                                                                                                                                  | 79   |

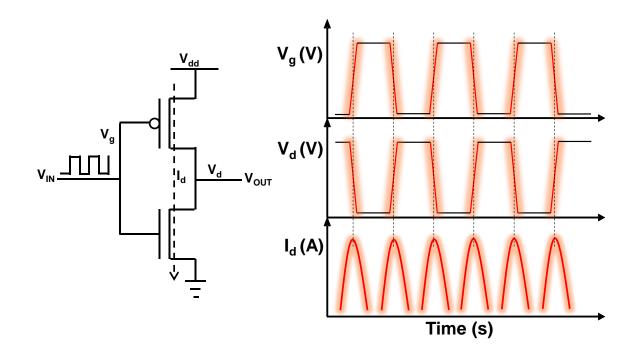

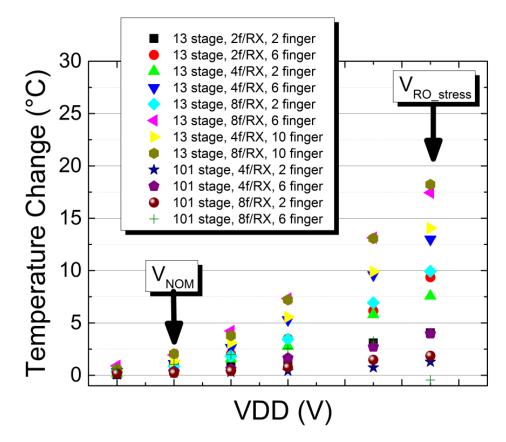

| 5.6  | Measured Ring-Oscillator self-heating characteristics showing temperature increase vs. power supply. Note that the RO heating is <2.5°C at nominal condition and <18°C at extreme stress.                                                            | 80   |

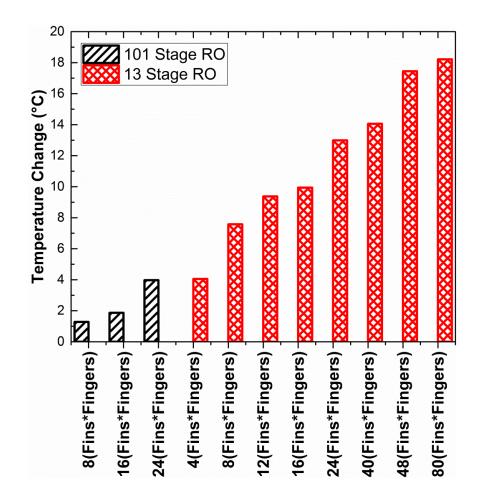

| 5.7  | Detail of Figure 5.3, showing measured Ring-Oscillator self-heating characteristics showing temperature increase vs. layout density (fins*fingers) for $V_{RO\_Stress}$ condition only. Clear density and stage count dependence is observed.        | 81   |

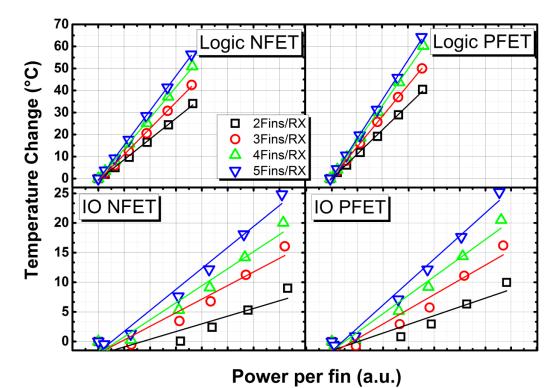

| 5.8  | Measured Self-heating characteristics showing device source temperature as a function of dissipated power for different device types/densities. The IO devices show a lower heating compared to logic                                                | 82   |

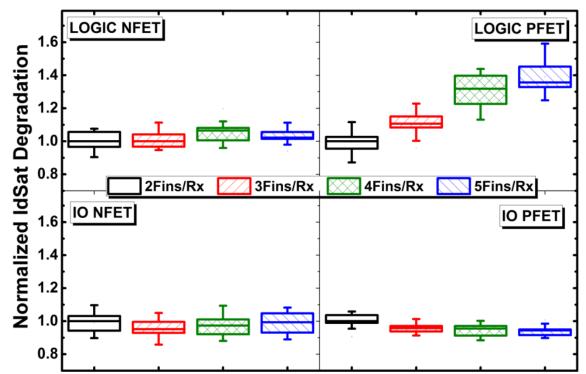

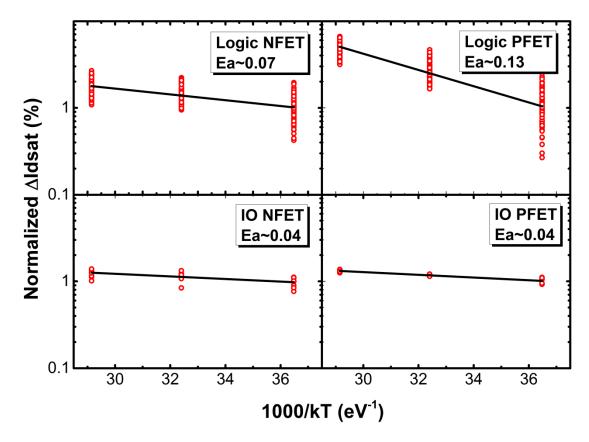

| 5.9  | Hot carrier degradation for different device types/densities. Logic PFET hot-<br>carrier degradation is modulated by self-heating (increasing with higher<br>Fins/RX count).                                                                         | 83   |

| 5.10 | Hot carrier degradation as function of temperature showing the Arrhenius<br>temperature acceleration of HC. The activation energy is extremely small except<br>for logic PFET                                                                        |      |

| Figu | re                                                                                                                                                                                                                                                                                                                                               | Page |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

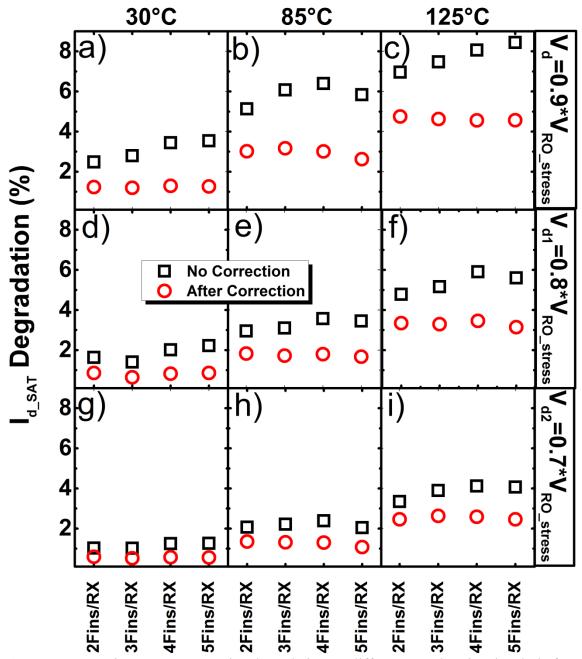

| 5.11 | Logic PFET Hot carrier degradation at different acceleration levels before and after correction. The difference in degradation at extreme condition (c) is eliminated at moderate stress (g, h, i). The need for a correction is unnecessary at moderate acceleration.                                                                           | 85   |

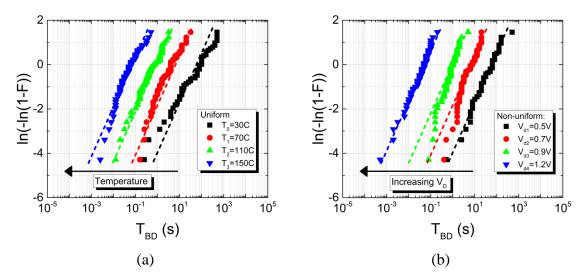

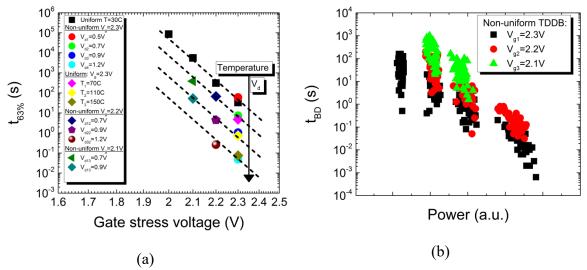

| 5.12 | Failure distributions at $V_g = 2.3V$ for different testing temperatures. TDDB lifetime decreases with increasing chuck temperatures (a). Failure distributions at $V_g = 2.3V$ for different drain voltages. TDDB lifetime decreases with increasing $V_d$ (b)                                                                                  | 87   |

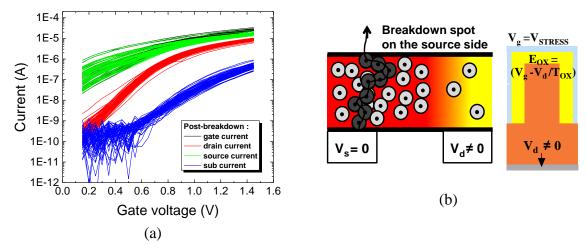

| 5.13 | Post stress non-uniform TDDB characteristic. At low $V_g$ the post stress leakage flows entirely into the source side where the breakdown spot is located (a). Representation of field distribution in non-uniform stress, where lower field is observed on the drain side explaining the reason for post stress characteristic observation (b). | 87   |

| 5.14 | Voltage acceleration for combined stress conditions under uniform and non-<br>uniform stress (a). Non-uniform lifetime correlation to power dissipated.<br>Expected decrease in life time is observed at elevated power conditions (b)                                                                                                           | 88   |

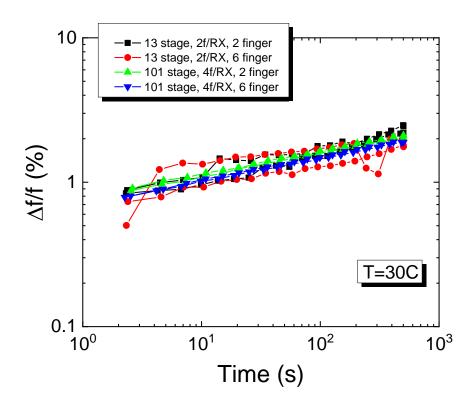

| 5.15 | Ring-Oscillator degradation showing no impact of density or heating. The SH effects on HC observed in DC are not observed in standard cell logic circuits                                                                                                                                                                                        | 89   |

| 6.1  | Illustrative figure showing a case when type III sensor ( $R_G$ ) can fail during heat dissipation in the channel while taking sensor measurement via sweep across $R_G$                                                                                                                                                                         | 95   |

# LIST OF SYMBOLS

| Symbol         | Unit              | Description                                        |

|----------------|-------------------|----------------------------------------------------|

| Α              | m <sup>2</sup>    | Area                                               |

| С              | $J m^{-3} K^{-1}$ | Volumetric specific heat                           |

| $D_N$          | $m^2 s^{-1}$      | Electron diffusion coefficient                     |

| $D_P$          | $m^2 s^{-1}$      | Hole diffusion coefficient                         |

| е              | С                 | Unit charge                                        |

| Ε              | J                 | Energy of one particle                             |

| E <sub>a</sub> | J                 | Activation energy                                  |

| $E_f$          | J                 | Chemical potential                                 |

| ε              | $V m^{-1}$        | Magnitude of electrostatic field                   |

| f              |                   | Distribution function                              |

| $f_0$          |                   | Equilibrium distribution function                  |

| f <sub>e</sub> |                   | Distribution function for electrons                |

| $f_p$          |                   | Distribution function for phonons                  |

| $f_{0e}$       |                   | Distribution function for electrons at equilibrium |

| $f_{0p}$       |                   | Distribution function for phonons at equilibrium   |

| F              | Ν                 | External force                                     |

| $g_e$          | $K^{-1} s^{-1}$   | Defined by equation on page 9                      |

| $g_p$          | $K^{-1} s^{-1}$   | Defined by equation on page 9                      |

| G                                                          |                                            |

|------------------------------------------------------------|--------------------------------------------|

| $I \qquad \qquad \mathbf{A} = \mathbf{C}  \mathbf{s}^{-1}$ | Electric current                           |

| $I_d$ or $I_{ds}$ A                                        | Drain current                              |

| <i>I</i> <sub>0</sub> A                                    | Saturation current                         |

| $J_e$ A m <sup>-2</sup>                                    | Electron current flux vector               |

| $J_h$ A m <sup>-2</sup>                                    | Hole current density                       |

| $J_u$ W m <sup>-2</sup>                                    | Flux of the total system energy            |

| $J_{u,e}$ W m <sup>-2</sup>                                | Flux energy of electrons                   |

| <b>k</b> m <sup>-1</sup>                                   | Phonon wavevector                          |

| k, k or $k_{th}$ W m <sup>-1</sup> K <sup>-1</sup>         | Thermal conductivity                       |

| $k_B$ J K <sup>-1</sup>                                    | Boltzmann constant                         |

| k <sub>e</sub>                                             | Thermal conductivity of electron           |

| L <sub>N</sub> m                                           | Electron minority-carrier diffusion length |

| L <sub>P</sub> m                                           | Hole minority-carrier diffusion length     |

| m kg                                                       | Electron effective mass                    |

| n                                                          | Phonon wavevector branch                   |

| <i>n</i> m <sup>-3</sup>                                   | Electron concentration                     |

| $n_i$ m <sup>-3</sup>                                      | Intrinsic carrier concentration            |

| $N_A$ m <sup>-3</sup>                                      | p-type dopant (acceptor) concentration     |

| $N_D$ m <sup>-3</sup>                                      | n-type dopant (donor) concentration        |

| <i>p</i> m <sup>-3</sup>                                   | Hole concentration                         |

| q C                                                        | Electronic charge (magnitude)              |

| $\dot{q}$ W m <sup>-3</sup>                                | Energy source term                         |

| R <sub>TH</sub>  | K W <sup>-1</sup> | Thermal resistance                            |

|------------------|-------------------|-----------------------------------------------|

| Q                | $W = J s^{-1}$    | Power dissipated                              |

| $Q_e$            | W m <sup>-2</sup> | Electron heat flux                            |

| $Q_p$            | W m <sup>-2</sup> | Phonon heat flux                              |

| r                |                   | Space coordinate vector                       |

| t                | S                 | Time                                          |

| t <sub>eff</sub> | S                 | Effective time                                |

| Т                | К                 | Temperature                                   |

| T <sub>amb</sub> | К                 | Ambient temperature                           |

| T <sub>e</sub>   | К                 | Electron temperature                          |

| $T_{op}$         | K                 | Temperature at operating condition            |

| $T_p$            | К                 | Phonon temperature                            |

| u                | J m <sup>-3</sup> | Total system energy per unit volume           |

| $u_e$            | J m <sup>-3</sup> | Internal energy per unit volume for electrons |

| $u_p$            | J m <sup>-3</sup> | Internal energy per unit volume for phonons   |

| v                | m s <sup>-1</sup> | Molecular instantaneous random velocity       |

| $v_s$            | m s <sup>-1</sup> | Speed of sound for longitudinal phonons       |

| v                | m s <sup>-1</sup> | Velocity                                      |

| V                | V                 | Voltage bias                                  |

| V <sub>b</sub>   | V                 | Bulk voltage bias                             |

| V <sub>d</sub>   | V                 | Drain voltage bias                            |

| $V_g$               | V | Gate voltage bias                                                     |

|---------------------|---|-----------------------------------------------------------------------|

| $V_{S}$             | V | Source voltage bias                                                   |

| $V_D$               | V | Diode forward bias voltage                                            |

| $V_T$ or $V_{Tlin}$ | V | Threshold voltage                                                     |

| Λ                   | m | Mean free path                                                        |

| τ                   | S | Relaxation or time constant                                           |

| $	au_e$             | S | Relaxation or time constant for electrons                             |

| $	au_p$             | S | Relaxation or time constant for phonons                               |

| Пе                  | V | Peltier coefficient                                                   |

| $\psi_e$            | J | Combined Fermi energy and electrostatic potential energy of electrons |

| $\psi_h$            | J | Combined Fermi energy and electrostatic potential energy of holes     |

#### **CHAPTER 1**

#### **INTRODUCTION**

The filing of the patent in 1925 by an Austrian-Hungarian physicist, Julius Edgar Lilienfeld on a method and apparatus for controlling electric currents [1] started an electronic era, which without a doubt changed many aspects and quality of our lives and still continues to do so. Modern microprocessors comprise of billions Metal-Oxide Semiconductor Field Effect Transistors (MOSFETs) which occupy a space of a fingernail-sized chip. The rise of computers enabled scientists and engineers to solve many complex problems in less time and gave means to continuously improve upon. The need for high performance computing and the competitive nature of the semiconductor industry motivates continuous scaling of the integrated circuit performance, power and circuit area which is ramped into manufacturing in two year cycles. The technology node names; 22nm, 14nm, 10nm, 7nm, et cetera, follow a 70% scaling trend of the transistor's linear physical dimension which enables doubling of circuit density every ~2 years as predicted by Moore's law [2].

While in early transistor technology nodes (>20nm) dynamic power was dominant, off-state leakage power will dominate <20nm nodes, which at the time of this writing is already one of the major power problems of cutting edge electronics. Nevertheless, active power dissipation is still on the rise, posing reliability and device performance degradation concerns.

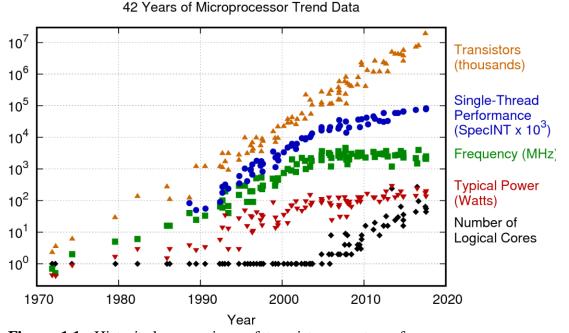

Figure 1.1 clearly shows that transistor count continues to follow an exponential growth over time, however performance of the single-thread shows signs of saturation

and multi core solutions are utilized. The increase of >100x in typical microprocessor power over the past three decades (Figure 1.1) is an alarming reality, which requires an assessment and solutions in areas at risk.

**Figure 1.1** Historical comparison of transistor count, performance, power usage and number of logical cores over 42 years. *Source: Original data by M. Horowitz, F. Labonte, O. Shacham, K. Olukotun, L. Hammond and C. Batten; 2010-2017 added by K. Rupp*

Many clever techniques have been developed to deal with both static and dynamic power dissipation. For dynamic power, frequency scaling helped to reduce power in less prioritized computational tasks and voltage scaling has been implemented to deal with off state power dissipation which both reduce power consumption and extend battery life in hand held electronics. Furthermore, many package cooling techniques have been implemented to dissipate power faster such as more effective heat sinks or on-package liquid cooling systems which are needed in high computational applications such as data servers. Better understanding of heat conduction and generation in current and future semiconductor technologies can be achieved both through thermal characterization and TCAD modeling. Such learning can aid in further improving the reduction of self-heating impact on device performance and reliability, which this dissertation will address.

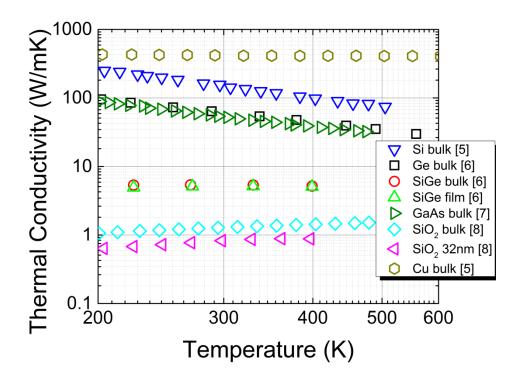

The increase of total heat rate of modern microprocessors has been addressed at interconnect and chip level [3, 4]. However, a similar thermal issue also faces circuit designers at nanometer length scales, in the transistor channel itself where considerable heat is released from the kinetic energy of the current flow. To further emphasize this concern, recent changes of the transistor geometry and introduction of new heterogeneous materials, has made the heat dissipation more difficult, making this topic important to research. Figure 1.2 illustrates the comparison of the thermal conductivities of common semiconductor and dielectric materials as a function of temperature.

**Figure 1.2** Thermal conductivities of common materials used in semiconductor manufacturing and their modulation with respect to temperature. Reduction in thermal conductivity is observed in alloy materials and dielectrics if compared to bulk Si or Ge.

Significant reduction of thermal conductivity in bulk Si is observed at increased temperatures, which has an opposite, but negligible effect in dielectrics and constant effect in copper material. Moreover, a clear reduction of thermal conductivity is observed in alloys and dielectrics if compared to Si or Ge. Search of new semiconductor materials with improved electrical and thermal properties is an active effort. Some success was observed in [9], where a thermal conductivity of 1300 (W/mK) in defect free (III-V) BAs material was reported. The findings in this dissertation will often rely on Figure 1.2 for explanation purposes.

While in operation, active and passive nanoscale electronic devices dissipate power locally in the form of heat. In a transistor, applied voltage to the channel leads to creation of an electric field that accelerates free charge carriers which gain energy and heat up. Electrons can deviate (scatter) from their path due to other electrons, phonons (lattice vibrations), interfaces or lattice imperfections. However, when scattered with phonons, electrons lose energy which in effect heats up the lattice via mechanism known as joule-heating or self-heating (SH). Electron-phonon scattering is a sum of inelastic and elastic scattering processes, of which the inelastic process is responsible of transforming the electron's kinetic energy into form of heat or lattice vibrations.

Heat transport can occur through the process of conduction, convection or radiation. Heat conduction requires a medium to transfer energy, as is the case in semiconductor material, where the heat transfer is caused by a temperature difference due to the random motion of the silicon lattice. Convection heat transfer involves a bulk fluid motion with overlaps a temperature gradient and radiation heat transfer does not require a medium, it can propagate through vacuum, where energy is carried by electromagnetic waves.

In metals, both electrons and phonons are considered heat carriers, but majority of energy flux is carried by electrons due to their abundance and greater velocity in such a medium. In semiconductors on the other hand, again both electrons and phonons act as heat carriers, but majority of heat is carried by phonons because concentration of free electrons in a semiconductor is much lower than in metals. Therefore, semiconductor doping concentration level will govern how much energy flux can be carried by electrons in a transistor channel, but it is usually negligible.

#### **1.1 Motivation**

While in bulk planar transistors heat dissipates by the process of conduction, vertically from the channel into the bulk material and laterally to source and drain contacts. In bulk FinFETs the same heatsink pathways are more confined due to its vertical geometry and poorly thermally conductive gate oxide which wraps the fin, making its narrow bulk connection the preferred heatsink pathway. Still, the channel operates at high voltage and current density which in combination with heat and poor thermal dissipation leads to a considerable self-heating effect.

#### **1.1.1 Self-Heating Effects on Semiconductor Devices**

Temperature has a direct and or inverse impact on many semiconductor parameters which can vary device performance and its reliability. The main performance parameters which are sensitive to temperature are; threshold voltage, channel mobility, offstate/junction/gate leakage and subthreshold slope of which only off-state/junction and gate leakage in Poole-Frenkel carrier transport mode show strongest thermal modulation. In the front-end-of-line devices, degradation mechanisms such as bias temperature instability (BTI), PMOS hot carrier injection (HCI) and time dependent dielectric breakdown (TDDB) are all aggravated by increase in temperature. HCI and non-uniform TDDB at constant voltage stress are most prone to self-heating effects due to channel current, which is present during stress. Nevertheless, self-heating due to switching, in highly dense and power hungry complementary logic circuits can also affect neighboring metal lines and accelerate other degradation mechanisms such as electronmigration (EM). Therefore, self-heating effects need to be understood in two operating conditions, switching as is the case in standard logic circuits and constant voltage stress as seen during reliability testing for end-of-life projections.

Local self-heating can potentially affect device performance due to inconsistency in threshold voltage ( $V_T$ ) and aggravate the effects of reliability mechanisms [10, 11, 12, 13]. With increasing switching speeds of successive technology nodes and thus rising dynamic power dissipation, the reliability degradation is accelerated for both the transistors and upper metal lines due to increased heat. This causes a reliability risk for metal lines, neighboring the power hungry circuit blocks, such as the clock buffers, which can create heat persistence modes leading to local hot spot effects. For design considerations and benchmarking across different technologies, quantifying self-heating and understanding its impact on reliability is essential for successful technology scaling.

#### **1.2 Objective**

The objective of this dissertation is to demonstrate different self-heating measurement methodologies on bulk FinFET and SOI FinFET devices and verify the results through predictive TCAD thermal simulation. Further objective is to study the impact of selfheating on reliability characterization assessment and its correlation to performance degradation. The resources utilized to perform the experimental work include; Cascade Microtech Elite 300 wafer prober, Keysight B1500A semiconductor analyzer, Keysight B2201A switching matrix and state of the art bulk/SOI 14nm FinFET wafer samples provided by GLOBALFOUNDRIES, Inc. Prober thermal chuck was used for testing at different temperatures. Because most reliability degradation mechanisms are accelerated at higher temperatures due to its Arrhenius relationship, study of self-heating effects on device performance and degradation are crucial for correct device end-of-life projections. Thus, methods to de-convolute self-heating from reliability testing and reduce its impact on device performance are needed, which will be addressed in this dissertation. Special structures were designed to study self-heating effects both in AC and DC conditions with different layout densities. With the established and verified self-heating characterization methods, this work compares the level of SH between bulk FinFET and SOI FinFET technologies. Furthermore, the dissertation assesses the impact of layout density and ambient temperature on SH characterization. Moreover, this work will evaluate the impact of self-heating on device reliability and ring-oscillator performance and propose methods to mitigate these effects. This dissertation will then summarize all the learning, draw conclusions and list areas which still need further exploration.

#### **1.3 Heat Conduction in Semiconductors**

To accurately quantify amount of heat generated in semiconductor devices under nominal operation or stress conditions, both experimental measurements and predictive simulation need to be employed. Experimental measurements aid in verifying the accuracy of the simulated results and simulation helps to quantify heat in regions which are difficult to resolve through experimental measurement. In bulk silicon the mean free path of an electron and phonon ranges from 5-10nm and 200-300nm, [14, 15] respectively. The classical heat conduction can no longer be well predicted by classical Fourier law equations as current feature size (7nm at the time of this writing) is well below the mean free path length scales, therefore quantum size effects need to be considered. To achieve correct models, the process needs to start with *ab-initio* density functional theory (DFT) simulations to predict electron/phonon transport properties in semiconductor materials and across wire/via interfaces to be then fed into continuum TCAD simulations of the 3D heat diffusion equation which incorporates the thermal conductivity of materials. Thermal conductivity of a semiconductor material can be well approximated by Equation (1.1) [5].

$$k = \frac{Cv^2\tau}{3} = \frac{Cv\Lambda}{3} \tag{1.1}$$

where C is the volumetric specific heat, v is the molecular instantaneous random velocity of a phonon,  $\tau$  is the relaxation time also known as the time constant and  $A=v\tau$  is the mean free path (average distance carrier of heat travels before scattering and losing its excess energy). *Ab-initio* methodologies have been developed that allow the calculation of C, v, and  $\tau$  for bulk materials. Phonon boundary scattering can be accounted for in Equation (1.1) by adding an extra term to the relaxation time using Matthiessen's rule. The classical heat conduction Equation (1.2) [5] can be written as,

$$C\frac{\partial T}{\partial t} = \nabla \cdot (k\nabla T) + \dot{q} \tag{1.2}$$

where  $\dot{q}$  can be identified as the energy source term. Equation 1.2 cannot properly resolve heat transfer quantity at small time scales of phonon relaxation times (nanoseconds) or at length scales shorter than an acoustic phonon mean free path (<10nm) [16]. At such scales a more elaborate formulation is needed which can discretize phonons energy and account for their frequency and different modes. The Boltzmann Equations (1.3) [5] for electrons and phonons, which accounts for coupled non-equilibrium Electron-Phonon transport without recombination, can be respectively written as

$$\frac{\partial f_e}{\partial t} + \mathbf{v} \bullet \nabla_{\mathbf{r}} f_e + \frac{\mathbf{F}}{m} \bullet \nabla_{\mathbf{v}} f_e = g_e (T_e - T_p) - \frac{f_e - f_{0e}}{\tau_e}$$

$$\frac{\partial f_p}{\partial t} + \mathbf{v} \bullet \nabla_{\mathbf{r}} f_p = -g_p (T_e - T_p) - \frac{f_p - f_{0p}}{\tau_p}$$

(1.3)

where the subscripts e and p denote electron and phonons, respectively, f is the probability distribution function,  $\mathbf{v}$  is the velocity,  $\mathbf{r}$  is the space coordinate vector,  $\mathbf{F}$  is the external force on the electron, m is mass, T is temperature,  $\tau$  is the relaxation time and g can be related to the relaxation time as  $g_{e,p} = \frac{2mv_s^2 E f_0}{k_B^2 T_e^2 T_p \tau}$  [5] for electrons and phonons.

From the Boltzmann Equations (1.3) for electrons and phonons, one can derive the energy conservation Equations (1.4) for electrons and phonons, respectively [5].

$$\frac{\partial u_e}{\partial t} + \nabla \bullet \boldsymbol{Q}_e - G(T_e - T_p) = \left(\mathcal{E} + \frac{\nabla E_f}{e}\right) \bullet \boldsymbol{J}_e$$

$$\frac{\partial u_p}{\partial t} + \nabla \bullet \boldsymbol{Q}_p + G(T_e - T_p) = 0 \tag{1.4}$$

Where, in energy conservation equation for electrons;  $Q_e$  is the heat flux carried by electrons, including both heat conduction flux and Peltier heat flux,  $\mathcal{E}$  is the electric field,  $J_e$  is the current density of electrons and the right-hand side is considered as Joule heating and thus a heat source term [5]. In the energy conservation for phonons (1.4),  $Q_p$  is the phonon heat flux. Because of difficulty in solving Boltzmann equations, the solutions can be achieved through Monte Carlo methods [17, 18] or finite volume methods [19] to calculate for thermal conductivity of a given material. The equations listed in (1.3) and (1.4) are limited to single type of charged carrier. However, a realistic semiconductor has both electrons and holes, where the recombination of an electron and hole can lead to emission of heat or light. The next section will focus on the formulation of a source term  $\dot{q}$ , which accounts for recombination.

#### **1.4 Heat Source in Semiconductors**

Heat source in a transistor occurs due to current flow through the channel and therefore power dissipated can be expressed as the product of current and voltage (1.5).

$$Q = VI \tag{1.5}$$

While Equation (1.5) offers good first order characterization results, it does not account for power loss in the instrumentation wire, semiconductor interconnect, vias and contacts.

For accurate transistor channel self-heating quantification such power drops need to be accounted for. Furthermore, it is important to understand that electrons do not entirely give up its energy in the semiconductor channel through scattering with phonons. Electrons also dissipate considerable amount of power in the contacts especially near the grounded source region where due to peak electric field, gain most energy. The rest of heat energy is dissipated in the interconnect wiring. Due to the fact that semiconductor material has both electrons and holes, which can recombine and release energy as either heat or light during transport, it is important in modeling to know where this takes place. The energy source term was discussed in [20, 21] where both treated the formulation of energy conservation as in Equation (1.6) [5].

$$\frac{\partial u}{\partial t} + \nabla \bullet \boldsymbol{J}_{\boldsymbol{u}} = 0 \tag{1.6}$$

Where in Equation (1.6), u is the total energy per unit volume, and  $J_u$  is the flux of the total system energy. Neither [20] nor [21] formulations include nonlocal transport effects and thus their usability in modeling heat transport in nanoscale devices should be taken with doubt. The extension to include nonlocal transport and nonequilibrium between carriers was derived in [5], where Equation (1.6) was casted onto equation (1.2) by deriving the energy source term,  $\dot{q}$  which includes these effects. This can be accomplished by first, including electrons, holes and phonons into u of Equation (1.6). Where, the rate of internal energy change can be expressed as in Equation (1.7) [5].

$$\frac{\partial u}{\partial t} = C \frac{\partial T}{\partial t} + \left[ \psi_e - T \left( \frac{\partial \psi_e}{\partial T} \right)_n \right] \frac{\partial n}{\partial t} - \left[ \psi_h - T \left( \frac{\partial \psi_h}{\partial T} \right)_p \right] \frac{\partial p}{\partial t}$$

(1.7)

Where in Equation (1.7), *C* is the volumetric specific heat of electrons, holes and phonons, *p* is the concentration of holes, and  $\psi_h$  is combined Fermi energy and electrostatic potential energy of holes [5]. Second, the energy flux of electrons of the total system in (1.6) is composed of the heat flux and the flux of electrochemical potential as expressed in (1.8) [5],

$$\boldsymbol{J}_{\boldsymbol{u},\boldsymbol{e}} = \boldsymbol{Q}_{\boldsymbol{e}} - \frac{\psi_{\boldsymbol{e}}}{e} \boldsymbol{J}_{\boldsymbol{e}} = \left( \Pi_{\boldsymbol{e}} - \frac{\psi_{\boldsymbol{e}}}{e} \right) \boldsymbol{J}_{\boldsymbol{e}} - k_{\boldsymbol{e}} \nabla T$$

(1.8)

where  $\Pi_e$  is the Peltier coefficient,  $J_e$  is the electron current flux vector, and  $k_e$  the electron thermal conductivity. Similar expression (1.8) can also be derived for energy flux of holes. Substituting equations (1.7) and (1.8) into equation (1.6), one can arrive at Equation (1.9) with the following expression for the energy source term [5], to be ultimately substituted into Equation (1.2).

$$\dot{q} = -\nabla \cdot \left[ \left( \Pi_e - \frac{\psi_e}{e} \right) J_e + \left( \Pi_h - \frac{\psi_h}{e} \right) J_h \right] - \left[ \psi_e - T \left( \frac{\partial \psi_e}{\partial T} \right)_n \right] \frac{\partial n}{\partial t} + \left[ \psi_h - T \left( \frac{\partial \psi_h}{\partial T} \right)_p \right] \frac{\partial p}{\partial t}$$

(1.9)

Where, in Equation (1.9)  $J_h$  is the hole current density. The divergence term includes the energy gain from the external field, the Joule heating, the Thomson effect, and the heat generation by recombination [5]. The time-dependent terms in Equation (1.9) signify the loss of carrier energy during transient processes.

### **1.5 Dissertation Organization**

### 1.5.1 Chapter 2

Chapter 2 will discuss the state of the art in self-heating research showing the understanding of problem statement and physics involved. Furthermore, quantification of self-heating will be presented with different thermally sensitive parameters which enable temperature characterization at wafer level test. Circuit layout density impact on self-heating will be explained and reliability implications examined based on research completed thus far. The research will be summarized and used as basis for subjects studied in the following chapters.

### 1.5.2 Chapter 3

Self-heating measurement methodologies including several sensor layout designs will be shown in Chapter 3. Detailed wafer level temperature characterization procedure will be explained. Moreover, self-heating measurement results will be compared and additivity of heat confirmed. Method and quantification of temperature error bar from measurements will be shown and self-heating sensor verification through stress cycle performed. The measurement results will be verified through TCAD thermal simulations, which will also reveal more learning on resolution of heat at regions unresolvable by measurement. Chapter 3 will also compare levels of self-heating between bulk FinFET and SOI FinFET technology to show ~5x more in the latter. Self-heating sensing techniques will be summarized and compared against each other and conclusions presented.

### 1.5.3 Chapter 4

Chapter 4 will focus on an experimental investigation of several effects on self-heating characterization such as layout density, measurement of the radial lateral heat dissipation distance affected by heat source in bulk and SOI front-end-of-line circuits and the impact of ambient temperature on heat conductivity in semiconductor devices. Characterization of ambient temperature effects on self-heating measurement will be verified both by introducing the heat by wafer level prober thermal chuck and by adjacent heater devices themselves. This will ultimately prove that, ambient temperature can substantially affect self-heating characterization and thus the thermal conductivity at FinFET level. The summarized findings in this chapter will be essential for further investigation of self-heating effects on reliability in FinFET technology presented in Chapter 5.

#### 1.5.4 Chapter 5

Verified test structures and a more robust understanding of self-heating characterization will bring this dissertation to study the reliability impact due to self-heating effects which will be the focus of Chapter 5. Specific structures for the design of experiments will be presented, including discrete structures for DC regime examination as seen in accelerated reliability testing and ring-oscillators for AC conditions as seen by standard logic circuits of electronic products. Self-heating due to device/circuit ON time in both operating cases will be quantified and its effects on hot carrier reliability and performance presented. Furthermore, to mitigate the effects of self-heating during DC hot-carrier degradation testing, a method of using moderate constant voltage stress will be presented which greatly reduces the impact of self-heating on device end-of-life projections. Non-uniform time dependent dielectric breakdown (TDDB) testing will examine the impact of selfheating on device time to breakdown and identify the general region of the breakdown along the channel. Additionally, in Chapter 5, results of experimental work will show no detrimental performance reliability impact due to self-heating effects on standard cell logic circuits, operating in switching conditions, based on measurements completed on different circuit densities at accelerated stress voltage conditions.

# 1.5.5 Chapter 6

Lastly, Chapter 6 will make conclusions based on the study cases of this dissertation and state recommendations based on the learning. Furthermore, future work will be discussed by highlighting key items which still need exploration and solutions.

### **CHAPTER 2**

# STATE OF THE ART

Thin body silicon FET devices such as bulk/SOI FinFET are now a reality. These novel devices make heat removal challenging which poses a problem to understand and deal with. Self-heating in semiconductors has been researched for the past 5 decades [22, 23, 24] with many advancements being made in its understanding and measurement capabilities both through characterization and TCAD thermal modeling. The state of the art in topics focusing on phonon effects and understanding of thermal conductivity in semiconductors, quantification of transistor self-heating, impact of layout on self-heating and transistor reliability will be presented in this chapter.

## 2.1 Phonon Confinement Effects

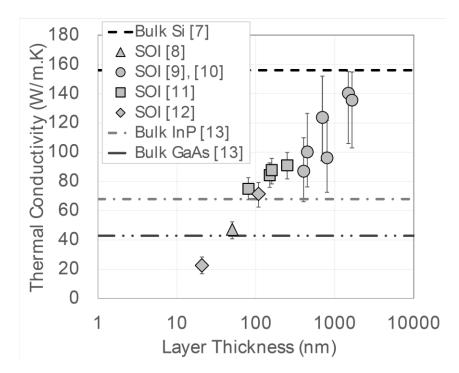

It has been shown that semiconductor channel thickness can modulate its thermal conductivity [15, 25, 26, 27, 28]. With major re-structuring of transistor geometry, advancing from planar to FinFET, emphasizes the need in understanding its impact on device performance or reliability. FinFET was introduced with many advantages, such as increased voltage headroom or higher drive currents, on the other hand its thermal characteristics is worse when compared to planar technology. Figure 2.1 compares how thermal conductivity scales with silicon layer thickness in bulk SOI, InP and GaAs substrates. The illustrated decrease in thermal conductivity for thinner SOI is due to phonon boundary scattering modes which increase with the decrease in layer thickness [27]. Quantum mechanics treat heat carriers such as electrons and phonons as material waves. Systems of finite size (i.e FinFET) can influence energy transport by altering the

wave characteristics by forming standing waves and creating new modes, which do not exist in bulk materials [5]. Standing waves, as the name implies, can oscillate the heat energy in one place without fast displacement. Thus, Figure 2.1 concludes that more selfheating can be expected from transistors built on SOI, InP or GaAs [25, 27] substrates compared to bulk silicon. Furthermore, increase in self-heating is also expected from fin engineering, where the fin aspect ratio can increases due to growing fin height and thinning of the fin, to ultimately boost the device performance.

**Figure 2.1** A summary of thermal conductivity data at 300 K for various bulk and SOI materials, showing strong scaling of thermal conductivity with Si layer thickness. *Source: C. Prasad, S. Ramey and L. Jiang, "Self-heating in advanced CMOS technologies," IEEE International Reliability Physics Symposium (IRPS), Monterey, CA, pp. 6A-4.1-6A-4.7, 2017.*

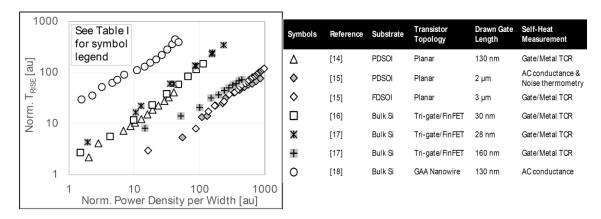

Thermal conductance degradation is also device architecture and topology dependent. While planar SOI transistors allow for thermal transport in the lateral direction and limit it in the vertical direction, the SOI FinFETs limit thermal transport in both directions. Device topology and architecture dependence on self-heating can be compared by studying the reciprocal of thermal conductivity, the thermal resistivity, which is a ratio of temperature rise to power, dissipated over distance as represented by the slope of Figure 2.2.

**Figure 2.2** A normalized plot of temperature rise ( $T_{RISE}$ ) as a function of power density per transistor width across different device architectures and substrate types, demonstrating the impact of phonon confinement on local self-heating effects. *Source: C. Prasad, S. Ramey and L. Jiang, "Self-heating in advanced CMOS technologies," IEEE International Reliability Physics Symposium (IRPS), Monterey, CA, pp. 6A-4.1-6A-4.7, 2017.*

The greater thermal headroom of bulk Si substrate in Figure 2.2 is the first observation, where the laterally confined 28-30nm bulk FinFETs (squares & asterisks) measure similar temperature rise when compared with 130nm planar PDSOI (triangles) or noting matching results of 2-3um planar SOI substrate topology (diamonds) to 160nm bulk silicon FinFET (crosses). The gate-all-around transistor (circles) shows an order of magnitude higher self-heating when compared to same gate length planar PDSOI and gives insight as to what self-heating levels can be expected in future device architectures [29, 30].

Most heat in the channel of bulk FinFET technology is dissipated down the fin and into the bulk substrate with small fraction of heat also dissipating through the source/drain contact regions as shown in Figure 2.3. It has also been shown [31] that thermal conductivity from the fin to substrate decreases as the fin aspect ratio increases, demonstrated in Figure 2.4, due to a thermal bottleneck, which makes phonon scattering modes more pronounced.

**Figure 2.3** FinFET self-heat, during transistor operation gets dissipated via several nanometers of Fin width to bulk substrate and also through the contacts.

Source: H. C. Sagong, K. Choi, J. Kim, T. Jeong, M. Choe, H. Shim, W. Kim, J. Park, S. Shin, and S. Pae, "Modeling of FinFET Self-Heating Effects in multiple FinFET Technology Generations with implication for Transistor and Product Reliability," Symposium on VLSI Technology (VLSI Technology), Honolulu, 2018.

**Figure 2.4** With increased aspect ratio in advancing technology node (left) NMOS FinFET and PMOS (not shown) exhibits self-heating temperature increase (@same power).