## **Copyright Warning & Restrictions**

The copyright law of the United States (Title 17, United States Code) governs the making of photocopies or other reproductions of copyrighted material.

Under certain conditions specified in the law, libraries and archives are authorized to furnish a photocopy or other reproduction. One of these specified conditions is that the photocopy or reproduction is not to be "used for any purpose other than private study, scholarship, or research." If a, user makes a request for, or later uses, a photocopy or reproduction for purposes in excess of "fair use" that user may be liable for copyright infringement,

This institution reserves the right to refuse to accept a copying order if, in its judgment, fulfillment of the order would involve violation of copyright law.

Please Note: The author retains the copyright while the New Jersey Institute of Technology reserves the right to distribute this thesis or dissertation

Printing note: If you do not wish to print this page, then select "Pages from: first page # to: last page #" on the print dialog screen

The Van Houten library has removed some of the personal information and all signatures from the approval page and biographical sketches of theses and dissertations in order to protect the identity of NJIT graduates and faculty.

#### ABSTRACT

## HIGH PERFORMANCE CLOUD COMPUTING ON MULTICORE COMPUTERS

#### by Jianchen Shan

The cloud has become a major computing platform, with virtualization being a key to allow applications to run and share the resources in the cloud. A wide spectrum of applications need to process large amounts of data at high speeds in the cloud, e.g., analyzing customer data to find out purchase behavior, processing location data to determine geographical trends, or mining social media data to assess brand sentiment. To achieve high performance, these applications create and use multiple threads running on multicore processors. However, existing virtualization technology cannot support the efficient execution of such applications on virtual machines, making them suffer poor and unstable performance in the cloud.

Targeting multi-threaded applications, the dissertation analyzes and diagnoses their performance issues on virtual machines, and designs practical solutions to improve their performance. The dissertation makes the following contributions. First, the dissertation conducts extensive experiments with standard multicore applications, in order to evaluate the performance overhead on virtualization systems and diagnose the causing factors. Second, focusing on one main source of the performance overhead, excessive spinning, the dissertation designs and evaluates a holistic solution to make effective utilization of the hardware virtualization support in processors to reduce excessive spinning with low cost. Third, focusing on application scalability, which is the most important performance feature for multi-threaded applications, the dissertation models application scalability in virtual machines and analyzes how application scalability changes with virtualization and resource sharing. Based on the modeling and analysis, the dissertation identifies key application features and system

factors that have impacts on application scalability, and reveals possible approaches for improving scalability. Forth, the dissertation explores one approach to improving application scalability by making fully utilization of virtual resources of each virtual machine. The general idea is to match the workload distribution among the virtual CPUs in a virtual machine and the virtual CPU resource of the virtual machine manager.

## $\begin{array}{c} \textbf{HIGH PERFORMANCE CLOUD COMPUTING ON MULTICORE} \\ \textbf{COMPUTERS} \end{array}$

by Jianchen Shan

A Dissertation

Submitted to the Faculty of

New Jersey Institute of Technology

in Partial Fulfillment of the Requirements for the Degree of

Doctor of Philosophy in Computer Science

Department of Computer Science

May 2018

Copyright © 2018 by Jianchen Shan ALL RIGHTS RESERVED

### APPROVAL PAGE

## $\begin{array}{c} \textbf{HIGH PERFORMANCE CLOUD COMPUTING ON MULTICORE} \\ \textbf{COMPUTERS} \end{array}$

#### Jianchen Shan

| Xiaoning Ding, PhD, Dissertation Advisor                                                               | Date   |

|--------------------------------------------------------------------------------------------------------|--------|

| Assistant Professor, Computer Science, New Jersey Institute of Technology                              |        |

|                                                                                                        |        |

| Cristian Borcea, PhD, Committee Member                                                                 | Date   |

| Professor, Computer Science, New Jersey Institute of Technology                                        |        |

|                                                                                                        |        |

|                                                                                                        |        |

| Narain Gehani, PhD, Committee Member  Professor, Corportor Science, New Jorgey Institute of Technology | Date   |

| Professor, Computer Science, New Jersey Institute of Technology                                        |        |

|                                                                                                        |        |

| Reza Curtmola, PhD, Committee Member                                                                   | Date   |

| Associate Professor, Computer Science, New Jersey Institute of Technology                              | Date   |

|                                                                                                        |        |

|                                                                                                        |        |

| Qing Liu, PhD, Committee Member                                                                        | Date   |

| Assistant Professor, Electrical and Computer Engineering, New Jersey Instit<br>Technology              | ute of |

#### BIOGRAPHICAL SKETCH

Author: Jianchen Shan

**Degree:** Doctor of Philosophy

Date: May 2018

#### Undergraduate and Graduate Education:

- Doctor of Philosophy in Computer Science,

New Jersey Institute of Technology, Newark, NJ, USA, 2018

- Master of Science in Computer Science, Shanghai University, Shanghai, China, 2011

- Bachelor of Science in Computer Science, Shanghai University, Shanghai, China, 2008

Major: Computer Science

#### Presentations and Publications:

- J. Shan, X. Ding, "Dynamically adjusting virtual CPU features to avoid low and unstable performance in big VMs". (under submission)

- W. Jia, C. Wang, X Chen, J. Shan, H. Cui, X. Ding, L. Cheng, F. Lau, Y. Wang, "Effectively Mitigating I/O Inactivity in vCPU Scheduling", in 2018 USENIX Annual Technical Conference (USENIX ATC 2018), 2018.

- N. R. Paiker, J. Shan, C. Borcea, N. Gehani, R. Curtmola, X. Ding, "Design and implementation of an overlay file system for cloud-assisted mobile apps", in *IEEE Transactions on Cloud Computing (TCC)*, 2018.

- J. Shan, W. Jia, X. Ding, "Rethinking the scalability of multicore applications on big virtual machines", in *IEEE 23rd International Conference on Parallel and Distributed Systems (ICPADS 2017)*, 2017.

- X. Ding, J. Shan, S. Jiang, "A general approach to scalable buffer pool management", in *IEEE Transactions on Parallel and Distributed Systems (TPDS)*, 2016.

- P. Neog, H. Debnath, J. Shan, N. Paiker, N. Gehani, R. Curtmola, X. Ding, C. Borcea, "FaceDate: A mobile cloud computing app for people matching", in 7th International Conference on MOBILe Wireless MiddleWARE, Operating Systems, and Applications (Mobilware 2016), 2016.

- J. Shan, X. Ding, N. Gehani, "APPLES: Efficiently handling spin-lock synchronization on virtualized platforms", in *IEEE Transactions on Parallel and Distributed Systems (TPDS)*, 2017.

- J. Shan, N. R. Paiker, X. Ding, N. Gehani, R. Curtmola, C. Borcea, "An overlay file system for cloud-assisted mobile applications", in 32nd International Conference on Massive Storage Systems and Technology (MSST 2016), 2016.

- J. Shan, X. Ding, N. Gehani, "APLE: Addressing lock holder preemption problem with high efficiency", in 2015 IEEE 7th International Conference on Cloud Computing Technology and Science (CloudCom 2015), 2015.

- X. Ding, J. Shan, "Diagnosing virtualization overhead for multi-threaded computation on multicore platforms", in 2015 IEEE 7th International Conference on Cloud Computing Technology and Science (CloudCom 2015), 2015.

- X. Ding, P. B. Gibbons, M. A. Kozuch, J. Shan, "Gleaner: Mitigating the blocked-Waiter wakeup problem for virtualized multicore applications", in 2014 USENIX Annual Technical Conference (USENIX ATC 2014), 2014.

- J. Shan, Y. Lei, "A novel parallel algorithm for near-field computation in N-body problem on GPU", in 2011 IEEE International Conference on Intelligent Computing and Intelligent Systems (ICIS 2011), 2011.

- J. Shan, Y. Lei, J. Zhu, "The algorithm mapping of the near-field computation in N-body problem on GPU", in 2011 International Conference on Computers, Communications, Control and Automation (CCCA 2011), 2011.

- J. Zhu, Y. Lei, J. Shan, "Parallel FMM algorithm based on space decomposition", in 2010 9th International Conference on Grid and Cloud Computing (GCC 2010), 2010.

To my beloved parents 单正海,赵玉花

#### ACKNOWLEDGMENT

First, I would like to express my deep and sincere gratitude to my doctoral advisor, Dr. Xiaoning Ding. I have been very fortunate to become his first Ph.D student and to get the opportunity to work closely with him. Being my role model, his enthusiasm, hard working, and courage to face challenges strongly motivated me. Give a man a fish, and you feed him for a day; teach a man to fish, and you feed him for a lifetime. His mentorship not only leaded me to the world of research but also made me an independent researcher and thinker, which would benefit me for a lifetime. Being my advisor, he has been always there to help and to give advice, from identifying research topics, designing experiments, to revising papers and improving presentation skills. He always holds a high and strict standard on our research work while being patient with my learning process and giving me freedom to choose research interest. His understanding, wide knowledge, and wisdom have been invaluable to me. Moreover, I sincerely appreciate his warm care and kind support that helped me going through the hard time of my life in the united states. As an international student studying oversea without family nearby, I think him not only as my advisor but also as my family.

I also wish to thank my collaborators: Dr. Cristian Borcea, Dr. Narain Gehani, Dr. Reza Curtmola, Dr. Hillol Debnath, Nafize Paiker, Weiwei Jia and Pradyumna Neog. It has been my true pleasure to work together with them. The fruitful discussions with them have been of a great value for me to broaden my perspective on how brainstorming can be so effective. In particular, I thank Dr. Cristian Borcea, the chair of the Computer Science department. He gave me the opportunity to work in the excellent and stimulating academic environment in his group. I am very grateful that he has extended my research scope and introduced me to the mobile cloud computing. I thank Dr. Narain Gehani and Dr. Reza Curtmola who made

constructive suggestions and feedbacks to my research that improved my scientific thinking and technical writing. I thank Dr. Hillol Debnath, Nafize Paiker, Weiwei Jia and Pradyumna Neog for exchanging ideas and discussing technical problems with me. They are also my lab mates who gave me their kind supports and friendships. For me, they are not only lab mates but also members in a big family.

I would like to thank all committee members of my Ph.D. dissertation for their help and advice. Especially, I thank Dr. Qing Liu from the Department of Electrical and Computer Engineering at NJIT for serving as the external committee member. I would also like to thank many anonymous conference and journal reviewers who have given me constructive comments on improving the quality of my papers.

Finally, I owe a lot to my parents, Zhenghai Shan and Yuhua Zhao, for all the sacrifices they have made to provide me the best education and support. I could not imagine how I could have gone through the toughest moments in these years, if I had not got their unconditional and endless love.

### TABLE OF CONTENTS

| $\mathbf{C}$ | Chapter Pag |                                                                                          |    |

|--------------|-------------|------------------------------------------------------------------------------------------|----|

| 1            | INT         | RODUCTION                                                                                | ]  |

|              | 1.1         | Background and Motivation                                                                | ]  |

|              | 1.2         | Contributions of Dissertation                                                            | 4  |

|              |             | 1.2.1 Diagnosing the Virtualization Overhead in the Multicore VMs                        | 4  |

|              |             | 1.2.2 Reducing the Synchronization Overhead in Multicore VMs                             | Ę  |

|              |             | 1.2.3 Analyzing the Application Scalability in the Multicore VMs                         | (  |

|              |             | 1.2.4 Improving the Application Scalability in the Multicore VMs                         | (  |

|              | 1.3         | Structure of Dissertation                                                                | 7  |

| 2            |             | GNOSING VIRTUALIZATION OVERHEAD FOR MULTI-<br>HREADED COMPUTATION ON MULTICORE PLATFORMS | Ć  |

|              | 2.1         | Introduction                                                                             | ć  |

|              | 2.2         | Experimental Settings and Methodology                                                    | 11 |

|              | 2.3         | Measuring Virtualization Overhead                                                        | 13 |

|              | 2.4         | Diagnosing Virtualization Overhead                                                       | 16 |

|              |             | 2.4.1 Overhead Due to Switching/Rescheduling Idle VCPUs                                  | 17 |

|              |             | 2.4.2 Overhead Due to Switching/Rescheduling Spinning VCPUs                              | 19 |

|              |             | 2.4.3 Overhead Due to Inter-VCPU Coordination                                            | 21 |

|              |             | 2.4.4 Overhead Due to Spinning in User Space                                             | 24 |

|              |             | 2.4.5 Overhead due to Cache-Unaware Virtualization                                       | 25 |

|              | 2.5         | Summary and Discussion                                                                   | 26 |

|              | 2.6         | Related Work                                                                             | 29 |

| 3            |             | LES: EFFICIENTLY HANDLING SPIN-LOCK YNCHRONIZATION ON VIRTUALIZED PLATFORMS              | 31 |

|              | 3.1         | Background and Motivation                                                                | 31 |

|              |             | 3.1.1 Problems Caused by Spin-locks in VMs                                               | 31 |

# TABLE OF CONTENTS (Continued)

| C | hapt                                                                         | $\mathbf{er}$ |                                                                      | Page |  |

|---|------------------------------------------------------------------------------|---------------|----------------------------------------------------------------------|------|--|

|   |                                                                              | 3.1.2         | Hardware Facilities in Processors to Control Excessive VCPU Spinning |      |  |

|   |                                                                              | 3.1.3         | The Utilization of the Hardware Facilities in VMM                    | . 33 |  |

|   | 3.2                                                                          | APPI          | LES Design and Implementation                                        | . 39 |  |

|   |                                                                              | 3.2.1         | APLE for Adjusting Spinning Thresholds                               | . 40 |  |

|   |                                                                              | 3.2.2         | Heuristic VCPU Scheduling (HVS)                                      | . 47 |  |

|   |                                                                              | 3.2.3         | APPLES Implementation                                                | . 51 |  |

|   | 3.3                                                                          | Evalu         | ation                                                                | . 53 |  |

|   |                                                                              | 3.3.1         | Experimental Setup                                                   | . 53 |  |

|   |                                                                              | 3.3.2         | Overall Performance of APPLES                                        | . 55 |  |

|   |                                                                              | 3.3.3         | APLE Performance                                                     | . 58 |  |

|   |                                                                              | 3.3.4         | HVS Performance                                                      | . 64 |  |

|   | 3.4                                                                          | Relate        | ed Work                                                              | . 66 |  |

|   | 3.5                                                                          | Concl         | usion                                                                | . 68 |  |

| 4 | RETHINKING THE SCALABILITY OF MULTICORE APPLICATIONS ON BIG VIRTUAL MACHINES |               |                                                                      |      |  |

|   | 4.1                                                                          | Introd        | duction                                                              | . 69 |  |

|   | 4.2                                                                          | Resou         | arce Sharing's Impact on Scalability                                 | . 70 |  |

|   |                                                                              | 4.2.1         | Resource Sharing between VMs                                         | . 71 |  |

|   |                                                                              | 4.2.2         | Efficiency-Based Scalability Measurement                             | . 72 |  |

|   |                                                                              | 4.2.3         | Virtualization's Impact on Scalability                               | . 75 |  |

|   | 4.3                                                                          | Appli         | cation Features Affecting Scalability                                | . 76 |  |

|   |                                                                              | 4.3.1         | Key Application Features and Scalability Indications                 | . 76 |  |

|   |                                                                              | 4.3.2         | Experimental Verification                                            | . 77 |  |

|   | 4.4                                                                          | Impro         | oving Scalability at the System Level                                | . 82 |  |

|   |                                                                              | 4.4.1         | Potential for Improving Scalability on VMs                           | . 83 |  |

|   |                                                                              | 4.4.2         | Possible Optimizations on CPU Time Allocation                        | . 84 |  |

# TABLE OF CONTENTS (Continued)

| C. | Pag  |        |                                                                                  | Page  |

|----|------|--------|----------------------------------------------------------------------------------|-------|

|    | 4.5  | Relate | ed Work                                                                          | . 89  |

|    | 4.6  | Concl  | usion                                                                            | . 90  |

| 5  |      |        | CALLY ADJUSTING VIRTUAL CPU FEATURES TO AVOID ND UNSTABLE PERFORMANCE IN BIG VMS |       |

|    | 5.1  | Introd | duction                                                                          | . 92  |

|    | 5.2  | Relate | ed Work                                                                          | . 96  |

|    | 5.3  | Key I  | deas and General Approach                                                        | . 98  |

|    |      | 5.3.1  | Amount and Urgency of CPU Time Demand                                            | . 99  |

|    |      | 5.3.2  | Predicting CPU Time Demand                                                       | . 100 |

|    | 5.4  | System | m Solution                                                                       | . 101 |

|    |      | 5.4.1  | CPU Time Allocation Component                                                    | . 102 |

|    |      | 5.4.2  | Scheduling Latency Adjustment Component                                          | . 103 |

|    |      | 5.4.3  | Resource Conflict Resolver                                                       | . 104 |

|    | 5.5  | Evalu  | ation                                                                            | . 106 |

|    |      | 5.5.1  | Prototype Implementation                                                         | . 106 |

|    |      | 5.5.2  | Experimental Setup                                                               | . 107 |

|    |      | 5.5.3  | Performance Improvement                                                          | . 108 |

|    |      | 5.5.4  | System Throughput Improvement                                                    | . 110 |

|    |      | 5.5.5  | Reducing Response Time                                                           | . 112 |

|    |      | 5.5.6  | Scalability Improvements                                                         | . 113 |

|    |      | 5.5.7  | Improvements on Performance Stability                                            | . 116 |

|    |      | 5.5.8  | Performance Improvement Breakdown                                                | . 118 |

|    | 5.6  | Concl  | usion and Future Work                                                            | . 120 |

| 6  | COI  | NCLUS  | SION                                                                             | . 121 |

| В  | BLIC | GRAF   | РНҮ                                                                              | . 123 |

### LIST OF TABLES

| Table |                                                                      |    |

|-------|----------------------------------------------------------------------|----|

| 4.1   | Summary of Four Types of Applications Based on Their Key Scalability |    |

|       | Features on VMs                                                      | 77 |

### LIST OF FIGURES

| Page | figure                                                                                                                                                                                                                                                                                                                                                                                       | Figu |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

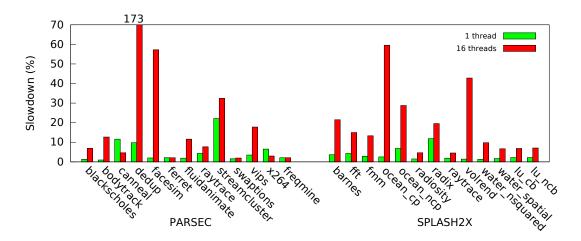

| 13   | 2.1 Slowdowns of PARSEC benchmarks and SPLASH2X benchmarks in a 16-VCPU virtual machine relative to their executions on the 16-core R720 server                                                                                                                                                                                                                                              | 2.1  |

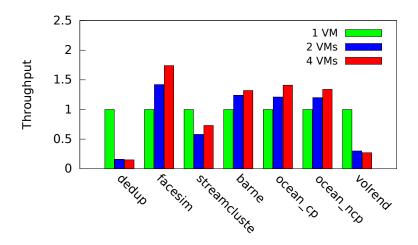

| 15   | 2.2 Throughput of PARSEC benchmarks and SPLASH2X benchmarks when the number of VMs was increased from 1 to 4                                                                                                                                                                                                                                                                                 | 2.2  |

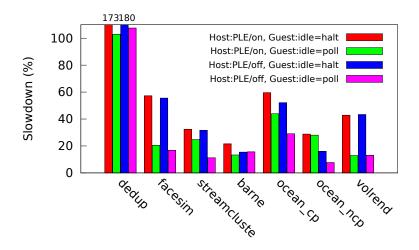

| 17   | 2.3 Slowdowns of the benchmarks are reduced after the overhead incurred by switching/rescheduling idle VCPUs and spinning VCPUs is removed.                                                                                                                                                                                                                                                  | 2.3  |

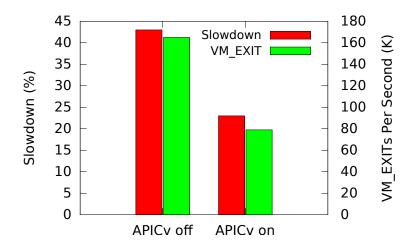

| 23   | 2.4 Slowdowns of <i>dedup</i> and the numbers of VM_EXITs per second incurred by APIC accesses when APICv is turned off and on. The number of VCPUs in the VM and the number of threads in <i>dedup</i> are 4                                                                                                                                                                                | 2.4  |

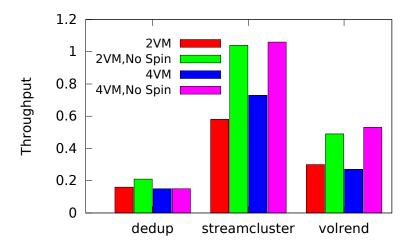

| 24   | 2.5 Throughput of dedup, streamcluster, and volrend when the system is oversubscribed                                                                                                                                                                                                                                                                                                        | 2.5  |

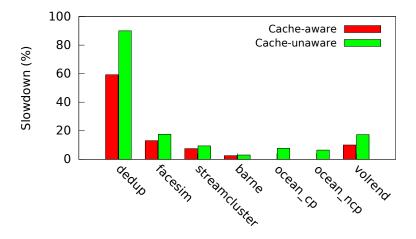

| 25   | 2.6 Comparison of the slowdowns of the benchmarks when threads in the same benchmark instance share the last level cache and when they do not                                                                                                                                                                                                                                                | 2.6  |

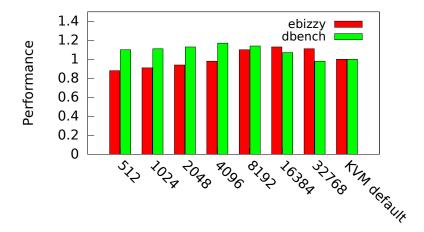

| 36   | Normalized performance of <i>ebizzy</i> and <i>dbench</i> when the spinning threshold is varied from 512 cycles to 32768 cycles, relative to the performance with the <i>default</i> KVM configuration                                                                                                                                                                                       | 3.1  |

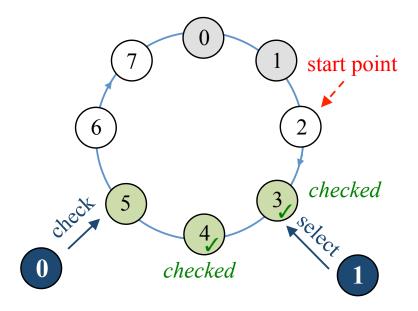

| 38   | 3.2 Candidate VCPU selection in KVM                                                                                                                                                                                                                                                                                                                                                          | 3.2  |

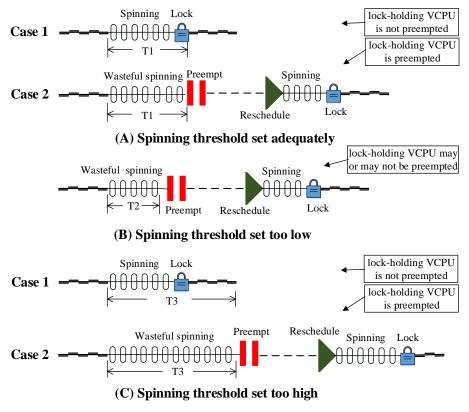

| 42   | Overhead from wasteful spinning and wasteful VCPU switches under three scenarios, using the LHP problem as an example. The figure only shows the VCPU requesting a spin-lock. The lock-holding VCPU is not shown in the figure, but its status is shown in the boxes. A "pause" symbol (parallel vertical bars) indicates that the corresponding VCPU is preempted                           | 3.3  |

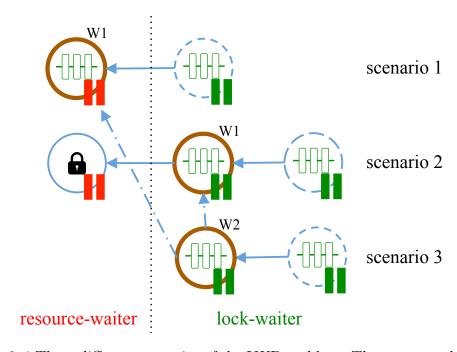

| 49   | Three different scenarios of the LWP problem. The preempted ticket-lock waiter in each scenario is illustrated using a solid circle in thick line. A "pause" symbol in red color indicates that the corresponding VCPU is preempted due to the depletion of its time slice, and a "pause" symbol in green color indicates that the corresponding VCPU is preempted due to excessive spinning | 3.4  |

# $\begin{array}{c} {\bf LIST~OF~FIGURES}\\ {\bf (Continued)} \end{array}$

| Figu | ıre                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Page |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

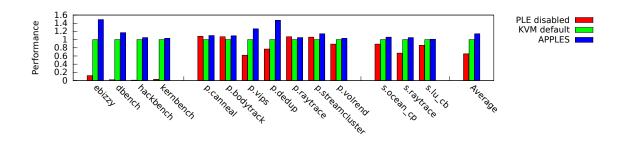

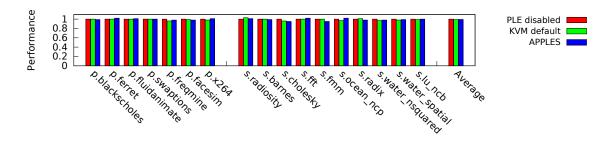

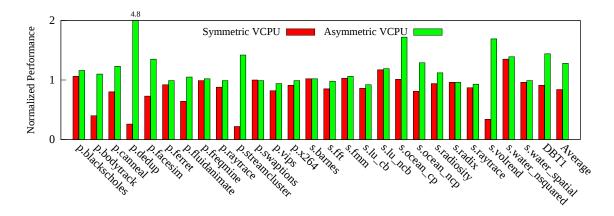

| 3.5  | Normalized performance of the spinlock-intensive benchmarks with <i>KVM</i> and <i>APPLES</i> (PLE support enabled) and PLE support disabled, when 2 VMs co-run. Prefixes 'p.' in benchmark names stand for PARSEC benchmarks, and prefixes 's.' stand for SPLASH2X benchmarks                                                                                                                                                                                                                                                                                          | 55   |

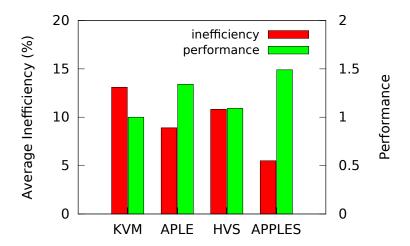

| 3.6  | Normalized performance and average inefficiency of $ebizzy$ with $KVM$ , $APLE$ , $HVS$ , and $APPLES$ when 2 VMs co-run                                                                                                                                                                                                                                                                                                                                                                                                                                                | 57   |

| 3.7  | Normalized performance of the non-spinlock-intensive benchmarks with $KVM$ and $APPLES$ (PLE support enabled) and PLE support disabled, when 2 VMs co-run. Prefixes 'p.' in benchmark names stand for PARSEC benchmarks, and prefixes 's.' stand for SPLASH2X benchmarks                                                                                                                                                                                                                                                                                                | 57   |

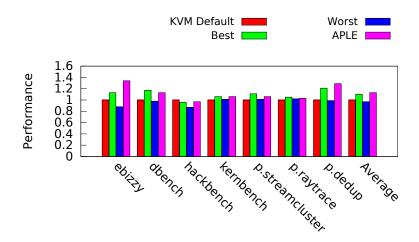

| 3.8  | Normalized performance of the benchmarks with KVM, "best", "worst", and APLE when 2 VMs co-run.                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 60   |

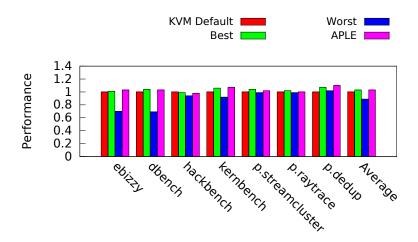

| 3.9  | Normalized performance of the benchmarks with $KVM$ , "best" and "worst", and $APLE$ when 4 VMs co-run                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 61   |

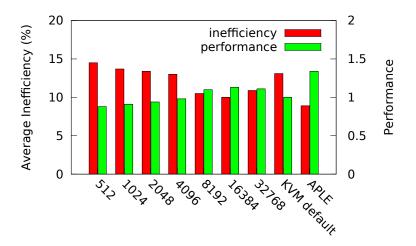

| 3.10 | Normalized performance and average inefficiency of $ebizzy$ when a system-wide spinning threshold is changed from 512 cycles to 32768 cycles, and when the stock $KVM$ and APLE is used to adjust the spinning threshold. Two VMs are used                                                                                                                                                                                                                                                                                                                              | 62   |

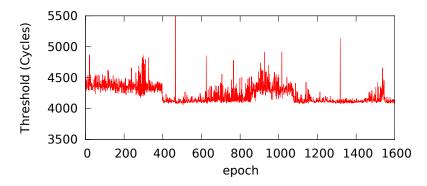

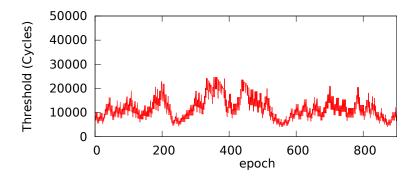

| 3.11 | Spinning threshold adjusted by the stock KVM when two VMs co-run .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 63   |

| 3.12 | Spinning threshold adjusted by APLE when two VMs co-run                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 63   |

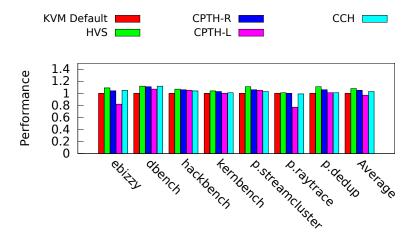

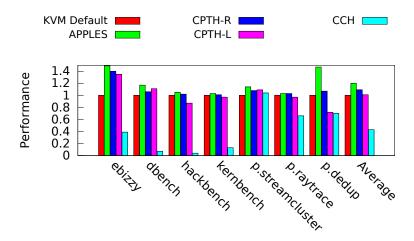

| 3.13 | Normalized performance of the benchmarks with the stock KVM, HVS, and three variants of HVS when 2 VMs co-run. The default mechanism in KVM is used to adjust spinning thresholds                                                                                                                                                                                                                                                                                                                                                                                       | 65   |

| 3.14 | Normalized performance of the benchmarks with the stock KVM, HVS, and three variants of HVS when 2 VMs co-run. APLE is used to adjust spinning thresholds for HVS and its variants                                                                                                                                                                                                                                                                                                                                                                                      | 66   |

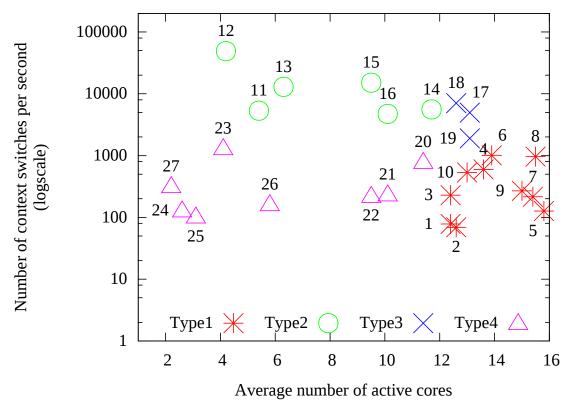

| 4.1  | Types of the PARSEC benchmark and their scalability features. The numbers are the indexes of the benchmarks, which are indexed as follows.  1: p.freqmine, 2: s.water_nsquared, 3: s.barnes, 4: s.lu_ncb, 5: p.swaption, 6: p.x264, 7: p.ferret, 8: p.vips, 9: s.raytrace, 10: s.radix, 11: p.bodytrack, 12: p.dedup, 13: p.facesim, 14: s.ocean_cp, 15: s.volrend, 16: s.cholesky, 17: s.ocean_ncp, 18: p.streamcluster, 19: p.fluidanimate, 20: s.lu_cb, 21: s.water_spatial, 22: s.fmm, 23: p.canneal, 24: s.fft, 25: p.raytrace, 26: p.blackschole, 27: s.radiosity | 79   |

# $\begin{array}{c} {\rm LIST~OF~FIGURES} \\ {\rm (Continued)} \end{array}$

| Figu | ire                                                                                                                                                                                            | Page |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

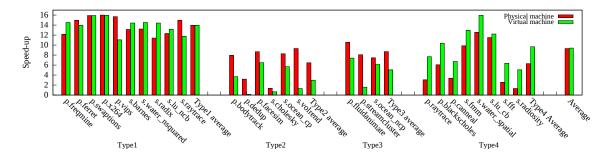

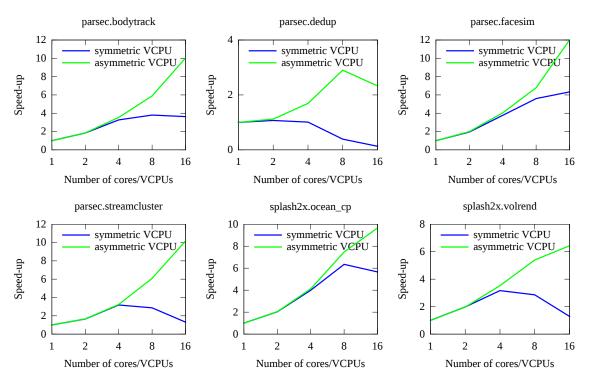

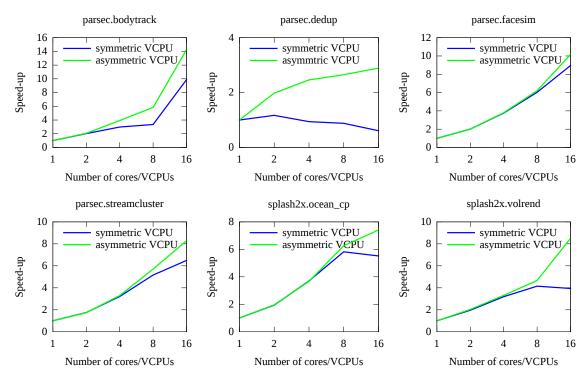

| 4.2  | Speedups of PARSEC and SPLASH2X benchmarks                                                                                                                                                     | 80   |

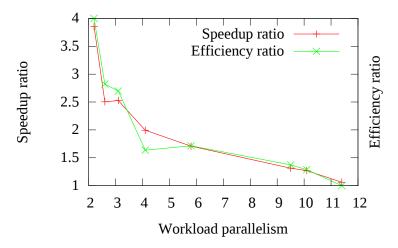

| 4.3  | Impact of virtualization on scalability for applications with different workload parallelism                                                                                                   | 82   |

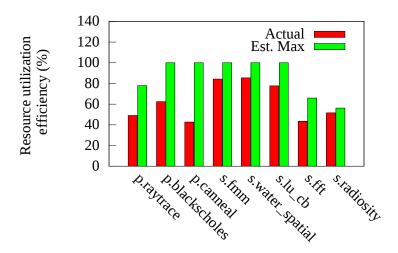

| 4.4  | Actual resource utilization efficiency and estimated maximal resource utilization efficiency of the benchmarks of the fourth type on a VM.                                                     | 84   |

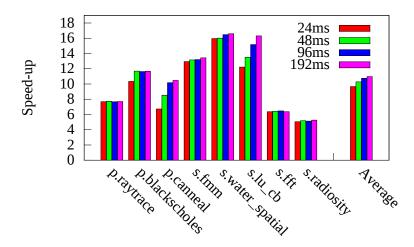

| 4.5  | Speedups when allocation period length is varied from 24ms to 192ms                                                                                                                            | 85   |

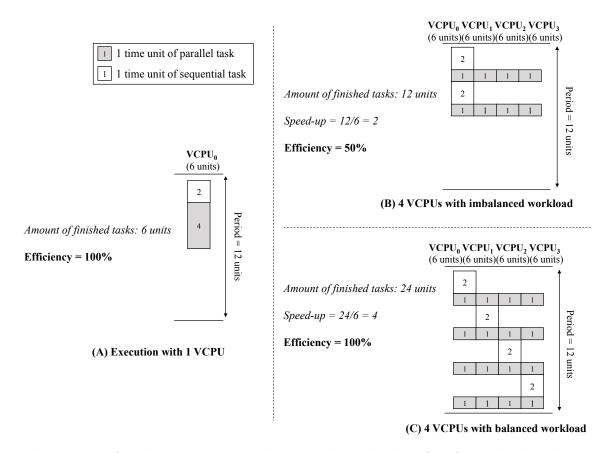

| 4.6  | An illustrative example to explain the benefit of evenly distributing workload and how even workload distribution can be achieved                                                              | 87   |

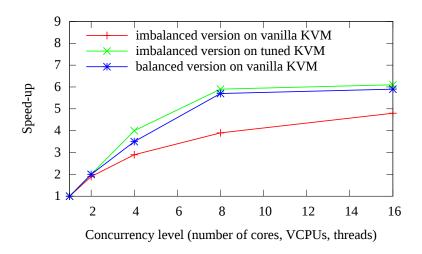

| 4.7  | Speedups of the synthetic benchmark                                                                                                                                                            | 88   |

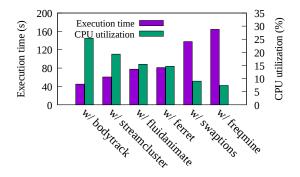

| 5.1  | Performance and CPU utilization of $bodytrack$ when it is executed on a VM colocated with another VM running different benchmarks                                                              | 92   |

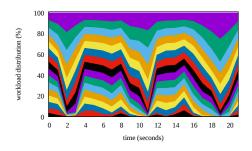

| 5.2  | Workload distribution of bodytrack                                                                                                                                                             | 93   |

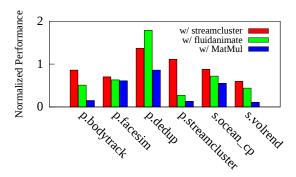

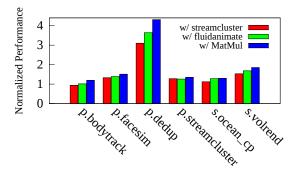

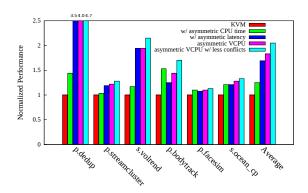

| 5.3  | Normalized performance with symmetric VCPUs and dynamic asymmetric VCPUs. The number of threads that can run concurrently in each VM is 16                                                     | 107  |

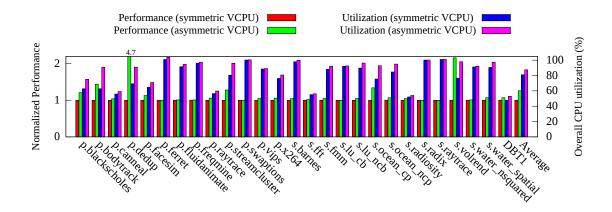

| 5.4  | Normalized performance and CPU utilization of PARSEC and SPLASH2X benchmarks on symmetric VCPUs and dynamic asymmetric VCPUs. The number of threads that can run concurrently in each VM is 16 | 111  |

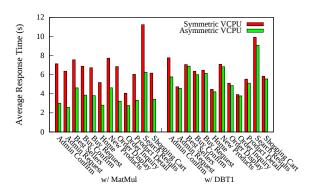

| 5.5  | Average response time of different types of transactions in DBT-1                                                                                                                              | 113  |

| 5.6  | Speedups of six benchmarks when concurrency level is varied from 1 to 16 (each benchmark is co-located with CPU-bound workload)                                                                | 115  |

| 5.7  | Speedups of six benchmarks when concurrency level is varied from 1 to 16 (four instances of the same benchmark are colocated)                                                                  | 115  |

| 5.8  | Performance variations of the six benchmarks on symmetric VMs under different interferences                                                                                                    | 117  |

| 5.9  | Performance variations of the six benchmarks on asymmetric VMs under different interferences                                                                                                   | 117  |

| 5.10 | Performance Breakdown for the six benchmarks under the five scenarios                                                                                                                          | 119  |

#### CHAPTER 1

#### INTRODUCTION

#### 1.1 Background and Motivation

Cloud computing has become main stream with virtualization being a cornerstone technology. With virtualization, virtual machines (VMs) are created as an abstraction of physical resources and complete execution environments for applications; applications from different users can be encapsulated into different virtual machines and be consolidated on the same physical machine to reduce cost and improve efficiency.

In this multi-core era, with increasing core count and memory size, the computational capacity of a physical machine keeps growing. At the same time, the demand for computing power in the cloud keeps increasing. A wide spectrum of applications need to process large amounts of data at high speeds in the cloud, e.g., analyzing customer data to find out purchase behavior, processing location data to determine geographical trends, or mining social media data to assess brand sentiment. To satisfy the demand for increasing computing power in each VM and to utilize the growing computational capacity of underlying physical machines, virtual machine sizes also grow steadily. For example, Amazon EC2 platform now provides virtual machines with 128 virtual CPUs and 3904 GiB memory.

To achieve high performance on virtual machines, similar to the executions on physical machines, applications usually create multiple threads and distribute computation to these threads. These threads run on multiple virtual CPUs in the VM, which are in turn scheduled on multiple cores in the physical machine, in order to utilize the computing power of multiple cores. Most VMs in the cloud are now with multiple virtual CPUs, and this percentage still keeps increasing. It is imperative to

study how multi-threaded applications perform in such VMs and ensure that high performance can really be achieved in the cloud.

Despite the similarity in the architectures (e.g., a VM with multiple virtual CPUs vs. a physical machine with multiple physical CPUs/cores) and execution environments (e.g., OSs and libraries), the execution and the performance of a multithreaded application on a VM can be substantially different from those on a physical machine. It has been noticed that multi-threaded applications suffer serious and unpredictable performance degradation on VMs. The causes of such difference and performance issues include an additional layer of software (i.e., overhead introduced by virtualization) and the resource sharing and resource contention between the VMs hosted on the same physical machine. While these factors also affect the executions of single-thread applications, performance impact is particularly significant for multithreaded applications, because of the special execution features of multi-threaded applications (e.g., synchronization and communications during their executions).

The performance issues with multi-threaded applications on VMs are also due to the lack of support at different system layers to fully consider the execution features of these applications. For example, at the hardware layer, many efforts have been paid to implement various hardware assistance to eliminate virtualization overhead for single-thread executions. However, the virtualization overhead caused by multi-threaded executions, such as the virtualization overhead associated with synchronization and communication, has not received enough attention, and there is little hardware assistance to effectively reduce such virtualization overhead.

At the virtual machine manager layer, virtual CPUs are not built to provision CPU resource to applications in an efficient way. For example, a virtual CPU is now implemented as an entity that is independently scheduled on a physical core and time-share the core with other virtual CPUs on the core. Thus, the virtual CPU cannot run continuously, and its computational capacity varies over time. This makes

it being unable to meet the expectation of multi-threaded applications for threads making continuous and steady progress. Also, virtual CPUs in a virtual machine are built to have symmetric performance. But such symmetry doesn't necessarily fit the application's resource demand. All these factors can significant impact the execution of multi-threaded applications on virtual machines.

Inside virtual machines, task scheduling at the guest OS layer is designed for physical cores, and is not aware of the non-continuity and varying computing capacity of the virtual CPUs. It cannot distribute workloads to virtual CPUs based on their activity and capability, and thus cannot fully utilize the allocated CPU resource to achieve high performance.

Targeting multi-threaded applications, the dissertation analyzes and diagnoses their performance issues on virtual machines, and designs practical solutions to improve their performance. First, focusing on the execution features of multi-threaded applications, the dissertation conducts extensive experiments with standard multicore applications, in order to evaluate the performance overhead on virtualization systems and diagnose the causing factors. The dissertation identifies the hardware assistance required to eliminate the virtualization overhead for multi-threaded applications to achieve high performance on virtual machines. Second, one of main sources of the performance overhead for multi-threaded applications is excessive spinning caused by spin-based synchronization, such as spin-locks. Focusing on excessive spinning, the dissertation designs and evaluates a holistic solution to make effective utilization of the hardware virtualization support in processors to reduce excessive spinning with low cost. Third, focusing on application scalability, which is the most important performance feature for multi-threaded applications, the dissertation models application scalability in virtual machines and analyzes how application scalability changes with virtualization and resource sharing. Based on the modeling and analysis, the dissertation identifies key application features and system factors that have impacts on application scalability, and reveals possible approaches for improving scalability. Forth, the dissertation explores one approach to improving application scalability by making fully utilization of virtual resources of each virtual machine. The general idea is to match the workload distribution among the virtual CPUs in a virtual machine and the virtual CPU resource of the virtual machine manager.

The research contributions are summarized in the following sections.

#### 1.2 Contributions of Dissertation

#### 1.2.1 Diagnosing the Virtualization Overhead in the Multicore VMs

Hardware-assisted virtualization, as an effective approach to low virtualization overhead, has been dominantly used. However, existing hardware assistance mainly focuses on single-thread performance. Much less attention has been paid to facilitate the efficient interaction between threads, which is critical to the execution of multi-threaded computation on virtualized multicore platforms. We aim to answer two questions: 1) what is the performance impact of virtualization on multi-threaded computation, and 2) what are the factors impeding multi-threaded computation from gaining full speed on virtualized platforms. Targeting the first question, we measure the virtualization overhead for computation-intensive applications that are designed for multicore processors. We show that some multicore applications still suffer significant performance losses in virtual machines. Even with hardware assistance for reducing virtualization overhead fully enabled, the execution time may be increased by more than 150% when the system is not over-committed, and the system throughput can be reduced by 6x when the system is over-committed. To answer the second question, with experiments, we diagnose the main causes for the performance losses. Focusing the interaction between threads and between VCPUs, we identify and examine a few performance factors, including the intervention of the

virtual machine monitor (VMM) to schedule/switch virtual CPUs (VCPUs) and to handle interrupts required by inter-core communication, excessive spinning in user space, and cache-unaware data sharing.

#### 1.2.2 Reducing the Synchronization Overhead in Multicore VMs

Spin-locks are widely used in software for efficient synchronization. However, they cause serious performance degradation on virtualized platforms, such as the Lock Holder Preemption (LHP) problem and the Lock Waiter Preemption (LWP) problem, due to excessive spinning by virtual CPUs (VCPUs). The excessive spinning occurs when a VCPU waits to acquire a spin-lock. To address the performance degradation, hardware facilities, such as Intel PLE and AMD PF, are provided on processors to preempt VCPUs when they spin excessively. Although these facilities have been predominantly used on mainstream virtualization systems, using them in a manner that achieves the highest performance is still a challenging issue. There are two core problems in using these hardware facilities to reduce excessive spinning. One is to determine the best time to preempt a spinning VCPU (i.e., the selection of spinning thresholds). The other is which VCPU should be scheduled to run after the spinning VCPU is descheduled. Due to the semantic gap between different software layers, the virtual machine monitor (VMM) does not have information about the computation characteristics on VCPUs, which is needed to address the above problems. This makes the problems inherently challenging. We propose a framework named AdPtive Pause-Loop Exiting and Scheduling (APPLES) to address these problems. APPLES monitors the overhead caused by excessive spinning and preempting spinning VCPUs, and periodically adjusts spinning thresholds to reduce the overhead. APPLES also evaluates and schedules "ready" VCPUs in a VM by their potential to reduce the spinning incurred by the spin-lock synchronization. The evaluation is based on the causality and the time of VCPU preemptions. The implementation of APPLES incurs only minimal changes to existing systems (about 100 lines of code in KVM). Experiments show that APPLES can improve performance by 3% - 49% (14% on average) for the workloads with frequent spin-lock operations.

#### 1.2.3 Analyzing the Application Scalability in the Multicore VMs

Virtual machine (VM) sizes keep increasing in the cloud. However, little attention has been paid to analyze and understand the scalability of multicore applications on big VMs with multiple virtual CPUs (VCPUs), assuming that application scalability on VMs can be analyzed in the same ways as that on physical machines (PMs). We demonstrate that, since hardware CPU resource is dynamically allocated to VCPUs, the executions of multicore applications on VMs show different scalability from those on PMs. We systematically study how the virtualization of CPU resource changes execution scalability, identifies key application features and system factors that affect execution scalability on VMs, and investigates possible directions to improve scalability.

We present a few important findings. First, the execution scalability of applications on VMs is determined by different factors than those on PMs. Second, virtualization and resource sharing can improve scalability by nature. Thus, applications may show better scalability on VMs than on PMs. Linear scalability can be achieved even when there is substantial sequential computation. Third, there is still much space to further improve execution scalability by enhancing system designs. Better scalability can be achieved by increasing allocation period length and/or matching resource allocation and workload distribution.

#### 1.2.4 Improving the Application Scalability in the Multicore VMs

Hosting big virtual machines (VMs) with multiple virtual CPUs (VCPUs) on multicore servers has become a norm in modern cloud computing infrastructures.

However, multicore programs may suffer significant performance degradation and unpredictable performance variation on such VMs, when the VMs are co-located with other VMs. One of the major causes is the CPU utilization problem of the computation on such VMs, i.e., low CPU utilization causing performance degradation and unpredictable CPU utilization causing performance variation. The CPU utilization problem is in turn caused by the mismatch between the allocation of CPU time to VCPUs and the demand for CPU time of the computation distributed on the VCPUs.

We proposes dynamically adjusting the performance features of the VCPUs in each VM, including the amount of CPU time distributed to the VCPUs and the responsiveness of the VCPUs, based on the CPU time demand of the computation on each VCPU. The objective is to match the allocation of CPU time to VCPUs with the demand for CPU time, such that the computation in the VM can proceed at the highest speed possible, which is usually determined by the fair share of CPU time made available to the VM. We provides a system solution to adjust VCPU performance features, evaluates it with extensive experiments using PARSEC and TPC-W-like workloads, and demonstrates that it can effectively avoid performance degradation and performance variation of multicore programs on virtualized platforms, and can also improve overall system throughput.

#### 1.3 Structure of Dissertation

The rest of the dissertation is organized as follows. Chapter 1.3 analyzes and identifies the virtualization overhead for the multicore applications in the cloud. Chapter 2.6 focus on the synchronization overhead in cloud. It introduces the APPLES framework to efficiently handle the spin-lock synchronization and reduce the excessive spinning. Chapter 3.5 reveals how scalability is affected by the virtualization system in the cloud and the directions to improve it. Chapter 4.6 describes how dynamic asymmetric

virtual CPUs matches the resource allocation and workload distribution for desired scalability in the cloud. We conclude this dissertation in Chapter 6.

#### CHAPTER 2

#### DIAGNOSING VIRTUALIZATION OVERHEAD FOR MULTI-THREADED COMPUTATION ON MULTICORE PLATFORMS

#### 2.1 Introduction

Applications usually have lower performance on virtual machines than on physical machines, due to the overhead introduced by virtualization. Virtualization overhead is one of the major concerns when people consolidate their workloads using virtual machines (VMs) or migrate their workloads into virtualized clouds. Processors, as primary system resources, are usually first evaluated before other resources. Thus, identifying and reducing CPU virtualization overhead are a main focus of virtualization technology [1, 2, 3, 4, 5, 6].

Hardware-assisted virtualization is an effective method to reduce virtualization overhead, and has been widely used in almost all mainstream virtualization platforms. Hardware assistance, especially that from hardware processors (e.g. Intel VT-x [7] and AMD-V [3]), makes virtual devices behave and perform identically to the corresponding hardware devices for improved performance. However, existing hardware assistance for CPU virtualization is mainly focused on single thread performance. While various types of hardware support has been developed to accelerate each individual thread (e.g., the support for nonfaulting accesses to privileged states and the support for accelerating address translation), little attention has been paid to efficient multi-threaded execution on virtual machines, especially the efficient interaction between threads. CPU virtualization usually incurs minimal performance penalty for single-thread applications on latest processors. But, as this chapter will show, multi-threaded applications may suffer substantial performance losses, even with the hardware assistance for reducing virtualization overhead fully enabled.

For example, due to the lack of facilitates to efficiently coordinate VCPUs, a multicore processor is usually virtualized into a set of single-core virtual CPUs (VCPUs) that are scheduled independently by the virtual machine monitor (VMM). This mismatch between multicore processors and virtual CPUs may not slow down single-thread applications. But it penalizes multi-threaded applications, which are designed and optimized for multicore processors and expect VCPUs to behave identically to real computing cores.

This chapter measures and diagnoses the execution overhead of multi-threaded applications on virtualized multicore platforms with the latest hardware assistance for virtualization. With the maturity of hardware-assisted virtualization, virtualization overhead has been significantly reduced for single-thread executions, and the intent of further reducing the virtualization overhead for computation-intensive applications is losing its momentum recently. With the measurement, we want to motivate architects and system designers to further reduce virtualization overhead for multi-threaded applications, and with the diagnosis, we want to find out a few promising directions for developing new techniques and/or optimizing existing designs. The contributions of this chapter are as follows.

First, this chapter shows that, while single-thread computation has decent performance on virtual machines, multi-threaded computation still suffer significant performance losses. The execution time may be increased by more than 150%, even when the host system is not over-committed. The performance loss is not due to resource sharing or contention. When the host system is over-committed, the overhead increases significantly and the system throughput may be reduced by as much as 6x. This clearly shows that there is still strong demand for further reducing the virtualization overhead for computation-intensive applications.

Then, with experiments, this chapter reveals a few factors degrading the performance of multi-threaded computation on virtualized multicore platforms. As

far as we know, some factors have not been identified or studied in other literatures. Specifically, this chapter identifies the following performance-degrading factors: 1) VCPU rescheduling/switching overhead incurred by VCPU state changes; 2) the overhead incurred by handling inter-processor interrupts (IPIs) cannot be eliminated even with hardware support such as Advanced Programmable Interrupt Controller virtualization (APICv) [8]; 3) excessive VCPU spinning in user space cannot be eliminated with hardware support such as Pause-Loop Exiting (PLE) [9]; 4) VCPU rescheduling/switching overhead incurred by preempting spinning VCPUs; 5) opaque cache architectures in virtual machines prevent efficient data sharing among threads.

Finally, this chapter discusses a few techniques that can be used to reduce the overhead caused by the above factors. To our best knowledge, this is the first work that systematically measures the virtualization overhead and diagnoses the performance degradation of multi-threaded applications on the systems with the latest hardware assistance for efficient virtualization.

#### 2.2 Experimental Settings and Methodology

We conducted our experiments on two Dell PowerEdge servers. One is a R720 server with 64GB of DRAM and two 2.40GHz Intel Xeon E5-2665 processors, each of which has 8 cores. The other is a R420 server with 48GB of DRAM and a 2.50GHz Intel Xeon E5-2430 V2 processor with 6 Ivy Bridge-EN cores. We created virtual machines on the servers. The VMM is KVM [10]. The host OS and the guest OS are Ubuntu version 14.04 with the Linux kernel version updated to 3.19.8. CPU power management can reduce application performance on VMs [11]. To prevent such performance degradation, in the experiments, we disabled the C states other than C0 and C1 of the processors, which have long switching latencies.

We selected the benchmarks in PARSEC 3.0 and SPLASH2X suites in the PARSEC benchmark package [12]<sup>1</sup>. We compiled the PARSEC and SPLASH2X

benchmarks using gcc with the default settings of the gcc-pthreads configuration in PARSEC 3.0. We used the parsecmgmt tool in the PARSEC package to run them with native inputs. In the experiments, unless stated otherwise, When we ran a benchmark in a VM we set the minimum number of threads in each benchmark equal to the number of VCPUs in the VM with the "-n" option. We pre-warmed the buffer cache in the guest operating system to minimize I/O operations. Please note that the memory capacity (16GB) of a VM is large enough to buffer the input and output data sets of the benchmark and to provide the memory space for its execution.

We carried out two groups of experiments. In the first group of experiments, we ran benchmarks with default system settings. The hardware assistance for reducing virtualization overhead (e.g. Extended Page Tables (EPT) and Pause-Loop Exiting (PLE)) was fully enabled in KVM. We ran each benchmark under three different scenarios: 1) on a VM with dedicated hardware resources, 2) on multiple VMs sharing hardware resources and with one instance of the benchmark running in each VM, and 3) on the physical machine hosting the VMs. With these experiments, we want to compare the performance of the benchmark under these scenarios and show the overhead incurred by virtualization.

In the second group of experiments, we reran the benchmarks suffering large performance degradation. We want to diagnose the root causes for the performance degradation and reveal the factors causing virtualization overhead. In the experiments, we used the following methods to diagnose the executions. In some experiments, we temporarily changed some system settings when we execute a benchmark. We selected the settings that can remove or alleviate certain types of virtualization overhead. For example, by disabling PLE support, we can reduce the overhead due to handling the VM\_EXITs triggered by PLE events. In some other experiments, we used the perf tool for Linux and KVM to profile the executions [13].

$<sup>^{1}</sup>$ We did not select benchmark *cholesky* in SPLASH2X since its execution time is too short (less than 0.01s) and varies significantly across different runs.

**Figure 2.1** Slowdowns of PARSEC benchmarks and SPLASH2X benchmarks in a 16-VCPU virtual machine relative to their executions on the 16-core R720 server.

In some cases, neither of the above methods could identify the root causes. In these cases, we tried to manually modify the benchmarks and examine the performance difference.

#### 2.3 Measuring Virtualization Overhead

This section shows the virtualization overhead of the benchmarks under two different scenarios. First, we measure the virtualization overhead when the physical machine is not over-subscribed. Only one VM was launched in the experiments, and the number of VCPUs was equal to the number of cores on the physical machine hosting the VM. We compare the performance of the benchmarks on the VM against that on the physical machine.

Figure 2.1 shows the slowdowns of the benchmarks due to virtualization on the R720 server for both single-thread executions (i.e., -n 1) and multi-threaded executions (16 threads are used, i.e., -n 16). The figure clearly shows that multi-threaded executions were slowed down on virtual machines by much larger percentages than single-threaded executions. On average, these benchmarks were slowed down by 4% with single-thread executions and by 21% with 16-thread

executions. The slowdowns of multi-threaded executions vary across the benchmarks in a very large range, from less than 1% (canneal, radiosity, and lu\_ncb) to more than 150% (dedup). While half of the benchmarks were slowed down slightly by less than 10%, seven benchmarks were slowed down substantially by more than than 20%, and three benchmarks were slowed down by more than 50%.

Then, we measure the virtualization overhead when the physical machine is over-subscribed. We launched multiple VMs and run an instance of the benchmark in each VM. We set the number of VCPUs in each VM equal to the number of cores in the physical machine and set the number of threads in each instance equal to the number of the VCPUs in a VM. Since we launched multiple VMs, the physical cores were time-shared by VMs. Thus, instead of using the performance of each individual benchmark instance, we use system throughput to analyze virtualization overhead. Specifically, we use Weighted-Speedup to measure the system throughput, which is the aggregated speedup of the benchmark instances. The speedup is relative to the execution of the benchmark on a VM when the system is not over-subscribed. Thus, the scenario with only one VM launched and one instance running on the VM serves as the baseline, and the throughput under the baseline scenario is 1. For example, if there are two instances of the benchmark running on two VMs and the execution time of the benchmark is doubled, the Weighted-Speedup is also 1 (i.e., 0.5+0.5), indicating that the throughput is the same as that under the baseline scenario. A weighted-speedup larger than 1 indicates higher throughput than the baseline.

In the experiments, we gradually increased the number of VMs (and the number of benchmark instances) from 1 to 4 before the physical memory is filled. Figure 2.2 shows how the system throughput changes for the benchmarks which suffer high virtualization overhead (slowed down by more than 20% when the system is not over-subscribed). Since VCPUs might not be always active when these benchmarks ran, the system was not fully loaded when there were fewer active VCPUs than

**Figure 2.2** Throughput of PARSEC benchmarks and SPLASH2X benchmarks when the number of VMs was increased from 1 to 4

physical cores. Increasing the number of VMs helped making a full utilization of the hardware resources and thus led to higher throughput. We observed this trend with some benchmarks. For example, the system throughput was increased by 74% for facesim when the number of VMs was increased to 4.

However, we also observed that, with a few benchmarks, the system throughput reduced dramatically when there was more than one VM. For example, when the number of VMs was increased to 2, surprisingly the throughputs of *dedup*, *streamcluster*, and *volrend*, were reduced by about 6x, 2x, and 3x, respectively. Please note that, since the baseline is the performance with the system hosting 1 VM, the performance degradation is in addition to that incurred by the virtualization overhead in the baseline scenario.

Under both scenarios, the performance degradation was measured when the same amount of physical resource was used (i.e., all the resource on the physical machine). Thus, the performance degradation was due to virtualization overhead, instead of short of physical resource. The experiments evidently show that the virtualization overhead is still high for some multicore applications and must be effectively reduced. While some execution overhead is expected on virtual

machines, the large performance degradation observed in the above experiments is not normal and makes virtualized platforms an inefficient choice for some multi-threaded workloads.

To better understand the virtualization overhead, we have investigated the possible causes for the performance degradation. Since I/O operations are minimized and memory resources are not oversubscribed, we concentrate on examining the factors related to the virtualization of hardware resources on processors. Because only some multi-threaded executions show large slowdowns, we do not investigate the factors that affect both single-thread and multi-threaded applications (e.g., increased pressure on TLBs due to the adoption of techniques such as EPT). Instead, we focus on the factors related to the interaction between threads and between VCPUs.

#### 2.4 Diagnosing Virtualization Overhead

In this section, we analyze and diagnose the performance degradation of the multithreaded applications running on virtual machines. We want to find out the factors degrading performance and to what degree they can degrade performance. Thus, we select the workloads with large performance degradation in the experiments in the previous section.

We focus our investigation on the interaction between threads and between VCPUs. Specifically, threads may interact with each other using various types of IPCs. They may also share or exchange data through shared memory space. Processors/cores usually rely on Inter Processor Interrupts (IPIs) to coordinate with each other. They access shared data in shared caches. If there are multiple caches holding multiple copies of shared data, they must keep the copies consistent. With experiments, we reveal that IPCs, IPIs, and data sharing can incur high virtualization overhead in different ways on virtual machines. In the following several subsections, we first isolate the factors degrading performance and examine their overhead when

the system is not over-subscribed. Then we analyze the executions with the system over-subscribed with multiple VMs.

Figure 2.3 Slowdowns of the benchmarks are reduced after the overhead incurred by switching/rescheduling idle VCPUs and spinning VCPUs is removed.

#### 2.4.1 Overhead Due to Switching/Rescheduling Idle VCPUs

Multi-threaded computation usually runs on multiple VCPUs in a virtual machine. Some VCPUs become idle when there lacks runnable tasks, and are activated when some tasks become runnable. To make efficient utilization of hardware resources, the VMM must be notified to handle these state changes of VCPUs. The overhead is thus incurred.

Frequent VCPU state changes can be caused by blocking synchronization, with which a thread waiting for an event blocks itself by giving up its execution resources (mainly the CPU) spontaneously. A blocked thread relies on the operating system to wake it up when the event happens. Blocking makes the number of active threads in a virtual machine change dynamically. The number of VCPUs employed by these threads also changes accordingly. When the number of active threads drops below the number of active VCPUs, some VCPUs will become idle. When the number of active threads increases beyond the number of active VCPUs, idle VCPU must be

activated. For example, when a thread calls *pthread\_mutex\_lock()* to request a mutex that is held by another thread, it will block itself through appropriate library/system calls, waiting for the release of the mutex. If there are no other threads ready to run in the system, the VCPU running the thread becomes idle. In the guest OS, an idle VCPU executes the idle loop, which typically calls a special instruction (e.g., HLT on Intel 64 and IA-32 architecture ("x86") platforms). When the mutex is released, the threads waiting for it are woken up. To maximize throughput, the guest OS may activate idle VCPUs to schedule waking threads onto them.

In a virtualized environment, the special instruction and the operations to activate idle VCPUs must be handled by the VMM, even though they would be carried out directly by hardware in a non-virtualized environment. When software issues the special instruction to place a particular VCPU into the idle state, the core running the VCPU will raise an exception and trap into the VMM. The VMM may take this opportunity to reschedule other VCPUs onto this idling core. When a thread is ready to run on an idle VCPU, the VMM must activate the VCPU and reschedule it onto a physical core. These operations incur much higher cost (e.g., usually a few microseconds) than those required in a non-virtualized environment to switching an idle core back (e.g., switching from C1 to C0 states takes no more than 1 microsecond on contemporary Intel Xeon CPUs).

To evaluate the overhead caused by switching and rescheduling idle VCPUs, we change the idling operation in the guest OS. Instead of having an idle VCPU call HLT instruction, we make it enter a polling idle loop. In this way, the overhead incurred by descheduling and rescheduling idle VCPUs can be avoided. Thus, the overhead can be indicated by comparing the performance of the benchmarks before and after the change.

We select the benchmarks with slowdowns larger than 20% with the default idling operation, and re-run them with polling idle loop. Figure 2.3 compares

the slowdowns of the benchmarks with different idling operations. By removing the overhead of descheduling and rescheduling idle VCPUs (polling idle loop), the slowdowns of the benchmarks can be significantly reduced<sup>2</sup>. The average slowdown is reduced from 59% to 35%. Among these benchmarks, dedup receives the largest performance improvement, and its slowdown is reduced from 173% to 103%. The slowdown of volrend is reduced by the largest percentage (about 2/3 of the slowdown is removed).

In real practice, the performance degradation due to handling idle VCPUs can be reduced by reducing the cost of context switches. There have been some enhancements adopted in KVM to reduce such cost (e.g., by reducing the cost of saving and restoring FPUs) [14]. For this reason, compared to the measurement that we performed earlier [15], handling idle VCPUs now causes smaller performance degradation. This shows the effectiveness of these enhancements. However, the experiments in this section also show that the overhead of handling idle VCPUs can still cause significant performance degradation to some applications and should be further reduced.

# 2.4.2 Overhead Due to Switching/Rescheduling Spinning VCPUs

After the overhead to handle idle VCPUs has been removed, the benchmarks still suffer some performance losses. To identify the causes, we continued to examine the overhead caused by switching and rescheduling spinning VCPUs.

VCPU spinning is usually caused by *spinning* synchronization, with which a thread repeatedly checks some condition (e.g., the value of a shared variable) to determine if it can continue. The spinning may be initiated explicitly by the program, and the thread remains in user space during spinning. It may also be initiated by

<sup>&</sup>lt;sup>2</sup>Note that system setting changes in this section are for diagnosis purposes and cannot be applied to general practice. While some changes may be used to improve performance in some specific scenarios (e.g., when the system is under-subscribed), they may cause serious performance degradation in other scenarios (e.g., when the system is over-subscribed).

the OS kernel when the execution of the thread traps into the kernel. On virtual machines, spinning may cause the Lock-Holder Preemption problem (LHP). LHP happens when a VCPU is descheduled from the host platform while it is holding a lock. Since the VCPU is descheduled, it cannot proceed and the lock cannot be released quickly. Thus, other VCPUs that are waiting on the lock must spin until this descheduled VCPU is rescheduled. The spinning, however, prevents the descheduled VCPU from being rescheduled quickly. This forms a situation of live-lock and significantly reduces system throughput. This live-lock situation may also be caused by spinning in synchronization primitives other than spinlocks (e.g., barriers) on virtualized platforms. For brevity, we use LHP-like problems to refer to the lock holder preemption problem and other similar problems caused by spinning<sup>3</sup>.

To deal with LHP-like problems, hardware solutions (such as Intel pause-loop-exiting (PLE) support [16]) have been implemented on processors. They detect VCPUs that have been spinning for a while and preempt these VCPUs. Thus, the VMM can involve to reallocate the resources to other VCPUs that can make progress, e.g., the VCPUs holding the locks.

However, spinning is usually used to replace blocking in synchronization primitives for higher performance. Preempting spinning VCPUs actually changes spinning back to blocking. Since the hardware support, such as PLE, preempts VCPUs only based on the lengths of spinning periods, it may degrade performance if spinning VCPUs are preempted when there are not LHP-like problems. For example, when CPU cores are not over-subscribed, LHP-like problems will not happen. Even on an over-subscribed system, it is still possible that spinning VCPUs are preempted

<sup>&</sup>lt;sup>3</sup>Synchronization primitives may combine spinning and blocking operations — a thread spins for a period of time, and if the expected event has not happen, it blocks itself. Usually, the spinning lasts only a brief period of time. Thus, the spinning will not cause LHP-like problems, and the hardware support (e.g. PLE) dealing with LHP-like problems does not detect or interrupt such short-period spinning. Since only blocking operations incur virtualization overhead with this combined approach, we does not consider the spinning in these synchronization primitives.

when they are about to finish spinning. In such cases, preempting spinning VCPUs introduces unnecessary overhead.

To test whether the PLE support causes any performance degradation, we disabled PLE support in KVM and re-ran the experiments. The slowdowns of the benchmarks (relative to their executions on the physical machine) are shown in Figure 2.3. When PLE support is disabled, the performance is only slightly improved. When polling idle loop is used, the average slowdown is lowered to 29% (from 35%) by disabling PLE support. With the default idling operation, disabling PLE reduces the average slowdown to 56% (from 59%). Disabling PLE support is most effective for ocean\_ncp, which only suffers the virtualization overhead caused by preempting spinning VCPUs. By disabling PLE, its slowdown can be reduced from 28% to 8%.