# **Copyright Warning & Restrictions**

The copyright law of the United States (Title 17, United States Code) governs the making of photocopies or other reproductions of copyrighted material.

Under certain conditions specified in the law, libraries and archives are authorized to furnish a photocopy or other reproduction. One of these specified conditions is that the photocopy or reproduction is not to be "used for any purpose other than private study, scholarship, or research." If a, user makes a request for, or later uses, a photocopy or reproduction for purposes in excess of "fair use" that user may be liable for copyright infringement,

This institution reserves the right to refuse to accept a copying order if, in its judgment, fulfillment of the order would involve violation of copyright law.

Please Note: The author retains the copyright while the New Jersey Institute of Technology reserves the right to distribute this thesis or dissertation

Printing note: If you do not wish to print this page, then select "Pages from: first page # to: last page #" on the print dialog screen

The Van Houten library has removed some of the personal information and all signatures from the approval page and biographical sketches of theses and dissertations in order to protect the identity of NJIT graduates and faculty.

#### ABSTRACT

### EXPERIMENTAL AND THEORETICAL EVALUATION OF IN-DEPTH DAMAGE DISTRIBUTION IN SAWN SILICON WAFERS

#### by Srinivasamurthy Devayajanam

As-sawn silicon wafers have surface damage that needs to be removed before any further processing into solar cells. This damage distribution can vary with cutting parameters such as wire size, slurry particle/diamond grit size, and wire usage. To date, there is no simple way to measure the degree of damage, damage depth, and damage distribution. But, this information is needed by the wafer manufacturers as well as solar cell manufacturers.

A technique based on sequential etching of silicon wafers and minority carrier lifetime ( $\tau_{eff}$ ) measurements is used to determine damage depth. In this technique, samples are sequentially etched to remove thin layers from each surface and minority carrier lifetime is measured after each etch step. Lifetime increases after each layer of damage is removed and reaches a plateau once the damage is totally removed. The thickness-removed at which the lifetime reaches a peak value corresponds to the damage depth. An accurate measurement of  $\tau_{eff}$  requires corrections to optical reflection, and transmission from silicon wafers to account for changes in the surface morphology and in the wafer thickness. This technique also allows the in-depth distribution of the damage to be quantified in terms of surface recombination velocity (SRV).

Although this method is routinely used at the National Renewable Energy Laboratory to measure damage depth, determination of damage distribution from these data requires an accurate model that coverts the minority carrier lifetime data into carrier recombination distribution. Continuity equation for excess minority carrier density ( $\Delta n$ ) is solved for the material of interest (silicon wafer with surface damage layer), and carrier concentration is integrated and normalized to match the normalized lifetime vs thickness removed curve. A simplified model for determining the recombination distribution within a wafer having surface damage is presented. Potential improvements for this model are discussed.

## EXPERIMENTAL AND THEORETICAL EVALUATION OF IN-DEPTH DAMAGE DISTRIBUTION IN SAWN SILICON WAFERS

by Srinivasamurthy Devayajanam

A Dissertation Submitted to the Faculty of New Jersey Institute of Technology in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy in Materials Science and Engineering

**Interdisciplinary Program in Materials Science and Engineering**

January 2016

Copyright © 2016 by Srinivasamurthy Devayajanam

ALL RIGHTS RESERVED

### **APPROVAL PAGE**

## EXPERIMENTAL AND THEORETICAL EVALUATION OF IN-DEPTH DAMAGE DISTRIBUTION IN SAWN SILICON WAFERS

#### Srinivasamurthy Devayajanam

| Dr. Nuggehalli M. Ravindra, Dissertation Advisor<br>Professor, Department of Physics<br>Director, Interdisciplinary Program in Materials Science & Engineering, NJIT | Date |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Dr. Bhushan Sopori, Dissertation Co-Advisor<br>Principal Engineer, National Renewable Energy Laboratory, Golden, CO                                                  | Date |

| Dr. Anthony Fiory, Committee Member<br>Consultant, Department of Physics, NJIT                                                                                       | Date |

| Dr. Eon Soo Lee, Committee Member                                                                                                                                    | Date |

Dr. Siva P.V. Nadimpalli, Committee Member Date Assistant Professor, Department of Mechanical and Industrial Engineering, NJIT

Assistant Professor, Department of Mechanical and Industrial Engineering, NJIT

### **BIOGRAPHICAL SKETCH**

| Author: | Srinivasamurthy Devayajanam |

|---------|-----------------------------|

|---------|-----------------------------|

**Degree:** Doctor of Philosophy

Date: January 2016

### **Undergraduate and Graduate Education:**

- Doctor of Philosophy in Materials Science and Engineering New Jersey Institute of Technology, Newark, NJ, 2016

- Master of Science in Physics Jawaharlal Nehru Technological University, Hyderabad, Andhra Pradesh, India, 2006

- Bachelor of Science Osmania University, Hyderabad, Andhra Pradesh, India, 2003

- Major: Materials Science and Engineering

#### **Selected Presentations and Publications:**

- Devayajanam, S., Rupnowski, P., Shet, S., Sopori, B. L., Ravindra, N. M., Caskey, D., Chang, J., and Covington, J. (2011, June 19-24). Studies on the use of liquid surface-passivation for lifetime measurements on good quality silicon wafers, Paper presented at the 37<sup>th</sup> IEEE Photovoltaic Specialists Conference, Seattle, Washington. DOI: 10.1109/PVSC.2011.6186272

- Devayajanam, S., Rupnowski, P., Shet, S., Sopori, B. L., Ravindra, N. M., Caskey, D., Chang, J., and Covington, J. (2011, July 31-August 3). A comparison of liquid passivation methods using lifetime measurements on good-quality silicon wafers, Paper presented at the 21<sup>st</sup> workshop on Crystalline Silicon Solar Cells & Modules: Materials and Processes, Breckenridge, CO.

- **Devayajanam, S.**, Rupnowski, P., Shet, S., Sopori, B. L., Ravindra, N. M., Caskey, D. (2011, October 4-7). *Evaluation of minority carrier lifetime of good quality silicon wafers using liquid surface passivation methods-A comparison*, Paper presented at the MRS Workshop on Photovoltaic Materials and Manufacturing Issues, Denver, CO, Materials Research Society, Warrendale, PA.

- **Devayajanam, S.,** Ramadass, A., and Ravindra, N. M. (2009, October 25-29). A novel approach to turbine design, Paper presented at the Material Science & Technology Conference and exhibition, Pittsburg, PA, ASM International, Materials Park, OH.

- Basnyat, P., Sopori, B., Devayajanam, S., Shet, S., Binns, J., Appel, J., Ravindra, N. M. (2015). Experimental study to separate surface and bulk contributions of light induced degradation in crystalline silicon solar cells, *Emerging Materials Research*, 4, 239-246.

- Sopori, B., Mehta, V., Devayajanam, S., Seacrist, M., Shi, G., Chen, J., Deshpande, A., Binns, J., Appel, J. (2014). Defect generation and propagation in mc-si ingots: Influence on the performance of solar cells, *Solid State Phenomena*, 205, 55-64.

- Sopori, B., **Devayajanam, S.,** Basnyat, P. (2015, June 14-19). Using minority carrier lifetime measurement to determine saw damage characteristics on Si wafer surfaces, Paper presented at the 42<sup>nd</sup> IEEE Photovoltaic Specialists Conference, New Orleans, LA.

- Sopori, B., Basnyat, P., **Devayajanam, S.,** Schnepf, R., Sahoo, S., Gedvilas, L., . . . Preece, S. (2015, June 14-19). *Analyses of diamond wire sawn wafers: effect of various cutting parameters*, Paper presented at the 42<sup>nd</sup> IEEE Photovoltaic Specialists Conference, New Orleans, LA.

- Sopori, B., Devayajanam, S., Basnyat, P., Schnepf, R., Sahoo, S., Gee, J., . . . Vansant, K. (2015, April 6-10). Surface damage introduced by diamond wire sawing of Si wafers: Measuring in-depth and the lateral distributions for different cutting parameters, Paper presented at the 2015 MRS Spring Meeting & Exhibit, San Francisco, CA, DOI: 10.1557/opl.2015.830

- Sopori, B., Devayajanam, S., Basnyat, P., Urias, F., Davis, J., Ravindra, N. M. (2015, July 26-29). Determination of damage characteristics of saw damage on Si wafers by minority carrier lifetime measurement, Paper presented at the 25<sup>th</sup> Workshop on Crystalline Silicon Solar Cells & Modules: Materials and Processes, Keystone, CO.

- Sopori, B., Basnyat, P., Devayajanam, S., (2015, July 26-29). Dependence of surface characteristics and damage distributions of diamond wire cut PV-Si wafers on cutting parameters: Implications on solar cell processing, Paper presented at the 25<sup>th</sup> Workshop on Crystalline Silicon Solar Cells & Modules: Materials and Processes, Keystone, CO.

- Sopori, B., Devayajanam, S., Basnyat, P., Moutinho, H., Nemeth, B., LaSalvia, V., Johnston, S., Binns, J., Appel, J. (2014, June 8-13). Some challenges in making accurate and reproducible measurements of minority carrier lifetime in highquality Si wafers, Paper presented at the 40<sup>th</sup> IEEE Photovoltaic Specialists Conference, Denver, CO, DOI: 10.1109/PVSC.2014.6925006

- Sopori, B., Yuan, H. C., **Devayajanam, S.**, Basnyat, P., LaSalvia, V., Norman, A., . . . Stradins, P. (2014, June 8-13). *Bulk defect generation during B-diffusion and*

oxidation of CZ wafers: Mechanism for degrading solar cell performance, Paper presented at the 40<sup>th</sup> IEEE Photovoltaic Specialists Conference, Denver, CO, DOI: 10.1109/PVSC.2014.6925021.

- Sopori, B., Devayajanam, S., Basnyat, P., Mehta, V., Moutinho, H., Nemeth, B., . . . Appel, J. (2014, April 21-25). A Comparison of surface passivation techniques for measurement of minority carrier lifetime in thin Si wafers: Toward a stable and uniform passivation, Paper presented at the 2015 MRS Spring Meeting & Exhibit, San Francisco, CA, DOI: 10.1557/opl.2014.591.

- Sopori, B., **Devayajanam, S.,** Basnyat, P., Moutinho, H., Reedy, R., VanSant, K., ... Nag, S. (2014, April 21-25). *Defects in epitaxial lift-off thin Si films/wafers and their influence on the solar cell performance*," Paper presented at the 2015 MRS Spring Meeting & Exhibit, San Francisco, CA, DOI: 10.1557/opl.2014.919.

- Sopori, B., Mehta, V., Devayajanam, S., Seacrist, M., Shi, G., Chen, J., . . . Appel, J. (2013, September 22-27). *Defect generation and propagation in mc-Si ingots: Influence on the performance of solar cells*, Paper presented at the 15<sup>th</sup> Gettering and Defect Engineering in Semiconductor Technology conference, Oxford, UK.

- Sopori, B., **Devayajanam, S.**, and Rivero, R. (2013, September 10-13). *Online solar cell process monitoring using spectroscopic imaging*, Paper presented at the MRS Photovoltaic Materials and Manufacturing Issues III Workshop, Golden, CO.

- Sopori, B., Basnyat, P., Devayajanam, S., Mehta, V., Binns, J., Appel, J. (2013, September 10-13). Bulk and surface contributions to light induced degradation in boron doped Si solar cells, Paper presented at the MRS Photovoltaic Materials and Manufacturing Issues III Workshop, Golden, CO.

- Seal, S., Budhraja, B., Sopori, B., Devayajanam, S., Basnyat, P., Varadan, V. V. (2013, September 10-13). Stress mapping of crystalline silicon wafers using ellipsometry, Paper presented at the MRS Photovoltaic Materials and Manufacturing Issues III Workshop, Golden, CO.

- Sopori, B., **Devayajanam, S.** (2013, July 28-31). *Online monitoring for Si solar cell manufacturing*, Paper presented at the 23<sup>rd</sup> workshop on crystalline silicon solar cells and modules: materials and processes, Breckenridge, CO.

- Sopori, B., **Devayajanam, S.**, Mehta, V., Nemeth, B., Binns, J., Appel, J., and Li, J. (2013, July 28-31). *Challenges in wafer preparation and surface passivation of Si wafers for reproducible measurement of high minority carrier lifetime*, Paper presented at the 23<sup>rd</sup> workshop on crystalline silicon solar cells and modules: materials and processes, Breckenridge, CO.

- Sopori, B., **Devayajanam, S.,** Rivero, R., Rupnowski, P. (2013, June 16-21). Online monitoring for Si solar cell manufacturing, Paper presented at the 39<sup>th</sup> IEEE

Photovoltaic Specialists Conference, Tampa, FL, DOI: 10.1109/PVSC.2013.6744297.

- Sopori, B., Devayajanam, S., Shet, S., Guhabiswas, D., Gedvilas, L., Jones, K., . . . Basnyat, P. (2013, June 16-21). *Characterizing damage on Si wafer surfaces cut* by slurry and diamond wire sawing, Paper presented at the 39<sup>th</sup> IEEE Photovoltaic Specialists Conference, Tampa, FL, DOI: 10.1109/PVSC.2013.6744298.

- S. Seal, Budhraja, B., Sopori, B., Devayajanam, S., Basnyat, P., Varadan, V. V. (2013, June 16-21). Defect mapping and stress mapping of crystalline silicon using spectroscopic ellipsometry, Paper presented at the 39<sup>th</sup> IEEE Photovoltaic Specialists Conference, Tampa, FL, June 2013 DOI: 10.1109/PVSC.2013.6744133.

- Sopori, B., Devayajanam, S., Basnyat, P., Shet, S., Guhabiswas, D., Sahoo, S., Mehta, V., and Rivero, R. (2012, November 19-23). *Crystalline and multi-crystalline silicon: Recent advances in the material growth and solar cell processing*, Paper presented at the 6<sup>th</sup> International Symposium on advanced science and technology of silicon materials, Kona, Hawaii.

- Sopori, B., Basnyat, P., Shet, S., Mehta, V., Devayajanam, S., Binns, J., and Appel, J., (2012, July 22-25). Experimental study of light induced degradation in c-Si solar cells: Separating the bulk and the surface contributions, Paper presented at the 22<sup>nd</sup> workshop on crystalline silicon solar cells and modules: Materials and processes, Vail, CO.

- Sopori, B., Basnyat, P., Devayajanam, S., Shet, S., Mehta, V., Binns, J., Appel, J., (2012, June 3-8). Understanding light-induced degradation of c-Si solar cells, Paper presented at the 38<sup>th</sup> IEEE Photovoltaic Specialists Conference, Austin, TX, DOI: 10.1109/PVSC.2012.6317798.

- Sopori, B., Guhabiswas, D., Rupnowski, P., Shet, S., Devayajanam, S., and Moutinho, H. (2011, June 19-24). A new method for rapid measurement of orientations and sizes of grains in multi-crystalline silicon wafers, Paper presented at the 37<sup>th</sup> IEEE Photovoltaic Specialists Conference, Seattle, Washington, DOI: 10.1109/PVSC.2011.6186278.

- Sopori, B., Guhabiswas, D., Rupnowski, P., Shet, S., Devayajanam, S., Moutinho, H., and Ravindra, N. M. (2011, July 31-August 3). *Rapid measurement of* orientations and sizes of grains in multi-crystalline silicon wafers: A new technique, Paper presented at the 21<sup>st</sup> workshop on Crystalline Silicon Solar Cells & Modules: Materials and Processes, Breckenridge, CO.

- Sopori, B., Guhabiswas, D., Rupnowski, P., Shet, S., Devayajanam, S., Moutinho, H. and N. M.Ravindra, (2011, October 4-7). *Characterization of grains in multi-*

*crystalline Si wafers using an optical reflectance technique*, Paper presented at the MRS Photovoltaic Materials and Manufacturing Issues II, Denver, CO.

- Sopori, B., Rupnowski, P., Guhabiswas, D., Devayajanam, S., Shet, S., Khattak, C. P., Albert, M. (2010, June 20-25). *Reflectance spectroscopy-based tool for high-speed characterization of silicon wafers and solar cells in commercial production*, Paper presented at the 35<sup>th</sup> IEEE Photovoltaic Specialists Conference, Honolulu, Hawaii, DOI: 10.1109/PVSC.2010.5616540.

- Sopori, B., Rupnowski, P., Shet, S., Budhraja, B., **Devayajanam, S.,** Seacrist, M., . . . Deshpande, A. (2010, August 1-4). *Defects, defect distributions, andiImpurities in multi-crystalline silicon: Their influence on solar cell performance*, Paper presented at the 20<sup>th</sup> Workshop on Crystalline Silicon Solar Cells & Modules: Materials and Processes, Breckenridge, CO.

Dedicated to my mother, Lalitha Kumari Devayajanam and father, (Late) Venkata Rama Charyulu Devayajanam

#### ACKNOWLEDGEMENTS

I would like to express my sincere gratitude to my advisor, Dr. Nuggehalli M. Ravindra, at the New Jersey Institute of Technology, Newark, NJ and co-advisor, Dr. Bhushan Sopori, at the National Renewable Energy Laboratory, Golden, CO for their invaluable guidance and constant encouragement given to me throughout this research work. I thank committee members: Dr. Anthony Fiory, Dr. Eon-Soo Lee and my Dr. Siva P.V. Nadimpalli for actively participating in my dissertation committee and providing constructive criticism and valuable suggestions at all stages of this research work.

I acknowledge the support from the collaborative research program between New Jersey Institute Technology and National Renewable Energy Laboratory through which funding for this study and my research assistantship is sponsored.

I express my gratitude to my colleagues, Dr. Prakash Basnyat, Dr. Peter Rupnowski, Dr. Vishal Mehta, Dr. Sudhakar Shet, Dr. Vinay Budhraja, Dr. Debraj Guhabiswas, and Dr. Satosh Sahoo for their help and support during this research work.

I am thankful to my uncle Mr. Krishna Prasad Agnihotram for his unwavering support and Mr. Manohar Madeppa, Mr.Nagaraju Kalal for their friendship.

X

| Cł | Chapter                                          |      |

|----|--------------------------------------------------|------|

| 1  | INTRODUCTION                                     | 1    |

|    | 1.1 Silicon Sawing                               | 1    |

|    | 1.2 Surface and In-depth Damage Caused by Sawing | 3    |

|    | 1.2.1 Roughness                                  | 6    |

|    | 1.2.2 Morphology or Phase Transformation         | 8    |

|    | 1.2.3 Micro-Cracks                               | 12   |

|    | 1.2.4 Periodic Features or Striations            | 14   |

|    | 1.2.5 Stress and Dislocations                    | 16   |

|    | 1.3 Need for the In-depth Damage Evaluation      | 16   |

| 2  | LITERATURE REVIEW                                | 17   |

|    | 2.1 Angle Polishing                              | 17   |

|    | 2.2 Electron Microscopy                          | 20   |

|    | 2.3 Photoluminescence                            | 22   |

|    | 2.4 Lasers                                       | 23   |

|    | 2.5 Fracture Mechanics                           | 25   |

|    | 2.6 Electrical Characterization                  | 26   |

| 3  | EXPERIMENTAL METHODS AND TECHNIQUES              | . 29 |

# **TABLE OF CONTENTS**

# TABLE OF CONTENTS (Continued)

| Cł | Chapter                                           | Page   |

|----|---------------------------------------------------|--------|

|    | 3.1 Optical Microscopy                            | 29     |

|    | 3.2 Optical Surface Profiling                     | 32     |

|    | 3.3 Contact Surface Profiling                     | 36     |

|    | 3.4 Taper Etching and µw-PCD Imaging              | 39     |

|    | 3.5 Photoluminescence                             | 40     |

|    | 3.6 Minority Carrier Lifetime                     | 41     |

| 4  | SEQUENTIAL ETCHING AND MINORITY CARRIER LIFETIME  | 45     |

|    | 4.1 Wafer Preparation                             | 45     |

|    | 4.2 Etching                                       | 46     |

|    | 4.3 Changes in Reflectance and Transmittance      | 49     |

|    | 4.4 Minority Carrier Lifetime                     | 51     |

|    | 4.5 Photoluminescence                             | 56     |

| 5  | THEORETICAL MODEL FOR EVALUATION OF IN-DEPTH DAMA | AGE 58 |

|    | 5.1 Introduction                                  | 58     |

|    | 5.2 Theoretical Model                             | 59     |

|    | 5.3 Results and Discussion                        | 63     |

# TABLE OF CONTENTS (Continued)

| Ch | hapter      | Page |

|----|-------------|------|

| 6  | CONCLUSIONS | 69   |

| RE | EFERENCES   | 70   |

# LIST OF TABLES

| Tab | ble                                                                                 | Page |

|-----|-------------------------------------------------------------------------------------|------|

| 5.1 | Material Property Values of n-type Si DCW Wafer Quarters Etched for Different Times | 65   |

| 5.2 | Material Property Values of p-type Si DCW Wafer Quarters Etched for Different Times | 67   |

# LIST OF FIGURES

| Figure |                                                                                                                                                                                                                                   | Page |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 1.1    | Illustrations of SWC and DWC sawing techniques                                                                                                                                                                                    | 3    |

| 1.2    | Optical and SEM images showing lower and higher magnification images of<br>the saw patterns/marks in DWC-Resin cut, slurry cut, and DWC-Nickel cut<br>wafers                                                                      |      |

| 1.3    | Illustration of a single grain indentation in silicon, also showing various crack types                                                                                                                                           | 5    |

| 1.4    | SEM images showing surface roughness in (a) lower and (b) higher<br>magnification. (c) Schematic of surface roughness and various terms<br>associated                                                                             |      |

| 1.5    | Raman spectra of crystalline silicon wafer surfaces indented with various indenters (of varying indenter angle $\psi$ ) at various maximum loads                                                                                  |      |

| 1.6    | AFM images of (a) SWC wafer and (b) DWC wafer                                                                                                                                                                                     | 10   |

| 1.7    | Raman spectra of (a) chipped-off region (b) a smooth groove                                                                                                                                                                       | 11   |

| 1.8    | A cross-sectional TEM image of a diamond cut sample showing formation of dislocation loops that are about 1 $\mu$ m deep and a layer of amorphous phase going to a depth of 0.8 $\mu$ m                                           |      |

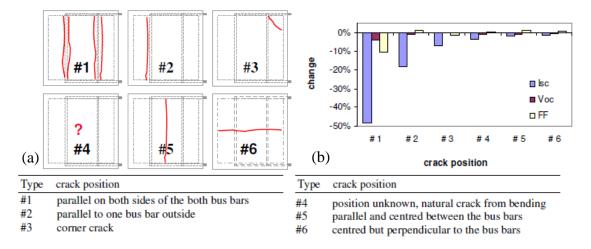

| 1.9    | (a) Illustrations of single cell modules with different crack positions intitated manually, (b) change in cell paramters with respect to the crack position (note- Crack locations are numbered and described in the same figure) |      |

| 1.10   | SEM image of an as-sawn silicon wafer sample showing micro-cracks propagating into to the wafer bulk (scale 2 $\mu$ m).                                                                                                           | 13   |

| 1.11   | Optical scanner images of (a) DWC wire cut and (b) SWC wire cut mc-<br>silicon wafers                                                                                                                                             | 14   |

| 1.12   | 3D Laser confocal microscope map of as sawn wafer surface cut by reciprocating wire saw (note-feature height scan is shown next to the map in the same image for reference)                                                       |      |

| 2.1    | Optical microscope images of angle polished and defect etched (a) DWC and (b) SWC wafers                                                                                                                                          | 18   |

| Figu | re I                                                                                                                                                                                                                                                                                                                | Page |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 2.2  | Box plots of crack depth as a function of crystal orientation                                                                                                                                                                                                                                                       | 19   |

| 2.3  | (a) Sub-surface crack density distribution at a given area on wafer surface,<br>(b) Distribution of crack density occurrence compared at three different<br>locations on a given wafer surface (IM= wire entry point, MM= center of<br>the wafer, OM= wire exit point, $c_{max}$ =critical subsurface damage depth) | 19   |

| 2.4  | TEM micrographs of as-sawn DWC wafer surfaces cut with diamond grit impregnated in (a) electroplated grit binder, (b) Resin grit binder                                                                                                                                                                             | 20   |

| 2.5  | SEM micrographs of oxidized, etched wafer surfaces showing (a) Dislocation loops generated because of heavier mechanical damage imparted by the wire sawing, (b) Stacking faults generated because of lighter mechanical damage induced by the lapping process                                                      | 21   |

| 2.6  | Photoluminescence line scans across the 156mm x 156mm wafer surface                                                                                                                                                                                                                                                 | 22   |

| 2.7  | Band-to-band (top row) and defect band (bottom row) PL images of sister wafers after each cell fabrication step                                                                                                                                                                                                     | 23   |

| 2.8  | Raman laser scattering images of silicon wafers of same final thickness but with different sub-surface damage conditions, (a) #320 diamond grit, coarse grinding damage (wafer A), and #2000 diamond grit, fine grinding damage removal of (b) 10µm, and (c) 30µm                                                   | 23   |

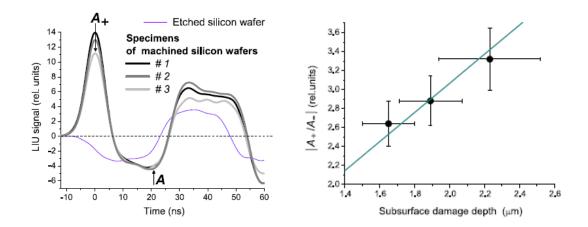

| 2.9  | (a) Temporal profiles of laser induced ultrasonic signals in silicon wafers with varying SSD (#1-1.65 $\mu$ m, #2-1.89 $\mu$ m, #3-2.23 $\mu$ m), (b) Plot showing empirical relation between experimental (points) and ratio of amplitudes of compression and rarefaction phases of the LIU signal                 | 24   |

| 2.10 | 2D Raman spectra of (a) CMP, (b) CP, and (c) as-sawn SWC wafer cross-<br>sections, (d) Raman shift depth profiles extracted from the 2D spectra,<br>(RED line- as-sawn SWC, BLACK line- CMP, BLUE line-CP)                                                                                                          | 25   |

| 2.11 | Theoretical (red x marks) and experimental strength distributions of as-<br>sawn, and etched silicon wafers                                                                                                                                                                                                         | 26   |

| 2.12 | Change in surface photo voltage as a function of thickness removed from<br>one side of the silicon wafer                                                                                                                                                                                                            | 27   |

| Figu | re                                                                                                                                                                                                                                                                                                               | Page |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 2.13 | Minority carrier lifetime measured vs depth of damage layer removed from<br>each side of the silicon wafer (plots of various polycrystalline wafers cut<br>using SWC and DWC methods are shown)                                                                                                                  | 28   |

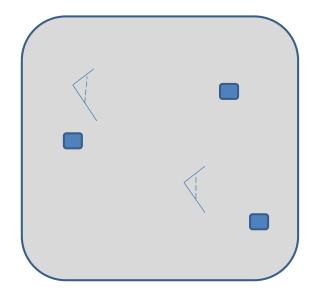

| 3.1  | Illustration of sample preparation method for optical microscopy, contact<br>and optical profilometry. (Note- L shaped Scribing marks for reference, and<br>dashed lines represent locations from where the Dektak scans are obtained.<br>Colored squares are arbitrary locations chosen for optical microscopy) | 30   |

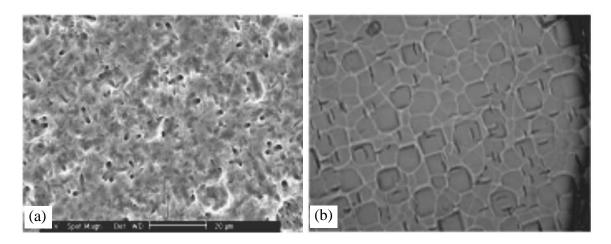

| 3.2  | Optical microscope images (at 10x magnification) of a DWC wafer (thick wire/grit) sample (a) before (or as-sawn surface), and (b) after damage removal etching in 115 solution for 15 min                                                                                                                        | 31   |

| 3.3  | Optical microscope images (at 10x magnification) of a DWC wafer (thick wire/grit) sample (a) before (or as-sawn surface), and (b) after damage removal etching in 115 solution for 15 min                                                                                                                        | 31   |

| 3.4  | Optical microscope images (at 10x magnification) of a DWC wafer (thin wire/grit) sample (a) before (or as-sawn surface), and (b) after damage removal etching in 115 solution for 15 min                                                                                                                         | 31   |

| 3.5  | Optical microscope images (at 50x magnification) of a DWC wafer (thin wire/grit) sample (a) before (or as-sawn surface), and (b) after damage removal etching in 115 solution for 15 min                                                                                                                         | 32   |

| 3.6  | Optical profilometer images of DWC wafer (wire/grit size: $120/12-25 \mu m$ ) surface in (a) as-sawn (b) 2 min etched and (c) 4 min etched condition                                                                                                                                                             | 34   |

| 3.7  | Optical profilometer images of DWC wafer (wire/grit size: $100/10-20 \mu m$ ) surface in (a) as-sawn (b) 2 min etched and (c) 4 min etched condition                                                                                                                                                             | 35   |

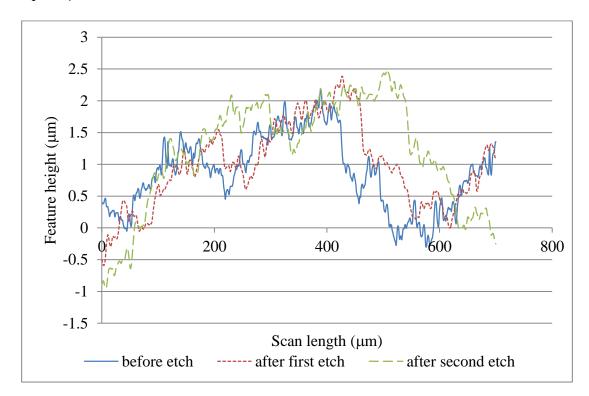

| 3.8  | Dektak scans of as-sawn, 2 min etched (first etch) and 4 min etched (second etch) wafer surfaces. (Cutting wire/grit size - $100/10-20 \mu m$ )                                                                                                                                                                  | 36   |

| 3.9  | Dektak scans of as-sawn, 2 min etched (first etch) and 4 min etched (second etch) wafer surfaces. (Cutting wire/grit size - $120/12-25 \mu m$ )                                                                                                                                                                  | 37   |

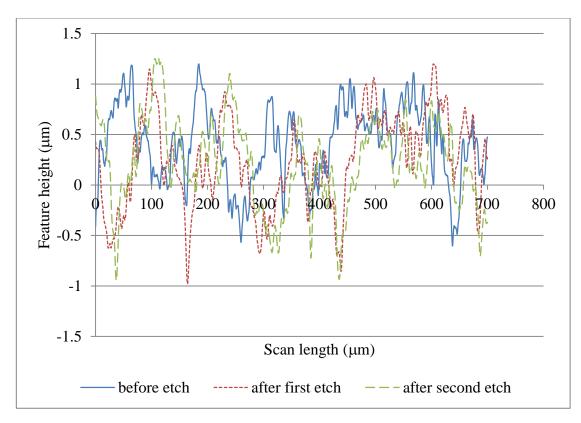

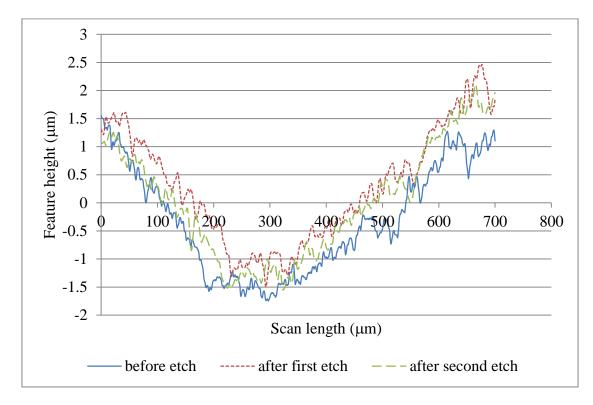

| 3.10 | Dektak scans of as-sawn, 2 min etched (first etch) and 4 min etched (second etch) wafer surfaces over a groove produced by sawing. (Cutting wire/grit size - 100/10-20 µm)                                                                                                                                       | 38   |

| Figu | re                                                                                                                                                                                                                                                             | Page |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

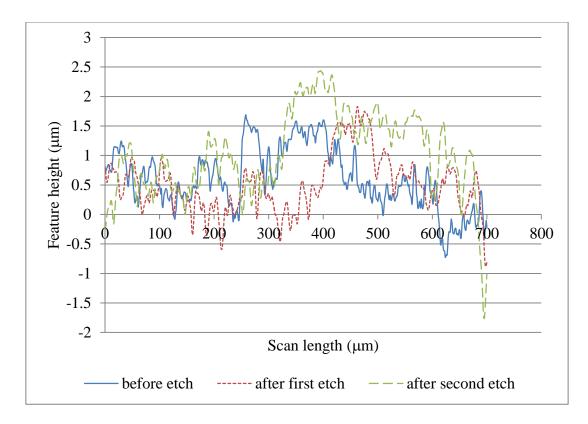

| 3.11 | Dektak scans of as-sawn, 2 min etched (first etch) and 4 min etched (second etch) wafer surfaces at a different area on the sample used in Figure 3.9. (Cutting wire/grit size - $120/12-25 \mu m$ )                                                           | 39   |

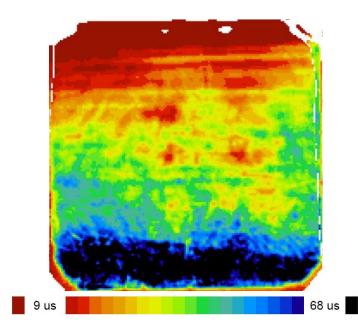

| 3.12 | Microwave PCD image of an as-sawn wafer surface after taper etching in 115 solution                                                                                                                                                                            | 40   |

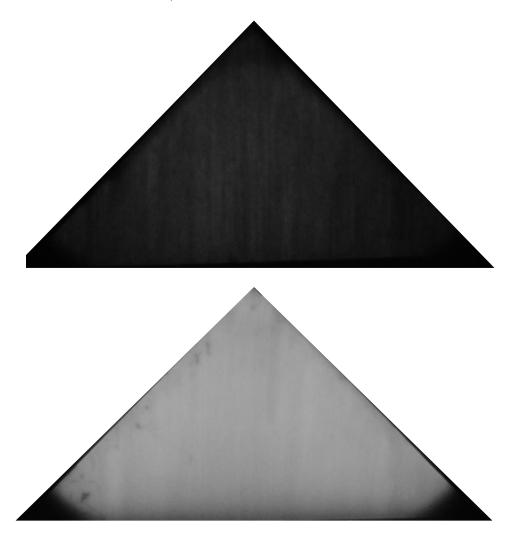

| 3.13 | Photoluminescence images of (a) partially etched wafer quarter surface and,<br>(b) fully etched wafer quarter surface (damage removed completely).Both<br>the samples are cleaned in piranha solution, HF dipped and passivated in<br>Iodine-Ethanol solution. | 41   |

| 3.14 | Wafer-lifetime tool used for the evaluation of minority carrier lifetime                                                                                                                                                                                       | 42   |

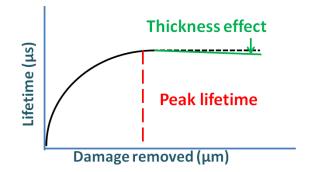

| 3.15 | Illustration of ideal curve of change in $\tau_{eff}$ as a function of damage layer thickness removed from each surface of the wafer                                                                                                                           | 43   |

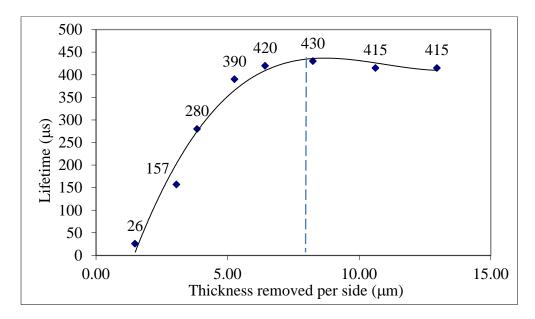

| 3.16 | Lifetime as a function of thickness removed from one side of a DWC wafer (Dashed line representing the damage depth of approximately $8.25 \mu m$ )                                                                                                            | 44   |

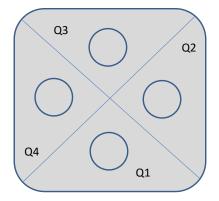

| 4.1  | Illustration of sample preparation method for the damage depth evaluation, and location of minority carrier lifetime measurement region (marked in circles)                                                                                                    | 46   |

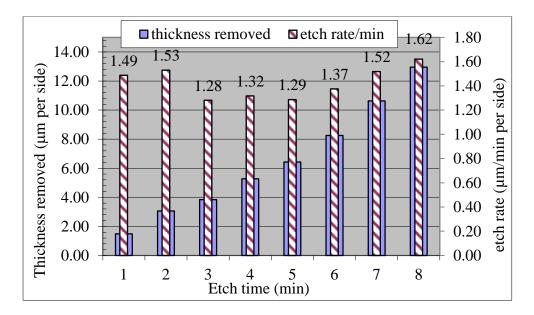

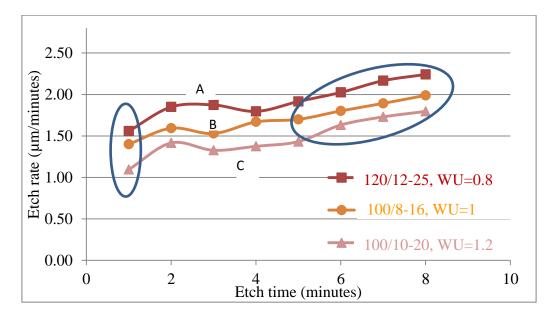

| 4.2  | Bar chart representation of sample thickness removed and etch rates vs etch time                                                                                                                                                                               | 47   |

| 4.3  | Etch rate as a function of etch time for three batches of DWC wafers cut<br>under different sawing conditions                                                                                                                                                  | 48   |

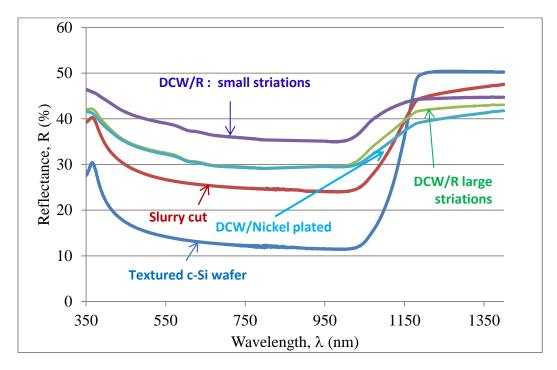

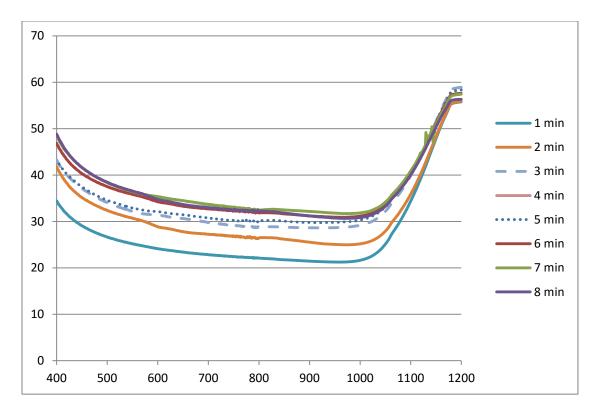

| 4.4  | Reflectance spectra of crystalline silicon wafers cut under different conditions                                                                                                                                                                               | 49   |

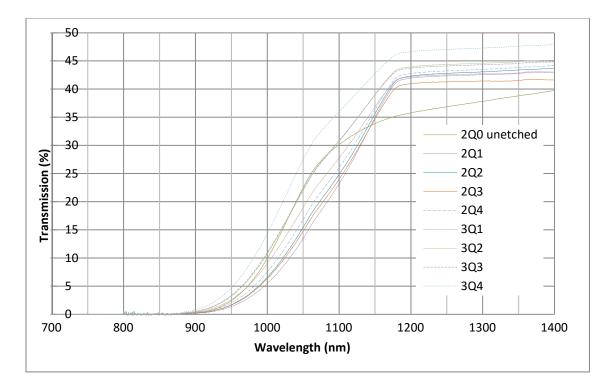

| 4.5  | Reflectance spectra of DWC cut crystalline silicon wafer etched for different times                                                                                                                                                                            | 50   |

| 4.6  | Reflectance spectra of a thin (145µm) DWC cut crystalline silicon wafer<br>etched for different times (from 2Q1 to 3Q4 in 0.5 min increments in etch<br>time, removing approximately 1µm at a time)                                                            | 51   |

| Figu | re P                                                                                                                                                                                                                                       | age |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

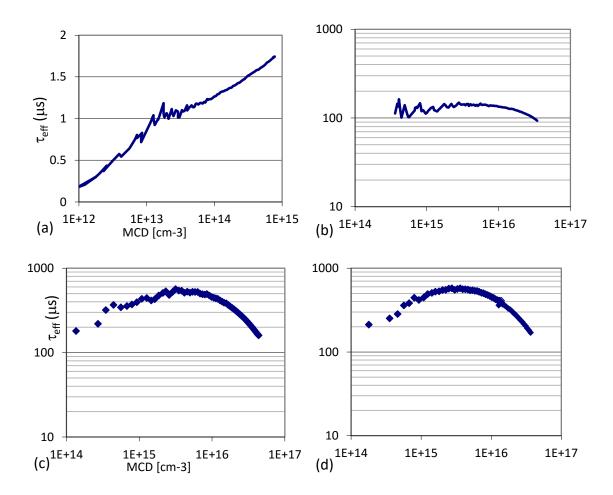

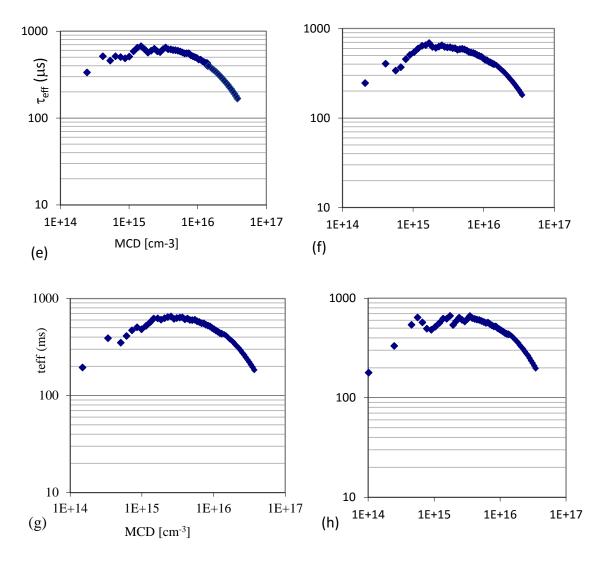

| 4.7  | Minority carrier lifetime measurements performed on sequentially etched DWC cut crystalline silicon wafer quarters. Samples are etched for different times (a) 0.5 min (b) 1 min, (c) 1.5 min, (d) 2 min (Continued)                       | 52  |

| 4.7  | (Continued) Minority carrier lifetime measurements performed on sequentially etched DWC cut crystalline silicon wafer quarters. Samples are etched for different times (e) 3 min, (f) 4 min, (g) 5 min and (h) 6 min                       | 53  |

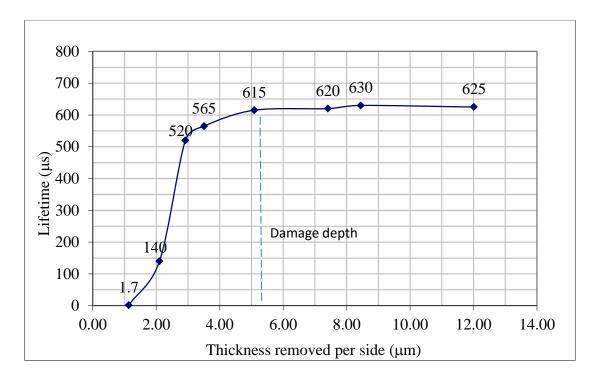

| 4.8  | Minority carrier lifetime vs thickness removed plot of DWC cut crystalline silicon wafer quarters. Samples are etched for different times (etch times mentioned in the caption of Figure 4.7 )                                             | 54  |

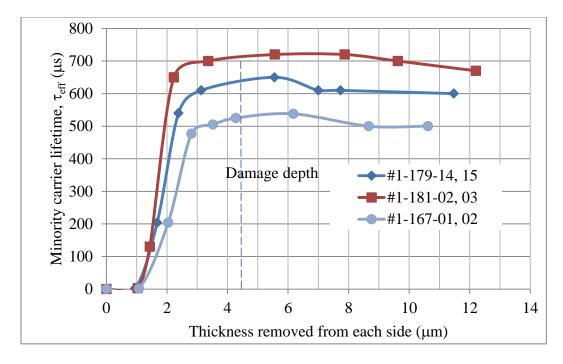

| 4.9  | Minority carrier lifetime vs thickness removed plot of DWC cut crystalline silicon wafer quarters from three different ingots (#179, #181, and #167). Samples are etched for different times (etch times mentioned in Figure 4.7 caption). | 55  |

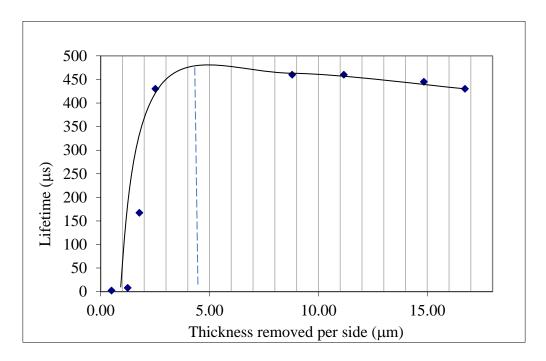

| 4.10 | Lifetime vs thickness removed plot of DWC cut wafer wire/grit size (80/6-12 µm).                                                                                                                                                           | 55  |

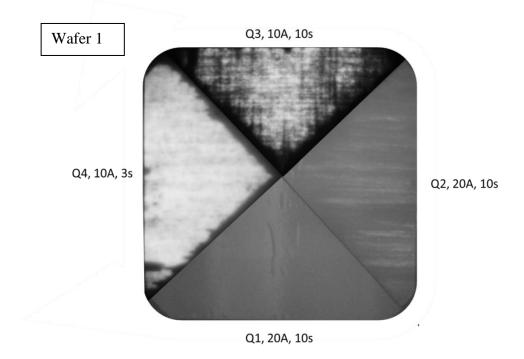

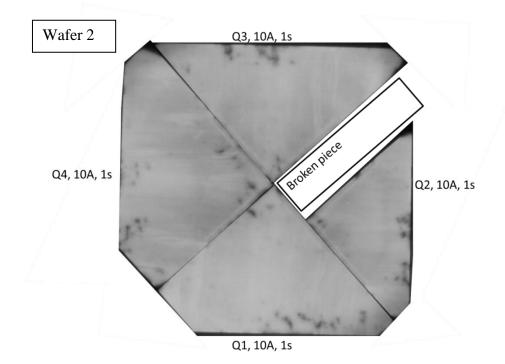

| 4.11 | PL images of wafer quarters etched in one minute incremental time steps (for 1, 2, 3 and 4 minutes) (in the order Q1 to Q4) (Current through laser diodes is mentioned in Amps and exposure in seconds)                                    | 56  |

| 4.12 | PL images of wafer quarters etched in one minute incremental time steps (for 5, 6, 7, and 8 minutes) (in the order Q1 to Q4) (Current through laser diodes is mentioned in Amps and exposure in seconds)                                   | 57  |

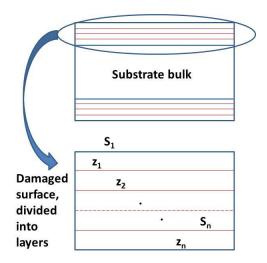

| 5.1  | Illustration of layered model of the surface damage on a silicon wafer                                                                                                                                                                     | 60  |

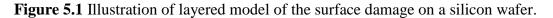

| 5.2  | An illustration of a silicon wafer sample illuminated from one side                                                                                                                                                                        | 61  |

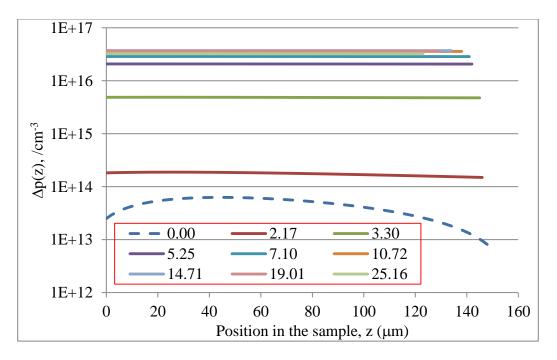

| 5.3  | Change in excess carrier density as a function of etch depth and location in the sample                                                                                                                                                    | 64  |

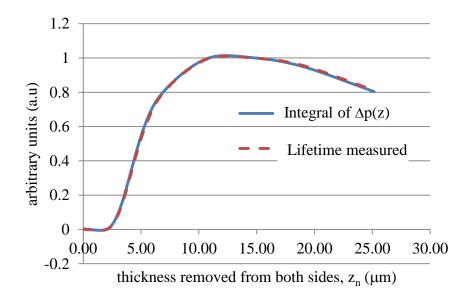

| 5.4  | Normalized excess carrier density and lifetime plot as a function of thickness removed from each surface (n type 150 µm thick wafer)                                                                                                       | 65  |

| Figu | ire I                                                                                                                                                                                                                                                                             | Page |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

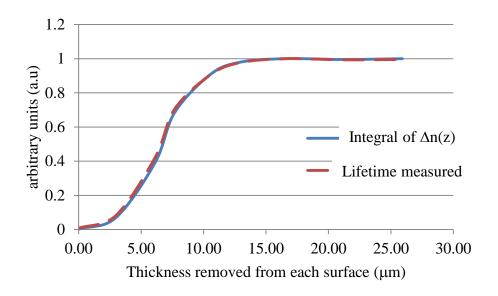

| 5.5  | Normalized excess carrier density and lifetime plot as a function of thickness removed from each surface (p type 200 µm thick wafer)                                                                                                                                              | 66   |

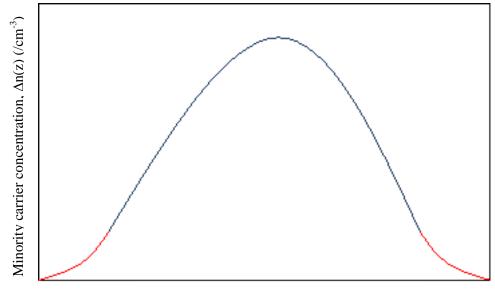

| 5.6  | Illustration of Excess carrier density as a function of depth in silicon wafer<br>for a three layer model (A bulk layer and a damage layer on each side of it),<br>red colored parts of the curve illustrate the minority carrier concentration<br>profiles in the damaged layers | 68   |

# LIST OF SYMBOLS

| α  | Absorption coefficient             |

|----|------------------------------------|

| τ  | Minority carrier lifetime          |

| Φ  | Light flux                         |

| Ω  | Resistivity                        |

| λ  | Wavelength of light                |

| ©  | Copyright                          |

| Å  | Angstrom(10 <sup>-10</sup> meters) |

| R  | Reflectance                        |

| °C | Degrees Celsius                    |

| Т  | Transmittance                      |

| D  | Diffusion coefficient              |

| S  | Surface recombination velocity     |

# LIST OF ABBREVIATIONS

| Si  | Silicon                          |

|-----|----------------------------------|

| Cz  | Czochralski                      |

| FZ  | Float zone                       |

| SiC | Silicon Carbide                  |

| ID  | Inner diameter                   |

| OD  | Outer diameter                   |

| SWC | Slurry wire cutting              |

| DWC | Diamond wire cutting             |

| TTV | Total thickness variation        |

| PCD | Photoconductance decay           |

| μW  | Microwave                        |

| μS  | Microseconds                     |

| SEM | Scanning electron microscopy     |

| TEM | Transmission electron microscopy |

| XRD | X-ray diffraction                |

| SRV | Surface recombination velocity   |

#### **CHAPTER 1**

#### **INTRODUCTION**

Silicon is the most widely used material in both photovoltaic and semiconductor industries. Silicon is grown in a variety of methods and, currently Czochralski (Cz) and Float-Zone (FZ) are the predominantly used crystal pulling techniques utilized by the industry to grow crystalline silicon ingots. Sawing is a process step required to cut a silicon ingot or a boule into bricks/wafers, and these wafers will then be used for device fabrication after a multitude of preparation steps. Sawing itself constitutes a large amount of material loss. Because silicon is a hard and brittle material, any cutting/sawing action results in a surface and subsurface damage that must be removed before a device is fabricated using it, resulting in additional material loss. This combined material loss due to cutting (kerf loss) and wafer preparation (damage removal) constitutes about half of the Si ingot. Hence, it is important to minimize the material loss, and the added costs associated with sawing and wafer preparation.

In this Chapter, an overview of silicon ingot sawing is presented. Subsequently, surface damage caused by sawing, including a detailed account of the types of surface damage and their origins are discussed. Finally, the need for an accurate evaluation of surface damage is elucidated.

#### 1.1 Silicon Sawing

Many ingot sawing methods viz. outside diameter (OD) cutting, inside diameter (ID) cutting, and multi-wire sawing have evolved over the last 50 years with the objectives of

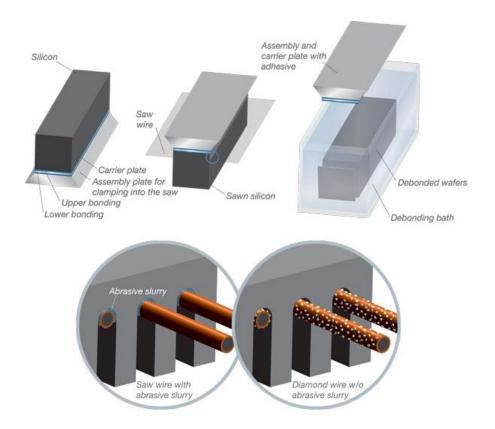

minimizing the kerf loss, making thinner wafers of uniform thickness, and minimizing the sub-surface damage (Herring, 1976; Kachajian, 1972; Lane, 1985; Tonshoff et al., 1997; Pauli, 2005). Although, multi-wire sawing methods are slower (half a day per cutting cycle), they offer lower kerf loss and high throughput because of their ability to cut larger ingot lengths (Wu, PhD thesis, 2012). Slurry wire cutting (SWC), a multi-wire sawing method uses steel wire and silicon carbide (SiC) particles in oil or ethylene glycol solution (most often referred to as slurry) as the abrasive medium. It has been the industry standard for silicon ingot sawing for more than a decade now (Moller, 2006), (Liedke et al., 2011). However, a newer technique consisting of diamond wire cutting (DWC) (using diamond abrasive particles (grit) patched to a copper alloy or resin on a metal wire), is garnering interest in both research community and industry, particularly for photovoltaic ingot slicing (X Yu et al., 2012). Figure 1.1 is an illustration of the slurry wire cutting and diamond wire cutting processes.

This new diamond impregnated wire is deemed to provide high throughput with a reasonable total thickness variation (TTV), low surface roughness, low kerf, and comparable or low surface damage values to that of slurry wire cutting. In this thesis work, focus will be on the determination of in-depth damage caused on crystalline silicon wafers cut by multi-wire sawing methods only.

The sawing and the wafer preparation must be considered together. For example, aggressive cutting to increase the throughput can increase the kerf loss as well as the surface damage. On the other hand, under etching/texturing/polishing performed in an attempt to reduce kerf may leave some residual damage on the device surface, which can

lead to a high surface recombination, defect generation during high temperature processing and concomitant degradation in device performance.

Figure 1.1 Illustrations of SWC and DWC sawing techniques.

Source: <u>http://www.delo-adhesives.com/typo3temp/fl\_realurl\_image/photovoltaik-waefersaegen-en-ph.jpg</u>, retrieved, June 20, 2015.

#### 1.2 Surface and In-depth Damage Caused by Sawing

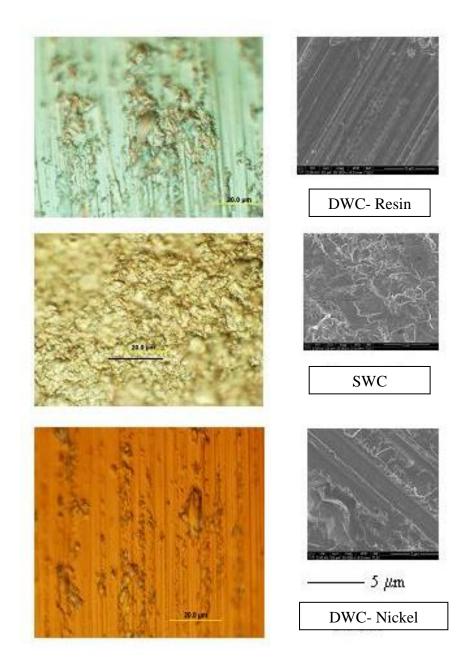

Wire sawing (both SWC and DWC) produces surface damage and in-depth damage (which is several microns deep) on the wafers. The chipping or "tearing away" of small pieces of silicon from the path of the saw wire/grit is a micro-cleavage process. This can be seen in optical and SEM images of the as-sawn surfaces shown in Figure 1.2. This damage would be responsible for the wafer breakage because of micro cracks induced,

uneven wafer surface and residual damage if the wafer is not properly etched [Wu et al., 2012].

**Figure 1.2** Optical and SEM images showing lower and higher magnification images of the saw patterns/marks in DWC-Resin cut, slurry cut, and DWC-Nickel cut wafers (Sopori et al., 2013).

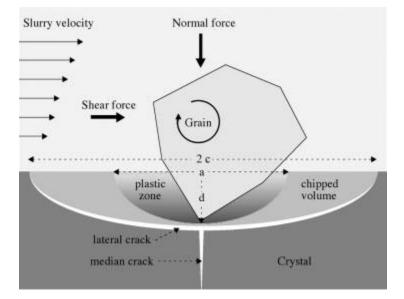

In SWC mechanism, the surface roughness  $(R_z)$  is approximately equal to the indentation depth (d) of the grains (or grit) and the extension of the damage zone equals the mean length of the crack (c) [defined in Equation 1.1] generated by that grain and is shown in Figure 1.3 (Moller et al., 2004).

$$c = (\gamma \beta I_0 d/K_{IC})^{2/3}$$

(1.1)

**Figure 1.3** Illustration of a single grain indentation in silicon, also showing various crack types (Moller et al , 2004).

There are several other parameters viz. wire velocity/feed rate (Wurzner et al., 2015), cutting rate/down feed rate, force applied on the ingot/brick or the tension in wire, wire/grit usage (Bidiville, PhD Thesis, 2010), and wire reciprocation (back and forth motion used in multi-wire cutting methods) which determine the final damage depth and distribution in a wafer.

Silicon wafer manufacturers are rapidly moving from slurry wire cutting method to a more economical and environmental friendly diamond wire cutting for ingot slicing. This brings a new set of issues to deal with viz. surface morphology (on contrary, very uniform for slurry cut), different depths and distributions of damage. However, newer etching methodologies can help resolve some of these issues. Recently, in 2014, it has been reported that the round run fringes caused by back and forth motion of the cutting wire can be completely removed from wafer surface by a new etching technique called vapor blast etching (Chen et al., 2014).

Surface damage caused by wire sawing on silicon wafers can be broadly categorized into two types.

(a) Superficial/surface damage, which can be classified into

- (i) Roughness

- (ii) Morphology (or phase transformation), and

(b) Sub-surface or in-depth damage, which can further be classified into

- (i) Micro-cracks,

- (ii) Periodic features (striations),

- (iii) Stress and Dislocations.

Origins of these damage varieties and their quantitative representations are described in the following Sections.

#### **1.2.1 Roughness**

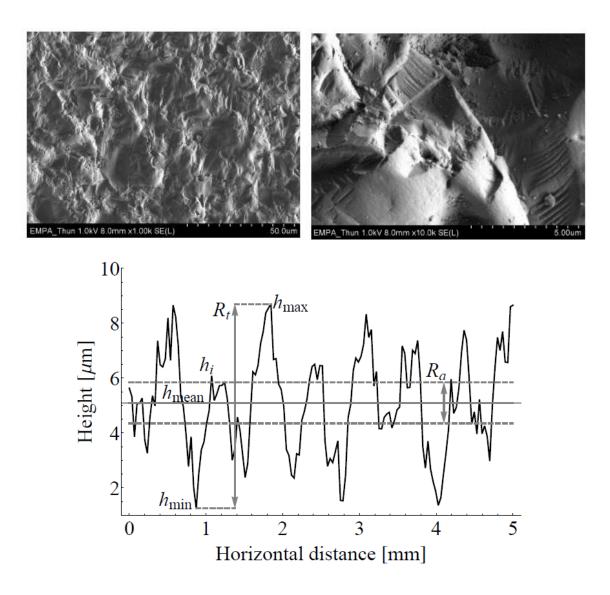

Surface roughness generation is an inherent macroscopic phenomenon associated with silicon ingot sawing. Figure 1.4 (a) and (b) depict the surface roughness caused by sawing. The average variation in height (i.e perpendicular to the large wafer plane)  $R_a$  [defined in Equation 1.2, (Wu, PhD thesis, 2012), and total roughness ( $R_t$ = peak to valley

difference, see Figure 1.4 (c)] are good measures of roughness and constant efforts are made by saw manufacturers to keep these values always under a few microns. The lower the  $R_a$  and  $R_t$  values, better the cutting method.

$$R_a = \frac{\sum_{i=1}^n |h_{i-}h_{mean}|}{n} \tag{1.2}$$

**Figure 1.4** SEM images showing surface roughness in (a) lower and (b) higher magnification. (c) Schematic of surface roughness and various terms associated (Wu, PhD thesis, 2012).

In multi-wire sawing methods, roughness generated depends on various parameters such as wire size, grit size, and cutting speed etc. Roughness is undesirable as it increases the amount of silicon material that needs to be removed before device fabrication. Measurements performed by Chen et al. (2010) on surface roughness of wafers sawn by SWC and DWC methods imply that the DWC is a better cutting mechanism because of less roughness it leaves on the wafer.

Studies by Wefringhaus et al. (2013) show that there is a direct correlation between the inhomogeneities in surface roughness of the as-cut wafers and the isotextured wafers. Wafer sawing process is attributed for this inhomogeneity. Roughness variation on isotextured wafers influences cell appearance (homogeneity of silicon nitride thickness / color), electrical performance will suffer from non-uniformities in reflection.

#### **1.2.2 Morphology or Phase Transformation**

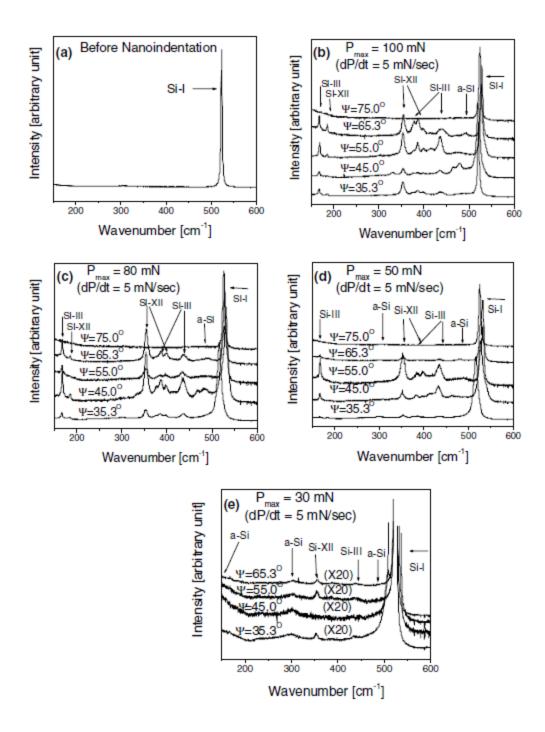

It is known that the local stress during multi-wire sawing (either SWC or DWC) cutting process can exceed few hundred MPa, and as a result of this large stress, silicon wafers are expected to experience lattice damage in the form of crystal defects such as dislocations as well as phase transformation (Yu et al., 2012; Bidiville, PhD thesis, 2010; Bidiville et al., 2009), similar to those observed in the case of micro-indentation (Domnich et al., 2002; Jian et al., 2010; Jang et al., 2005) or nano-scratching (Gassiloud, 2005) as seen in Figure 1.5.

**Figure 1.5** Raman spectra of crystalline silicon wafers surfaces indented with various indenters (of varying indenter angle  $\psi$ ) at various maximum loads (Jang et al., 2005).

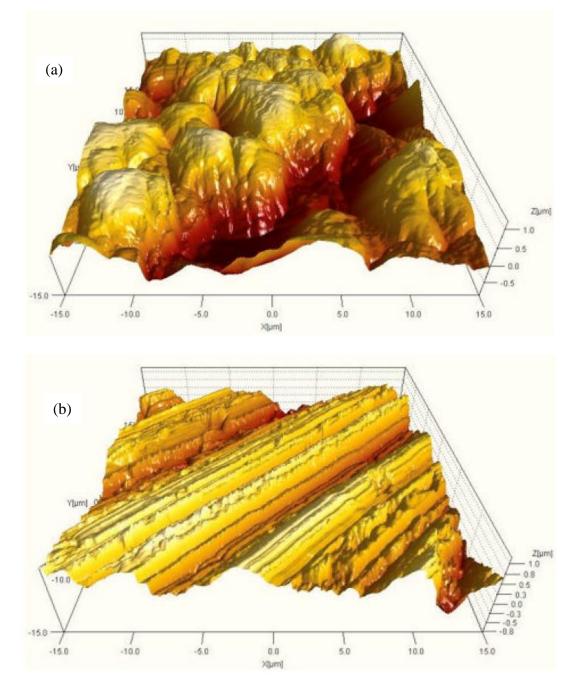

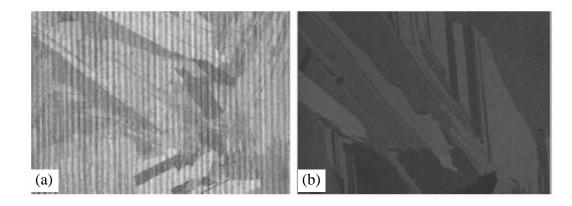

Since the SWC process is a three body abrasion process, it results in chipping of the wafer surface and, on the contrary, the two body abrasion process in DWC method results in grooving of the wafer surface and occasional chipping (Moller, 2004). Atomic Force Microscopy performed on the wafers cut using these two kinds of sawing methods illustrates the difference [see Figure 1.6].

Figure 1.6 AFM images of (a) SWC wafer and (b) DWC wafer (Holt et al., 2010).

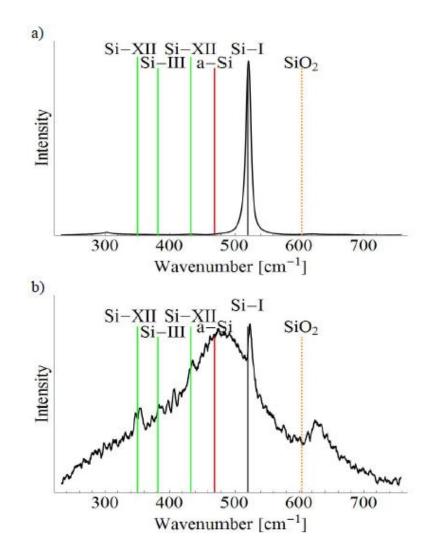

The chipped off region on the surface preserves its crystalline form whereas the abraded or grooved region undergoes phase transformation and the same can be confirmed using Raman spectroscopy. Figure 1.7 is a Raman spectrum obtained from two different regions (chipped off and abraded) on a silicon wafer cut using DWC method. A multitude of silicon phases are observed in the grooved region whereas the signal from chipped region is that of crystalline silicon.

**Figure 1.7** Raman spectra of (a) chipped-off region (b) a smooth groove (Bidiville et al., 2009).

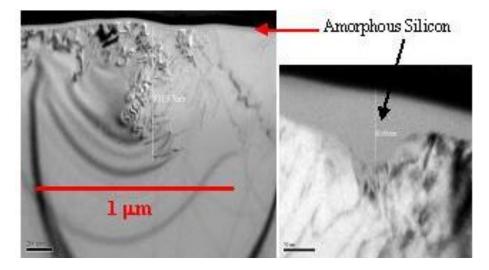

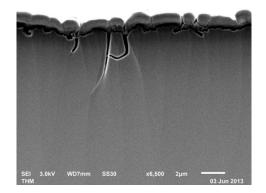

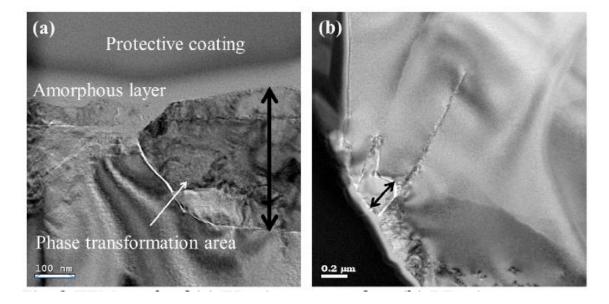

It is observed that commercial multi-wire sawing generates very shallow amorphous phase transformation damage (typically of the order of a few nm to a micro meter) and hence is not a significant contributor to the kerf loss. Figure 1.8 is a crosssectional TEM image that shows the local damage by diamond wire sawing. It shows two important features: (i) a thin (50 -100 nm deep) amorphous region at the surface, and (ii) dislocation networks that can be nearly  $1\mu m$  deep below the cutting surface. The amorphous phase is determined by a lack of diffraction pattern from this region, and occurs in all sawn samples. This amorphous phase present on the wafer surface can alter the etch parameters and in-turn change the way the wafers are etched (Holt et al., 2010).

**Figure 1.8** A cross-sectional TEM image of a DWC wafer sample showing formation of dislocation loops that are about 1  $\mu$ m deep and a layer of amorphous phase going to a depth of 0.8  $\mu$ m (Sopori et al., 2013).

## 1.2.3 Micro-Cracks

Micro-cracks generated during sawing are several microns deep. By improper handling, they propagate during processing and negatively affect the mechanical strength of the wafer and electrical parameters of the cell made using that wafer. Length of the microcracks and their position in the wafer are very critical in determining this effect. Figure 1.9 shows the positions of various cracks and their impact on cell parameters.

**Figure 1.9** (a) Illustrations of single cell modules with different crack positions intitated manually, (b) change in cell paramters with respect to the crack position (note- Crack locations are numbered and described in the same figure) (Grunow et al., 2005).

Attempts have been made to detect the micro-cracks, and evaluate the relationship between the crack-length, their density and mechanical strength of the wafer (Abdelhamid et al., 2014; Demant et al., 2014; Trautmann et al., 2011). Figure 1.10 is an SEM micrograph of micro-cracks generated in a DWC wafer during sawing.

**Figure 1.10** SEM image of an as-sawn silicon wafer sample showing micro-cracks propagating into the wafer bulk (scale  $2 \mu m$ ).

Source- https://www.ise.fraunhofer.de/en/business-areas/silicon-photovoltaics/researchtopics/feedstock-crystallization-and-wafering/projects/completed-projects/diasip-silicon-waferproduction-with-diamond-coated-sawing-wire, retrieved, June25, 2015.

It is known that micro-cracks generated at the edge and surface are more deleterious, and in order to prevent the wafers from breakage during cell processing, specific amount of silicon has to be etched away from each wafer surface (Perez et al., 2009) to ensure complete damage removal.

Although there exists a vast variety of experimental techniques to detect the micro-cracks in silicon wafer, limitations such as minimum crack length required, and interference with scratches inhibit their reliable use. A comparison of these techniques for micro-crack detection is given by Abdelhamid et al. (2014).

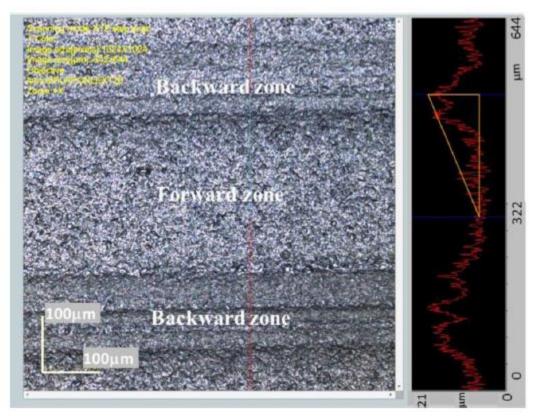

### **1.2.4 Periodic Features or Striations**

Striations are stripe like features which run across the wafer along the cutting wire direction and are the most commonly and immediately noticeable feature of DWC. Often there is a height variation of a few microns associated with these striations and these are spaced a few hundreds of microns apart. Figure 1.11 shows typical striation patterns observed on a mc-Si wafer cut using DWC method; a wafer cut with SWC method is also shown for comparison.

Figure 1.11 Optical scanner images of (a) DWC wire cut and (b) SWC wire cut mcsilicon wafers (Chen et al., 2014).

Although striations can be categorized as simply a surface damage problem, the amount of kerf loss associated with the etching process to get rid of these patterns can be significant and places them under in-depth damage category. Recent attempts in eliminating these patterns from the wafer surfaces using a new vapor blast etching technique are presented by Chen et al. (2014).

Origins of the striations are the back and forth motion of the cutting wire (wire reciprocation) during ingot cutting (Wu et al., 2014; Kray et al., 2006). Since more wire is used in the forward cutting direction compared to the backward direction in order to feed fresh wire into the system, there is a difference in depth of surface roughness and width of these zones [see Figure 1.12].

**Figure 1.12** 3D Laser confocal microscope map of as sawn wafer surface cut by reciprocating wire saw (note-feature height scan is shown next to the map in the same image for reference) (Wu et al., 2014).

## **1.2.5 Stress and Dislocations**

As was discussed earlier in Section 1.2.2, the process of sawing induces large amount of stress on the silicon surface. Excessive stress leads to generation of dislocations and deteriorates the sample quality. The use of X-rays to efficiently image various types of defects in thin semiconductor films and substrates has been reported long ago (Rozgonyi et al., 1976). This technique can be been used to analyze different types of dislocations, as well as for quantitative determination of stress in the material.

#### **1.3 Need for the In-depth Damage Evaluation**

While saw manufacturers and wafer suppliers can easily measure TTV and other physical parameters of wafers, there are no easy ways to measure the degree, depth and distribution of damage. Yet, this information is needed by sawing companies for optimizing throughput. This information is also needed by the solar cell manufacturers to ensure that all the damage is etched away during wafer preparation before solar cell processing. Silicon wafer standard thickness is reducing (currently from 180 to 140µm for commercial 156mm x 156mm wafers) and is expected to reach 100µm mark in the near future. Hence, characterization of the surface and in-depth saw damage in sawn silicon wafers and quantification of its distribution is very crucial.

#### **CHAPTER 2**

## LITERATURE REVIEW

A number of approaches are being used by researchers to evaluate the surface and indepth damage. One of the earliest methods developed for evaluation of polishing induced damage is based on the fact that damage present on a silicon wafer surface results in the formation of stacking faults (SF) when such a wafer is oxidized thermally. This phenomenon can be utilized for the manifestation of residual damage. A thin layer of silicon is etched away from the wafer surface (to get rid of the polishing induced surface damage); it is subjected to oxidation and inspected for the density of stacking faults (SF). This procedure is repeated until the SF density becomes negligible. The thickness removed per side corresponds to the depth of the polishing induced damage.

This repetitive oxidation and etching is a very tedious process. Therefore, the use of less labor and time intensive techniques such as XRD, SEM, laser scattering microscopy, resonance ultrasonic vibrations, acoustic microscopy, X-Ray topography, photoluminescence, surface photo voltage and angle polishing followed by defect etching have garnered more interest. In this chapter, a brief review of these measurement techniques and results obtained by various research groups using these methods are presented.

#### **2.1 Angle Polishing**

One of the most common approaches for measuring the depth of surface damage is to angle polish a small section of a wafer, which is then defect etched, followed by

17

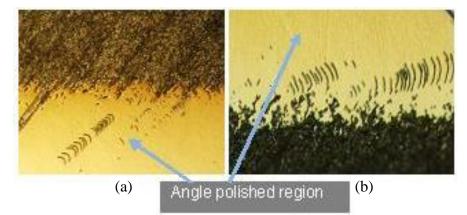

examination under an optical microscope to measure the depth of dislocations and microcracks below the surface. Figure 2.1 shows dislocation loops propagating into the bulk of the angle polished and defect etched samples taken from the wafers cut by SWC and DWC cutting methods.

**Figure 2.1** Optical microscope images of angle polished and defect etched (a) DWC and (b) SWC wafers (Sopori et al., 2013).

These images show a large defect concentration at the surface of the original assawn wafer. The defects show a striation pattern for the diamond cut and a 2-D pattern for the slurry cut wafer.

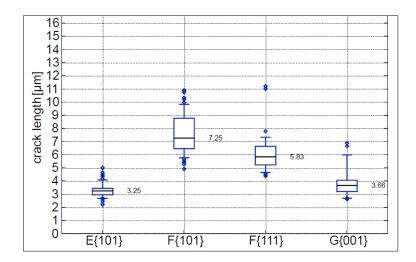

Crack depth analysis has been performed on different grains in angle polished mc-Si wafer samples by R Buchwald et al. (2013). Crack depths generated by sawing single crystal silicon wafers are compared with those in mc-Si wafers, crack depths are significantly lower in single crystal silicon. R Buchwald et al. (2013) found that the median of the maximum crack depth increases from the {100} plane to the {111} plane to the {101} plane [see Figure 2.2].

**Figure 2.2** Box plots of crack depth as a function of crystal orientation (Buchwald et al., 2013).

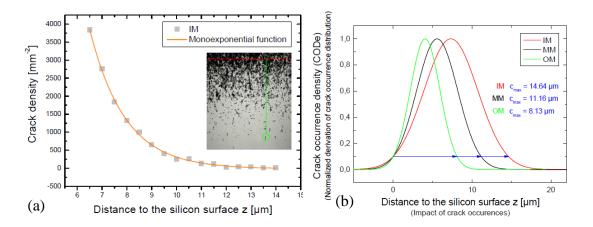

Crack counting and crack occurrence density evaluation at various locations on a wire sawn wafer is performed by Grun et al. (2012). From their studies, it is evident that the crack density decreases exponentially from the wafer surface. Also, the distribution of crack occurrence density shifts towards the surface from cutting wire entry point to the exit point on the wafer [Figure 2.3]. Similar findings were reported by Wagner et al. (2010).

**Figure 2.3** (a) Sub-surface crack density distribution at a given area on wafer surface, (b) Distribution of crack density occurrence compared at three different locations on a given wafer surface (IM= wire entry point, MM= center of the wafer, OM= wire exit point,  $c_{max}$ =critical subsurface damage depth) (Grun et al., 2012).

All these procedures are quite tedious and the information generated is only from a small region. However, if the surface roughness is large, it becomes increasingly difficult to demarcate the original and the angle polished surfaces, reducing the accuracy of these techniques.

## 2.2 Electron Microscopy

Electron microscopy techniques yield reliable information but the information obtained is at the microscopic level. These methods are implemented in estimating the subsurface damage induced by grinding and polishing (Zarudi et al., 1996; Kang et al., 2005; Mchedlidze et al., 1995). DWC wire method employs multiple grit binders. Tsai et al. (2013) reported that a wire with resin-binder generates a thinner amorphous phase compared to the electroplated metal binder as seen in Figure 2.4. Again these measurements are very local and the results obtained cannot be generalized for the entire wafer surface.

**Figure 2.4** TEM micrographs of as-sawn DWC wafer surfaces cut with diamond grit impregnated in (a) electroplated grit binder, (b) Resin grit binder (Tsai et al., 2013).

Kim et al. (2005), in their experimental studies, reported that there is a critical value for the damage depth created on wafer surfaces. Above this critical value of the damage depth, it generates dislocation loops upon oxidation of the as-sawn wafer surface and wire sawing comes under this category. However, the same material with lower critical damage depth value (lapped or silica blasted surfaces) generates stacking faults upon oxidation. These features can be visualized in SEM images obtained from two different wafer surfaces etched in Wright solution for 5 min [Figure 2.5].

**Figure 2.5** SEM micrographs of oxidized, etched wafer surfaces showing (a) Dislocation loops generated because of heavier mechanical damage imparted by the wire sawing, (b) Stacking faults generated because of lighter mechanical damage induced by the lapping process (Kim et al., 2005).

Scanning Electron Acoustic Microscopy (SEAM), a well-established technique for depth discrimination of multilevel integrated circuits is used in characterizing the defects in wire sawn silicon wafers after saw damage etch (Meng et al., 2013). But more studies are required on this topic to confirm that this can be a reliable method.

#### **2.3 Photoluminescence**

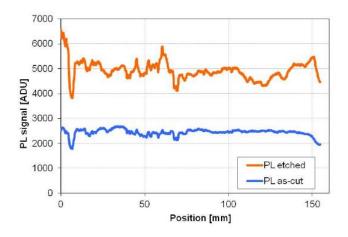

During the past decades, efforts have been made by researchers to utilize the method of photoluminescence (PL) for evaluation of silicon material quality. In-line qualitative analysis of damaged wafers is reported by Korsos et al. (2012). In their approach, photoluminescence images are obtained from as-cut and damage etched wafer surfaces. PL intensity line scans are obtained front these images for comparison. Figure 2.6 shows the increase in PL signal for the etched wafer.

**Figure 2.6** Photoluminescence line scans across the 156mm x 156mm wafer surface (Korsos et al., 2012).

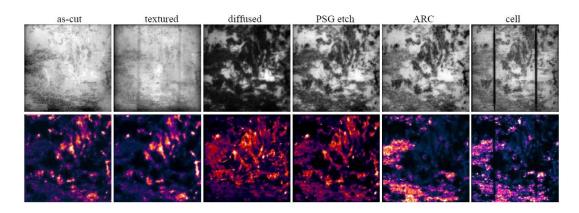

Attempts are made to measure the sub-surface damage quantitatively using photoluminescence (PL). This approach is limited by the strict temperature dependence of the PL technique. A comparison of various techniques, including photoluminescence, for subsurface damage evaluation is given by Lu et al. (2007). Figure 2.7 shows qualitative comparison of band to band and defect-band images obtained from multiple mc-Si sister (sequential) wafers after each cell fabrication step. Image correlation of a starting wafer to the final cell would ideally provide information for predicting the performance of the wafers from that same ingot/location before the wafers are processed.

**Figure 2.7** Band-to-band (top row) and defect band (bottom row) PL images of sister wafers after each cell fabrication step (Johnston et al., 2012).

## 2.4 Lasers

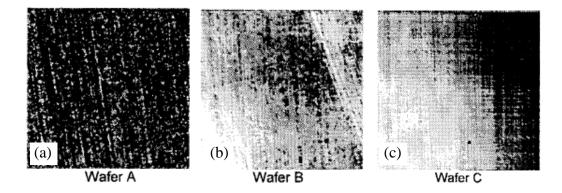

Lasers are used by many researchers in multiple ways to evaluate subsurface damage. Zhang et al. (2002) used the concept of laser scattering to generate 2D scatter images of the subsurface damage. Laser scattering has the potential to scan the whole wafer within tens of minutes, and detect the deepest damage in the whole wafer. This is a big advantage over other methods (such as cross-sectional microscopy) that can only reveal SSD information at localized areas on the wafer. But the information generated (SUM-IMAGES) by this technique is only qualitative as seen in Figure 2.8.

**Figure 2.8** Raman laser scattering images of silicon wafers of same final thickness but with different sub-surface damage conditions, (a) #320 diamond grit, coarse grinding damage (wafer A), and #2000 diamond grit, fine grinding damage removal of (b) 10 $\mu$ m, and (c) 30 $\mu$ m (Zhang et al., 2002).

A A Karabutov et al. (2014) used the concept of laser ultrasonic method. They could estimate the damage depth using an empirical relation between subsurface damage depth and the ratio of amplitudes of compression and rarefaction phases of the laser induced ultrasound (LIU) signals [see Figure 2.9]. But the main disadvantage of this technique is, it has a minimum limit on the depth of the sub-surface damage it can detect (approximately 0.15 to 0.2  $\mu$ m).

**Figure 2.9** (a) Temporal profiles of laser induced ultrasonic signals in silicon wafers with varying SSD (#1-1.65 $\mu$ m, #2-1.89 $\mu$ m, #3-2.23 $\mu$ m), (b) Plot showing empirical relation between experimental (points) and ratio of amplitudes of compression and rarefaction phases of the LIU signal (Karabutov et al., 2014).

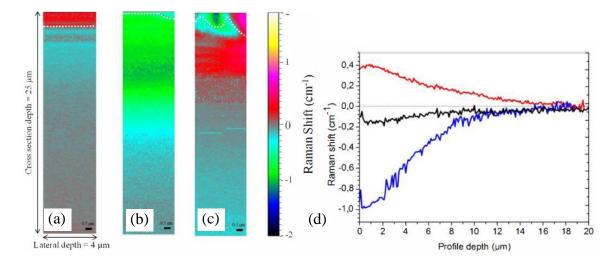

Recently, Photo Modulated Optical Reflectance (PMOR) measurements have been performed on SWC wafers by Bogdanowicz et al. (2012). Surface roughness was measured by the variation in average DC reflectance and the saw damage depth by the change in AC reflectance signal. The small measurement area ( $0.5\mu$ m) limits the use of this technique for macroscopic evaluation of the damage. Also, accurate determination of the damage depth is hindered by the interference of surface roughness in altering the AC signal. Lasers of varying wavelength are used for Raman spectroscopy analysis of crosssections of silicon samples by Radet et al. (2011) for sub-surface damage analysis. Chemically mechanically polished (CMP), chemically polished (CP) and as-sawn slurry cut wafers are analyzed for the estimation of damage depth. Figure 2.10 shows a 2D spectral image of these three wafer cross sections and depth profiles of Raman shift obtained from the map.

**Figure 2.10** 2D Raman spectra of (a) CMP, (b) CP, and (c) as-sawn SWC wafer crosssections, (d) Raman shift depth profiles extracted from the 2D spectra, (RED line- assawn SWC, BLACK line- CMP, BLUE line-CP) (Radet et al., 2011).

#### **2.5 Fracture Mechanics**

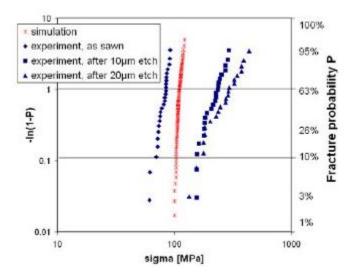

Micro-cracks cause a severe deterioration in the mechanical strength of the wafer. Depth and location of these micro-cracks determine the overall fracture strength. From the literary works mentioned in Section 1.2.3, we learned that the micro-cracks located near the surface are more effective in causing the deterioration in mechanical strength. Attempts are made by various researchers to relate micro-crack density, crack-length and position to the mechanical strength of the wafers by experimental (two-point, three-point, and four-point bending tests, ring-on-ring tests, angle polishing, and defect etching), and theoretical analysis (finite element analysis, and monte-carlo simulations) (Yang et al., 2013; Rupnowski et al., 2008; Saffar et al., 2014; Popovich et al., 2013; Jeong et al., 2000).

Figure 2.11 shows the comparison of theoretical wafer strength distribution (under a certain assumptions of crack density, shape, and lengths) with the experimental data obtained from as-sawn and damage etched silicon wafers.

**Figure 2.11** Theoretical and experimental strength distributions of as-sawn, and etched silicon wafers (Rupnowski et al., 2008).

This approach suffers from the requirement of extensive experimental analysis on numerous wafers for supplying reliable and sufficient information for theoretical calculations for accurate evaluation of damage depth.

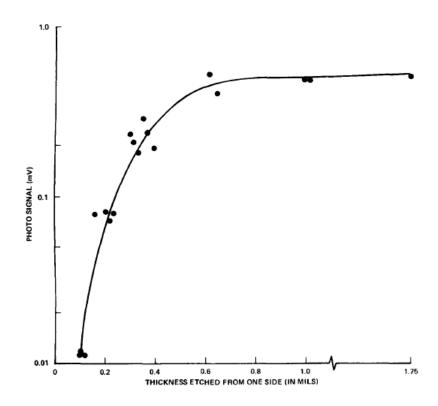

# **2.6 Electrical Characterization**

Surface photo voltage developed on a semiconductor wafer as a means to observe the polishing damage has been realized long ago (Sopori, 1980). Change in the amplitude of photo voltage signal is directly related to the damage removal and saturation in the signal

after subsequent chemical polishing or etching confirms the complete damage removal as seen in Figure 2.12.

**Figure 2.12** Change in surface photo voltage signal as a function of thickness removed from one side of the silicon wafer (Sopori, 1980).

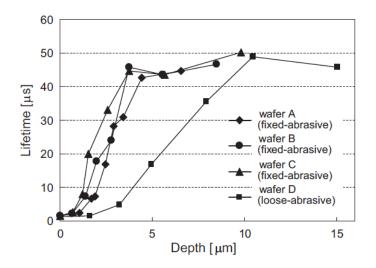

Minority carrier lifetime measurement is another technique which can reliably yield information about the material quality, surface passivation. These measurements are very sensitive to the surface and sub-surface damage. Watanabe et al. (2010) demonstrated the use of minority carrier lifetime measurements on sequentially etched polycrystalline silicon wafers for damage depth evaluation. This technique is based on measurement of the effective minority carrier lifetime ( $\tau_{eff}$ ) of the wafers after sequential etching of thin layers from the damaged surface. The measured  $\tau_{eff}$  increases as the more and more thickness is removed from the surface. The thickness-removed that yields the peak value of  $\tau_{eff}$  represents the damage depth. Figure 2.13 shows minority carrier

lifetime plots of as-sawn polycrystalline wafers etched in steps and the corresponding incremental lifetime recorded.

**Figure 2.13** Minority carrier lifetime measured vs depth of damage layer removed from each side of the silicon wafer (plots of various polycrystalline wafers cut using SWC and DWC methods are shown) (Watanabe et al., 2010).

This method of sequential etching and minority carrier lifetime measurement has many advantages. It can be used for the subsurface damage depth evaluation in crystalline silicon wafers cut by different wire sawing mechanisms. The damage distribution can be obtained theoretically in terms of recombination velocity and can be correlated to various parameters such as wire/grit size, wire usage etc. (Sopori et al., 2013; Sopori et al., 2014).

#### **CHAPTER 3**

## **EXPERIMENTAL METHODS AND TECHNIQUES**

Experimental methods for the evaluation of silicon surface and in-depth damage have been developed and optimized since the beginning of the silicon industry. Researchers are still trying to develop a more reliable means of measuring the saw damage. Various methods have been discussed in the previous chapter. Some of those techniques are implemented in the damage analysis on as-sawn wafers.

In this chapter, a brief description of the experimental techniques adopted for the damage depth analysis, variations in saw damage on wafers cut by different sawing methods, etch rate as a means of estimating the depth and degree of damage will be presented. Finally, a relatively novel mechanism of using minority carrier lifetime for quantitative determination of saw damage on crystalline silicon wafers will be introduced.

#### **3.1 Optical Microscopy**

Optical microscopy is a quick and easy method for examining the sample surface. It immediately reveals the topography of the surfaces for qualitative analysis of damaged wafer surface. In R&D, there is an array of optical microscopes available, depending on the technology. A Nomarski microscope is used and the samples under investigation are the as-sawn silicon wafers cut with DWC method. Silicon wafers sliced with various wire sizes with and different grit sizes are obtained from the commercial wafer manufacturers. These wafers are cleaved into pieces of manageable size (approx. 4cm x 4cm for

DEKTAK and 1cm x 1cm for angle polishing). At different locations on the sample surface, scribing is performed by a diamond scriber to identify the location before and after saw damage removal [Figure 3.1].

**Figure 3.1** Illustration of sample preparation method for optical microscopy, contact and optical profilometry. (Note- L shaped Scribing marks for reference, and dashed lines represent locations from where the Dektak scans are obtained. Colored squares are arbitrary locations chosen for optical microscopy).

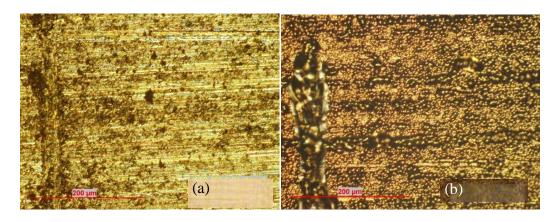

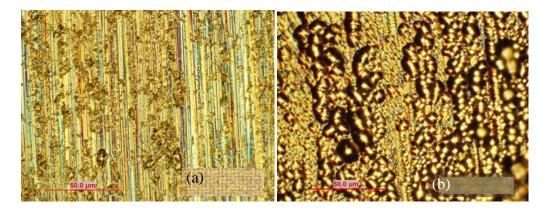

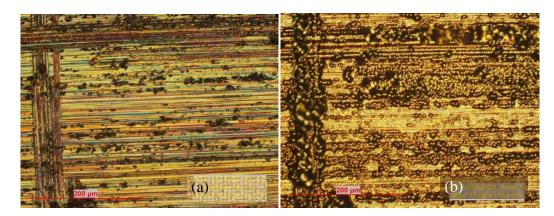

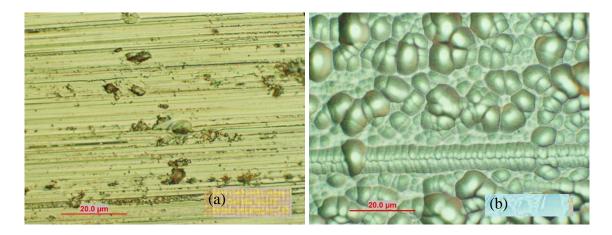

Samples are etched for 15 min in 1:1:5 :: HF:HNO<sub>3</sub>:CH<sub>3</sub>COOH (here after referred to as 115 solution) mixture to ensure the complete removal of the saw damage. Figure 3.2 (a) shows silicon sample with vague characteristic striation patterns of DWC cutting method. After etching for 15 minutes, the same location is observed under the microscope for striations, change in topography, and uniformity of etching [see Figure 3.2 (b)]. Samples in Figures 3.2 and 3.3 are sawn using thicker wire/larger grit (120µm/12-25µm) while the samples in Figure 3.4 are sawn using thinner wire/smaller grit (100µm/10-20µm). Images shown in Figure 3.5 are 50 times magnified images of the sample surfaces shown in Figure 3.4.

**Figure 3.2** Optical microscope images (at 10x magnification) of a DWC wafer (thick wire/grit) sample (a) before (or as-sawn surface), and (b) after damage removal etching in 115 solution for 15 min.

**Figure 3.3** Optical microscope images (at 20x magnification) of a DWC wafer (thick wire/grit) sample (a) before (or as-sawn surface), and (b) after damage removal etching in 115 solution for 15 min.

**Figure 3.4** Optical microscope images (at 10x magnification) of a DWC wafer (thin wire/grit) sample (a) before (or as-sawn surface), and (b) after damage removal etching in 115 solution for 15 min.

**Figure 3.5** Optical microscope images (at 50x magnification) of a DWC wafer (thin wire/grit) sample (a) before (or as-sawn surface), and (b) after damage removal etching in 115 solution for 15 min.

From the images shown in Figure 3.2 to Figure 3.4, following conclusions can be made: (i) The striation pattern generated during the DWC method causes non-uniformities in wafer surface roughness during the saw damage removal process. (ii) Thicker wire/grit size causes higher surface roughness. For estimating the variation in damage depth, further studies are required.

## **3.2 Optical Surface Profiling**

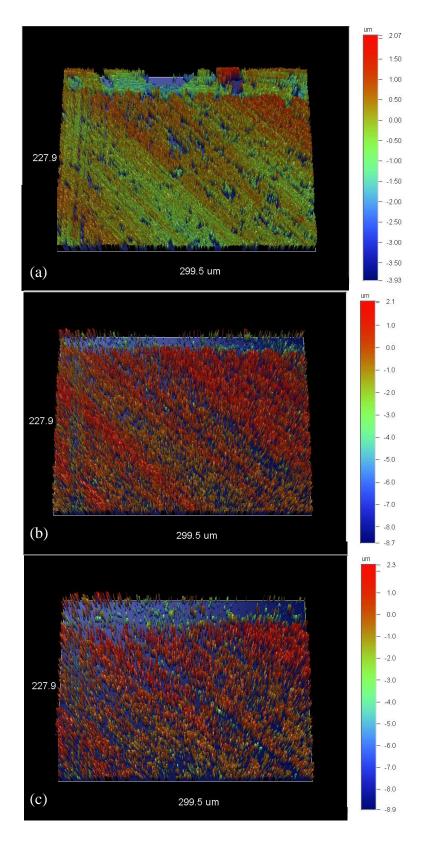

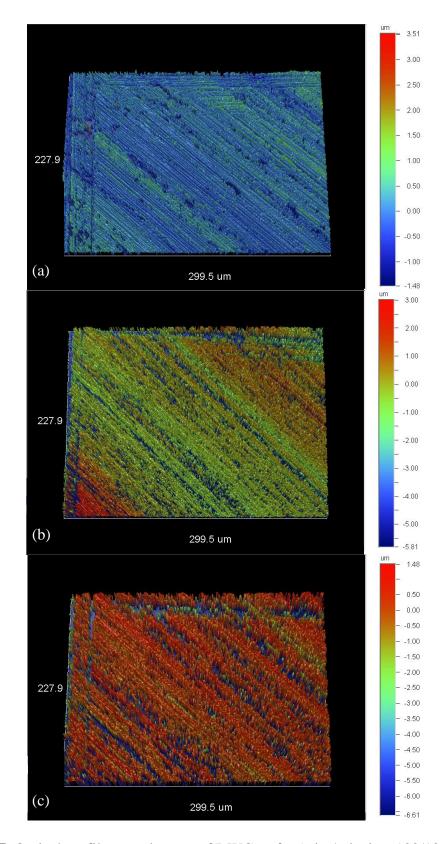

As-sawn silicon wafers cut using DWC method with different wire/grit sizes are chosen for examination. These samples have been scribed (L shaped marks) for identification of the regions of interest as mentioned in Section 3.1. Variation in surface roughness is evident from the interference microscopy measurements. Each sample is etched twice for 2 minutes each time and vertical scanning interference (VSI) images are obtained after each etching step using a WYKO NT1100 optical profiler system.

The original sample surface is shinier and after initial etching in 1:1:5 solution, the appearance of the sample surface becomes dull. After the second etch step, the surface becomes rough making it difficult to obtain interference pattern and in turn the feature height from the surface. Figure 3.6 shows these three surface conditions (a) assawn, (b) after 2 min etching and (c) after 4 min etching of DWC wire sawn wafers ccut with a thick wire/larger grit (120/12-25  $\mu$ m). The original as-sawn surface roughness value is 6 $\mu$ m. After the first etching, roughness increases to approximately 10.77 $\mu$ m and subsequent etchings make it more difficult to obtain an interference pattern from the surface and reliable data from the measurements. Figure 3.7 shows a similar set of samples prepared from DWC wafers cut with a thinner wire/grit size (100/10-20 $\mu$ m) compared to the earlier 120/12-25  $\mu$ m wire/grit size. Because of the lower surface roughness caused by the thinner wire and smaller grit, significant interference signal is still obtained from the wafer surfaces after second etch step. Debris from the sawing action may occasionally deposit over the sample surface and cause the absence of interference signal from the wafer surface as seen in of the Figure 3.6 (a).