# **Copyright Warning & Restrictions**

The copyright law of the United States (Title 17, United States Code) governs the making of photocopies or other reproductions of copyrighted material.

Under certain conditions specified in the law, libraries and archives are authorized to furnish a photocopy or other reproduction. One of these specified conditions is that the photocopy or reproduction is not to be "used for any purpose other than private study, scholarship, or research." If a, user makes a request for, or later uses, a photocopy or reproduction for purposes in excess of "fair use" that user may be liable for copyright infringement,

This institution reserves the right to refuse to accept a copying order if, in its judgment, fulfillment of the order would involve violation of copyright law.

Please Note: The author retains the copyright while the New Jersey Institute of Technology reserves the right to distribute this thesis or dissertation

Printing note: If you do not wish to print this page, then select "Pages from: first page # to: last page #" on the print dialog screen

The Van Houten library has removed some of the personal information and all signatures from the approval page and biographical sketches of theses and dissertations in order to protect the identity of NJIT graduates and faculty.

### **ABSTRACT**

# INSTRUCTION FUSION AND VECTOR PROCESSOR VIRTUALIZATION FOR HIGHER THROUGHPUT SIMULTANEOUS MULTITHREADED PROCESSORS

### by Yaojie Lu

The utilization wall, caused by the breakdown of threshold voltage scaling, hinders performance gains for new generation microprocessors. To alleviate its impact, an instruction fusion technique is first proposed for multiscalar and many-core processors. With instruction fusion, similar copies of an instruction to be run on multiple pipelines or cores are merged into a single copy for simultaneous execution. Instruction fusion applied to vector code enables the processor to idle early pipeline stages and instruction caches at various times during program implementation with minimum performance degradation, while reducing the program size and the required instruction memory bandwidth. Instruction fusion is applied to a MIPS-based dual-core that resembles an ideal multiscalar of degree two. Benchmarking using an FPGA prototype shows a 6-11% reduction in dynamic power dissipation as well as a 17-45% decrease in code size with frequent performance improvements due to higher instruction cache hit rates.

The second part of this dissertation deals with vector processors (VPs) which are commonly assigned exclusively to a single thread/core, and are not often performance and energy efficient due to mismatches with the vector needs of individual applications. An easy-to-implement VP virtualization technology is presented to improve the VP in terms of utilization and energy efficiency. The proposed VP virtualization technology, when applied, improves aggregate VP utilization by enabling simultaneous execution of multiple threads of similar or disparate vector lengths on a multithreaded VP. With a vector register

file (VRF) virtualization technique invented to dynamically allocate physical vector registers to threads, the virtualization approach improves programmer productivity by providing at run time a distinct physical register name space to each competing thread, thus eliminating the need to solve register name conflicts statically. The virtualization technique is applied to a multithreaded VP prototyped on an FPGA; it supports VP sharing as well as power gating for better energy efficiency. A throughput-driven scheduler is proposed to optimize the virtualized VP's utilization in dynamic environments where diverse threads are created randomly. Simulations of various low utilization benchmarks show that, with the proposed scheduler and power gating, the virtualized VP yields a larger than 3-fold speedup while the reduction in the total energy consumption approaches 40% compared to the same VP running in the single-threaded mode.

The third part of this dissertation focuses on combining the two aforementioned technologies to create an improved VP prototype that is fully virtualized to support thread fusion and dynamic lane-based power-gating (PG). The VP is capable of dynamically triggering thread fusion according to the availability of similar threads in the task queue. Once thread fusion is triggered, every vector instruction issued to the virtualized VP is interpreted as two similar instructions working in two independent virtual spaces, thus doubling the vector instruction issue rate. Based on an accurate power model of the VP prototype, two different policies are proposed to dynamically choose the optimal number of active VP lanes. With the combined effort of VP lane-based PG and thread fusion, compared to a conventional VP without the two proposed capabilities, benchmarking shows that the new prototype yields up to 33.8% energy reduction in addition to 40% runtime improvement, or up to 62.7% reduction in the product of energy and runtime.

# INSTRUCTION FUSION AND VECTOR PROCESSOR VIRTUALIZATION FOR HIGHER THROUGHPUT SIMULTANEOUS MULTITHREADED PROCESSORS

by Yaojie Lu

A Dissertation

Submitted to the Faculty of

New Jersey Institute of Technology

in Partial Fulfillment of the Requirements for the Degree of

Doctor of Philosophy in Electrical Engineering

Helen and John C. Hartmann Department of Electrical and Computer Engineering

Copyright © 2016 by Yaojie Lu

ALL RIGHTS RESERVED

### **APPROVAL PAGE**

# INSTRUCTION FUSION AND VECTOR PROCESSOR VIRTUALIZATION FOR HIGHER THROUGHPUT SIMULTANEOUS MULTITHREADED PROCESSORS

## Yaojie Lu

| Dr. Sotirios G. Ziavras, Dissertation Advisor                                 | Date |

|-------------------------------------------------------------------------------|------|

| Professor of Electrical and Computer Engineering,                             |      |

| Associate Provost for Graduate Studies and Dean of the Graduate Faculty, NJIT |      |

|                                                                               |      |

|                                                                               |      |

|                                                                               |      |

| Dr. Durgamadhab Misra, Committee Member                                       | Date |

| Professor of Electrical and Computer Engineering, NJIT                        |      |

|                                                                               |      |

|                                                                               |      |

|                                                                               |      |

|                                                                               |      |

| Dr. Edwin Hou, Committee Member                                               | Date |

| Professor of Electrical and Computer Engineering, NJIT                        |      |

|                                                                               |      |

|                                                                               |      |

|                                                                               |      |

|                                                                               |      |

| Dr. Roberto Rojas-Cessa, Committee Member                                     | Date |

| Associate Professor of Electrical and Computer Engineering, NJIT              |      |

|                                                                               |      |

|                                                                               |      |

|                                                                               |      |

|                                                                               |      |

| Dr. Alexandros V. Gerbessiotis, Committee Member                              | Date |

| Associate Professor of Computer Science, NJIT                                 |      |

### **BIOGRAPHICAL SKETCH**

**Author:** Yaojie Lu

**Degree:** Doctor of Philosophy

**Date:** May 2016

### **Undergraduate and Graduate Education:**

- Doctor of Philosophy in Electrical Engineering,

New Jersey Institute of Technology, Newark, NJ, 2016

- Master of Science in Electrical Engineering,

New Jersey Institute of Technology, Newark, NJ, 2012

- Bachelor of Science in Physics,

Fudan University, Shanghai, P. R. China, 2010

Major: Electrical Engineering

### **Presentations and Publications:**

- Y. Lu, S. Rooholamin and S.G. Ziavras, "Power-Performance Optimization of a Virtualized SMT Vector Processor via Thread Fusion and Lane Configuration," submitted to IEEE Computer Society Annual Symposium on VLSI, 2016.

- Y. Lu, S. Rooholamin and S.G. Ziavras, "Vector Coprocessor Virtualization for Simultaneous Multithreading," accepted for publication, ACM Transactions on Embedded Computing Systems, March 2016.

- Y. Lu and S.G. Ziavras, "Instruction Fusion for Multiscalar and Many-Core Processors," International Journal of Parallel Programming, Springer, 2015. DOI: 10.1007/s10766-015-0386-1.

- Y. Lu and S.G. Ziavras, "Instruction Fusion for Multiscalar and Many-Core Processors," 12th IFIP International Conference on Network and Parallel Computing (IFIP and ACM SIGMICRO), New York, NY, September 17-19, 2015.

### To my Family, with Love and Gratitude

在此,我希望用中文,把最特别最诚挚的谢意献给我的家人。感谢我的父母,陆禹 先生以及王瑛女士,这些年来对我无条件的爱护和支持。是你们含辛茹苦养育了我, 并用自己多年的积蓄帮我完成学业和梦想。你们是这个世界上最伟大的父亲和母亲。 我也要感谢我亲爱的太太,戴旭斐女士。是你这些年来不离不弃的陪伴,让我有勇 气和信心一直走到了今天。

#### **ACKNOWLEDGMENT**

In the first place, I would like to express my deepest gratitude to my adviser, Dr. Sotirios Ziavras, for being my mentor throughout my PhD research. As my advisor, he not only gave me great research related advice, but also inspired me to think independently and gave me the opportunity and confidence to pursue my own innovations. His extraordinary skills in academic writing and in depth knowledge in various fields really made the research process a wonderful learning experience. I wouldn't have learned and achieved this much without his time and patience.

I would like to thank Dr. Durga Misra for serving on my dissertation committee and also for his guidance and support during my master program. His VLSI courses have been of great value to me. I would also like to extend my sincere appreciation to Dr. Edwin Hou, Dr. Roberto Rojas-Cessa and Dr. Alexandros V. Gerbessiotis for serving as members of my dissertation committee. They were always willing to spend the time whenever I needed their help and advice.

Moreover, I am truly indebted and thankful to the ECE Department at NJIT. My work as PhD student would not have been possible without the teaching assistant award granted by the ECE Department.

Further thanks go to the staff of the office of global initiatives, the staff of graduate studies, and the staff of the ECE Department for their advice, help and support with administrative matters during my PhD studies and work as teaching assistant.

Additionally, I would like to thank my friends and colleagues, Seyedamin, Tim, Shiyang, Zhihao and Xiaolu for all the great and unforgettable moments we shared together during these years.

### TABLE OF CONTENTS

| Chapter |                                                       | Page |

|---------|-------------------------------------------------------|------|

| 1       | INTRODUCTION                                          | 1    |

|         | 1.1 The Utilization Wall                              | . 1  |

|         | 1.2 Inefficient VP Usage                              | . 2  |

|         | 1.3 Motivation and Objectives                         | . 5  |

| 2       | RELATED WORK                                          | 9    |

|         | 2.1 Work Related to Instruction Fusion                | . 9  |

|         | 2.2 Work Related to VP Virtualization                 | . 11 |

| 3       | IMPLEMENTATION AND EVALUATION OF INSTRUCTION FUSION   | 15   |

|         | 3.1 How Instruction Fusion Works                      | . 15 |

|         | 3.1.1 Instruction Similarity                          | 15   |

|         | 3.1.2 Instruction Fusion                              | 17   |

|         | 3.2 Processor Implementation for Fused Mode Execution | . 19 |

|         | 3.2.1 MIPS-I Like Multiscalar Architecture            | 19   |

|         | 3.2.2 FPGA Implementation                             | 22   |

|         | 3.3 Benchmarking for Instruction Fusion               | . 22 |

|         | 3.3.1 Evaluation Procedure                            | 22   |

|         | 3.3.2 Analysis of Results                             | 23   |

| 4       | VP VIRTUALIZATION                                     | 29   |

|         | 4.1 Virtual Register Name Space for Multithreading    | . 29 |

|         | 4.2 The VRF Structure                                 | . 30 |

# **TABLE OF CONTENTS** (Continued)

| Ch | apter                                                         | Page |

|----|---------------------------------------------------------------|------|

|    | 4.3 The Vector Register Management Module (RMM) and Algorithm | 31   |

|    | 4.4 Assigning/Releasing VRF Resources                         | 34   |

|    | 4.5 Fragmentation Analysis                                    | 35   |

|    | 4.6 Performance of the VRF Management Algorithm               | 36   |

| 5  | VIRTUALIZED VP ARCHITECTURE AND FPGA IMPLEMENTATION           | 39   |

|    | 5.1 The Host Subsystem Architecture                           | 39   |

|    | 5.2 The VP Architecture                                       | 42   |

|    | 5.2.1 VP ISA and Pipeline                                     | 42   |

|    | 5.2.2 VP-MB Interface                                         | 45   |

|    | 5.2.3 Hazard Detection Unit (HDU)                             | 46   |

|    | 5.2.4 Vector Lane Structure                                   | 47   |

|    | 5.3 FPGA Implementation                                       | 48   |

| 6  | BENCHMARKING AND HOMOGENEOUS SMT                              | 51   |

|    | 6.1 Benchmark Details                                         | 51   |

|    | 6.2 Homogeneous SMT Results                                   | 53   |

|    | 6.3 Comparison with Prior Works                               | 58   |

| 7  | SCHEDULING VECTOR THREADS                                     | 59   |

|    | 7.1 The Scheduling Algorithm                                  | 59   |

|    | 7.2 Queues of Fixed Length                                    | 61   |

|    | 7.3 Open System with Randomly Arriving Threads                | 63   |

# **TABLE OF CONTENTS** (Continued)

| Cha | apter                                                           | Page |

|-----|-----------------------------------------------------------------|------|

| 8   | VP ENERGY CONSUMPTION                                           | . 67 |

|     | 8.1 VP Dynamic Power                                            | 67   |

|     | 8.2 Total Energy Consumption                                    | 70   |

| 9   | VIRTUALIZED VP FOR THREAD FUSION AND DYNAMIC LANE CONFIGURATION | . 72 |

|     | 9.1 Virtualized VM Address Space                                | 72   |

|     | 9.2 SMT VP and Thread Fusion                                    | 75   |

|     | 9.3 System Architecture and FPGA Implementation                 | 79   |

|     | 9.4 Benchmarking                                                | 81   |

|     | 9.5 The Power Model                                             | 84   |

|     | 9.6 The Scheduling Policy                                       | 87   |

| 10  | A PIPELINED INTER-LANE NETWORK FOR EFFICIENT DATA SHUFFLE       | . 91 |

|     | 10.1 The Benefits of the Network                                | 91   |

|     | 10.2 Structure of the Shuffle Network                           | 92   |

|     | 10.3 The Decoder Virtualization Technique                       | 96   |

| 11  | CONCLUSIONS AND FUTURE WORK                                     | 99   |

|     | 11.1 Conclusions                                                | . 99 |

|     | 11.2 Future Work                                                | 102  |

| REI | FEDENCES                                                        | 104  |

## LIST OF TABLES

| Tab | ole State of the Control of the Cont | Page |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 3.1 | Performance/Power/Energy Benchmarking (Normal and Fused Execution)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 24   |

| 5.1 | ISA of the VP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 45   |

| 5.2 | Resource Consumption of the VP Prototype                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 50   |

| 6.1 | Matrix Multiplication Performance (Input Matrix Size: VL*VL, 1 Iteration per Core)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 54   |

| 6.2 | FIR Performance (Input Vector Size: VL, 1 Iteration per Core)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 54   |

| 6.3 | VDP Performance (Input Vector Size: VL, 1 Iteration per Core)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 55   |

| 6.4 | DCT Performance (Input: VL/8 Blocks of Size 8*8, 1 Iteration per Core)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 55   |

| 6.5 | RGB2YIQ Performance (Input: 1024 Pixels, 1 Iteration per Core)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 55   |

| 6.6 | Speedup Comparison with Prior Works                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 58   |

| 7.1 | Detailed Results for a Schedule with Pending Thread Queue Length of 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 62   |

| 7.2 | Detailed Results for a Schedule with Pending Thread Queue Length of 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 63   |

| 7.3 | Characteristics of Chosen Tasks for an Open System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 64   |

| 7.4 | Detailed Task Arrivals and Execution Time for $\lambda$ =0.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 65   |

| 7.5 | Detailed Task Arrivals and Execution Time for $\lambda$ =0.75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 65   |

| 7.6 | Detailed Task Arrivals and Execution Time for $\lambda=1$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 66   |

| 8.1 | Power and Energy Consumption for Benchmarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 69   |

| 9.1 | Resource Consumption and Utilization Percentage of the New VP Prototype                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 81   |

| 9.2 | Performance Profile Data for Unfused VP with Four Active Lanes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 82   |

| 9.3 | Performance Profile Data for Fused VP with Four Active Lanes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 82   |

| 9.4 | Performance Profile Data for Unfused VP with Two Active Lanes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 82   |

## LIST OF FIGURES

| Figu | ure                                                                                                                                                                                        | Page |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 3.1  | Example of MIPS-like code for loop unrolling and instruction fusion. a. Original loop. b. Loop after unrolling it twice. c. The unrolled loop of part b after pair-wise instruction fusion | •    |

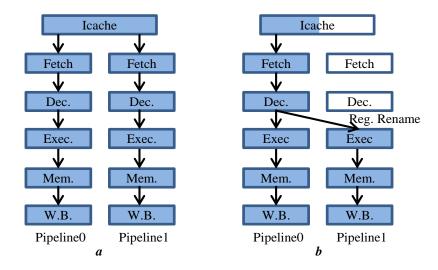

| 3.2  | Pipeline stage and Icache usage for a MIPS-like multiscalar processor with two complete pipelines or a dual-core processor. a. Normal execution mode. b. Fused execution mode.             |      |

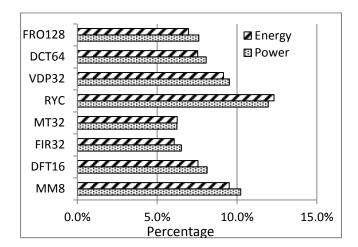

| 3.3  | Dynamic power/energy reduction                                                                                                                                                             | 24   |

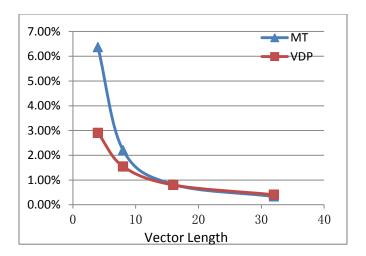

| 3.4  | Performance loss in the fused mode for various vector lengths.                                                                                                                             | 25   |

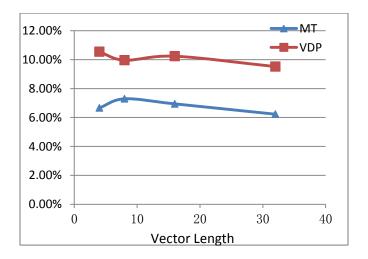

| 3.5  | Dynamic power reduction in the fused mode for various vector lengths                                                                                                                       | 25   |

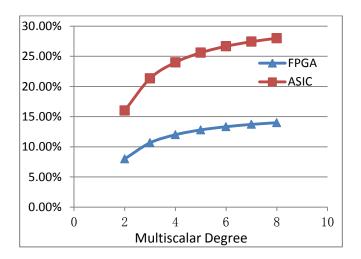

| 3.6  | Projection for FPGA and ASIC energy savings. Fused mode. Various multiscalar degrees.                                                                                                      |      |

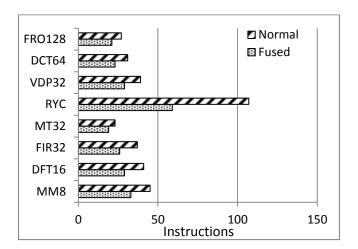

| 3.7  | Numbers of instructions in Icache                                                                                                                                                          | 28   |

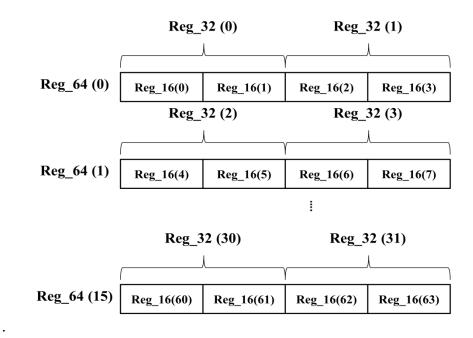

| 4.1  | VRF structure.                                                                                                                                                                             | 31   |

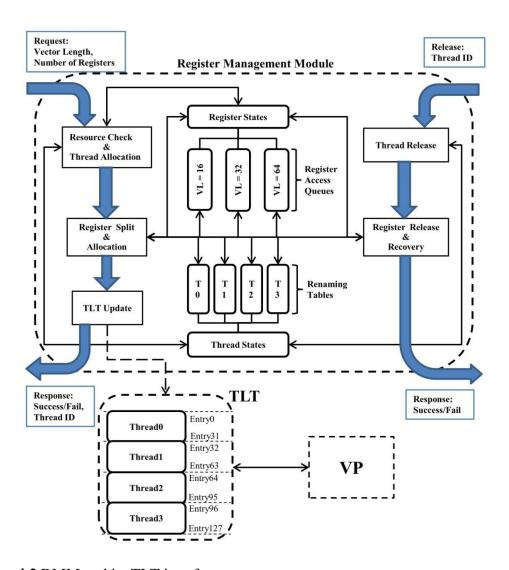

| 4.2  | RMM and its TLT interface.                                                                                                                                                                 | 32   |

| 4.3  | Data structures used to manage the VRF.                                                                                                                                                    | . 33 |

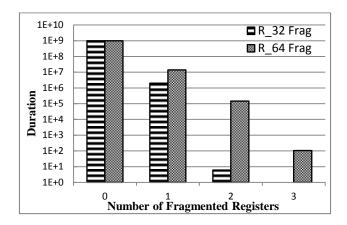

| 4.4  | Duration of fragmented registers for VL=32 and 64.                                                                                                                                         | 36   |

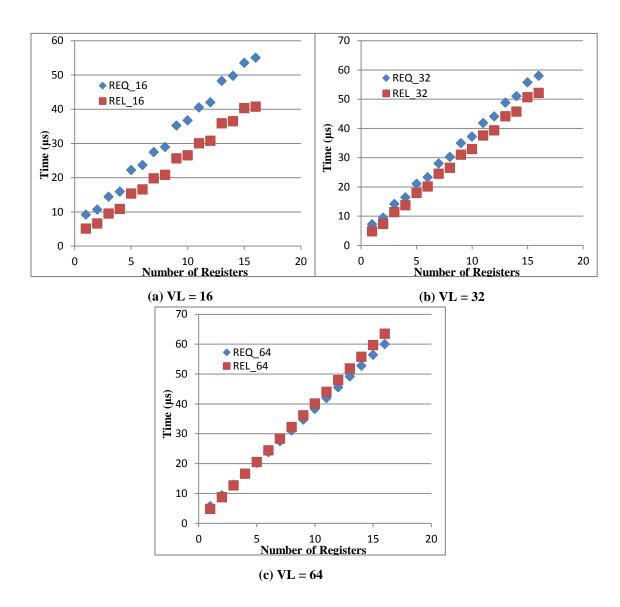

| 4.5  | Thread request and release functions runtimes under various VLs and number of registers.                                                                                                   |      |

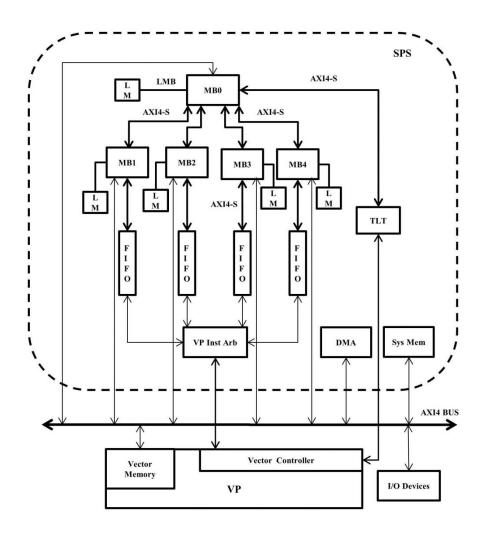

| 5.1  | Multicore architecture for VP sharing (Instr Arb: vector instruction arbitrator)                                                                                                           | 40   |

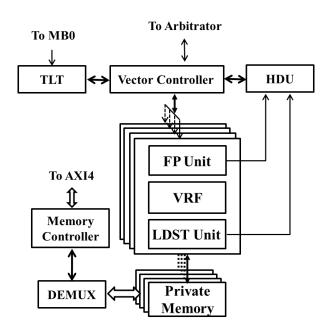

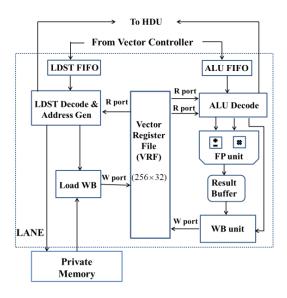

| 5.2  | Detailed architecture of the four-lane VP (FP: Floating-point).                                                                                                                            | 43   |

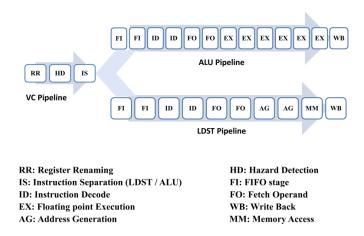

| 5.3  | Pipeline structure in the LDST and ALU data paths.                                                                                                                                         | 44   |

| 5.4  | Vector lane architecture.                                                                                                                                                                  | 48   |

| 6.1  | Macros to define vector instructions.                                                                                                                                                      | 52   |

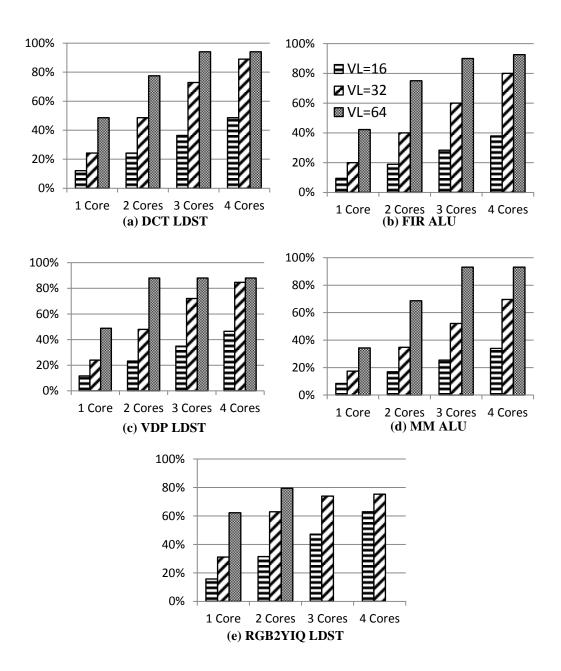

| 6.2  | Utilization of the LDST or ALU units for various benchmarks, VLs, and number of simultaneous threads.                                                                                      |      |

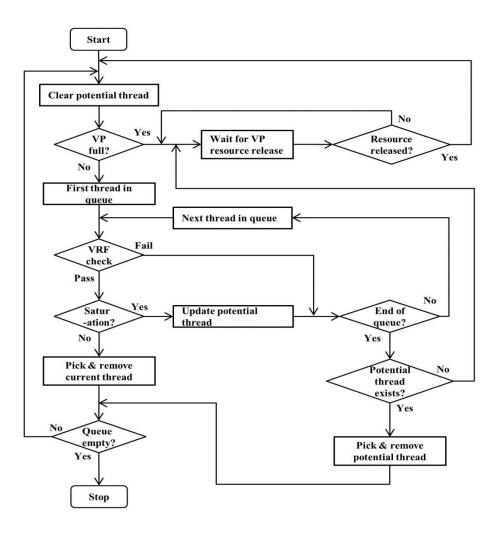

| 7.1  | Software flowchart of the throughput-driven scheduler.                                                                                                                                     | 60   |

# LIST OF FIGURES (Continued)

| Fig  | ure                                                                                                                                                                                    | Page |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

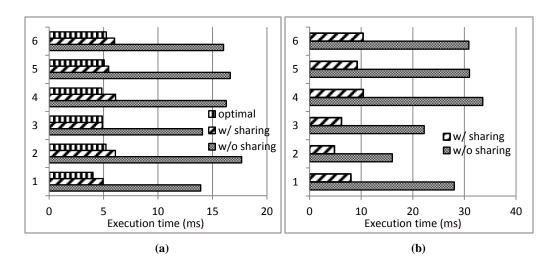

| 7.2  | Average execution time per schedule for pending thread queues of length; (a) 8, (b) 16                                                                                                 | 62   |

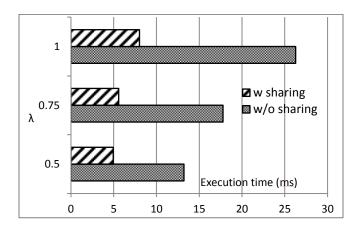

| 7.3  | The average of the total execution time for all threads scheduled in a time slice, with and without VP sharing, for $\lambda$ = 0.5, 0.75 and 1. (Time slice: 10ms.)                   | 64   |

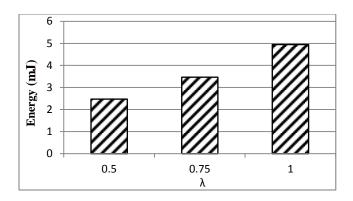

| 8.1  | Average total dynamic energy consumption per time slice for $\lambda$ =0.5, 0.75 and 1.                                                                                                | 70   |

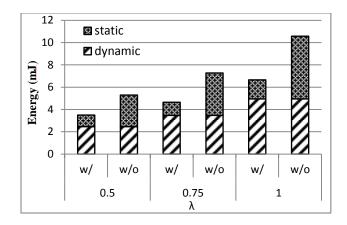

| 8.2  | Total energy consumption with (w/) and without (w/o) VP sharing, and with power gating, for $\lambda$ =0.5, 0.75 and 1                                                                 | 71   |

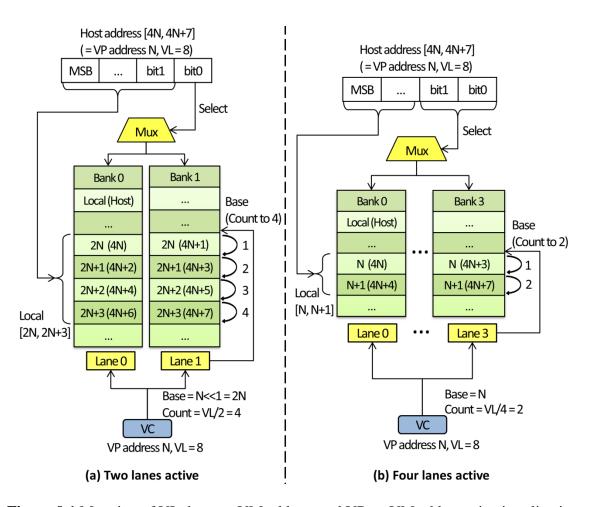

| 9.1  | Mapping of VL, host-to-VM address and VP-to-VM address via virtualization                                                                                                              | 74   |

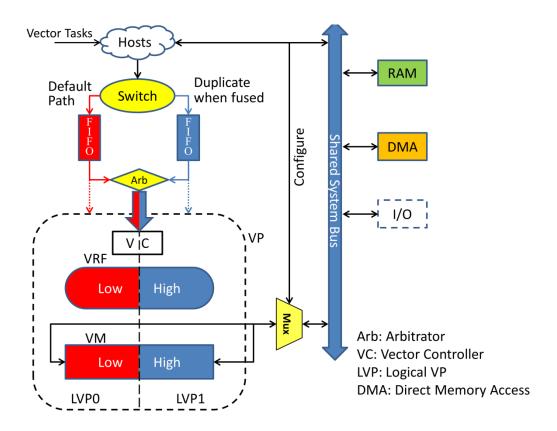

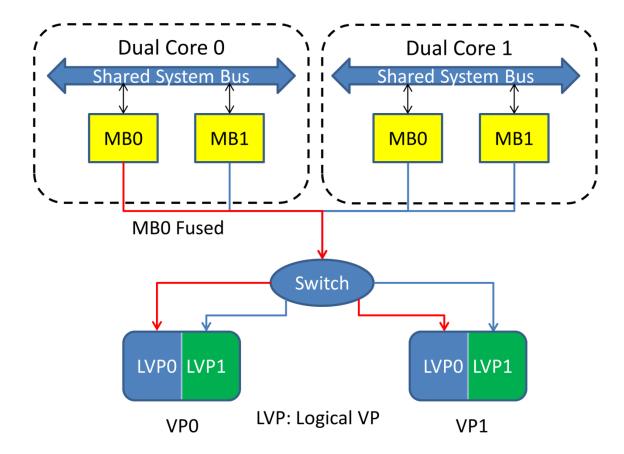

| 9.2  | System architecture of a fusion capable VP of degree two                                                                                                                               | 77   |

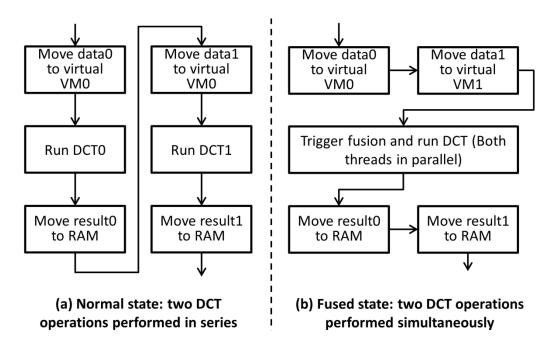

| 9.3  | Fusion of two DCT operations                                                                                                                                                           | 79   |

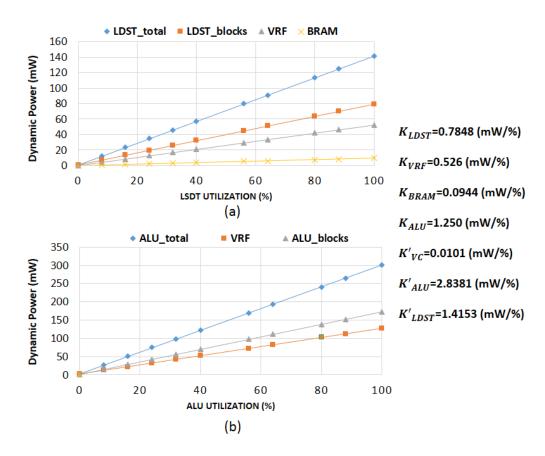

| 9.4  | Dynamic power vs. utilization for both ALU and LDST data paths                                                                                                                         | 84   |

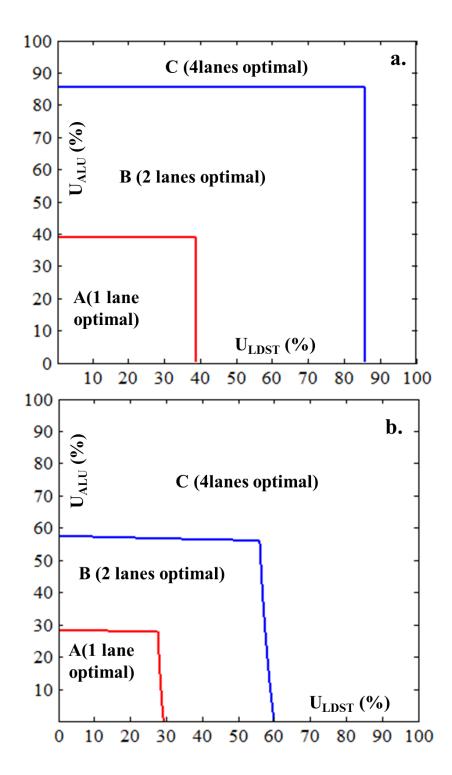

| 9.5  | Optimal utilization boundaries for a. minimum energy b. minimum energy-execution time product.                                                                                         | 88   |

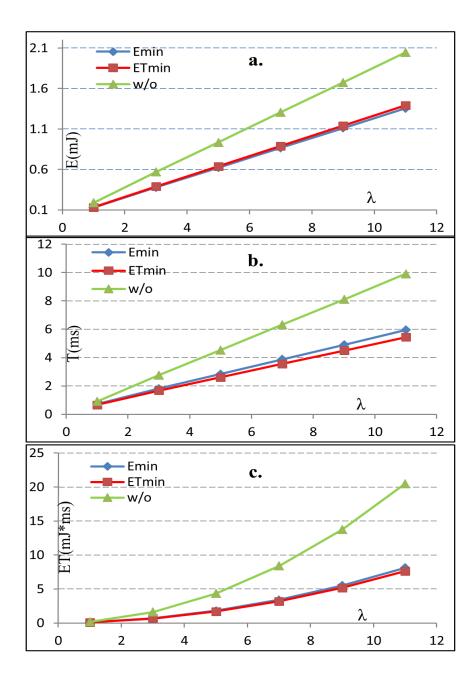

| 9.6  | Comparison of the $E_{min}$ , $ET_{min}$ policies against a VP w/o fusion and lane configuration over the average of 1000 time slices. a. energy b. runtime c. energy-runtime product. | 90   |

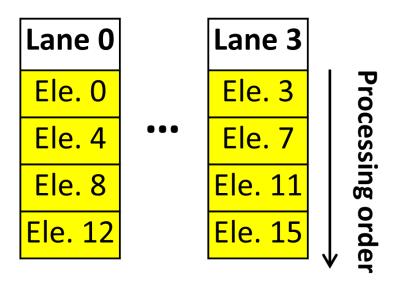

| 10.1 | Execution order of elements within an array of VL=16                                                                                                                                   | 93   |

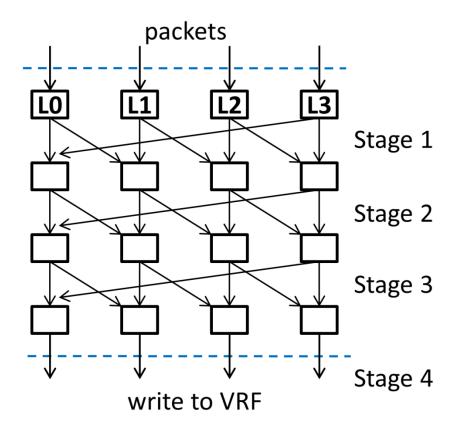

| 10.2 | 2 The ring-based structure of the data shuffle network                                                                                                                                 | 94   |

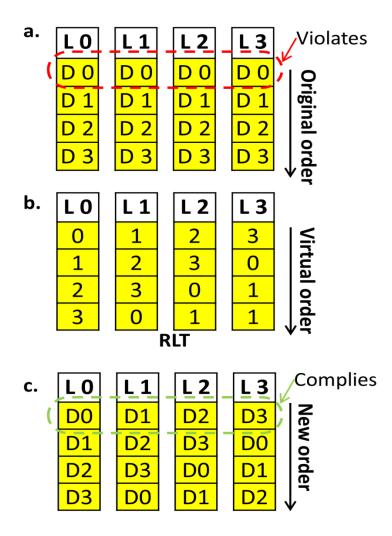

| 10.3 | 3 Execution order and element destinations of a 4*4 matrix transpose. a. the original order b. the RLT setup c. the new order after RLT order translation                              | 97   |

| 11.1 | An example of multiple SMT VPs shared across processor groups                                                                                                                          | 103  |

### LIST OF ABBREVIATIONS

ALU Arithmetic Logic Unit

AC Application Core

ASIC Application Specific Integrated Circuit

AXI Advanced eXtensible Interface

CTS Coarse-grain Temporal Sharing

DCT Discrete Cosine Transform

DLP Data Level Parallelism

DMA Direct Memory Access

DSP Digital Signal Processor

FFT Fast Fourier Transform

FIR Finite Impulse Response

FPGA Field Programmable Gate Array

FTS Fine-grain Temporal Sharing

GPU Graphical Processing Unit

HDU Hazard Detection Unit

LDST Load Store

LM Local Memory

LMB Local Memory Bus

MIMD Multiple Instruction Multiple Data

MM Matrix Multiplication

RLT Reorder Lookup Table

RMM Register Management Module

SIMD Single Instruction Multiple Data

SMT Simultaneous Multithreading

SPS Scalar Processor Subsystem

TLT Translation Lookup Table

VC Vector Controller

VDP Vector Dot Product

VL Vector Length

VLS Vector Lane Sharing

VM Vector Memory

VP Vector Processor

VRF Vector Register File

VT Vector Thread

WB Write Back

#### CHAPTER 1

### INTRODUCTION

This dissertation consists of three major parts: the instruction fusion technique, the vector processor (VP) virtualization technique, and the method to combine the two techniques. In this chapter, the two core technologies proposed by this dissertation are briefly introduced. The problems to be solved are defined first, and then the solutions to the problems are briefly introduced. At the end of this chapter, potential benefits of combining the two techniques are discussed.

### 1.1 The Utilization Wall

Increased requirements for energy consumption, memory size and system bandwidth have always been major concerns in the design of System-on-Chip (SoC) embedded systems. The situation became really insurmountable around 2005 when we entered the era of post-Dennardian scaling [Taylor, 2012]. The utilization wall [Goulding-Hotta et al., 2012], also known as the dark silicon problem, states the following: "With a constant power budget, the percentage of transistors on a chip that can switch at full frequency decreases exponentially with each process generation." This implies that an increasing portion of on-chip transistors will have to stay idle or even be power gated (i.e., to get in the sleep mode) with each new generation, thus giving rise to the name "dark silicon".

The utilization wall is caused by the breakdown of Dennard's MOSFET scaling law that was proposed in 1974 [Dennard et al., 1974]. When the CMOS process scales by a factor of k in the Dennard regime, it increases by  $k^3$  the computational capabilities of a chip of fixed size due to increased operating frequency (f) and transistor density. On the other

hand, the accompanied decreases in the capacitance (C) and supply voltage (Vdd) lead to a decrease of  $k^3$  in the energy consumption of each computation, therefore keeping the total power consumption almost constant.

Unfortunately, Dennard scaling has stopped since 2005 due to the breakdown of Vdd scaling caused by current leakage associated with threshold voltage scaling [Goulding-Hotta et al., 2012]. Without the downward scaling of Vdd in this post-Dennardian CMOS era, the performance of a fixed size chip still grows as  $k^3$  in theory but the energy per computation only drops by k, thus limiting the on-chip resource usage when power consumption is constrained.

Experiments as well show that CMOS may have already hit the utilization wall; with a 45nm TSMC process, only 7% of a 300mm<sup>2</sup> die can switch at full frequency to stay under an 80W power budget [Venkatesh et al., 2010]. As CMOS technology continues to scale in the post-Dennardian era, this problem's impact worsens exponentially. This challenge requires microprocessor architects to focus on energy efficiency while achieving required performance levels. In fact, improved energy efficiency may facilitate higher performance by enabling more transistors to switch.

### 1.2 Inefficient VP Usage

Single instruction multiple data (SIMD) architectures are highly efficient in exploiting data level parallelism (DLP) in applications due to their specialization. A VP, also known as array processor, employs an SIMD architecture capable of processing an array of data elements simultaneously by executing a single vector instruction. As an accelerator, a VP can offload the DLP workload from general-purpose processors, thus enhancing the overall performance and energy efficiency. The VIRAM's multi-lane architecture is the basis of

several VP designs [Kozyrakis and Patterson, 2003]. VIRAM has separate pipeline structures for load-store (LDST) units and arithmetic logic units (ALUs). Vector registers are distributed evenly across the vector lanes. Each lane carries out ALU array operations on data within its local VRF. Vector elements in a lane are processed sequentially due to the ALU's pipelined architecture while all lanes work in parallel on different array parts. SODA [Lin et al., 2006] is a fully programmable VP that realizes the W-CDMA and IEEE802.11a protocols. [Lee et al., 2013] compared accelerators having MIMD (Multiple-Instruction Multiple-Data), vector SIMD and vector thread (VT) architectures in reference to programmability and implementation efficiency; it confirmed that SIMD vector architectures exploit DLP more efficiently than MIMD even for irregular data pattern accesses.

Multicores with embedded VPs have been implemented on FPGAs. They are often referred to as soft vector processors (SVPs). [Cho et al., 2006] introduced an SVP that eliminates memory bank conflicts by using address generation and rearrangement units in the vector memory. VESPA [Yiannacouras et al., 2008] allows the addition of vector lanes with minimum hardware modifications. Benchmarking shows a speedup of 6.3 under saturation with 16 lanes compared to a single lane. VIPERS achieves a speedup of 44 compared to the Nios II scalar processor [Yu et al., 2008]. Its number of functional units and register file bandwidth are configured by software; it occupies 25 times more area compared to its host scalar core. VEGAS [Chou et al., 2011] improves VIPERS's area-delay product. Using scratchpad memory instead of a VRF, it achieves a speedup of up to 208 compared to Nios II. Further improvements to reduce ALU bottlenecks produced VENICE [Severance and Lemieux, 2012] that doubles the performance-per-logic block

compared to VEGAS. With the integration of a streaming pipeline in the data path, a speedup of 7000 over a scalar processor was reported for the N-body problem [Severance et al., 2014].

Application specific VPs are optimized for certain applications. Multimedia applications containing video processing kernels deal with massive DLP. SIMD vector architectures are the best candidates to exploit the parallelism in video frames. Many researchers have tried to optimize codecs for the implementation of new video coding standards such as H.264 or MPEG4. [Iranpour and Kuchcinski, 2004; Lee et al., 2004; Kim et al., 2005; Shengfa et al., 2006; Lee et al., 2008] propose SIMD-based video codecs. A major challenge in video applications is irregular data accesses for video compression. [Lo et al., 2011] overcome this issue by inserting a crossbar between the ALUs and the VRF. [Yang et al., 2005] propose an application-specific VP prototyped on an FPGA for sparse multiplication. IBM's PowerEN processor integrates five hardwired matrix application-specific accelerators in a heterogeneous architecture for key functions such as compression, encryption, authentication, intrusion detection and XML processing. This approach facilitates energy-proportional performance scaling [Heil et al., 2014].

Unfortunately, single-thread dedicated VPs are often not efficiently utilized for the following reasons. First, every application contains some serial code for flow control or other system management, thus vector instructions may not be issued at a rate sufficient to keep the VP highly utilized. Second, data dependencies within some applications' vector instruction flows can cause frequent stalls, wasting precious clock cycles in the VP's super-pipelined floating-point units (FPUs). Finally, it may be preferable that applications with small vectorizable code be executed on the scalar host in order to give another

highly-vectorized application exclusive VP access. However, the former applications as well could benefit from using simultaneously the VP. Benchmarking shows that applications with VP utilization as low as 8.5% can yield a speedup of 84 by executing on a VP compared to a scalar processor with the same clock frequency: an 8\*8 Matrix Multiplication performed by a MicroBlaze (MB) scalar processor takes 20.5ms to complete, while the VP used in this dissertation only requires 241µs as shown in Section 6.2. Given the 100MHz clock rate of its implementation, the 4-lane VP's average ALU utilization is calculated to be 8.5%.

The issue of inefficient usage worsens as VPs scale in the number of lanes: Traditional VPs designed to service exclusively one host scalar processor are normally optimized for applications of a certain level of DLP, and scale easily so that more vector lanes can be added to exploit other applications of higher DLP [Kozyrakis and Patterson, 2003; Yiannacouras et al., 2008; Yu et al., 2008]. However, an increased number of lanes will further reduce the already low VP utilization for the lower-DLP applications.

### 1.3 Motivation and Objectives

To alleviate the impact of the utilization wall as mentioned in Section 1.1, an instruction fusion technique is proposed in this dissertation. The technique can be applied to multiscalar and many-core processors to fuse similar instructions within vector code, and therefore reduce processor dynamic power by idling early processor stages. When running in the proposed fused mode, the multicore processor only fetches one instruction per clock cycle while executing multiple copies of the fetched instruction, thus saving energy in the fused early pipeline stages as well as in the instruction cache.

To address the challenges imposed by inefficient VP utilization as mentioned in Section 1.2, virtualization for VP sharing with simultaneous multithreading (SMT) is introduced in this dissertation. The SMT approach is similar to Intel's Hyper-Threading Technology (HTT) for general-purpose processors that "makes a single physical processor appear as multiple logic processors" [Marr et al., 2002]. However, in this dissertation, SMT is applied to vector code. This approach achieves high aggregate VP utilization independent of individual vector thread DLP rates. VP virtualization solves register name conflicts among threads using a novel VRF virtualization algorithm that can dynamically allocate physical registers of varying lengths to threads. With easy-to-use VRF management kernel functions, programmers are provided with a fixed register name space and VRF management becomes transparent. To prove its viability, VP virtualization is realized on a multi-lane VP [Rooholamin and Ziavras, 2015], and the VP is interfaced with a multicore processor system to benchmark its performance and energy consumption.