# **Copyright Warning & Restrictions**

The copyright law of the United States (Title 17, United States Code) governs the making of photocopies or other reproductions of copyrighted material.

Under certain conditions specified in the law, libraries and archives are authorized to furnish a photocopy or other reproduction. One of these specified conditions is that the photocopy or reproduction is not to be "used for any purpose other than private study, scholarship, or research." If a, user makes a request for, or later uses, a photocopy or reproduction for purposes in excess of "fair use" that user may be liable for copyright infringement,

This institution reserves the right to refuse to accept a copying order if, in its judgment, fulfillment of the order would involve violation of copyright law.

Please Note: The author retains the copyright while the New Jersey Institute of Technology reserves the right to distribute this thesis or dissertation

Printing note: If you do not wish to print this page, then select "Pages from: first page # to: last page #" on the print dialog screen

The Van Houten library has removed some of the personal information and all signatures from the approval page and biographical sketches of theses and dissertations in order to protect the identity of NJIT graduates and faculty.

#### ABSTRACT

### AN EMBEDDED SYSTEM SUPPORTING DYNAMIC PARTIAL RECONFIGURATION OF HARDWARE RESOURCES FOR MORPHOLOGICAL IMAGE PROCESSING

by

#### Gyana Ranjan Sahu

Processors for high-performance computing applications are generally designed with a focus on high clock rates, parallelism of operations and high communication bandwidth, often at the expense of large power consumption. However, the emphasis of many embedded systems and untethered devices is on minimal hardware requirements and reduced power consumption. With the incessant growth of computational needs for embedded applications, which contradict chip power and area needs, the burden is put on the hardware designers to come up with designs that optimize power and area requirements.

This thesis investigates the efficient design of an embedded system for morphological image processing applications on Xilinx FPGAs (Field Programmable Gate Array) by optimizing both area and power usage while delivering high performance. The design leverages a unique capability of FPGAs called dynamic partial reconfiguration (DPR) which allows changing the hardware configuration of silicon pieces at runtime. DPR allows regions of the FPGA to be reprogrammed with new functionality while applications are still running in the remainder of the device.

The main aim of this thesis is to design an embedded system for morphological image processing by accounting for real time and area constraints as compared to a statically configured FPGA. IP (Intellectual Property) cores are synthesized for both static and dynamic time. DPR enables instantiation of more hardware logic over a period of time on an existing device by time-multiplexing the hardware realization of functions. A comparison of power consumption is presented for the statically and dynamically reconfigured designs. Finally, a performance comparison is included for the implementation of the respective algorithms on a hardwired ARM processor as well as on another general-purpose processor. The results prove the viability of DPR for morphological image processing applications.

# AN EMBEDDED SYSTEM SUPPORTING DYNAMIC PARTIAL RECONFIGURATION OF HARDWARE RESOURCES FOR MORPHOLOGICAL IMAGE PROCESSING

by Gyana Ranjan Sahu

A Thesis Submitted to the Faculty of New Jersey Institute of Technology in Partial Fulfillment of the Requirements for the Degree of Master of Science in Computer Engineering

**Department of Electrical and Computer Engineering**

January 2015

## **APPROVAL PAGE**

# AN EMBEDDED SYSTEM SUPPORTING DYNAMIC PARTIAL RECONFIGURATION OF HARDWARE RESOURCES FOR MORPHOLOGICAL IMAGE PROCESSING

### Gyana Ranjan Sahu

Dr. Sotirios Ziavras, Thesis Advisor Date Professor of Electrical and Computer Engineering & Associate Provost for Graduate Studies, NJIT

Dr. Durga Madhab Misra, Committee Member Professor of Electrical and Computer Engineering, NJIT Date

Dr. Roberto Rojas Cessa, Committee Member Associate Professor of Electrical and Computer Engineering, NJIT

Date

# **BIOGRAPHICAL SKETCH**

Author: Gyana Ranjan Sahu

**Degree:** Master of Science

Date: January 2015

# **Undergraduate and Graduate Education:**

- Master of Science in Computer Engineering, New Jersey Institute of Technology, Newark, U.S.A, 2015

- Bachelor of Technology in Electrical Engineering, National Institute of Technology, Rourkela, India, 2010

Major: Computer Engineering

Dedicated to my late grandfather, my first teacher and friend in the journey of life, my father who has always supported me and has been a never ending source of inspiration for me and my family.

Finally, this thesis is dedicated to all those who believe in the richness of learning.

#### ACKNOWLEDGMENT

First and foremost, I would like to thank my advisor, Dr. Sotirios Ziavras, for all his guidance, support, and encouragement throughout my thesis work. I have learned a tremendous amount under his supervision, for which I am deeply grateful. His knowledge and assistance have been invaluable. I would also like to thank my committee members Dr. Durga Madhab Misra and Dr. Roberto Rojas Cessa for their feedback.

I would also like to express my gratitude to my friends Dario Gomez and Yaojie Lu, also members of the Computer Architecture and Parallel Processing Laboratory (CAPPL), who have assisted and guided me in the initial stage of the thesis.

Lastly, I would like to thank my family and my friends for their loving support, encouragement and confidence during my thesis work.

# **TABLE OF CONTENTS**

| C | hapter                                           | Page |

|---|--------------------------------------------------|------|

| 1 | INTRODUCTION                                     | 1    |

|   | 1.1 Motivations and Objectives                   | 1    |

|   | 1.2 Overview                                     | 2    |

| 2 | RECONFIGURABLE COMPUTING                         | 4    |

|   | 2.1 von-Neumann Computing Paradigm               | 4    |

|   | 2.2 Application Specific Processors and ASICs    | 6    |

|   | 2.3 Reconfigurable Computing                     | 7    |

|   | 2.4 FPGA Architecture                            | 8    |

|   | 2.4.1 CLB (Configurable Logic Block)             | 9    |

|   | 2.4.2 Interconnects                              | 10   |

|   | 2.4.3 Select IO (IOB)                            | 11   |

|   | 2.4.4 Memory                                     | 11   |

|   | 2.4.5 Clock Management.                          | 12   |

|   | 2.4.6 SRAM-based Configuration                   | 12   |

|   | 2.4.7 Logic Implementation on FPGAs              | 13   |

|   | 2.4.8 Place and Route                            | 14   |

|   | 2.5 Hardware/Software Codesign for Platform FPGA | 15   |

|   | 2.6 Types of Reconfiguration and Granularity     | 17   |

# TABLE OF CONTENTS (Continued)

| C | Chapter                                                  |    |

|---|----------------------------------------------------------|----|

| 3 | DESIGN FLOW FOR PARTIAL RECONFIGURATION                  | 18 |

|   | 3.1 Introduction                                         | 18 |

|   | 3.2 System Overview                                      | 18 |

|   | 3.3 Device Configuration Interface                       | 21 |

|   | 3.4 Configuration Ports and Interfaces                   | 23 |

|   | 3.5 Image Processing Pipeline in Vivado Design Suite     | 23 |

|   | 3.5.1 Zynq Configuration                                 | 24 |

|   | 3.5.2 AXI Interconnect                                   | 26 |

|   | 3.5.3 DMA Core                                           | 26 |

|   | 3.5.4 AXI Stream Subset Converter                        | 27 |

|   | 3.6 Bottom Up Synthesis and Partial Bitstream Generation | 27 |

| 4 | MORPHOLOGICAL IMAGE PROCESSING ALGORITHMS                | 30 |

|   | 4.1 Erosion and Dilation                                 | 31 |

|   | 4.1.1 Erosion                                            | 32 |

|   | 4.1.2 Dilation                                           | 33 |

|   | 4.2 Opening                                              | 38 |

|   | 4.3 Closing                                              | 38 |

|   | 4.4 Morphological Smoothing                              | 41 |

# TABLE OF CONTENTS (Continued)

| С | hapter                                              | Page |

|---|-----------------------------------------------------|------|

|   | 4.5 Morphological Gradient                          | 42   |

|   | 4.6 Top-Hat and Bottom-Hat Transformations          | 43   |

|   | 4.6.1 Top-Hat Transformation                        | 43   |

|   | 4.6.2 Bottom-Hat Transformation                     | 45   |

| 5 | VIVADO HIGH LEVEL SYNTHESIS AND ALGORITHM SYNTHESIS | 46   |

|   | 5.1 Introduction                                    | 46   |

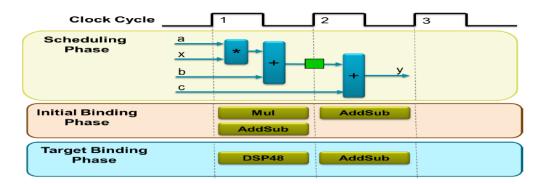

|   | 5.2 Scheduling and Binding                          | 48   |

|   | 5.3 Interface Synthesis and IO Protocols            | 49   |

|   | 5.3.1 Block-level Interface Protocols               | 50   |

|   | 5.3.2 Port-level Memory Interface Protocols         | 51   |

|   | 5.4 AXI Interfaces                                  | 52   |

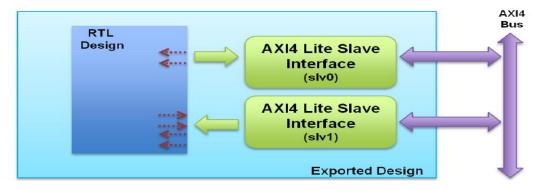

|   | 5.4.1 AXI Lite Slave Interface                      | 53   |

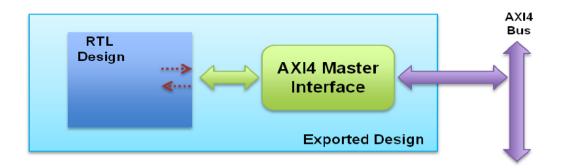

|   | 5.4.2 AXI4 Master Interface                         | 54   |

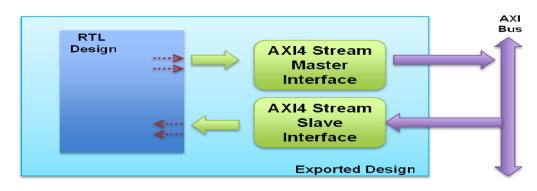

|   | 5.4.3 AXI Stream Interface                          | 55   |

|   | 5.5 Optimizations                                   | 55   |

|   | 5.5.1 Function Inlining                             | 56   |

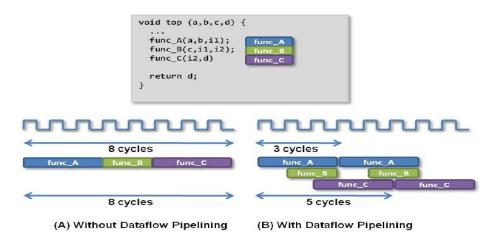

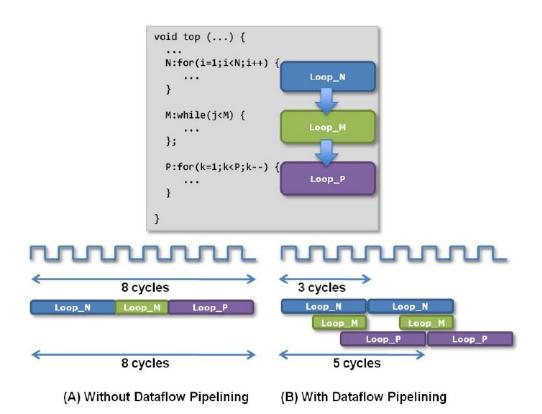

|   | 5.5.2 Function Dataflow Pipelining                  | 56   |

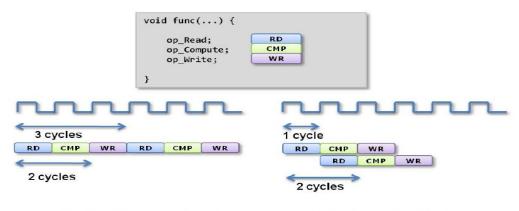

|   | 5.5.3 Function Pipelining                           | 57   |

# TABLE OF CONTENTS (Continued)

| C | hapter                                                  | Page |

|---|---------------------------------------------------------|------|

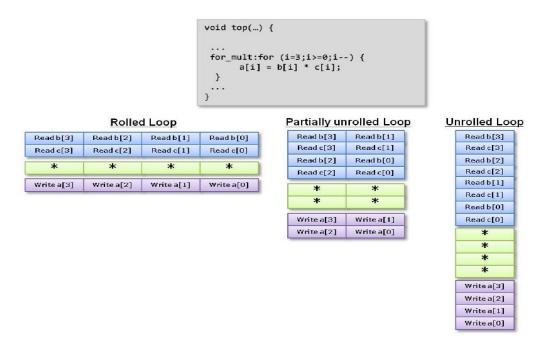

|   | 5.5.4 Loop Unrolling                                    | 58   |

|   | 5.5.5 Loop Merging                                      | 59   |

|   | 5.5.6 Flattening Nested Loops                           | 59   |

|   | 5.5.7 Loop Dataflow Pipelining                          | 59   |

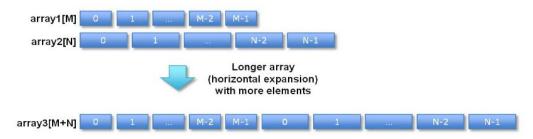

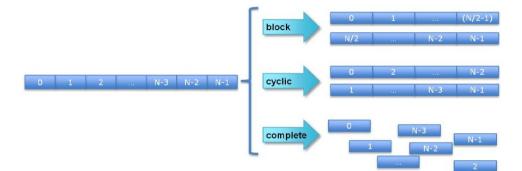

|   | 5.5.8 Array Partitioning and Optimizations              | 60   |

|   | 5.5.9 Arbitrary Precision Data types                    | 62   |

|   | 5.6 Morphological Algorithm Synthesis and Optimizations | 63   |

|   | 5.6.1 Input and Output Interfaces                       | 63   |

|   | 5.6.2 Memory Architecture and Image Buffers             | 64   |

|   | 5.6.3 Arbitrary Precision Data types                    | 66   |

|   | 5.6.4 Optimizations                                     | 67   |

|   | 5.7 5.7 Simulation and Waveforms                        | 67   |

| 6 | PERFORMANCE ANALYSIS OF PARTIAL RECONFIGURATION         | 70   |

|   | 6.1 Introduction                                        | 70   |

|   | 6.2 Comparison of Hardware Resource Utilization         | 70   |

|   | 6.3 Comparison of Power Usage                           | 76   |

|   | 6.4 Comparison of Performance                           | 78   |

| 7 | CONCLUSIONS                                             | 81   |

# LIST OF SYMBOLS

# LIST OF TABLES

| Tab | Table                                                                                         |    |

|-----|-----------------------------------------------------------------------------------------------|----|

| 6.1 | Hardware Resource Utilization for the Static Configuration Design                             | 72 |

| 6.2 | Hardware Resource Utilization for the Reconfigurable Design                                   | 73 |

| 6.3 | Performance of Morphological Algorithms on MATLAB, Zynq (static configuration) and Zynq (DPR) | 76 |

# LIST OF FIGURES

| Figu | ire                                                                                                          | Page |

|------|--------------------------------------------------------------------------------------------------------------|------|

| 2.1  | General structure of a von-Neumann Computer                                                                  | 5    |

| 2.2  | Comparison of various types of computers in terms of performance and flexibility                             | 8    |

| 2.3  | Matrix structure of a FPGA consisting of CLBs and interconnects                                              | 9    |

| 2.4  | Structure of a CLB consisting of LUT and multiplexers                                                        | 10   |

| 2.5  | Structure of SLICE cells and switch matrix for a Xilinx FPGA                                                 | 10   |

| 2.6  | On-chip memory arranged in memory banks and available as BRAMs on Xilinx FPGAs.                              | 11   |

| 2.7  | Dynamic configuration of logic cells by changing SRAM configuration                                          | 13   |

| 2.8  | Entire design flow steps, such as logic synthesis, place, route and bitstream generation to configure a FPGA | 15   |

| 3.1  | Proposed design for the morphological processing pipeline                                                    | 19   |

| 3.2  | Comparison of original, dilated and eroded Lena images                                                       | 20   |

| 3.3  | Zynq 7000 AP SoC system overview                                                                             | 20   |

| 3.4  | DevC block diagram                                                                                           | 22   |

| 3.5  | ICAP primitive on Xilinx FPGA                                                                                | 22   |

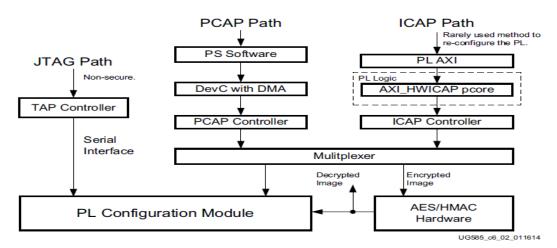

| 3.6  | PL programming paths on Zynq 7000 devices                                                                    | 22   |

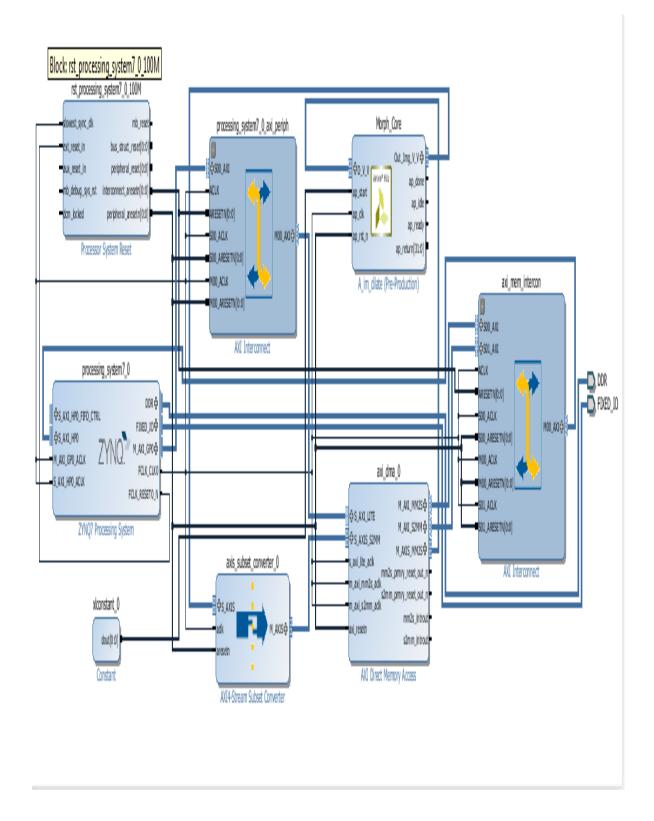

| 3.7  | Final block diagram of the image processing pipeline                                                         | 25   |

| 4.1  | Original Lena image and eroded image for SE(2)                                                               | 34   |

| 4.2  | Matlab runtime profile of the Erosion function                                                               | 35   |

# LIST OF FIGURES (Continued)

| Figur | e                                                                                                                                                                                                                      | Page |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 4.3   | Original Lena image and dilated image by SE(2)                                                                                                                                                                         | 35   |

| 4.4   | Matlab runtime profile of the Dilation function                                                                                                                                                                        | 36   |

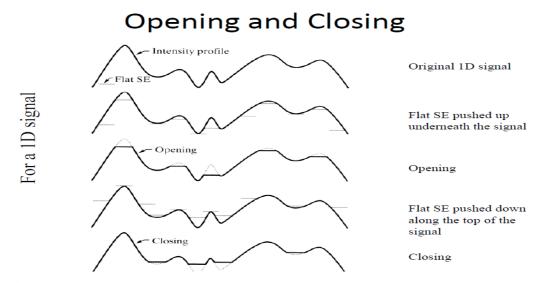

| 4.5   | Geometrical interpretation of Opening and Closing operations                                                                                                                                                           | 39   |

| 4.6   | Original Lena image and the results of the Opening operation for SE(2)                                                                                                                                                 | 40   |

| 4.7   | Matlab runtime profile of the Opening function                                                                                                                                                                         | 40   |

| 4.8   | Original Lena image and results of the Closing operation for SE (2)                                                                                                                                                    | 40   |

| 4.9   | Salt and Pepper added to the Lena image(top-left), Morphological Smoothing with SE (1) (bottom left), Morphological Smoothing with SE (2) (top-right)<br>Morphological Smoothing with SE (1) and SE (3) (bottom-right) | 41   |

| 4.10  | Matlab runtime profile of the Morphological Smoothing function                                                                                                                                                         | 42   |

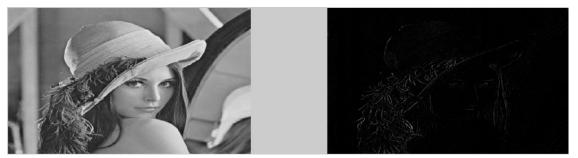

| 4.11  | The original Lena image and the Morphological gradient operated image                                                                                                                                                  | 43   |

| 4.12  | Matlab runtime profile of the Morphological gradient function                                                                                                                                                          | 43   |

| 4.13  | Original Lena image and results of the top-hat transformation image                                                                                                                                                    | 44   |

| 4.14  | Matlab runtime profile of top-hat transformation function                                                                                                                                                              | 44   |

| 4.15  | Original Lena image and results of the bottom-hat transformation image                                                                                                                                                 | 45   |

| 4.16  | Matlab runtime profile of bottom-hat transformation function.                                                                                                                                                          | 45   |

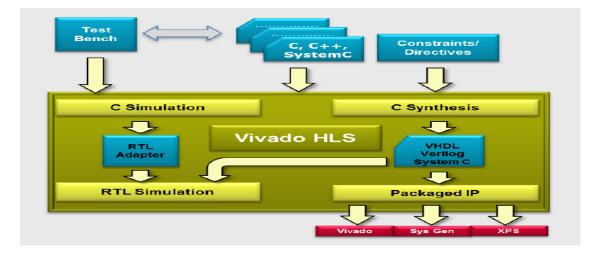

| 5.1   | Vivado HLS design flow                                                                                                                                                                                                 | 47   |

| 5.2   | Scheduling and Binding in HLS                                                                                                                                                                                          | 48   |

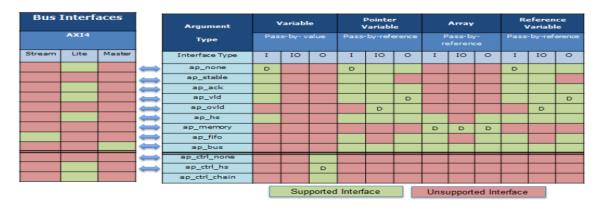

| 5.3   | Interface Synthesis in Vivado HLS                                                                                                                                                                                      | 50   |

| 5.4   | Bus Interface compatibility with different port and block level interfaces                                                                                                                                             | 53   |

| 5.5   | AXI4 Lite Slave Interfaces with Grouped RTL Ports                                                                                                                                                                      | 53   |

# LIST OF FIGURES (Continued)

| Figur<br>5.6 | Figure 5.6 AXI4 Master Interface                                                              |    |

|--------------|-----------------------------------------------------------------------------------------------|----|

| 5.7          | AXI4 Stream Interface                                                                         | 55 |

| 5.8          | Function dataflow pipelining for top function                                                 | 56 |

| 5.9          | Function dataflow pipelining for top function                                                 | 57 |

| 5.10         | Loop unrolling in Vivado HLS                                                                  | 58 |

| 5.11         | Loop dataflow pipelining in Vivado HLS.                                                       | 60 |

| 5.12         | Horizontal mapping of arrays in Vivado HLS                                                    | 61 |

| 5.13         | Vertical mapping of arrays in Vivado HLS.                                                     | 61 |

| 5.14         | Partitioning of arrays in Vivado HLS                                                          | 62 |

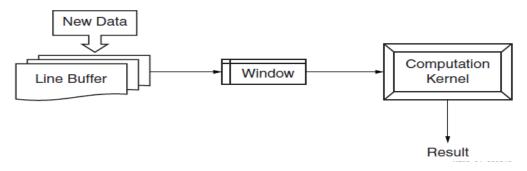

| 5.15         | Processing of data with memory buffers                                                        | 66 |

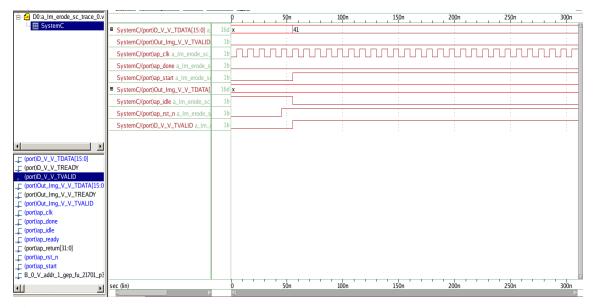

| 5.16         | Waveform generated for erosion IP core showing beginning of transaction                       | 68 |

| 5.17         | Waveform generated for erosion IP core showing streaming input pixel values.                  | 69 |

| 6.1          | Static configuration design                                                                   | 72 |

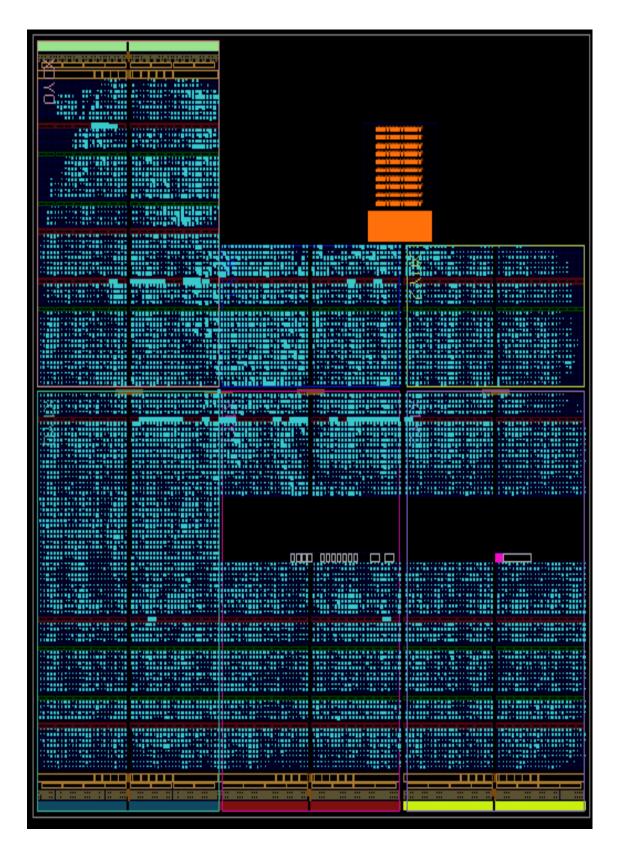

| 6.2          | Floor design of the device for static configuration, showing placed and routed cells          | 73 |

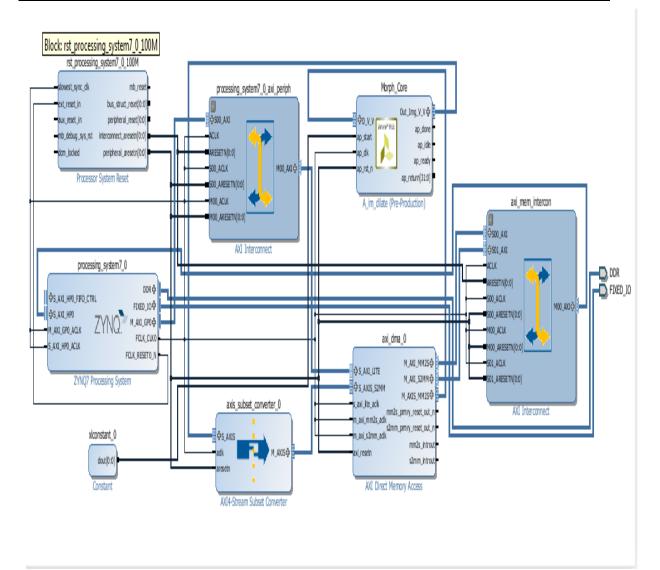

| 6.3          | Reconfigurable design.                                                                        | 74 |

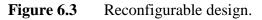

| 6.4          | Floor design of the device for reconfigurable configuration, showing placed and routed cells. | 75 |

| 6.5          | Power analysis of the static design as report by Vivado Design Suite                          | 77 |

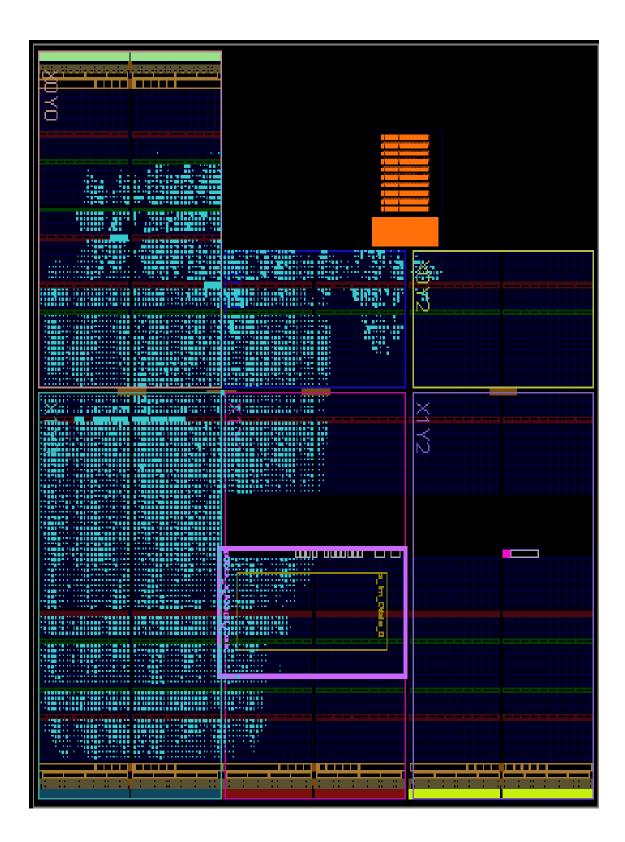

| 6.6          | Power analysis of the reconfigurable design as report by Vivado Design Suite                  | 78 |

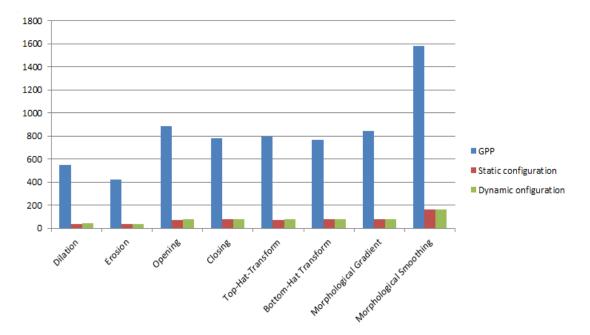

| 6.7          | Scaled execution time on the GPP, and on the FPGA for static and dynamic configurations       | 80 |

#### **CHAPTER 1**

### **INTRODUCTION**

#### **1.1** Motivations and Objectives

As per [1], FPGAs are known to outperform General-Purpose Processors (GPPs) when they are used to implement a specific function in a hardware design. The main aim of this thesis is to present an efficient design of an embedded system targeting at morphological image processing applications. The said embedded system was implemented on the Xilinx AP-SoC FPGA Zedboard. Usually, the FPGA is treated as a slave component in such a reconfigurable system, when required; the complete FPGA is configured to offload the main processor, in this case an ARM processor. With the development of dynamic partial reconfiguration (DPR) features for some FPGAs, only part of the FPGA can be partially reconfigured at runtime when needed. By doing this, such a partially reconfigurable system can provide hardware adaptation for real time functionality.

In designing the embedded system, the image processing cores were built in IP and were stored in the configuration memory. Depending upon the algorithm to be executed, DPR allows the FPGAs to be reconfigured dynamically at runtime to match up changes in application behavior. By leveraging dynamic partial reconfiguration, not only do we achieve a significant reduction in the required floor area but can also gain in terms of power reduction. As for all chips, the power dissipation of FPGAs embodies static and dynamic ingredients. A study released by Xilinx reports that the static power rises substantially below the .25 micron feature size [16].

The major contributors to the dynamic energy consumption of an embedded platform FPGA are the processor and IP cores, and the auxiliary and I/O blocks. Any

FPGA asset consumes both static and dynamic power in the active state, and only static power in standby when its clock signal is disabled. Any power consumption could be eliminated by shutting down the power supply to an asset to put it into the sleep state. However, current FPGAs do not support this feature for specific assets. By configuring only parts of the FPGA to actually employ in computations, we can significantly cut down the dynamic power consumption.

#### 1.2 Overview

The thesis is organized in seven chapters. Chapter 2 discusses the theory of reconfigurable computing. The philosophy of GPP designs, which is based on the von-Neumann computing paradigm, is presented. It also discusses the Application-Specific Integrated Circuit (ASIC) method of implementing designs on silicon. ASICs are the fastest and most optimized designs when it comes to match up application needs. But the fixed structure of ASICs renders them inflexible since they cannot be changed once fabricated. However, when there is a need for flexibility and high performance computational power, DPR has major advantages. Reconfigurable computing, also known as spatial computing, is generally implemented on FPGAs. The same chapter discusses at length the architecture of FPGAs and their ability to reconfigure the design by changing their SRAM configuration. We also present an entire design flow using FPGA-based logic synthesis tools and hardware/software codesign strategies. The chapter concludes by presenting various types of runtime DPR reconfiguration for FPGAs.

Chapter 3 briefly discusses the design flow for logic synthesis on Xilinx FPGAs supporting DPR. It assumes that IP cores used as hardware accelerators are already synthesized and have been converted into partial bitstreams. These bitstreams are available as binary files to be stored in the memory of the host processor.

Chapter 4 discusses the theory of mathematical morphology and various operators which will be implemented on the user programmable host. These different operators are programmed in MATLAB. Only basic operators are discussed as the main aim of this thesis is to design the embedded system for image processing applications. Complex applications can be run for high performance once the core algorithms are synthesized in hardware.

Chapter 5 summarizes the Vivado High-Level synthesis tool that was used to synthesize our design. The optimization effort for our application is included as well.

Chapter 6 presents performance and power analysis results, while Chapter 7 contains conclusions.

#### CHAPTER 2

### **RECONFIGURABLE COMPUTING**

#### 2.1 von-Neumann Computing Paradigm

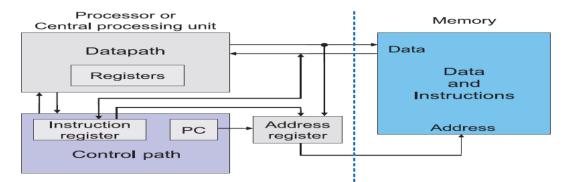

The Hungarian mathematician John von-Neumann (VN) showed that a computing machine could have a simple, fixed hardware structure for the execution of any kind of computation, when given properly programmed control. Since then, the VN machine paradigm has been universally accepted as the standard computing architecture for conventional processing. The general architecture of a VN machine is shown in Figure 2.1 and consists of the following major components:

- A memory for storing data and programs which is sequentially accessed for operands and instructions. To improve performance, Harvard architectures contain two parallel accessible memories for storing program and data separately.

- A control unit featuring a program counter that holds the address of the next instruction to be executed.

- An arithmetic and logic unit (ALU) and CPU registers along with a data path for instruction execution.

A VN machine executes programs sequentially, instruction by instruction. At each step of program execution, the next instruction is fetched from the memory at the specified address stored in the program counter. The fetched instruction is then decoded and executed; a result may be written back into the memory or register.

The main advantage of the VN computing paradigm is its flexibility, because it can be used to program any given algorithm. Each algorithm to be run on a VN machine has to be coded sequentially according to VN rules. That is, 'the algorithm must adapt itself to the hardware'. Because of the VN rules, that imply sequential execution, VN computation is also referred to as 'temporal computation'.

Generally, algorithms have some form of inherent instruction-level parallelism (ILP). They can be executed faster by taking advantage of ILP and often data-level parallelism (DLP). Since all algorithms executed on a pure VN machine are run sequentially; many algorithms cannot be executed to their best possible performance. Modern GPPs exploit ILP and/or some DLP to speed-up execution. Additionally, modern uni-core or multi-core architectures also exploit thread-level parallelism (TLP) to further enhance the performance.

However, if the class of algorithms to be executed is known in advance, then an adaptive processor could be modified to better match the computation paradigm of that class of applications.

**Figure 2.1** General structure of a von-Neumann Computer. *Source*: [2]

Individual processor performance doubled about every 18 months until 2003, following the doubling of transistors as per Moore's law. However, memory improvements did not keep up. As processor speeds increased, the processors spend more time in the idle mode, waiting for data to be fetched from memory. No matter how fast a given processor can work, in effect it is limited by the rate of memory transfers.

Some of the approaches to overcoming this von-Neumann memory bottleneck are:

- Caching: The storage of frequently used data in a special area (usually SRAM), so that it is more readily accessible than if it were stored in the main memory.

- Prefetching: Moving some data into the cache before it is requested to speed up access in the event of a request.

- Multithreading: Managing multiple requests simultaneously in separate threads.

- New types of RAM: For example, DDR SDRAM, which provides an output on both the rising and falling edges of the system clock, rather than on just the rising edge. This doubles the transfer rate.

- Out of order execution: Instructions are dispatched to instruction queues called reservation stations and allowed to complete out of program order. But the instructions are committed to memory or the register file as per the order they appear in the original sequential program order.

### 2.2 Application Specific Processors and ASICs

If an algorithm or computation is fixed for an application, it can be optimized for the best possible performance by designing specialized hardware. In this case, we say that the hardware design matches the application. The hardware or the processing unit which is designed for the specific application is called an Application Specific Processor (ASIP). These, ASIPs are further classified into Domain Specific Processors (DSPs) and ASICs. In an ASIC, the entire application or computation is executed directly on the hardware and offers the best possible performance. In ASICs, the instruction fetch-based cycles are eliminated and hence the need for sequential execution is overcome. Moreover, in ASICs the computation is executed faster by taking advantage of the inherent parallelism in the program. ASICs use a spatial approach to execute an application since all the functional blocks needed for the computation are implemented in hardware. Hence, this kind of

computation is also called 'Spatial Computing'. ASICs are generally implemented with CMOS technology in a single chip. For example, in cell phones certain communication protocol algorithms are implemented on ASICs to provide real-time functionality.

The main drawback of ASICs is that, after fabrication the circuit design cannot be altered. This is in contrast to GPPs where, by changing the software instructions, the functionality of the system is altered on demand without changing the hardware. However, the downside of this flexibility is that the performance suffers, and is far below that of an ASIC. However, due to higher engineering costs resulting from longer design cycles and the increasing costs of design tools, the overall cost of ASICs may be prohibitively high.

### 2.3 Reconfigurable Computing

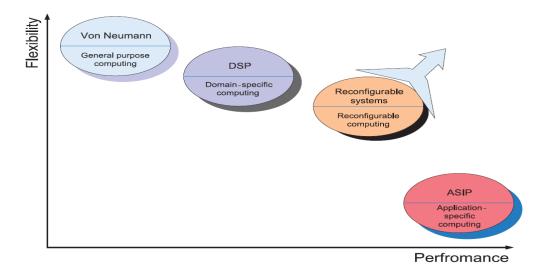

There exist two main attributes to characterize processors: flexibility and performance. Since, VN computers can execute any kind of algorithm, they are considered highly flexible. However, they do not execute the algorithm in ways that achieve the highest performance.

ASICs, on the other hand, allow the functional units to be fabricated on a chip. High performance is possible because 'the hardware is adapted to the application'. If we consider two scales, one for the performance and the other one for the flexibility, then the VN computers can be placed at one end and ASICs at the other end.

Ideally, system designers desire the flexibility of GPPs and the performance of ASICs for the same device. To this extent, a hardware device is needed that can provide spatial computing for the application while simultaneously adapting to the algorithm. Such a hardware device is called a reconfigurable processing unit (RPU).

**Figure 2.2** Comparison of various types of computers in terms of performance and flexibility. *Source:* [2].

The main idea behind a reconfigurable device is to take advantage of the application inherent parallelism to achieve the best possible speedup. The structure of reconfigurable devices is changed by modifying all or part of the hardware at compile or run time, by downloading a configuration bitstream into the device. The most popular devices that support this type of reconfiguration are FPGAs.

#### 2.4 FPGA Architecture

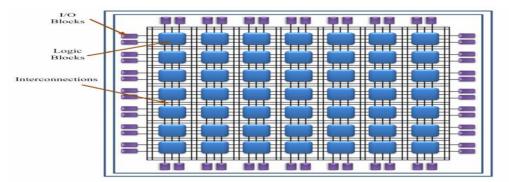

FPGAs were first introduced in the 1985s by Xilinx Inc. as programmable logic devices. The FPGA architecture consists of three main parts: a set of programmable logic cells (CLBs), a programmable interconnect network for routing information between input/output blocks, and a set of input and output cells around the device. About 90% of the FPGA area is made of programmable interconnects; the rest of the FPGA is made of logic blocks [3,6]. Figure 2.3 shows a generic FPGA architecture. Additional, resources such as memory, DSP blocks, embedded processors, etc., may be available on a FPGA depending on the vendor.

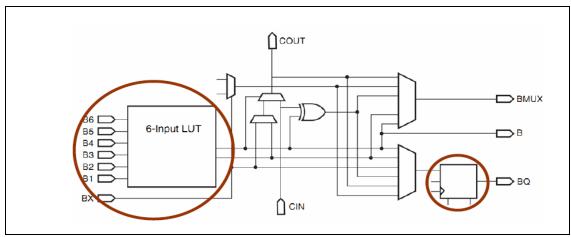

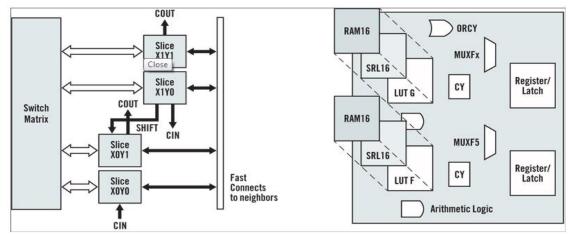

#### 2.4.1 CLB (Configurable Logic Block)

The CLB is the basic logic unit in a FPGA. Exact numbers and features vary from device to device, but every CLB commonly consists of a configurable switch matrix with 4 or 6 inputs, some selection circuitry (MUX, etc.), and flip-flops [2]. The switch matrix is highly flexible and can be configured to handle combinatorial logic, shift registers or RAM. Altera Corp. refers to these logic blocks as Logic Array Blocks (LABs). In addition, each CLB contains several look-up tables (LUTs).

**Figure 2.3** Matrix structure of a FPGA consisting of CLBs and interconnects. *Source:* [2].

The LUT is used by most of the FPGA vendors mainly because an n-input LUT is capable of implementing of any n-input logic function. In other words, a LUT is a small memory that directly stores the truth table to realize a fundamental digital circuit. The number of CLBs and their configuration depend on the size and type of the FPGA. Figure 2.4 illustrates Xilinx CLB components.

**Figure 2.4** Structure of a CLB consisting of LUT and multiplexers. *Source:*[2].

**Figure 2.5** Structure of SLICE cells and the switch matrix for a Xilinx FPGA. *Source:* [4].

### **2.4.2 Interconnects**

While the CLBs provide logic capability, flexible interconnect routing routes [2] the signals between CLBs and to/from I/O ports. Routing comes in several flavors, from interconnecting CLBs, to fast horizontal and vertical long lines spanning the device, to global low-skew routing for clocking and other global signals. The design software hides interconnect routing from the user, unless specified otherwise.

Input/Output blocks provided on FPGAs are generally programmable for input or output. They are used to propagate signals from one logic element to another. Xilinx FPGAs provide support for various I/O standards [4]. In Xilinx 7 series FPGAs, each I/O bank contains fifty SelectIO pins which can support different I/O standards (single ended and differential ended I/O standards) [5].

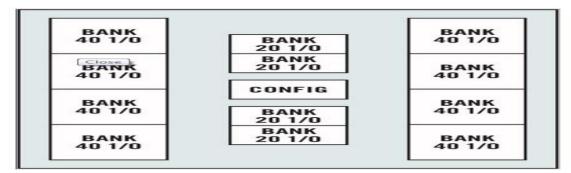

### 2.4.4 Memory

Embedded BRAM (Block RAM) memory, which is available in most FPGAs, allows for on-chip memory to be instantiated in the design. These on-chip memories allow the designer to store coefficient and other buffer data.

**Figure 2.6** On-chip memory arranged in memory banks and available as BRAMs on Xilinx FPGAs. *Source:*[4].

Xilinx FPGAs provide up to 10Mbits of on-chip memory in 36kbit blocks that can support true dual-port operation. Figure 2.6 shows the on-chip memory arranged as memory banks in the FPGA chip.

#### 2.4.5 Clock Management

Digital clock management is provided by most FPGAs in the industry (all Xilinx FPGAs have this feature). The most advanced FPGAs from Xilinx offer both digital clock management and phase-looped locking that provide precision clock synthesis combined with jitter reduction and filtering [4]. This lets the designer operate the hardware module at different clock frequencies. Sometimes different IP cores instantiated in the design need to operate in a particular fixed clock domain and then synchronize the system with other modules running in a different clock domain. For example, in building a HDMI video pipeline, the design needs to operate at 148.5MHz while letting the other modules operate at 200MHz.

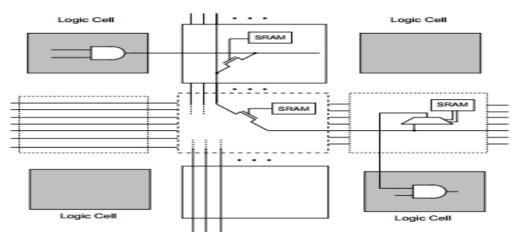

### 2.4.6 SRAM-based Configuration

Static memory is the most widely used method of configuring FPGAs. FPGAs can be configured any number of times by changing the bits stored in the static SRAM memory cells. The output of a memory cell is directly connected to another circuit and the state of the memory cell continuously controls the circuit being configured. Although using volatile SRAM cells has some disadvantages, the advantages far out-weight the disadvantages. Some disadvantages of SRAM-cell FPGAs are:

- The SRAM configuration memory consumes a noticeable amount of power, even when the program is not changed.

- The bits in the SRAM configuration may be susceptible to flipping.

- A large number of bits must be set in order to program an FPGA. Each combinational logic element requires many programming bits and each programmable interconnection point requires its own bit.

An example of using SRAM-controlled switches is illustrated in Figure 2.7. It shows two applications of SRAM cells for controlling the gate nodes of pass-transistor switches, and for control lines of multiplexers that drive logic block inputs. When both SRAM cells store one, the output of one logic block is connected to the other through the multiplexer. Whether an FPGA uses pass-transistors or multiplexers, or both, depends on the particular product.

**Figure 2.7** Dynamic configuration of logic cells by changing the SRAM configuration. *Source:* [4].

### 2.4.7 Logic Implementation on FPGAs

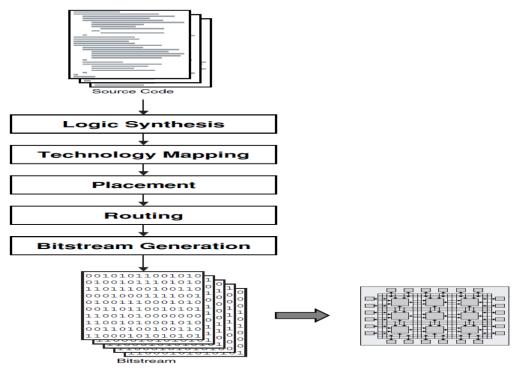

The steps required to implement an application or algorithm on an FPGA are commonly referred to as design flow. Programming an FPGA is significantly different from programming a GPP. Rather than generating sequences of instructions, we generate the hardware components that will be mapped at different times to the available resources. As per algorithm needs, the hardware resources will be generated for spatial computation. The generation of such components is called logic synthesis. It is an optimization process whose goal is to minimize some cost function aimed at producing, for instance, the fastest hardware with the smallest amount of resources and the smallest power consumption.

The algorithm or function is generated using either a schematic editor, a hardware description language (HDL), or a finite state machine (FSM) editor. HDLs, such as VHDL, Verilog and System C, are the most commonly used tools to generate the RTL of the hardware. Other than VHDL and Verilog, there are other hardware synthesis tools provided by different vendors which allow the synthesis of hardware from high level languages like C/C++. High-level synthesis or C-based design flows are relatively simpler and provide a straightforward approach for hardware synthesis tools provide a faster approach for simulation and debugging of hardware before synthesis. For example, the high-level synthesis tool provided by Xilinx is called Vivado HLS; Altera uses OpenCL.

#### 2.4.8 Place and Route

After functional simulation, the design can be compiled and optimized. It is first translated into a set of Boolean equations. Technology mapping is then used to implement the functions with the available modules in the function library of the target architecture. In case of FPGAs, this step is called LUT-based technology mapping, because LUTs are the modules used in the FPGA to implement the Boolean operators. The result of logic synthesis is called netlist. A netlist describes the modules used to implement the functions as well as their interconnections. For the netlist generated in the logic synthesis process, operators (LUTs, Flip-Flops, Multiplexers, etc.) should be placed on the FPGA and connected together through routing. These two steps are normally achieved by CAD tools provided by the FPGA vendors. After the placement and routing of a netlist, the CAD tools generate a file called a bitstream. A bitstream provides the

description of all the bits used to configure the LUTs, the interconnect matrices, the state of the multiplexer and the I/O of the FPGA. Full and partial bitstreams (for partial FPGA reconfiguration) can now be stored in a memory to be downloaded into the FPGA fabric.

This thesis uses Vivado HLS to synthesize most of the morphological functions; they were implemented on the FPGA fabric by a different tool the Vivado Design Suite. The entire process of the FPGA design flow is shown in Figure 2.8.

**Figure 2.8** Entire design flow steps, such as logic synthesis, place, route and bitstream generation to configure a FPGA. *Source* [2].

### 2.5 Hardware/Software Codesign for Platform FPGA

Currently, many FPGA vendors provide FPGA platforms in the form of a System-on-a-Programmable Chip (SoPC). Xilinx refers to its design architecture as "All Programmable-System on a Chip (SoC)" whereas Altera refers to its design architecture as "System on a Programmable Chip". These devices, apart from containing an FPGA fabric, also include other system level components such as memory, ADC converters, USB ports, HDMI ports, etc. These SoCs enable extensive system level differentiation, integration, and flexibility through hardware, software, and I/O programmability.

System-on-a-chip FPGAs include embedded processors (hard or soft), bus protocols, memory and other IPs which provide an opportunity for system designers to develop high performance systems. Hard processors are microprocessors that have been diffused in the silicon that contains an FPGA. For example, the Virtex II chip from Xilinx includes a PowerPC processor whereas the Zedboard APSoC includes a dual-core ARM processor. Soft processors are microprocessors that are created out of the FPGA gate array and can be configured to suite a particular application. An example is the MicroBlaze 32-bit RISC processor available from Xilinx as an IP.

HW/SW codesign meets system level objectives by exploiting the synergism of hardware and software through a concurrent design. It attempts to manage the simultaneous development of hardware and software, it requires the use of multiple discrete design flows at the implementation level (the system is specified and analyzed, and then the hardware specification is passed to the hardware designers while the software specification is passed to the software designers).

In this thesis, the implementation is done on a Xilinx Zynq-7000 series SoC contained in the Zedboard. The Zedboard includes a dual-core ARM Cortex-A9 MPCore hard Processing System (PS) that interacts with tightly coupled 7 series 85K Programmable Logic (PL) cells. Other key peripherals on the board include:

- 512 MB DDR3

- 256 Mb Quad-SPI Flash

- 4 GB SD card

- USB-JTAG port

- 10/100/1000 Ethernet

- USB OTG 2.0 and USB-UART

- HDMI output supporting 1080p60 with 16-bit, YCbCr, 4:2:2 mode color

- VGA output (12-bit resolution color)

- 128x32 OLED display

- 8 user LEDs, 7 push buttons and 8 DIP switches.

### 2.6 Types of Reconfiguration and Granularity

Depending upon the granularity of the device, the reconfiguration can be classified as fine-grain or coarse-grain. Fine-grain reconfigurable devices are modified at a very low level of granularity. For instance, the device can be modified to add or remove a single inverter or a single two-input NAND gate. Fine-grain reconfigurable devices are mostly programmable logic devices (PLDs). However, fine-grain architectures may not be efficient because of large routing areas and poor routablity. Most of the reconfigurable architectures are built as coarse-grain reconfigurable arrays with large path widths. Computational data paths generally have widths greater than one bit and, hence, more area efficient designs are possible by using custom reconfigurable data paths of width greater than one. Several basic computing blocks are grouped into a coarse-grain CLB.

#### **CHAPTER 3**

### **DESIGN FLOW FOR PARTIAL RECONFIGURATION**

#### 3.1 Introduction

This chapter presents a detailed description of the design flow for generating partial configuration bitstreams targeting at Zynq AP-SoC devices. The final implementation of the modules is done on a Zedboard which contains a Zynq 7 series device. The process of generating a static configuration was explained in the preceding chapter. In partial reconfiguration, the design flow consists of generating both the static configuration and the partial reconfiguration bitstreams. In our case, the static configuration consists of generating a morphological image processing pipeline with functionality that remains fixed. Different morphological operations and algorithms are explained in the next chapter, and the synthesis of the algorithms is discussed in Chapter 5. For now, we assume that we have the synthesized algorithm and generate the RTL model. The next section describes the rest of the design flow for partial reconfiguration.

#### 3.2 System Overview

This section describes our system for implementing two morphological image processing accelerators in Programmable Logic (PL) by using partial reconfiguration to load the desired functionality on demand. The Zynq-7000 AP-SoC integrates a dual-core ARM Cortex-A9 based processing system (PS) and programmable logic (PL) in a single device. The proposed design makes use of both the PS and PL portions and

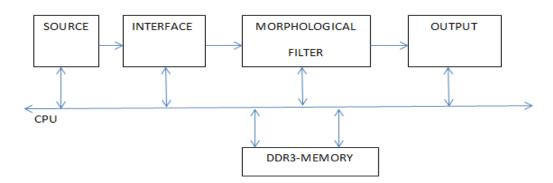

demonstrates how it is best to separate control (mapped onto the PS) and data path (mapped onto the PL). The PL implements a powerful, high-performance image processing pipeline that consists of input, core processing, and output stages (shown in Figure 3.1).

Figure 3.1 Proposed design for the morphological image processing pipeline.

The PS is used to configure the individual IP cores inside the PL and to control the data flow. The first morphological IP core is a dilation operation that increases the grayscale intensity of the image as per a structural element (SE) used in this process; the second morphological IP core is an erosion operator that does the opposite.

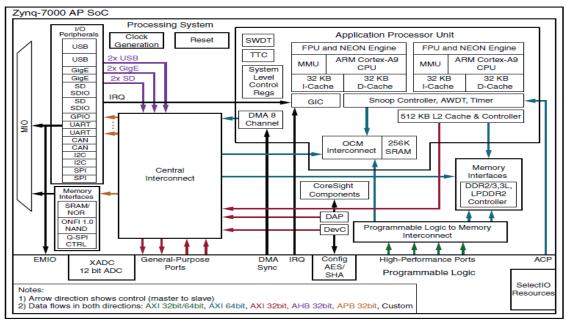

Figure 3.2 shows a comparison of original, dilation-processed, and erosionprocessed images. The RTL for both morphological IP cores is generated from a Calgorithm description using the High-Level Synthesis tool Vivado HLS. The system overview of the PS section is shown in Figure 3.3. The PS is configured with the following I/O peripherals enabled: USB0, SD0, UART1, and GPIO. All I/O peripheral interfaces are configured for multiplexed I/O. Interrupt signals are connected to the DMA channel and the morphological IP cores.

Figure 3.2 Comparison of original, dilated and eroded Lena images.

The General Purpose Master Port GP0 is used to configure and control memorymapped IP cores via the AXI4-lite interface. The HP0 High Performance Ports are connected via the AXI4: the core processing pipeline is connected to the HP0 read/write channels; the input pipeline is connected to the HP0 write channel; the output pipeline is connected to the HP0 read channel. A PS internal clock generator provides a 100 MHz clock to the PL which sets the clock domain for the rest of the modules.

**Figure 3.3** Zynq 7000 AP SoC system overview. *Source:*[7].

#### **3.3 Device Configuration Interface**

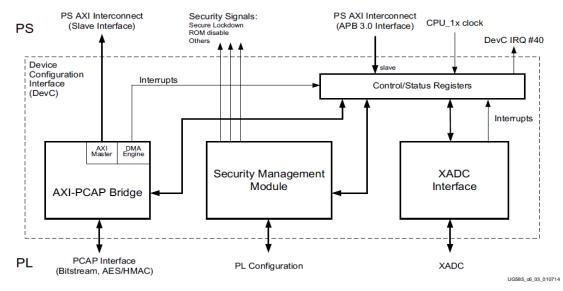

The device configuration interface (DevC) includes the methods and procedures for initializing and configuring the PL under PS software control [7]. The DevC consists of a set of control/status registers and three main functional modules. The PS accesses the APB registers to control the three independent modules in the DevC which are the AXI-PCAP bridge, security management module and XADC interface. If an AES encrypted bitstream is used for configuration, then the AXI-PCAP bridge with the DMA is used by the PS to decrypt the bitstream in order to configure the FPGA. In this thesis, the PCAP (Processor Configuration Access Port) mode of reconfiguration is chosen as the interface for DPR. Xilinx provides access to all the registers in the DevC using a header file, Devcfg.h, and necessary function calls to specify the mode of configuration and DMA transfer calls. In this thesis the lower level functions have been further abstracted through a function call to the "XDcfg TransferBitfile" function which takes in a pointer to the Devcfg, the starting address of the bitfile, and the word length of the bitfile. The starting address can be obtained by downloading the bitstream to a fixed location using the XMD tool or by using a FAT file system to download the bitstream from the SD card to a fixed location in memory. Figure 3.4 shows the block diagram of the DevC interface.

**Figure 3.4** DevC Block diagram. *Source*: [7].

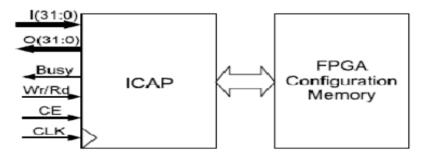

**Figure 3.5** ICAP primitive on Xilinx FPGA. *Source:* [8].

**Figure 3.6** PL programming paths on Zynq 7000 devices. *Source:* [7].

# 3.4 Configuration Ports and Interfaces

The PL can be configured by the PS in the secure or non-secure mode. The PL can also be configured by the TAP controller on the JTAG chain in the non-secure mode. The interfaces which allow the configuration of the PL are:

- 1. PS AXI-PCAP Interface [7]: The PL can be configured by downloading the bitstream to the PCAP (Processor Configuration Access Port) through the DevC interface in secure and non-secure modes. In PCAP mode of configuration the partial bitstreams are stored in a SD card and transferred to the DDR memory by calling a FAT file system function. From the memory the PL is configured by the PS section by downloading the bitstream to the PCAP through the DevC interface. Using this interface, the device can be configured at run-time to support DPR. The AXI-PCAP bridge converts 32-bit AXI formatted data to the 32-bit PCAP protocol and vice-versa. A transmit and receive FIFO buffers the data between the AXI and the PCAP interface. The 32-bit PCAP interface is clocked at 100 MHz and supports 400 MB/s download throughput for non-secure PL configuration and 100 MB/s for secure PL configuration where data is sent only every 4th clock cycle. To transfer data across the PCAP interface a DevC driver function needs to be called. The driver takes care of setting the correct PCAP mode and initiating the DMA transfer. The function call returns only after both the AXI and the PCAP transfers are complete.

- 2. JTAG TAP Controller: The PL section can also be configured by the JTAG interface through the TAP controller. This can be only done in the non-secure mode.

- 3. ICAP interface [8]: In this mode of partial reconfiguration, the bitstream is stored in a logic module instantiated in the PL section and dynamically loaded into the configuration memory. As shown in Figure 3.5, ICAP (Internal Configuration Access Port), which is the Xilinx provided hardware interface for partial reconfiguration, interfaces to the configuration memory and furthermore provides parallel access ports to programmable resources. During run-time, a master device (normally an embedded microprocessor) can transmit the partial reconfiguration bitstream from the storage devices to the ICAP to accomplish the reconfiguration process. The complete design, in which the ICAP primitive is instantiated, interfaces the system interconnect fabric in order to communicate with the processor and memories.

# 3.5 Image Processing Pipeline in the Vivado Design Suite

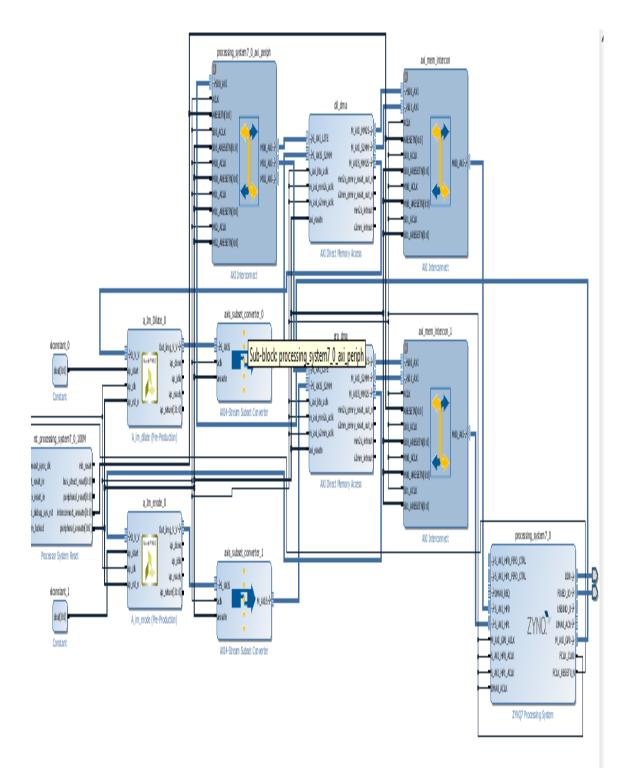

The morphological image processing pipeline is designed and built using needed IP core

blocks. First, the primary morphological operators are built into IP core blocks using the

Vivado HLS tool. Algorithm synthesis and optimizations are explained in subsequent

chapters. For now, we assume the primary image processing operators are available as the Dilate IP core and the Erode IP cores. The processing pipeline is first designed with static configuration using the Erode and Dilate IP cores. The corresponding reconfigurable image processing pipeline design is shown in Figure 3.7. In the reconfigurable design the Morph IP core is time multiplexed to execute at will the functionality of Erode IP core or the Dilate IP core.

# 3.5.1 Zynq Configuration

The design consists of a Zynq processor instantiated with the following configuration:

- UART 1 is enabled at the baud rate of 1152Hz.

- All the four DMA channels are enabled.

- SD0 is enabled.

- GPIO is enabled.

- The ARM host processor frequency is set at 666.66MHz.

- The DDR frequency is set at 533MHz.

- Two fabric clocks FLCK0 and FCLK1 are enabled at 100MHz and 150MHz respectively. Two clock frequencies are selected because if system synthesis cannot meet the static timing requirements needed we switch to a slower clock.

- Fabric interrupts from the PL to PS sections used to select up to 16 peripheral interrupts from the PL section.

- Master AXI GPIO 0 is enabled to interface the low throughput data path from the ARM PS to PL.

- The slave high performance port HPO is enabled to transfer data between the DDR memory and the PL section using a peripheral DMA transaction. The data width is set at 64 bits.

Figure 3.7 Final block diagram of the reconfigurable image processing pipeline.

#### **3.5.2 AXI Interconnect**

The IP AXI Interconnect core connects one or more AXI memory-mapped master devices to one or more memory-mapped slave devices. The AXI interfaces conform to the AMBA AXI4 specification from ARM, including the AXI4-Lite control register interface subset [9]. It is used in this design to connect the Zynq processor with the Morph IP core through the DMA. When connecting one master to one slave, the AXI Interconnect core can optionally perform address range checking. It can also perform data-width conversions, clock-rate conversions, protocol conversions, register pipelining, and data path buffering functions. Each master and slave connection of the AXI interconnect can independently use data widths of 32, 64, 128, 256, 512, or 1024 bits. The AXI interconnect is very robust for our design because it is capable of addressing different AXI bus protocols such as the AXI Lite and the AXI MM (Memory mapped). In our design, the Morph core implements both the AXI streaming and the AXI4lite interface protocols.

# 3.5.3 DMA Core

The AXI DMA core is a soft Xilinx IP core for use with the Vivado Design Suite. The AXI DMA engine provides high-bandwidth DMA between the memory and the AXI4-Stream-type Morph peripherals. Its optional scatter and gather capabilities can off-load data movement tasks from the host CPU [10]. Initialization, status, and management registers are accessed through an AXI4-Lite slave interface which is connected to the ARM Master GPIO interface via the AXI interconnect. Primary high-speed DMA data movement between the system memory and the stream interface is through the AXI4 Memory Map Read Master to the AXI MM2S Stream Master, and the AXI S2MM

Stream Slave to the AXI4 Memory Map Write Master. The MM2S and S2MM channels operate independently and in the full-duplex mode. Furthermore, the AXI DMA provides byte-level data realignment allowing memory reads and writes to any byte offset location.

The MM2S channel supports an AXI Control stream for sending application data to the Morph IP. For the S2MM channel, an AXI Status stream is provided for receiving user application data from the Morph IP. All these features of the DMA IP core enable high performance data transfer rates for image pixel data between the Morph core and the Zynq PS.

#### 3.5.4 AXI Stream Subset Converter

The AXI4-Stream Subset Converter provides a solution for connecting together slightly incompatible AXI4-Stream signal sets. The IP has configurable AXI4-Stream signals for each interface that allows converting one signal set to another in a consistent manner. All signals can be configured to be removed or added, and additionally the TDATA/TUSER signals can be remapped [11]. Vivado HLS generates the Morph IP cores which are slightly incompatible with the AXI DMA cores. Hence, to ensure proper transfers of data from memory to the Morph cores and back to memory, we need to use the AXI4 Stream subset converter.

# **3.6 Bottom Up Synthesis and Partial Bitstream Generation**

Bottom-Up Synthesis is a design strategy to synthesize by modules. Bottom-Up Synthesis requires that a separate netlist is written for each partition, and no optimizations are done across these boundaries, ensuring that each portion of the design is synthesized independently. Since, we have built the Morph cores separately, we can implement the IP

cores using the bottom up synthesis process. Top-level logic for the Morph core is synthesized assuming black boxes for the partitions. Here a partition refers to a logical section of the design, defined by the user at a hierarchical boundary to be considered for design reuse. A partition is either implemented as new or preserved from a previous implementation. A partition that is preserved maintains not only identical functionality but also identical implementation. Partition pins are the logical and physical connection between static logic and reconfigurable logic. Partition pins are automatically created for all reconfigurable partition ports. Here the static logic consists of the portion of the design that remains fixed and the reconfigurable portion refers to the synthesized Morph cores which keep on changing depending upon the higher level algorithms. The tool flow for generating the full and partial reconfiguration can be explained as follows:

• We synthesize the static and reconfigurable modules separately. The files for the static and reconfigurable designs are synthesized and stored as checkpoint files. If the reconfigurable logic consists of more than one reconfigurable module, we should have all the reconfigurable modules synthesized as checkpoint files for that configuration.

• The static design is opened in the netlist pane and consists of reconfigurable modules instantiated as black boxes. Following this, all the constraints for the static design are loaded into the memory.

• In the floor plan of the design, a partition called pblock is created which assigns the pins and ports for the reconfigurable partition. For creating a reconfigurable partition, a property HD.RECONFIGURABLE has to be set on the pblock. It is required that all the reconfigurable modules have the same ports and interfaces.

• The first reconfigurable module is now opened inside the partition assigned for the reconfigurable design. The entire design is reconfigurable, which is now ready for synthesis. Since partial reconfiguration is a licensed feature, the design can only be synthesized if the license is available.

• The design is now placed and routed, and two bitstreams are generated. The first bitstream is the static bitstream which can be used to configure the FPGA at power-on time. The second file is called the partial reconfiguration bitstream which is used for DPR. The file has to be in a binary form so as to be uploaded to the PL section of the FPGA at runtime.

• The same procedure is repeated for other reconfigurable modules and partial binary bitstreams are generated accordingly.

• All the binary bitstreams are uploaded into fixed locations in the DDR memory and function calls are made to transfer the bitstreams to the PL section through the DevC interface.

#### **CHAPTER 4**

# MORPHOLOGICAL IMAGE PROCESSING ALGORITHMS

This chapter gives a detailed overview of the theory and application of Morphological image processing. All the image processing operators and functions described in this chapter have been implemented in MATLAB, on the ARM-processor (without DPR and PL acceleration), and on the Zynq device with both static and dynamic PL configuration. For simplicity, only MATLAB processed images are presented in this chapter.

Mathematical morphology is a set of tools for extracting image components that are useful in the representation and description of region and shape, such as boundaries, skeletons, etc. Morphological processing is constructed with operations on sets of pixels. Furthermore, morphological operations can be used for filtering, thinning and pruning. Originally, morphological operations were defined for binary images but they can be easily extended for gray-scale images.

Binary images contains pixels having only two values (0 and 1, or black and white). Instead of referring to the colors black and white, we can refer to them as foreground and background. In binary morphological image processing, operations are typically performed on the foreground or background only, and not on all the pixels in the image. Therefore, at any time either the set of black pixels or the set of white pixels will comprise the set of interest because any operation which affects the set of black pixels will also affect the set of white pixels. The two basic operations for the construction of morphological operators are dilation and erosion. In the basic Minkowski set operations, the Minkowski addition of two sets F and B is defined as the piecewise vector sum of the elements of F and B:

$$F \bigoplus B = \{ f+b \mid f \in F \text{ and } b \in B \}$$

$$(4.1)$$

The Minkowski subtraction of a set B from a set F is defined as:

$$\mathbf{F} \overleftrightarrow{\mathbf{B}} = \cap \mathbf{F} \cdot \mathbf{b} \tag{4.2}$$

where -b represents the reflection of set b and the subtraction is obtained by taking the intersection ( $\cap$ ) with the set F.

In mathematical morphology, the Minkowski addition and subtraction are called dilation and erosion, respectively. Although both operands F and B are sets of the same type, the first operand is commonly interpreted as the image on which the operation is applied, and the second operand is usually a much smaller set called the structuring element (SE). SEs can be either non-flat (continuous variation of intensity is rarely used) or flat [12]. Unless mentioned otherwise, SEs are flat and symmetrical with the origin at the center. Two-dimensional, or flat, structuring elements consist of a matrix of 0's and

1's, typically much smaller than the image being processed. The center pixel of the SE, called the origin, identifies the pixel of interest that is the pixel being processed. The pixels in the SE containing 1's define the neighborhood of the structuring element. Some of the flat structuring elements available in the MATLAB library are:

- Arbitrary.

- Diamond.

- Pair.

- Disk.

- Line.

- Octagon.

- Periodic line.

- Rectangle.

- Square.

In most of the algorithms we consider an SE of disk type with a radius of two units and use the short hand notation SE(2). For the SE(2) of size 5x5, all the co-ordinates which are at a distance of 2 are marked as 1 and the others as 0. For gray-scale images, erosion and dilation are defined as follows:

# 4.1.1 Erosion

The erosion of an image f by a flat structuring element b at any location (x, y) is defined as the minimum value of the image in the region coincident with b when the origin of b is at (x, y) [12]. Therefore, the erosion at (x, y) of an image f by a structuring element b is given by:

$$[f \bigoplus b](x,y) = \min_{(s,t) \in b} \{(x+s,y+t)\}$$

$$(4.3)$$

Here, the ordered pair (x,y) denotes the co-ordinates in the image f and (s,t) denotes the co-ordinates of the structuring element b.

The image co-ordinates x and y are incremented through all values required so that the origin of b visits every pixel in f. To find the erosion of image f by b, we place the origin of the structuring element at every pixel location in the image. The erosion is the minimum value of f from all values of f in the region of f coincident with b. Since, erosion replaces the current pixel with the minimum value from the neighborhood, the resultant image is darker than the original one.

# 4.1.2 Dilation

The dilation of an image f by a flat structuring element b at any location (x, y) is defined as the maximum value of the image in the window outlined by  $b^{+} = b(-x,-y)$  with the origin of b<sup>+</sup> being at (x,y) [12]. That is

$$[f \bigoplus b](x,y) = \max_{(s,t) \in b} \{ (x-s,y-t) \}$$

$$(4.4)$$

where (s,t) are the co-ordinates of structuring element b.

The algorithm is similar to the one for erosion except for using maximum instead of minimum, also, the structuring element is reflected about the origin. Since dilation replaces the current pixel with the maximum value from the neighborhood, the effects are opposite to that of the dilation algorithm. That is, the resultant image after dilation with a flat SE is brighter than the original one.

In developing the algorithms for dilation and erosion, the SE of disk type and radius 2, i.e., SE (2), is used on images of size 512x512. The morphological operators of erosion and dilation were run on an Intel i5 quad-core processor which is configured to run at a maximum frequency of 2.50GHz.

Figure 4.1 Original Lena image and the eroded image for SE(2).

The morphological operator Erode was first implemented as a MATLAB function and its run-time was profiled through the MATLAB profiler. The results are shown in Figure 4.2. We can see that for the 512x512 Lena image the erosion function takes about 5.571 seconds. Start Profiling Run this code: crap = erode(imread('lena.jpg'),se)

#### Profile Summary

Generated 13-Oct-2014 19:50:07 using cpu time.

| Function Name                             | <u>Calls</u> | <u>Total Time</u> | <u>Self Time</u> * | Total Time Plot<br>(dark band = self time) |

|-------------------------------------------|--------------|-------------------|--------------------|--------------------------------------------|

| erode                                     | 1            | 5.577 s           | 5.571 s            |                                            |

| images\private\imapplymatrixc (MEX-file)  | 1            | 0.003 s           | 0.003 s            |                                            |

| imagesci\private\imftype                  | 1            | 0.002 s           | 0.001 s            |                                            |

| imagesci\private\isjpg                    | 1            | 0 s               | 0.000 s            |                                            |

| imagesci\private\jpeg_depth (MEX-file)    | 1            | 0 s               | 0.000 s            |                                            |

| imagesci\private\readjpg                  | 1            | 0.008 s           | 0.000 s            |                                            |

| <u>imagesci\private\rjpg8c</u> (MEX-file) | 1            | 0.008 s           | 0.008 s            |                                            |

| imapplymatrix                             | 1            | 0.005 s           | 0.002 s            |                                            |

| imapplymatrix>checkOutputClass            | 1            | 0 s               | 0.000 s            |                                            |

| imapplymatrix>parseVarargin               | 1            | 0 s               | 0.000 s            |                                            |

| <u>imformats</u>                          | 1            | 0.001 s           | 0.000 s            |                                            |

| imformats>find_in_registry                | 1            | 0.001 s           | 0.001 s            |                                            |

| imread                                    | 1            | 0.012 s           | 0.002 s            |                                            |

| imread>parse_inputs                       | 1            | 0 s               | 0.000 s            |                                            |

| <u>rgb2gray</u>                           | 1            | 0.006 s           | -0.000 s           |                                            |

| rgb2gray>parse_inputs                     | 1            | 0.001 s           | 0.001 s            |                                            |

Self time is the time spent in a function excluding the time spent in its child functions. Self time also includes overhead resulting from the process of profiling.

# Figure 4.2 Matlab runtime profile of the Erosion function.

Figure 4.3 Original Lena image and the dilated image for SE(2).

#### Profile Summary

Generated 13-Oct-2014 22:18:59 using cpu time.

| Function Name                                 | <u>Calls</u> | <u>Total Time</u> | Self Time* | Total Time Plot<br>(dark band = self time) |

|-----------------------------------------------|--------------|-------------------|------------|--------------------------------------------|

| <u>dilate</u>                                 | 1            | 4.200 s           | 4.194 s    |                                            |

| images\private\imapplymatrixc (MEX-file)      | 1            | 0.003 s           | 0.003 s    |                                            |

| imagesci\private\imftype                      | 1            | 0.002 s           | 0.000 s    |                                            |

| imagesci\private\isjpg                        | 1            | 0 s               | 0.000 s    |                                            |

| <u>imagesci\private\jpeg_depth</u> (MEX-file) | 1            | 0 s               | 0.000 s    |                                            |

| imagesci\private\readjpg                      | 1            | 0.007 s           | 0.000 s    |                                            |

| <u>imagesci\private\rjpg8c</u> (MEX-file)     | 1            | 0.007 s           | 0.007 s    |                                            |

| imapplymatrix                                 | 1            | 0.005 s           | 0.002 s    |                                            |

| imapplymatrix>checkOutputClass                | 1            | 0 s               | 0.000 s    |                                            |

| imapplymatrix>parseVarargin                   | 1            | 0 s               | 0.000 s    |                                            |

| imformats                                     | 1            | 0.002 s           | 0.001 s    |                                            |

| imformats>find_in_registry                    | 1            | 0.001 s           | 0.001 s    |                                            |

| imread                                        | 1            | 0.012 s           | 0.002 s    |                                            |

| imread>parse_inputs                           | 1            | 0.001 s           | 0.001 s    |                                            |

| rgb2gray                                      | 1            | 0.006 s           | 0.000 s    |                                            |

| rgb2gray>parse_inputs                         | 1            | 0.001 s           | 0.001 s    |                                            |

Self time is the time spent in a function excluding the time spent in its child functions. Self time also includes overhead resulting from the process of profiling.

Figure 4.4 Matlab runtime profile of the Dilation function.

Erosion and dilation by themselves are not very useful in gray-scale image processing. These operations become powerful when used in combination to develop high-level algorithms. Some of the properties of Erosion and Dilation are [13]:

- Erosion is in general not commutative:  $A \ominus B \neq B \ominus A$ .

- Dilation is associative:  $A \bigoplus (B \bigoplus C) = (A \bigoplus B) \bigoplus C$ , for any sets A, B, and C.

- Translation is invariant: Ax  $\bigoplus B = (A \bigoplus B)x$  and Ax  $\bigoplus B = (A \bigoplus B)x$ .

- Dilation and erosion are in a sense dual operators. Dilation can be defined as the erosion of the complement of a set. If A<sup>c</sup> denotes the complement of the set A (i.e., a € Ac implies a does not belong to A), then the dilation of a set A by a set B is equivalent to the complement of eroding A<sup>c</sup> by set B. In other words,

# $A \oplus B = (A^c \Theta B)^c$ .

- Dilation and erosion are not inverses of each other.

- Dilation distributes over union.

- Erosion distributes over intersection.

- The erosion of a set A by the union of two sets B and C is the same as the intersection of the erosion of A by B and the erosion of A by C.

- Repeated erosion of a set A by sets B0, ..., Bn, is the same as the erosion of A by the dilation of the sets B0, ..., Bn.

The last four properties are called decomposition theorems. These properties of dilation and erosion can be utilized in the parallel implementation of morphological functions. That is, a large SE can be decomposed into smaller subsets allowing efficient and parallel implementations.

For example, if we have to dilate a set A by a set B, then we need to visit every possible neighborhood of A as defined by the size of set B. This makes the algorithm unsuitable for parallel implementation. However, using the above mentioned property, if we can decompose the set B into smaller subsets, then the computations can be performed in parallel. For FPGAs, we can take advantage of the concurrency of hardware to spawn such parallel functions which can complete the computation in a small number of clock cycles. In modern multi-core digital computers, such parallel computations are performed through thread-based implementations where a function is split over several threads toward parallel computation.

# 4.2 Opening

For binary and gray-scale images, the opening of image f by SE b is defined as the erosion of f by b followed by the dilation of the result by b. The opening operation is shown in Equation 4.5.

$$\mathbf{f} \frown \mathbf{b} = (\mathbf{f} \boxdot \mathbf{b}) \bigoplus \mathbf{b} \tag{4.5}$$

### 4.3 Closing

For binary and gray-scale images, the closing of image f by SE b is defined as the dilation of f by b followed by the erosion of the result by b. The closing operation is shown in Equation 4.6.

$$\mathbf{f} \bullet \mathbf{b} = (\mathbf{f} \bigoplus \mathbf{b}) \bigoplus \mathbf{b} \tag{4.6}$$

The opening and closing for gray-scale images are duals with respect to complementation and SE reflectioner, as per equation 4.7.

$$(\mathbf{f} \bullet \mathbf{b})^{c} = \mathbf{f}^{c} \bullet \mathbf{b}^{\wedge}$$

$$(\mathbf{f} \bullet \mathbf{b})^{c} = \mathbf{f}^{c} \bullet \mathbf{b}^{\wedge}$$

$$\mathbf{f}^{c} = -\mathbf{f}(\mathbf{x}, \mathbf{y})$$

$$-(\mathbf{f} \bullet \mathbf{b}) = (-\mathbf{f} \bullet \mathbf{b}^{\wedge})$$

(4.7)

$$-(f \circ b) = (-f \bullet b^{\wedge})$$

The opening and closing of images has a simple geometrical interpretation. The Image f(x,y) can be viewed as a 3D surface, where the intensity values of pixels are interpreted as heights over the xy-plane [12]. Then, the opening of f by b can be interpreted as "pushing" SE b up from below against the under surface of f. At each location of the origin of b, the opening is the highest value reached by any part of b as it pushes against the under surface of f. The complete opening is then the set of all such values obtained by having the origin of b visit every (x, y) coordinate of f. See Figure 4.5.

**Figure 4.5** Geometrical interpretation of the Opening and Closing operations. *Source*: [12].

Since the opening operation first erodes the image before dilation, the overall effect of the opening operation is that the intensity of all bright features decreases, depending on the sizes of the features compared to the SE. In the opening operation, erosion has a negligible effect on dark features and, hence, the effect on the background

is negligible. The overall effect of the closing operation is that the dark features get attenuated, with the background unaffected. In developing the algorithms for opening and closing, SE(2) is used for images of size 512x512. The results of the opening operations are shown in Figures 4.6 and 4.8. Performance results are shown in Figure 4.7.

Figure 4.6 Original Lena image and the results of the Opening operation for SE(2).

| Profile Summary<br>Generated 14-Oct-2014 06:18:13 using cpu time. |              |                   |            |                                            |  |  |  |  |

|-------------------------------------------------------------------|--------------|-------------------|------------|--------------------------------------------|--|--|--|--|