### **Copyright Warning & Restrictions**

The copyright law of the United States (Title 17, United States Code) governs the making of photocopies or other reproductions of copyrighted material.

Under certain conditions specified in the law, libraries and archives are authorized to furnish a photocopy or other reproduction. One of these specified conditions is that the photocopy or reproduction is not to be "used for any purpose other than private study, scholarship, or research." If a, user makes a request for, or later uses, a photocopy or reproduction for purposes in excess of "fair use" that user may be liable for copyright infringement,

This institution reserves the right to refuse to accept a copying order if, in its judgment, fulfillment of the order would involve violation of copyright law.

Please Note: The author retains the copyright while the New Jersey Institute of Technology reserves the right to distribute this thesis or dissertation

Printing note: If you do not wish to print this page, then select "Pages from: first page # to: last page #" on the print dialog screen

The Van Houten library has removed some of the personal information and all signatures from the approval page and biographical sketches of theses and dissertations in order to protect the identity of NJIT graduates and faculty.

#### **ABSTRACT**

### VECTOR COPROCESSOR SHARING TECHNIQUES FOR MULTICORES: PERFORMANCE AND ENERGY GAINS

### by Spiridon Florin Beldianu

Vector Processors (VPs) created the breakthroughs needed for the emergence of computational science many years ago. All commercial computing architectures on the market today contain some form of vector or SIMD processing.

Many high-performance and embedded applications, often dealing with streams of data, cannot efficiently utilize dedicated vector processors for various reasons: limited percentage of sustained vector code due to substantial flow control; inherent small parallelism or the frequent involvement of operating system tasks; varying vector length across applications or within a single application; data dependencies within short sequences of instructions, a problem further exacerbated without loop unrolling or other compiler optimization techniques. Additionally, existing rigid SIMD architectures cannot tolerate efficiently dynamic application environments with many cores that may require the runtime adjustment of assigned vector resources in order to operate at desired energy/performance levels.

To simultaneously alleviate these drawbacks of rigid lane-based VP architectures, while also releasing on-chip real estate for other important design choices, the *first part* of this research proposes three architectural contexts for the implementation of a shared vector coprocessor in multicore processors. Sharing an expensive resource among multiple cores increases the efficiency of the functional units and the overall system throughput. The *second part* of the dissertation regards the evaluation and

characterization of the three proposed shared vector architectures from the performance and power perspectives on an FPGA (Field-Programmable Gate Array) prototype. The third part of this work introduces performance and power estimation models based on observations deduced from the experimental results. The results show the opportunity to adaptively adjust the number of vector lanes assigned to individual cores or processing threads in order to minimize various energy-performance metrics on modern vectorcapable multicore processors that run applications with dynamic workloads. Therefore, the fourth part of this research focuses on the development of a fine-to-coarse grain power management technique and a relevant adaptive hardware/software infrastructure which dynamically adjusts the assigned VP resources (number of vector lanes) in order to minimize the energy consumption for applications with dynamic workloads. In order to remove the inherent limitations imposed by FPGA technologies, the fifth part of this work consists of implementing an ASIC (Application Specific Integrated Circuit) version of the shared VP towards precise performance-energy studies involving highperformance vector processing in multicore environments.

### VECTOR COPROCESSOR SHARING TECHNIQUES FOR MULTICORES: PERFORMANCE AND ENERGY GAINS

by Spiridon Florin Beldianu

A Dissertation

Submitted to the Faculty of

New Jersey Institute of Technology

in Partial Fulfillment of the Requirements for the Degree of

Doctor of Philosophy in Computer Engineering

**Department of Electrical and Computer Engineering**

May 2012

Copyright © 2012 by Spiridon Florin Beldianu

ALL RIGHTS RESERVED

.

### APPROVAL PAGE

# VECTOR COPROCESSOR SHARING TECHNIQUES FOR MULTICORES: PERFORMANCE AND ENERGY GAINS

### Spiridon Florin Beldianu

| Dr. Sotirios G. Ziavras, Dissertation Advisor Professor of Electrical and Computer Engineering, NJIT       | Date     |

|------------------------------------------------------------------------------------------------------------|----------|

| Tolessor of Electrical and Computer Engineering, 1971                                                      |          |

| Dr. Edwin Hou, Committee Member                                                                            | Date     |

| Associate Professor of Electrical and Computer Engineering, NJIT                                           | <i>-</i> |

| Dr. Durgamadhab Misra, Committee Member<br>Professor of Electrical and Computer Engineering, NJIT          | Date     |

| Or. Roberto Rojas-Cessa, Committee Member Associate Professor of Electrical and Computer Engineering, NJIT | Date     |

| Or. Alexandros V. Gerbessiotis, Committee Member                                                           | Date     |

#### **BIOGRAPHICAL SKETCH**

Author: Spiridon Florin Beldianu

Degree: Doctor of Philosophy

**Date:** May 2012

#### **Undergraduate and Graduate Education:**

- Doctor of Philosophy in Computer Engineering,

New Jersey Institute of Technology, Newark, NJ, 2012

- Master of Science in Electrical Engineering,

"Gheorghe Asachi" Technical University, Iasi, Romania, 2002

- Bachelor of Science in Electrical Engineering,

"Gheorghe Asachi" Technical University, Iasi, Romania, 2001

Major: Computer Engineering

#### **Presentations and Publications:**

- Beldianu, S. F., and Ziavras, S.G., "Performance-Energy Optimizations for Shared Vector Accelerators in Multicores" submitted to IEEE Transactions on Computers, 2012.

- Beldianu, S. F., and Ziavras, S.G., "ASIC Implementation of a Shared Vector Processor," to be submitted.

- Beldianu, S. F., and Ziavras, S.G., "Multicore-based Vector Coprocessor Sharing for Performance and Energy Gains," accepted for publication, ACM Transactions on Embedded Computing Systems, 2012.

- Beldianu, S. F., Dahlberg, C., Steele, T., and Ziavras, S.G., "Versatile Design of Shared Vector Coprocessors for Multicores" re-submitted to Elsevier Microprocessors and Microsystems: Embedded Hardware Design after a minor revision.

- Beldianu, S. F., and Ziavras, S.G., "On-chip Vector Coprocessor Sharing for Multicores," Parallel, Distributed and Network-Based Processing (PDP), 19th Euromicro International Conference on, pp. 431-438, 9-11 Feb. 2011.

- Beldianu, S.F., Rojas-Cessa, R., Oki, E., and Ziavras, S.G., "Scheduling for input-queued packet switches by a re-configurable parallel match evaluator," Communications Letters, IEEE, vol. 14, no. 4, pp. 357-359, April 2010.

- Beldianu, S.F., Rojas-Cessa, R., Oki, E., and Ziavras, S.G., "Re-Configurable Parallel Match Evaluators Applied to Scheduling Schemes for Input-Queued Packet Switches," Computer Communications and Networks, (ICCCN 2009) Proceedings of 18th International Conference on , pp. 1-6, 3-6 Aug. 2009.

To my Family, with Love and Gratitude.

Familiei mele, cu multă dragoste și recunoștință.

#### **ACKNOWLEDGMENT**

In the first place, I would like to express my deepest appreciation to my adviser, Dr. Sotirios Ziavras for being my mentor throughout my PhD research process. As my adviser, he guided and motivated me to find and pursue my research topic. Through long and daily talks in his office during the first semesters I was able to identify an original and innovative research direction. His extraordinary skills to inspire new and original ideas, his in depth knowledge in a vast number of areas and ability to provide up to date valuable references guided me throughout my entire research. Also, I would like to thank him for his time, energy and patience in reviewing my entire text work.

I would like to thank Dr. Roberto Rojas-Cessa for serving in my dissertation committee and also for giving me the opportunity to work on another research topic (scheduling in packet switches). Also, I would like to extend my special thanks to Dr. Durga Misra, Dr. Edwin Hou and Dr. Alexandros V. Gerbessiotis for serving as members in my dissertation committee. Dr. Misra's VLSI courses and Dr. Hou's Computer Algorithms course have been of great value to me.

Moreover, I am truly indebted and thankful to the ECE Department at NJIT. My work as TA and PhD student would not have been possible without the Teaching Assistant Award granted by the ECE Department.

Further thanks go to the staff of the office for international students, the staff of graduate studies, and the staff of the ECE Department for their advice, help and support with administrative matters during my PhD studies and work as Teaching Assistant.

Additionally, I would like to thank my friends, Vlad, Roxana, Ciprian and Viorica for all the great and unforgettable moments we shared together during these years.

Finally, I would like to express my deepest gratitude to my Family - for their support and understanding. I am deeply grateful to my wonderful parents, Georgeta and Spiridon, for their unconditional support and for always being there for me, and to my sister and my brother, Mariana and Liviu for being so close to me (geographically and, the most important, emotionally). My final and special acknowledgment goes to my love and best friend, my wife Oana for her patience and support throughout these years.

### TABLE OF CONTENTS

| C | hapter                                                       | Page |

|---|--------------------------------------------------------------|------|

| 1 | INTRODUCTION                                                 | 1    |

|   | 1.1 Multithreading and Multiprocessing                       | 1    |

|   | 1.2 Related Work on Vector Processors                        | 6    |

|   | 1.2.1 Modern Vector Processor Architectures                  | 6    |

|   | 1.2.2 Vector Processors for High Performance Computing (HPC) | 9    |

|   | 1.2.3 Emerging SIMD and Vector Architectures                 | 11   |

|   | 1.3 Motivation and Objectives                                | 14   |

| 2 | VECTOR COPROCESSOR SHARING                                   | 21   |

|   | 2.1 VP Sharing Techniques                                    | 21   |

|   | 2.1.1 Coarse-grain Temporal Sharing (CTS)                    | 23   |

|   | 2.1.2 Vector Lane Sharing (VLS)                              | 24   |

|   | 2.1.3 Fine-grain Temporal Sharing (FTS)                      | 25   |

|   | 2.2 VP Sharing Architecture                                  | 26   |

|   | 2.2.1 VP Scheduler                                           | 36   |

|   | 2.2.2 Additional Architectural Features                      | 43   |

|   | 2.3 Resource Consumption and Resource Scalability            | 47   |

| 3 | APPLICATIONS                                                 | 52   |

|   | 3.1 Software Implementation                                  | 52   |

|   | 3.2 Benchmarks                                               | 54   |

## **TABLE OF CONTENTS** (Continued)

| C | hapter                                                                       | Page  |

|---|------------------------------------------------------------------------------|-------|

| 4 | ANALYSIS OF PERFORMANCE AND POWER RESULTS                                    | 59    |

|   | 4.1 Evaluation Procedure                                                     | 59    |

|   | 4.2 Performance and Power Results                                            | . 60  |

|   | 4.3 Performance Scalability                                                  | 72    |

|   | 4.4 Guaranteed Quality of Service                                            | 74    |

|   | 4.5 Conclusions                                                              | 76    |

| 5 | PERFORMANCE AND POWER CHARACTERIZATION                                       | 77    |

|   | 5.1 Performance Model                                                        | 77    |

|   | 5.2 Dynamic Power Model                                                      | 81    |

|   | 5.3 Static Power Estimation                                                  | 87    |

|   | 5.4 Energy Performance Trade-off Preliminaries                               | 88    |

| 6 | PERFORMANCE-ENERGY OPTIMIZATIONS FOR SHARED VECTOR ACCELERATOR IN MULTICORES |       |

|   | 6.1 Related Work                                                             | 95    |

|   | 6.2 Total Energy Minimization                                                | 98    |

|   | 6.2.1 Dynamic Power Gating with Static Information (DPGS)                    | . 100 |

|   | 6.2.2 Adaptive Power Gating with Profiled Information (APGP)                 | 102   |

|   | 6.3 Simulation Model and Experimental Setup                                  | 108   |

|   | 6.3.1 Simulation Model                                                       | 108   |

|   | 6.3.2 Experimental Setup                                                     | 109   |

|   | 6.4 Experimental Results and Discussion                                      | 111   |

## **TABLE OF CONTENTS** (Continued)

| C | Chapter I                                       |       |

|---|-------------------------------------------------|-------|

|   | 6.5 Energy-Performance Trade-off Mechanism      | . 115 |

|   | 6.6 Conclusions                                 | 118   |

| 7 | ASIC IMPLEMENTATION OF THE VECTOR PROCESSOR     | 120   |

|   | 7.1 FPGA to ASIC Design Transition              | 120   |

|   | 7.2 ASIC Design Flow                            | 122   |

|   | 7.3 Design Exploration                          | . 126 |

|   | 7.4 ASIC Implementation Results                 | 129   |

|   | 7.5 Per VRF Bank Dynamic Power Gating           | 137   |

|   | 7.6 Energy Minimization with Quality of Service | 138   |

|   | 7.7 Conclusions                                 | 139   |

| 8 | CONCLUSIONS AND FUTURE WORK                     | 141   |

|   | 8.1 Conclusions                                 | 141   |

|   | 8.2 Future Work                                 | 144   |

| R | EFERENCES                                       | 149   |

### LIST OF TABLES

| Tabl | e                                                                                                                                                                                                                          | Page |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 2.1  | Load/Store (LDST) Instructions Summary                                                                                                                                                                                     | 33   |

| 2.2  | ALU Instructions Summary                                                                                                                                                                                                   | 33   |

| 2.3  | Examples of Vector Length and Number of Registers                                                                                                                                                                          | 35   |

| 2.4  | VP Control Instructions Summary                                                                                                                                                                                            | 39   |

| 2.5  | Examples of Transition for Scheduler States                                                                                                                                                                                | 41   |

| 2.6  | Resource Consumption in the Virtex-6 XC6VLX130T FPGA Device for a Configuration of Eight Lanes and Eight Memory Banks                                                                                                      |      |

| 4.1  | Performance Comparison for 32-tap FIR                                                                                                                                                                                      | 62   |

| 4.2  | Performance Comparison for 32-point Complex FFT                                                                                                                                                                            | 62   |

| 4.3  | Performance Comparison for Matrix Multiplication                                                                                                                                                                           | 63   |

| 4.4  | Performance Comparison for LU Decomposition                                                                                                                                                                                | 63   |

| 4.5  | Performance Comparison for Sparse Matrix Vector Multiplication (Eight Lanes and Eight Memory Banks Configuration); Sparse Matrix is <i>bcsstk13</i> ; Utilization and Time is Averaged Over one Dense Row (2003 Elements). | 64   |

| 4.6  | Average Execution Time (µs) for the 32-tap FIR Routine with Various Statistical Average Stall Ratios (VL=128; Unrolled Three Times)                                                                                        | 64   |

| 4.7  | Power Comparison for 32-tap FIR                                                                                                                                                                                            | 67   |

| 4.8  | Power Comparison for 32-point Complex FFT                                                                                                                                                                                  | 68   |

| 4.9  | Power Comparison for MM                                                                                                                                                                                                    | 68   |

| 4.10 | Power Comparison for LU Decomposition                                                                                                                                                                                      | 68   |

| 4.11 | Power Comparison for Sparse Matrix Vector Multiplication (Eight Lanes and Eight Memory Banks Configuration); Sparse Matrix is <i>bcsstk13</i> ; Utilization and Time is Averaged over One Dense Row (2003 Elements)        | 69   |

## LIST OF TABLES (Continued)

| Tabl | e                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Page |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 4.12 | Advantages and Disadvantages of the VP Sharing Schemes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 71   |

| 5.1  | Dynamic Power Model Equations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 84   |

| 5.2  | Mean Absolute Error for Dynamic Power Estimation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 85   |

| 5.3  | Static Power Breakdown for a 8×8 VP Design on XC6VLX130t Device (Internal Supply Voltage Relative to Ground is 1V; Junction Temperature is 85° C)                                                                                                                                                                                                                                                                                                                                                                                      | 87   |

| 6.1  | Time and Energy Overheads for PGC State Transition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 109  |

| 6.2  | Absolute and Relative Thresholds for APGP Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 110  |

| 7.1  | VP Components Replaced for the FPGA to ASIC Transition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 121  |

| 7.2  | VRF and Vector Memory Area and Power Consumption Figures for a Frequency of 1.0 GHz (CACTI 6.0 for a Feature Size of 40nm)                                                                                                                                                                                                                                                                                                                                                                                                             | 122  |

| 7.3  | Description of Various TSMC High Performance 40nm Process Corners (PC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 126  |

| 7.4  | Maximum Working Frequency for the Main VP Components                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 129  |

| 7.5  | Area and Power Results for Each VP Component, and Total VP Area for Various Configurations. The Standby Power is the Power Consumption when the VP is Idle (it Involves Leakage Power). The Maximum Power for Each Component Includes the Standby Power. The Percentage Figures are Relative to the First Module in the Hierarchy; i.e., ALU and LDST. The Power Consumption is Measured at 1.0 GHz Clock Frequency. The Total VP Area Includes the Vector Memory and One Equivalent Gate Comprises Four Transistors [TSMC 40nm, 2011] | 130  |

| 7.6  | Performance and Power Comparison for Various Application Kernels Running on the ASIC Implementation of the VP with Eight Lanes and Eight Memory Banks. The Applications are Presented in Chapter 3 (nu - no loop unrolling; u1-loop unrolled once). The Power Consumption is Measured After the System Reaches a Steady State                                                                                                                                                                                                          | 133  |

| 7.7  | Comparison of Power Coefficients for the FPGA (from Table 5.1) and ASIC Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 135  |

## LIST OF TABLES (Continued)

| Tabl | e I                                                                                                                         | Page |

|------|-----------------------------------------------------------------------------------------------------------------------------|------|

| 7.8  | Mean Absolute Error for Dynamic Power Estimation of the ASIC Implementation. The <i>w</i> Weights are Detailed in Table 5.1 | 135  |

| 7.9  | Number of VRF Banks Required by Each Scenario                                                                               | 137  |

| 7.10 | Power Efficiency Comparison with Other Streaming Processors                                                                 | 140  |

### LIST OF FIGURES

| Figu | re                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Page |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

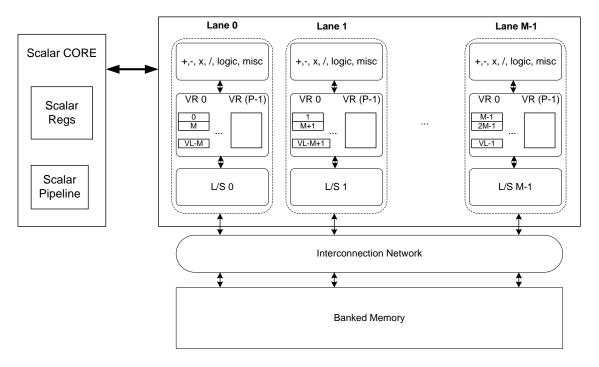

| 1.1  | Lane based modern Vector Processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 8    |

| 1.2  | Source code and the produced vector instructions (VL is 256 and the scalar instructions are omitted for simplicity)                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 8    |

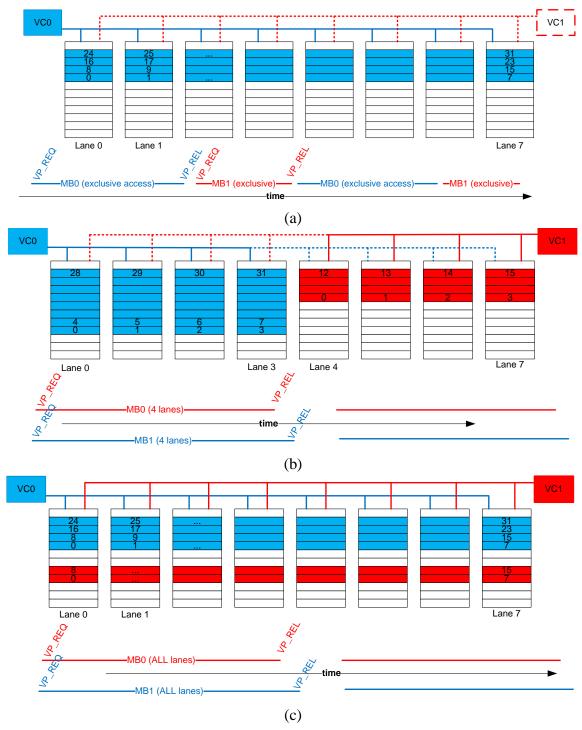

| 2.1  | VP sharing contexts: (a) Coarse-grain temporal (CTS) sharing; (b) Vector lane sharing (VLS); and (c) Fine-grain temporal sharing (FTS). Each lane contains a fixed number of pipeline stages; colored boxes show the busy pipeline stages in each lane and white boxes are unused pipeline stages (pipeline bubbles)                                                                                                                                                                                                                                                               | 27   |

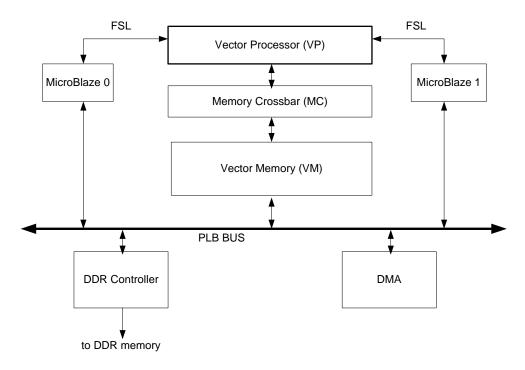

| 2.2  | Architecture of the FPGA-based VP sharing prototype (PLB: Xilinx Processor Local Bus, used mostly for data transfers via DMA control; FSL: Xilinx Fast Simplex Link)                                                                                                                                                                                                                                                                                                                                                                                                               | 28   |

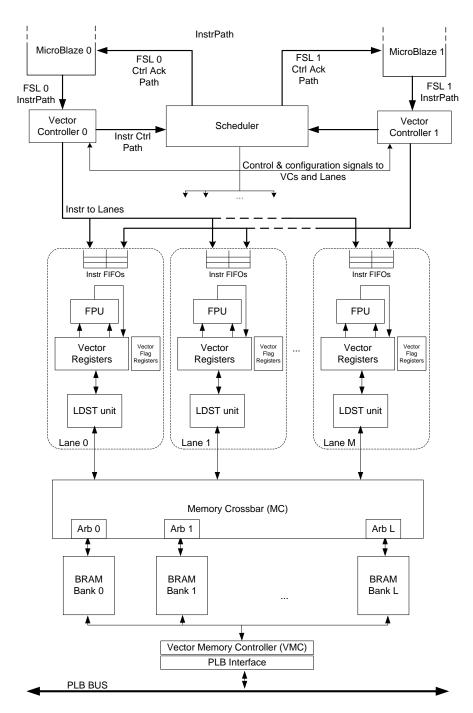

| 2.3  | M vector lanes shared between two MicroBlaze processors (FSL serves as the instruction path between a MicroBlaze and its associated Vector Controller, through the Scheduler; BRAM: Xilinx Block RAM; each MUX in the figure is part of the respective lane)                                                                                                                                                                                                                                                                                                                       | 29   |

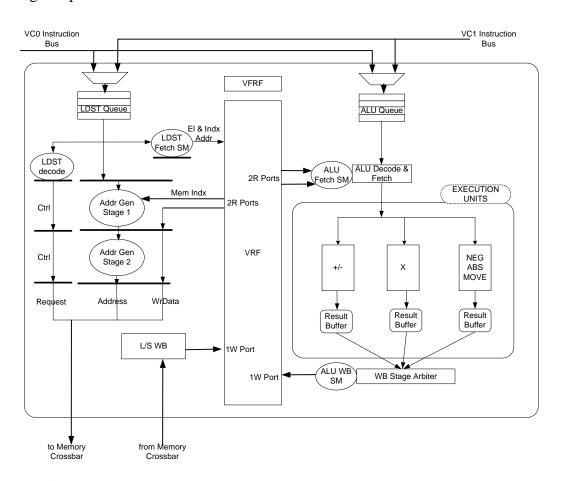

| 2.4  | Vector lane architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 32   |

| 2.5  | State Examples for the Scheduler (each cell in the figure contains the state of the corresponding lane: which VC it is assigned to, the total number of lanes assigned to that VC, and the lane index)                                                                                                                                                                                                                                                                                                                                                                             | 38   |

| 2.6  | Scheduler to MicroBlaze reply word in response to a VP_REQ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 38   |

| 2.7  | Scheduler algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 40   |

| 2.8  | Main MicroBlaze routine for CTS, FTS and VLS sharing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 42   |

| 2.9  | CTS vector sharing MicroBlaze routine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 43   |

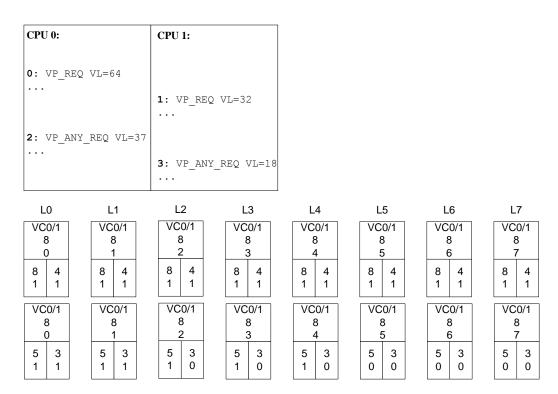

| 2.10 | The configuration state of each lane after instructions 0 and 1 are executed (top row) and after instructions 2 and 3 are executed (bottom row). Each lane configuration state contains (in each cell from top to bottom): VC ID(s) indicating from which VC the lane receives instructions; number of total lanes forming the VP; the lane index; per VC (VC0 or VC1) number of elements from each vector register in the lane; per VC mask bit required to mask the last operation of any instruction in each lane for vector lengths which are not multiple of number of lanes. | 45   |

| Figu | re                                                                                                                                                                                                                                                                                     | Page |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

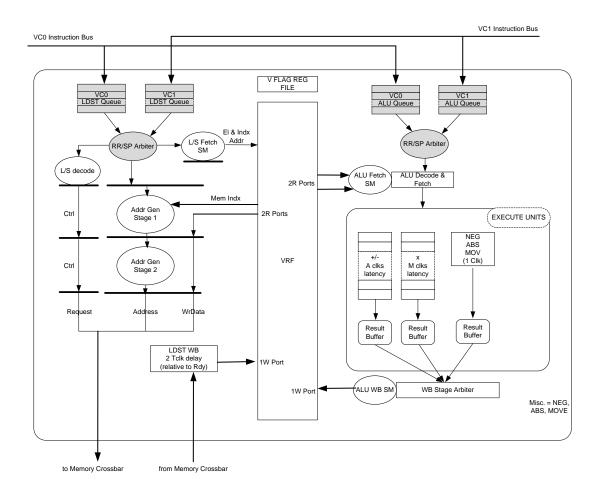

| 2.11 | Vector Lane architecture to support QoS and two VP instructions per cycle. The modifications from the baseline architecture are colored in gray                                                                                                                                        |      |

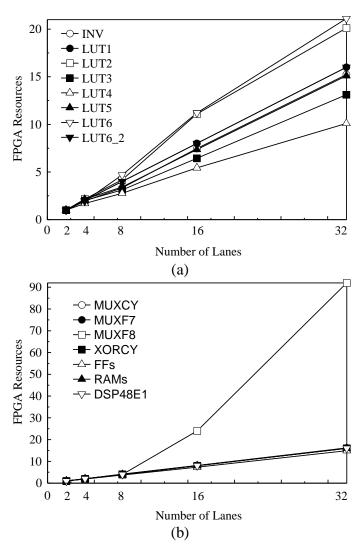

| 2.12 | Resource scaling for a vector processor with a number M of lanes equal with 2, 4, 8, 16 and 32 on XC6VLX130T FPGA device. Number of memory bank equals the number of lanes and the crossbar has the size M×M. All the numbers are normalized to the 2 lanes configuration numbers      |      |

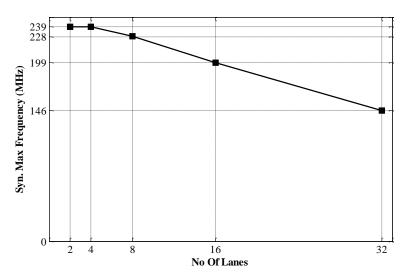

| 2.13 | Maximum Frequency after synthesis for a Vector Processor with 2, 4, 8, 16 and 32 number of lanes on XC6VLX130T FPGA device. Number of memory bank equals the number of lanes and the fully connected crossbar has size $M \times M$                                                    |      |

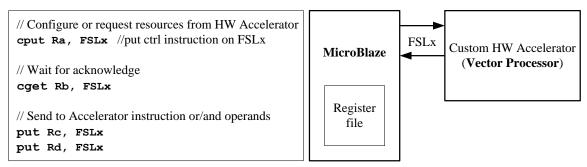

| 3.1  | FSL used with the Vector Processor                                                                                                                                                                                                                                                     | 53   |

| 3.2  | (a) DMA transfer utilities and (b) implementation of a FIR kernel                                                                                                                                                                                                                      | 55   |

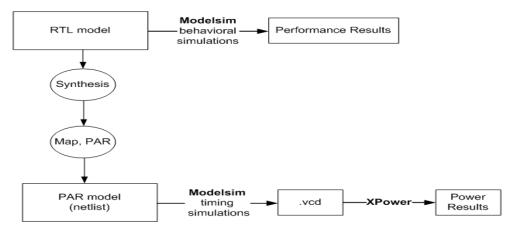

| 4.1  | Evaluation Procedure                                                                                                                                                                                                                                                                   | 59   |

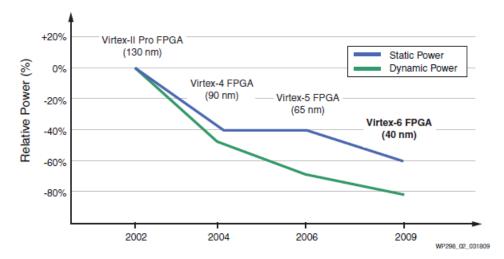

| 4.2  | Relative power reduction of different Xilinx Virtex FPGA families (taken from Xilinx wp298 white paper [Xilinx wpp, 2009])                                                                                                                                                             | 69   |

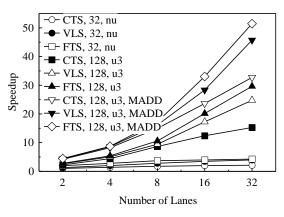

| 4.3  | FIR routine for 2, 4, 8, 16 and 32 lanes configuration. Each application consists in sharing context, Vector Length, unroll type (nu=no unroll; u3=unrolled three times), and with or without VMADD instruction extension                                                              |      |

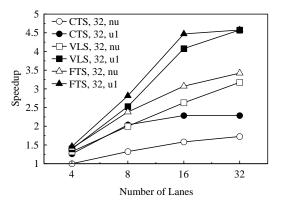

| 4.4  | FFT routine for 4, 8, 16 and 32 lanes configuration. Each application consists in sharing context, Vector Length, and unroll type (nu=no unroll; u1=unrolled once)                                                                                                                     |      |

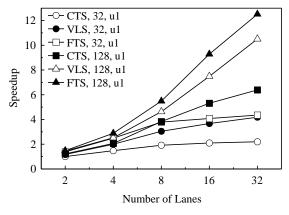

| 4.5  | MM routine for 2, 4, 8, 16 and 32 lanes configuration. Each application consists in sharing context, Vector Length, and unroll type (u1=unrolled once)                                                                                                                                 | 73   |

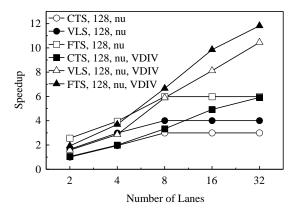

| 4.6  | LU decomposition routine for 2, 4, 8, 16 and 32 lanes configuration. Each application consists in sharing context, Vector Length, unroll type (nu=no unroll), and with or without VDIV instruction extension                                                                           |      |

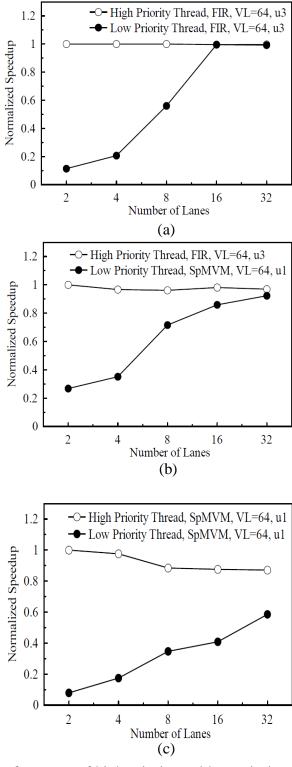

| 4.7  | Relative performance of high priority and low priority threads on a VP with a number <i>M</i> of lanes between 2 and 32 (M memory banks): (a) two FIR VL=64, u3; (b) FIR VL=64 u3 & SpMV_k1 VL=64 u1; (c) two SpMV_k1 VL=64 u1 (u1 – loop unrolled once; u3-loop unrolled three times) |      |

| Figu | ıre                                                                                                                                                                                                                                                                                    | Page |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

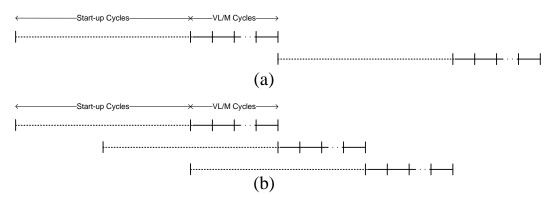

| 5.1  | Execution of a) two data dependent instructions; b) three instructions without data dependencies.                                                                                                                                                                                      | 78   |

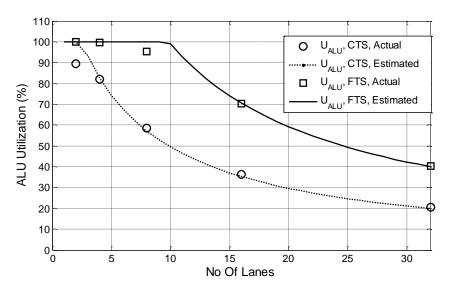

| 5.2  | Estimated and actual ALU utilization for FIR 32 with VL=64 and loop unrolled 3 times ( $SU_{ALU} = 13 \ IP_{ALU}^{CTS} = 1.5 \ IP_{ALU}^{FTS} = 3.0$ )                                                                                                                                 | 80   |

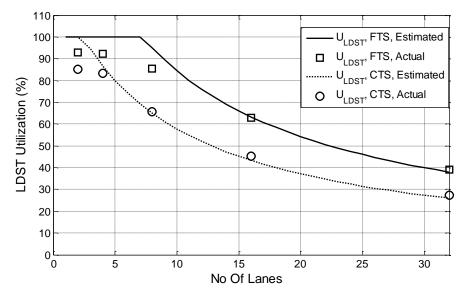

| 5.3  | Estimated and actual LDST utilization for SpMV (kernel 1) VL=64 and loop unrolled one time ( $SU_{LDST} = 8$ $IP_{LDST}^{CTS} = 1.3$ $IP_{LDST}^{FTS} = 1.9$ )                                                                                                                         | 81   |

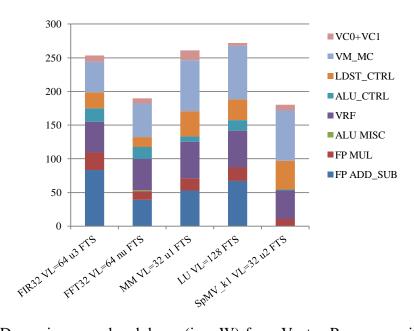

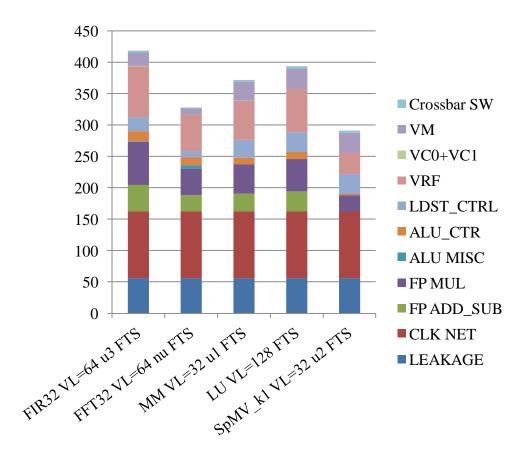

| 5.4  | Dynamic power breakdown (in mW) for a Vector Processor with eight lanes and eight memory banks running different application kernels                                                                                                                                                   | 82   |

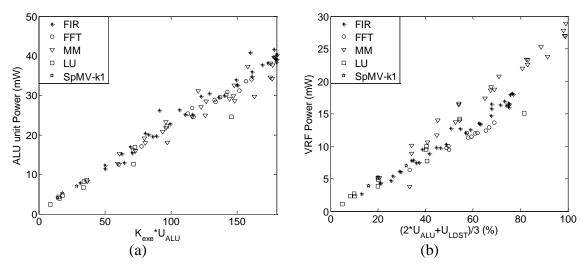

| 5.5  | a) ALU power consumption vs. ALU utilization ( $K_{exe} = \sum_{i} K_{exe(i)} w_{i}$ ); b) VRF power consumption vs. ALU and LDST utilization                                                                                                                                          | 83   |

| 5.6  | Memory Crossbar (MC) and Vector Memory (VM) power consumption vs. LDST utilization                                                                                                                                                                                                     | 83   |

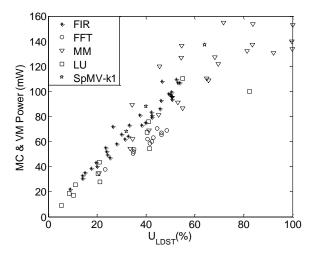

| 5.7  | Performance-Energy scalability opportunities in a lane-based VP system. Speed-up is displayed in black lines and static energy in red lines. Static power is shown in a doted blue line and its offset is caused by VP hardware components that do not scale (VC, MC, VM, buses, etc.) | 88   |

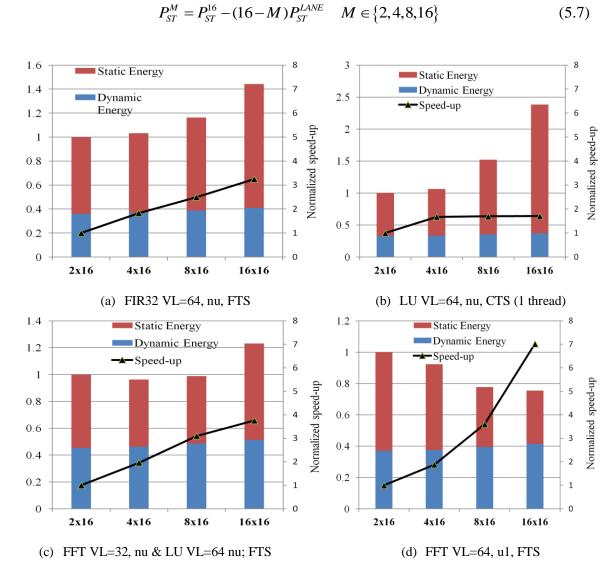

| 5.8  | Normalized energy consumption for a workload of 10K FP operations for various kernels (normalization is with respect to the 2x16 configuration; nu - no loop unrolling, u1- loop unrolled once)                                                                                        | 91   |

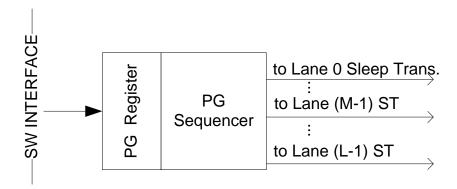

| 6.1  | Hardware support for DPGS scheme. In DPGS, the Power Gate (PG) Register is configured by software. ST: Sleep Transistor (Header or Footer)                                                                                                                                             | 101  |

| 6.2  | Interrupt routines to handle DPGS                                                                                                                                                                                                                                                      | 101  |

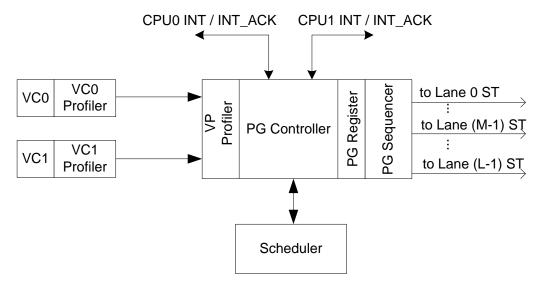

| 6.3  | Hardware support for APGP scheme. In APGP, the PG Register is configured by the PG Controller. The VP Profiler aggregates the utilizations from both VCs. ST: Sleep Transistor (Header or Footer)                                                                                      | 104  |

| Figu | re                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Page |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

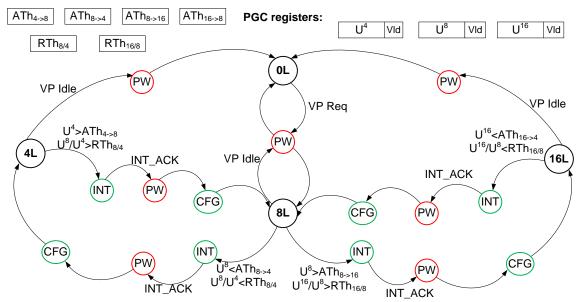

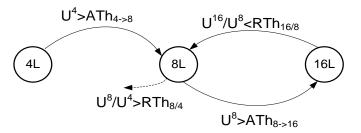

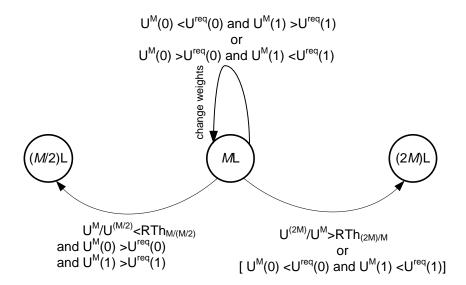

| 6.4  | PG Controller (PGC) state machine and PGC registers for state transitions under APGP. INT, PW and CFG are transitional VP (i.e., non-operating) states. 4L, 8L and 16L are stable VP operating states that represent the 4-, 8- and 16-lane VP configurations. $ML$ is a PGC state with $M$ active lanes, $M \in \{0,4,8,16\}$ ; INT is a PGC state where the PGC asserts an interrupt and waits for an Interrupt Acknowledge (INT_ACK); PW is a PGC state where some of the VP lanes are powered-up/down; CFG is a PGC state where the Scheduler is reconfigured to a new VP state. Threshold registers are fixed during runs and utilization registers are updated for every profile window. The registers store 8-bit integers. The Vld bit is used to show that the utilization register $U^M$ , with $M=4$ , 8 or 16, for the $M$ -lane VP configuration does not contain an updated value |      |

| 6.5  | Example of state transitions upon a VP event                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 107  |

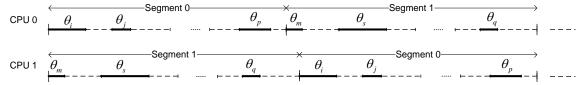

| 6.6  | VP threads issued by each scalar core with embedded idle times. Each thread contains 1000 segment runs. Each segment contains 10,000 kernel runs. A solid line shows the time spent by the core to issue the entire code for the corresponding kernel workload                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |

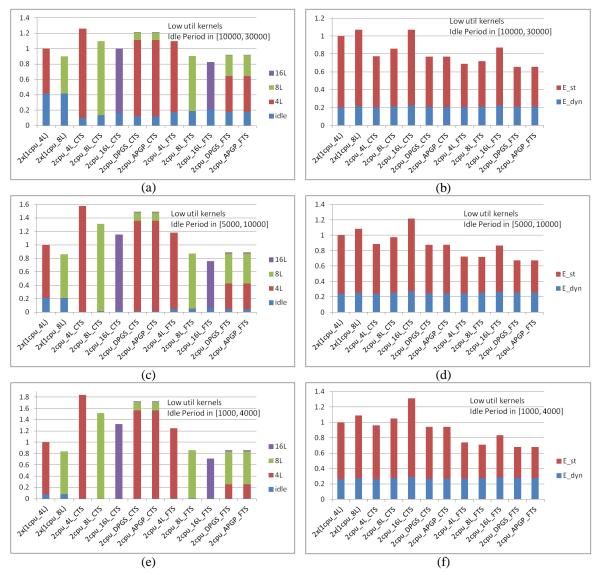

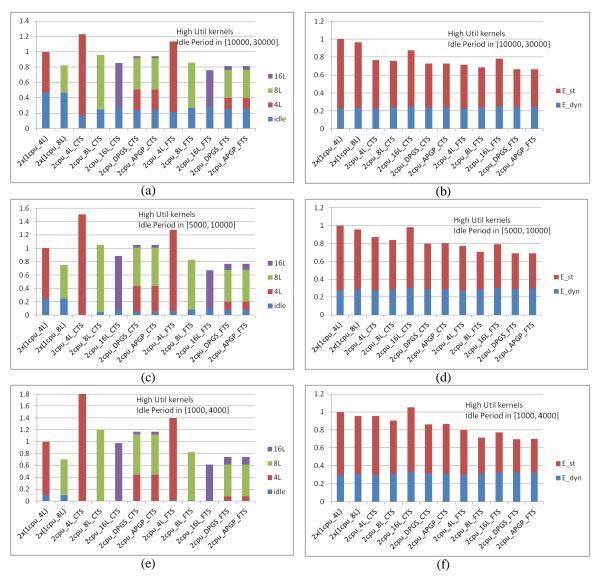

| 6.7  | Normalized execution time (a, c, e) and normalized energy consumption (b, d, f) where the majority of kernels in a thread have low ALU utilization, for various idle periods. The ratio of low to high utilization kernels in a thread is 4:1. E_st and E_dyn are the energy consumptions due to static and dynamic activities, respectively. "2x" means two scalar CPUs of the type that follows in parentheses, such as "(1cpu_4L)" which means one CPU having a dedicated VP with four lanes. Whenever CTS or FTS shows, it implies two CPUs with VP sharing                                                                                                                                                                                                                                                                                                                                 |      |

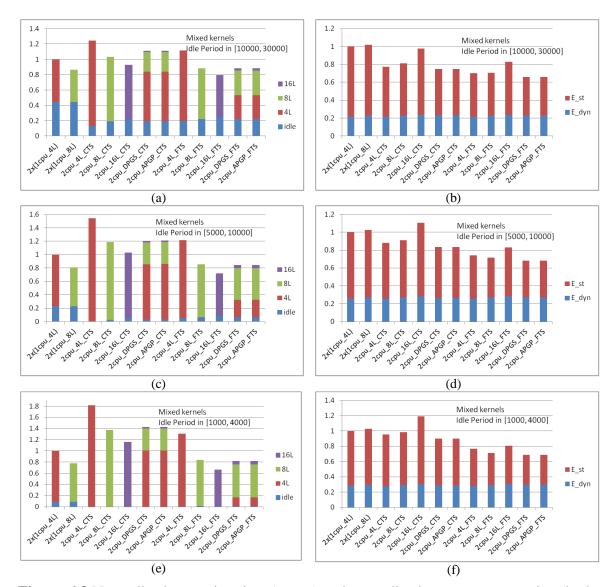

| 6.8  | Normalized execution time (a, c, e) and normalized energy consumption (b, d, f) for threads with mixed utilization kernels, for various idle periods. The ratio of low to high utilization kernels in a thread is 1:1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |

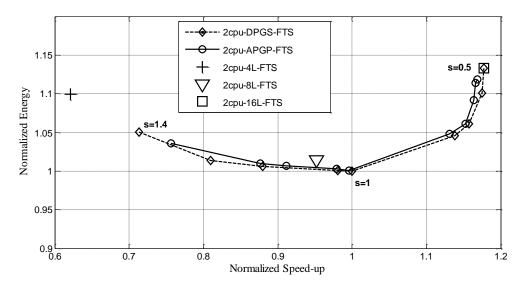

| 6.9  | Normalized execution time (a, c, e) and normalized energy consumption (b, d, f) for threads dominated by high utilization kernels, for various idle periods. The ratio of low to high utilization kernels in a thread is 1:4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |

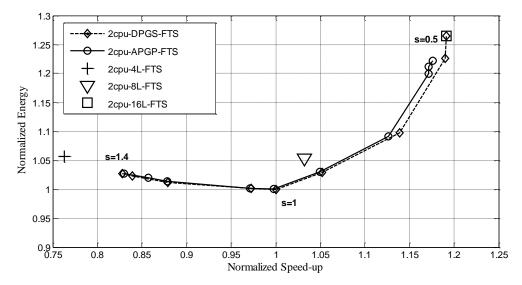

| 6.10 | Normalized energy vs. normalized execution time for threads dominated by low utilization kernels. The idle period is in the range [5000, 10000] VP clock cycles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      |

| Figu | re                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Page |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

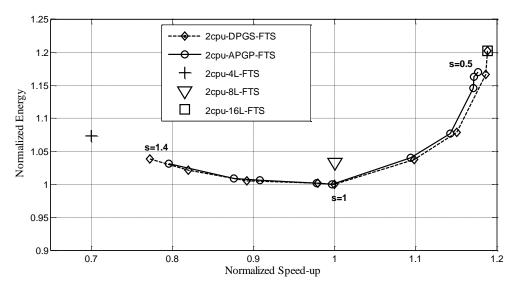

| 6.11 | Normalized energy vs. normalized execution time for threads dominated by mixed utilization kernels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 116  |

| 6.12 | Normalized energy vs. normalized execution time for threads dominated by high utilization kernels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 117  |

| 6.13 | Routine to minimize the energy consumption for a given kernel or pair of kernels requiring minimum performance. This routine runs continuously after a VP event                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 118  |

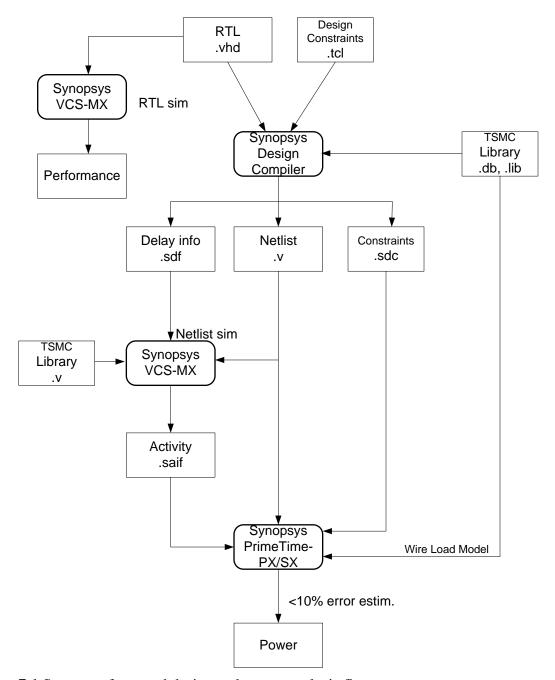

| 7.1  | Synopsys front-end design and power analysis flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 123  |

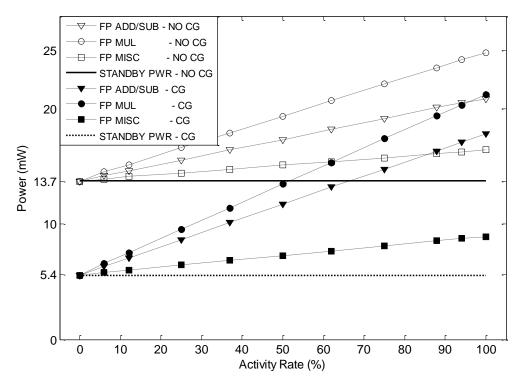

| 7.2  | Power consumption of the VP Lane execution unit for the ADD/SUB, MUL and MISC operations under various activity rates. FP ADD/SUB - Single Precision Floating Point Add/Subtract; FP MUL - Single Precision Floating Point Multiply; FP MISC - Single Precision Floating Point Absolute, Negate, Move and IntraLane Shift operations; NO CG - No Clock Gating support during synthesis; CG - with Clock Gating support during synthesis; STANDBY PWR - Power consumption when no operation is performed. The lane execution unit is implemented in the 40 nm TSMC process with VDD=1.21V and low voltage threshold. The power consumption is measured at 1 GHz clock frequency and after the system reaches a steady state of operations | 125  |

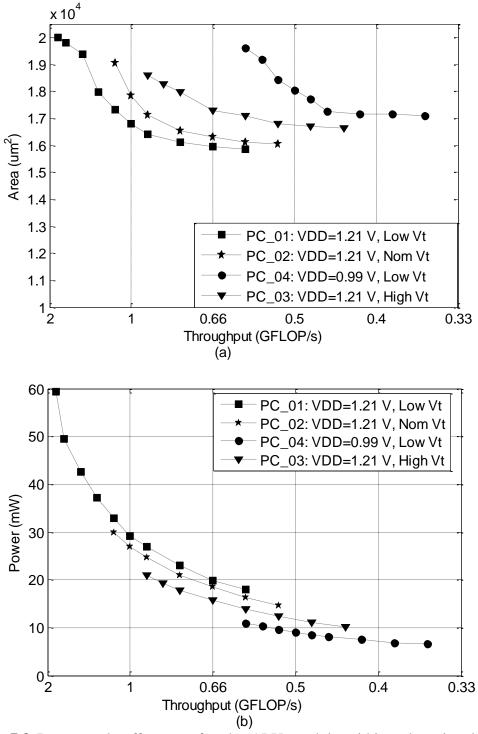

| 7.3  | Pareto trade-off curves for the ALU module within a lane involving: (a) performance and area; (b) performance and power. Details for the PC_01 to PC_04 process corners are shown in Table 7.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 128  |

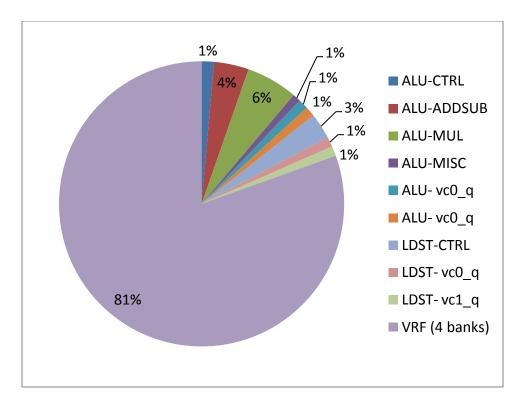

| 7.4  | VP lane area breakdown. A lane has four VRF banks, each one containing 128 32-bit elements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 131  |

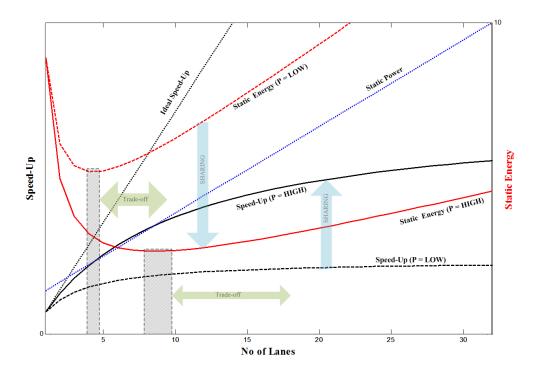

| 7.5  | Power breakdown (in mW) for a Vector Processor with eight lanes and eight memory banks running different application kernels. Even if contained in each VP component, the leakage and clock distribution network power consumption are displayed separately. The power consumption is measured at 1.0 GHz clock frequency                                                                                                                                                                                                                                                                                                                                                                                                                | 132  |

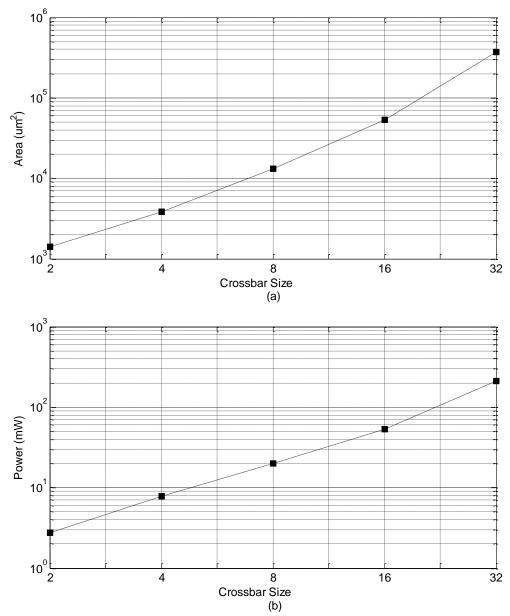

| 7.6  | Area (a) and Power consumption (b) for an N×N VP crossbar switch, where N is the number of masters. The crossbar contains the arbiters and the logic that supports shuffle operations. The design is synthesized to meet the constraint of 1 GHz for the clock frequency. The power consumption is extracted under maximum LDST utilization                                                                                                                                                                                                                                                                                                                                                                                              | 136  |

| Figure |                                                                                       | Page |

|--------|---------------------------------------------------------------------------------------|------|

| 7.7    | PG Controller state machine update for QoS support. $U^{M}(0)$ and $U^{M}(1)$ are the |      |

|        | monitored utilizations corresponding to VC0 and VC1 respectively and $U^{req}(0)$     |      |

|        | and $U^{req}(1)$ are the required utilizations for each thread                        | 139  |

#### LIST OF ABBREVIATIONS

ASIC Application Specific Integrated Circuit

CMP Chip Multi-Processor

CPU Central Processing Unit

CTS Coarse-grain Temporal Sharing

DLP Data Level Parallelism

DMA Direct Memory Access

DSP Digital Signal Processor

EPI Energy Per Instruction

FFT Fast Fourier Transform

FIR Finite Impulse Response

FPGA Field Programmable Gate Array

FSL Fast Simplex Link

FTS Fine-grain Temporal Sharing

GPU Graphical Processing Unit

HPC High Performance Computer

ILP Instruction Level Parallelism

IPC Instructions Per Cycle

MB MicroBlaze

MC Memory Crossbar

MM Matrix Multiplication

PLB Processor Local Bus

QoS Quality of Service

SaaS Software as a Service

SIMD Single Instruction Multiple Data

SIMT Single Instruction Multiple Threads

SMT Simultaneous Multithreading

SPM Scratch Pad Memory

SpMV Sparse Matrix Vector multiplication

TLB Translation Lookaside Buffer

VC Vector Controller

VLIW Very Long Instruction Word

VLS Vector Lane Sharing

VLSI Very Large Scale Integration

VM Vector Memory

VP Vector Processor

VRF Vector Register File

#### CHAPTER 1

#### INTRODUCTION

#### 1.1 Multithreading and Multiprocessing

The two important techniques for throughput-oriented computing are multithreading and multiprocessing.

Multithreading is used to increase the instruction level parallelism (ILP) handled by superscalar processors since it stalled more than a decade ago. Due to the difficulty of further speeding up an ILP-constrained single thread or program most computer systems actually multi-task multiple threads or programs. This technique improves the overall system throughput by increasing the average number of executed Instructions Per Cycle (IPC). The basic hardware multithreading scheme, namely coarse-grain, consists of switching one stalled thread with another one that is ready to execute [Kurihara et al., 1991; Agarwal, 1992]. The thread switch takes less than a few clock cycles (usually one) and the active thread does not share the functional pipeline with any other thread. The extra hardware cost is the replicated program registers and some control registers (that form the context). Quick context switching can potentially hide long latency stalls and increase the overall throughput and utilization of a processor's resources. Interleaved multithreading (fine-grain multithreading) takes advantage of the relative independence between threads and allows switching processor's context in any cycle [Horowitz et al., 1994]. In a given cycle a processor issues instructions from one of the threads, and in the next clock cycle it switches to a different thread context and issues instructions from the new thread. The primary advantage of interleaved multithreading is that it can better tolerate short latency stalls and increase the overall throughput. In addition to coarsegrain needs, hardware support consists of labeling each instruction with a thread ID, increasing the number of registers, and also incorporating larger caches and Translation Lookaside Buffers (TLB) in order to minimize the conflicts between different threads.

The most efficient type of multithreading, which is currently deployed in most of the desktop and server microprocessors, is Simultaneous Multithreading (SMT) [Tullsen et al., 1995; Eggers et al., 1997]. SMT alleviates limited per thread instruction level parallelism by allowing superscalar processors to issue instructions from multiple threads in every CPU cycle. The extra hardware support is rather minimal as compared with interleaved multithreading, and shared resources such as L1/L2 caches and TLBs have to be adjusted appropriately to accommodate larger numbers of active threads. Most of the current processing units are either high-end chip multiprocessors with SMT cores (e.g., Intel i3/5/7, with 2 or 4 threads per core; AMD Opteron series with 2 to 4 threads per core; IBM Power7 with 4 threads per core) or embedded single-core SMTs (e.g., Intel Atom Z series with two threads per core). A more aggressive approach, i.e., Thread-Level Speculation [Oplinger et al., 1999; Wang et al., 2002], allows the compiler to optimistically generate parallel threads even if the threads are not eventually proved to be independent. Minimal hardware support is needed to track at runtime data dependences between speculative threads, to buffer the speculative state and to recover from a failed speculation [Colohan et al., 2007].

Multiprocessing refers to the use of multiple central processing units (CPUs) coupled together in a computer system. There are many variations on the definition of multiprocessors. If not explicitly stated otherwise, the one that this work refers to is multiple CPUs on a single die, i.e., Chip Multi-Processors (CMPs) in a single VLSI chip.

Instead of focusing on super-scalar processors, processor designers have recently increased core counts for CMPs. The emergence of multicores is caused mainly by:

- (i) The fast evolution of VLSI technologies, such that the ever increasing number of transistors per unit area, made it possible to accommodate multiple cores on a single die (Moore's Law).

- (ii) Memory Wall: The CPU performance has increased much faster than the memory performance, and now the memory performance becomes the bottleneck in many applications. Traditional Symmetric Multi-Processor (SMP) systems share the memory bandwidth among processors, further reducing the performance. For these systems, the traditional way to improve the memory performance by incorporating many levels of even larger caches has reached the point of diminishing returns.

- (iii) Frequency Wall: To accommodate more threads and keep the frequency high, SMT requires deeper pipelines. Increasing the length of the pipeline increases the chances of resource conflicts in the instruction stream that will stall the pipeline or will cause a high cost for missed branches, thus reaching the point of diminishing returns [Chishti and Vijaykumar, 2008].

- (iv) *Power Wall*: As the SMT processor tries to accommodate more threads and increase the frequency, the power consumption per operation increases dramatically as compared with CMP. More threads in SMT require a larger register file, larger data and address caches (TLBs) and more complex control logic. This comes at the cost of dynamic power and, more recently substantially increased leakage power (due to larger area), with no substantial performance improvement as the number of threads increases. It has been shown [Sasanka et al., 2004] that as the number of simultaneous threads per core increases, the Energy Per Instruction (EPI) at the same performance point gets higher than the EPI for a CMP. The main cause is contention for limited resources among threads that produces extra cache and TLB misses and, thus, more energy consumption for the same IPC. Also, increasing the operational frequency in a SMT processor increases the power consumption due to at least two factors: (a)

a higher frequency requires either increasing the voltage supply level (Vdd) or decreasing the threshold voltage (Vth); as the dynamic power is proportional to the square of Vdd, the active power will eventually increase quadratically; (b) the static power also increases linearly with Vdd and decreases exponentially with Vth [Butts and Sohi, 2000]. Some decisions can be made that minimize the amount of interaction between threads. This minimization is accomplished by choosing threads that access different regions of the cache or different computational resources [Kihm et al., 2005].

- (v) Small time to market pressure and reduced cost requirements necessitate the reuse of off-the-shelf uni-processor IPs when building multiprocessors. The new IP for multicores consists of the glue logic (interconnection) and minimal verification primarily focusing on the interconnection logic. It is much easier to replicate already tested cores than just improving a single out-of-order superscalar core.

- (vi) The emergence of the Software as a Service (SaaS) paradigm [Wang et.al, 2011], is now deployed in datacenters. Amdahl's Law is often replaced by Gustafson's law [Gustafson, 1988] which states that problems with large and repetitive data sets can be efficiently parallelized (they have a high DLP or data level parallelism).

Since the mid 2000's designers have increased the number of cores per chip rather than focusing on single-core performance. However, a new limit on multicore scaling will soon make this approach less useful, thus creating a transistor utility economics wall in relation to underutilized resources (called dark silicon). A recent study, that takes into consideration the device, core and CMP scaling models, showed that regardless of chip organization and topology, a large area of the chip will have to be powered down [Esmaeilzadeh et al., 2011]. For example, at 22 nm (to be available soon), the study suggests that 21% of a chip must be off, and this number grows to more than 50% with 8 nm. Moreover, according to their unified model, in the next decade only an average

speedup of eight will be possible for common parallel workloads; this will yield a substantial gap (up to 24) between the expected and actual performance; ideally, each newer generation silicon technology node is currently expected to double the performance.

Scaling the performance and energy could be achieved by:

- (i) Scaling the off-chip memory bandwidth capacity and the overheads associated with the process of moving data [Rogers et al., 2009].

- (ii) Reducing the energy overheads associated with useful operations [Horowitz et al., 2011]. This further requires reducing the energy overheads on the instruction path and the instruction memory hierarchy.

The first requirement could be addressed by using a heterogeneous memory hierarchy, that is, by employing memories that are not fully cacheable but rather explicitly managed. This category includes Scratch Pad Memories (SPM) or Local Stores (LS) [Flachs et al., 2005]. SPM reduces the energy consumption by almost 40% and the area by 34% for applications with regular memory accesses [Banakar et al., 2002; Milidonis et al., 2009]. Unlike caches, it is the programmer's responsibility (possibly with the help of the compiler) to explicitly manage data transfers between the main memory and the SPM. The applications that can fully use SPM are scientific and multimedia (streaming) applications where data movement could be managed explicitly and uniformly between off-chip memory and stream processors. Applications that have a low degree of parallelism could be mapped to scalar cores such that the memory transfers can make use of the cache [Kudlur et al., 2008].

The second problem could be addressed by using more specialized cores for each task based on heterogeneous computing. This category includes ASIC custom designs

specialized for a single application, like video compression and encryption engines, Vector Processors (VP) operating in the Single Instruction Multiple Data (SIMD) mode, Graphical Processing Units (GPUs) operating in the Single Instruction Multiple Threads (SIMT) mode, and Digital Signal Processors (DSPs).

#### 1.2 Related Work on Vector Processors

Vector code offers a compact, predictable, single-threaded programming model, with the possibility for loop unrolling to be performed directly at the hardware level under branch prediction. Moreover, the already compiled vector object code can directly benefit from new implementations even if some rescheduling is required for optimal performance on new SIMD micro-architectures. In recent years, SIMD extensions have become ubiquitous. Even scalar processors on the market today contain them in some form. Since the focus of this work is the vector processor architecture, an overview of this architecture is presented in the following sections. Section 1.2.1 presents the architecture of a modern vector processor, Section 1.2.2 presents an overview of high performance applications and vector processors used in supercomputers and Section 1.2.3 presents the emerging SIMD architectures targeting embedded applications.

#### 1.2.1 Modern Vector Processor Architectures

Vector Computers created the breakthrough needed for the emergence of computational science. The vector architecture was first fully exploited with Cray-1 in 1976 [Russell, 1978]. Cray had a register file with eight vector registers which held 64 64-bit words each and achieved a peak performance of 240 MFLOPs. In the 1980s NEC introduced its first vector system (SX-2) which was an improved version of Cray-1. The vector processor

simultaneously performed mathematical operations on multiple data elements from an array, called vector, by instructions named vector instructions. A modern vector processor falls into the SIMD category, and usually consists of a scalar unit and a vector unit as shown in Figure 1.1. The scalar unit is similar to an ordinary pipelined scalar processor which executes scalar instructions for control functions, the unvectorizable part of the operating system and application code. The vector unit consists of vector registers, pipelined arithmetic unit(s) and a pipelined Load/Store unit (L/S). Most of the modern vector processors implement a register-bank scheme for the vector register file (VRF) [Asanovic, 1998]. By interleaving vector register storage across multiple banks, the number of ports required on each bank can be reduced. A separate interconnection network connects banks and arithmetic pipeline ports. In effect, all of these bank partitioning schemes reduce the connectivity between element storage and arithmetic unit ports. As depicted in Figure 1.1, in a lane based modern Vector Processor, a single vector register (VR0) with length VL can be low interleaved across M lanes resulting into VL/M elements from each vector register in a single lane. A vector lane is an independent vector subunit containing its own bus interfaces, processing units and vector registers; during its operation it does not compete for resources with any other lane, except for external accesses going to the same memory modules. As a note, the maximum number of elements to be held in a vector register, Maximum Vector Length, is 64 in Cray-1 and 256 in the NEC SX systems. The pipelined arithmetic units from each lane usually implement Add, Multiply, Divide, Logical and Shift operations in a pipelined fashion, in which the vector data are input from vector registers and the results are output every clock cycle into the vector registers.

Figure 1.1 Lane based modern Vector Processor architecture.

Vectorization is the process of converting a computer program to a sequence of vector instructions for executing on a vector processor. Figure 1.2 shows a for loop in C code and the produced vector instructions. The vector length is 256 and each vector instruction processes 256 elements.

**Figure 1.2** Source code and the produced vector instructions (VL is 256 and the scalar instructions are omitted for simplicity).

#### 1.2.2 Vector Processors for High Performance Computing (HPC)

Computer modeling and simulations of physical phenomena and engineered systems have become widely spread in supporting theory and experimentation. High Performance Computers (HPC) are used in weather and climate research, bioscience, energy, military, automotive and many other engineering fields.