# **Copyright Warning & Restrictions**

The copyright law of the United States (Title 17, United States Code) governs the making of photocopies or other reproductions of copyrighted material.

Under certain conditions specified in the law, libraries and archives are authorized to furnish a photocopy or other reproduction. One of these specified conditions is that the photocopy or reproduction is not to be "used for any purpose other than private study, scholarship, or research." If a, user makes a request for, or later uses, a photocopy or reproduction for purposes in excess of "fair use" that user may be liable for copyright infringement,

This institution reserves the right to refuse to accept a copying order if, in its judgment, fulfillment of the order would involve violation of copyright law.

Please Note: The author retains the copyright while the New Jersey Institute of Technology reserves the right to distribute this thesis or dissertation

Printing note: If you do not wish to print this page, then select "Pages from: first page # to: last page #" on the print dialog screen

The Van Houten library has removed some of the personal information and all signatures from the approval page and biographical sketches of theses and dissertations in order to protect the identity of NJIT graduates and faculty.

#### ABSTRACT

#### TiN/HfO<sub>2</sub>/SiO<sub>2</sub>/Si GATE STACKS RELIABILITY: CONTRIBUTION OF HfO<sub>2</sub> AND INTERFACIAL SiO<sub>2</sub> LAYER

#### by Nilufa Rahim

Hafnium Oxide based gate stacks are considered to be the potential candidates to replace  $SiO_2$  in complementary metal-oxide-semiconductor (CMOS), as they reduce the gate leakage by over 100 times while keeping the device performance intact. Even though considerable performance improvement has been achieved, reliability of high- $\kappa$  devices for the next generation of transistors (45nm and beyond) which has an interfacial layer (IL: typically SiO<sub>2</sub>) between high- $\kappa$  and the substrate, needs to be investigated. To understand the breakdown mechanism of high- $\kappa$ /SiO<sub>2</sub> gate stack completely, it is important to study this multi-layer structure extensively. For example, (i) the role of SiO<sub>2</sub> interfacial layers and bulk high- $\kappa$  gate dielectrics without any interfacial layer can be investigated separately while maintaining same growth conditions; (ii) the evolution of breakdown process can be studied through stress induced leakage current (SILC); (iii) relationship of various degradation mechanisms such as negative bias temperature instability (NBTI) with that of the dielectric breakdown; and (iv) a fast evaluation process to estimate statistical breakdown distribution.

In this dissertation a comparative study was conducted to investigate individual breakdown characteristics of high- $\kappa$ /IL (ISSG SiO<sub>2</sub>)/metal gate stacks, in-situ steam generated (ISSG)-SiO<sub>2</sub> MOS structures and HfO<sub>2</sub>-only metal-insulator-metal (MIM) capacitors. Experimental results indicate that after constant voltage stress (CVS) identical degradation for progressive breakdown and SILC were observed in high- $\kappa$ /IL and SiO<sub>2</sub>-

only MOS devices, but  $HfO_2$ -only MIM capacitors showed insignificant SILC and progressive breakdown until it went into hard breakdown. Based on the observed SILC behavior and charge-to-breakdown (Q<sub>BD</sub>), it was inferred that interfacial layer initiates progressive breakdown of metal gate/high- $\kappa$  gate stacks at room temperature. From normalized SILC ( $\Delta J_g/J_{g0}$ ) at accelerated temperature and activation energy of the timeto-breakdown (T<sub>BD</sub>), it was observed that IL initiates the gate stack breakdown at higher temperatures as well. A quantitative agreement was observed for key parameters of NBTI and time dependent dielectric breakdown (TDDB) such as the activation energies of threshold voltage change and SILC. The quality and thickness variation of the IL causes similar degradation on both NBTI and TDDB indicating that mechanism of these two reliability issues are related due to creation of identical defect types in the IL.

CVS was used to investigate the statistical distribution of  $T_{BD}$ , defined as soft or first breakdown where small sample size was considered. As  $T_{BD}$  followed Weibull distribution, large sample size was not required. Since the failure process in static random access memory (SRAM) is typically predicted by the realistic TDDB model based on gate leakage current ( $I_{FAIL}$ ) rather than the conventional first breakdown criterion, the relevant failure distributions at  $I_{FAIL}$  are non-Weibull including the progressive breakdown (PBD) phase for high- $\kappa$ /metal gate dielectrics. A new methodology using hybrid two-stage stresses has been developed to study progressive breakdown phase further for high- $\kappa$  and SiO<sub>2</sub>. It is demonstrated that VRS can be used effectively for quantitative reliability studies of progressive breakdown phase and final breakdown of high- $\kappa$  and other dielectric materials; thus it can replace the time-consuming CVS measurements as an efficient methodology and reduce the resources manufacturing cost.

## TiN/HfO<sub>2</sub>/SiO<sub>2</sub>/Si GATE STACKS RELIABILITY: CONTRIBUTION OF HfO<sub>2</sub> AND INTERFACIAL SiO<sub>2</sub> LAYER

by Nilufa Rahim

A Dissertation Submitted to the Faculty of New Jersey Institute of Technology in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy in Electrical Engineering

**Department of Electrical and Computer Engineering**

January 2011

Copyright © 2011 by Nilufa Rahim

# ALL RIGHTS RESERVED

## **APPROVAL PAGE**

# TiN/HfO<sub>2</sub>/SiO<sub>2</sub>/Si GATE STACKS RELIABILITY: CONTRIBUTION OF HfO<sub>2</sub> AND INTERFACIAL SiO<sub>2</sub> LAYER

### Nilufa Rahim

| Dr. Durgamadhab Misra, Dissertation Advisor<br>Professor of Electrical and Computer Engineering, NJIT | Date |

|-------------------------------------------------------------------------------------------------------|------|

| Dr. Haim Grebel, Committee Member<br>Professor of Electrical and Computer Engineering, NJIT           | Date |

| Dr. Leonid Tsybeskov, Committee Member<br>Professor of Electrical and Computer Engineering, NJIT      | Date |

| Dr. Marek Sosnowski, Committee Member<br>Professor of Electrical and Computer Engineering, NJIT       | Date |

| Dr. Roland A. Levy, Committee Member<br>Distinguished Professor of Physics, NJIT                      | Date |

## **BIOGRAPHICAL SKETCH**

| Author: Ni | ufaRahim |

|------------|----------|

|------------|----------|

Degree: Doctor of Philosophy

Date: January 2011

## **Undergraduate and Graduate Education:**

- Doctor of Philosophy in Electrical Engineering, New Jersey Institute of Technology, Newark, NJ, 2011

- Master of Science in Electrical Engineering, New Jersey Institute of Technology, Newark, NJ, 2004

- Bachelor of Science in Electrical Engineering, Bangladesh University of Engineering and Technology, Dhaka, Bangladesh, 2000

## Major: Electrical Engineering

#### **Presentations and Publications:**

- Nilufa Rahim, and Ernest Wu, "Investigation of Progressive Breakdown and non-Weibull Failure Distribution of High-κ Dielectric by Ramp Voltage Stress", accepted for publication in IEEE International Reliability Physics Symposium, 2011.

- Nilufa Rahim, and Durga Misra, "Correlation of Negative Bias Temperature Instability and Breakdown in HfO<sub>2</sub>/TiN Gate Stacks", ECS Transactions, 28(2), pp. 323-330, 2010.

- Naser A. Chowdhury, X. Wang, G. Bersuker, C. Young, Nilufa Rahim, and Durga Misra, "Temperature Dependent Time-to-Breakdown (T<sub>BD</sub>) of TiN/HfO<sub>2</sub> n-channel MOS Devices in Inversion", Microelectronics Reliability, 49(5), pp. 495-498, 2009.

- Nilufa Rahim, and Durga Misra, "Temperature Effects on Breakdown Characteristics of High- $\kappa$  Gate Dielectrics with Metal Gates", IEEE Transactions on Device and Materials Reliability, 8 (4), pp. 689-693, 2008.

- Nilufa Rahim, and Durga Misra, "TiN/HfO<sub>2</sub>/SiO<sub>2</sub>/Si Gate Stack Breakdown: Contribution of HfO<sub>2</sub> and Interfacial SiO<sub>2</sub> layer", Journal of the Electrochemical Society, 155 (10), pp. G194-G198, 2008.

- Nilufa Rahim, and Durga Misra, "Role of Hydrogen in Ge/HfO<sub>2</sub>/Al Gate Stacks Subjected to Negative Bias Temperature Instability", Applied Physics Letters, 92(2), pp. 023511, 2008.

- Naser A. Chowdhury, D. Misra, and Nilufa Rahim, "Negative bias temperature instability in TiN/Hf-Silicate based gate stacks", International Journal of High Speed Electronics and Systems, 17(1), pp. 127-141, 2007.

- Durga Misra, Reenu Garg, Purushothaman Srinivasan, Nilufa Rahim, and Naser A.Chowdhury, "Interface Characterization of high-κ dielectrics on Ge substrate", Materials Science in Semiconductor Processing, 9 (4-5 SPEC ISS.), pp. 741-748, 2006.

- Nilufa Rahim, and Durga Misra, "Low Voltage SILC Analysis for High-κ/Metal gate Dielectrics", Advanced Gate Stack, Source/Drain, and Channel Engineering for Si-Based CMOS 5: New Materials, Processes, and Equipment, ECS Transactions, 19 (1), pp. 283-287, 2009.

- Nilufa Rahim, and Durga Misra, "NBTI Behavior of Ge/HfO<sub>2</sub>/Al Gate Stacks", 46th annual Proceedings of the 2008 IEEE international reliability physics symposium, pp. 653-654, 2008.

- Nilufa Rahim, and Durga Misra, "Breakdown Characteristics of High-κ Gate Dielectrics With Metal Gate", International Symposium on Dielectrics for Nanosystems 3: Materials Science, Processing, Reliability, and Manufacturing, ECS Transactions, 13(2), pp. 91-97, 2008.

- Nilufa Rahim, Naser A. Chowdhury, and Durga Misra, "Role of Bulk HfO<sub>2</sub> and Interfacial layer in Breakdown Characteristics of TiN/HfO<sub>2</sub>/SiO<sub>2</sub>/Si Gate Stacks", 5th International Symposium on Physics and Technology of High-κ gate Dielectrics, ECS transactions, 11(4), pp. 629-638, 2007.

- Nilufa Rahim, and Durga Misra, "Low Voltage SILC Analysis for High-κ/Metal gate Dielectrics", Advanced Gate Stack, Source/Drain, and Channel Engineering for Si-Based CMOS 5: New Materials, Processes, and Equipment, 215th Electro Chemical Society Conference, San Francisco, CA, May 24- May 29, 2009.

- Nilufa Rahim, and Durga Misra, "Elevated Temperature Breakdown Study for High-  $\kappa$ /Metal Gate Stacks", The Dana Knox Student Research Showcase, NJIT, Newark, NJ, April 8,2009.

- Nilufa Rahim, and Durga Misra, "NBTI Behavior of Ge/HfO<sub>2</sub>/Al Gate Stacks", 46th annual IEEE international reliability physics symposium, Phoenix, AZ, April 2008.

- Nilufa Rahim, and Durga Misra, "Breakdown Characteristics of Metal Gate/HfO<sub>2</sub> based Multi-layer Gate Stacks", National Science Foundation GK-12 Annual Meeting, NSF Headquarter, Arlington, VA, Feb. 29, 2008.

- Nilufa Rahim, Naser A. Chowdhury and Durga Misra, "Role of Bulk HfO<sub>2</sub> and Interfacial layer SiO<sub>2</sub> Layer in Breakdown characteristics in TiN/ HfO<sub>2</sub>/SiO<sub>2</sub>/Si Gate stacks", 212th Electro Chemical Society Conference, Washington DC, Oct. 7-Oct. 12, 2007.

- Nilufa Rahim, Naser A. Chowdhury and Durga Misra, "Role of Experimentally Observed Defect Energy Levels in Carrier Transport and Charge Trapping in Metal Gate/Hf-SilicateBased Gate Stacks", 210th ECS conference, Cancun, Mexico, Oct. 29- Nov. 3, 2006.

To my family

#### ACKNOWLEDGMENT

I am heartily thankful to my dissertation advisor, Dr. Durgamadhab Misra, whose supervision, encouragement, and support throughout this research work enabled me to develop an understanding of the subject. He not only guided me through when I needed assistance in ideas, also helped me enormously to be independent. I am very much grateful to Dr. Ernest Wu for guiding me during my Co-Op at IBM. I was able to learn a lot from him and most importantly I was motivated by him immensely. I also want to thank all my committee members, Dr. Haim Grebel, Dr. Leonid Tsybeskov, Dr. Marek Sosnowski and Dr. Roland Levy for their valuable suggestions.

This research work was supported by various funding source as NSF, ECE department and C2PRISM of NJIT, IBM at Vermont. I am expressing my gratitude for supporting my work.

I am indebted to Dr. John Aitken, my manager during my Co-Op at IBM, for his continuous inspiration, encouragement and support. My colleagues and friends at NJIT have always given me technical and moral support during this time of research work. I want to take this opportunity to thank Amrita Banerjee, Dr. Naser Chowdhury and Dr. Purushothaman Srinivasan in this regard.

Lastly, I am extremely thankful to my family specially my parents who have taught me to dream. Heartfelt gratitude to my husband, Abdullah Ahmed who supported me single handedly, my sister, Selina Mala for her support. Finally, thanks to my son, Shayaan Ahmed, who was my most inspiration in this journey.

viii

# **TABLE OF CONTENTS**

| C | hapter                                                                | Page |

|---|-----------------------------------------------------------------------|------|

| 1 | INTRODUCTION, MOTIVATION AND OBJECTIVES                               | 1    |

|   | 1.1 Introduction                                                      | 1    |

|   | 1.2 Motivation and Approach                                           | 5    |

|   | 1.3 Objectives                                                        | 7    |

|   | 1.3.1 Time Dependent Dielectric Breakdown (TDDB)                      | 7    |

|   | 1.3.2 Stressed-Induced Leakage Current (SILC)                         | 8    |

|   | 1.3.3 Negative Bias Temperature Instability (NBTI)                    | 9    |

|   | 1.4 Dissertation Organization                                         | 10   |

| 2 | RELIABILITY ISSUES OF HIGH-κ DIELECTRICS: CURRENT STATUS              | 12   |

|   | 2.1 Introduction                                                      | 12   |

|   | 2.2 Breakdown Behaviors of HfO <sub>2</sub> under DC Stress           | 14   |

|   | 2.2.1 Trap Generation in Bulk Oxide                                   | 14   |

|   | 2.2.2 Stress Induced Leakage Current (SILC)                           | 15   |

|   | 2.2.3 Soft Breakdown of HfO <sub>2</sub> with Constant Voltage Stress | 19   |

|   | 2.2.4 Progressive Breakdown (PBD regime)                              | 22   |

|   | 2.2.5 Hard Breakdown (HBD).                                           | 24   |

|   | 2.3 High-κ/IL Breakdown Mechanism                                     | 24   |

|   | 2.4 NBTI of High- κ/Metal Gate                                        | 27   |

|   | 2.4.1 Degradation Mechanism of NBTI for SiO <sub>2</sub>              | 27   |

|   | 2.4.2 Degradation Mechanism of NBTI in High- κ                        | 29   |

# TABLE OF CONTENTS (Continued)

| С | hapter                                                       | Page |

|---|--------------------------------------------------------------|------|

|   | 2.5 PBTI of High- κ/Metal Gate                               | 30   |

|   | 2.6 Breakdown by Ramped Voltage Stress.                      | 31   |

|   | 2.7 Chapter Summary                                          | 33   |

| 3 | DEVICE FABRICATION AND ELECTRICAL CHARACTERIZATION           | 35   |

|   | 3.1 Introduction                                             | 35   |

|   | 3.2 TiN/HfO <sub>2</sub> based MOS Devices Fabrication       | 35   |

|   | 3.2.1 Interfacial Layer Growth                               | 37   |

|   | 3.3 Electrical Characterization                              | 37   |

|   | 3.3.1 Capacitance-Voltage (C-V) Measurement                  | 38   |

|   | 3.3.2 Conductance Measurement                                | 38   |

|   | 3.3.3 Stress Measurement                                     | 39   |

|   | 3.3.3.1 Constant Voltage Stress                              | 40   |

|   | 3.3.3.2 Negative Bias Temperature Instability (NBTI)         | 43   |

|   | 3.3.3.3 Stress-Induced Leakage Current (SILC) Measurement    | 44   |

|   | 3.3.3.4 Differential Resistance                              | 45   |

|   | 3.3.4 TDDB (Time Dependent Dielectric Breakdown) Measurement | 46   |

|   | 3.3.5 Weibull Statistics of Time-to-Breakdown                | 47   |

|   | 3.3.6 Voltage Ramp Stress (VRS) Measurement                  | 48   |

|   | 3.4 Chapter Summary                                          | 50   |

# TABLE OF CONTENTS (Continued)

| C | hapter                                                                    | Page |

|---|---------------------------------------------------------------------------|------|

| 4 | CONSTANT VOLTAGE STRESS AND TIME DEPENDENT DIELECTRIC<br>BREAKDOWN (TDDB) | 51   |

|   | 4.1 Introduction                                                          | 51   |

|   | 4.2 Constant Voltage Stress at Room Temperature                           | 52   |

|   | 4.2.1 Gate Current Analysis with Stress Time                              | 52   |

|   | 4.2.2 Analysis with Electric Field Dependence                             | 56   |

|   | 4.3 Analysis with Stress-Induced Leakage Current                          | 58   |

|   | 4.3.1 Analysis with Differential Resistance                               | 60   |

|   | 4.3.2 Voltage Dependence of SILC                                          | 62   |

|   | 4.3.2.1 Stress Voltage Dependence of SILC                                 | 64   |

|   | 4.3.2.2 Sense Voltage Dependence of SILC                                  | 65   |

|   | 4.3.3 Normalized SILC Comparison: Varying Interfacial Layer               | 67   |

|   | 4.4 Charge to Breakdown (Q <sub>BD</sub> ) Analysis                       | 68   |

|   | 4.5 Constant Voltage Stress at Elevated Temperature                       | 70   |

|   | 4.6 Temperature Dependence of SILC                                        | 72   |

|   | 4.7 TDDB: Temperature Dependence                                          | 76   |

|   | 4.8 Chapter Summary                                                       | . 81 |

| 5 | CORRELATION OF NEGATIVE BIAS TEMPERATURE INSTABILITY AND BREAKDOWN.       | 83   |

|   | 5.1 Introduction                                                          | 83   |

|   | 5.2 NBTI Degradation with Time and Temperature                            | 86   |

# TABLE OF CONTENTS (Continued)

| С | hapter                                                                                                    | Page |

|---|-----------------------------------------------------------------------------------------------------------|------|

|   | 5.3 Time-to-Breakdown Comparison during NBTI and TDDB                                                     | 88   |

|   | 5.4 Activation Energy of $\Delta V_{th}$ and SILC                                                         | 91   |

|   | 5.5 NBTI and TDDB Dependence on IL Thickness                                                              | 93   |

|   | 5.6 NBTI and TDDB Dependence on High-κ Layer Thickness                                                    | 94   |

|   | 5.7 Chapter Summary                                                                                       | 96   |

| 6 | PROGRESSIVE BREAKDOWN AND NON-WEIBULL FAILURE<br>DISTRIBUTION OF HIGH-K DIELECTRIC BY RAMP VOLTAGE STRESS | 97   |

|   | 6.1 Introduction                                                                                          | 97   |

|   | 6.2 Experimental Setup                                                                                    | 98   |

|   | 6.3 Conversion from Voltage Domain to Time Domain                                                         | 100  |

|   | 6.4 Progressive Breakdown Time by VRS                                                                     | 106  |

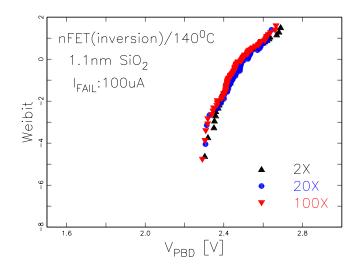

|   | 6.5 Area Independence of Progressive Breakdown Voltage                                                    | 111  |

|   | 6.6 Time-to-Fail by VRS                                                                                   | 113  |

|   | 6.6.1 Time-to-Fail of Thick and Thin SiO <sub>2</sub>                                                     | 113  |

|   | 6.6.2 Time-to-Fail of High-κ/SiO <sub>2</sub> Gate Stack                                                  | 115  |

|   | 6.6.3 Temperature Acceleration of High-κ Gate Stack by VRS and CVS                                        | 116  |

|   | 6.7 Weak Link                                                                                             | 118  |

|   | 6.8 Chapter Summary                                                                                       | 118  |

| 7 | SUMMARY AND FUTURE WORK                                                                                   | 119  |

# TABLE OF CONTENTS (Continued)

| Chapter         | Page |

|-----------------|------|

| 7.1 Summary     | 119  |

| 7.2 Future Work | 121  |

# LIST OF TABLES

| Table |                                                                             | Page |

|-------|-----------------------------------------------------------------------------|------|

| 1.1   | LSTP Technology Requirements from ITRS 2009 Winter Meeting                  | 2    |

| 1.2   | Minimum Requirements of High-κ Gate Dielectric                              | 3    |

| 5.1   | Gate Stacks with Various High-k and Interfacial Layer Quality and Thickness | 85   |

# LIST OF FIGURES

| Figu | re                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Page |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

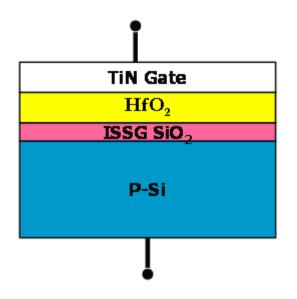

| 1.1  | TiN gate with HfO <sub>2</sub> /In Situ Steam generated (ISSG) SiO <sub>2</sub> on p-Si                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 6    |

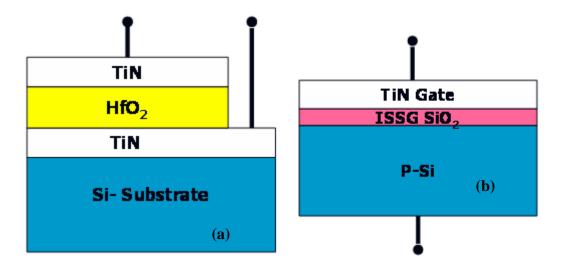

| 1.2  | Two test structures to study breakdown characteristics (a) Metal-Insulator-Metal (MIM) capacitor with $HfO_2$ and (b) TiN gate with ISSG SiO <sub>2</sub>                                                                                                                                                                                                                                                                                                                                                                                        | 7    |

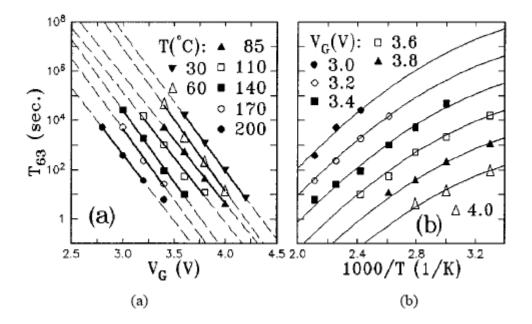

| 2.1  | (a) $T_{BD}$ versus $V_G$ and (b) $T_{BD}$ versus temperature for 2.15-nm oxides (SiO <sub>2</sub> ) using p+poly/n-Si capacitors (+ $V_G$ )                                                                                                                                                                                                                                                                                                                                                                                                     | 13   |

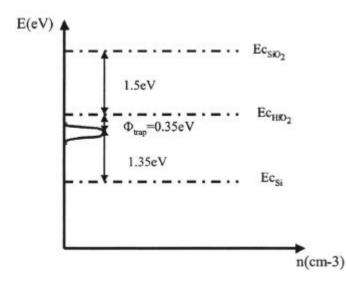

| 2.2  | Fermi-derivative energy distribution of the traps. Here trap energy was found to be $\phi_t = 0.35$ eV                                                                                                                                                                                                                                                                                                                                                                                                                                           | 14   |

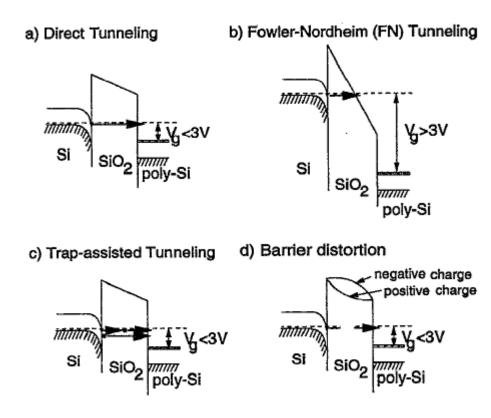

| 2.3  | Schematic energy-band diagram showing (a) direct tunneling of electrons from the cathode to the anode contact, (b) Fowler-Nordheim tunneling of electrons from the cathode to the bottom of the $SiO_2$ conduction band with subsequent ballistic transport through the oxide to the anode, (c) two examples of trapassisted tunneling in the direct tunneling regime including the use of both interfacial and bulk oxide sites, and (d) direct tunneling with barrier (field) distortion caused by trapped negative and positive oxide charges |      |

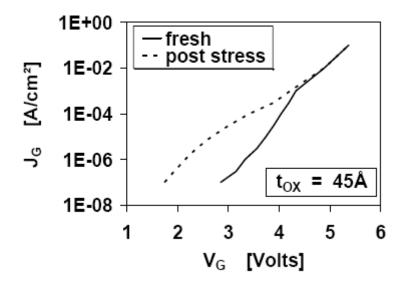

| 2.4  | Fresh and post ramp-stress I-V characteristics for 4.5nm NMOS oxides                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 17   |

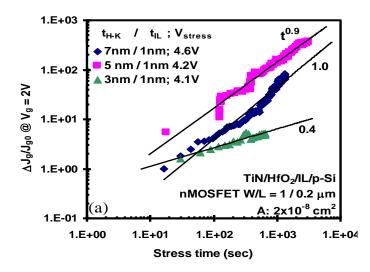

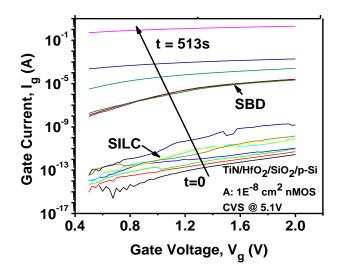

| 2.5  | SILC evolutions with stress time for various splits of high- $\kappa$ gate stacks. SILC is sensed at $V_g = 2 V$ .                                                                                                                                                                                                                                                                                                                                                                                                                               | 19   |

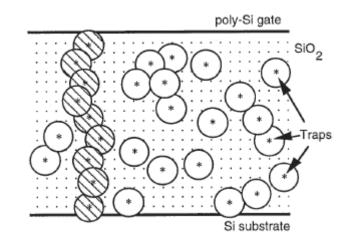

| 2.6  | Schematic illustration of the new spheres model for intrinsic oxide breakdown simulation based on trap generation and conduction via traps. A breakdown path is indicated by the shaded spheres                                                                                                                                                                                                                                                                                                                                                  |      |

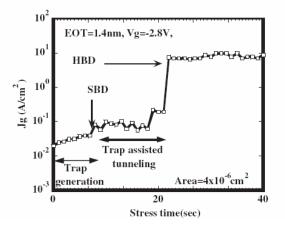

| 2.7  | Gate current density during constant voltage stress showing soft breakdown of HfO <sub>2</sub> MOS capacitors with EOT 1.4 nm                                                                                                                                                                                                                                                                                                                                                                                                                    | 20   |

| 2.8  | Competing sequences of trap generation, percolation (small black dots) and subsequent wear out (dots growing) on a given capacitor                                                                                                                                                                                                                                                                                                                                                                                                               | 21   |

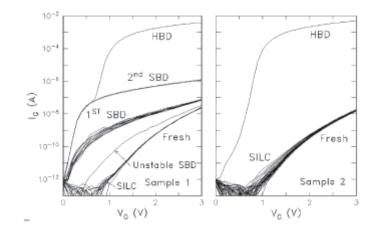

| 2.9  | Gate current measured interrupting stress for ultrathin SiO <sub>2</sub> oxide showing SILC, SBD and HBD                                                                                                                                                                                                                                                                                                                                                                                                                                         | 22   |

| Figur | re                                                                                                                                                                                                                                                                                                                                                             | Page |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

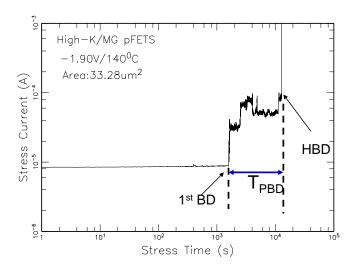

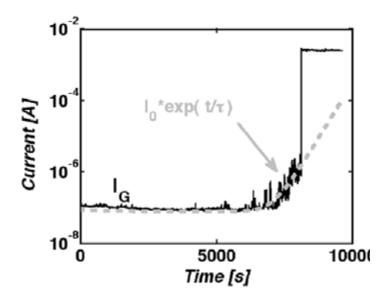

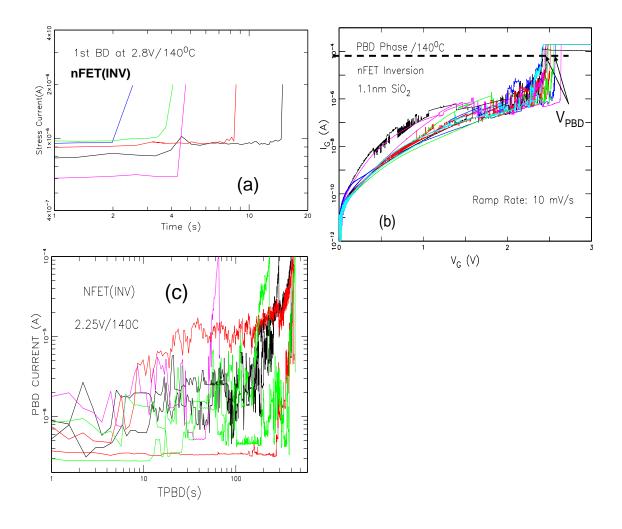

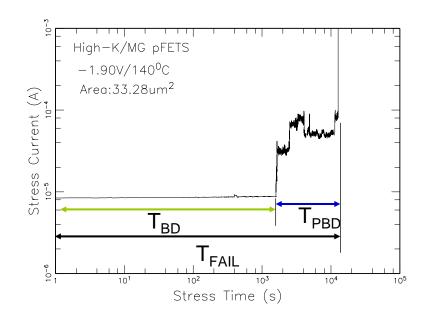

|       | Example of the time dependence of gate leakage $I_g$ during CVS at $V_G = -1.9$ V, in TiN/HfO <sub>2</sub> /SiO <sub>2</sub> pFETs of 3.328 x 10 <sup>-7</sup> cm <sup>2</sup> gate area. Progressive breakdown time, T <sub>PBD</sub> is the time of growth of percolation path which is the time between HBD and 1 <sup>st</sup> BD.                         |      |

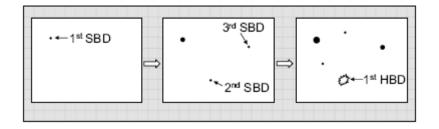

|       | Example of exponential growth of the current $I_G$ during the PBD phase. The dotted line is the exponential fit to the measured current                                                                                                                                                                                                                        | 23   |

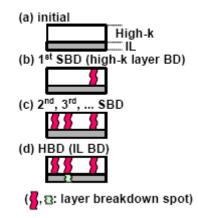

|       | The proposed mechanism for the gradual increase of gate leakage through pMOSFETs (HfAlO <sub>x</sub> /SiO <sub>2</sub> = $5.1/2.2$ nm) under negative stress. (a) Before breakdown, (b) after the first SBD of the high- $\kappa$ layer, (c) successive multiple SBDs occur, (d) ntil the HBD occurs due to the layer breakdown of the interfacial layer (IL). |      |

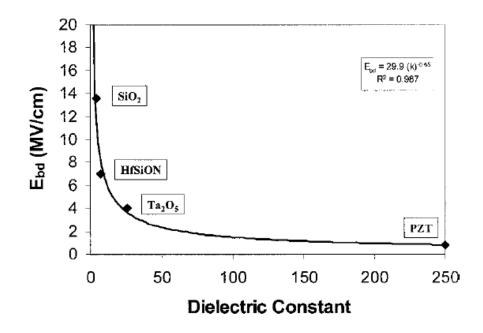

| 2.13  | Observed breakdown strength with dielectric constant                                                                                                                                                                                                                                                                                                           | 26   |

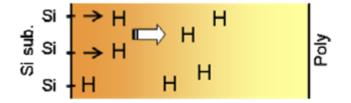

|       | The dissociation of Si-H bonds at the Si-SiO <sub>2</sub> interface triggered by hole is shown schematically. Passivation along with dissociation of these Si-H bonds also occurs at the same time                                                                                                                                                             |      |

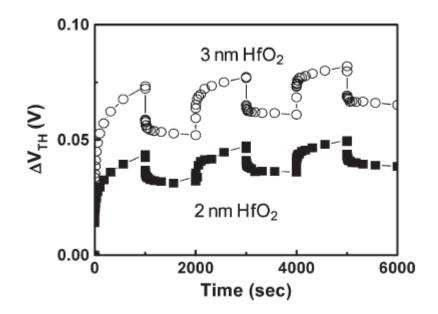

|       | Reversible threshold voltage change by applying alternating negative ( $V_T$ -1V) and positive bias (+1V) for 1000s cycle. Two gate stacks has 2 and 3 nm HfO <sub>2</sub> with identical 1.1 nm ISSG-SiO <sub>2</sub> as interfacial layer. Both stress and relaxation phases show fast and slow components.                                                  |      |

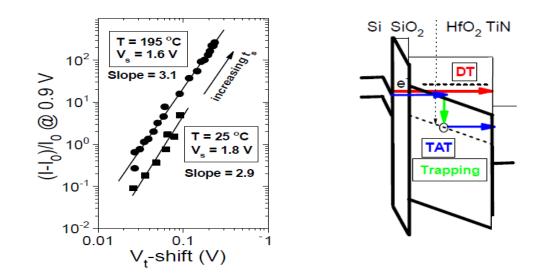

|       | (left) SILC and V <sub>t</sub> -shift shows direct correlation at both room and high temperature. (Right) High- $\kappa$ /MG band diagram during PBT stressing showing tunneling and charge trapping in the bulk HfO <sub>2</sub> . DT is direct tunneling and TAT is trap-assisted tunneling.                                                                 |      |

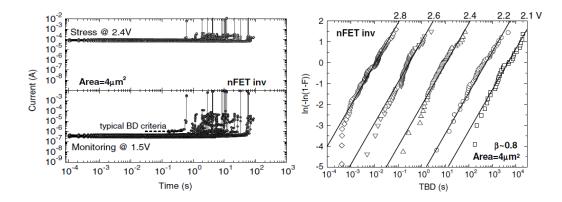

|       | (left) Current-time traces during CVS for high- $\kappa$ nFEts. (Right) Time-to-<br>breakdown (T <sub>BD</sub> ) distributions with Weibull slope, $\beta \sim 0.8$ determined from<br>current time traces (left figure) using a breakdown criteria of 1 $\mu$ A at monitoring<br>condition                                                                    |      |

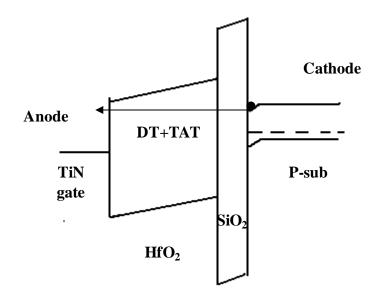

|       | Schematic of a band diagram during constant voltage stress (CVS) showing the flow of electrons from cathode to anode side                                                                                                                                                                                                                                      | 39   |

#### Figure

43

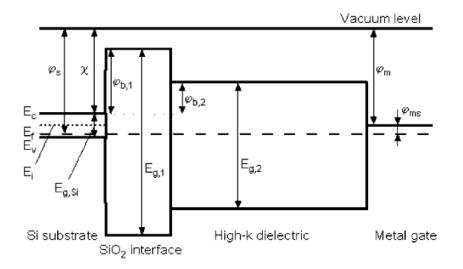

- 3.3 The energy band diagram in flatband condition with  $E_c$  the Si conduction band,  $E_v$  the Si valence band,  $E_f$  the semiconductor Fermi level,  $E_i$  the intrinsic Fermi level,  $E_g$  the band gap,  $\varphi_s$  the semiconductor work function,  $\varphi_m$  the metal work function,  $\varphi_{b,1}$  the potential barrier for the interface and  $\varphi_{b,2}$  for the high- $\kappa$ ,  $\varphi_{ms}$ the work function difference and  $\chi$  the semiconductor electron affinity. The EOT of the stack is 1.6 nm with p-Si substrate, 1 nm interfacial SiO<sub>2</sub>, 3 nm high- $\kappa$  dielectric ( $\kappa = 20$ ,  $\varphi_{b,2} = 1.5$  eV) and a mid gap metal gate electrode...... 42

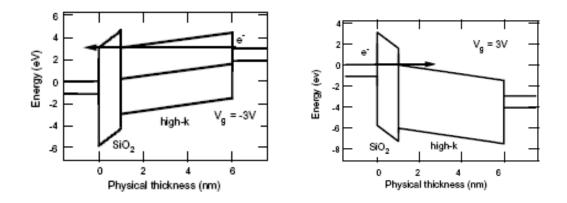

- 3.4 (a) Gate injection: If a negative bias at the gate is applied electrons tunnel from the gate electrode through the high-κ and then the interfacial layer. (b) Substrate injection: With a positive bias applied electrons tunnel from the Si substrate towards the electrode. Already at relative low voltages electrons start to enter the high-κ conduction band and tunnel only through the interfacial layer.....

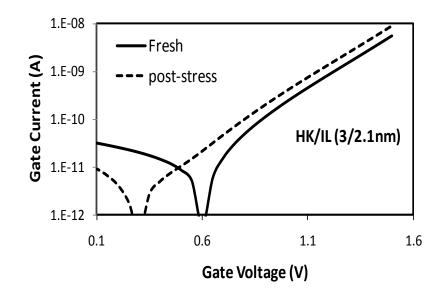

| 3.5 | Fresh and post ramp-stress I-V characteristics for high-k nMOS devices in  |    |

|-----|----------------------------------------------------------------------------|----|

|     | inversion. Stress voltage was 2.4V and post-stress current measured at low |    |

|     | voltage shown in the figure was measured after 1000 seconds stress         | 45 |

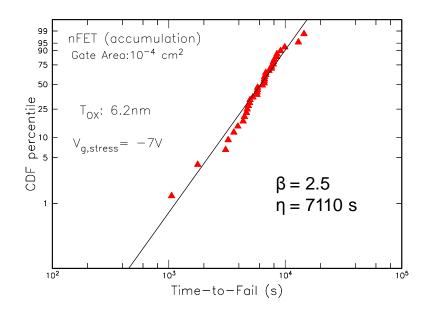

- 3.6 Weibull distribution of  $T_{BD}$  for thick SiO<sub>2</sub> nFET capacitors in accumulation. Symbols represent experimental  $T_{BD}$  data and line is a Weibull fit using maximum likelihood estimation (MLE). Weibull slope,  $\beta$  was 2.5 and  $\eta$  (or t<sub>63%</sub>) was 7110 seconds found from the fit. 48

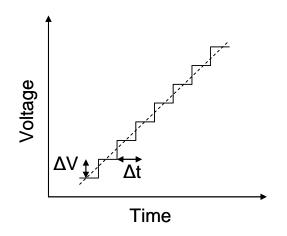

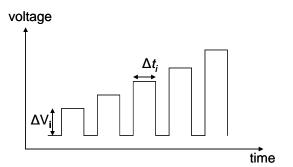

- 3.7 Schematic of voltage ramp stress. Small voltage step was chosen to approximate linear ramp and also avoid the granularity effect.49

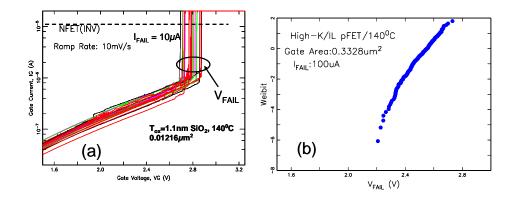

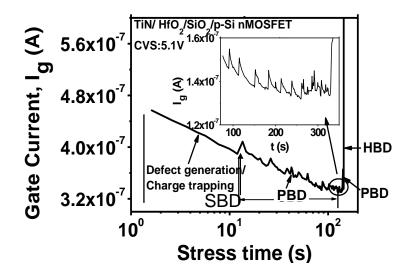

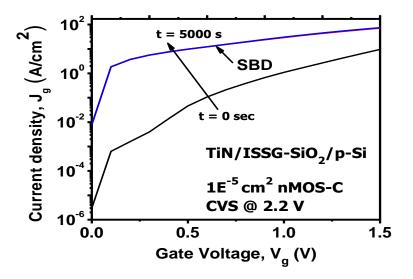

- 4.1 Gate current with stress time at CVS (5.1V) at 25<sup>o</sup>C for TiN/HfO<sub>2</sub>/IL (SiO<sub>2</sub>)/Si under substrate injection. Different degradation phases as trapping, SBD, PBD and HBD can be observed. It is important to note that PBD time is observed to be very short for this stress condition.

53

| Figu | re                                                                                                                                                                                                                                                                                                                                                                                              | Page |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

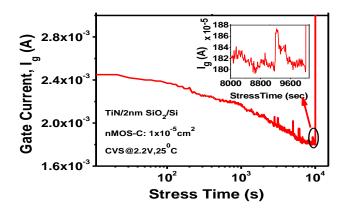

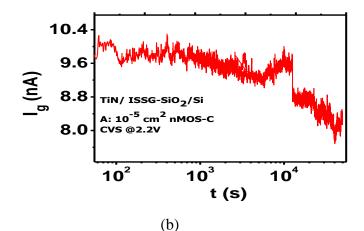

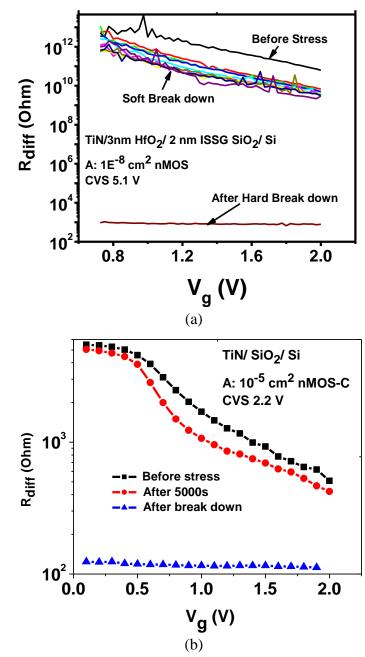

| 4.2  | (a), (b) Gate current evolution at CVS (2.2V, 25 <sup>o</sup> C) for TiN/SiO <sub>2</sub> /Si nMOS capacitor.                                                                                                                                                                                                                                                                                   | 54   |

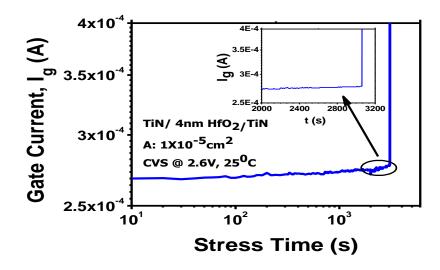

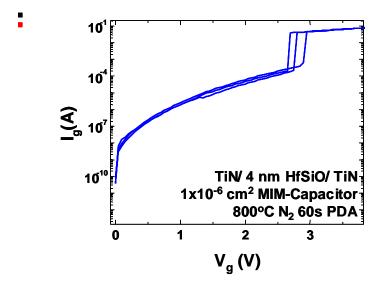

| 4.3  | Gate current with stress time at CVS (2.6V, 25 <sup>o</sup> C) for ALD TiN/HfSiO(10% SiO <sub>2</sub> )/TiN MIM-C.                                                                                                                                                                                                                                                                              | 55   |

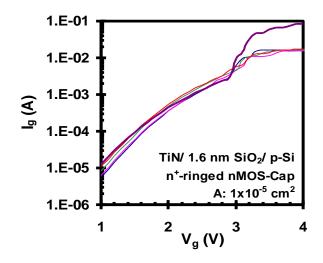

| 4.4  | I-V characteristics under ramped voltage stress (RVS) applied on n+-ringed nMOS-C. $E_{BD} \approx 17$ MV/cm is comparable with the theoretical value of ~ 15 MV/cm.                                                                                                                                                                                                                            |      |

| 4.5  | I-V characteristics under RVS applied on $HfSi_xO_y$ (10% SiO <sub>2</sub> ) based MIM capacitors. EBD $\approx 6.5$ MV/cm is comparable with the theoretical value of ~ 7 MV/cm.                                                                                                                                                                                                               |      |

| 4.6  | Stress induced leakage current (SILC) in TiN/HfO <sub>2</sub> /IL (SiO <sub>2</sub> )/Si. These $I_g$ -V <sub>g</sub> measurements taken at stress intervals show gradual increase in gate current for the measured voltage range. Few orders of magnitude increase in $I_g$ is observed from SILC to soft breakdown mode.                                                                      |      |

| 4.7  | Stress induced leakage current (SILC) in TiN/SiO <sub>2</sub> /Si nMOS-C                                                                                                                                                                                                                                                                                                                        | 59   |

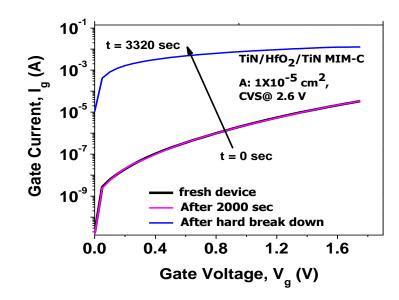

| 4.8  | Stress induced leakage current (SILC) in TiN/HfO <sub>2</sub> /TiN MIM-C. Sense current did not show any SILC in the form of a gate current increase                                                                                                                                                                                                                                            |      |

| 4.9  | Differential resistance of the dielectric for (a) HfO <sub>2</sub> /IL gate stack; (b) ISSG SiO <sub>2</sub> -only nMOS-C; (c) metal-insulator-metal capacitors                                                                                                                                                                                                                                 |      |

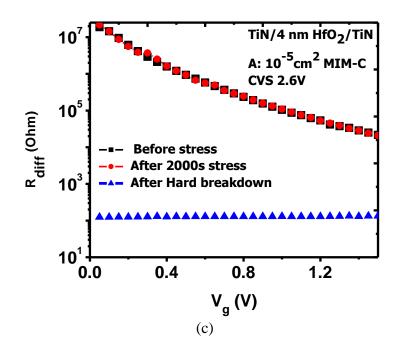

| 4.10 | Stress voltage dependence of stress-induced leakage current for TiN/HfO <sub>2</sub> /SiO <sub>2</sub> (3 nm/2.1 nm) nMOS capacitors ( $10^{-5}$ cm <sup>2</sup> ). For all stress voltages, SILC follows power law.                                                                                                                                                                            |      |

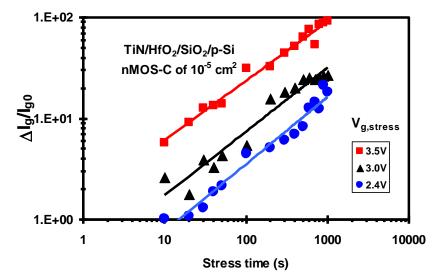

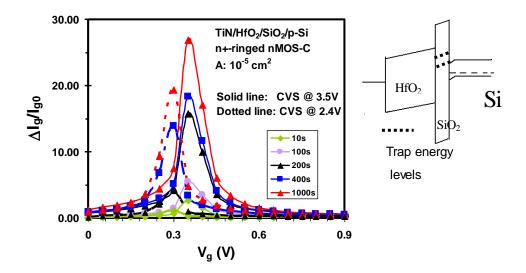

| 4.11 | Sense voltage dependence of stress-induced leakage current for TiN/HfO <sub>2</sub> /SiO <sub>2</sub> (3 nm/2.1 nm) nMOS capacitors ( $10^{-5}$ cm <sup>2</sup> ). Two different constant voltage stresses were applied at substrate injection mode. The lines are drawn for visual guide. The right figure is a schematic of the trap energy levels in the interfacial SiO <sub>2</sub> layer. |      |

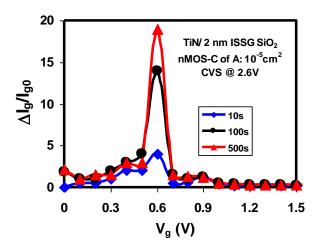

| 4.12 | Sense voltage dependence of stress-induced leakage current for 2 nm SiO <sub>2</sub> -only nMOS capacitor $(10^{-5} \text{ cm}^2)$ with metal gate. Constant voltage stress was performed at substrate injection mode (+2.6V)                                                                                                                                                                   |      |

| Figu | re                                                                                                                                                                                                                                                                                                                                       | Page |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

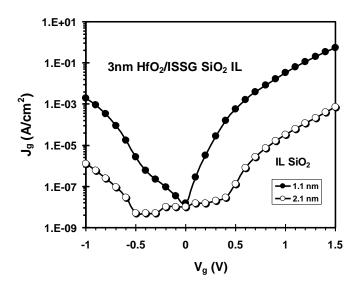

| 4.13 | Before stress current comparison for different interfacial $SiO_2$ layer thickness.<br>Both of these gate stacks have 3 nm HfO <sub>2</sub> layer                                                                                                                                                                                        | 67   |

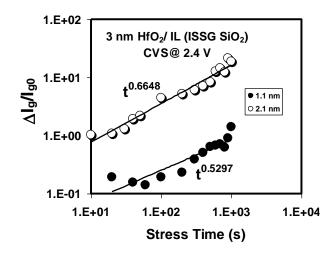

| 4.14 | Normalized SILC comparison varying interfacial layer thickness. Thicker interfacial layer (2.1nm) showed more defect generation than thinner IL. High-k thickness was 3 nm for both gate stacks                                                                                                                                          |      |

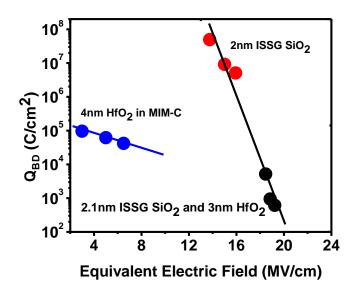

| 4.15 | $Q_{BD}$ vs. equivalent electric field for high- $\kappa$ gate stack, MIM capacitor and SiO <sub>2</sub> -only devices under substrate injection. An agreement is observed for the gate stack and SiO <sub>2</sub> -only devices.                                                                                                        | 69   |

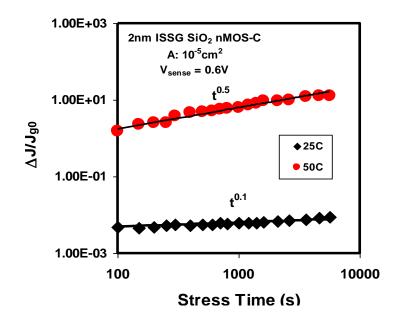

| 4.16 | Temperature dependent time evolutions of the SILC of TiN/ISSG SiO <sub>2</sub> nMOS capacitors under substrate injection                                                                                                                                                                                                                 | 72   |

| 4.17 | (a) Temperature dependent time evolutions of the SILC and (b) Frenkel-Poole plot for leakage current of TiN/HfO <sub>2</sub> /ISSG SiO <sub>2</sub> nMOS capacitors under substrate injection.                                                                                                                                           |      |

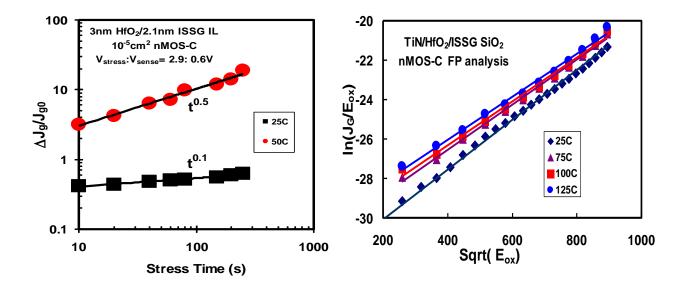

| 4.18 | Change in leakage current in $HfO_2$ based MIM capacitor with Stress time at room temperature and $50^{0}C$ . At $V_g = 0.6V$ sense voltage, leakage current has low dependence on stress time.                                                                                                                                          |      |

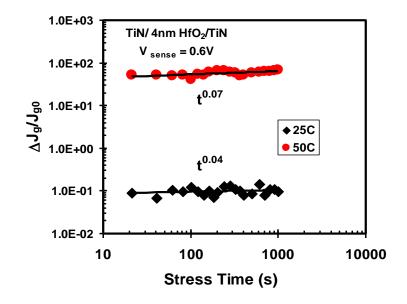

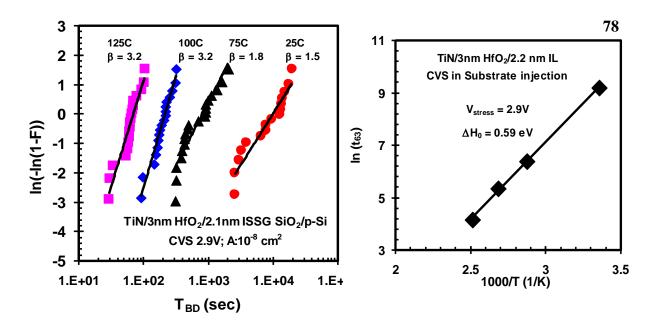

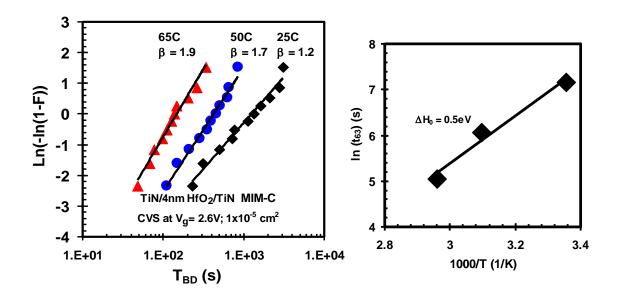

| 4.19 | Weibull plots of $T_{BD}$ at different temperatures for 3nm HfO <sub>2</sub> /2.1nm ISSG SiO <sub>2</sub> capacitors and Arrhenius plot of $T_{BD}$                                                                                                                                                                                      | 78   |

| 4.20 | Weibit plot of $T_{BD}$ at different temperatures for 4nm HfO <sub>2</sub> based MIM capacitors and Arrhenius plot of $T_{BD}$                                                                                                                                                                                                           | 79   |

| 4.21 | (a) Weibit plot of $T_{BD}$ at different temperatures for 2nm ISSG SiO <sub>2</sub> based nMOS capacitor and (b) Arrhenius plot of $T_{BD}$                                                                                                                                                                                              | 80   |

| 5.1  | Schematic of the gate stack of TiN/HfO <sub>2</sub> /SiO <sub>2</sub> /n-Si                                                                                                                                                                                                                                                              | 86   |

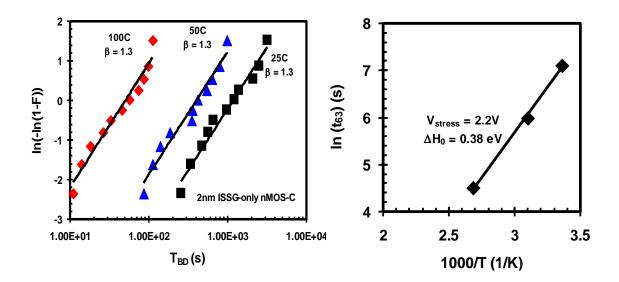

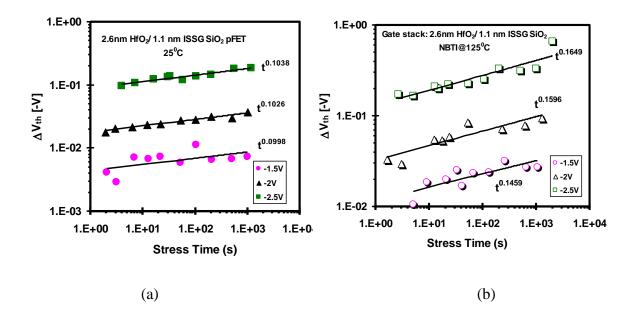

| 5.2  | NBTI Time evolutions of gate stack (2.6nm HfO <sub>2</sub> /1.1 nm ISSG SiO <sub>2</sub> ) for various gate stress voltages at (a) room temperature and (b) $125^{0}$ C. The degradation rate (power-law exponent, n) is independent of the applied bias. A comparatively low <i>n</i> was observed for these high- $\kappa$ gate stacks |      |

| Figu | ire                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Page     |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

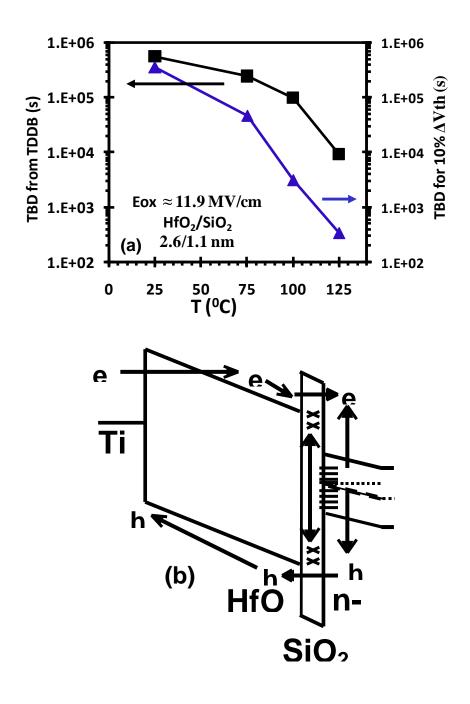

| 5.3  | (a) $T_{BD}$ (defined as, time for 10% increase in threshold voltage during NBTI) (triangles) and time-to-breakdown (squares) during TDDB at various temperatures show similar degradation trend and (b) shows the energy band diagram to depict the process of defects generation during the constant voltage stress.                                                                                                                                                                                                                                                                                                                   | ;<br>[   |

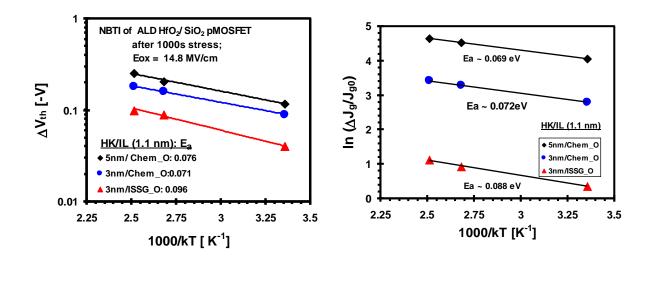

| 5.4  | Activation energies of threshold voltage change during NBTI for three different gate stacks with 3 and 5 nm high- $\kappa$ thicknesses and 1.1 nm IL (a). Two of the devices had Chemical Oxide as IL and the third had ISSG oxide as IL. The gate stack with ISSG SiO <sub>2</sub> IL shows the impact of the quality of the IL (higher E <sub>a</sub> ). (b) Activation energies of SILC during TDDB of same gate stack. Similar observation can be made from E <sub>a</sub> of SILC.                                                                                                                                                  | ;<br>;   |

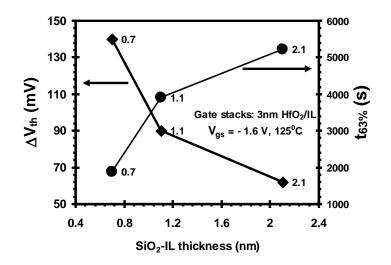

| 5.5  | Threshold voltage change and time to breakdown for a $3nm HfO_2$ gate stack.<br>Three different SiO <sub>2</sub> IL (ISSG) were used (0.7, 1.1 and 2.1 nm). Gate stacks<br>with lower EOT showed similar maximum degradation in both NBTI and<br>TDDB domain.                                                                                                                                                                                                                                                                                                                                                                            |          |

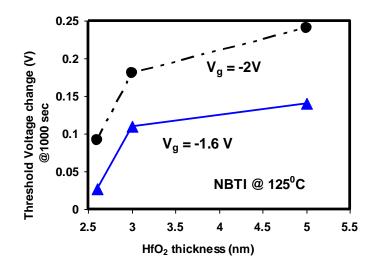

| 5.6  | $HfO_2$ thickness dependence of the threshold voltage shift measured after 1000 seconds of stress. For this NBTI measurement, $V_g$ was -2 and -1.6 V. The contribution of the bulk oxide layer is observed through charge trapping in that layer.                                                                                                                                                                                                                                                                                                                                                                                       | <u>}</u> |

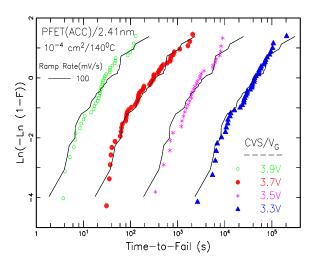

| 6.1  | Hybrid two-stage VRS technique. (a) at first stage, BD was detected by CVS with a low current compliance (here 2 $\mu$ A). For 2nd stage those samples were either subjected to (b) VRS to extract V <sub>PBD</sub> or (c) CVS for direct T <sub>PBD</sub> measurements with a specified fail current (200 $\mu$ A).                                                                                                                                                                                                                                                                                                                     | ;<br>)   |

| 6.2  | Typical stress current evolutions with time for high- $\kappa$ /metal gate dielectrics. $T_{FAIL}$ is summation of time to 1st breakdown ( $T_{BD}$ ) and progressive breakdown time ( $T_{PBD}$ ).                                                                                                                                                                                                                                                                                                                                                                                                                                      |          |

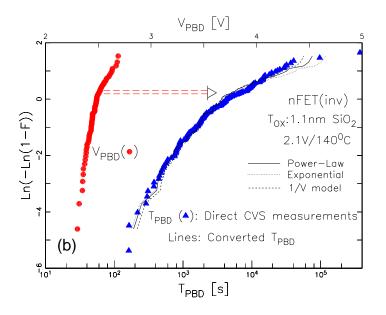

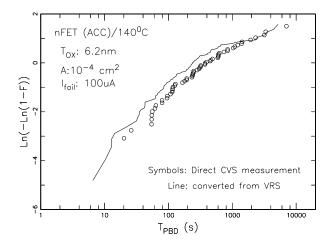

| 6.3  | Conversion of $V_{PBD}$ to $T_{PBD}$ distribution. Symbols represent $T_{PBD}$ data from CVS stress. Very steep $V_{PBD}$ distribution is translated to shallow $T_{PBD}$ distribution due to the exponential dependence of $T_{PBD}$ on $V_{PBD}$ . Three popular models as power-law (solid line), exponential (dotted line) and 1/V model (dashed line) have been used as acceleration model for conversion. The $T_{PBD}$ converted from $V_{PBD}$ for a reference voltage of 2.1V agrees quite reasonably irrespective of the choice of the model. The variations among different models would be visible for a larger time window. |          |

| Figu | re                                                                                                                                                                                                                                                               | Page |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

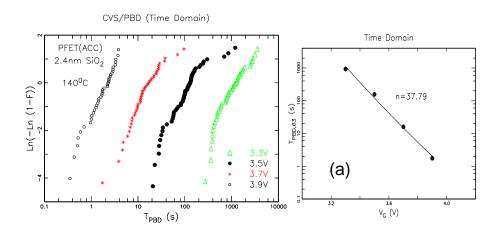

| 6.4  | (a) Voltage acceleration derived from CVS/PBD (b) from VRS/PBD show<br>power-law exponents within statistical uncertainty. For time domain, and for<br>voltage domain, $R \propto V_{PBD,63\%}^{n+1}$ have been used                                             |      |

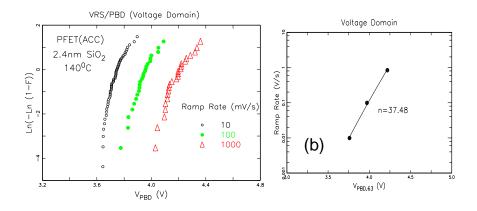

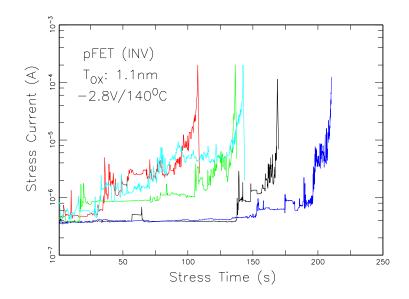

| 6.5  | 1 <sup>st</sup> BD detection difficulties in ultra-thin oxide pFETs. The noise in early stress time seen in this figure would impede to fix a low current compliance level for 1st stage of the hybrid stress method                                             |      |

| 6.6  | Comparison of residual times $(T_{PBD})$ for thick (6.2nm) oxide. These devices were intrinsically broken at 7V at 1st stage. For PBD phase or $2^{nd}$ stage, $V_{ref}$ was also 7V.                                                                            |      |

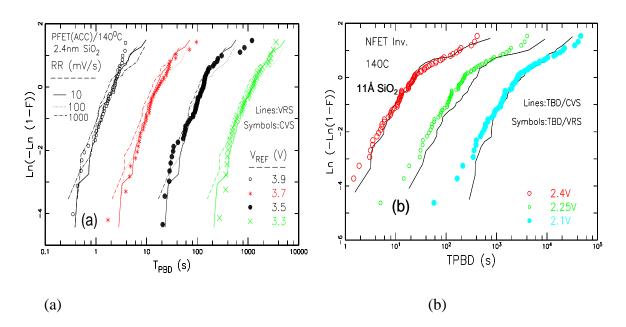

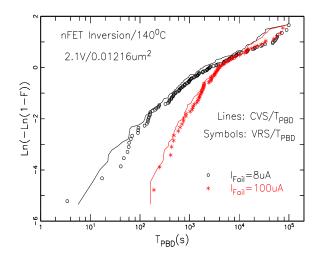

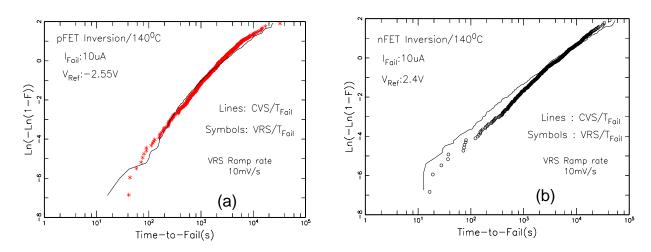

| 6.7  | Comparison of residual times (TPBD) for (a) thick oxide, 2.4nm, (b) thin oxide, 1.1nm SiO <sub>2</sub> . An excellent agreement between $CVS/T_{PBD}$ and $VRS/T_{PBD}$ can be observed for different reference voltages and 100 $\mu$ A fail current            |      |

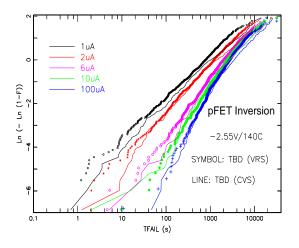

| 6.8  | Similar failure current dependence of Time-to-PBD $(T_{PBD})$ is observed for both VRS and CVS for thin (11Å) SiO <sub>2</sub>                                                                                                                                   | 110  |

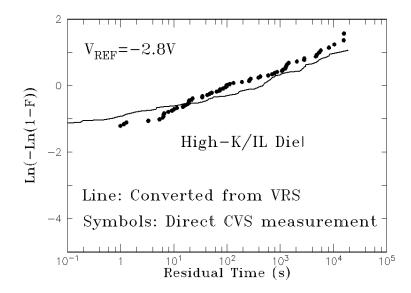

| 6.9  | Comparison of residual times (TRES) of high- $\kappa$ /IL dielectric pFET in inversion at 125 <sup>o</sup> C. Constant voltage of -3.1V was used in the first step                                                                                               | 111  |

| 6.10 | $V_{PBD}$ distributions of ultra-thin oxides extracted during 2nd stage of hybrid stress. Three different area nFETs (2x to 100x) were investigated. Area independence of $V_{PBD}$ indicates single spot BD during PBD phase                                    |      |

| 6.11 | Time-to-fail ( $T_{FAIL}$ ) extracted from CVS and converted from $V_{FAIL}$ by VRS for thick SiO <sub>2</sub> (2.4nm) pFET in accumulation show excellent agreement. Lines are $T_{FAIL}$ from VRS and symbols represent $T_{FAIL}$ from CVS                    |      |

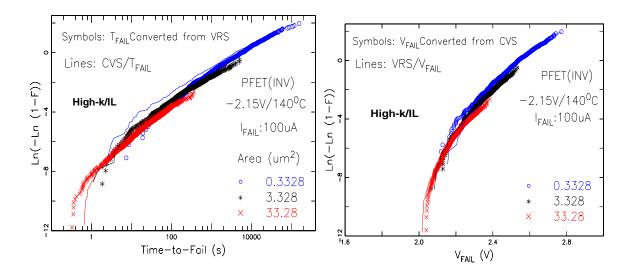

| 6.12 | (a) Time-to-fail ( $T_{FAIL}$ ) extracted from CVS and converted from $V_{FAIL}$ by VRS for ultra-thin SiO <sub>2</sub> (1.1nm) pFET show excellent agreement on large sample size (~1000 devices each) and (b) For nFET, high percentile data agrees quite well |      |

| 6.13 | The final failure distributions as a function of fail currents for ultra-thin SiO <sub>2</sub> pFETs. For both CVS (lines) and VRS (symbols), strong failure current dependence of final fail time is observed                                                   |      |

# Figure

| Symbols represent $T_{FAIL}$ converted from $V_{FAIL}$ and lines are direct CVS |     |

|---------------------------------------------------------------------------------|-----|

| measurements. (b) Similar comparison between direct and converted $V_{FAIL}$ in |     |

| voltage domain. Poisson area scaling has been applied in both cases             | 116 |

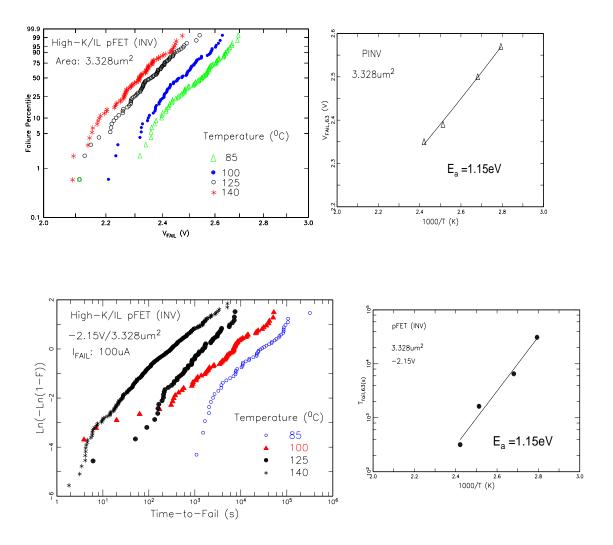

| 6.15 | Thermal activation energy, $E_a$ of $V_{FAIL}$ (top) and $T_{FAIL}$ (bottom) by VRS and |     |

|------|-----------------------------------------------------------------------------------------|-----|

|      | CVS measurements. In both cases, Ea was ~1.15eV                                         | 117 |

# LIST OF SYMBOLS

| K              | Dielectric constant                  |

|----------------|--------------------------------------|

| В              | Weibull slope, Beta                  |

| η              | Characteristic life (Eta)            |

| Å              | Angstrom $(10^{-10} \text{ meters})$ |

| Γ              | Voltage acceleration factor, Gamma   |

| $k_B$          | Boltzmann constant                   |

| $\varphi_{ms}$ | Work function difference             |

| φ <sub>t</sub> | Trap energy                          |

| $\psi_s$       | Surface potential                    |

#### **CHAPTER 1**

#### INTRODUCTION, MOTIVATION AND OBJECTIVES

#### 1.1 Introduction

In today's world, microelectronics became an integral part of our lives. So, continuous effort in microelectronics research is essential to achieve higher performance and functionality of various electronic devices that eventually will improve quality of life in the world. Metal-oxide-semiconductor field-effect transistor (MOSFET) is the basic device in integrated circuit (IC). Continuous scaling of MOSFET for the past few decades has followed an evolutionary path. The supply voltage,  $V_{dd}$ , channel length and physical thickness of dielectrics are scaled to achieve higher circuit speed/performance, increased bit density and lower power dissipation which tremendously improve the computing power at a reasonable cost.

To meet the requirements of diverse applications, MOSFETs have been categorized into different families, such as high performance (HP) logic family (i.e. microprocessors), low operating power (LOP) logic family (i.e. notebook) and low standby power (LSTP) logic family (i.e. cell phone). High performance logic devices require smaller threshold voltage ( $V_{th}$ ), shorter channel length and thin dielectric for fast switching speed. But for LSTP logic family, power dissipation is the main concern which requires low standby leakage current. The scaling of devices via thinning of gate dielectric and shortening of channel length causes substantial gate tunneling current and subthreshold leakage current. For LSTP logic devices, direct tunneling current has become a significant portion of leakage current for sub 2 nm oxide [1]. Based on the International Technology Roadmap for Semiconductor (ITRS) 2009 report, the physical

gate length of the transistor have been shrunk below 45-nm node and equivalent oxide thickness (EOT) of the dielectric scaled down to less than 0.9 nm [2].

| Year of production             | 2010 | 2013 | 2016 | 2019 | 2022 |

|--------------------------------|------|------|------|------|------|

| Technology node                | 45   | 32   | 22   | 16   | 11   |

| Physical gate length           | 27   | 20   | 15.3 | 11.7 | 8.9  |

| (nm)                           |      |      |      |      |      |

| V <sub>dd</sub> (Low operating | 0.95 | 0.80 | 0.75 | 0.65 | 0.60 |

| power supply                   |      |      |      |      |      |

| voltage)                       |      |      |      |      |      |

| Off state current              | 0.1  | 0.1  | 0.1  | 0.1  | 0.1  |

| under high drain bias          |      |      |      |      |      |

| $(nA/um)$ at $25^{\circ}C$     |      |      |      |      |      |

Table 1.1 LSTP Technology Requirements from ITRS 2009 Winter Meeting [1]

Replacement materials for the gate dielectric were expected below 90 nm to maintain the pace of Moore's Law. However, the widespread adoption of channel strains engineering postponed gate dielectric replacement by a few generations. Strained silicon boosted the transistor performance and power consumption to maintain progress without the introduction of revolutionary materials. But thinning of oxynitride, or SiON, the current gate dielectric is at the end of the road. With SiON providing only about a 50 percent improvement in dielectric constant ( $\kappa$ ), a fundamental shift in materials was required. Further scaling of SiON would create unacceptably high gate leakage current and reduce device reliability. The 1-nm-thick layer of SiON, required for 45-nm device targets, is essentially just three atomic layers thick. Not only is leakage a huge problem, but there is no margin left for thickness variation. The revolution of new material (high- $\kappa$ /metal gate) has solved this problem. The advantage of using a high-dielectric-constant material is that it has a greater dielectric constant ( $\kappa$ ) than SiO<sub>2</sub> ( $k_{SiO2} = 3.9$ ) and thus can

afford larger physical thickness to minimize leakage while maintaining similar capacitance values. But the new dielectric material needs to satisfy the minimum requirements for transistor application. Some of these requirements are listed in the table below [1.2].

Table 1.2 Minimum Requirements of High-κ Gate Dielectric

- 1. Higher permittivity than SiO<sub>2</sub> and oxynitride ( $9 \le \kappa \le 25$ ).

- 2. Larger bandgap and conduction band offset.

- 3. Lower leakage current than  $SiO_2$  for similar EOT.

- 4. Thermodynamically stable on Si.

- 5. Good interface quality with low interface states ( $\leq 5 \times 10^{10} \text{ eV/cm}^2$ ).

- 6. Good reliability.

The research on high-k materials as the new gate dielectric started off with Tantalum Oxide (Ta<sub>2</sub>O<sub>5</sub>) and Strontium Titanate (SrTiO<sub>3</sub>), as these materials were already studied for DRAM applications [3,4]. As the research for new dielectric material continued, several other oxides have been proposed such as Titanium Oxide (TiO<sub>2</sub>), Aluminum Oxide (Al<sub>2</sub>O<sub>3</sub>), Yttrium Oxide (Y<sub>2</sub>O<sub>3</sub>), Zirconium Oxide (ZrO<sub>2</sub>), Hafnium Oxide (HfO<sub>2</sub>) [5-7] etc. to replace SiO<sub>2</sub>. Among these high-k dielectrics, HfO<sub>2</sub> has been considered as the potential candidate because of various reasons; such as 1) high dielectric constant of ~25-30 (~6-7 times that of SiO<sub>2</sub>), 2) energy band gap of 5.68eV, though much lower than SiO<sub>2</sub> but with band offsets greater than 1eV (1.5eV for electron and 3.4eV for holes), 3) free energy of reaction with Si is about 47.6Kcal/mol at 727°C making it more stable material on Si substrate in comparison to other high- $\kappa$  dielectrics,

4) unlike other silicides, silicide of Hf can be easily oxidized [8] to form  $HfO_2$ . All these properties of  $HfO_2$  make it an attractive alternative for  $SiO_2$ .

In high- $\kappa$  HfO<sub>2</sub> gate stacks, SiO<sub>2</sub>-rich interfacial layer (IL) which is between the Si substrate and the high- $\kappa$  layer is needed to facilitate the growth of the high-k layer, as well as attain sufficient channel mobility. This interfacial layer forms either as a result of oxidizing growth conditions [9] or because they are intentionally grown as nucleation layers before high- $\kappa$  deposition [10]. For oxidizing growth condition, oxygen (O) is released and diffused to Si during HfO<sub>2</sub> deposition. This O release forms thick bottom interface SiOx that severely limits scaling. It was also proven by transmission electron microscopy (TEM) and EOT that this bottom interface SiOx grows uncontrollably [11-14].

There are manifold advantages of intentionally grown  $SiO_2$  interfacial layer. First, the thickness and quality of this  $SiO_2$  IL can be controlled, which would eventually help in gate stack EOT scaling. Second, the use of an oxide bottom layer enables  $HfO_2$ nucleation with almost no barrier, linear growth rate, growth at constant density, and the most two-dimensionally continuous  $HfO_2$  films [10]. So, interfacial  $SiO_2$  is essential for the ease of nucleation of  $HfO_2$  on Si. Also, the presence of this interfacial layer of  $SiO_2$ improves carrier mobility and reduces positive bias temperature instability (PBTI).

However, these high- $\kappa$  materials exhibit a higher defect density compared to SiO<sub>2</sub>, aggravating some major device reliability issues including the bias temperature instability, the reduction in channel mobility, time dependent dielectric breakdown, and hot carrier induced degradation etc for the complete gate stack. The knowledge of stress induced defects, charge to breakdown can improve the understanding of their effects on

device reliability, as reliability remains to be the most critical factor to hold back its successful incorporation into the mainstream commercial intergraded circuits [15-18].

#### **1.2** Motivation and Approach

The high-k material currently being considered for gate dielectric applications results in a multilayer structure that includes a SiO<sub>2</sub>-like layer either spontaneously or intentionally formed at the interface [19]. A schematic of the gate stack is shown in Figure 1.1 where the interfacial layer was intentionally formed. The reliability of high-k gate dielectric stacks is influenced by both interfacial layer and high- $\kappa$  layer. Stress induced breakdown is one of the vital issues of the reliability of the high-k gate stacks. The difficulty in the breakdown study of the gate stack arises as the potential drop/electric field across interfacial and high- $\kappa$  layers are different due to the differences in the value of the dielectric constant,  $\kappa$  and thickness [20]. This, along with the differences in their respective atomic structures [21], leads to the difference in the degradation in IL and high- $\kappa$  layer as the stress bias is applied. It was also observed from transistor electrical characteristics and high resolution chemical and spectroscopic analysis that the high-k film modifies the stoichiometry of the underlying SiO<sub>2</sub> layer by rendering it oxygen deficient [22]. This oxygen vacancy may be responsible to induce a higher density of fixed charges in the IL associated with the Si-Si defects. The mechanism of device degradation under constant voltage stress of both polarities is still under debate due to the lack of techniques to separate the traps in the interfacial and the high-k layer. So, this research attempts to explore the gate stack in terms of its long term reliability which

would help its inclusion in future CMOS devices. More emphasis was given to identify the weak link between high-k layer and  $SiO_2$ -like IL.

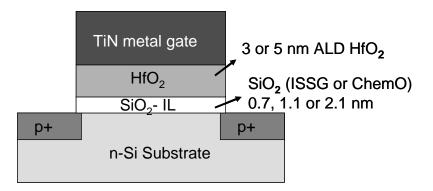

To understand the breakdown characteristics of high- $\kappa$ /SiO<sub>2</sub> gate stack, this work has followed an approach by investigating two other control structures along with the gate stack: one with only SiO<sub>2</sub> and other with bulk high- $\kappa$  gate dielectric without any interfacial layer, while maintaining identical growth conditions and thickness as the gate stack. The high- $\kappa$  dielectric without an interfacial layer was achieved by using a metalinsulator-metal (MIM) structure. The test structures are shown in Figure 1.2.

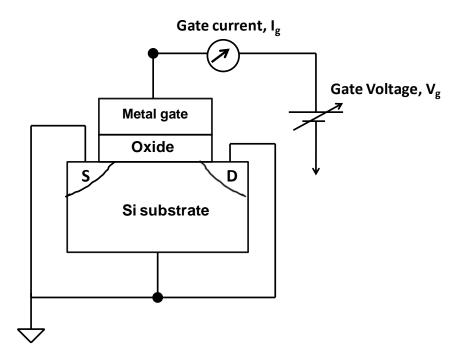

Figure 1.1 TiN gate with HfO<sub>2</sub>/In Situ Steam generated (ISSG) SiO<sub>2</sub> on p-Si.

**Figure 1.2** Two test structures to study breakdown characteristics (a) Metal-Insulator-Metal (MIM) capacitor with  $HfO_2$  and (b) TiN gate with ISSG SiO<sub>2</sub>.

This experimental design has enabled to understand the contribution of  $SiO_2$ interfacial layers and bulk high- $\kappa$  gate dielectrics in terms of the detail degradation and breakdown behavior of the composite gate stack.

#### 1.3 Objectives

For high- $\kappa$  /metal gate stacks, two important reliability issues relating to bulk traps are time dependent dielectric breakdown (TDDB) and stress-induced leakage current (SILC). Also, Negative bias temperature instability (NBTI) is a cause of concern for long term reliability where both bulk and interface are degraded. A brief description of these degradation mechanisms and their impact on reliability are mentioned below.

#### **1.3.1** Time Dependent Dielectric Breakdown (TDDB)

When a voltage is applied across the gate oxide, a measurable tunneling current will flow if the gate voltage  $(V_g)$  is high enough and/or the oxide is thin enough. For thick oxides at fields above about 7 MV/cm the current is controlled by Fowler-Nordheim tunneling through the triangular barrier [23-24], while for thin oxides ( $t_{ox} <3$  nm) at voltages below about 3 V (corresponding to the barrier height between n-type silicon and SiO<sub>2</sub>) the current is due to direct quantum mechanical tunneling. Electrons (or holes) flowing across the oxide will trigger several processes depending on their energy. At least three defect generation mechanisms have been identified: The first two, impact ionization and anode hole injection, occur at higher voltages and lead to hole trapping and hole-related defect generation [25-26] as the stress with time continues. The lowest-energy process so far identified, which dominates at the voltages where present MOSFETs operate, is the so-called trap creation process attributed to hydrogen release [27-28] or hole injection [29] from the anode. This process continues in the subthreshold region even at operating voltages down to 1.2 V or lowers [30-32]. These defects buildup (hydrogen or holes), form a conduction path between cathode and anode and eventually breaks down the oxides destructively. This catastrophic electrical breakdown is known as time dependent dielectric breakdown (TDDB).

#### **1.3.2 Stressed-Induced Leakage Current (SILC)**

Besides the as-deposited defects, additional bulk traps in high- $\kappa$  gate stacks are created during constant voltage stress (CVS), leading to dielectric breakdown when a critical trap density is reached. These generated traps give rise to stressed-induced leakage current (SILC) through trap assisted tunneling even long before breakdown [33]. For high- $\kappa$  gate stacks, especially nFETs show large SILC during positive bias temperature which eventually affects proper detection of breakdown time as well.

#### **1.3.3 Negative Bias Temperature Instability (NBTI)**

Negative bias temperature instability (NBTI) occurs in p-channel MOS devices stressed with negative gate voltages at elevated temperatures. The detrimental effects of NBTI on devices are threshold voltage ( $V_T$ ) increase, absolute "off" current I<sub>off</sub> increase and absolute drain current ( $I_{Dsat}$ ) and transconductance ( $g_m$ ) decrease. Typical stress temperatures lie in the 100– 250 °C range with oxide electric fields typically below 6 MV/cm, i.e., fields below those that lead to hot carrier degradation. Such fields and temperatures are typically encountered during burn in, but are also approached in high performance ICs during routine operation. Either negative gate voltages or elevated temperatures can produce NBTI, but their combined action produces a stronger and faster effect.  $V_T$  shifts due to NBTI has now become an important reliability concern for both digital and analog CMOS circuits. This is primarily due to the scaling of gate oxide for digital circuits without corresponding scaling of their supply voltages. So, the devices are exposed to moderately high electric field [34].

For various applications (i.e. automotive industry), it is possible that the operating temperature of semiconductor device will be much higher than room temperature. The above mentioned physical degradation mechanisms (TDDB, NBTI and SILC) will be accelerated with this temperature increase. So, a basic understanding of these degradation phenomena at elevated temperature is fundamental to allow accurate reliability predictions.

The objectives of this research are—

- 1. to critically and comprehensively examine the dielectric breakdown mechanism (specially, time dependent dielectric breakdown, TDDB) of the high- $\kappa$ /IL gate stack on Si at both room and elevated temperatures.

- 2. to estimate the lifetime of these stacks at operating voltage from experimental results.

- 3. to investigate negative bias temperature instability(NBTI).

- 4. to probe into the origin of low voltage stress-induced leakage current (SILC).

- 5. to correlate NBTI, LV-SILC and TDDB effects for a comprehensive reliability model.

- 6. to develop methodology for investigating gate dielectric integrity.

## **1.4 Dissertation Organization**

Chapter 2 discusses the reliability study of high- $\kappa$ /metal gate devices from literature focusing on breakdown. Recent work involving MIM capacitors with high- $\kappa$  and past research on thin SiO<sub>2</sub> reliability have also been discussed.

The fabrication process for high- $\kappa$ /IL (TiN/HfO<sub>2</sub>/SiO<sub>2</sub>/Si) MOS devices, MIM capacitors and control SiO<sub>2</sub> devices used in the present work has been described in Chapter 3. The electrical characterization set up and details of the measurement procedures for this research are also discussed here.

Chapter 4 deals with the breakdown mechanisms of metal gate/high- $\kappa$ /IL based gate stacks at room temperature. The roles of IL and high- $\kappa$  layer in TDDB are determined from sets of TiN/HfO<sub>2</sub> based gate stacks, SiO<sub>2</sub>-only MOS structures and HfO<sub>2</sub>-only MIM capacitors. Four different degradation regimes i) Defect generation, (ii) Soft breakdown (SBD), (iii) Progressive breakdown (PBD) and (iv) Hard breakdown (HBD) under constant voltage stress (CVS) for HfO<sub>2</sub>/SiO<sub>2</sub> gate stacks were discussed.

For accurate estimation of operating voltage extrapolation, it is required that time dependent breakdown study be evaluated at an elevated temperature. Hence, this chapter also expands the discussion on basic understanding of temperature dependence of high- $\kappa$ /IL gate stack breakdown by investigating the response of the individual layers at elevated temperature.

Chapter 5 talks about the origin of low voltage stress-induced leakage current (SILC) and correlates to breakdown of the gate dielectric. The initiation of breakdown process can be understood by studying the low voltage SILC growth as a function of stress voltage. Then the issues of negative bias temperature instability (NBTI) to explore the traps formation and how it impacts the device degradation were also discussed. Also, a correlation of NBTI and TDDB is presented.

Chapter 6 narrates the new hybrid 2 step stress methodology developed to study progressive breakdown and final failure distribution of high- $\kappa$ /IL gate stack and also thick and thin single layer SiO<sub>2</sub> dielectric. This chapter presents extensive experimental results of progressive breakdown time (T<sub>PBD</sub>) and final failure time (T<sub>FAIL</sub>) by voltage ramp stress (VRS) and compared it with traditional constant voltage stress. It has been shown that VRS method can be very useful and efficient to study non-Weibull T<sub>FAIL</sub> distribution and thus save significant time and manufacturing cost.

Chapter 7 gives a summary of this research and a brief discussion on future work.

## CHAPTER 2

## **RELIABILITY ISSUES OF HIGH-K DIELECTRICS: CURRENT STATUS**

## 2.1 Introduction

Major efforts have been invested to replace SiO<sub>2</sub> by high- $\kappa$  gate dielectrics. Promising results in terms of equivalent oxide thickness (EOT), leakage current reduction and integration have been obtained with SiO<sub>2</sub>/high- $\kappa$  stacks [35]. Except at very low fields, the generation of traps in the dielectric is the most important aspect of degradation prior to breakdown. The dielectric reliability of these stacks (high- $\kappa$ /interfacial SiO<sub>2</sub>) is evaluated by measuring time-to-breakdown (T<sub>BD</sub>) during constant voltage stress (CVS) or constant current stress (CCS). The degradation mechanisms in double-layer stacks might be quite different from single layer degradation and the material properties of high- $\kappa$ dielectrics might allow for additional physical mechanisms [35]. Besides, several mechanisms may be taking place at the same time during stress. The microscopic origin of the degradation occurring in these layers is not well understood yet. It has been claimed by Torii *et al.* [36] that the hole-injection-induced release of hydrogen from Si-H terminations causes IL (interfacial layer) breakdown. This mechanism also accelerates negative bias temperature instability (NBTI).

For ultra thin oxides (SiO<sub>2</sub>) with poly gate, very strong  $T_{BD}/Q_{BD}$  temperature dependence has been found for thin oxides as compared to thick oxides [25, 37-42] shown in figure 2.1. As the gate stack considered for high- $\kappa$  has an interfacial layer of thin SiO<sub>2</sub>, it is speculated that there will be strong  $T_{BD}/Q_{BD}$  temperature dependence for high- $\kappa$ /IL gate stack as well. So, to evaluate the reliability of MOS devices with this new dielectric stack, it is imperative to look into critical reliability issues such as TDDB, NBTI, and stress-induced leakage current (SILC) at both room and elevated temperatures. Additionally, a correlation between various degradation mechanisms need to established.

**Figure 2.1** (a)  $T_{BD}$  versus  $V_G$  and (b)  $T_{BD}$  versus temperature for 2.15-nm oxides (SiO<sub>2</sub>) using p+poly/n-Si capacitors (+  $V_G$ ) [43].

To study breakdown, issues such as soft breakdown, hard breakdown, the physical and chemical nature of the interface layer and the bulk high- $\kappa$  layer, polarity dependence due to asymmetric band structure, charging effect by preexisting traps, thickness dependence, and area scaling are critical for the accurate reliability projection of this new dielectric material.

## 2.2 Breakdown Behaviors of HfO<sub>2</sub> under DC Stress

## 2.2.1 Trap Generation in Bulk Oxide

Various temperature dependent leakage current and threshold voltage instability measurements have been performed to explain the physical origin of electron traps in Hfbased dielectrics [44]. From V<sub>t</sub> instability, an equilibrium of electron tunneling from channel to traps and detrapping by Frenkel-Poole conduction can be explained. From this F-P model, the extracted trap energy was found to be 0.35eV. There have been reports of different trap energy levels present in the bulk Hf-oxide varying from 0.35eV to 1.5eV from HfO<sub>2</sub> conduction band. The source of these defects were claimed to be oxygen vacancy related defects. [45].

**Figure 2.2** Fermi-derivative energy distribution of the traps. Here trap energy was found to be  $\varphi_t=0.35$  eV [44].

# 2.2.2 Stress Induced Leakage Current (SILC)

It was first reported in the early 1980s that currents measured on thin oxides (4-5 nm in thickness) at low applied electric fields increased after stressing at high fields [46]. The low-field current measurements were performed at low voltages, referred to as the direct tunneling (DT) regime, as illustrated in Figure 2.3 (a). The DT current is produced by electrons tunneling from the cathode contact to the anode contact without entering the oxide conduction band. The stressing was performed at higher fields where the electrons tunneled first into the oxide conduction band before entering the anode [as shown in Figure 2.3 (b). This latter type of tunneling phenomenon is called Fowler-Nordheim (FN) tunneling. It was assumed that the increase in the DT current was caused by oxide film deterioration due to the presence of hot electrons in the oxide conduction band and related to the presence of positive oxide charges generated near the anode during FN stress [47].