## **Copyright Warning & Restrictions**

The copyright law of the United States (Title 17, United States Code) governs the making of photocopies or other reproductions of copyrighted material.

Under certain conditions specified in the law, libraries and archives are authorized to furnish a photocopy or other reproduction. One of these specified conditions is that the photocopy or reproduction is not to be "used for any purpose other than private study, scholarship, or research." If a, user makes a request for, or later uses, a photocopy or reproduction for purposes in excess of "fair use" that user may be liable for copyright infringement,

This institution reserves the right to refuse to accept a copying order if, in its judgment, fulfillment of the order would involve violation of copyright law.

Please Note: The author retains the copyright while the New Jersey Institute of Technology reserves the right to distribute this thesis or dissertation

Printing note: If you do not wish to print this page, then select "Pages from: first page # to: last page #" on the print dialog screen

The Van Houten library has removed some of the personal information and all signatures from the approval page and biographical sketches of theses and dissertations in order to protect the identity of NJIT graduates and faculty.

### **ABSTRACT**

### NEW DATA STRUCTURES, MODELS, AND ALGORITHMS FOR REAL-TIME RESOURCE MANAGEMENT

### by Xinfa Hu

Real-time resource management is the core and critical task in real-time systems. This dissertation explores new data structures, models, and algorithms for real-time resource management.

At first, novel data structures, i.e., a class of Testing Interval Trees (TITs), are proposed to help build efficient scheduling modules in real-time systems. With a general data structure, i.e., the TIT\* tree, the average costs of the schedulability tests in a wide variety of real-time systems can be reduced. With the Testing Interval Tree for Vacancy analysis (TIT-V), the complexities of the schedulability tests in a class of parallel/distributed real-time systems can be effectively reduced from  $O(m^2n\log n)$  to  $O(m\log n+m\log m)$ , where m is the number of processors and n is the number of tasks. Similarly, with the Testing Interval Tree for Release time and Laxity analysis (TIT-RL), the complexity of the online admission control in a uni-processor based real-time system can be reduced from  $O(n^2)$  to  $O(n\log n)$ , where n is the number of tasks. The TIT-RL tree can also be applied to a class of parallel/distributed real-time systems. Therefore, the TIT trees are effective approaches to efficient real-time scheduling modules.

Secondly, a new utility accrual model, i.e., UAM<sup>+</sup>, is established for the resource management in real-time distributed systems. UAM<sup>+</sup> is constructed based on the timeliness of computation and communication. Most importantly, the interplay between

computation and communication is captured and characterized in the model. Under UAM<sup>+</sup>, resource managers are guided towards maximizing system-wide utility by exploring the interplay between computation and communication. This is in sharp contrast to traditional approaches that attempt to meet the timing constraints on computation and communication separately. To validate the effectiveness of UAM<sup>+</sup>, a resource allocation algorithm called IAUASA is developed. Simulation results reveal that IAUASA is far superior to two other resource allocation algorithms that are developed according to traditional utility accrual model and traditional idea. Furthermore, an online algorithm called IDRSA is also developed under UAM<sup>+</sup>, and a Dynamic Deadline Adjustment (DDA) technique is incorporated into IDRSA algorithm to explore the interplay between computation and communication. The simulation results show that the performance of IDRSA is very promising, especially when the interplay between computation and communication is tight. Therefore, the new utility accrual model provides a more effective approach to the resource allocation in distributed real-time systems.

Thirdly, a general task model, which adapts the concept of calculus curve from the network calculus domain, is established for those embedded real-time systems with random event/task arrivals. Under this model, a prediction technique based on history window and calculus curves is established, and it provides the foundation for dynamic voltage-frequency scaling in those embedded real-time systems. Based on this prediction technique, novel energy-efficient algorithms that can dynamically adjust the operating voltage-frequency according to the predicted workload are developed. These algorithms aim to reduce energy consumption while meeting hard deadlines. They can

accommodate and well adapt to the variation between the predicted and the actual arrivals of tasks as well as the variation between the predicted and the actual execution times of tasks. Simulation results validate the effectiveness of these algorithms in energy saving.

## NEW DATA STRUCTURES, MODELS, AND ALGORITHMS FOR REAL-TIME RESOURCE MANAGEMENT

by Xinfa Hu

A Dissertation

Submitted to the Faculty of

New Jersey Institute of Technology

in Partial Fulfillment of the Requirements for the Degree of

Doctor of Philosophy in Computer Science

**Department of Computer Science**

May 2010

Copyright © 2010 by Xinfa Hu

ALL RIGHTS RESERVED

### **APPROVAL PAGE**

# NEW DATA STRUCTURES, MODELS, AND ALGORITHMS FOR REAL-TIME RESOURCE MANAGEMENT

### Xinfa Hu

|                                                                                          | 4/16/10                               |

|------------------------------------------------------------------------------------------|---------------------------------------|

| Dr. Jøseph Leung, Dissertation Advisor                                                   | Date                                  |

| Dr. Joseph Leung, Dissertation Advisor Distinguished Professor of Computer Science, NJIT |                                       |

|                                                                                          |                                       |

|                                                                                          |                                       |

|                                                                                          | _                                     |

|                                                                                          | 11. 1819                              |

| Dy. Michael A. Baltrush, Committee Member                                                | 16 APLIO Date                         |

| Associate Professor and Chairperson of Computer Science, NJIT                            | Date                                  |

| Tissociate Trolessor and Charperson of Computer Science, 14311                           |                                       |

|                                                                                          |                                       |

|                                                                                          | . 1                                   |

| $\mathcal{O}(\mathcal{O})$                                                               | 1/16/2010                             |

| Dr. Vincent Oria, Committee Member                                                       | Data -                                |

| Associate Professor of Computer Science, NJIT                                            | Date                                  |

| Associate Professor of Computer Science, 1971                                            |                                       |

|                                                                                          |                                       |

|                                                                                          |                                       |

|                                                                                          | 4/16/10                               |

| Dr. Edwin Hou, Committee Member                                                          | $\frac{\varphi/(b/(c))}{\text{Date}}$ |

| Associate Professor of Electrical and Computer Engineering, NJIT                         | Date                                  |

| Tissociate Troicessor of Diceateur and Computer Engineering, 1311                        |                                       |

|                                                                                          |                                       |

|                                                                                          |                                       |

|                                                                                          | MIL 16 1201.                          |

| Dr. Jie Hu, Committee Member                                                             | Date                                  |

| Assistant Professor of Electrical and Computer Engineering, NJIT                         | Duto                                  |

### **BIOGRAPHICAL SKETCH**

Author:

Xinfa Hu

Degree:

Doctor of Philosophy

Date:

May 2010

### **Undergraduate and Graduate Education:**

- Doctor of Philosophy in Computer Science, New Jersey Institute of Technology, Newark, NJ, 2010

- Master of Engineering in Computer Science,

Xi'an Jiaotong University, Xi'an, P. R. China, 2000

- Bachelor of Engineering in Computer Science,

Xi'an Jiaotong University, Xi'an, P. R. China, 1994

Major:

Computer Science

### **Technique Reports and Publications:**

### Xinfa Hu and Joseph Leung,

"Integrating communication cost into the utility accrual model for the resource allocation in distributed real-time systems,"

Proceedings of the fourteenth IEEE International Conference on Embedded and Real-Time Computing Systems and Applications, pp. 217-226, August 2008.

### Xinfa Hu and Joseph Leung,

"Testing interval trees for real-time scheduling systems,"

Proceedings of the fourteenth IEEE International Conference on Embedded and Real-Time Computing Systems and Applications, pp. 327-336, August 2008.

### Xinfa Hu, Guoliang Xing, and Joseph Leung,

"Exploring the interplay between computation and communication in distributed real-time scheduling," submitted to *IEEE Transactions on Computers*, October 2009.

### Xinfa Hu and Guoliang Xing,

"Real-time dynamic voltage-frequency scaling based on calculus curves," submitted to the sixteenth IEEE International Conference on Embedded and Real-Time Computing Systems and Applications, April 2010.

This work is dedicated to

my wife, Fan Zhou,

and to

my parents, Songbing Hu and Baoxiu Li,

all of whom have dedicated so much of their lives,

and themselves,

to me.

### **ACKNOWLEDGMENT**

Many thanks to my advisor, Professor Joseph Leung, for all his help throughout my PhD study.

Special thanks to Professor Michael A. Baltrush, Professor Vincent Oria, Professor Edwin Hou, and Professor Jie Hu for serving as members of the Committee.

I am very grateful to the Computer Science Department of NJIT for consistent financial support throughout my PhD study.

Special thanks to my friend, Dr. Guoliang Xing at the Michigan State University, for his valuable and constructive advice for my papers.

Special thanks to Professor Michael A. Baltrush, for helping me improve the presentation of my dissertation.

I wish to express my sincere gratitude to Professor Vincent Oria for his helpful advice, friendship, and encouragement throughout my PhD study.

I appreciate the advice and encouragement from Professor Andrew Sohn and Professor Alexander Thomasian. Without the encouragement from them and Professor Vincent Oria, I would never be able to accomplish my PhD study here at NJIT.

Many thanks to Professor Grace Wang for correcting my English errors.

And finally, I would like to acknowledge my debt to my wife, Fan Zhou. Without her consistent help, support, and encouragement, I would never have reached this milestone.

## TABLE OF CONTENTS

| C | hapter                                                                                           | Page |

|---|--------------------------------------------------------------------------------------------------|------|

| 1 | INTRODUCTION                                                                                     | 1    |

|   | 1.1 Background                                                                                   | 1    |

|   | 1.2 Objectives                                                                                   | 3    |

| 2 | TESTING INTERVAL TREES FOR REAL-TIME SCHEDULING SYSTEMS                                          | 5    |

|   | 2.1 Definition and Properties of the TIT tree                                                    | 7    |

|   | 2.2 TIT* Tree and Its Applications to Real-Time Scheduling Systems                               | 9    |

|   | 2.3 TIT-V Tree and Its Applications to Real-Time Scheduling Systems                              | 12   |

|   | 2.3.1 Definition and Properties of the TIT-V Tree                                                | 14   |

|   | 2.3.2 Operation on TIT-V Tree and Its Complexity                                                 | 15   |

|   | 2.3.3 Using TIT-V Tree to Construct Feasibility Test for DDRAA                                   | 17   |

|   | 2.3.4 Using TIT-V Tree to Construct Feasibility Test for a Generic Resource Allocation Algorithm | 20   |

|   | 2.4 TIT-RL Tree and Its Applications to Real-Time Scheduling Systems                             | 21   |

|   | 2.4.1 Definition and Properties of the TIT-RL Tree                                               | 23   |

|   | 2.4.2 Operations on TIT-RL Tree and Their Complexities                                           | 27   |

|   | 2.4.3 Using TIT-RL Tree to Construct ACA                                                         | 27   |

| 3 | NEW UTILITY ACCRUAL MODEL FOR RESOURCE ALLOCATION IN ASYNCHRONOUS REAL-TIME DISTRIBUTED SYSTEMS  | 32   |

|   | 3.1 System Model                                                                                 | 35   |

|   | 3.2 Task, Message, and Scheduling Models                                                         | 36   |

|   | 3.3 The New Utility Accrual Model                                                                | 38   |

|   | 3.3.1 Utility Function                                                                           | 38   |

# TABLE OF CONTENTS (Continued)

| Chapter P                                                                                           |      |

|-----------------------------------------------------------------------------------------------------|------|

| 3.3.2 Utility Accrual Criteria                                                                      | . 40 |

| 3.4 Interplay-Aware Utility Accrual Scheduling Algorithm                                            | . 42 |

| 3.4.1 The Algorithm                                                                                 | 42   |

| 3.4.2 Complexity Analysis                                                                           | 47   |

| 3.4.3 An Example                                                                                    | . 48 |

| 3.5 Simulation Analysis                                                                             | . 51 |

| 3.5.1 Simulation Settings                                                                           | 52   |

| 3.5.2 Simulation Results                                                                            | . 54 |

| 4 EXPLORING THE INTERPLAY BETWEEN COMPUTATION AND COMMUNICATION IN DISTRIBUTED REAL-TIME SCHEDULING | 60   |

| 4.1 System Model                                                                                    | 61   |

| 4.2 Scheduling Element Model                                                                        | 61   |

| 4.3 Utility Function                                                                                | 63   |

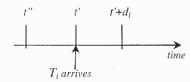

| 4.4 Dynamic Deadline Adjustment                                                                     | 66   |

| 4.5 Interplay-aware Distributed Resource Allocation Algorithm                                       | 70   |

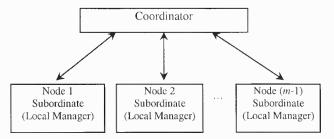

| 4.5.1 Two-level Scheduling Framework                                                                | 70   |

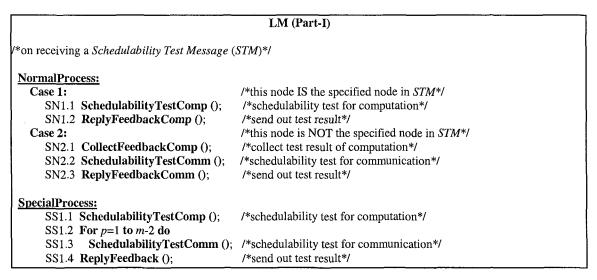

| 4.5.2 The Algorithm                                                                                 | 71   |

| 4.5.3 Complexity Analysis                                                                           | 76   |

| 4.6 Simulation Analysis                                                                             | 78   |

| 4.6.1 Simulation Settings                                                                           | 79   |

| 4.6.2 Simulation Results                                                                            | . 82 |

# TABLE OF CONTENTS (Continued)

| C | hapt | <b>r</b>                                                                                         | Page |

|---|------|--------------------------------------------------------------------------------------------------|------|

| 5 |      | CULUS CURVE BASED ONLINE REAL-TIME DYNAMIC TAGE- FREQUENCY SCALING                               | 87   |

|   | 5.1  | Calculus Curves                                                                                  | 91   |

|   |      | 5.1.1 Arrival Curve                                                                              | 91   |

|   |      | 5.1.2 Service Curve                                                                              | 92   |

|   | 5.2  | System and Task Model                                                                            | 93   |

|   | 5.3  | Schedulability/Feasibility Analysis                                                              | 93   |

|   |      | 5.3.1 Schedulability/Feasibility Analysis According to Preemptive Earliest Deadline First Policy | 94   |

|   |      | 5.3.2 Schedulability/Feasibility Analysis According to Preemptive Fixed Priority Policy          | 96   |

|   | 5.4  | Online Real-Time DVS Algorithms                                                                  | 97   |

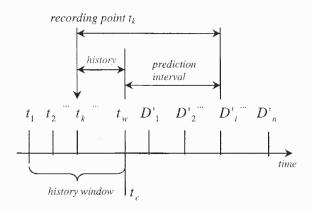

|   |      | 5.4.1 History Window Based Prediction                                                            | 97   |

|   |      | 5.4.2 Prediction-Enabled EDF Based Online Real-Time DVS Algorithm                                | 102  |

|   |      | 5.4.3 Prediction-Enabled Fixed Priority Based Online Real-Time DVS Algorithm                     | 106  |

|   |      | 5.4.4 Further Discussion on the Algorithms                                                       | 110  |

|   | 5.5  | Simulation Analysis                                                                              | 111  |

|   |      | 5.5.1 Simulation Settings                                                                        | 112  |

|   |      | 5.5.2 Simulation Results                                                                         | 113  |

| 6 | CO   | CLUSION                                                                                          | 119  |

| 7 | FU   | URE WORK                                                                                         | 121  |

# TABLE OF CONTENTS (Continued)

| Chapter                                                  | Page |

|----------------------------------------------------------|------|

| APPENDIX THE ADJUST OPERATION ON TIT-V TREE (FOR CASE 4) | 123  |

| REFERENCES                                               | 128  |

## LIST OF TABLES

| Table |                                             | Page |

|-------|---------------------------------------------|------|

| 3.1   | Complexity Analysis                         | 47   |

| 3.2   | Parameters for the Task Graph in Figure 3.1 | 50   |

| 3.3   | Simulation Settings(1)                      | . 53 |

| 3.4   | Simulation Settings(2)                      | . 53 |

| 4.1   | Complexity Analysis                         | . 77 |

| 4.2   | Simulation Settings(1)                      | . 80 |

| 4.3   | Simulation Settings(2)                      | . 81 |

| 4.4   | Simulation Settings(3)                      | . 81 |

| 5.1   | Simulation Settings                         | 113  |

## LIST OF FIGURES

| Figure | Page                                                                                 |

|--------|--------------------------------------------------------------------------------------|

| 2.1    | The TIT tree                                                                         |

| 2.2    | A TIT tree                                                                           |

| 2.3    | The TIT* tree                                                                        |

| 2.4    | Schedulability test by using TIT* tree                                               |

| 2.5    | Deadline-driven heuristic resource allocation algorithm                              |

| 2.6    | The feasibility test algorithm                                                       |

| 2.7    | The TIT-V tree                                                                       |

| 2.8    | Four cases                                                                           |

| 2.9    | The TIT-V tree based feasibility test algorithm                                      |

| 2.10   | Compute available vacancy                                                            |

| 2.11   | (a) and (b) compute $Available Vacancy$ and (c) TIT-V tree after inserting $T'_6$ 19 |

| 2.12   | The generic resource allocation algorithm                                            |

| 2.13   | Online admission control algorithm                                                   |

| 2.14   | The TIT-RL tree                                                                      |

| 2.15   | TIT-RL tree based online admission control algorithm                                 |

| 2.16   | Feasibility test                                                                     |

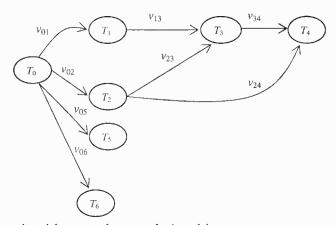

| 3.1    | Task graph with precedence relationships                                             |

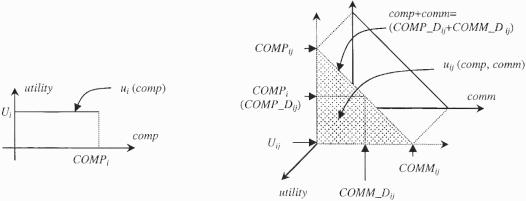

| 3.2    | Utility functions                                                                    |

| 3.3    | IAUASA scheduling algorithm                                                          |

| 3.4    | IAUASA scheduling                                                                    |

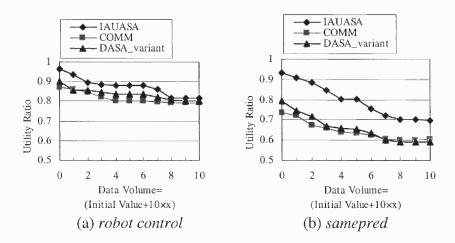

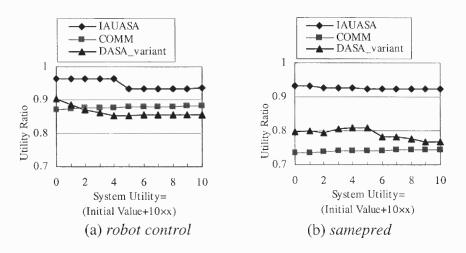

| 3.5    | Utility ratios achieved vary with the increment of data volume                       |

# LIST OF FIGURES (Continued)

| Figure | e Pa                                                                           | ge |

|--------|--------------------------------------------------------------------------------|----|

| 3.6    | Utility ratios achieved vary with the increment of the workload of computation | 55 |

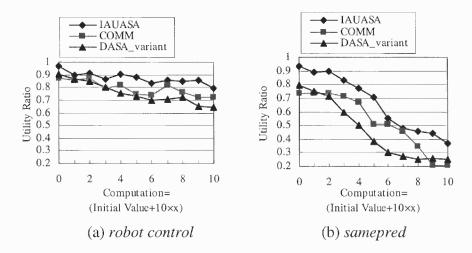

| 3.7    | Utility ratios achieved vary with the increment of the number of processors    | 55 |

| 3.8    | Utility ratios achieved vary with the increment of channel speed               | 56 |

| 3.9    | Utility ratios achieved vary with the increment of system utility              | 57 |

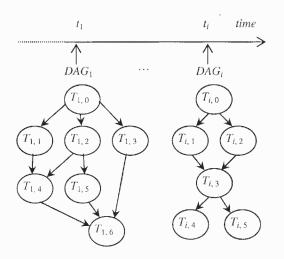

| 4.1    | Task graphs                                                                    | 52 |

| 4.2    | Utility function of scheduling element $E_{ij}$ 6                              | 54 |

| 4.3    | Two-level scheduling framework                                                 | 70 |

| 4.4    | Interplay-aware distributed resource scheduling algorithm                      | 14 |

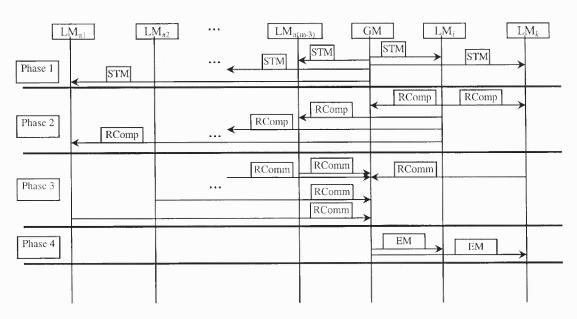

| 4.5    | Simplified message sequence chart for the normal case                          | 15 |

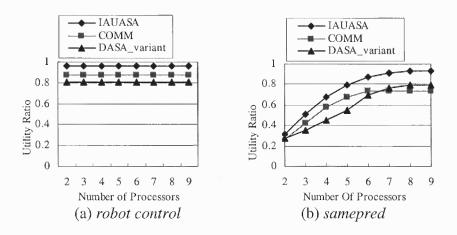

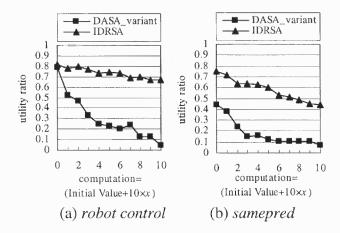

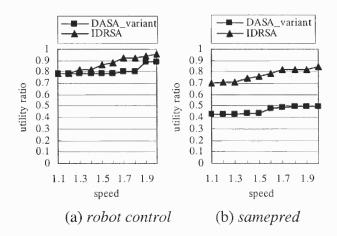

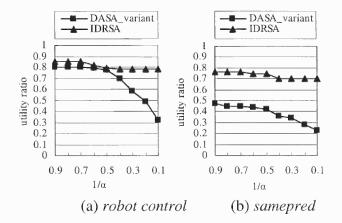

| 4.6    | Utility ratios achieved vary with the increment of the workload of computation | 32 |

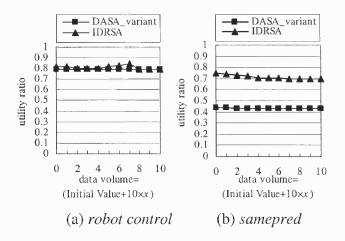

| 4.7    | Utility ratios achieved vary with the increment of data volume                 | 32 |

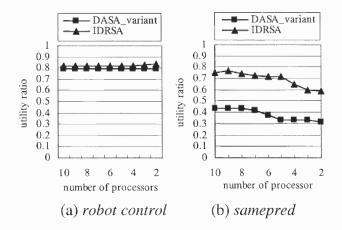

| 4.8    | Utility ratios achieved vary with the decrement of the number of processors 8  | 33 |

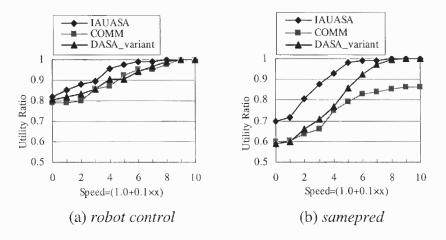

| 4.9    | Utility ratios achieved vary with the increment of channel speed               | 3  |

| 4.10   | Utility ratios achieved vary with the increment of interplay factor $\alpha$   | 34 |

| 5.1    | Schedulability analysis according to preemptive EDF policy                     | 15 |

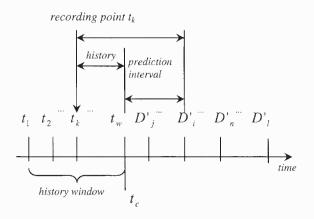

| 5.2    | History window based prediction for EDF policy                                 | 19 |

| 5.3    | History window based prediction for Fixed Priority policy                      | 0  |

| 5.4    | Power-aware prediction-enabled EDF algorithm                                   | 13 |

| 5.5    | Frequency analysis                                                             | 4  |

| 5.6    | Schedulability analysis                                                        | 6  |

# LIST OF FIGURES (Continued)

| Figure | e                                                                                        | Page  |

|--------|------------------------------------------------------------------------------------------|-------|

| 5.7    | Power-aware prediction-enabled fixed priority algorithm                                  | 107   |

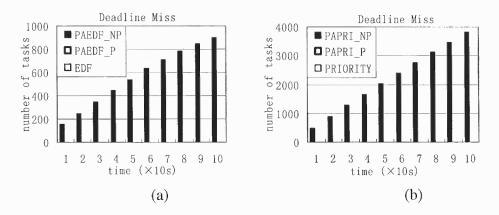

| 5.8    | Deadline miss with infinite levels of frequencies                                        | 114   |

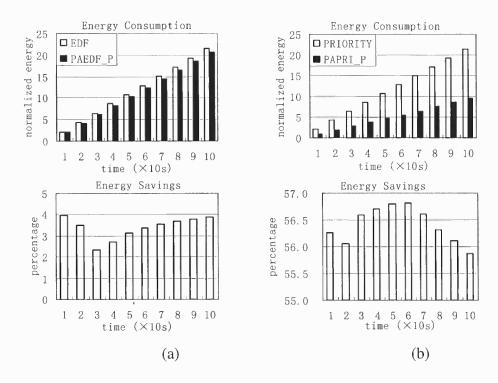

| 5.9    | Energy consumption and energy saving with infinite levels of frequencies                 | . 114 |

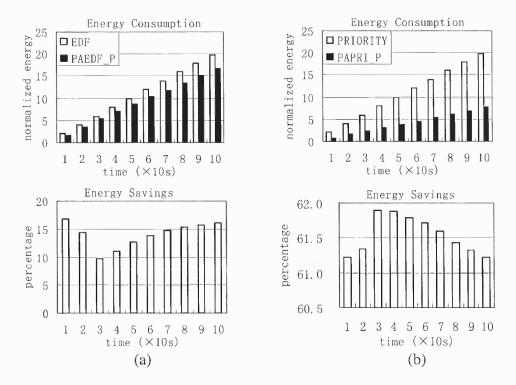

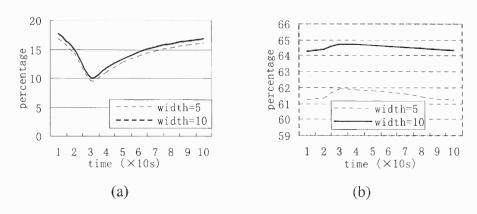

| 5.10   | Energy savings with infinite levels of frequencies under different history window widths | 115   |

| 5.11   | Energy consumption and energy savings with limited levels of frequencies                 | . 116 |

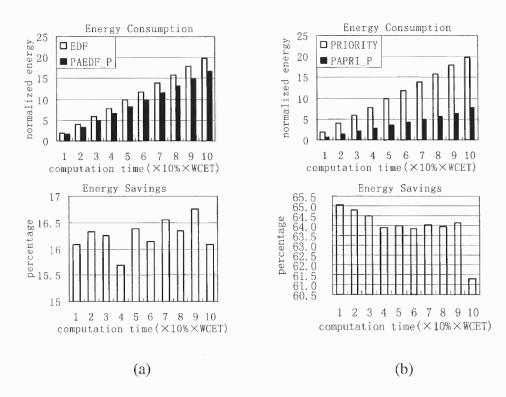

| 5.12   | Energy consumption and energy savings with varying execution/computation time            | . 117 |

### **CHAPTER 1**

#### INTRODUCTION

Real-time computer systems have wide applications in many fields in the real world, such processing, digital control, signal medical diagnosis and monitoring, telecommunication, industrial automation, military command and control, and multimedia. Unlike general purpose computer systems, the tasks to be performed by these real-time computer systems have timing constraints, and the services provided by realtime computer systems must be delivered in a timely way. Whether the tasks could be accomplished within the specified timing constraints and the services could be provided in a timely way depend on whether the resources in the systems could be managed efficiently and the requests of resources could be always satisfied sufficiently timely. This makes real-time resource management the core and critical task in almost all realtime computer systems.

### 1.1 Background

Over the past few years, real-time resource management has been extensively studied in various flavors. While a lot of problems could be dealt with by employing existing techniques, many important problems are in need of exploration. Among them, how to find appropriate data structures for building efficient real-time resource management did not receive too much attention in the past. However, solutions to this problem are of great importance in real-time systems in the sense that well-designed data structures not only make resource management efficient (thus improve system performance in reducing

complexity), but also make more resources available for applications (thus improve system performance in meeting timing constraints).

The other important problem is the model for the resource management in asynchronous real-time distributed systems, which are emerging in many domains, including defense, telecommunication and industrial automation, for the purpose of strategic mission management. These systems are distinguished in the sense that they must be able to accommodate significant run-time uncertainties that are inherent in their application environment and system resource states. This violates the static, deterministic, synchronous premises on which most classical/conventional real-time computing concepts, theorems, and techniques are founded. Hence, how to establish an appropriate model for resource management in these systems is a core task. Resource management in asynchronous real-time distributed systems has been explored for years. Up to now, lots of work has been conducted under Jensen's utility accrual models. These models are constructed based on the timeliness of computation or communication. Resource management under these models is limited due to the fact that they are inadequate for capturing the interplay between computation and communication, which are two main factors in asynchronous real-time distributed systems. Solutions to this problem will establish the foundations for more effective resource management in asynchronous real-time distributed systems.

Another important problem is concerned with the efficient power/energy management in those embedded real-time systems with random event/task arrivals. Most past and current work on power-efficient real-time resource management is based on classical/conventional task models, i.e., periodic, aperiodic and sporadic task models.

These models, however, are incapable of accommodating random task arrivals. A more general task model is needed to capture the characteristics of random task arrival, and corresponding foundations are needed for building power-efficient resource management in those embedded real-time systems.

### 1.2 Objectives

This dissertation explores the following techniques for the resource management in real-time systems: (1) new data structures, (2) new model and algorithms for asynchronous real-time distributed systems, and (3) new model, technique, and algorithms for embedded real-time systems.

The first objective is to establish new data structures for building efficient real-time resource management. Some new data structures are established and applied to the resource management of several classes of real-time systems. These new data structures not only help to construct efficient resource management, but also save processing resource and significantly improve system performance.

The second objective is to establish new utility accrual model for the resource management in asynchronous real-time distributed systems. The new model overcomes the inadequacy of existing utility accrual models and can fully capture the interplay between computation and communication, which are the two main factors in asynchronous real-time distributed systems. New resource allocation algorithms under the new model are developed. Extensive simulations show the excellence of these algorithms. The results validate the effectiveness of the new model for resource management in asynchronous real-time distributed systems.

The third objective is to establish new task model and foundations for power-efficient resource management in embedded real-time systems. Conventional task models are inadequate for accommodating the random (including burst) arrivals of tasks. The new general model adapts the concept of calculus curve from network calculus domain and uses calculus curves to characterize random event/task arrivals and system processing capacity. History window based prediction technique is established under the general task model. The prediction technique provides the foundation for online real-time Dynamic Voltage-frequency Scaling (DVS). Two online DVS algorithms are developed based on the prediction technique. Extensive simulations are conducted. Both algorithms exhibit excellent performance in energy saving.

### **CHAPTER 2**

#### TESTING INTERVAL TREES FOR REAL-TIME SCHEDULING SYSTEMS

In real-time systems, the efficiency of the resource Scheduling Module (SM) is of critical importance [1, 2, 3]. An efficient SM not only implies the overhead of the SM is low but also makes it possible to obtain better decisions on resource allocation without loss of system performance. Better decisions usually are more time-consuming and can be obtained only at the cost of system performance. Due to the stringent timing constraints and the high cost of analyzing and computing the optimal resource allocation decisions, some online real-time scheduling systems have to sacrifice the optimality of their decisions for the speed with which the decision can be computed [5, 6].

The efficiency of a real-time SM depends not only on how efficient the underlying algorithms employed in the SM are but also on how efficiently these algorithms are implemented. On one hand, a good algorithm with poor implementation may still be unacceptable in practice. On the other hand appropriate implementation of the algorithm can further improve the efficiency of the SM. In the past, how to apply some novel and effective data structures to the SMs so as to improve their efficiency did not receive much attention. The author believes that by introducing effective data structures, the efficiency of many real-time SMs could be improved, which in turn will help to improve the performance of the system. This is of great importance in the domain of *real-time* systems. The author is motivated to find novel and effective data structures to help construct efficient SMs. Because *feasibility analysis* (or schedulability analysis) is the critical part of a SM, The author will focus on how to find novel and effective data structures for conducting efficient feasibility test. It is easy to see that the main task of the

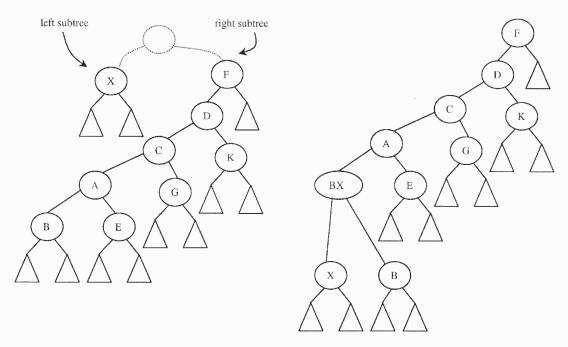

feasibility analysis is actually to check whether a group of intervals (corresponding to the execution of tasks) could be arranged without conflicts between them. Hence, the author first introduces the Testing Interval Tree (TIT), a balanced binary tree that is constructed based on intervals, and use it as the basic data structure. The author then extends this data structure for different uses. The first extension of TIT tree is the TIT\* tree, which does not rely on any specifics of the underlying scheduling/testing algorithm, and is a general data structure that can be applied to a wide variety of real-time scheduling systems to reduce the average cost of the schedulability test. The second extension of TIT tree is the Testing Interval Tree for Vacancy analysis (TIT-V), which is used to conduct vacancy (unoccupied intervals) analysis in some parallel/distributed real-time systems; whenever a task/message is to be added to the task/message set, the schedulability test computes the available vacancy for that task/message according to the current TIT-V tree. Lastly, the TIT tree is extended to the Testing Interval Tree for Release time and Laxity analysis (TIT-RL), which is used to conduct the admission control in a uni-processor based realtime service system; whenever a request arrives, the admission control component checks whether the requested service could be feasibly provided according to the current TIT-RL tree. Because the TIT trees can effectively reduce the cost of the corresponding feasibility/schedulability tests, they provide an effective approach to constructing efficient SMs.

### 2.1 Definition and Properties of the TIT Tree

Before proceeding to the discussion of the TIT tree, the author defines a simple task model, under which a task T is characterized by a triple (r, d, e), where r, e and d are the release time, the absolute deadline and the execution time of T, respectively.

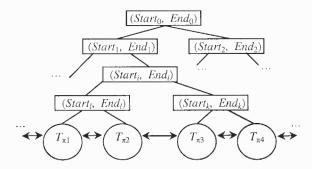

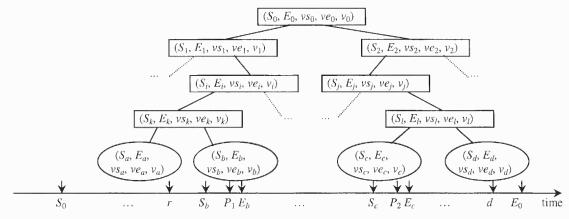

Figure 2.1 The TIT tree.

The TIT tree (Figure 2.1) is based on intervals and used for interval analysis. Its properties can be summarized as follows.

- (1) It is a balanced binary tree.

- (2) There are two types of nodes on it, i.e., the leaf nodes which represent tasks and the non-leaf nodes which represent intervals.

- (3) Every leaf node is characterized by a triple, which defines a valid interval for a task to execute. For example,  $(r_{\pi 1}, d_{\pi 1}, e_{\pi 1})$  defines a valid interval  $(r_{\pi 1}, d_{\pi 1})$  for  $T_{\pi 1}$  with start point  $r_{\pi 1}$  and end point  $d_{\pi 1}$ .

- (4) Every non-leaf node defines an interval. For example, (*Start<sub>i</sub>*, *End<sub>i</sub>*) defines an interval with start point *Start<sub>i</sub>* and end point *End<sub>i</sub>*.

- (5) The interval of a non-leaf node covers those of its children. For example,  $(Start_i, End_i)$  covers  $(Start_l, End_l)$  and  $(Start_k, End_k)$ , and  $(Start_l, End_l)$  covers  $(r_{\pi 1}, d_{\pi 1})$  and  $(r_{\pi 2}, d_{\pi 2})$ , where  $r_{\pi 1}$  and  $d_{\pi 1}$  are the release time and absolute deadline of task  $T_{\pi 1}$ , respectively, and  $r_{\pi 2}$  and  $d_{\pi 2}$  are the release time and absolute deadline of task  $T_{\pi 2}$ , respectively.

- (6) The leaf nodes are placed in ascending order of their release times, and if more than one node has identical release time, they are placed in ascending order of their deadlines.

- (7) For any non-leaf node, the interval of its left child is smaller than that of its right child, compared first on start point and then on end point if needed. For example, for  $(Start_i, End_i)$ , either  $(Start_l < Start_k)$  or  $((Start_l = Start_k))$  and  $(End_l \le End_k)$  holds.

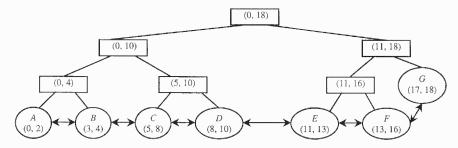

Figure 2.2 A TIT tree.

There are two basic operations on the TIT tree, i.e., *Insert* and *Delete/Remove*.

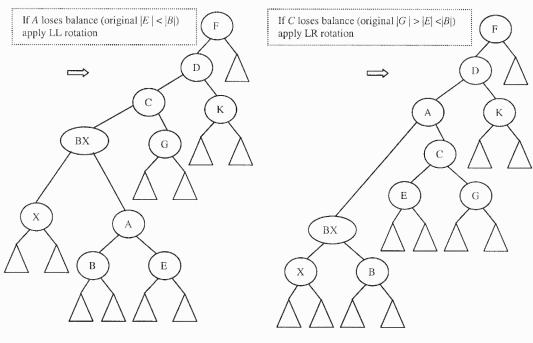

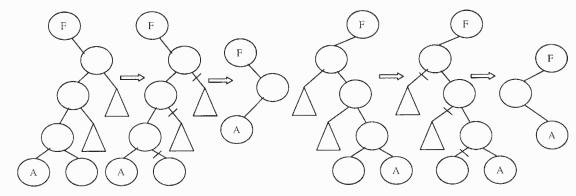

*Insert* is invoked to insert a new task into the tree. It is accomplished in two steps. At the first step, it starts from the root of the TIT tree and searches down the tree to find an appropriate location where the new task should be placed. This step will identify a non-leaf node, and the new task should be inserted as its child. At the second step, the new task is put at the location that is identified in the first step. If the identified non-leaf node has only one child, *Insert* only needs to insert the new task as the left or right child of that node; otherwise, the identified node is split into two nodes, and the intervals of the two nodes are reset accordingly. Figure 2.2 illustrates a TIT tree. Suppose that a new task N (12, 17) is to be inserted into the tree, node (11, 16) will be split into two nodes (say O1 and O2); one of the nodes (say O1) and F(13, 16) will become the left and right children of the other node (i.e., O2), respectively. E(11, 13) and N(12, 17) will become the left and right children of O1, respectively. The intervals of O1 and O2 are both set to (11, 17) so as to cover the intervals of their children. If the split causes the TIT tree to lose balance, rotation is needed to rebalance the tree. Throughout this chapter and the Appendix, the rotation operation is similar to that with an AVL tree [7]. Insert also includes a procedure to update the intervals of the nodes on the path starting from the parent of the new task to the root of the tree.

**Delete/Remove** operation is invoked to delete a leaf node from the TIT tree. For this operation, two cases may exist. In the first case, it only needs to delete the leaf node, and no other operations are involved. In the second case, the removal of the leaf node causes the TIT tree to lose balance, and *rotation*(s) is needed to rebalance the tree. Similar to *Insert*, *Delete* also includes a procedure to update related intervals.

It is easy to see that for a TIT tree containing n leaves, the height of the tree is bounded by  $O(\log n)$ . For both *Insert* and *Delete*, their complexities are bounded by the height of the tree, i.e.,  $O(\log n)$ .

### 2.2 TIT\* Tree and Its Applications to Real-Time Scheduling Systems

Schedulability tests are usually performed by calling the underlying scheduling algorithm to preprocess the whole task/message set. (In this section, the author uses tasks to describe TIT\* tree, and illustrates how to apply TIT\* tree to the schedulability test of tasks. The basic principles also apply to the schedulability test in message scheduling.) The main problem with this approach is that whenever a task is added to the task set, to test the schedulability of the new task set, the system needs to process the whole task set. The overhead of the test will be very high if the task set constantly contains a large number of tasks (this is very likely in an online dynamic environment, where new tasks are constantly added to the system). This overhead, however, may be reduced due to the fact that the joining of the new task may influence only a limited number of tasks, not the whole task set. Test on the whole task set is needed only in the worst case.

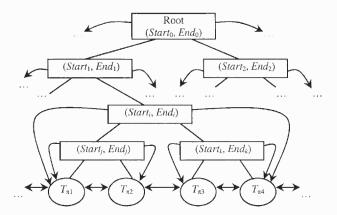

Figure 2.3 The TIT\* tree.

The TIT\* tree proposed here fully realizes this fact. Whenever the system performs the test, it only needs to test the schedulability of the tasks that correspond to a subtree of a TIT\* tree, which corresponds to the whole task set. The TIT\* tree (Figure

- 2.3) is an extension of the TIT tree, and inherits all the properties of TIT tree including the following property.

- (1) Every non-leaf node contains two pointers. One pointer points to the first task that is bounded by the interval of this node, and the other pointer points to the last task that is bounded by the interval of this node.

To see how to apply the TIT\* tree to the schedulability test, let's look at the example in Figure 2.4. For simplicity, the "first task" and "last task" pointers of all non-leaf nodes are omitted except those of the node with interval (11, 18). Suppose that currently there are seven unfinished tasks in the scheduling queue (i.e., A, B, C, D, E, F, and G) and another task H (15, 20) arrives, the schedulability test is performed in two steps.

- Step 1: Find the set of tasks that may conflict with task *H*. This is accomplished by a checking procedure that starts from the root. At each node, it checks to see whether the interval of this node overlaps with that of task *H*. If the two intervals overlap, it checks the children of this node. This procedure repeats until it reaches a leaf node or a non-leaf node that satisfies: (1) both of its children overlap with task *H*, or (2) one of its child overlaps with task *H* and its children overlap with each other. In the case that even the root does not overlap with *H*, the schedulability test is not needed at all. (No task currently in the system conflicts with *H*.) For the above example, the checking procedure ends at the node with interval (11, 18).

- **Step 2:** Once it identifies the node and hence the corresponding set of tasks, the schedulability test is conducted against this set of tasks plus H. In the above example, a schedulability test on tasks E, F, G and H is performed.

Figure 2.4 Schedulability test by using TIT\* tree.

The average cost of the TIT\* tree based schedulability test is analyzed as follows. Suppose that there are n tasks currently on a TIT\* tree, and the underlying task scheduling algorithm is preemptive Earliest Deadline First (EDF). The average cost of the schedulability test is computed as follows. (The average cost includes two parts, i.e., the cost of search and that of EDF to process the specified task set. For a TIT\* tree containing n tasks, its height is bounded by  $(\log n+2)$ . At height i, the number of nodes on a TIT\* tree is at most  $2^i$ . The search will take (i+1) steps, and the cost of EDF will be  $O(\frac{n}{2^i}\log\frac{n}{2^i})$ .)

Average Cost =

$$O(\frac{\sum_{i=0}^{(\log n+2)} 2^i ((i+1) + \frac{n}{2^i} \log \frac{n}{2^i})}{\sum_{i=0}^{(\log n+2)} 2^i}) = O((\log n)^2)$$

By comparison, the average cost of the schedulability test without the TIT\* tree will be  $O(n\log n)$ .

It is easy to see that the advantage of TIT\* tree lies in that it helps to reduce the number of tasks to be tested, and thus reduce the average cost of the schedulability test. Additionally, the advantage of TIT\* tree does not rely on any specifics of the underlying scheduling algorithm, and this makes it a general data structure and applicable to a wide variety of scheduling systems with different scheduling policies. For example, the underlying scheduling algorithm could be the preemptive or non-preemptive version of Highest Priority First, Least Slack Time First, Highest Utility/Benefit First, or some other similar algorithm (the average cost of the schedulability test is still  $O((\log n)^2)$ ). Further study reveals that the TIT\* tree is applicable to those schedulability tests that need to

process the whole task set whenever a task is to be added to the task set, no matter whether the test is conducted online or offline, and whether the underlying scheduling algorithm is preemptive or non-preemptive.

### 2.3 TIT-V Tree and Its Applications to Real-Time Scheduling Systems

Consider a parallel/distributed real-time system containing *m* processors. There are *n* independent tasks to be dispatched to these processors. Suppose every task has a release time, an absolute deadline and the workload to be finished by it. Every task can be replicated, and the workload of the task can be partitioned and distributed to these replicas. Replicas are dispatched to processors (but more than one replica of the same task can not be dispatched to the same processor). Tasks/replicas are preemptively scheduled according to their deadlines on every processor. The objective is to find a mapping of tasks/replicas to processors such that the *deadline-satisfied ratio* (the ratio of the number of tasks whose deadlines are met to the total number of tasks) is maximized.

Because this problem is NP-hard, only heuristic/approximation algorithms can be employed in the real world. A simple heuristic approach is to first sort the tasks in ascending order of deadline and then test the feasibility of tasks one by one in that order. On every processor, tasks are also processed according to their deadlines. It turns out that this heuristic can be well applied to real system to solve the aforementioned and similar problems. For example, in [8], a best-effort algorithm called *DPR* is constructed according to this heuristic to maximize the deadline-satisfied ratio in a distributed real-time system, and another algorithm based on similar heuristic is also constructed to

achieve the same goal. The highest level framework of this heuristic is listed in Figure 2.5, which is similar to the highest level framework in [8].

```

Input: \Gamma = \{T_1, T_2, ..., T_n\}; /*the task set to be processed*/

Output: resource allocation result;

1 Sort tasks T_1, T_2, ..., T_n in ascending order of deadline;

2 For T = T_1 to T_n do /*T_1 ... T_n are in ascending order of deadline*/

3 Determine_Replicas_Processors(T); /*determine the number of replicas and the processors for task T */

```

Figure 2.5 Deadline-driven heuristic resource allocation algorithm.

```

Determine_Replicas_Processors (T)

Input: T;

/*the task to be processed */

Output:

determine the number of replicas and the processors for T if enough resource is available for it,

otherwise do not allocate any resource for it;

Variables:

PT = \emptyset:

/*the set of processors that have NO replica of T */

/*the set of all processors*/

PR = \phi;

/*the set of processors that HAVE replicas of T */

MinResponse;

/*the minimum response time*/

PID;

/*ID of the processor that has the minimum response time*/

MinResponse = \infty;

PT=P-PR;

If (PT == \emptyset)

Return FAILURE;

For each processor q \in PT do

Response Time = EDF_Analyze Response (q, T, (|PR|+1)); /*(|PR|+1) is the current number of processors that

will get a replica of T, and the workload of the replica that is to be

tested on q is the total workload of T divided by (|PR|+1)*/

If (ResponseTime < MinResponse)

MinResponse=ResponseTime;

PID=q;

10 PT = PT - \{PID\};

11 PR = PR + \{PID\};

12 If (MinResponse > T.d)

Goto step 1;

13 For each processor q \in PR - \{PID\} do

If (EDF_AnalyzeResponse (q,T,|PR|) > T. d) Goto step 1;

15 Return SUCCESS:

```

Figure 2.6 The feasibility test algorithm.

The framework of the feasibility test ( $Determine\_Replicas\_Processors()$ ) is listed in Figure 2.6. It is similar to the feasibility test contained in [8]. The subroutine  $EDF\_AnalyzeResponse()$  contained in  $Determine\_Replicas\_Processors()$  uses Earliest Deadline First (EDF) rule to perform response time analysis (because tasks on every processor are processed according to EDF rule). It is easy to see that the complexity of this feasibility test is  $O(m^2n\log n)$ , given n independent tasks and m processors. (In the worst case, a task T may have m replicas. To decide one replica, the test tries every processor that has no replica of T. The test takes  $O(n\log n)$  time on every processor. Hence the total cost is  $O(m^2n\log n)$ .) In the following subsection, the TIT-V tree is introduced to construct more efficient feasibility tests.

### 2.3.1 Definition and Properties of the TIT-V Tree

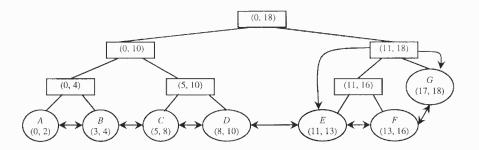

In a TIT-V tree, a *vacancy* is an interval that is not occupied by any task. Every vacancy has a left-endpoint and a right-endpoint. The TIT-V tree (Figure 2.7) is used for vacancy analysis. Its properties can be summarized as follows.

Figure 2.7 The TIT-V tree.

- (1) A TIT-V tree is an extension of the TIT tree.

- (2) A node in a TIT-V tree is characterized by a 5-tuple  $(S_i, E_i, vs_i, ve_i, v_i)$  (Figure 2.7), where  $S_i$  and  $E_i$  are the start and end points of interval  $(S_i, E_i)$ ,  $vs_i$  and  $ve_i$

- are the left-most and right-most points of the vacancies contained in  $(S_i, E_i)$ , and  $v_i$  is the total length of the vacancies contained in  $(vs_i, ve_i)$  (please note that there may be more than one vacancy within  $(vs_i, ve_i)$ , and they are separated by some intervals that are occupied by tasks).

- (3) For a non-leaf node, the interval of its left child is smaller than that of its right child, compared on start point. For example, for node  $(S_k, E_k, vs_k, ve_k, v_k)$ , the interval of its left child  $((S_a, E_a))$  is smaller than the interval of its right child  $((S_b, E_b))$ , i.e.,  $(S_a < S_b)$ .

- (4) Given a non-leaf node in a TIT-V tree, the interval defined by its left child never overlaps with that by its right child, and the end point of its left child is equal to the start point of its right child. For example, in Figure 2.7,  $(E_a = S_b)$  holds.

- (5) For a non-leaf node, its parameters are decided according to those of its child/children. For example, in Figure 2.7, for node  $(S_k, E_k, vs_k, ve_k, v_k)$ , the following holds:  $vs_k = Min\{vs_a, vs_b\} = vs_a, ve_k = Max\{ve_a, ve_b\} = ve_b, v_k = (v_a + v_b), S_k = Min\{S_a, S_b\} = S_a$  and  $E_k = Max\{E_a, E_b\} = E_b$ .

### 2.3.2 Operation on TIT-V Tree and Its Complexity

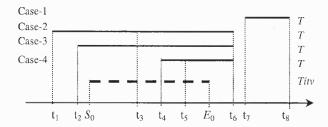

Figure 2.8 Four cases.

The main operation on the TIT-V tree is Adjust. It is invoked when a task (say T=(r, d, e)) is to be inserted into a TIT-V tree (say Titv). Titv needs to be adjusted because some vacancies of it may be occupied by T. The main work contained in Adjust is to find the left-most point of vacancy  $P_1$  (Figure 2.7) and the right-most point of vacancy  $P_2$ , such that  $(r \le P_1 \le P_2 \le d)$ , and the total length of the vacancies within interval  $(P_1, P_2)$  is equal to e. Once  $P_1$  and  $P_2$  are identified, all the vacancies within  $(P_1, P_2)$  will be occupied by T. Titv needs to be adjusted according to the remaining vacancies and those vacancies, created due to T. To be more specific, four cases may exist (Figure 2.8).

Case 1:  $T = (t_7, t_8, e)$ , and  $(t_7, t_8)$  does not overlap with the interval defined by Titv (i.e.,  $(S_0, E_0)$ ). So, a new vacancy (i.e.,  $(E_0, t_7)$ ) needs to be appended to the right side of Titv. Besides, a leaf node created according to T also needs to be appended to the right side of the tree.

Case 2:  $T = (t_1, t_3, e)$ , and it can finish before  $S_0$ . A new leaf node needs to be created and appended to the left side of the tree. Please note that if  $T = (t_1, t_6, e)$ , another vacancy  $(E_0, t_6)$  needs to be appended to the right side of Titv.

Case 3:  $T=(t_2, t_3, e)$ , and it can not finish before  $S_0$  (i.e., part of the vacancies contained in  $(S_0, E_0)$  will be occupied by T). the system needs to find the right-most point that will be occupied by T and adjust the tree accordingly (because all the vacancies between  $t_2$  and that right-most point will be occupied by T). Similar to case 2, if  $T=(t_2, t_6, e)$  and it can finish before  $E_0$ , another vacancy  $(E_0, t_6)$  needs to be appended to the right side of Titv.

Case 4:  $T = (t_4, t_5, e)$ , and T will occupy some vacancies contained in  $(S_0, E_0)$ . This is the most complicated case. The system needs to find the left-most point and the right-most point that will be occupied by T and adjust the tree accordingly (because the vacancies between that left-most point and that right-most point will be occupied by T). Similar to case 2 and case 3, if  $T = (t_4, t_6, e)$  and it can finish before  $E_0$ , another vacancy  $(E_0, t_6)$  needs to be appended to the right side of the TIT-V tree. (Please refer to the Appendix for more details about the process on this case. For the other cases, their processes can be easily constructed by employing subroutines in the Appendix.)

Because the complexity of every operation contained in *Adjust* is bounded by the height of the TIT-V tree, the complexity of *Adjust* is bounded by the height of the tree.

Given a TIT-V tree containing n leaves, the height of the tree is bounded by  $O(\log n)$ . Hence, the complexity of Adjust is  $O(\log n)$ .

### 2.3.3 Using TIT-V Tree to Construct Feasibility Test for DDRAA

```

Determine_Replicas_Processors (T)

Input: T;

/*the task to be processed*/

Output:

determine the number of replicas and the processors for T if enough resource is available for it,

otherwise do not allocate any resource for it;

Max=0;

For p=1 to m do

/* test T on processor 1 to processor n^*/

Result[p]. Available Vacancy=Compute_Vacancy (p, T); /*compute the available vacancies on processor p^*/

Result [p]. NodeID= p;

/*record the processor ID*/

If (Max < Result [p]. Available Vacancy)

Max= Result [ p]. AvailableVacancy;

Node=p;

/*record the processor that has the maximum available vacancies*/

If (Max \ge T. e)

Dispatch T to Node;

/*one node is enough*/

10

Return;

11 Sort Result [ ] in descending order of Available Vacancy;

12 Num = 0;

13 Sum=0;

14 For i=1 to m do

Sum = Sum + Result [i]. Available Vacancy;

15

16

If (Sum \geq T.e)

17

Num=i:

Break for loop;

18

19 If (Sum < T.e)

20

Return;

/*no resource is allocated for T */

21 Else

22

Sum=0;

23

24

25

26

27

For i=1 to (Num-1) do

Make a replica of T, and dispatch it to node Result [ i ]. NodeID;

The processing time of this replica is Result [i]. Available Vacancy;

Sum = Sum + Result[i]. Available Vacancy;

Make a replica of T, and dispatch it to node Result [ Num ]. NodeID;

The processing time of this replica is set to (T. e - Sum);

Return;

```

**Figure 2.9** The TIT-V tree based feasibility test algorithm.

Now, the TIT-V tree is employed to reconstruct the feasibility test for *DDRAA* (listed in Figure 2.5). The pseudo code of the TIT-V tree based feasibility test is listed in Figure 2.9 and Figure 2.10.

$Determine\_Replicas\_Processors(T)$  (Figure 2.9) is used to determine the number of replicas of T and the processors to which these replicas can be feasibly dispatched.

$Compute\_Vacancy(p, T)$  (Figure 2.10) is used to compute the total length of the available vacancies for T on processor p.

```

Compute_Vacancy (p, T)

Input:

/*the processor ID*/

/*the task to be tested */

T:

Output: Available Vacancy; /*the available vacancies within the interval (T. r, T. d) on processor p*/

/*Titv is the TIT-V tree constructed according to the tasks on p^*/

1 Case 1: (Titv is EMPTY) or (Titv. Root. S \ge T. d) or (Titv. Root. E \le T. r)

Available Vacancy = (T. d - T. r);

3 Case 2: (other cases)

If (Titv. Root. S > t. r)

If (Titv. Root. E < t.d)

Available Vacancy=(Titv. Root. S - T. r) + Titv. Root. v + (T. d - Titv. Root. E);

Else

Travel down the tree, compute the total length of vacancies within (Titv-Root-S, T.d), and record it in Vacancy;

Available Vacancy = (Titv. Root. S - T. r) + Vacancy;

10 Else

If (Titv. Root. E < t.d)

11

12

Travel down the tree, compute the total length of the vacancies that lie at the left side of T. r (these vacancies

can not be occupied by T), and record it in Uncovered_v;

13

AvailableVacancy=(T. d - Titv. Root. E) + (Titv. Root. v - Uncovered_v);

14

Else

15

Travel down the tree, compute the total length of the vacancies that lie at the left side of T \cdot r (these vacancies

can not be occupied by T), and record it in Uncovered_v;

16

Travel down the tree, compute the total length of vacancies within (Titv.Root.S, T.d), and record it in Vacancy;

AvailableVacancy= Vacancy - Uncovered_v;

18 Return (AvailableVacancy);

```

Figure 2.10 Compute available vacancy.

It is easy to see the complexity of  $Compute\_Vacancy()$  is bounded by the height of the TIT-V tree, i.e.,  $O(\log n)$ . Hence, the  $for \log (Figure 2.9)$  from step 2 to step 7 runs in  $O(m\log n)$ . The sorting in step 11 can be done in  $O(m\log n)$ . Because the Adjust operation on a TIT-V tree can be finished in  $O(\log n)$  time, the complexity of steps 23–28 is  $O(m\log n)$ . (In the worst case, every processor gets a replica of T, the corresponding TIT-V tree is adjusted, and there are at most m processors.)

Thus the complexity of  $Determine\_Replicas\_Processors()$  is  $O(m \log n + m \log m)$ . Compared to  $O(m^2 n \log n)$ , this is a big improvement.

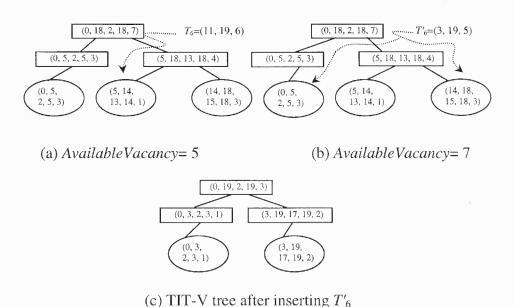

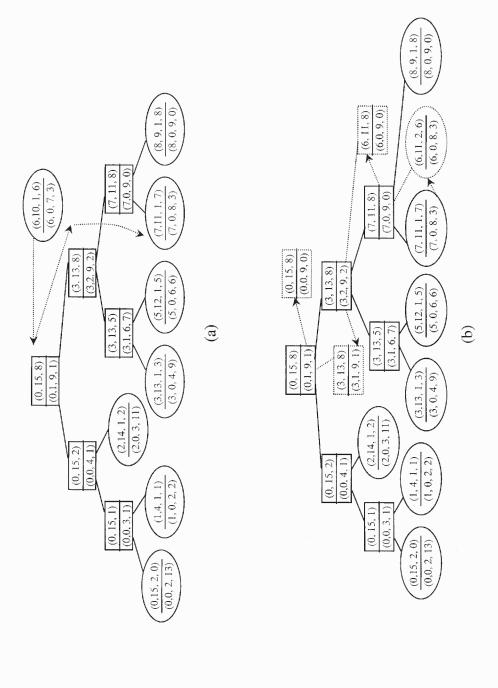

Figure 2.11(a) and Figure 2.11(b) show the computations of available vacancies for task  $T_6$ =(11, 19, 6) and task  $T'_6$ =(3, 19, 5) based on a given TIT-V tree. (This tree is constructed by inserting tasks  $T_1$ = (0, 10, 2),  $T_2$ = (5, 13, 2),  $T_3$ = (14, 16, 1),  $T_4$ = (10, 17, 2) and  $T_5$ = (6, 18, 4) into an empty TIT-V tree one by one.). As is shown the total length of the available vacancies for  $T_6$  is 5 time units while that for  $T'_6$  is 7 time units. Figure 2.11(c) is the adjusted TIT-V tree after inserting task  $T'_6$ .

Figure 2.11 (a) and (b) compute Available Vacancy and (c) TIT-V tree after inserting  $T'_{6}$ .

**Theorem 2.1** Under DDRAA, a replica T = (r, d, e) can be feasibly scheduled on a processor p if and only if the total length of the available vacancies returned by Compute\_Vacancy(p,T) is equal to or larger than e.

**Proof:**  $\leftarrow$  If T is schedulable under preemptive EDF on processor p (and no task misses its deadline), this certainly implies that there are enough vacancies within (r, d) for accommodating T. Because  $Compute\_Vacancy(p,T)$  always computes the total length of the available vacancies within (r, d), the AvailableVacancy returned by  $Compute\_Vacancy(p, T)$  will be equal to or larger than e.

$\rightarrow$  (1) Before the process on replica T, all tasks (or replicas) on processor p are schedulable under preemptive EDF. The process on T will have no influence on those tasks because tasks are processed in ascending order of their deadlines. Hence those tasks will still be schedulable, and they will occupy the same intervals even if T is dispatched to processor p. (2)  $Compute\_Vacancy(p,T)$  always computes the total length of the available vacancies within (r, d). If the total length returned by it is equal to or larger than e, this implies that enough vacancies can be found for T. Obviously, it is safe to conclude that T will be schedulable under preemptive EDF.

**Theorem 2.2** With TIT-V tree, the complexity of Compute\_Vacancy() is O(logn), and the complexity of Determine\_Replicas\_Processors() is O(mlogn+mlogm), given n tasks and m processors.

**Proof:** This can be proved by previous complexity analysis.

# 2.3.4 Using TIT-V Tree to Construct Feasibility Test for a Generic Resource Allocation Algorithm

Further study shows that the TIT-V tree can be applied to a class of real-time scheduling systems. Figure 2.12 is the framework of a generic resource allocation algorithm. It is similar to the frameworks in [8, 9, 10, 11, 12, 13, 14]. This algorithm can be instantiated to achieve different objectives, e.g., maximizing deadline-satisfied ratio [8], maximizing utility/benefit [9, 10, 11, 12, 13, 14] (in this case, every task is associated with a utility value), maximizing deadline-satisfied ratio of the tasks with high priorities (in this case, every task is associated with a priority), etc. Accordingly, a scheduling rule is applied to every processor. To maximize deadline-satisfied ratio, EDF is applied; to maximize utility, a utility based discipline such as *DASA* [15] is applied; to maximize the deadline-satisfied ratio of the tasks with high priorities, the highest priority first rule is applied.

The sorting in *GRAA* (see below) will sort tasks according to the objective. For example, if the objective is to maximize utility, tasks are sorted in non-increasing order of utility value; if the objective is to maximize the deadline-satisfied ratio of the tasks with

high priorities, tasks are sorted in non-increasing order of priority, etc. *GRAA* uses the same *Determine\_Replicas\_Processors*() as that in Figure 2.9, which in turn uses the same *Compute\_Vacancy*() as that in Figure 2.10.

```

GRAA(\Gamma)

Input: \Gamma = \{T_1, T_2, ..., T_n\}; /*the task set to be processed*/

Output: resource allocation result;

1. Sort tasks T_1, T_2, ..., T_n according to the objective;

2. For T = T_1 to T_n do /* process tasks in sorted order */

3. Determine_Replicas_Processors(T);

```

Figure 2.12 The generic resource allocation algorithm.

**Theorem 2.3** Under an instantiated GRAA, a replica T = (r, d, e) can be feasibly scheduled on a processor p if and only if the total length of the available vacancies returned by Compute\_Vacancy(p,T) is equal to or larger than e.

**Proof:** The proof is similar to that of Theorem 2.1 except that tasks are now processed according to the objective of the instantiated *GRAA*.

**Theorem 2.4** Under an instantiated GRAA, the complexity of Compute\_Vacancy() is  $O(\log n)$ , and the complexity of Determine\_Replicas\_Processors() is  $O(m\log n + m\log m)$ , given n tasks and m processors.

**Proof:** Because the instantiated *GRAA* uses the same *Compute\_Vacancy()* and the same *Determine\_Replicas\_Processors()* as those used in *DDRAA*, Theorem 2.4 holds.  $\Box$

# 2.4 TIT-RL Tree and Its Applications to Real-Time Scheduling Systems

This section studies TIT-RL tree and its application to the online admission control in a real-time system. Previous work on how to use novel data structures to improve the efficiency of online admission control can be found in [16]. There, an augmented red-black tree [7] is used for a real-time service system.

Consider an open system that is designed to provide online real-time services for customers. Customers send requests to the system and specify the types of the services

and the time intervals within which the services are needed. This system can be viewed as a model extracted from some applications such as online media service, call admission and other service [16, 17, 18, 19, 20, 21]. The system will enforce admission control over the requests. The policy of the admission control is simple: if a requested service can be feasibly provided, the request is admitted, and a corresponding task will be created to provide the specified service within the specified interval, otherwise, it is rejected. Suppose tasks are executed non-preemptively, and the system aims to (1) minimize the max-flow (i.e., the maximum response time) [21] and (2) maximize the number of accepted requests. Because this is an online system, and it has no idea about the future requests, it employs some heuristics to process the requests. To achieve the first objective, the system always processes a task (created due to a request) at the earliest available time (but never earlier than its release time). The point behind this heuristic is that the online First In First Out (FIFO) discipline is optimal in minimizing max-flow for single processor [21]. To achieve the second objective, it tries to accept every request whenever possible since the system has no idea about the future requests.

Accordingly, the online admission control algorithm (ACA) can be constructed as Figure 2.13. ACA is used to check whether a new task T(r, d, e) (created due to a new request) can be safely accepted (T can be finished within interval (r, d), and no accepted tasks miss their deadlines), given that there are n accepted tasks, including those that have already been released and those that haven't been released.

Admitted tasks will be put at the appropriate positions in the task queue. Whenever a task completes, the task scheduler always picks the next task from the head of the queue for execution.

```

ACA(T,\Gamma)

Input:: T;

/*the task to be tested*/

\Gamma = \{T_1, T_2, \ldots, T_n\};

/*the set of the admitted tasks*/

Output: accept or reject T;

/*find the appropriate position of T according to its release time*/

1 k= Position (T, \Gamma);

2 Check the feasibility of putting T at the kth position;

3 If (FEASIBLE)

Insert T into the task queue at the kth position;

Return FEASIBLE; /*T is accepted */

For i=(k+1) to n do

Check the feasibility of putting T at the ith position;

If (FEASIBLE)

10

Insert T into the task queue at the ith position;

Return FEASIBLE;

11

/*T is accepted */

12 Return INFEASIBLE;

/*T is rejected */

```

Figure 2.13 Online admission control algorithm.

It is easy to see, the complexity of ACA is  $O(n^2)$ . (Step 1 will take  $O(\log n)$  time by using binary search; step 2 will take O(n) time because the system needs to check all those tasks that are ordered after T; step 7 will be executed (n-k-1) times in the worst case; hence the complexity of steps 7 and 8 will be  $O(n^2)$ .)

In the next subsection, the TIT-RL tree is introduced to reduce the complexity of *ACA*.

#### 2.4.1 Definition and Properties of the TIT-RL Tree

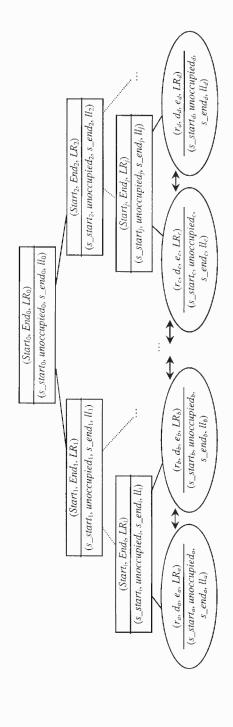

The TIT-RL tree (Figure 2.14) is an extension of the TIT tree, and it is used for release time and laxity analysis. A TIT-RL tree has all the properties of a TIT tree except the following.

(1) A non-leaf node in the TIT-RL tree is characterized by a triple (Start, End, LR) and a 4-tuple (s\_start, unoccupied, s\_end, ll). Start and End are the start and end points of interval (Start, End), and LR (Last Release time) is the release time of the task that is last released within (Start, End). s\_start and s\_end identify the start and end points of current schedule within (Start, End). unoccupied is the total unoccupied time units within (s\_start, s\_end) (please note that this interval is contained in (Start, End) and is not necessarily equal

to interval (Start, End)), and ll (largest laxity) is the largest laxity of the schedule within (s\_start, s\_end). The largest laxity of a schedule within (s\_start, s\_end) is defined as the maximum number of time units that the schedule can be pushed backwards without causing any task to lose its deadline. This implies that a task with that much of processing time can be safely inserted at s\_start without causing any task to miss its deadline.

(2) The definition of a leaf node is similar to that of a non-leaf node except that the triple (Start, End, LR) is replaced with a 4-tuple (r, d, e, LR) (where r, d and e are the release time, absolute deadline and execution time of a task T, respectively). Please note that the LR in a leaf node is always set to the r of this node. Although it is not useful for a leaf node, it will facilitate the operations on the TIT-RL tree.

For a leaf node, its parameters are decided as follows.

```

LR= s_start= r;

unoccupied= 0;

s_end= (r+e);

ll= [d-(r+e)];

```

(In the following discussion, for a leaf node, its r corresponds to the Start, and its d corresponds to the End.)

For a non-leaf node, its parameters are determined according to those of its child (children). Given a non-leaf node *Parent* having two children *Node*1 and *Node*2, its parameters are determined as follows.

```

Parent.Start = Min\{Node1.Start, Node2.Start\} \qquad \qquad --(A1) \\ Parent.End = Max\{Node1.End, Node2.End\} \qquad --(A2) \\ Parent.LR = Max\{Node1.LR, Node2.LR\} \qquad --(A3) \\ Parent.s\_start = Min\{Node1.s\_start, Node2.s\_start\} \qquad --(A4)

```

For the *s\_end*, *unoccupied* and *ll* of *Parent*, they depend on the relationship between interval (*Node1.s\_start*, *Node1.s\_end*) and interval (*Node2.s\_start*, *Node2.s\_end*). To be more specific, four cases exist.

```

Case 1: (Node1.s\_end \le Node2.s\_start). They are obtained according to (A5.1), (A6.1) and (A7.1), respectively.

Parent.s\_end= Node2.s\_end —(A5.1)

Parent.unoccupied= (Node1.unoccupied+Node2.unoccupied+Node2.s\_start-Node1.s\_end) —(A6.1)

Parent.ll= Min\{Node1.ll, (Node1.unoccupied+Node2.ll+(Node2.s\_start-Node1.s\_end))\} —(A7.1)

```

```

Case 2: (Node2.s\_end \le Node1.s\_start). They are obtained according to (A5.2),

(A6.2) and (A7.2), respectively.

Parent.s_end=Node1.s_end

-(A5.2)

Parent.unoccupied= (Node1.unoccupied+ Node2.unoccupied+

Node1.s_start-Node2.s_end)

-(A6.2)

Parent.ll= Min{Node2.ll, (Node2.unoccupied+Node1.ll+

(Node1.s_start-Node2.s_end))}

-(A7.2)

Case 3: (Node2.s_end > Node1.s_start > Node2.s_start). In this case, the overlap

part of the two intervals needs to be taken into account, and they are

obtained according to (A5.3), (A6.3) and (A7.3), respectively.

Parent.unoccupied= (Max{(Node1.unoccupied+Node1.s start

-Node2.s\_end), 0}+ Node2.unoccupied)

-(A6.3)

Parent.ll= Min{Node2.ll, (Node2.unoccupied+Node1.ll-

(Node2.s_end-Node1.s_start))}

-(A7.3)

if ((Node2.s_end-Node1.s_start) < Node1.unoccupied)

Parent.s_end=Node1.s_end

-(A5.3)

else Parent.s_end= (Node1.s_end+Node2.s_end-

Node1.s start-Node1.unoccupied)

--(A5.3)

Case 4: (Node1.s_end > Node2.s_start > Node1.s_start). Similar to Case 3, the

overlap part of the two intervals needs to be taken into account, and they

are obtained according to (A5.4), (A6.4) and (A7.4), respectively.

Parent.unoccupied= (Max{(Node2.unoccupied+Node2.s_start

-Node1.s end), 0}+ Node1.unoccupied)

-(A6.4)

Parent.ll= Min{Node1.ll, (Node1.unoccupied+Node2.ll-

--(A7.4)

(Node1.s_end-Node2.s_start))}

if ((Node1.s_end-Node2.s_start) < Node2.unoccupied)

Parent.s end=Node2.s end

-(A5.4)

else Parent.s_end=(Node2.s_end+Node1.s_end-

Node2.s_start-Node2.unoccupied)

-(A5.4)

```

Figure 2.14 The TIT-RL tree.

# 2.4.2 Operations on TIT-RL Tree and Their Complexities

The basic operations on the TIT-RL tree include *Insert* and *Delete/Remove*.

*Insert* is invoked to insert a new task. This operation is similar to the *Insert* operation discussed in Section 2.1 except that the parameters of nodes need to be adjusted according to the definition of TIT-RL tree. The adjustment of parameters is conducted according to what is discussed in Section 2.4.1.

Delete/Remove is invoked to delete a leaf node from a TIT-RL tree. This operation is similar to the Delete/Remove described in Section 2.1 except that the parameters of related nodes need to be adjusted according to the definition of TIT-RL tree after the removal of the leaf node. The basic idea involved in the adjustment is similar to what is discussed in Section 2.4.1.

It is easy to see that the complexities of both *Insert* and *Delete/Remove* are  $O(\log n)$ , given a TIT-RL tree containing n tasks.

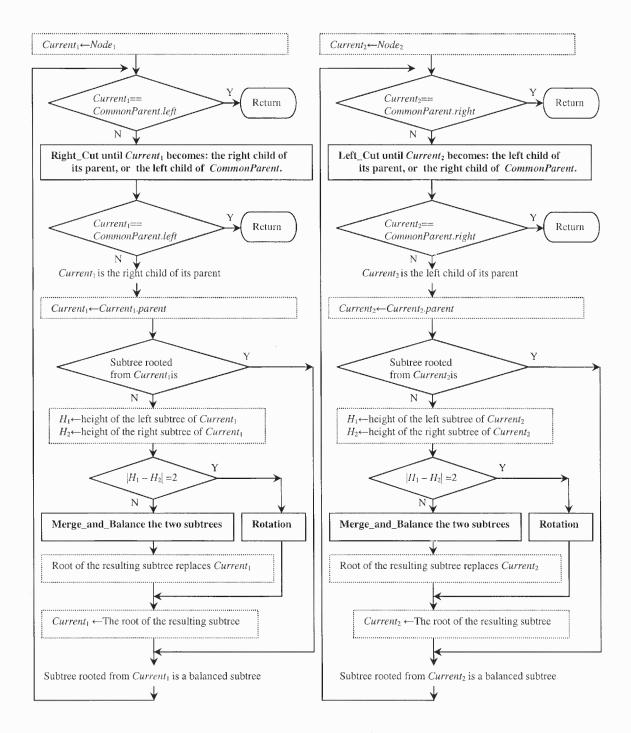

# 2.4.3 Using TIT-RL Tree to Construct ACA

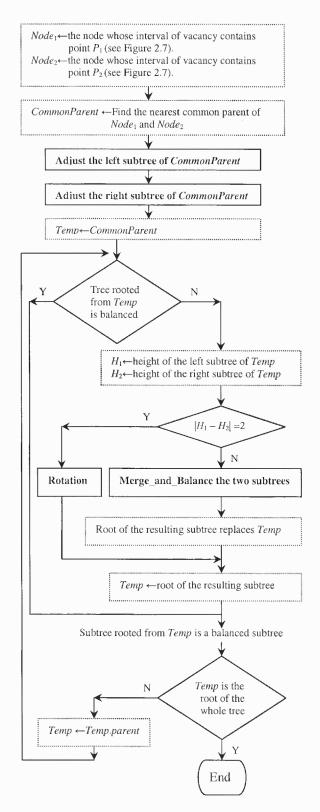

Now, the TIT-RL tree is employed to reconstruct the ACA algorithm (Figure 2.13). The pseudo code of the TIT-RL tree based algorithm is listed in Figure 2.15. The basic idea of the new algorithm is the same as that contained in Figure 2.13. In Figure 2.15, ACA first checks some simple cases (steps 2-7). More complicated cases are processed by steps 8-32. Basically, it first finds the appropriate position for a new task T (step 9) and then checks whether it can be safely inserted into that position (steps 12-27). The checking procedure starts from Temp (this is the task before which the new task is to be inserted) and goes up the tree. If any node indicates deadline miss (i.e., the updated largest laxity of the node is less than zero), ACA stops current checking procedure and attempts to

insert the new task before the next task (step 17). This invokes a new checking procedure. If T can not be inserted into any position, it is rejected (steps 14 and 29). Otherwise, it is inserted before First (step 23) or inserted at the end of the task queue (step 31). See step 23 and step 31, when the new node is inserted in the queue, its parameters may be adjusted if needed. The adjustment is used to make the updated tree conform to the definition of TIT-RL tree. However, it never changes the actual executions of tasks, nor does it have any impact on the admission of future tasks.

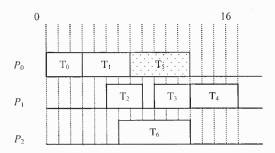

Figure 2.16 shows how the test is conducted, given a TIT-RL tree and a new task (6, 10, 1). Please note that *ACA* updates the parameters of some nodes during the test. Whether the test succeeds or not, those parameters that are changed need to be restored. This procedure can be avoided by using two copies of parameters. One copy is used only for test, and its values are copied from the other one. The copy operation is needed only for those nodes whose parameters are changed in the test. During the test, the parameters of every related node are first copied and then changed.

- **Definition 2.1** (Safe Acceptance) A task T = (r, d, e) can be safely accepted if a suitable position (on the TIT-RL tree) can be found for T, and it can be inserted there without causing any task (including T itself) to miss its deadline.

- **Theorem 2.5** A new task T = (r, d, e) can be safely accepted by the system if and only if ACA returns TRUE when it processes the corresponding TIT-RL tree.

- **Proof:**  $\leftarrow$  (1) That T is schedulable implies that a position, which is the earliest suitable position according to current system status, is available for T. (2) ACA always tries to find the earliest suitable position for T. Hence, ACA will be able to find that position, successfully insert T there and return TRUE.

- $\rightarrow$  (1) Before the test, all existing tasks are schedulable. (2) When ACA conducts the test, it always tries to find the earliest suitable position for the new task such that the new task can be safely inserted there (i.e., it does not cause any existing task to miss its deadline, and there is enough vacancy to

accommodate it). ACA returns TRUE implies that such a position is available for T. Hence it can be safely accepted.

```

ACA(Titrl, T)

Input: Titrl;

/*the TIT-RL tree that contains all accepted tasks */

/*the new task to be tested*/

Output: TRUE/FALSE;

/*T is admitted/rejected */

1 Create a new node NewNode according to T;

Case 1: (T. d < Titrl. root. Start)

Insert NewNode into the front of the queue;

Return TRUE;

Case 2: (T. r > Titrl. root. End)

Insert NewNode into the end of the queue;

Return TRUE;

8 Case 3: (Other cases)

Search down the tree, and find the first leaf node First such that

(First. r > T. r) or ((First. r == T. r) and (First. d > T. d));

10

If (NOT FOUND)

11

Goto step 28;

12

Temp = First;

13

If ((Temp \rightarrow prev. s\_end + T. e) > T. d)

14

Return FALSE;

/*the new task can not be safely accepted*/

15

Push in T. e time units before Temp, and adjust its parameters;

If (Temp. ll < 0)

16

/*implies deadline miss*/

17

First = First \rightarrow next;

/*attempt to insert the new task before the next task in the task queue*/

18

If (First == NULL)

/*implies the new task can not be inserted before ANY task in the task queue*/

19

Goto step 28;

20

Else Goto step 12;

21

Temp = Temp \rightarrow parent;

/*go upward the tree*/

If (Temp == NULL)

/*implies the test succeeds*/

22

23

24

25

26

27

28

29

Adjust the parameters of NewNode, and insert NewNode before First;

Return TRUE;

Adjust the parameters of Temp;

Goto step 16;

If ((Titrl. root. s\_end + T. e) > T. d)

Return FALSE;

/*the new task can not be safely accepted*/

30

Else

31