# **Copyright Warning & Restrictions**

The copyright law of the United States (Title 17, United States Code) governs the making of photocopies or other reproductions of copyrighted material.

Under certain conditions specified in the law, libraries and archives are authorized to furnish a photocopy or other reproduction. One of these specified conditions is that the photocopy or reproduction is not to be "used for any purpose other than private study, scholarship, or research." If a, user makes a request for, or later uses, a photocopy or reproduction for purposes in excess of "fair use" that user may be liable for copyright infringement,

This institution reserves the right to refuse to accept a copying order if, in its judgment, fulfillment of the order would involve violation of copyright law.

Please Note: The author retains the copyright while the New Jersey Institute of Technology reserves the right to distribute this thesis or dissertation

Printing note: If you do not wish to print this page, then select "Pages from: first page # to: last page #" on the print dialog screen

The Van Houten library has removed some of the personal information and all signatures from the approval page and biographical sketches of theses and dissertations in order to protect the identity of NJIT graduates and faculty.

#### **ABSTRACT**

# VECTOR SUPPORT FOR MULTICORE PROCESSORS WITH MAJOR EMPHASIS ON CONFIGURABLE MULTIPROCESSORS

### by Hongyan Yang

It recently became increasingly difficult to build higher speed uniprocessor chips because of performance degradation and high power consumption. The quadratically increasing circuit complexity forbade the exploration of more instruction-level parallelism (ILP). To continue raising the performance, processor designers then focused on thread-level parallelism (TLP) to realize a new architecture design paradigm. Multicore processor design is the result of this trend. It has proven quite capable in performance increase and provides new opportunities in power management and system scalability. But current multicore processors do not provide powerful vector architecture support which could yield significant speedups for array operations while maintaining area/power efficiency.

This dissertation proposes and presents the realization of an FPGA-based prototype of a multicore architecture with a shared vector unit (MCwSV). FPGA stands for Filed-Programmable Gate Array. The idea is that rather than improving only scalar or TLP performance, some hardware budget could be used to realize a vector unit to greatly speedup applications abundant in data-level parallelism (DLP). To be realistic, limited by the parallelism in the application itself and by the compiler's vectorizing abilities, most of the general-purpose programs can only be partially vectorized. Thus, for efficient resource usage, one vector unit should be shared by several scalar processors. This approach could also keep the overall budget within acceptable limits. We suggest that this type of vector-unit sharing be established in future multicore chips.

The design, implementation and evaluation of an MCwSV system with two scalar processors and a shared vector unit are presented for FPGA prototyping. The MicroBlaze processor, which is a commercial IP (Intellectual Property) core from Xilinx, is used as the

scalar processor; in the experiments the vector unit is connected to a pair of MicroBlaze processors through standard bus interfaces. The overall system is organized in a decoupled and multi-banked structure. This organization provides substantial system scalability and better vector performance. For a given area budget, benchmarks from several areas show that the MCwSV system can provide significant performance increase as compared to a multicore system without a vector unit.

However, a MCwSV system with two MicroBlazes and a shared vector unit is not always an optimized system configuration for various applications with different percentages of vectorization. On the other hand, the MCwSV framework was designed for easy scalability to potentially incorporate various numbers of scalar/vector units and various function units. Also, the flexibility inherent to FPGAs can aid the task of matching target applications. These benefits can be taken into account to create optimized MCwSV systems for various applications. So the work eventually focused on building an architecture design framework incorporating performance and resource management for application-specific MCwSV (AS-MCwSV) systems. For embedded system design, resource usage, power consumption and execution latency are three metrics to be used in design tradeoffs. The product of these metrics is used here to choose the MCwSV system with the smallest value.

# VECTOR SUPPORT FOR MULTICORE PROCESSORS WITH MAJOR EMPHASIS ON CONFIGURABLE MULTIPROCESSORS

by Hongyan Yang

A Dissertation

Submitted to the Faculty of

New Jersey Institute of Technology

in Partial Fulfillment of the Requirements for the Degree of

Doctor of Philosophy in Electrical Engineering

**Department of Electrical and Computer Engineering**

May 2008

# Copyright © 2008 by Hongyan Yang ALL RIGHTS RESERVED

### APPROVAL PAGE

# VECTOR SUPPORT FOR MULTICORE PROCESSORS WITH MAJOR EMPHASIS ON CONFIGURABLE MULTIPROCESSORS

## Hongyan Yang

| Dr. Sotirios G. Ziavras, Dissertation Advisor                                                              | Date |

|------------------------------------------------------------------------------------------------------------|------|

| Professor of Electrical and Computer Engineering, NJIT                                                     |      |

| Dr. Edwin Hou, Committee Member                                                                            | Date |

| Associate Professor of Electrical and Computer Engineering, NJIT                                           |      |

| Dr. Jie Hu, Committee Member<br>Assistant Professor of Electrical and Computer Engineering, NJIT           | Date |

| Dr. Roberto Rojas-Cessa, Committee Member Associate Professor of Electrical and Computer Engineering, NJIT | Date |

| Dr. Alexandros V. Gerbessiotis, Committee Member                                                           | Date |

Associate Professor of Computer Science, NJIT

#### **BIOGRAPHICAL SKETCH**

**Author:** Hongyan Yang

**Degree:** Doctor of Philosophy

**Date:** May 2008

#### **Undergraduate and Graduate Education:**

- Doctor of Philosophy in Electrical Engineering,

New Jersey Institute of Technology, Newark, NJ, 2008

- Master of Science in Electrical Engineering,

Beijing University of Posts and Telecommunications, Beijing, China, 2001

- Bachelor of Science in Electrical Engineering,

Beijing University of Posts and Telecommunications, Beijing, China, 1998

Major: Electrical Engineering

#### **Publications:**

- H. Yang, S. G. Ziavras, and J. Hu, "Reconfiguration support for vector operations," *International Journal of High Performance Systems Architecture*, vol. 1, no. 2, pp. 89–97, 2007.

- S. Wang, H. Yang, J. Hu, S. G. Ziavras, "Asymmetrically banked value-aware register files for low energy and high performance," *Microprocessors and Microsystems*, 2007.

- H. Yang, S. G. Ziavras, and J. Hu, "FPGA-based vector processing for matrix operations," in *International Conference on Information Technology: New Generations*, Las Vegas, USA, April 2007, pp. 989–994.

- H. Yang and S. G. Ziavras, "FPGA-based vector processor for algebraic equation solvers," in *IEEE International Systems-On-Chip Conference*, Washington, DC, USA, 2005, pp. 115–116.

- H. Yang, S. Wang, S. G. Ziavras, and J. Hu, "Vector processing support for FPGA-oriented high performance applications," in *IEEE Computer Society Annual Symposium on VLSI*, Porto Alegre, Brazil, May 2007, pp. 447–448.

S.Wang, H. Yang, J. Hu, and S. G. Ziavras, "Asymmetrically banked value-aware register files," in *IEEE Computer Society Annual Symposium on VLSI*, Porto Alegre, Brazil, May 2007, pp. 363–368.

To my parents, Jianyun Zhang and Caifeng Yang

To my husband, Shuangquan Wang

To my daughter, Andrea Wang

#### **ACKNOWLEDGMENT**

First of all, I would like to express my deep and sincere gratitude to my advisor: Dr. Sotirios G. Ziavras. I could not have finished this dissertation without his patience, understanding and encouragement during the last five years. His knowledge and expertise in computer architecture has constantly helped and inspired me to go further in my research. I want to thank him for his help in many aspects: his stimulating and constructive suggestions on my research; his patience to review and improve my writings hundreds of times; his kindness for providing financial support during my study and research and much more. I also learned a lot from his professional work style. Those will be of great value in my future career.

I warmly thank Dr. Edwin Hou, Dr. Hu Jie, Dr. Roberto Rojas-Cessa and Dr. Alexandros Gerbessiotis for being my committee members, spending time on reviewing my dissertation and giving me valuable suggestions.

I also thank my lab colleagues in CAPPL for our interesting discussions on various research topics and the fun of being together.

I owe my deepest gratitude to my husband, Dr. Shuangquan Wang, for his understanding and help.

Finally, I am deeply indebted to my father, Jianyun Zhang, my mother, Caifeng Yang, for their unconditional love and continuous support.

## TABLE OF CONTENTS

| $\mathbf{C}$ | Papter Pa |        |                                                   | Page |

|--------------|-----------|--------|---------------------------------------------------|------|

| 1            | INT       | RODU   | CTION                                             | . 1  |

|              | 1.1       | Vector | r Processing                                      | . 1  |

|              |           | 1.1.1  | Vector Supercomputers and Their Applications      | . 2  |

|              |           | 1.1.2  | Vector Processing in Embedded Systems             | . 3  |

|              | 1.2       | Multio | core Processors                                   | . 5  |

|              |           | 1.2.1  | Motivation for Their Development                  | . 5  |

|              |           | 1.2.2  | State of the Art and Future Multicore Processors  | . 5  |

|              | 1.3       | Config | gurable Computing                                 | . 8  |

|              |           | 1.3.1  | Overview of Field-Programable Gate Arrays (FPGAs) | . 8  |

|              |           | 1.3.2  | Recent Advances in FPGAs                          | . 9  |

|              |           | 1.3.3  | Design Flow                                       | . 11 |

|              | 1.4       | Motiv  | ations and Objectives                             | . 12 |

| 2            | VE        | CTOR I | PROCESSING FOR EMBEDDED APPLICATIONS              | . 15 |

|              | 2.1       | Archit | tecture of the Vector Processor                   | . 16 |

|              |           | 2.1.1  | Instruction Set Architecture                      | . 17 |

|              |           | 2.1.2  | Scalar Unit                                       | . 18 |

|              |           | 2.1.3  | Vector Register File                              | . 19 |

|              |           | 2.1.4  | Vector Memory Interface (VMI)                     | . 22 |

|              | 2.2       | Perfor | rmance Results                                    | . 22 |

|              |           | 2.2.1  | Preliminaries on Vector Processing                | . 23 |

|              |           | 2.2.2  | Sparse Linear Equation Solver                     | . 26 |

|              |           | 2.2.3  | Dense Matrix-Matrix Multiplication                | . 30 |

|              |           | 2.2.4  | Sparse Matrix-Vector Multiplication               | . 31 |

| 3            | MU        | LTICO  | RE PROCESSOR SYSTEM WITH A SHARED VECTOR UNIT     | . 33 |

# **TABLE OF CONTENTS** (Continued)

| C | hapt | er                                      | I I                                                                   | Page |

|---|------|-----------------------------------------|-----------------------------------------------------------------------|------|

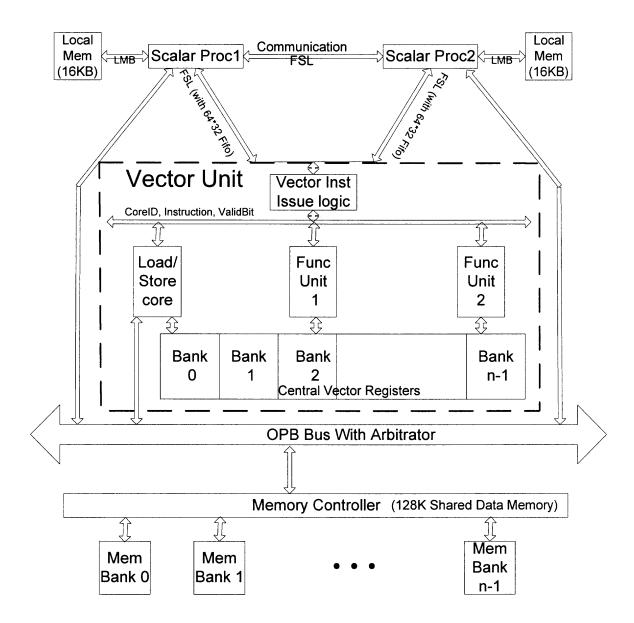

|   | 3.1  | 3.1 Scalar Processor and FPGA Resources |                                                                       | 34   |

|   |      | 3.1.1                                   | MicroBlaze Soft Processor                                             | 34   |

|   |      | 3.1.2                                   | Virtex-5 Resources                                                    | 35   |

|   | 3.2  | Syster                                  | m Design and Organization                                             | 36   |

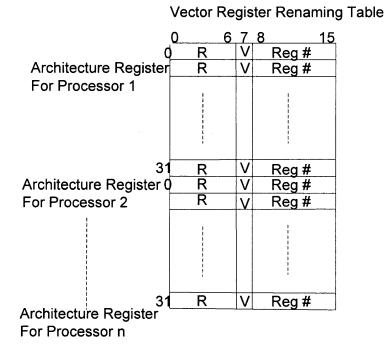

|   |      | 3.2.1                                   | Vector Issue Logic                                                    | 36   |

|   |      | 3.2.2                                   | Vector Register File                                                  | 38   |

|   |      | 3.2.3                                   | Function Units                                                        | 41   |

|   |      | 3.2.4                                   | Memory Controller                                                     | 42   |

|   | 3.3  | System                                  | m Implementation on the FPGA Chip                                     | 43   |

|   |      | 3.3.1                                   | Digital Signal Processing (DSP) Blocks                                | 43   |

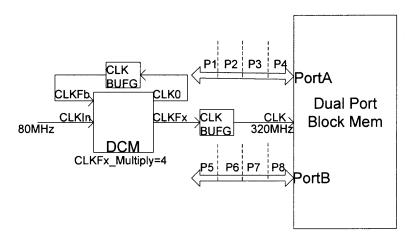

|   |      | 3.3.2                                   | Digital Clock Manager (DCM) Primitive                                 | 44   |

|   |      | 3.3.3                                   | On-Chip Block Memories                                                | 44   |

|   |      | 3.3.4                                   | Resource Usage for Various Configurations                             | 45   |

| 4 | PEF  | RFORM                                   | IANCE RESULTS AND ANALYSIS                                            | 47   |

|   | 4.1  | RGB 1                                   | to YIQ Conversion (RGB2YIQ)                                           | 47   |

|   | 4.2  | Demo                                    | dulation Algorithm in Communication Systems                           | 49   |

|   | 4.3  | Discre                                  | ete Cosine Transform                                                  | 54   |

| 5 |      |                                         | ONSUMPTION CHARACTERIZATION AND RESOURCE MAN-<br>NT FOR MCWSV SYSTEMS | 58   |

|   | 5.1  | Resou                                   | rce/Power Modeling for the MCwSV System                               | 59   |

|   |      | 5.1.1                                   | Dynamic Power Consumption of Floating-Point Arithmetic Units .        | 60   |

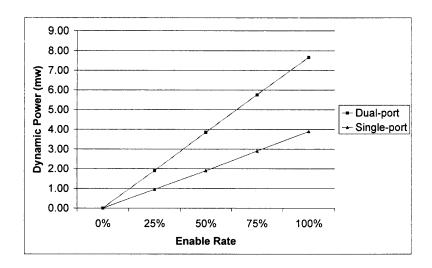

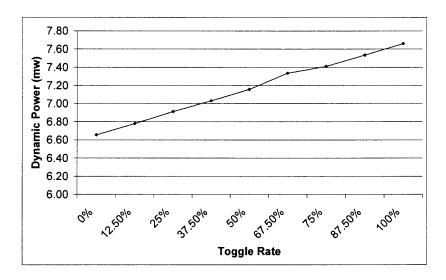

|   |      | 5.1.2                                   | Dynamic Power Consumption of Dual-Port Block Memories                 | 62   |

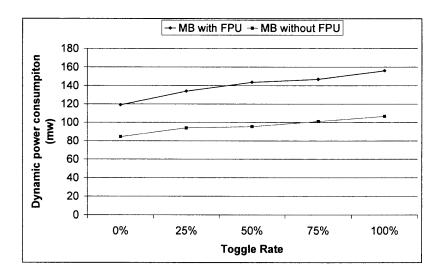

|   |      | 5.1.3                                   | Power Consumption of MicroBlaze w/wo a Floating-Point Unit            | 64   |

|   |      | 5.1.4                                   | Power Consumption of the Vector Unit for Different Configurations     | 64   |

|   | 5.2  | Power                                   | Resource-Efficient MCwSV Systems for Various Applications             | 67   |

|   |      | 5.2.1                                   | Scalar/Vector Execution Time Estimation                               | 71   |

# **TABLE OF CONTENTS** (Continued)

| Chapter |      |                                                                               |    |  |  |  |

|---------|------|-------------------------------------------------------------------------------|----|--|--|--|

|         |      | 5.2.2 Application-Specific MCwSV (AS-MCwSV) System for Power/Resou Efficiency |    |  |  |  |

| 6       | COI  | CLUSIONS AND FUTURE WORK                                                      | 81 |  |  |  |

| (       | 6.1  | Conclusions                                                                   | 81 |  |  |  |

| (       | 6.2  | Future Work                                                                   | 83 |  |  |  |

| REF     | FERI | NCES                                                                          | 84 |  |  |  |

## LIST OF TABLES

| Tabl | le P                                                                                                                             | age |

|------|----------------------------------------------------------------------------------------------------------------------------------|-----|

| 2.1  | Non-Zero Element (NNZ) Changes in W-Matrix Partition Generation                                                                  | 28  |

| 2.2  | Input Sparse Matrices from the Harwell-Boeing Collection in Our Experiments                                                      | 31  |

| 3.1  | Resource Consumption of Single-Precision Implementations                                                                         | 43  |

| 3.2  | Configuration and Usage of Block Memories                                                                                        | 45  |

| 3.3  | Resource Usage of the Vector Unit and the Memory Controller                                                                      | 46  |

| 4.1  | Execution Times (us) for RGB2YIQ Conversion                                                                                      | 48  |

| 4.2  | Execution Times $(ms)$ of the Distance Calculation Algorithm when Run on One MicroBlaze with the Vector Unit for 1000 Input Data | 51  |

| 4.3  | Execution Times (ms) of the Demodulation Algorithm (MB: MicroBlaze, DIS:Distance, VU:Vector Unit.)                               | 53  |

| 4.4  | Vector and Scalar Execution Times and Their Ratio for the DCT Algorithm .                                                        | 55  |

| 5.1  | Resource Usage and Dynamic Power Consumption of IEEE Single-Precision FPUs on the Virtex-5 FPGA                                  | 62  |

| 5.2  | Resource Usage and Power Consumption of a MicroBlaze w/wo FPU Support                                                            | 64  |

| 5.3  | Resource Usage and Power Consumption of the Vector Unit Without Enable Control of Block Memories                                 | 65  |

| 5.4  | Dynamic Power Consumption of the BRAMs and the VRF                                                                               | 66  |

| 5.5  | Resource Usage and Power Consumption of the Vector Unit with Enable Control of the Block Memories                                | 67  |

| 5.6  | Estimated Execution Time for the Demodulation Algorithm                                                                          | 78  |

| 5.7  | Execution Time and Resource/Power Consumption for the Demodulation Algorithm                                                     | 79  |

## LIST OF FIGURES

| Figu | Figure                                                                                                                                                                                                            |    |  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|

| 1.1  | FPGA design flow.                                                                                                                                                                                                 | 11 |  |

| 2.1  | Overview of the system                                                                                                                                                                                            | 16 |  |

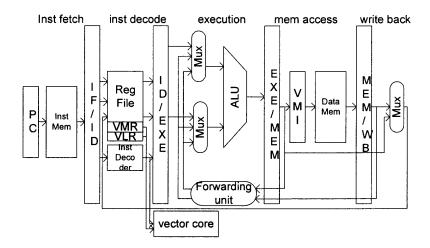

| 2.2  | Block diagram of the vector processor (VLR: Vector Length Register, VMR: Vector Mask Register)                                                                                                                    | 17 |  |

| 2.3  | Instruction formats                                                                                                                                                                                               | 18 |  |

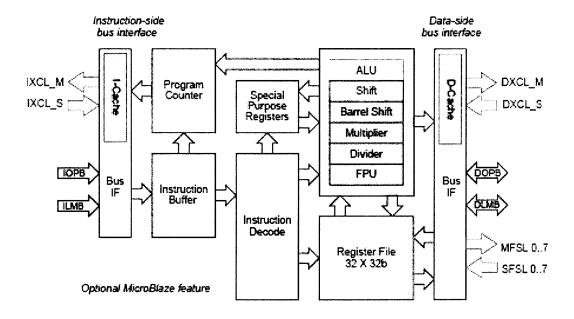

| 2.4  | Scalar processor architecture                                                                                                                                                                                     | 18 |  |

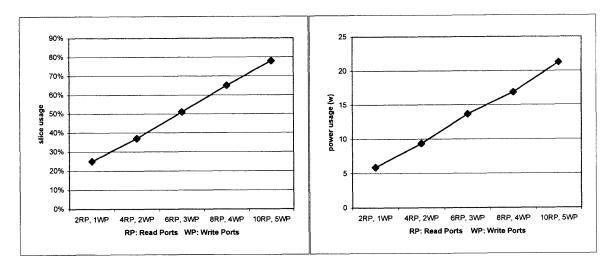

| 2.5  | Resource and power consumption for single-block implementation of a vector register file containing 8 vector registers of 32 32-bit elements                                                                      | 20 |  |

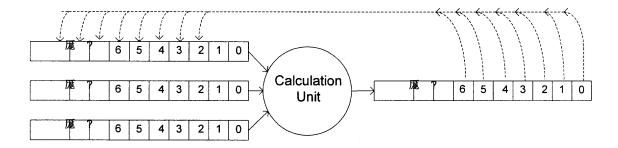

| 2.6  | Vector register file organization and connections with other components                                                                                                                                           | 20 |  |

| 2.7  | Recurrence problem.                                                                                                                                                                                               | 24 |  |

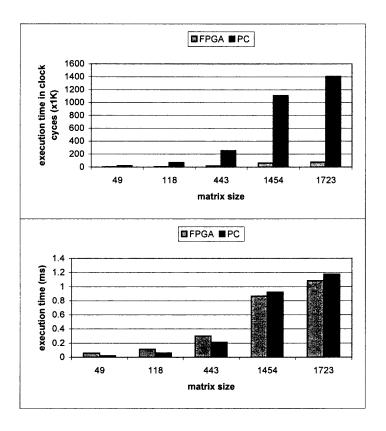

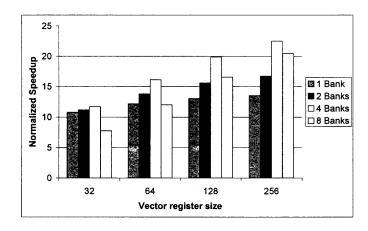

| 2.8  | Performance of sparse linear equation solver                                                                                                                                                                      | 29 |  |

| 2.9  | Performance of dense matrix-matrix multiplication                                                                                                                                                                 | 30 |  |

| 2.10 | Performance of sparse matrix-vector multiplication.                                                                                                                                                               | 32 |  |

| 3.1  | MicroBlaze core block diagram [1]                                                                                                                                                                                 | 34 |  |

| 3.2  | MCwSV multicore processor system with a shared vector unit (The scalar registers are not shown in the vector unit)                                                                                                | 37 |  |

| 3.3  | Vector register renaming table (R: Reserved; V: Valid)                                                                                                                                                            | 38 |  |

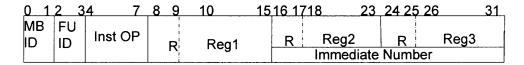

| 3.4  | The format of incoming and outgoing instructions in VIL. "MB ID" indicates which MicroBlaze issued the operation; "FU ID" indicates which function unit should this instruction go to. (OP: Opcode, R: Reserved.) | 38 |  |

| 3.5  | Multiport vector register implementation                                                                                                                                                                          | 40 |  |

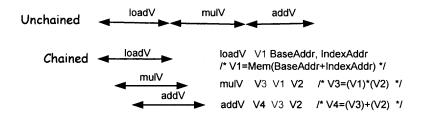

| 3.6  | Vector chaining.                                                                                                                                                                                                  | 41 |  |

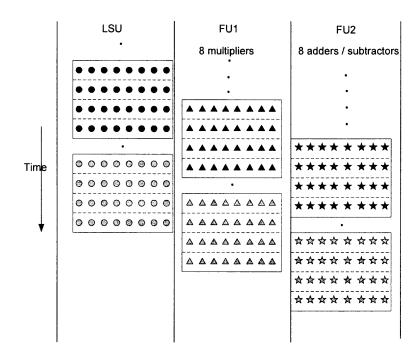

| 3.7  | Vector chaining in a multi-lane structure (LSU: load/store unit)                                                                                                                                                  | 42 |  |

| 4.1  | RGB2YIQ speedup of using the vector unit as compared to one MicroBlaze processor without this unit.                                                                                                               | 49 |  |

| 4.2  | RGB2YIQ normalized speedup (using resource usage) of the vector unit as compared to one MicroBlaze processor.                                                                                                     | 50 |  |

# LIST OF FIGURES (Continued)

| rıgu | ire F                                                                                                                                              | age |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------|-----|

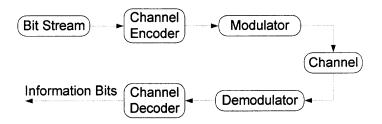

| 4.3  | A typical digital communication system.                                                                                                            | 50  |

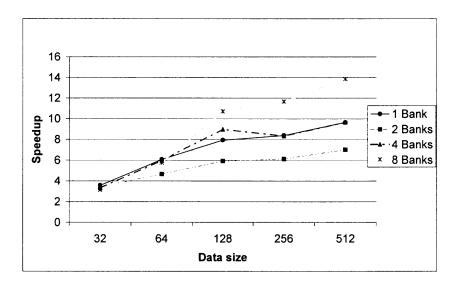

| 4.4  | The speedup for distance calculation of the vector unit over one MicroBlaze                                                                        | 52  |

| 4.5  | Speedup normalized by the slice usage ratio for distance calculation                                                                               | 52  |

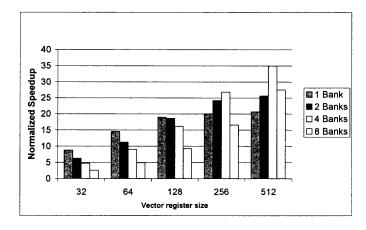

| 4.6  | Speedup of including a vector unit in a MicroBlaze processor for the DCT algorithm                                                                 | 56  |

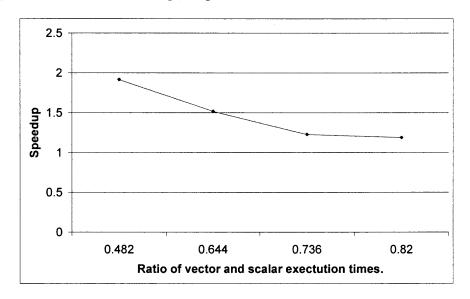

| 4.7  | Speedup of two MicroBlazes versus one MicroBlaze, both systems with a vector unit, as a function of the ratio of vector and scalar execution times | 57  |

| 5.1  | Dynamic power consumption of one memory block VS the enable rate                                                                                   | 63  |

| 5.2  | Dynamic power consumption of the dual-port memory VS the toggle rate                                                                               | 63  |

| 5.3  | Dynamic power consumption of a MicroBlaze w/wo an FPU at different toggle rates.                                                                   | 65  |

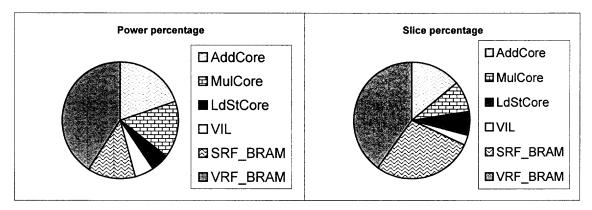

| 5.4  | Percentage of power consumption and slice usage for the vector unit with the 1-bank configuration                                                  | 67  |

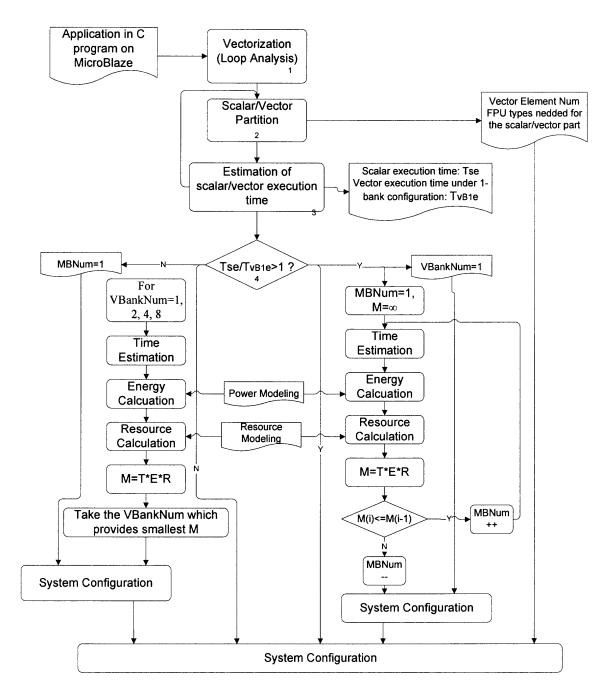

| 5.5  | Overview of the procedure for architecture template creation                                                                                       | 69  |

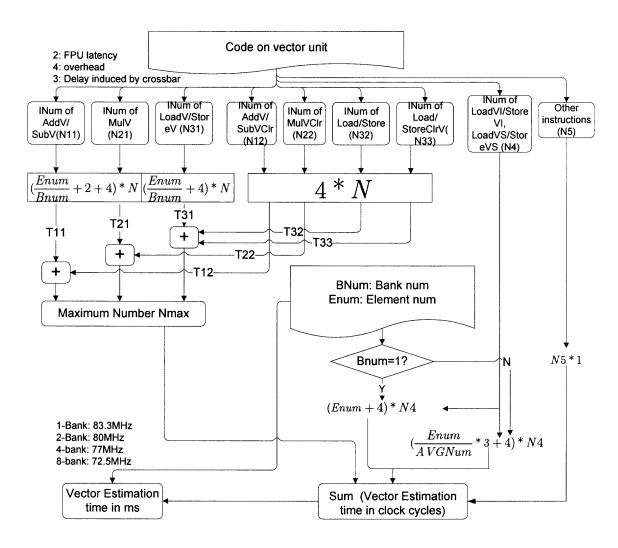

| 5.6  | Estimation model for the vector execution time                                                                                                     | 72  |

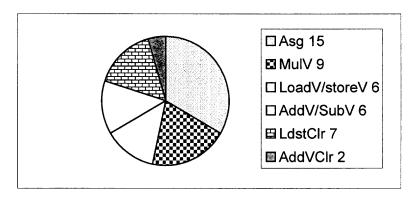

| 5.7  | Instruction profiling for the RGB2YIQ algorithm on the vector unit                                                                                 | 73  |

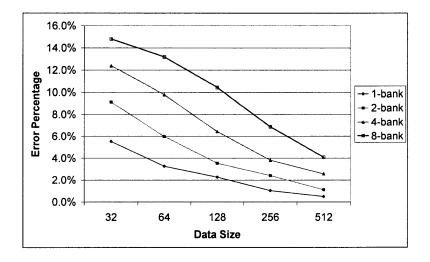

| 5.8  | Error percentage of the vector time estimation model for the RGB2YIQ algorithm.                                                                    | 73  |

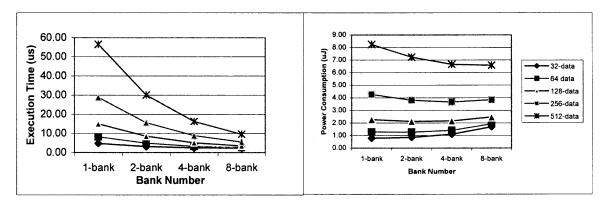

| 5.9  | Execution time and power estimation for the MCwSV system for various data sizes and different bank configurations for the RGB2YIQ algorithm        | 76  |

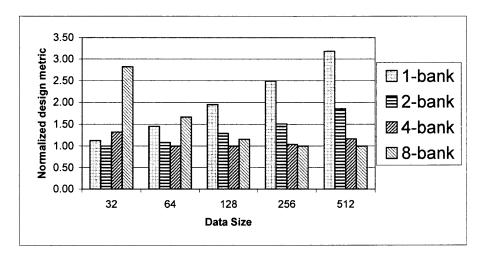

| 5.10 | Normalized design metric $(M)$ for various data sizes and different bank configurations                                                            | 76  |

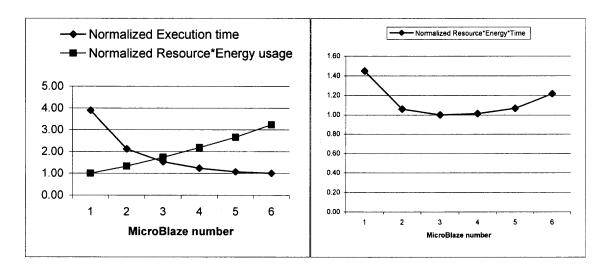

| 5.11 | Normalized design metrics                                                                                                                          | 80  |

#### **CHAPTER 1**

#### INTRODUCTION

#### 1.1 Vector Processing

During the past thirty years processor designers have mainly concentrated on exploring instruction-level parallelism (ILP) to improve performance; only recently have they applied thread-level parallelism (TLP) approaches in chip design. The former approach has lead to the development of superscalar and VLIW (Very Long Instruction Word) architectures [2]. Superscalar architectures are flexible, can exploit ILP dynamically by hardware and have dominated CPU design for a long time. This design paradigm, however, requires a complex control unit with complexity growing exponentially; this eventually diminishes the return of issuing more instructions [3]. Also, the majority of applications have a limited degree of ILP. The pure VLIW paradigm relies on the compiler to exploit ILP and issues each time a fixed number of instructions fetched as one large instruction. It has simpler hardware as compared to superscalars, but requires large instruction cache space, increased instruction fetch bandwidth and very sophisticated compilers.

Vector processing avoids the above problems of superscalar and VLIW architectures for applications rich in data parallelism [2]. It was very common for supercomputers built in the 1980s and 1990s; then it began to fade away but some relevant features were realized in advanced microprocessors for operations on streams of data. The release of the Earth Simulator in 2002, the fastest supercomputer in the world for three consecutive years [4], led to a resurgence of interest in the vector architecture [2]. Vector processors have made a comeback in several domains, including scientific computing [5, 6], multimedia processing [7–9], telecommunications and signal processing [10, 11]. Abundant data-level parallelism (DLP) in these domains allows vector processors to provide higher peak and sustained performance than superscalar, VLIW and chip multiprocessor (CMP) designs [9, 12]. IBM,

Toshiba and Sony announced the Cell processor in 2000 which consists in part of many vector processors and is optimized for compute-intensive workloads, broadband data transmission and multimedia processing [13]. Today almost all commodity CPU designs include some vector processing instructions, typically known as of the Single Instruction, Multiple Data (SIMD) type. Modern video game consoles and consumer computer-graphics hardware in particular rely heavily on vector processors.

The properties of the vector architecture, which render it the most efficient and lowest-complexity approach for array operations are [2]:

- A single vector instruction implies lots of essential work; it is equivalent to an entire loop implemented in sequential processing. So the instruction fetch and decode bandwidths needed to feed multiple, deeply pipelined functional units are dramatically reduced.

- Each element in the resulting vector is independent of the current computation of other results in the same vector. Thus, multiple operations can be executed in parallel on vector elements and the effect of data hazards is minimized. A multi-lane memory-access structure which explores data parallelism is described in Subsection 1.1.2; this structure is power efficient, simple to design, and easy to scale [14].

- Vector instructions access the memory with known patterns. Thus, the cost of the latency to access the main memory is amortized because a single access is initiated for a large part or the whole of a vector.

### 1.1.1 Vector Supercomputers and Their Applications

Vector processing is particularly useful for large science and engineering applications [2]. Actually, the early supercomputing arena was dominated by vector supercomputers. In 1993, 340 out of the top 500 supercomputers were based on the vector structure [4]. Cray, NEC, Fujitsu, Hitachi, Convex CDC, EDT and IBM all developed high performance vec-

tor supercomputers [2]. Then, the fast development of commodity clusters began to take a leading role in the supercomputing field, benefitting from the performance improvement of microprocessors [15]; vector supercomputers appeared to fade. For a decade most of the computer architects believed that the future belongs to Massively Parallel Processing (MPP) systems made from off-the-shelf commodity chips. Some persons even predicted that the vector structure will be of diminished value in the supercomputing area and will be totally replaced by systems built form large numbers of superscalar microprocessors [2]. But in 2002, NEC Inc. announced the world's fastest supercomputer, the Earth Simulator based on 5120 vector microprocessors. The impact of the Earth Simulator, together with the release of a new generation of vector machines from Cray, led to a renaissance of interest in the vector processing structure [2]. Vector processors still remain the most effective way to exploit data-parallel applications [9]. Due to the high communication latency of clusters, vector supercomputers have been widely used and will continue to play an essential role in many application areas in government, commercial and academic use [15]. These areas include stockpile stewardship, signal intelligence defense, climate prediction, plasma physics and etc. [15].

#### 1.1.2 Vector Processing in Embedded Systems

Embedded systems are ubiquitous and can be found in most of the electronic products related to consumer electronics, office automation, home appliances and automobiles. In recent years, embedded computing systems have grown tremendously not only in their popularity, but also in their complexity [16]. Embedded systems are typically single-functioned and have tight constraints on implementation. In particular, they must often react to the external events in real time, and meet tight the requirements of size, weight, budget power and cooling consumption [17].

The vector architecture is especially suitable for embedded systems targeting arraybased applications because of simplicity, good performance and small code size. The simple architecture implies small area, low power consumption, low cost and short design time. It can outperform the two architectures widely used in desktop domain, superscalar and VLIW by a factor of two to ten on array-intensive applications despite its much lower clock frequency [9].

Two previous vector systems were built at U.C. Berkeley for embedded applications: one is T0, a vector microprocessor [14]; the other is a scalable vector media-processor [18]. To divides the central vector register file into multiple lanes where each lane contains a slice of vector registers. Each lane also contains a datapath to a function unit, so data parallelism can be easily employed because there is no data dependency between element calculations [14]. The scalable vector media-processor not only uses the multi-lane structure, but also a cluster organization which divides the set of vector registers into different clusters, where each cluster contains part of the set. A communication network is used to transfer the data in vector registers between different clusters, when needed. Different function units are connected with the clusters to achieve ILP. One problem in conventional vector processor design is that the complexity and size of the centralized multi-port vector register file limits the number of function units [19]. Both of these architectures can solve the problem and the latter can also hide long memory latencies [14, 18].

Multimedia and telecommunications benchmarks from the Embedded Microprocessors Benchmark Consortium (EEMBC) [20] were run on the latter and results showed that the vector processor is two times faster than a 4-way superscalar processor running at five times higher clock frequency; it is also ten times faster than a 5-way to 8-way VLIW design. It also showed that the vector microprocessor has smaller code size and less power consumption as compared to RISC, VLIW and superscalar architectures [9].

#### 1.2 Multicore Processors

#### 1.2.1 Motivation for Their Development

In the 1990s, computer performance was increasing according to Moore's law, driven largely by increasing transistor density, accelerating operating frequency and exploring more ILP. But then it couldn't keep up. The performance increase was 60 percent per year in the 1990s but slowed to 40 percent from 2000 to 2004; then, it reached only 20 percent after 2004 [21]. Today, it costs twice the chip area to gain a 20 percent speed increase with a uniprocessor. The reason lies in two facts. One is that heat management is becoming a very serious problem with transistor size decreases. Leakage power constrains frequency acceleration [22]. The other is that both the superscalar and VLIW, two widely used architectures in modern computers, approached performance limits of exploring ILP because of quadratic increases in power, area, hardware control or compiler complexity [3]. The diminishing returns of building more complex uniprocessors forced researchers to change their design philosophy toward improving performance and managing power consumption.

As a result, chip processor makers have turned into multicore processor designs. It can potentially explore TLP to provide increased single-chip computational capability without requiring a complex microarchitecture. Multiple cores having the same microarchitecture are integrated. Generally these cores have a shared L2 cache and each core is equipped with its own cooling support. They do not necessarily run as fast as single-core models, but they can improve the overall performance by handling more work in parallel [21]. Thus simple multicore processors can provide better performance per watt for a given area than more complex single-core competitors [23]. The simplicity of their architecture also offers new opportunities for scalability and thermal control.

#### 1.2.2 State of the Art and Future Multicore Processors

Processor makers like Intel, AMD, IBM and Sun have introduced multicore chips for servers, desktops and laptops [21]. Intel has shipped Core Duo, Core 2 Duo, and Xeon

(x1xx series) microprocessors with dual-core technology; it also provided in 2006 quadcore versions of the Core 2 chip, called the Core 2 Quad and Core 2 Extreme [24]. Also, it has developed an 80-core processor prototype that can perform a trillion floating-point operations per second at 3.16GHz and this processor will be rolled out within the next five years. Moreover, Intel has more than 15 multicore processor projects underway, and the architecture is expected to hold dozens or even hundreds of processor cores in a single die [22]. AMD also has released its dual-core Opteron server/workstation processors, the Athlon 64 X2 family desktop and the Turion 64 X2 for laptops in 2005, and a quad-core Opteron processor in 2007 [25]. IBM has announced its dual-core chips POWER4 and POWER5. Sun Microsystems introduced its dual-core chip UltraSPARC IV early in 2003 and unveiled the UltraSPARC T1 in 2005, Sun's first microprocessor that is both multicore and multithreaded. The UltraSPARC T1 is available with four, six or eight CPU cores, and each core is able to handle four threads concurrently. Thus, the processor is capable of processing up to 32 threads concurrently [26]. It is widely believed by computer architects that future microprocessors will perhaps include hundreds or even thousands of cores in a single die [27].

Inspired by the fast development of multicore designs, accelerators prototyped on FPGA boards for multicore processors are under development by groups of researchers in universities and companies. They aim to build research platforms for multcore/multiple processor designs with up to thousands of cores in hardware/software IPs, in order to provide highly accurate performance prediction, parameterized reconfiguration and extensive monitoring. Such accelerators are supposed to provide multiple orders of magnitude speedup over software-based simulators of multicore processor designs [27].

While most of the current multicore processors only include homogeneous general processing cores, it could be promising to include heterogenous cores in the multicore design [22, 23, 28]. Frameworks for heterogenous multicore architectures were studied in [28, 29]. They tried to provide platforms for integrating different cores flexibly, while

offering the necessary software support for application scheduling and a simulation environment for multicore designs. A performance-asymmetric multicore design, where individual cores have different compute capabilities, was also described in [23]. While a few high-performance complex cores can provide good serial performance required by single threads, many low-performance simple cores could provide higher performance. It was demonstrated that some degree of asymmetric performance is beneficial to particular applications. Multicore designs mixed with multithreading and hyperthreading participants, such as the UltraSPARC announced by Sun, could increase computer performance even further [26]. Higher performance can also be expected from integrating special-purpose processor cores in multimedia processing, speech recognition, networking applications, etc. [22].

On the other hand, substantial effort has been made to improve software support for parallel programming on multicore processor platforms. Intel provides a number of compilers, software primitives and tools, aiming at enabling parallel programming on its processors. AMD, on the other hand, has announced plans to extend the X86 instruction set to ease the job of programming multicore processors.

Multicore processors also provide new opportunities in thermal management and scalability because of multithreading/multitasking. Many new innovations designed to optimize power, performance, inter connectivity and scalability have been implemented for multicore processors [23, 30, 31].

Multicore processors have been used to manage web applications (Sun Microsystems/UltraSparc T1 [32]), game consoles (IBM, Sony, Toshiba/Cell [33]), data storage networks (Cavium Networks/Octeon), image processing (Rapport/KC256), wireless communications (PicoChip/PC2xx), etc.

#### 1.3 Configurable Computing

Computation-intensive applications are a great challenge to conventional instruction set processors due to the latter's underlying sequential architecture. ASIC designs with abundant calculation units are very efficient for such tasks. But they are resilient to potential modifications required to fit new applications. This makes the ASIC approach prohibitively expensive for small productions and drives designers to search for flexible solutions. Configurable or reconfigurable computing provides a way to combine the flexibility of microprocessors and the implementation efficiency of ASICs. It has blurred the distinction between hardware and software, and benefits from the advantages of both [34]. Configurable computing has demonstrated its superiority in many application domains and many configurable computer systems are based on FPGAs. In this section, we will introduce the FPGA technology with recent developments that make it feasible to form computation elements.

### 1.3.1 Overview of Field-Programable Gate Arrays (FPGAs)

After their invention by the Xilinx Lab in 1984, the FPGA technology has developed rapidly in both capacity and performance. Take the example of the Virtex-5 series, a new 65nm FPGA announced by Xilinx Inc. It offers up to 51,840 slices, with each slice containing four 6-input look-up tables (LUTs), four storage elements, wide-function multiplexers and carry logic, 1200 user I/Os, 10Mbits of 36Kbit block RAM, and 3.4Mbits of distributed RAM, plus an abundance of hardened intellectual property (IP) blocks. It provides 30% higher speed, 35% lower dynamic power and 45% less area than the previous generation Xilinx FPGA Virtex-4. Additionally, FPGA providers continue to decrease their price. The cost of logic cells has been reduced 30-fold from their introduction, to as little as less than 50 cents per 1000 logic cells. Although FPGAs have historically been used as "glue logic" to connect various other elements within a system or to replace an ASIC phototype, they are now widely used in several diverse domains because of their advances

in capacity and performance provided mainly by the last couple of FPGA generations. The recently improved computational power of FPGAs has also attracted mainstream high-performance computing companies. Cray's XD1 supercomputer combines AMD Opteron processors with FPGAs to accelerate computations. This configurable supercomputer can yield orders-of-magnitude speedups. Silicon Graphics also includes FPGAs in its Altix platform [35].

As FPGAs have matured, researchers were quick to recognize their potential and they soon became the most common devices in configurable computing. Many reconfigurable systems are based on FPGA technology. They can be classified in fine grained and coarse grained architectures according to the complexity of the lowest level design; or closely coupled and loosely coupled architectures according to the proximity to the host machine [34]. These systems include Splash [36], BEE2 [37], ArMen [38], TM and TM-2 [39], BORG and BORG II, SPYDER, RENCO, etc. Performance increase of orders of magnitude has been reported in various application areas such as multimedia, wireless communications and signal processing [34].

#### 1.3.2 Recent Advances in FPGAs

Most of the recent generation FPGAs are called platform FPGAs as compared to previous products which were based on fine-grain reconfigurable architectures. The term "platform FPGA" represents a coarse-grain architecture with the integration of a wide variety of hard and soft IP cores on a single device. The programmability of this coarse-grain architecture greatly reduces system development time and complexity as compared to fine-grain FPGA architectures. Platform FPGAs generally provide plenty of DSP blocks, large on-chip memories, and a lot of IP cores, such as high-speed transceiver links, sophisticated memory controllers and network interfaces. Take the example of the newest Xilinx FPGA Virtex-5 series: it provides a built-in PCI express endpoint block which supports a ubiquitous serial connectivity standard, several built-in Ethernet MAC blocks and 1.25Gbps

selectIO in some models. It also provides up to 640 DSP48E slices with each of the enhanced slices containing a  $25 \times 18$  multiplier and a 48-bit adder, and greatly improves the signal processing ability. These DSP blocks can enable single-precision floating-point math, which was an impossible task for earlier FPGAs, and wide filters.

Another important feature provided by platform FPGAs is the embedded microprocessor. The FPGA processor can be of the "hard" core or "soft" core type. Hard processors are microprocessors that have been diffused into the silicon of the FPGA, similar to discrete processors. However, in the FPGA the CPU is surrounded by programmable logic which can be configured to perform other functions and can be coupled tightly with the CPU [40]. The IBM PowerPC is a hard processor which can be found in some Xilinx devices such as the Virtex-II PRO, Spartan-3 and Virtex-4 series chips. AVR is another hard processor used in the Atmel FPSLIC device in combination with Atmel's programmable logic architecture.

Soft processors are microprocessors that are implemented by the user using the logic primitives of the FPGA. They provide necessary elements and leave control to the user to choose optional features, which may include caches, various arithmetic units, FPUs, debug logic and other function modules for particular application requirements. The MicroBlaze is a 32-bit soft processor and PicoBlaze is a simpler alternative with an 8-bit data bus made available from Xilinx. Nios and NiosII are 32-bit soft processors provided by Altera. Other soft cores include the open source LatticeMico32 and LatticeMico8, as well as third-party (either commercial or free) processor cores.

The key benefits of using a soft processor include configurability to trade off price and performance, faster time to market, easy integration with the FPGA fabric, and no processor obsolescence [1]. It is easy to create a custom processor with the exact mix of peripherals, memory interfaces, and hardware accelerators for a given application. The number of soft processors that can be instantiated in a device is only limited by the FPGA's logic resources. The number of hard processors, conversely, is fixed in a particular FPGA. While soft IP cores provide flexibility to the user, the optimized design techniques for

hard IP blocks ensure low area/power consumption and substantially better performance as compared to typical un-optimized designs.

Their coarse-grained architectures and the embedded microprocessors have made FP-GAs feasible choices in the high-performance computing area. FPGA-based SIMD/MIMD systems [41–44], vector microprocessors [45–48] and other reconfigurable systems [34] have reported impressive performance improvement for applications from various domains.

#### 1.3.3 Design Flow

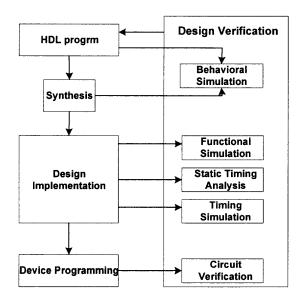

Fig. 1.1 shows the traditional FPGA design flow. Our design follows this conventional design flow and ModelSim is used for gate-level simulation, Synplify pro and Xilinx XST are used for synthesis, and Xilinx place-and-route tools are used to put the design on FPGA chips. Other development tools, such as Viva of Starbridge Systems [49] and Corefire of Annapolis Micro Systems[50] aim to provide alternative programming styles for FPGA designs targeting specific systems. They provide user friendly graphic interfaces and incorporate a bunch of high performance IP cores. The user can just use a "drag and drop approach." Their benefit is short design time and development that does not descend

Figure 1.1: FPGA design flow.

into low-level hardware details. But on the other hand, they limit the designer's control and, therefore, the hardware implementation can be hardly fully optimized. Our experiments show that a processor written in VHDL and running at 100 MHz on the Annapolis WildStar-II board can only run at 60 MHz when designed by Corefire.

#### 1.4 Motivations and Objectives

It is becoming increasingly difficult to build higher performance uniprocessor chips because of the complexities in manufacturing and power management. On the other hand, the quadratically increasing circuit complexity forbids the exploration of more ILP, which is anyway rather limited in the majority of programs. To continue raising the performance, silicon designers then focused on TLP to realize next generation processors. Multicore processor design is the result of this trend. It can potentially explore TLP to provide increased single-chip computational capability without requiring a complex microarchitecture. It has thus been deemed to be the most important trend in computer architecture and has been produced for servers, desktops and laptops by major processor chip makers like Intel, AMD, Sun and IBM.

On the other hand, in the embedded system market developers have been working with multicore devices for years. For example, the Apple iPOD features dual 90MHz ARM7TDMI processors; engineers at NEC have developed a processor for cellular telephones that includes three ARM processor cores in a single chip, aimed to improve the multimedia capabilities of cell phones. Texas Instruments Inc. (TI) will introduce two multicore DSPs for wireless infrastructure. ARM, a leader company in embedded system design, developed its multicore embedded processor ARM11 MPCore, which can be configured to contain one to four processors [51].

Although multicore processor designs can boost system performance by exploring both TLP and ILP, and can solve the power management problem, their ability to utilize DLP is still limited. Since vector processing is the most efficient way to explore DLP and

vector operations are rather common in embedded applications, including a vector processing unit in the embedded multicore processor can increase the system performance in many cases. Although current general-purpose processors normally support DLP, the allocated hardware resources are quite limited [9, 52]. We propose that some hardware budget in multicore processor systems be used to realize a shared vector unit to greatly speedup computations for applications abundant in DLP. As the number of transistors doubles in about 18 months (Moore's law), the need for shared vector units in multicore designs will become even more important. Thus, our thesis is that rather than improving only scalar or TLP performance, we could spend some of the hardware budget to realize a vector unit which will greatly speedup computations for applications abundant in DLP. To be realistic, limited by the application itself and the compiler's vectorizing capabilities, most of the general-purpose programs can only be partially vectorized. For efficient resource usage, one vector unit should be shared by several scalar processors. The specific objectives of this dissertation are as follows:

- Design and implement a vector microprocessor which can provide significant speedups on vector-oriented, computation-intensive algorithms, with low energy consumption.

- Build an FPGA-based prototype for a multicore processor system with a shared vector unit, which should be able to deliver higher performance as compared to multiple scalar processors under the same area budget for some full or partially vactorizable applications.

- The designed system should support high-level languages and compilers.

- The system should support modular hardware implementation.

- Benchmark the prototype for embedded applications.

Thus, the target is a vector processor design framework suitable for embedded systems in multicore processor environments with a shared vector unit (MCwSV). The vector

unit should support massive floating-point calculations, generally a time-consuming component in scientific computing. The design should be easily configured with respect to the kinds/number of function units in order to match various application requirements. MCwSV should be able to take advantage of mature programming languages and compiler technologies by using processor IPs, such as MicroBlaze, which is a commercial 32-bit RISC processor. The vector unit should be connected to the scalar processors with standard bus interfaces to provide ease of scalability and code portability.

Considering the inherent flexibility of FPGAs and due their (re)configuration capability, an MCwSV architecture template should be built based on tradeoffs involving resource consumption and performance.

#### **CHAPTER 2**

#### VECTOR PROCESSING FOR EMBEDDED APPLICATIONS

As stated before, a vector microprocessor has much simpler hardware architecture and lower energy consumption than VLIW and superscalar processors. And it is probably the most efficient way to deal with applications that have abundant data parallelism and little data reuse. Also, as shown in [18], the degree of vectorization can exceed 90% for most benchmarks in the EDN Embedded Microprocessor Benchmark Consortium (EEMBC) [20]. All of these make vector processing a very competitive choice for embedded systems.

In this chapter, a vector processing system with two identical vector processors is proposed and implemented on the Annapolis WildStar II board [53]. Each vector microprocessor has abundant parallel calculation units and supports floating-point calculations. Specialized hardware and respective user instructions for efficient sparse matrix operations were implemented as well. To test its performance, dense matrix-matrix multiplication, sparse matrix-vector multiplication and a sparse linear equation solver, with input matrices from various application domains, are run on the system [45–48]. Our comparison with a commercial PC demonstrates that our implementation is very efficient despite its low frequency. Our design permits general-purpose programmability and can be applied to other application areas as well. Such applications having similar types of data parallelism could benefit from reduced costs and smaller execution times on our vector processing system. With continued advances in FPGA technologies, the expected increased speeds and densities could yield much better performance in the near future for such computationally intensive problems on FPGA-based vector implementations.

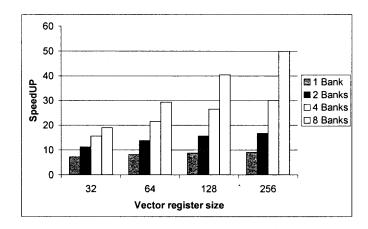

For area/power efficiency, the vector processor is organized in eight banks; each bank has part of the vector register file and two arithmetic units. The memory is also divided into eight banks to provide higher bandwidth.

#### 2.1 Architecture of the Vector Processor

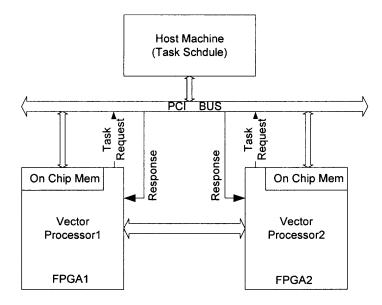

Our vector processing system includes two identical programmable vector microprocessors embedded in two Xilinx Virtex-II XC2V6000 chips on the Annapolis WildStar II board [53]. The Annapolis board can be mounted on the host machine through a PCI socket [53]. Libraries in the host machine and drivers for the board are provided for data transmissions between the off-chip/on-chip memories and the host. Our two vector processors communicate with the host machine via an on-chip dual port memory. The host machine assigns work to them based on their requests and the load balance. Each vector processor runs at 70MHz and supports the IEEE 754 single-precision floating-point standard and efficient implementation for sparse matrices. The overview of the system is shown in Fig. 2.1.

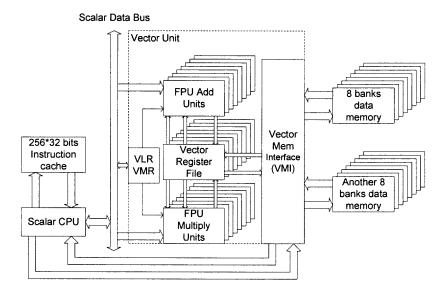

The vector processor is composed of a vector core and a tightly coupled five-stage pipelined scalar unit, as shown in Fig. 2.2. It is organized as a Harvard architecture with

Figure 2.1: Overview of the system.

Figure 2.2: Block diagram of the vector processor (VLR: Vector Length Register, VMR: Vector Mask Register).

separate bus interface units for instruction and data access. The scalar processor fetches and decodes instructions. It does the actual work for scalar commands and forwards the vector instructions to the vector core. The vector core is structured as eight parallel lanes, where each lane contains a portion of the vector register file, a floating-point multiplier, a floating-point adder and connection to the eight-bank memory system. It can produce up to eight results and get a maximum of eight data items from the memory banks per clock cycle.

#### 2.1.1 Instruction Set Architecture

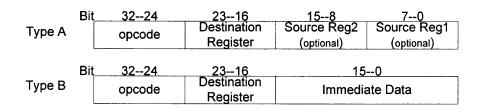

Our vector processor has a RISC architecture supporting 24 instructions. There are 16 scalar instructions in the areas of data transfer, arithmetic operations and program control. The other eight instructions run in the vector mode for data transfers and arithmetic operations. The latter instructions are of Type A or Type B, as shown in Fig. 2.3. Type A instructions use up to two source registers and one destination register. Type B instructions use one destination register and a 16-bit immediate operand. Although we do not need eight bits to represent the opcode or registers, it is a good choice for a possible extension

Figure 2.3: Instruction formats.

for the instruction set or register populations in the future. Two addressing modes are used in our design: direct and register indexed.

#### 2.1.2 Scalar Unit

The scalar processor in our system supports 16 instructions for control, register and memory access, and arithmetic operations. There is a five-stage pipeline (fetch, decode, execute, memory access and write back) in it, as shown in Fig. 2.4. This scalar processor includes an arithmetic logic unit (ALU), a register file, a data hazard detection unit, and a data forwarding unit. For the sake of simplicity, Fig. 2.4 does not depict all the hardware. The shaded areas are unique to the vector system design; they are used to transfer useful information to the vector core. The ALU is able to deal with 16-bit integer addition/subtraction and mul-

Figure 2.4: Scalar processor architecture.

tiplication. The register file includes 30 general-purpose registers and two special-purpose registers for vector processing. It supports two read ports and one write port.

Two specialized registers in the register file are used to control vector operations. They are: vector-length register (VLR) and vector-mask register (VMR). VLR is used to control the length of vector operations and VMR indicates that operations are to be applied only to the vector elements with corresponding entries equal to 1 in VMR.

To avoid EXE and MED data hazards due to pipelining, data hazard detection and forwarding units are implemented. We must emphasize that all scalar pipeline hazards can be avoided either with data forwarding or interlocking in hardware, so scalar instruction scheduling is not required for correctness; however, it may improve performance. This greatly eases code writing for our processor.

#### 2.1.3 Vector Register File

The vector register file lies in the heart of the vector unit. It provides both temporary storage for intermediate values as well as the interconnect between the vector floating-point units (VFUs) [14]. A straightforward way to implement the vector register file is to use a single multi-ported memory. But this is a very expensive solution requiring many logic resources that increase the power consumption of the FPGA chip. Take the example of eight vector registers each having 32 32-bit elements; the left diagram in Fig. 2.5 shows the slice usage for a Xilinx XC2V6000 chip and the right one shows the power consumption assuming that it runs at 70MHz. It can be observed that the slices will be used up quickly and the power consumption increases greatly for an increased number of ports. We'd like to emphasis here that all the results presented in this chapter are after the place-and-route step for the XC2V6000 chip.

To reduce the cost, we could divide the vector register file into banks having smaller numbers of register elements and ports. A similar method has been used in a media processor [7] and a smart memory structure [54]. In our design, the vector register file is divided

Figure 2.5: Resource and power consumption for single-block implementation of a vector register file containing 8 vector registers of 32 32-bit elements.

into eight banks, where each bank has two read ports and one write port. Take the example of 8 vector registers, each having 32 32-bit elements; the vector register file construction and its connections with other components are shown in Fig. 2.6.

| FPU            | FPU                                | FPU            | FPU            | FPU                     | FPU            | FPU            | FPU            |  |  |  |  |

|----------------|------------------------------------|----------------|----------------|-------------------------|----------------|----------------|----------------|--|--|--|--|

| Multiplier     | Multiplier                         | Multiplier     | Multiplier     | Multiplier              | Multiplier     | Multiplier     | Multiplier     |  |  |  |  |

| FPU            | FPU                                | FPU            | FPU            | FPU                     | FPU            | FPU            | FPU            |  |  |  |  |

| Adder          | Adder                              | Adder          | Adder          | Adder                   | Adder          | Adder          | Adder          |  |  |  |  |

| bank0          | bank1                              | bank2          | bank3          | bank4                   | bank5          | bank6          | bank7          |  |  |  |  |

| V0(0)          | V0(1)                              | V0(2)          | V0(3)          | V0(4)                   | V0(5)          | V0(6)          | V0(7)          |  |  |  |  |

| V0(8)          | V0(9)                              | V0(10)         | V0(11)         | V0(12)                  | V0(13)         | V0(14)         | V0(15)         |  |  |  |  |

| V0(16)         | .V0(17)                            | V0(18)         | .V0(19)        | V0(20)                  | V0(21)         | V0(22)         | V0(23).        |  |  |  |  |

| V0(24)         | V0(25)                             | V0(26)         | V0(27)         | V0(28)                  | V0(29)         | V0(30)         | V0(31)         |  |  |  |  |

| :              | :                                  | :              | i              | :                       | i              |                | i              |  |  |  |  |

| V7(0)          | V7(1)                              | V7(2)          | V7(3)          | V7(4)                   | V7(5)          | V7(6)          | V7(7)          |  |  |  |  |

| V7(8)          | V7(9)                              | V7(10)         | V7(11)         | V7(12)                  | V7(13)         | V7(14)         | V7(15)         |  |  |  |  |

| V7(16)         | V7(17)                             | V7(18)         | V7(19)         | V7(20)                  | V7(21)         | V7(22)         | V7(23)         |  |  |  |  |

| V7(24)         | V7(25)                             | V7(26)         | V7(27)         | V7(28)                  | V7(29)         | V7(30)         | V7(31)         |  |  |  |  |

|                | $\downarrow$                       |                |                | $\downarrow$ $\uparrow$ |                |                |                |  |  |  |  |

|                | Vector Memory interface controller |                |                |                         |                |                |                |  |  |  |  |

|                |                                    |                |                |                         |                |                |                |  |  |  |  |

| Data<br>Mem(0) | Data<br>Mem(1)                     | Data<br>Mem(2) | Data<br>Mem(3) | Data<br>Mem(4)          | Data<br>Mem(5) | Data<br>Mem(6) | Data<br>Mem(7) |  |  |  |  |

Figure 2.6: Vector register file organization and connections with other components.

The vector memory interface (VMI), FPU adder and FPU multiplier share the read/write ports of the register file in a time-multiplexed way. The bandwidth of the vector register file in this configuration is 6.72 GBytes/sec when operating at 70 MHz. If the equivalent bandwidth is to be provided by a single register bank, a register file with 16 read ports and 8 write ports would be required. This is significantly less efficient in terms of area, speed and power consumption than the bank-based architecture since the latter only consumes 24% of the slices and 4.3W of power while the resource and power consumptions increase dramatically with an increase in the number of ports, as shown in Fig. 2.5. The additional cost of the bank structure corresponds to a circuit for data transfers between any pair of memory-register banks. This circuit uses quite a few FPGA resources and lies in the critical path; but comparing to the single register file implementation, this resource usage is much smaller and does not change the fact that the bank structure is much more efficient than the single block implementation.

Besides the structure of the vector register file, we also need to determine its size. Eight vector registers are chosen in our implementation. Although increasing the number of vector registers can reduce the memory bandwidth requirements by allowing more data reuse, most matrix-based applications have little data reuse. Thus, eight vector registers suffice and can demonstrate the effectiveness of our design. Each vector element has 32 bits, which is required for single-precision floating-point calculations. More vector elements in a vector register could amortize the startup time and speedup the overall execution; the time to fill up the pipeline is eight clock cycles for floating-point multiplication and eleven clock cycles for floating-point addition. So, we decided to implement as many elements as allowed by the available resources without increasing the circuit complexity tremendously. We experimented with 8, 16, 32 and 64 elements per vector in our design. With the increased circuit complexity and congestion of the on-chip routing resources for more elements, the system frequency of the design drops from 70 MHz for 8, 16 and 32

elements to 62.5 MHz for 64 elements. A more substantial frequency reduction should be expected for more elements.

# 2.1.4 Vector Memory Interface (VMI)

VMI controls all the data transfers to/from the data memory banks. It supports scalar loads/stores from/to any data memory bank, vector loads/stores starting with any data memory bank and for any length, and indexed loads/stores for sparse matrices. The execution time of vector load/store and indexed load/store is not deterministic. The starting point in memory and the length of the data affect the execution time of these operations. Besides the impact of the vector length, different data storage patterns in the eight data memory banks may result in different contention patterns for the indexed load/store, thus resulting in different execution times. A 8x8 32-bit crossbar is implemented with 16 eight-to-one 32-bit multiplexers to transfer data between any pair of memory-register banks. This crossbar has a constant switch delay of one clock cycle. Because of the complicated control logic and large number of multiplexers, it contributes to part of the critical path in our design.

### 2.2 Performance Results

To test the performance of our vector processing system, dense matrix-matrix multiplication, sparse matrix-vector multiplication and a sparse linear equation solver were run on it. Our system makes no assumption about the sparsity structure of the input matrices to guarantee the performance. Various matrices from different application areas with different sparse structures are given as input. Comparisons are made with the calculation time on a commercial Dell PC that contains a 1.2G Pentium-III processor, 512M bytes of memory and 512K bytes of L2 cache, and employs the Linux operating system. It is a difficult job to get the accurate execution time on the PC; we apply several criteria to make sure that the time measured on the PC is representative of its capabilities [55].

- 1. Since the time for our experiments is at the milliseconds level, the interrupt timer that samples every 10ms is imprecise. So we use assembly-language code to reach the IA32 clock cycle register and get the clock cycles used by the program.

- 2. In order to minimize data and instruction cache misses, the code is run once before it is run again to measure the time.

- 3. We run the program twenty times and take the smallest value as the calculation time.

For the execution time on our vector processor, the transmission time between the host machine and the FPGA board is not included. Because data transmissions are through the PCI socket and under the control of the interrupt handler, the delay time is large and unpredictable. [44] presents a way to hide such latencies. We emphasize the architecture of the vector processor and how to provide efficient vector processing. Therefore, the transmission time is omitted in our performance analysis. We can see from the following examples that the clock cycles on our vector processing system are hundreds of times smaller than those on the Dell PC. But the architecture of the FPGAs limits the maximum frequency, so our system can only run at 70MHz. Despite the tremendous frequency disparity compared to the 1.2GHz of the commercial PC, we will see that our vector processing system still outperforms the PC when the matrix size becomes larger or when two vector microprocessors are used.

### 2.2.1 Preliminaries on Vector Processing

Vector computers require advanced pipelining [56]. Longer vectors in the program will provide better performance because the penalty caused by the start-up time is amortized. Actually the throughput of the vector processor highly depends on the length of the vectors. The recurrence problem and sparse matrices are two general situations which forbid generating long vectors. Without appropriate preprocessing, the vector processor can hardly achieve significant improvement [57, 58]. So in implementations the data storage scheme

Figure 2.7: Recurrence problem.

and application algorithm are modified to get longer input vectors. We explain respectively how to avoid the effects of the recurrence problem and sparse matrices in the flowing two subsections.

2.2.1.1 The Recurrence Problem. Optimizing a code for vector processing basically consists of arranging the algorithmic steps in such a form as to produce long and vectorizable DO loops [58]. One of the most common obstacles to vectorization is the "recurrence" problem; it is when a variable is obtained based on the value of that variable in an earlier iteration [2], as shown in Fig. 2.7. The delay caused by the recurrence problem can be large, especially for floating-point operations which require more clock cycles. Generally, this problem can be solved by loop unpacking and parallel calculations. Multiplication and accumulation (MAC) is highly used in matrix operations, and creates a recurrence problem. A common solution to MAC is to use more addition units and organize them in a binary tree. This way the delayed clock cycles can be reduced from  $n \times (delay \ clocks \ for \ addition)$ to  $\lceil \log(2, n) \rceil \times (delay \ clocks \ for \ addition)$ . But for floating-point operations, where, for example, 11 clock cycles are needed for single-precision floating-point addition in our implementation, the binary tree structure still has quite a significant delay. Also, the binary tree needs more circuit area and more complex control logic, which may make the MAC unit in a microprocessor a critical part in the circuit design [59]. So in our implementation we replace the MAC operations by vector multiplication and addition as shown in the following pseudo codes. Take the example of matrix-vector multiplication; matrix-matrix multiplication can be seen as an extension to matrix-vector multiplication.

```

loadV

V1

col 1 of result matrix c

loop1:loadV

col j of matrix a

V2

load

j element of vector b

R1

mulVS

V3

V2

R1

addV

V1

V3

V1

j--, if not zero, jump to loop1

storeV V1

col 1 of result matrix c

```

**2.2.1.2 Pseudo-Column Ordering for Sparse Matrix Operations.** The efficiency of sparse matrix multiplication highly depends on how the non-zero entries are represented in the memory. A proper storage scheme can greatly enhance the performance of the vector processor by allowing much longer vectors even in a very sparse matrix. The pseudo-column method stores the non-zeros in a compact way by shifting all non-zeros in a row to the left. The following example shows that the non-zeros in matrix A are shifted to the left to produce matrix AP and their corresponding column number is stored in matrix CI.

These two matrices are not actually built; they are just used for explanation. Values and column indices are stored in the memory based on the pseudo columns. Because the pseudo-column only contains data from different rows, the recurrence problem caused by

MAC can be avoided by vector multiplication and addition. Another advantage of this storage scheme is that elements in the pseudo-columns can be loaded contiguously and accessed in a unit stride fashion.

## 2.2.2 Sparse Linear Equation Solver

In a conventional way, a linear system of equations given in the form Ax = b is solved by factorizing matrix A into triangular matrices and then carrying out data forward/backward substitutions. These substitutions are essentially sequential and hinder parallel computing. Getting the inverse matrix of A and solving the problem by matrix multiplication is an obvious solution, but the question is how to get the inverse matrix. There will also be a major problem with sparse matrices: the inverse matrix of A may turn to be dense even if A has only a few non-zeros. The W-matrix method, which was proposed in [60, 61], provides an easy way to get the inverse matrix by partitioning the sparse matrix into a product having partitions with no fill-ins or with user controlled fill-ins. Thus, in each partition calculations can be done in parallel. Several W-matrix solvers have been run on shared-memory computers, multiprocessors and vector supercomputers [57, 58, 62, 63]. We show in this paper that it can also run efficiently on our vector system.

### **2.2.2.1 The W-matrix Method.** A linear equation given in the form

$$Ax = b (2.1)$$

where A is a large, sparse and symmetric matrix can be solved in the following steps:

$$x = A^{-1}b = (LDU)^{-1}b = U^{-1}D^{-1}L^{-1}b$$

(2.2)

where L, D and U represent the decomposition of A into a lower triangular, diagonal and upper triangular matrix, respectively. With appropriate ordering [61], we can first reduce the factorization fill-ins and factorize A into the form  $LDL^T$ . After this ordering, assume

that  $W = L^{-1}$ . Then, (2.2) can be rewritten as:

$$x = W^T D^{-1} W b. (2.3)$$

It is obvious that (2.3) can be solved in three steps:

$$z = Wb; y = D^{-1}z; x = W^{T}y$$

(2.4)

that replace forward and backward substitutions with matrix-vector products. Within each step, all multiplications can be carried out concurrently, which is suitable for parallel programming and vector computing. W-matrix is associated with algorithms that partition the inverses of L and U into elementary matrices with no fill-ins or only user controlled fill-ins. Based on [61] and [60], we can write matrix L as

$$L = L_1 L_2 \cdots L_n \tag{2.5}$$

where  $L_i$  is an identity matrix except that its *i*-th column is actually the *i*-th column of matrix L. Then:

$$W = L^{-1} = L_n^{-1} L_{n-1}^{-1} \cdots L_1^{-1} = W_n W_{n-1} \cdots W_1$$

(2.6)

where  $W_n$  is equal to  $L_n$  with the sign of its off-diagonal elements reversed. Plugging (2.6) into (2.3), we get the expression:

$$x = W_1^T W_2^T \cdots W_n^T D^{-1} W_n \cdots W_2 W_1 b. \tag{2.7}$$

To avoid fill-ins induced in (2.7), we need 2n + 1 sequential steps of multiplication to get the final solution; it has no advantage over the common substitution method. But according to [60, 61], adjacent matrices  $W_i$ , for  $1 \le i \le n$ , can be combined in several ways to form various partitions:

$$x = W_1^T W_2^T \cdots W_p^T D^{-1} W_p \cdots W_2 W_1 b.$$

(2.8)