### **Copyright Warning & Restrictions**

The copyright law of the United States (Title 17, United States Code) governs the making of photocopies or other reproductions of copyrighted material.

Under certain conditions specified in the law, libraries and archives are authorized to furnish a photocopy or other reproduction. One of these specified conditions is that the photocopy or reproduction is not to be "used for any purpose other than private study, scholarship, or research." If a, user makes a request for, or later uses, a photocopy or reproduction for purposes in excess of "fair use" that user may be liable for copyright infringement,

This institution reserves the right to refuse to accept a copying order if, in its judgment, fulfillment of the order would involve violation of copyright law.

Please Note: The author retains the copyright while the New Jersey Institute of Technology reserves the right to distribute this thesis or dissertation

Printing note: If you do not wish to print this page, then select "Pages from: first page # to: last page #" on the print dialog screen

The Van Houten library has removed some of the personal information and all signatures from the approval page and biographical sketches of theses and dissertations in order to protect the identity of NJIT graduates and faculty.

#### **ABSTRACT**

### RELIABILITY STUDIES OF TIN/Hf-SILICATE BASED GATE STACKS

### by Naser Ahmed Chowdhury

Hafnium-silicate based oxides are among the leading candidates to be included into the first generation of high- $\kappa$  gate stacks in nano-scale CMOS technology because of their distinct advantages as far as thermal stability, leakage characteristics, threshold stability and low mobility degradation are concerned. Their reliability, which is limited by trapping at pre-existing and stress induced defects, remains to be a major concern.

Energy levels of electrically active ionic defects within the thick high- $\kappa$  have been experimentally observed in the context of MOS band diagram for the first time in Hf-silicate gate stacks from low temperature and leakage measurements. Excellent match between experimental and calculated defect levels shows that bulk O vacancies are probably responsible for electron trapping at both shallow and deep levels. Their role in trapping and transport under different gate polarity and band bending conditions has been determined. For gate injection, electron transport through mid-gap states dominates, which leads to slow transient trapping at deep levels. Under substrate injection field and temperature dependent transport through conduction-edge shallow levels or trap-assisted tunneling due to *negative-U* transition occurs depending on bias condition. The former gives rise to fast transient trapping, whereas the latter is responsible for slow transient trapping.

Mixed degradation, due to trapping of both electrons and holes in the trap levels within the bulk high- $\kappa$ , was observed under constant voltage stress (CVS) applied on n-channel MOS capacitors with negative bias condition. Mixed degradation resulted in turn-around effect in flat-band voltage shift ( $\Delta V_{FB}$ ) with respect to stress time. Under CVS with positive bias, applied on nMOSFETs, lateral distribution of trapped charges in the deep levels causes turn-around effect in threshold voltage shift ( $\Delta V_T$ ) with respect to stress levels.

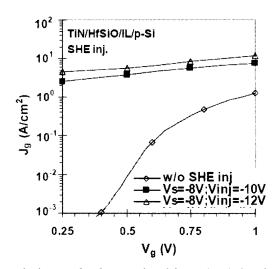

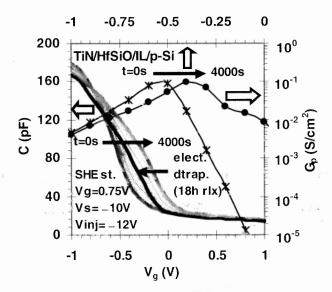

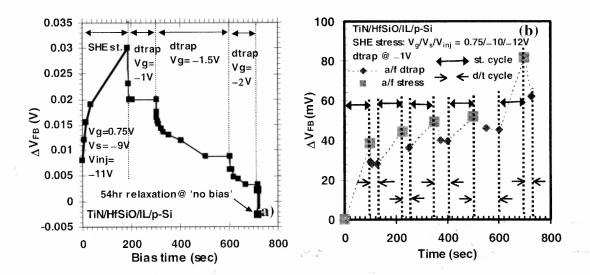

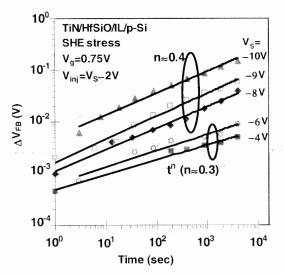

For the incident carrier energies above the calculated O vacancy formation threshold and thick high- $\kappa$  layer, both flatband voltage shift, due to electron trapping at the deep levels, and increase in leakage current during stress follow  $t^n$  (n  $\approx 0.4$ ) power-law dependence under substrate hot electron injection. Negative-U transitions to deep levels are shown to be responsible for the strong correlation between slow transient trapping and trap assisted tunneling.

As far as negative bias temperature instability, NBTI effects on pMOSFETs is concerned,  $\Delta V_T$  is due to the mixed degradation within the bulk high- $\kappa$  for low bias conditions. For moderately high bias,  $\Delta V_T$  shows an excellent match with that of SiO<sub>2</sub> based devices, which is explained by reaction-diffusion (R-D) model of NBTI. Under high bias condition at elevated temperatures, due to high Si-H bond-annealing/bond-breaking ratio, the experimentally observed absence of the impact ionization induced hot holes at the interfacial layer (IL)/Si interface probably limits the interface state generation and  $\Delta V_T$  as they quickly reach saturation.

Time-zero dielectric breakdown (TZBD) characteristics of TiN/HfO<sub>2</sub> based gate stacks show that thickness and growth conditions significantly affect the BD field of IL. For the thin high- $\kappa$  layers, BD of IL triggers BD of the gate stack. Otherwise, BD of high- $\kappa$  layer initiates it. During time dependent dielectric breakdown, TDDB, four regimes of degradation are observed under CVS with high gate bias conditions: (i) charge trapping/defect generation, (ii) soft breakdown (SBD), (iii) progressive breakdown and (iv) hard breakdown (HBD). Activation energy of bond-breakage, found from Arrhenius plots of 63% failure value of  $T_{BD}$ , shows that IL degradation triggers gate stacks BD, and the wear-out during TDDB.

### RELIABILITY STUDIES OF TIN/Hf-SILICATE BASED GATE STACKS

by Naser Ahmed Chowdhury

A Dissertation

Submitted to the Faculty of

New Jersey Institute of Technology

in Partial Fulfillment of the Requirements for the Degree of

Doctor of Philosophy in Electrical Engineering

**Department of Electrical and Computer Engineering**

May 2007

### APPROVAL PAGE

### RELIABILITY STUDIES OF TIN/Hf-SILICATE BASED GATE STACKS

### **Naser Ahmed Chowdhury**

|                                                                                                                          | 11/11/06               |

|--------------------------------------------------------------------------------------------------------------------------|------------------------|

| Dr. Durgamadhab Misra, Dissertation Advisor<br>Professor of Electrical and Computer Engineering, NJIT                    | Date                   |

|                                                                                                                          | Nov. 11, 2006          |

| Dr. Arvind Kumar, Committee Member<br>Member of Technical Staff, IBM T J Watson Research Center,<br>Yorktown Heights, NY | Date                   |

|                                                                                                                          | Nov. 11, 2006<br>Date  |

| Dr. Leonid Tsybeskov, Committee Member<br>Associate Professor of Electrical and Computer Engineering, NJ                 |                        |

|                                                                                                                          | 1/64 11 1200 6<br>Date |

| Dr. Marek Sosnowski, Committee Member<br>Professor of Electrical and Computer Engineering, NJIT                          | Date                   |

|                                                                                                                          | 11-11-2006             |

| Dr. Anthony Fiory, Committee Member<br>Research Professor of Physics, NJIT                                               | Date                   |

|                                                                                                                          | 11/11/2006             |

| Dr. N.M. Ravindra, Committee Member<br>Professor of Physics, NJIT                                                        | Date                   |

#### **BIOGRAPHICAL SKETCH**

**Author:** Naser Ahmed Chowdhury

**Degree:** Doctor of Philosophy

**Date:** May 2007

#### **Undergraduate and Graduate Education:**

- Doctor of Philosophy in Electrical Engineering, New Jersey Institute of Technology, Newark, NJ, 2007

- Master of Science in Electrical Engineering,

University of Texas at Arlington, Arlington, TX, 2001

- Bachelor of Science in Electrical and Electronic Engineering, Middle East Technical University, Ankara, Turkey, 1995

Major: Electrical Engineering

#### **Presentations and Publications:**

N. A. Chowdhury, P. Srinivasan and D. Misra,

"Trapping in Deep Defects under Substrate Hot Electron Stress in TiN/Hf-Silicate Based Gate Stacks".

Solid State Electronics,

(Accepted for publication).

N. A. Chowdhury and D. Misra,

"Charge Trapping at Deep States in Hf-Silicate based High-κ Gate Dielectrics".

Journal of Electrochemical Society,

(Accepted for publication).

N. A. Chowdhury, D. Misra and N. Rahim,

"Negative Bias Temperature Instability in TiN/Hf-Silicate Based Gate Stacks".

International Journal of High Speed Electronics and Systems, (Accepted for publication).

D. Misra, R. Garg, P. Srinivasan, N. Rahim and N.A. Chowdhury, "Interface Characterization of High-k Dielectrics on Ge Substrates", Materials Science in Semiconductor Processing, (Accepted for publication).

N. A. Chowdhury, G. Bersuker, C. Young, R. Choi, S. Krishnan and D. Misra, "Breakdown Characteristics of nFETs in Inversion with Metal/HfO<sub>2</sub> Gate Stacks",

Microelectronic Engineering,

(Accepted for publication).

P. Srinivasan, N.A. Chowdhury and D. Misra,

"Charge trapping in Ultra-thin Hafnium silicate/Metal gate stacks", Electron Device Letters, Vol.26, No. 12, pp. 913-915, 2005.

N. A. Chowdhury, R. Garg and D. Misra,

"Charge Trapping and Interface Characteristics of Thermally Evaporated HfO<sub>2</sub>",

Applied Physics Letters,

Vol. 85, No. 15, pp. 3289-3291, 2004.

R. Garg, N. A. Chowdhury, M. Bhaskaran, P. K. Swain and D. Misra, "Electrical characteristics of thermally evaporated HfO<sub>2</sub>", Journal of Electrochemical Society, Vol. 151., No.10, pp. F215-F219, 2004.

N. A. Chowdhury, G. Bersuker, C. Young, R. Choi, S. Krishnan, and D. Misra, "Time Zero Dielectric Breakdown Characteristics of TiN/HfO<sub>2</sub> Based High-k Gate Stacks",

IEEE Transactions on Device and Materials Reliability, (In preparation).

N. A. Chowdhury, G. Bersuker, R. Choi, H. Alshareef, N. Rahim and D. Misra, "Low Temperature Mobility Characteristics of Hf-Silicate Based nMOSFETs with Optimized N-metal Gate" Electrochemical and Solid-State Letters, (In preparation).

N. A. Chowdhury, G. Bersuker, C. Young, R. Choi, N. Rahim and D. Misra, "Temperature Dependent TDDB Characteristics of TiN/ HfO<sub>2</sub> Based Gate Stacks",

Electrochemical and Solid-State Letters, (In preparation).

### T. Kundu, R. Garg, N. A. Chowdhury and D. Misra,

"Electrical Techniques for the Characterization of Dielectric Films", Electrochemical Society Interface, Vol. 14, No. 3, pp.17-20, 2005.

#### N. A. Chowdhury and D. Misra,

"NBTI Effects in pMOSFETS with TiN/Hf-Silicate Based Gate Stacks", ECS Trans. on Physics and Technology of High-k Gate Dielectrics IV, Cancun, Mexico, pp. 215-224, October, 2006.

#### N. Rahim, N. A. Chowdhury and D. Misra,

"Role of Experimentally Observed Defect Energy Levels in Carrier Transport and Charge Trapping in Metal Gate/Hf-Silicate Based Gate Stacks",

The 210<sup>th</sup> Electrochemical Society Meeting, Cancun, Mexico, October, 2006.

#### N. A. Chowdhury, G. Bersuker, C. Young, S. Krishnan, R. Choi and D. Misra,

"Breakdown characteristics of TiN/HfO<sub>2</sub> based high-κ gate stacks", The 3<sup>rd</sup> International Workshop on Advanced Gate Stacks Technology, Austin, Texas, September, 2006.

### D. Misra, N. A. Chowdhury and N. Rahim,

"Negative bias Temperature Instability in TiN/Hf-silicate Based Gate Stacks",

IEEE Lester Eastman Conference on High Performance Devices, Cornell University, Itahaca, NY, August, 2006.

#### D. Misra and N. A. Chowdhury,

"Charge Trapping in High-k Gate Dielectrics: A Recent Understanding", ECS transactions on Dielectrics for Nanosystems II: Materials Science, Processing, Reliability, and Manufacturing, Denver, Colorado, pp. 311-321, May, 2006.

#### N. A. Chowdhury, P. Srinivasan and D. Misra,

"Trapping in Deep Defects under Substrate Hot Electron Stress in TiN/Hf-Silicate Based Gate Stacks",

Proceedings of International Semiconductor Device Research Symposium, Bethesda, Maryland, pp. WP1-03 to 04, December, 2005.

#### N. A. Chowdhury, P. Srinivasan and D. Misra,

"Evidence of deep energy states from low temperature measurements and their role in charge trapping in metal gate/Hf-silicate gate stacks", ECS transactions on Physics and Technology of High-k Gate Dielectrics III,

Los Angeles, California, pp. 767-776, October, 2005.

N. A. Chowdhury, P. Srinivasan, D. Misra, R. Choi and B. H. Lee,

"Observation of deep bulk defects using low temperature techniques in TiN/HfSi<sub>x</sub>O<sub>y</sub> gate stack and their role in BTI and HCS effects",

The 2<sup>nd</sup> International Symposium on Advanced Gate Stacks Technology, Austin, Texas, September, 2005.

P. Srinivasan, N. A. Chowdhury, A. Peralta, D. Misra, R. Choi and B. H. Lee,

"Charge Trapping in Metal Gate/High- k n-MOSFETS during Substrate Injection",

Proceedings of International Symposium on Advanced Gate Stack,

Source/Drain and Channel Engineering for Si-Based CMOS: New Materials, Processes and Equipment,

Quebec City, Canada, pp. 366-373, May, 2005.

D. Misra, N. A. Chowdhury, R. Garg and P. Srinivasan,

"Integration of High-k Dielectrics into Sub-65nm CMOS Technology:

Requirements and Challenges",

Proc. of the IEEE TENCON,

Chiang Mai, Thailand, pp. 1401-1405, November, 2004.

N. A. Chowdhury, P. Srinivasan, D. Misra, R. Choi and B. H. Lee,

"Charge Trapping Characteristics of TiN/HfSi<sub>x</sub>O<sub>y</sub>/SiO<sub>2</sub>/p-Si MOS Devices under Stress",

Int. SEMATECH Workshop on Electrical Characterization and Reliability of High-k Devices,

Austin, Texas, Nov., 2004.

N. A. Chowdhury, R. Garg and D. Misra,

"Time Dependent Dielectric Breakdown of Thermally Evaporated HfO<sub>2</sub> for Nanoscale Devices",

Proc. of 1<sup>st</sup> Intl. Symp. on Dielectrics for Nanosystems: Mat. Science,

Processing, reliability and Manufacturing,

Honolulu, Hawaii, pp. 381-390, October, 2004.

N. A. Chowdhury, R. Garg and D. Misra,

"Charge Trapping and Interface Characteristics of Thermally Evaporated HfO<sub>2</sub>",

The 205<sup>th</sup> Electrochemical Society Meeting, San Antonio, TX, May, 2004.

R. Garg, N. A. Chowdhury, M. Bhaskaran, P. K. Swain and D. Misra,

"Electrical Characteristics of Thermally Evaporated HfO<sub>2</sub>",

Proceedings of the Second International Symposium on High Dielectric Constant Materials.

Ontario, Florida, pp. 385-394, October, 2003.

Dedicated To My Father, Mother, Wife and Son

#### ACKNOWLEDGMENT

I would like to first sincerely and gratefully acknowledge the guidance, support and encouragement of my dissertation advisor, Prof. Durgamadhab Misra. Without his supervision this work could not be completed. I would like to express my sincere gratitude to the other dissertation committee members: Dr. Arvind Kumar, Prof. Leonid Tsybeskov, Prof. Marek Sosnowski, Prof. Anthony Fiory and Prof. N. M. Ravindra for their insightful comments during the course of proposal and final defense.

I would like to acknowledge the financial support from National Science Foundation (NSF) grant ECS-0140584.

I would also like to acknowledge the research collaboration with SEMATECH, Austin, Texas.

I am particularly grateful to Dr. Gennadi Bersuker, Dr. Rino Choi, Dr. Chadwin Young, Dr. Dwei Heh, Dr. Byong Hun Lee and Dr. Raj Jammy of SEMATECH for providing me with an opportunity to advance my research work.

My colleagues at NJIT extended their support and friendship throughout my graduate study. Their presence at the lab made the life bearable. Special thanks to Purushotham, Nilufa, Amrita, Reenu and Tias.

Last but not the least; I would like to extend my heart-felt gratitude to my loving wife, Samiya, for putting up with all the stress of being the significant half of a PhD student. I shall always remember the encouragement and support that I received from my wife, father, mother and younger brother. I, however, received the best inspiration from the beautiful smile of my son, Nameek Seenan.

### TABLE OF CONTENTS

| Cl | hapter                                                                   | Page |

|----|--------------------------------------------------------------------------|------|

| 1  | INTRODUCTION, MOTIVATION AND OBJECTIVES                                  | . 1  |

|    | 1.1 Introduction                                                         | . 1  |

|    | 1.2 Motivation                                                           | . 2  |

|    | 1.3 Objectives                                                           | 5    |

|    | 1.4 Scope of Work                                                        | 6    |

|    | 1.5 Dissertation Organization                                            | 6    |

| 2  | LITERATURE REVIEW: CHARGE TRAPPING IN HIGH-K DIELECTRIC                  | 9    |

|    | 2.1 Introduction                                                         | . 9  |

|    | 2.2 ChargeTrapping in Hf-based High-κ Oxides                             | . 10 |

|    | 2.2.1 Fast Transient Trapping                                            | . 11 |

|    | 2.2.2 Slow Transient Trapping                                            | . 17 |

|    | 2.3 Defect Energy Levels and Trapping                                    | 21   |

|    | 2.4 Physical Origins and Electronic Properties of Defects                | . 23 |

|    | 2.4.1 Why do High-κ Oxides Have More Defects than SiO <sub>2</sub> ?     | . 23 |

|    | 2.4.2 Physical Origin of Defects in High-κ Oxides                        | . 24 |

|    | 2.4.3 Calculation of Electronic Properties of O Vacancies/Interstitials. | . 24 |

|    | 2.5 Experimental Evidence of Presence of O Vacancies                     | . 30 |

|    | 2.6 Summary                                                              | . 33 |

| C | hapter                                                                 | Page |

|---|------------------------------------------------------------------------|------|

| 3 | DEVICE FABRICATION AND ELECTRICAL CHARACTERIZATION                     | 34   |

|   | 3.1 Introduction                                                       | 34   |

|   | 3.2 TiN/HfSi <sub>x</sub> O <sub>y</sub> based MOS Devices Fabrication | 34   |

|   | 3.2.1 TiN/HfO <sub>2</sub> based MOS Devices Fabrication               | 34   |

|   | 3.2.2 TiN/Hf-Silicate Based MOS Devices Fabrication                    | 35   |

|   | 3.2.3 TiN/HfO2-Based MOS Devices Fabrication                           | 36   |

|   | 3.3 Electrical Characterization                                        | 38   |

|   | 3.3.1 High Frequency and Low Frequency C-V Measurements                | 38   |

|   | 3.3.2 Conductance Measurement                                          | 43   |

|   | 3.3.3 I-V Measurements                                                 | 47   |

|   | 3.3.4 I <sub>d</sub> -V <sub>g</sub> Measurements                      | 51   |

|   | 3.3.5 MOSFET Subthreshold Current Method                               | 52   |

|   | 3.3.6 Stress Measurement                                               | 54   |

|   | 3.3.7 Low Temperature Measurements                                     | 58   |

|   | 3.3.8 Time Zero Dielectric Breakdown (TZBD)                            | 59   |

|   | 3.3.9 Time dependent Dielectric Breakdown                              | 59   |

|   | 3.4 Measurement Automation                                             | 60   |

|   | 3.4.1 I-V Measurements Automation                                      | 61   |

|   | 3.4.2 C-V and G-V Measurements Automation                              | 64   |

|   | 3.4.3 CVS Measurements Automation                                      | 66   |

| C | hapt | er er                                                                                           | Page |

|---|------|-------------------------------------------------------------------------------------------------|------|

|   |      | 3.4.4 I <sub>d</sub> -V <sub>g</sub> Measurement Automation                                     | 68   |

|   |      | 3.4.5 SHC Measurements Automation                                                               | 70   |

|   |      | 3.4.6 Transistor Stress Measurement Automation                                                  | 72   |

|   | 3.5  | Summary                                                                                         | 74   |

| 4 |      | PERIMENTAL OBSERVATION OF DEFECT LEVELS IN I/HfSi <sub>x</sub> O <sub>y</sub> BASED GATE STACKS | 75   |

|   | 4.1  | Introduction                                                                                    | 75   |

|   | 4.2  | Characteristics of Detrapping from Deep Defects                                                 | 76   |

|   | 4.3  | Defect Levels from Low Temperature Measurements                                                 | 77   |

|   |      | 4.3.1 Low Temperature C-V and G-V for pMOS-C                                                    | 78   |

|   |      | 4.3.2 Low Temperature C-V and G-V for nMOS-C                                                    | 82   |

|   |      | 4.3.3 Low Temperature C-V at Different Frequencies                                              | 83   |

|   |      | 4.3.4 Defect Levels in the Context of MOS Energy Band Diagram                                   | 84   |

|   | 4.4  | Defect Levels from Leakage Measurements                                                         | 86   |

|   |      | 4.4.1 P-F Plots under Gate Injection                                                            | 86   |

|   |      | 4.4.2 P-F Plots under Substrate Injection                                                       | 89   |

|   |      | 4.4.3 Defect Levels in the Context of MOS Energy Band Diagram                                   | 92   |

|   | 4.5  | Defect Levels from Time and Temperature Dependent Detrapping                                    | 93   |

|   | 4.6  | Defect Levels in Context of MOS Energy Band Diagram                                             | 96   |

|   | 4.7  | Summary                                                                                         | 97   |

| Cl | napter                                                                                          | Page |

|----|-------------------------------------------------------------------------------------------------|------|

| 5  | TRAPPING CHARACTERISTICS OF TiN/HfSi <sub>x</sub> O <sub>y</sub> BASED GATE STACKS UNDER STRESS | 98   |

|    | 5.1 Introduction                                                                                | 98   |

|    | 5.2 Understanding Defect Levels from De-trapping Characteristics                                | 104  |

|    | 5.3 CVS with Negative Gate Bias (Gate Injection)                                                | 100  |

|    | 5.3.1 CVS at Room Temperature                                                                   | 100  |

|    | 5.3.2 CVS at Elevated Temperature                                                               | 103  |

|    | 5.3.3. Physical Model for Gate Injection                                                        | 104  |

|    | 5.4 CVS with Positive Gate Bias (Substrate Injection)                                           | 106  |

|    | 5.5 Substrate Hot Electron (SHE) Stress                                                         | 110  |

|    | 5.6 Substrate Hot Hole (SHH) Stress                                                             | 121  |

|    | 5.7 Summary                                                                                     | 125  |

| 6  | NEGATIVE BIAS TEMPERATURE INSTABILITY (NBTI)                                                    | 126  |

|    | 6.1 Introduction                                                                                | 126  |

|    | 6.2 Stress at Room Temperature                                                                  | 127  |

|    | 6.3 Stress at Elevated Temperature                                                              | 132  |

|    | 6.4 Application of Reaction-Diffusion Model                                                     | 138  |

|    | 6.5 Summary                                                                                     | 142  |

| Cl | hapter                                                                                      | Page |

|----|---------------------------------------------------------------------------------------------|------|

| 7  | BREAKDOWN CHARACTERISTICS OF METAL GATE/Hf-BASED GATE STACKS                                | 143  |

|    | 7.1 Introduction                                                                            | 143  |

|    | 7.2 Calculation of $E_{BD}^{IL}$ and $E_{BD}^{H-K}$                                         | 144  |

|    | 7.3 E <sub>BD</sub> of SiO <sub>2</sub> based MOS and HfO <sub>2</sub> based MIM Structures | 147  |

|    | 7.4 TZBD Characteristics                                                                    | 149  |

|    | 7.4.1 Lot 1                                                                                 | 149  |

|    | 7.4.2 Lot 2                                                                                 | 154  |

|    | 7.4.3 Lot 3                                                                                 | 158  |

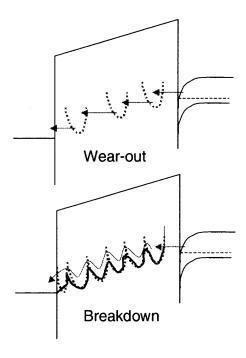

|    | 7.5 Wear-out Regimes during TDDB                                                            | 160  |

|    | 7.6 Effects of Charge Trapping on Degradation                                               | 163  |

|    | 7.7 Effect of IL Degradation on TDDB                                                        | 165  |

|    | 7.8 Breakdown Mechanisms during TDDB                                                        | 168  |

|    | 7.9 Effect of IL Quality on T <sub>BD</sub> and Q <sub>BD</sub>                             | 181  |

|    | 7.10 Temperature Dependence of T <sub>BD</sub>                                              | 188  |

|    | 7.11 Summary                                                                                | 192  |

| 8  | CONCLUSIONS                                                                                 | 194  |

|    | 8.1 Impact and Limitations                                                                  | 198  |

|    | 8.2 Future Work.                                                                            | 199  |

|    | REFERENCES                                                                                  | 200  |

### LIST OF TABLES

| Table |                                                                                                                | Page |

|-------|----------------------------------------------------------------------------------------------------------------|------|

| 2.1   | Calculated Defect Levels within HfO <sub>2</sub> Band-gap Responsible for Transient Trapping                   | 30   |

| 2.2   | Calculated Formation Energies of Defects Responsible for Transient Trapping                                    | 30   |

| 3.1   | Description of Different Splits from Various Lots Tested in the Work                                           | 37   |

| 7.1   | Physical Thickness and Effective Oxide Thickness (EOT) for Different Interfacial Layers (IL) Growth Conditions |      |

| 7.2   | Corrected $\Delta H_0^*$ for Different IL Conditions                                                           | 191  |

### LIST OF FIGURES

| Figure |                                                                                                                                                                                                                                                           | Page |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

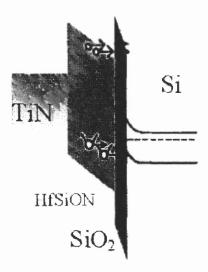

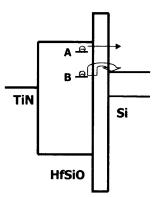

| 1.1    | An n-channel MOS structure of high-κ gate stack showing bulk high-κ and interfacial layer.                                                                                                                                                                | 2    |

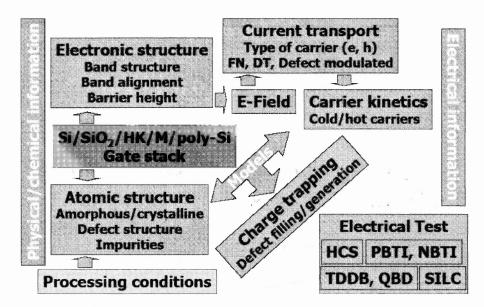

| 1.2    | Different components of the charge trapping induced degradation studies of the high-κ gate stacks                                                                                                                                                         | 4    |

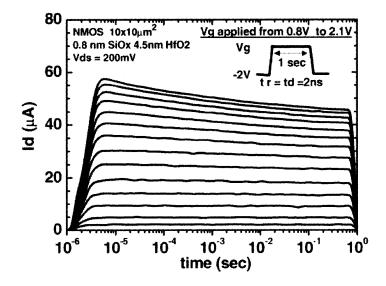

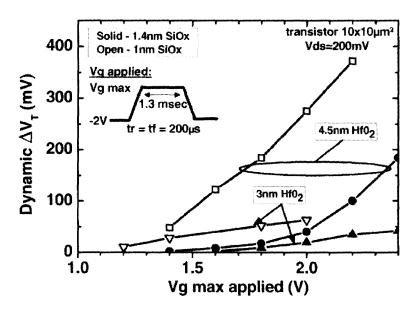

| 2.1    | Transient behavior of drain current (I <sub>d</sub> ) under multiple-pulsed technique                                                                                                                                                                     | 12   |

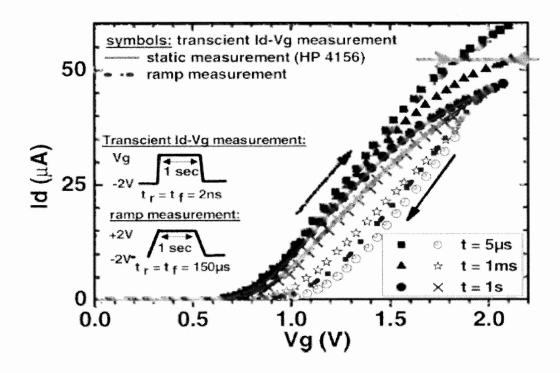

| 2.2    | Hysteresis in $I_d$ - $V_g$ characteristics under transient, static and ramp measurement techniques                                                                                                                                                       | 13   |

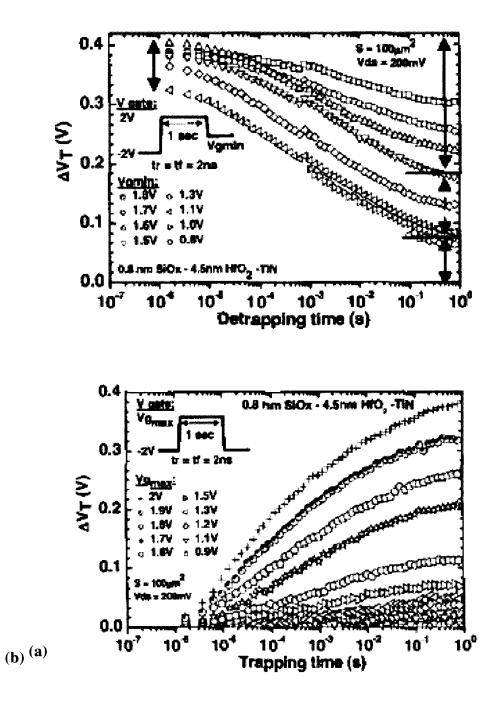

| 2.3    | (a) Fast transient trapping induced positive $\Delta V_T$ shift for different gate bias conditions. (b) Detrapping from shallow electron trap level induced fast reduction in $\Delta V_T$ at different reduced post-stress gate bias conditions          | 14   |

| 2.4    | Ramp measurement technique induced $\Delta V_T$ with respect to different gate biases for different HfO <sub>2</sub> /SiO <sub>x</sub> -based gate stack architectures                                                                                    | 15   |

| 2.5    | Physical models for fast transient trapping with defect levels located at (a) $SiO_2/HfO_2$ interface and (b) in the bulk high- $\kappa$ oxide                                                                                                            | 16   |

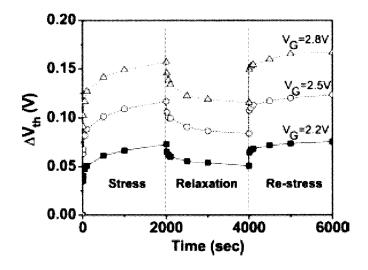

| 2.6    | $\Delta V_T$ w.r.t. time under stress/relaxation cycle                                                                                                                                                                                                    | 17   |

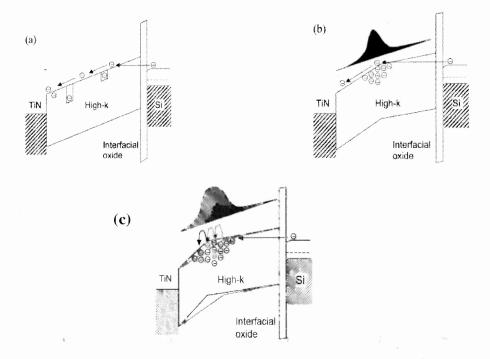

| 2.7    | MOS band diagram during stress: (a) initial electron trapping at conduction edge shallow trap levels. (b) Internal electric field distortion due to accumulation of localized trapping. (c) Charge redistribution to deeper levels induce stable trapping | 18   |

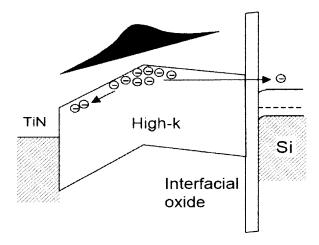

| 2.8    | Relaxation induced slow release and redistribution of trapped charges                                                                                                                                                                                     | 19   |

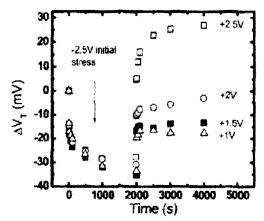

| 2.9    | $\Delta V_T$ vs. time during stress with negative gate bias followed by positive bias.                                                                                                                                                                    | 20   |

| 2.10   | Physical model of deep defect induced slow transient trapping during gate injection                                                                                                                                                                       | 21   |

| Figure |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Page |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

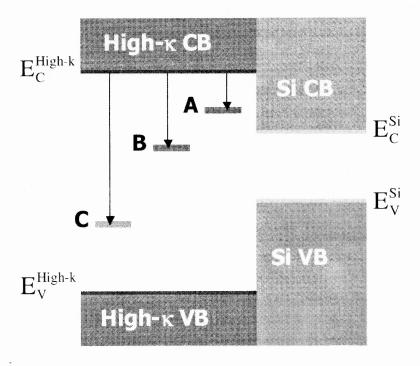

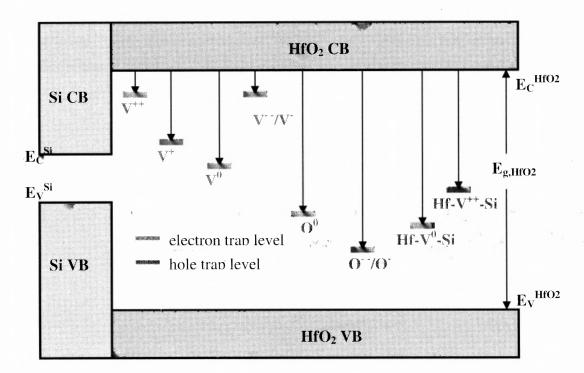

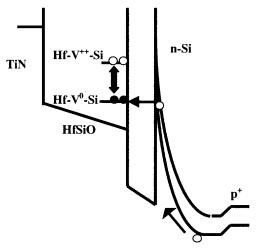

| 2.11   | Defect levels within bulk high-κ in the context of MOS band diagram                                                                                                                                                                                                                                                                                                                                                                                                                        | 22   |

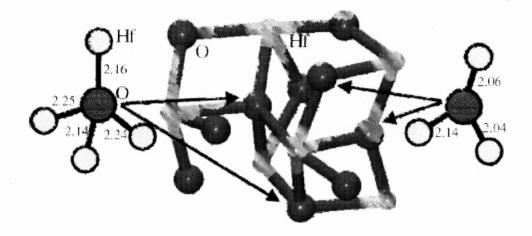

| 2.12   | 12-atom monoclinic hafnia cell having 3- and 4-fold coordinated O ions. Distances are in Armstrong                                                                                                                                                                                                                                                                                                                                                                                         | 26   |

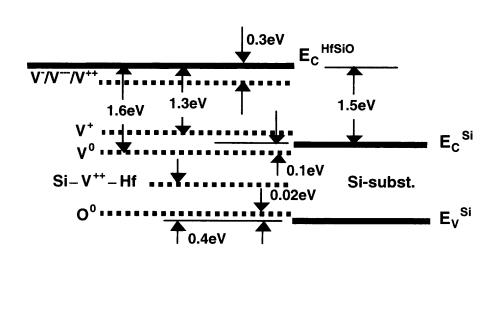

| 2.13   | Calculated defect levels in the context of MOS diagram                                                                                                                                                                                                                                                                                                                                                                                                                                     | 28   |

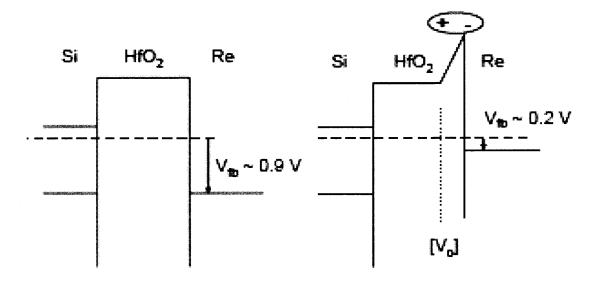

| 2.14   | MOS band diagrams showing flatband voltage $(V_{FB})$ shift due to dipole formation between positively charged O vacancy and metal gate.                                                                                                                                                                                                                                                                                                                                                   | 31   |

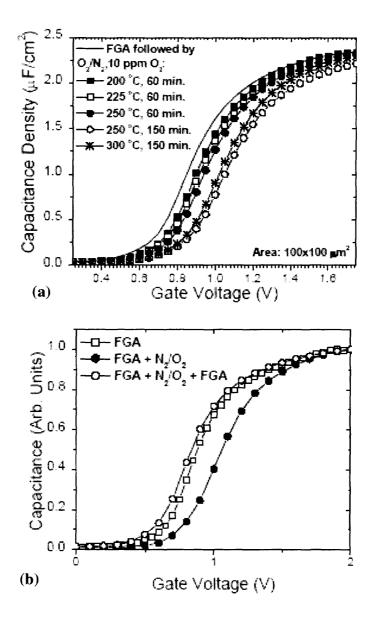

| 2.15   | (a) Shift in C-V for $N_2/O_2$ anneal at different low temperatures and time conditions. (b) Shift in C-V under oxidizing and reducing conditions.                                                                                                                                                                                                                                                                                                                                         | 32   |

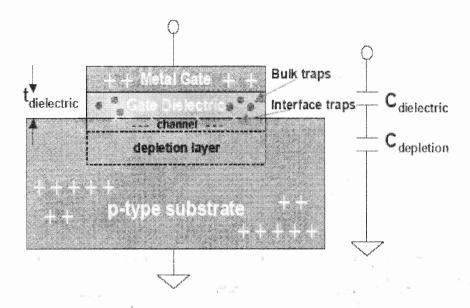

| 3.1    | A metal/insulator/semiconductor (p-type) (MIS) structure is shown that is used extensively to characterize dielectric films. Dielectric/semiconductor interface traps and bulk traps are shown. For positive gate bias, semiconductor and metal gate act as cathode and anode, respectively, whereas for negative gate bias, the opposite holds. The equivalent circuit of the series capacitance of dielectric and depletion capacitances is also provided                                | 39   |

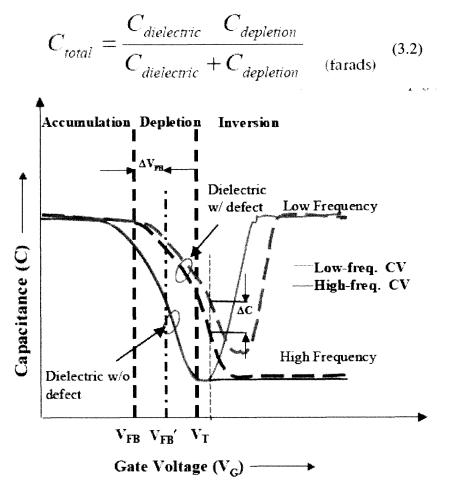

| 3.2    | High-frequency (hf) and low-frequency (lf) capacitance-voltage (C-V) characteristics of MIS structure for dielectric films with and without (ideal) defects are shown. Flatband voltage shift of hf C-V, $\Delta V_{FB} = (V_{FB}' - V_{FB}) > 0$ indicates negative charge trapping. For a film with defects, stretch-out of hf C-V, and offset in capacitance, $\Delta C$ , in between hf and lf C-V indicate the presence of interface traps.                                           | 41   |

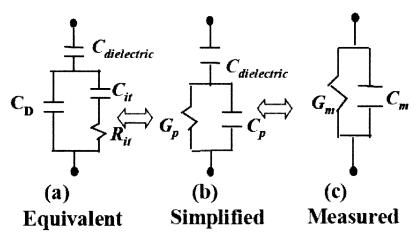

| 3.3    | (a) Equivalent circuit for MIS structures with interface traps. $R_{it}$ and $C_{it}$ represent interface traps induced energy loss and charge storage respectively. (b) Simplified circuit, derived from (a), for analysis. Equivalent conductance, $G_p$ , is computed from measured data as a function of both test (ac) signal frequency and gate bias (dc). (c) Circuit representing parallel capacitance $(C_m)$ and conductance $(G_m)$ , which is measured across two-terminal MIS | 44   |

| Figure |                                                                                                                                              | Page |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------|------|

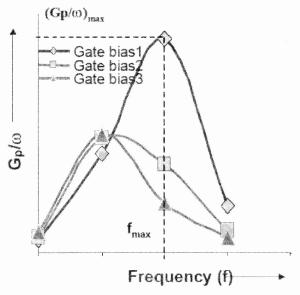

| 3.4    | $Gp/\omega$ vs. $log(f)$ plots for different gate biases in the depletion regime. $D_{it}$ is computed from the highest peak of the plots    | 46   |

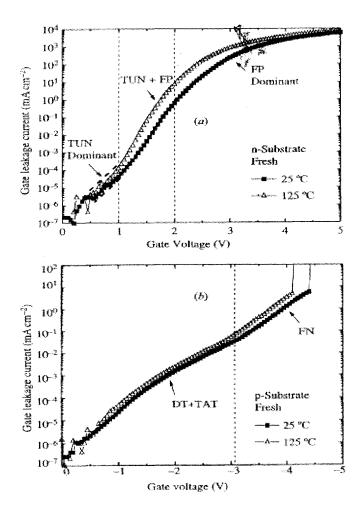

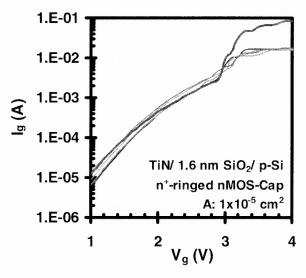

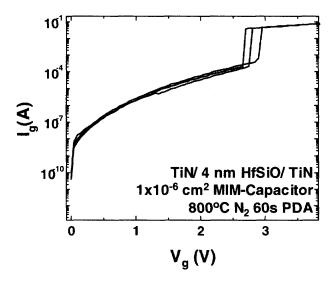

| 3.5    | I-V characteristics for TiN/HfO <sub>2</sub> (4 nm)/SiO <sub>2</sub> (1 nm) gate stack under (a) substrate and (b) gate injection conditions | 48   |

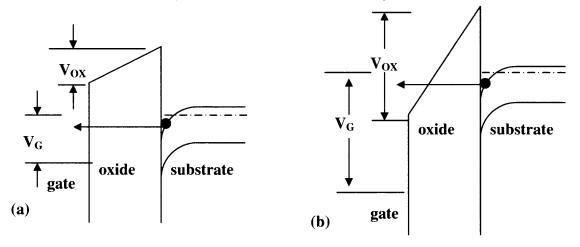

| 3.6    | Band diagram for (a) direct tunneling and (b) F-N tunneling under positive gate bias                                                         | 49   |

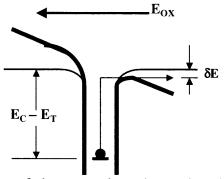

| 3.7    | P-F emission of the trapped carrier under electric field and elevated temperature conditions                                                 | 50   |

| 3.8    | $I_d$ - $V_g$ measurement set-up for an n-channel MOSFET                                                                                     | 51   |

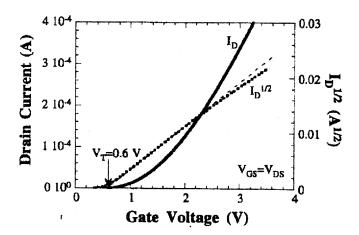

| 3.9    | $V_T$ determination from $I_d^{\ 0.5}$ - $V_g$ plot                                                                                          | 52   |

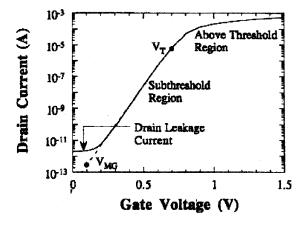

| 3.10   | Subthreshold swing determination from subthreshold slope                                                                                     | 53   |

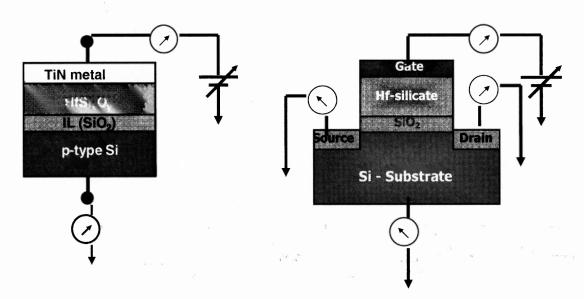

| 3.11   | (a) MOS-Capacitor and (b) MOSFET set-up for constant voltage stress                                                                          | 54   |

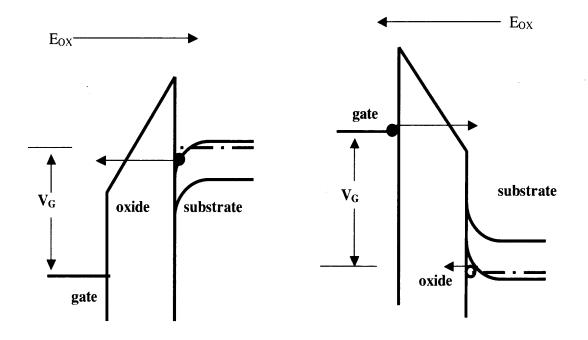

| 3.12   | Band diagram for (a) substrate and (b) gate injection during CVS with positive and negative gate bias respectively                           | 55   |

| 3.13   | Gate current vs. time during CVS                                                                                                             | 56   |

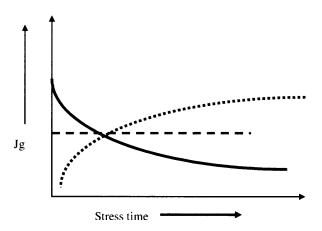

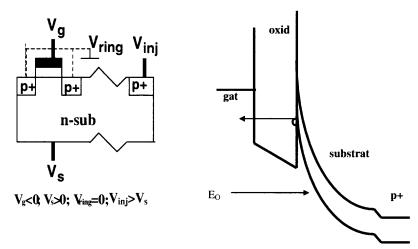

| 3.14   | Arrangements for (a) SHE stress on n+-ringed nMOS-C and (b) band diagram under SHE stress                                                    | 57   |

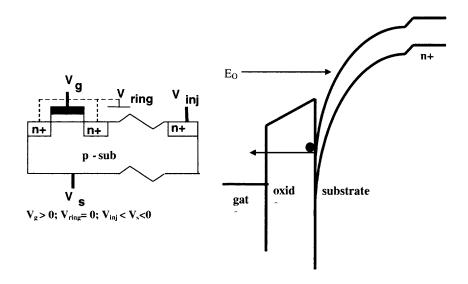

| 3.15   | Arrangements for SHH stress and (b) band diagram under SHH stress                                                                            | 58   |

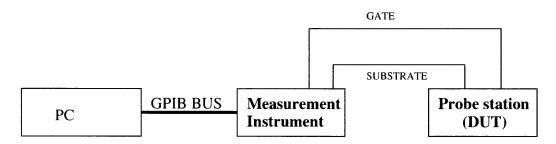

| 3.16   | Basic arrangement for electrical measurement automation of a simple two-terminal device, e.g. MOS-Capacitor                                  | 60   |

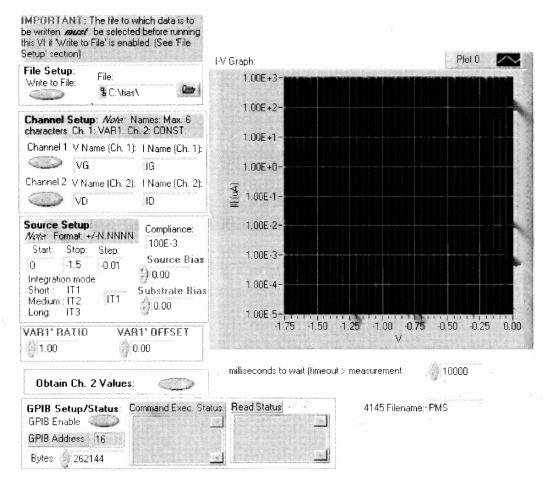

| 3.17   | View of the man machine interface (MMI) of I-V measurement automation system                                                                 | 62   |

| 3.18   | Flow chart of I-V automation algorithm                                                                                                       | 63   |

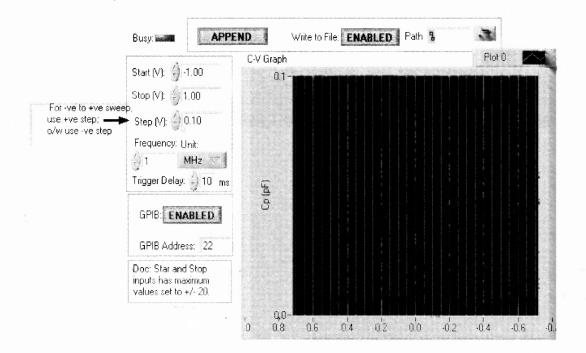

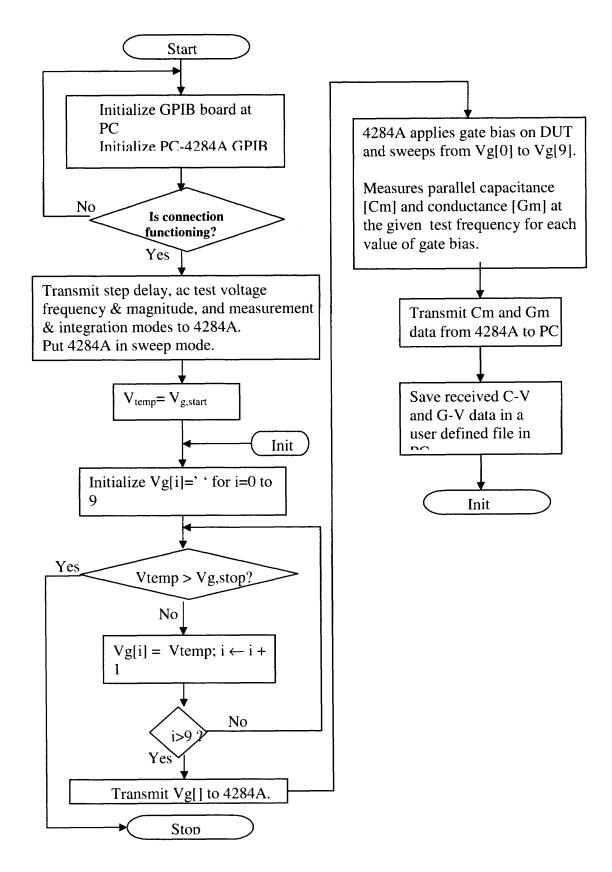

| 3.19   | View of the man machine interface (MMI) of C-V and G-V measurement automation system.                                                        | 64   |

| Figure |                                                                                                                                                                                                                      | Page |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 3.20   | Flow chart of C-V/G-V automation algorithm                                                                                                                                                                           | 65   |

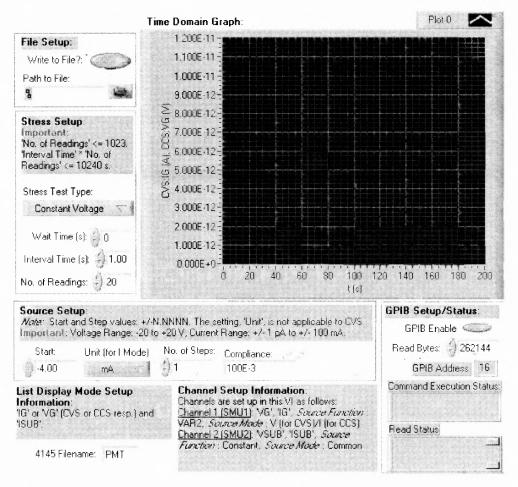

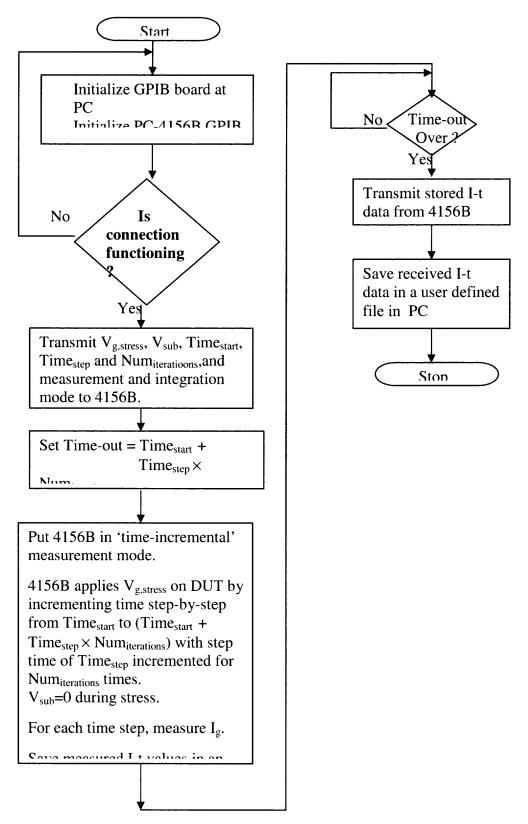

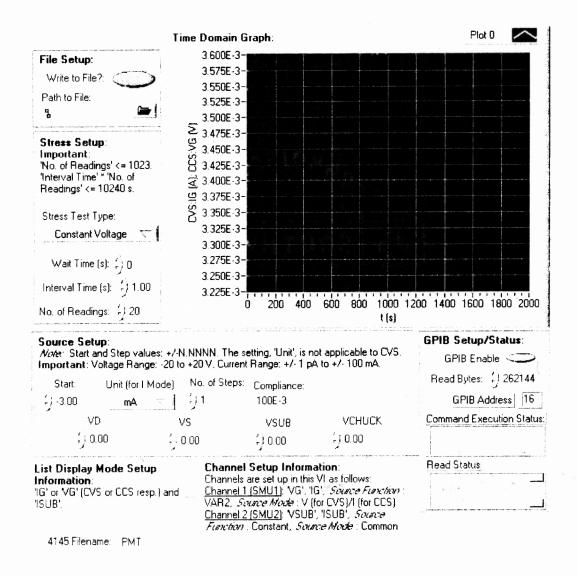

| 3.21   | View of the MMI of CVS automation system                                                                                                                                                                             | 66   |

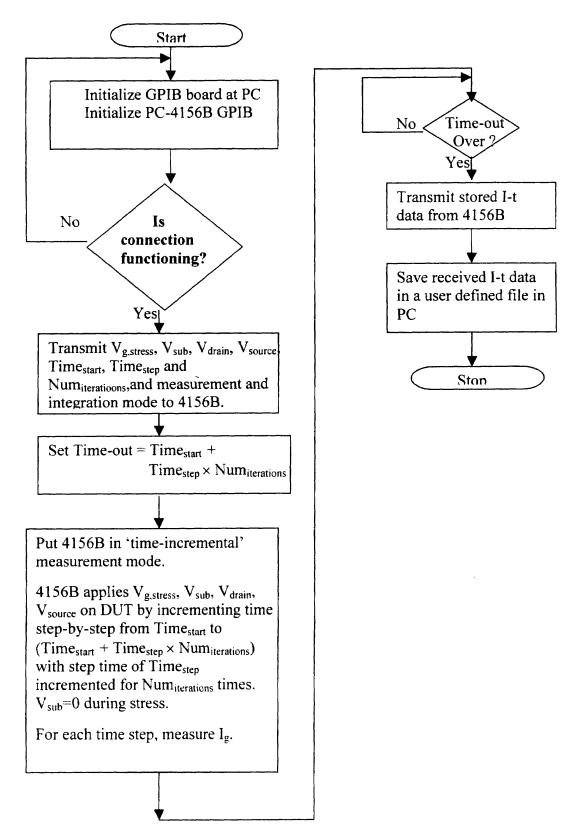

| 3.22   | Flow chart of CVS automation algorithm                                                                                                                                                                               | 67   |

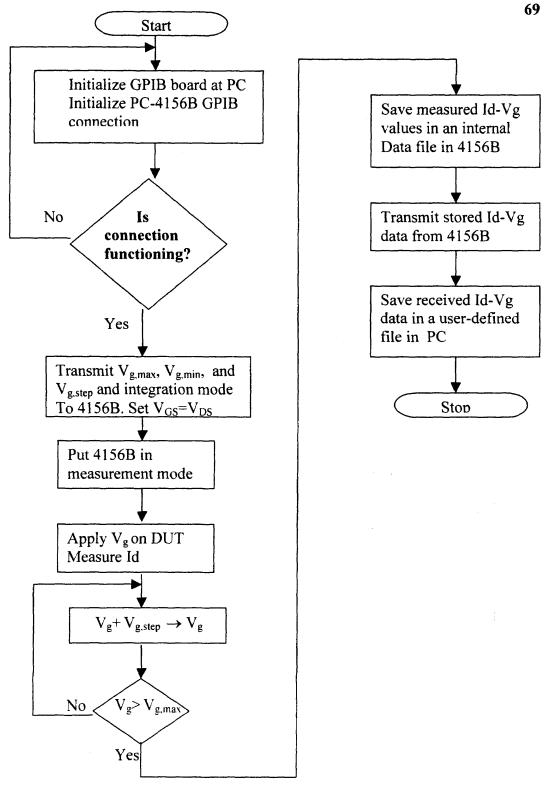

| 3.23   | View of the MMI of $I_d$ - $V_g$ measurement automation system                                                                                                                                                       | 68   |

| 3.24   | Flow chart of Id-Vg automation algorithm                                                                                                                                                                             | 69   |

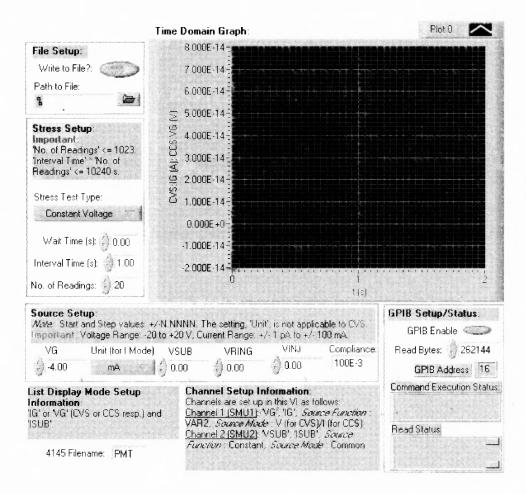

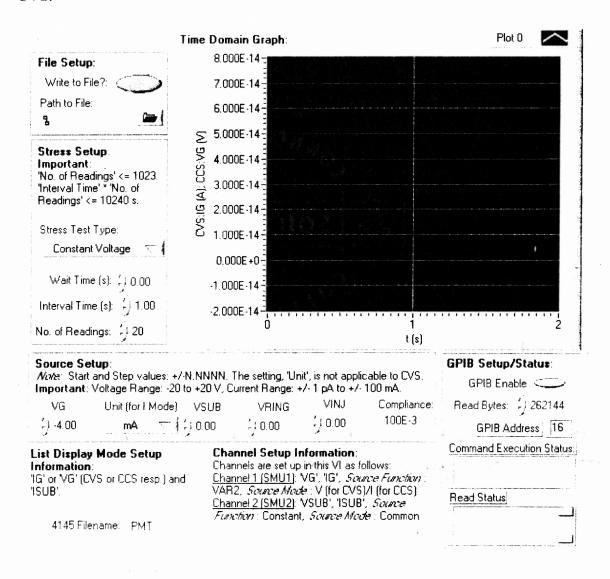

| 3.25   | View of the MMI of SHC measurement automation system                                                                                                                                                                 | 70   |

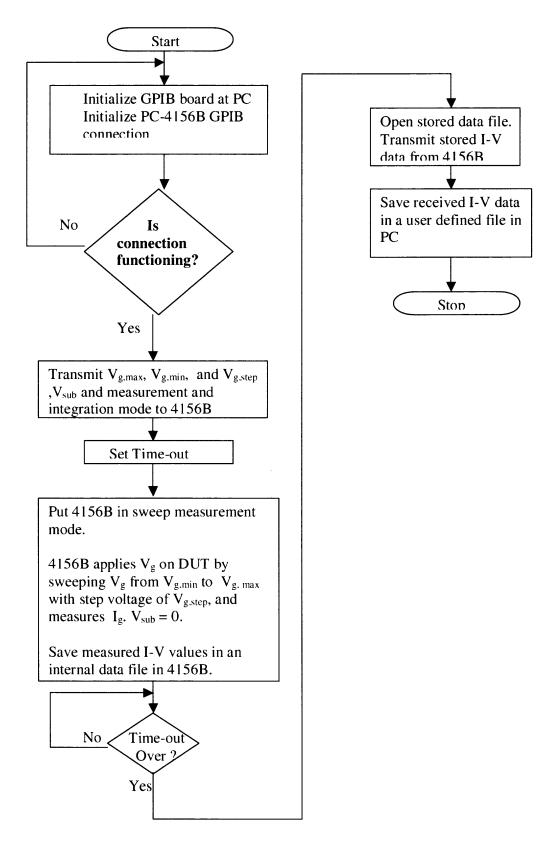

| 3.26   | Flow chart of SHC automation algorithm                                                                                                                                                                               | 71   |

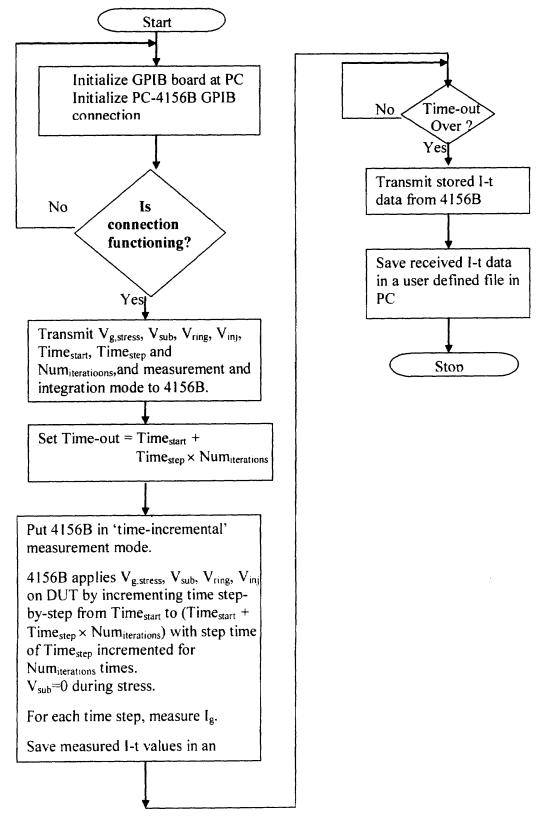

| 3.27   | View of the MMI of CVS measurement automation system                                                                                                                                                                 | 72   |

| 3.28   | Flow chart of CVS automation algorithm                                                                                                                                                                               | 73   |

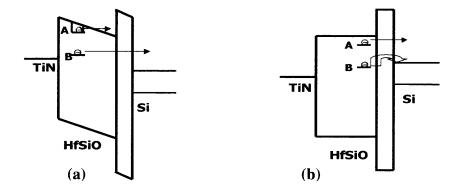

| 4.1    | Detrapping characteristics from shallow (A) and deep (B) traps under idealized 'no bias' condition for TiN/HfSi <sub>x</sub> O <sub>y</sub> based gate stacks                                                        | 77   |

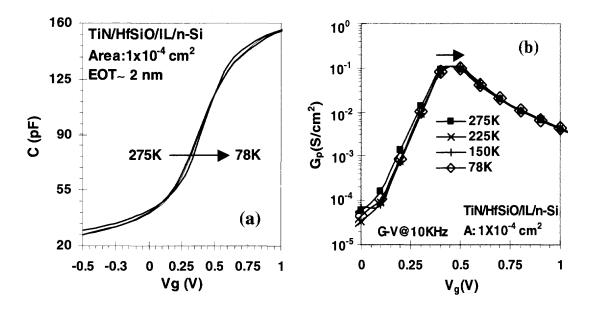

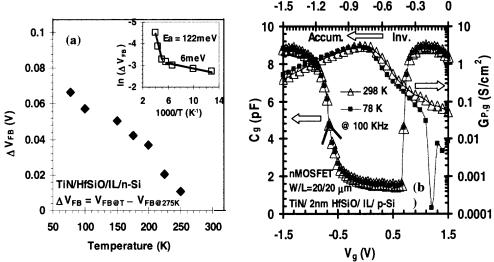

| 4.2    | (a) 1 MHz C-V plots, and (b) 10 KHz G-V plots in 275 K-78 K temperature range for pMOS-C                                                                                                                             | 79   |

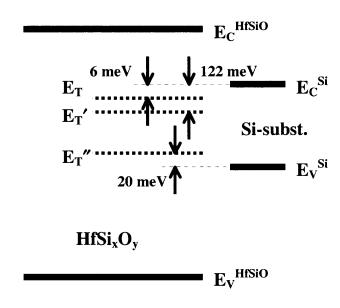

| 4.3    | (a) Flatband voltage shift ( $\Delta V_{FB}$ ) vs. temperature for pMOS-C. (Inset) Arrhenius plot of $\Delta V_{FB}$ . (b) 100 KHz C-V and G-V for 2 nm Hf-silicate/IL at 298 K and 78 K for nMOSFET.                | 80   |

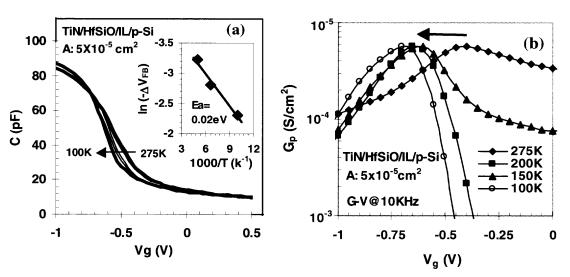

| 4.4    | <ul> <li>(a) 1MHz C-V in 100-275K temperature range for nMOS-C.</li> <li>(Inset) Arrhenius plot of -ΔV<sub>FB</sub> shows a single bulk defect level.</li> <li>(b) 10KHz G-V in 100-275K range for nMOS-C</li> </ul> | 81   |

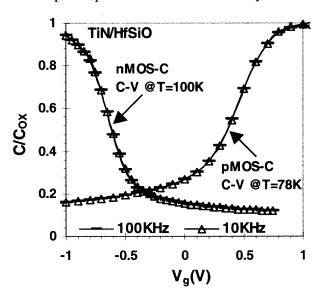

| 4.5    | 100 KHz and 10 KHz normalized C-V plots for nMOS-C at low temperature of 100K and for p-MOS-C at 78K                                                                                                                 | 83   |

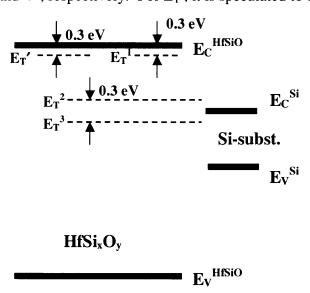

| 4.6    | Deep bulk electron ( $E_T$ and $E_T$ ) and hole ( $E_T$ ") trap levels in the context of MOS band diagram                                                                                                            | 84   |

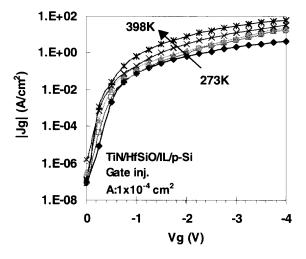

| 4.7    | I-V measurements in 273K-398K temperature range                                                                                                                                                                      | 87   |

| Figure |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Page |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

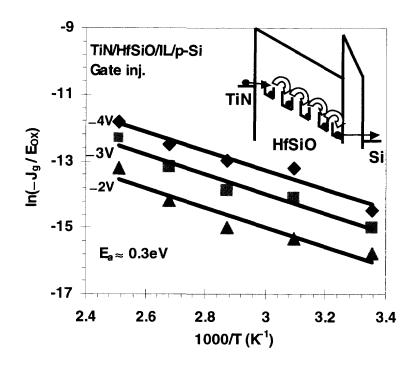

| 4.8    | Arrehnius plot of $ln(-J_g/E_{OX})$ for nMOS-C for different negative gate biases. (Inset) Transport through deep localized states under gate injection.                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 89   |

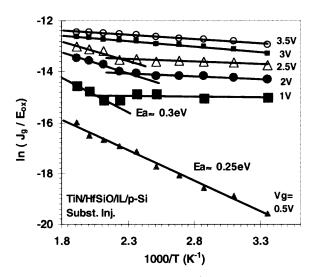

| 4.9    | Arrehnius plot of $ln(-J_g/E_{OX})$ for $n^+$ -ringed nMOS-C for different positive gate biases (substrate injection). $N^+$ -ring is grounded                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 90   |

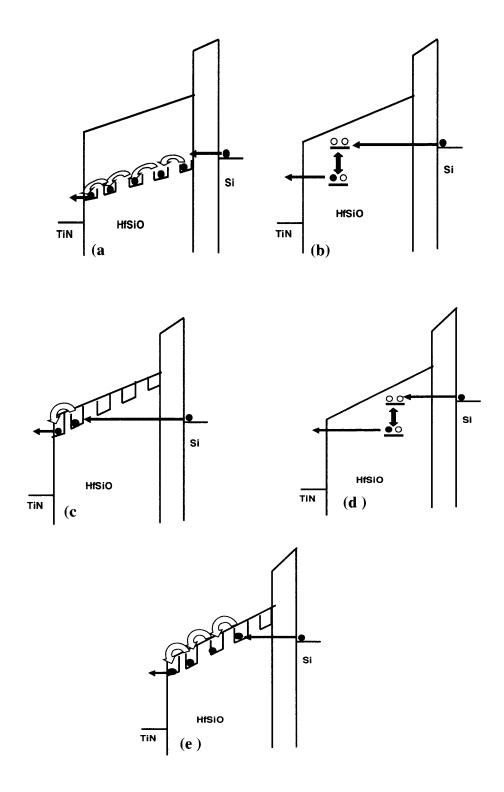

| 4.10   | Transport mechanisms during substrate injection TiN/HfSi $_x$ O $_y$ based gate stacks: (a) low gate bias, V $_g$ (~0.5 V); (b) moderate V $_g$ (~1 V) and temperature,T < 200 K; (c) moderate V $_g$ (~1 V) and T > 200 K; (d) high V $_g$ (~2 V) and T < 175 K and (e) high V $_g$ (~2 V) and T >175 K                                                                                                                                                                                                                                                                                                      | 91   |

| 4.11   | Defect levels in the context of MOS band diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 93   |

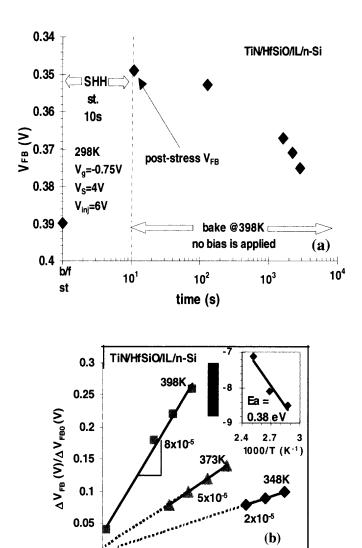

| 4.12   | (a) $V_{FB}$ during 10s of SHH stress followed by bake at 398K under 'no bias' condition. Bake is periodically interrupted to measure $V_{FB}$ at room temperature. (b) $\Delta V_{FB} = V_{FB}$ @bake time – post-stress $V_{FB}$ . $\Delta V_{FB}$ is normalized w.r.t. initial increase in $V_{FB}$ during stress ( $\Delta V_{FB0}$ ) and $\Delta V_{FB}/\Delta V_{FB0}$ is plotted for different bake temperatures. Slopes are calculated from normalized $\Delta V_{FB}$ vs. de-trapping time curves and are shown in the Figure. (Inset) Arrhenius plot of the slopes shows a single bulk defect level | 94   |

| 4.13   | Defect levels in the context of MOS band structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 96   |

| 5.1    | Detrapping characteristics from shallow (A) and deep (B) traps under (a) idealized 'non-zero bias' and (b) 'no bias' conditions for TiN/HfSi <sub>x</sub> O <sub>y</sub> based gate stacks                                                                                                                                                                                                                                                                                                                                                                                                                    | 100  |

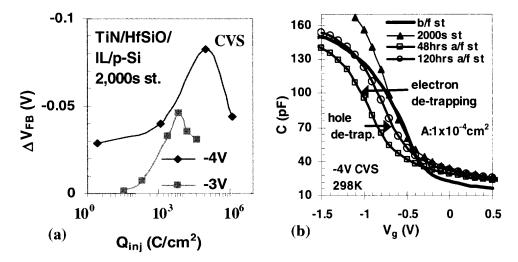

| 5.2    | (a) $\Delta V_{FB}$ vs. $Q_{inj}$ for $V_g = -4V$ and $-3V$ under CVS applied on nMOS-C for 2,000s. (b) Before stress, post-stress and post-relaxation C-V under CVS at $V_g = -4V$                                                                                                                                                                                                                                                                                                                                                                                                                           | 101  |

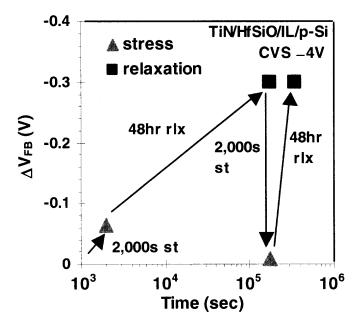

| 5.3    | Post-stress (2,000s st) and post-relaxation (48 hours of relaxation) $V_{FB}$ for two successive stress/relaxation cycles applied on nMOS-C.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 102  |

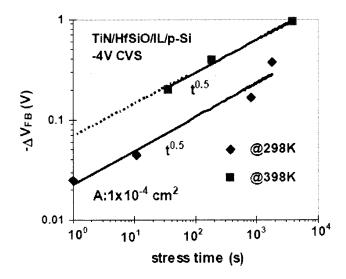

| 5.4    | (a) $\Delta V_{FB}$ vs. $Q_{inj}$ under CVS at $125^{0}$ C for different gate biases for nMOS-C. (b) Normalized change in $D_{it}$ vs. $Q_{inj}$ for different gate bias at room at elevated temperatures                                                                                                                                                                                                                                                                                                                                                                                                     | 103  |

| Figure |                                                                                                                                                                                                                                                                      | Page |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

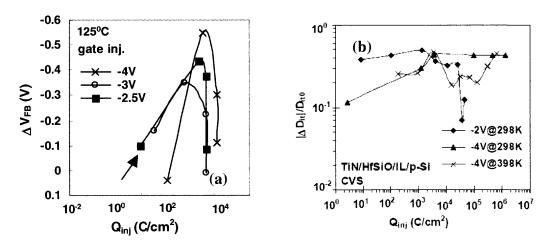

| 5.5    | $\Delta V_{FB}$ vs. stress time in log-log scale                                                                                                                                                                                                                     | 104  |

| 5.6    | Physical model of charge trapping under gate injection. Speculated physical origins of the observed defect levels are also shown                                                                                                                                     | 106  |

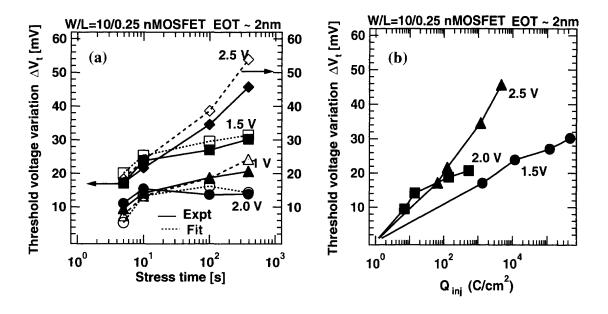

| 5.7    | (a) $\Delta V_T$ vs. stress time and (b) $\Delta V_T$ vs. $Q_{inj}$ for different gate biases under gate injection.                                                                                                                                                  | 107  |

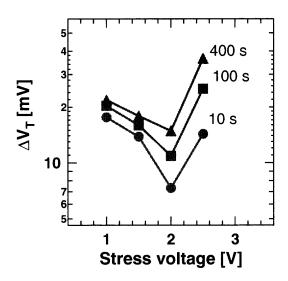

| 5.8    | $\Delta V_T$ vs. stress voltage for different stress times under substrate injection                                                                                                                                                                                 | 108  |

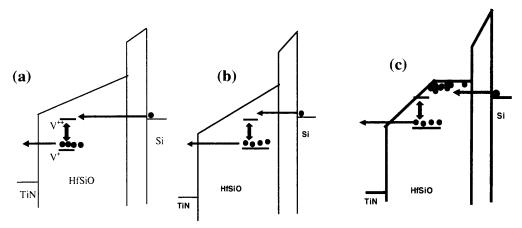

| 5.9    | MOS band diagrams under substrate injection for (a) $V_g \sim 1 \ V$ , (b) $V_g \sim 2 \ V$ and (c) $V_g \sim 2.5 \ V$                                                                                                                                               |      |

| 5.10   | I-V characteristics under hot and cold carrier injection conditions                                                                                                                                                                                                  | 109  |

| 5.11   | Pre- and post-stress, and post-relaxation 1MHz C-V and 10KHz G-V plots for SHE stress                                                                                                                                                                                | 110  |

| 5.12   | Time-dependent electron de-trapping characteristics under different post-stress reverse bias conditions. (b) $\Delta V_{FB}$ during SHE stress/ detrap cycles. SHE stress was applied with $V_g/V_s/V_{inj} = 0.75/-10/-12$ V. During detrapping cycle, $V_s = -1$ V | 111  |

| 5.13   | $\Delta V_{FB}$ vs. stress time in log-log scale for different substrate biases                                                                                                                                                                                      | 112  |

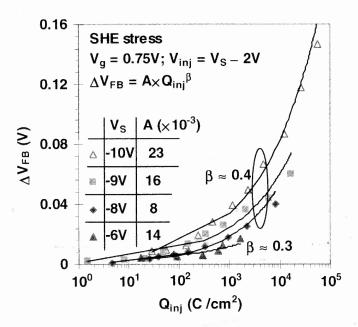

| 5.14   | $\Delta V_{FB}$ vs. $Q_{inj}$ under SHE stress at different $V_s$ ( $V_{inj} = V_s - 2V$ ) bias conditions. (Inset) Table showing the value of the coefficient A for different $V_s$ .                                                                               | 113  |

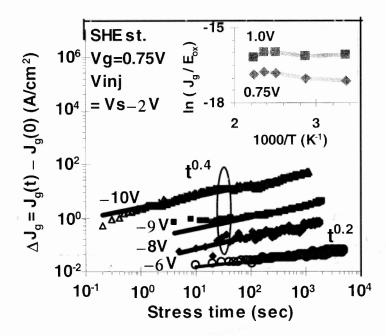

| 5.15   | $\Delta J_g(t)$ vs. stress time in log-log scale under SHE stress at different $V_s$ ( $V_{inj} = V_s - 2V$ ) bias conditions. (Inset) Arrehnius plot of $\ln (J_g/E_{ox})$ for different $V_g$                                                                      | 114  |

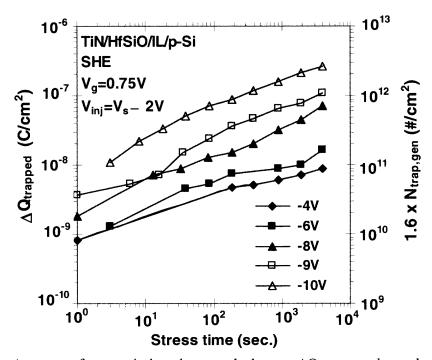

| 5.16   | Amount of stress induced trapped charge, $\Delta Q_{trapped}$ and number of stress induced traps, $N_{trap,gen}$ as a function os stress time for different $V_s$ conditions under SHE stress                                                                        | 115  |

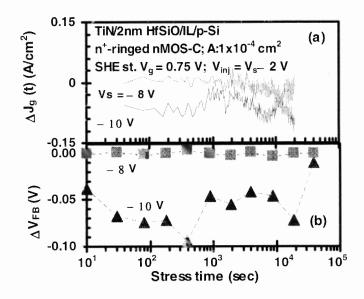

| 5.17   | For 2 nm Hf-silicate/IL, (a) $\Delta V_{FB}$ and (b) $\Delta J_g(t)$ vs. stress time under SHE stress with $V_s = -8$ and $-10$ V conditions                                                                                                                         | 117  |

| Figure |                                                                                                                                                                                                           | Page |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 5.18   | Band diagram of the MOS structure showing the negative-U behavior of the stress induced charged O vacancy defects during SHE stress.                                                                      | 119  |

| 5.19   | I-V characteristics under hot and cold carrier injection conditions                                                                                                                                       | 121  |

| 5.20   | $\Delta V_{FB}$ vs. $Q_{inj}$ under SHH injection, applied on p <sup>+</sup> -ringed pMOS-C for $V_s$ = -4V and -3V. (Inset) $\Delta V_{FB}$ follows t <sup>n</sup> power law dependence.                 | 122  |

| 5.21   | Time-dependent electron de-trapping characteristics under different post-stress reverse bias conditions                                                                                                   | 123  |

| 5.22   | Physical model of trapping at the stress-induced defect under SHH stress with high substrate bias                                                                                                         | 125  |

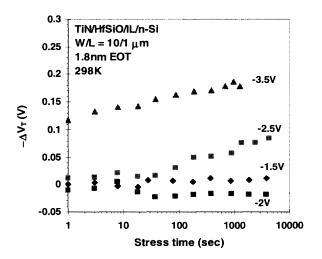

| 6.1    | $V_T$ vs. stress time for different $V_g$ during CVS at room temperature                                                                                                                                  | 128  |

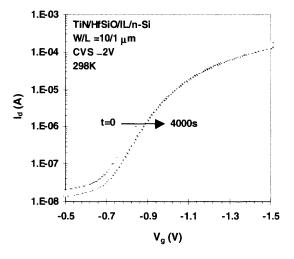

| 6.2    | $I_d$ - $V_g$ plots for CVS with $V_g = -2$ V at RT                                                                                                                                                       | 128  |

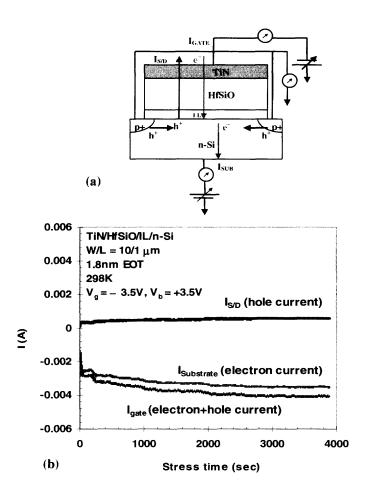

| 6.3    | (a) Carrier separation technique as CVS is applied with negative gate and nonzero substrate bias. (b) Current vs. stress time showing electron and hole injection during CVS with nonzero substrate bias. | 129  |

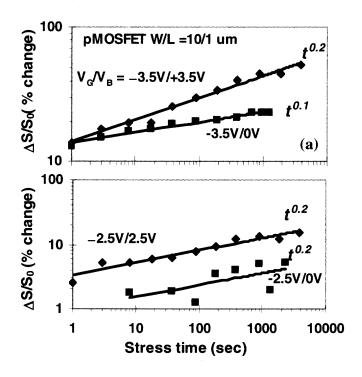

| 6.4    | (a) $\Delta S/S_0$ and (b) $\Delta V_T$ for both zero and non-zero substrate bias conditions during CVS at RT                                                                                             | 130  |

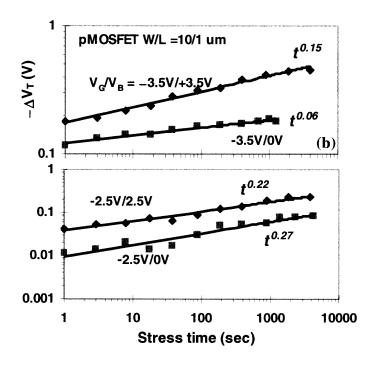

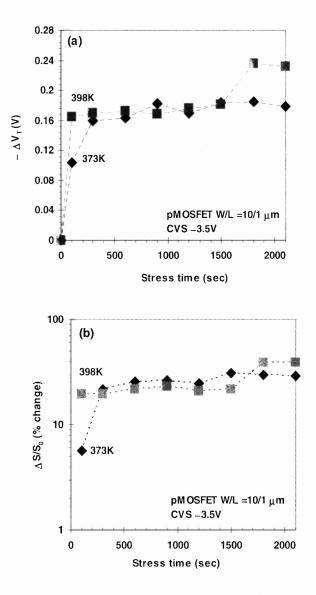

| 6.5    | $\Delta V_T$ vs. stress time for different $V_g$ at 398K (125°C) applied on pMOSFETS                                                                                                                      | 133  |

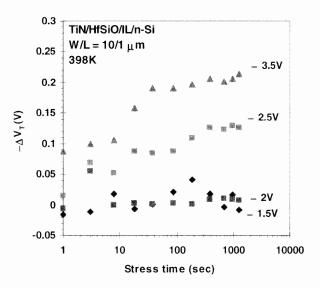

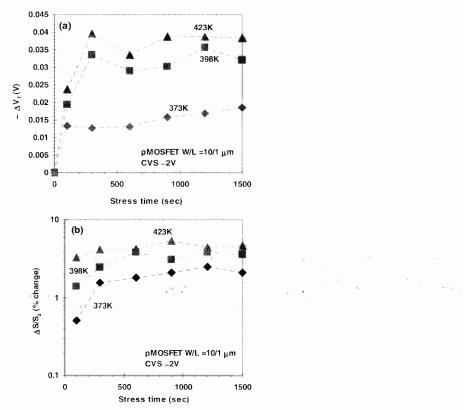

| 6.6    | (a) $\Delta V_T$ and (b) $\Delta S/S_0$ for CVS with $-2$ V of stress level at elevated temperatures                                                                                                      | 133  |

| 6.7    | (a) $\Delta V_T$ and (b) $\Delta S/S_0$ for CVS with -3.5 V of stress level at elevated temperatures                                                                                                      | 134  |

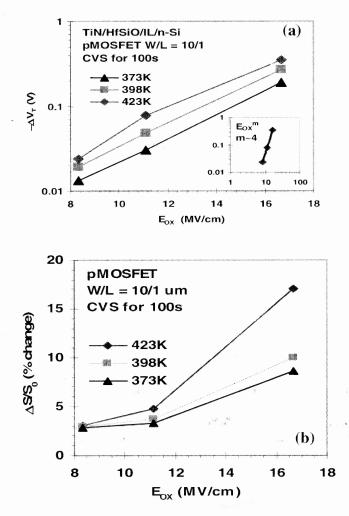

| 6.8    | (a) $\Delta V_T$ and (b) $\Delta S/S_0$ vs. $E_{ox}$ after initial 100s of CVS under different elevated temperatures conditions. [Inset of (a)] $\Delta V_T$ vs. $E_{ox}$ at 423K (150°C)                 | 135  |

| Figure |                                                                                                                                                                                                                                                                                  | Page |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

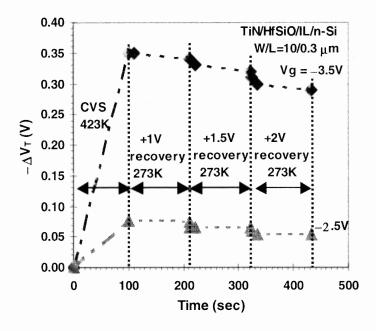

| 6.9    | $\Delta V_T$ vs. time during CVS at 423K (150°C) with $V_g = -3.5$ V and $-2.5$ V, and post-stress recovery under different positive gate bias conditions                                                                                                                        | 136  |

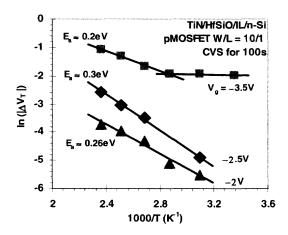

| 6.10   | Arrhenius plots of $\Delta V_T$ for different gate bias. $\Delta V_T$ was measured after initial 100s of CVS                                                                                                                                                                     | 137  |

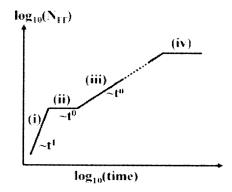

| 6.11   | N <sub>it</sub> vs. stress time as predicted by R-D model                                                                                                                                                                                                                        | 138  |

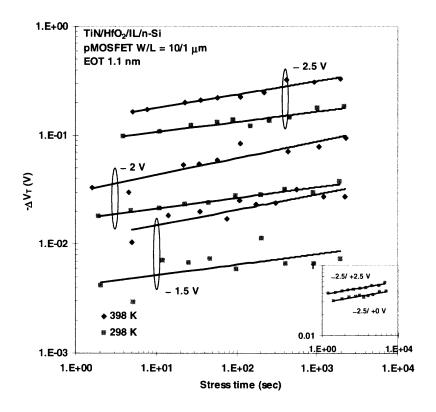

| 6.12   | $\Delta V_T$ vs. stress time for CVS applied on pMOSFETs with TiN/HfO $_2$ based gate stacks under different negative bias and temperature (RT and 398 K) conditions. (Inset) $\Delta V_T$ vs. stress time plots for CVS under zero and non-zero substrate bias conditions at RT | 139  |

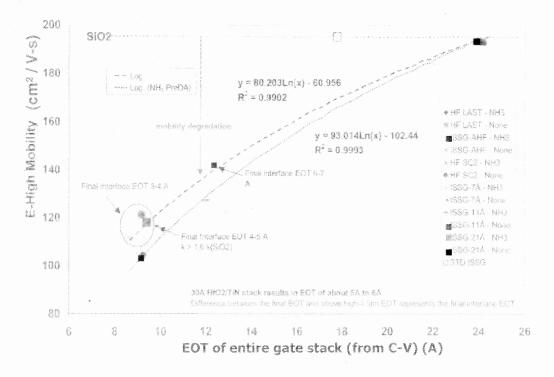

| 7.1    | High-field (~1 MV/cm) mobility vs. final EOT of TiN/3nm HfO <sub>2</sub> /IL/p-Si gate stacks for different IL growth conditions                                                                                                                                                 | 145  |

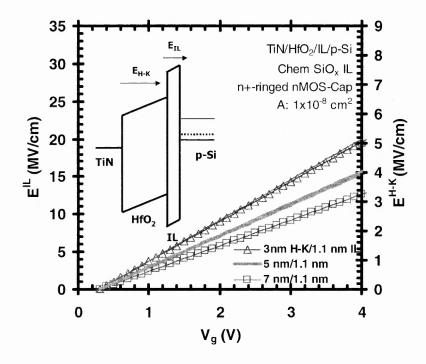

| 7.2    | Distribution of fields across IL $(E_{IL})$ and high-k layer $(E_{H-K})$ for a given stress bias. (Inset) Band diagram of the gate stack under positive gate bias condition.                                                                                                     | 147  |

| 7.3    | I-V characteristics under ramped voltage stress (RVS) applied on SiO <sub>2</sub> based n <sup>+</sup> -ringed nMOS-C                                                                                                                                                            | 148  |

| 7.4    | I-V characteristics under RVS applied on $HfSi_xO_y$ (10% $SiO_2$ ) based MIM capacitors. $E_{BD} \approx 6.5$ MV/cm is comparable with the theoretical value of ~ 7 MV/cm.                                                                                                      | 149  |

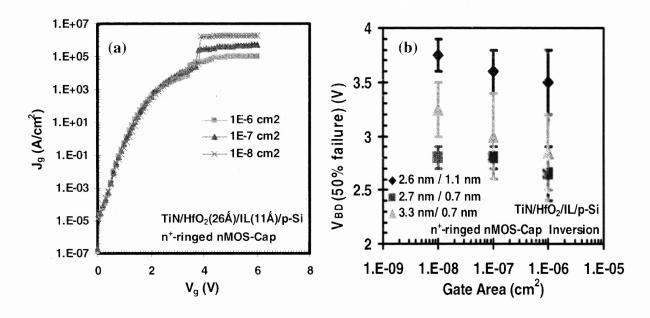

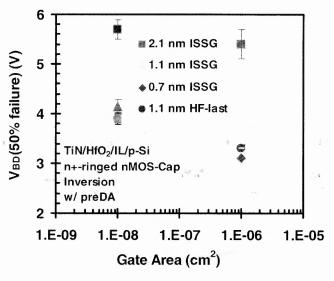

| 7.5    | (a) I-V characteristics under RVS applied on $n^+$ -ringed nMOS-C with gate stacks from split 1 of lot 1 (2.6 nm HfO <sub>2</sub> / 1.1 nm IL) for different area conditions. (b) 50% failure value of breakdown voltage, $V_{BD}$ vs. area for different splits of lot 1        | 150  |

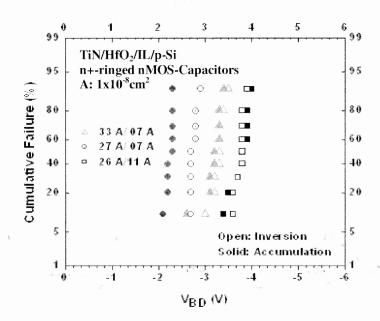

| 7.6    | Cumulative failure distribution of $V_{BD}$ for different splits in lot 1 under inversion and accumulation conditions                                                                                                                                                            | 150  |

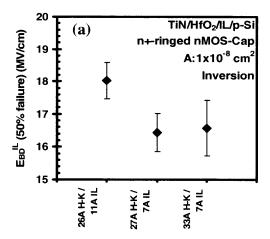

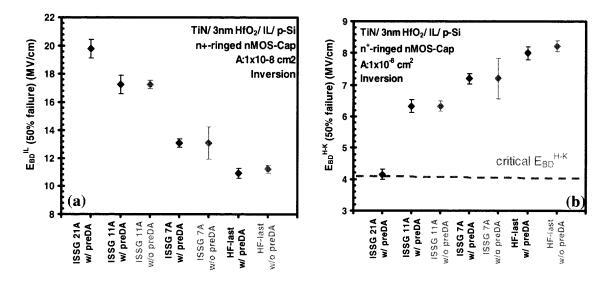

| 7.7    | 50% failure value of (a) $E_{BD}^{IL}$ and (b) $E_{BD}^{H-K}$ under inversion for different splits of lot 1. High- $\kappa$ layer BD occurs first followed by IL, which triggers gate stacks BD.                                                                                 | 151  |

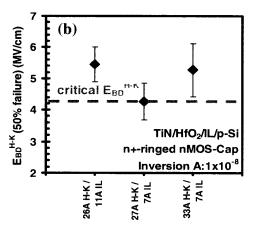

| 7.8    | 50% failure value of (a) $E_{BD}^{IL}$ and (b) $E_{BD}^{H-K}$ under accumulation for different splits of lot 1                                                                                                                                                                   | 152  |

| Figure |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Page |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 7.9    | 50% failure value of (a) $E_{BD}^{\ IL}$ and (b) $E_{BD}^{\ H-K}$ under accumulation for different splits of lot 1                                                                                                                                                                                                                                                                                                                                                                         | 154  |

| 7.10   | 50% failure value of (a) $E_{BD}^{\ IL}$ and (b) $E_{BD}^{\ H-K}$ under inversion for different splits of lot 2                                                                                                                                                                                                                                                                                                                                                                            | 155  |

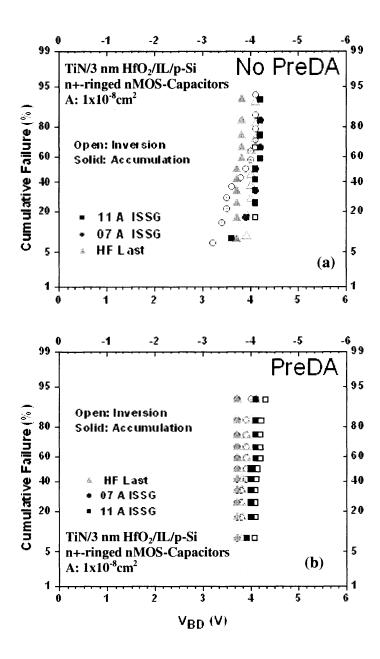

| 7.11   | Cumulative failure distribution of $V_{BD}$ for splits of lot 2, having (a) no PreDA, and (b) PreDA                                                                                                                                                                                                                                                                                                                                                                                        | 157  |

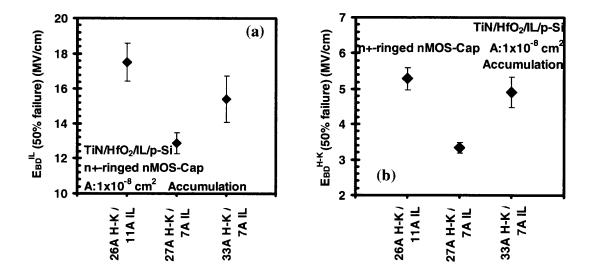

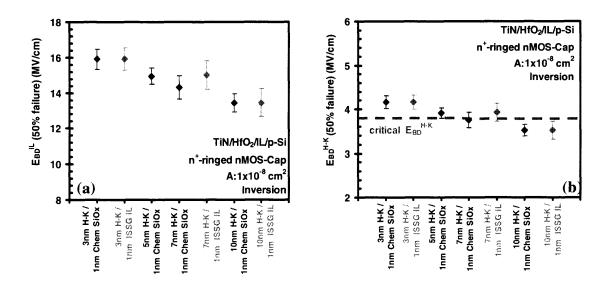

| 7.12   | 50% failure value of (a) $E_{BD}^{\ IL}$ and (b) $E_{BD}^{\ H-K}$ under inversion for different splits of lot 3                                                                                                                                                                                                                                                                                                                                                                            | 158  |

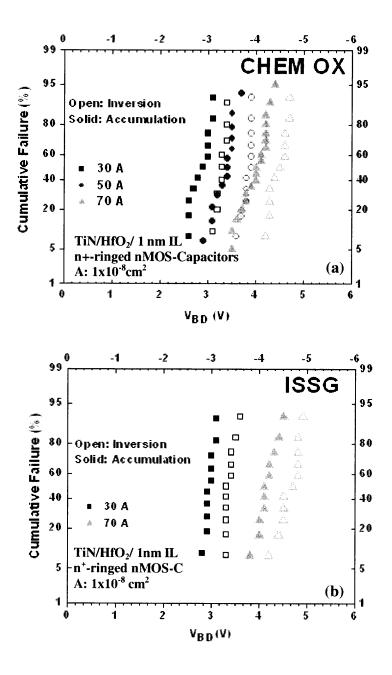

| 7.13   | Cumulative failure distribution of $V_{BD}$ for splits of lot 3, having (a) chemical $SiO_x$ , and (b) ISSG IL                                                                                                                                                                                                                                                                                                                                                                             | 159  |

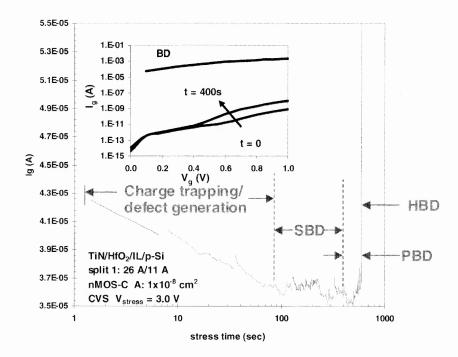

| 7.14   | I-t characteristics of split 1 of lot 1 under CVS with positive gate bias. Different degradation regimes during TDDB are specified. (Inset) I-V characteristics during TDDB                                                                                                                                                                                                                                                                                                                | 161  |

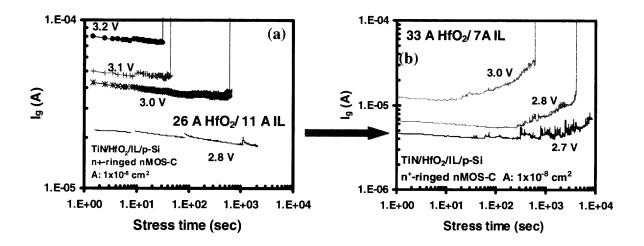

| 7.15   | I-t characteristics during TDDB under CVS with different positive gate bias conditions for (a) split 1 and (b) split 3 of lot 1                                                                                                                                                                                                                                                                                                                                                            | 162  |

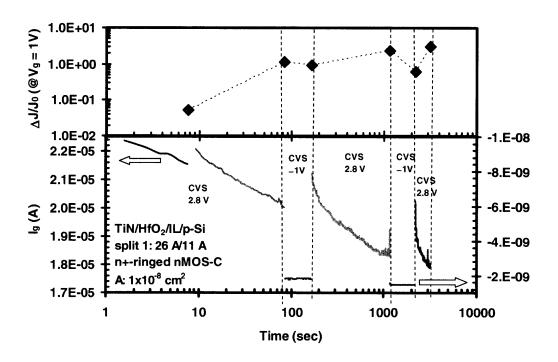

| 7.16   | (a) I-t characteristics of split 1 of lot 1 under stress with 2.8V / relaxation under -1 V cycles. (b) Corresponding SILC, sensed at V <sub>g</sub> = 1V w.r.t. stress/relaxation cycles                                                                                                                                                                                                                                                                                                   | 163  |

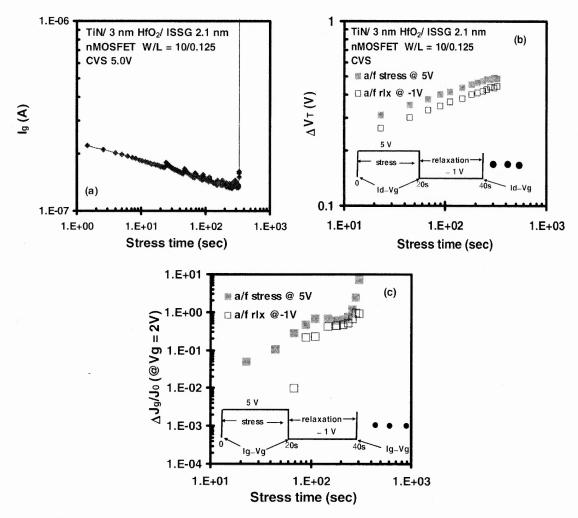

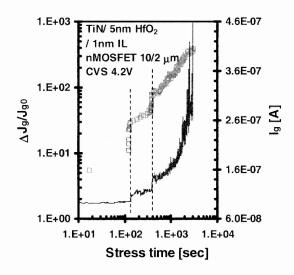

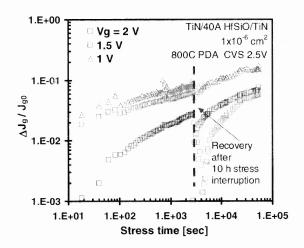

| 7.17   | (a) I-t during TDDB. (b) $\Delta V_T$ vs. stress time during TDDB. Each 20 s of stress is followed by 20s of relaxation at $-1$ V. $\Delta V_T$ after relaxation period is also plotted. (Inset) Stress/relaxation cycle during TDDB. (c) $\Delta J_g/J_{g0}$ (sensed at $V_g=2$ V) vs. stress time during TDDB. Each 20 s of stress is followed by 20s of relaxation at $-1$ V. $\Delta J_g/J_{g0}$ after relaxation period is also plotted. (Inset) Stress/relaxation cycle during TDDB. | 164  |

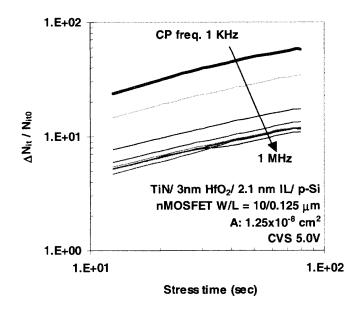

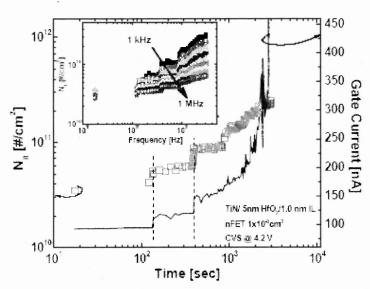

| 7.18   | Normalized $\Delta N_{it}$ (w.r.t. initial $N_{it}$ ) vs. stress time for split 7 of lot 2. Plots for CP frequency in 1 KHz to 1 MHz range are shown                                                                                                                                                                                                                                                                                                                                       | 166  |

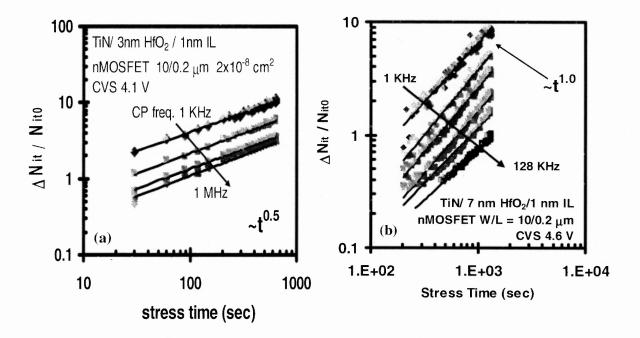

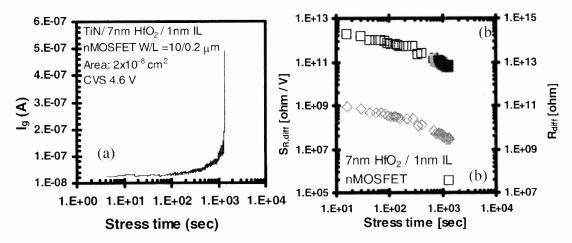

| 7.19   | Normalized $\Delta N_{it}$ (w.r.t. initial $N_{it}$ ), measured at different CP frequencies, vs. stress time during TDDB for (a) 3 nm HfO <sub>2</sub> / 1nm IL and (b) 7 nm HfO <sub>2</sub> / 1nm IL gate stacks                                                                                                                                                                                                                                                                         | 167  |

| Figure |                                                                                                                                                                                                                                                                       | Pag |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

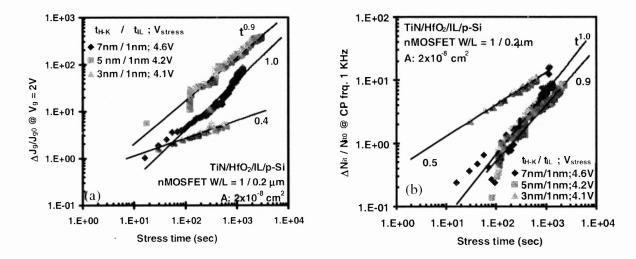

| 7.20   | (a) SILC vs. stress time and (b) normalized $\Delta N_{it}$ vs. stress time for splits 1, 3 and 4 of lot 3. SILC is sensed at $V_g = 2$ V and $N_{it}$ is measured at CP frequency of 1 KHz                                                                           | 16  |

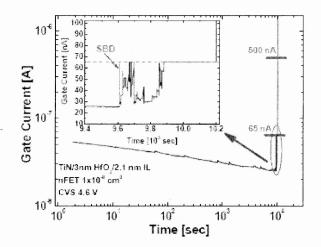

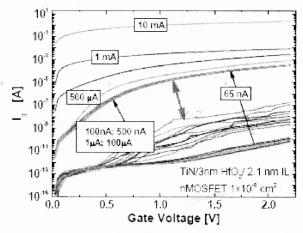

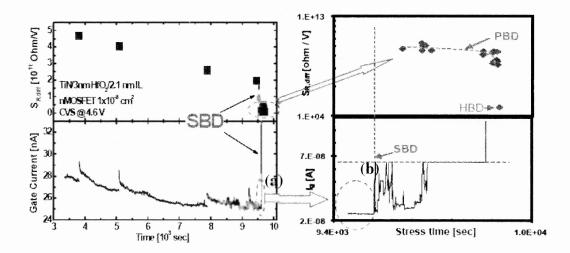

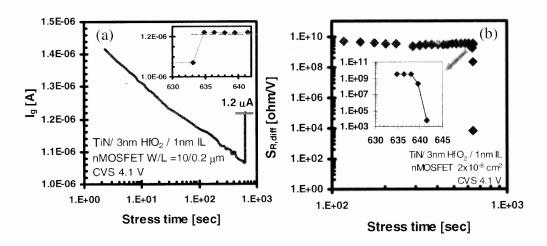

| 7.21   | I-t characteristics during TDDB under CVS with positive gate bias condition for split 7 of lot 2. Compliance limits are applied on I <sub>g</sub> (65 nA to 10 mA) during CVS. (Inset) SBD, PBD and HBD regimes are shown.                                            | 169 |

| 7.22   | I-V plots during TDDB. Compliance limits on I <sub>g</sub> during CVS are labeled and ,thus, specified                                                                                                                                                                | 169 |

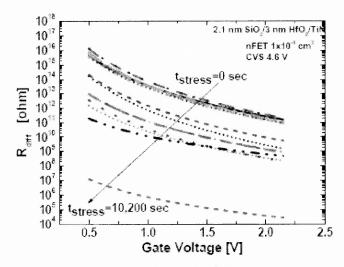

| 7.23   | Differential resistance curves for SILC data (smoothed) in Figure 7.22                                                                                                                                                                                                | 170 |

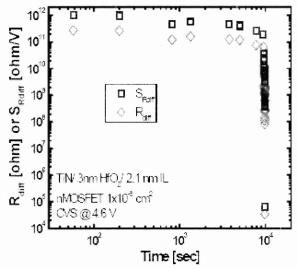

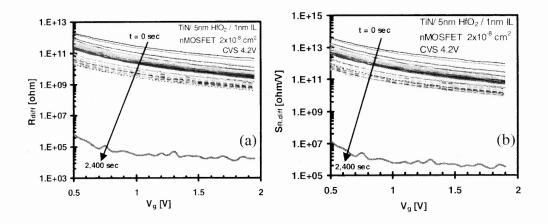

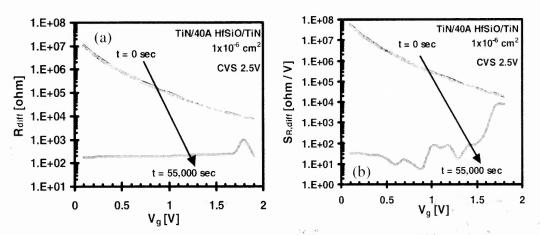

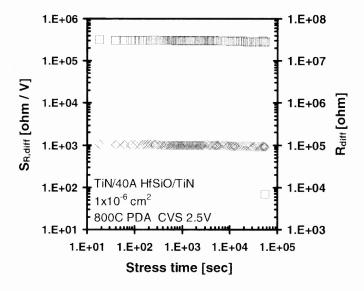

| 7.24   | Changes in $R_{\text{diff}}$ and $S_{R\text{dif}}$ values during the total stress time are plotted as a function of $V_g$ .                                                                                                                                           | 171 |

| 7.25   | (a) shows evolution of the slope of the differential resistance, $S_{Rdiff}$ , and leakage current during CVS prior to SBD. Figure 7.20 (b) shows post SBD evolution of the slope of the differential resistance, $S_{Rdiff}$ , and leakage current.                  | 172 |

| 7.26   | 5nm HfO <sub>2</sub> /1nm IL gate stack, (a) $R_{diff}$ and (b) $S_{R,diff}$ vs. $V_{g}$                                                                                                                                                                              | 173 |

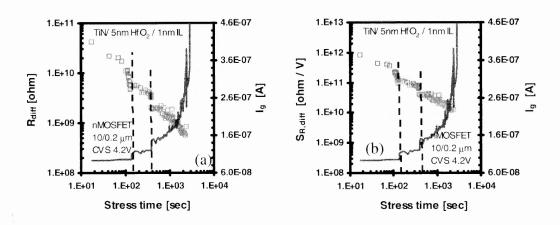

| 7.27   | Evolution of (a) differential resistance, $R_{diff}$ , and leakage current, and (b) $S_{Rdiff}$ , and leakage current, during CVS in 5nm HfO <sub>2</sub> stack                                                                                                       | 173 |

| 7.28   | Evolution of the 1 KHz CP trap density, Nit, and leakage current during CVS on 5 nm HfO2 stack. In the inset: N <sub>it</sub> vs. stress time for various CP frequencies                                                                                              | 174 |

| 7.29   | Evolution of SILC (sensed $@V_g = 2V$ ), and leakage current during CVS on 5 nm HfO2 stack                                                                                                                                                                            | 175 |

| 7.30   | Evolution of (a) gate current, (b) R <sub>diff</sub> and S <sub>R,diff</sub> during CVS for 7 nm HfO <sub>2</sub> stack.                                                                                                                                              | 176 |

| 7.31   | (a) Evolution of gate current during CVS for 3 nm HfO <sub>2</sub> stack. (Inset) Fast increase in gate current during PBD. (b) Evolution of S <sub>R,diff</sub> during CVS for 3 nm HfO <sub>2</sub> stack. (Inset) Fast decrease of S <sub>R,diff</sub> during PBD. | 176 |

| Figure |                                                                                                                                                                                         | Page |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

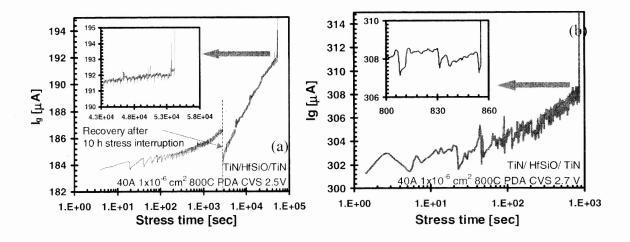

| 7.32   | For 4 nm HfSiO based MIM capacitors, I-t characteristics under CVS applied with stress levels of (a) 2.5 V and (b) 2.7 V. Insets of Figures (a) and (b) show I-t immediately before HBD | 177  |

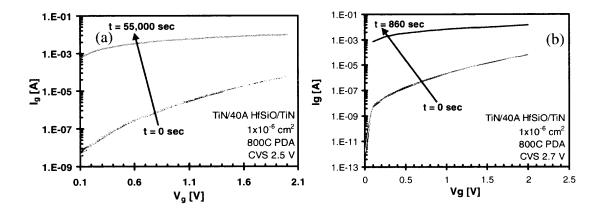

| 7.33   | For 4 nm HfSiO based MIM capacitors, I-V characteristics under CVS applied with stress levels of (a) 2.5V and (b) 2.7V                                                                  | 178  |

| 7.34   | SILC sensed at different V <sub>g</sub>                                                                                                                                                 | 179  |

| 7.35   | For 4 nm HfSiO based MIM capacitors, (a) R <sub>diff</sub> vs. V <sub>g</sub> and (b) S <sub>R,diff</sub> vs. Vg during TDDB                                                            | 179  |

| 7.36   | Evolution of the differential resistance, $R_{\text{diff}}$ , and its slope, $S_{\text{Rdiff}}$ , during CVS of MIM capacitors                                                          | 180  |

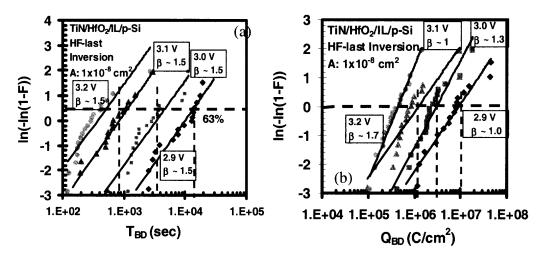

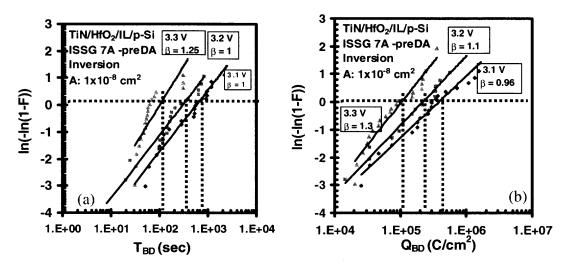

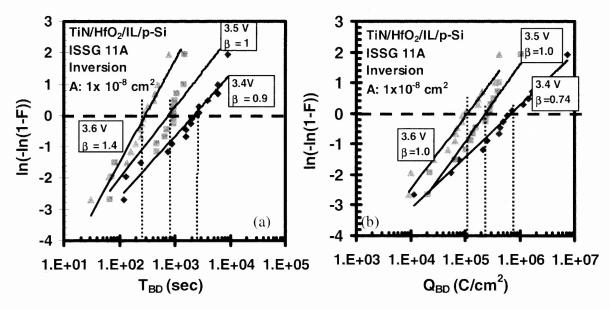

| 7.38   | Weibull plot of (a) $T_{BD}$ and (b) $Q_{BD}$ for 3nm HfO <sub>2</sub> / 1.1nm HF-last IL                                                                                               | 182  |

| 7.39   | Weibull plot of (a) $T_{BD}$ and (b) $Q_{BD}$ for 3nm HfO <sub>2</sub> / 0.7 nm ISSG IL case for different bias conditions. PreDA was performed for this split.                         | 182  |

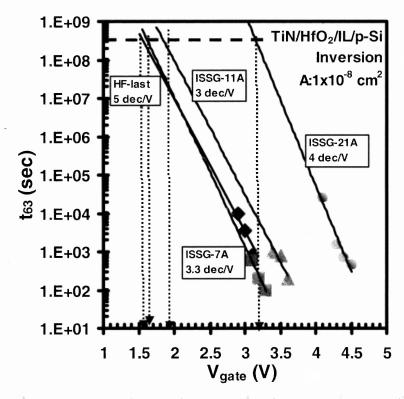

| 7.40   | Weibull plot of (a) $T_{BD}$ and (b) $Q_{BD}$ for 3nm HfO <sub>2</sub> / 1.1 nm ISSG IL case for different bias conditions. PreDA was performed for this split.                         | 183  |

| 7.41   | Sixty-thrre percent (63%) failure value of T <sub>BD</sub> , t <sub>63</sub> vs. Vgate for different IL growth conditions                                                               | 184  |

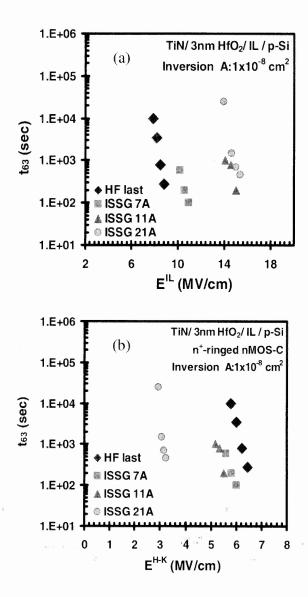

| 7.42   | 63% failure value of $T_{BD}$ (t <sub>63</sub> ) vs. (a) $E^{IL}$ and (b) $E^{H-K}$ for splits with different IL conditions. PreDA was performed for each split                         | 185  |

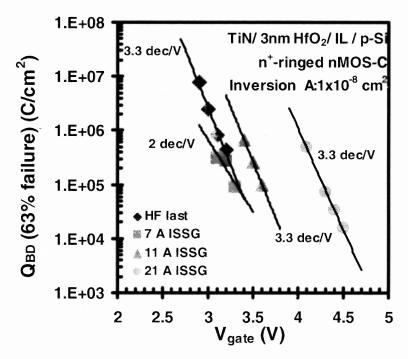

| 7.43   | 63% failure value of $Q_{BD}$ vs. $V_{gate}$ for different IL growth conditions. PreDA was performed on each split                                                                      | 186  |

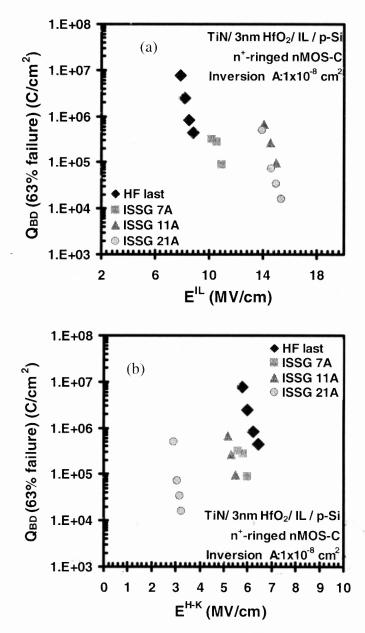

| 7.44   | 63% failure value of $Q_{BD}$ vs. (a) $E^{IL}$ and (b) $E^{H-K}$ for splits with different IL conditions. PreDA was performed for each split                                            | 187  |

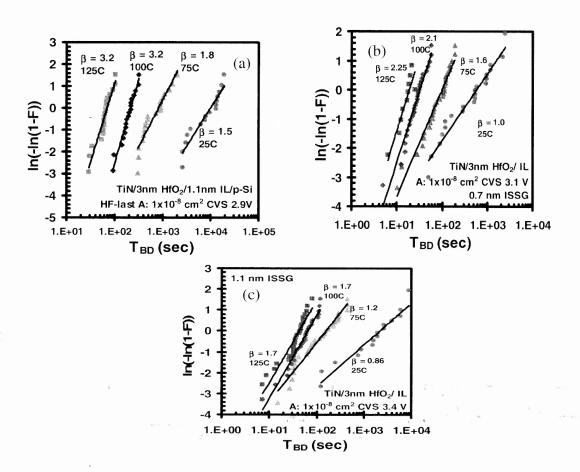

| 7.45   | Weibull plots of T <sub>BD</sub> at different temperatures for (a) HF-last, (b) 0.7 nm ISSG, and (c) 1.1 nm ISSG IL growth conditions                                                   | 190  |

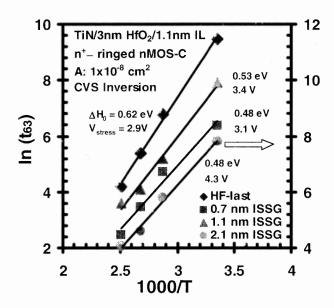

| 7.46   | Arrhenius plot of t <sub>63</sub> for different IL growth conditions                                                                                                                    | 191  |

#### **CHAPTER 1**

### INTRODUCTION, MOTIVATION AND OBJECTIVES

#### 1.1 Introduction

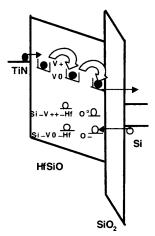

Unabated demands for higher density and faster operational speed of transistors, and lower power consumption in integrated circuits (IC) have pushed complementary metal oxide semiconductor (CMOS) technology into the forefront of the microelectronics industry. Transistor scaling has so far achieved a remarkable success in optimizing these diverse objectives. However, further downscaling of MOS field effect transistor (MOSFET) dimensions, specifically for oxide thickness (tox) below 1.6 nm, increases transistor leakage current to levels unacceptable for low power applications [1]. An attractive solution is to replace SiO<sub>2</sub> with high-κ dielectric materials (mostly Hf, Zr and Al-based) while retaining the standard MOSFET design [2], [3]. This has the prospect of resulting in higher effective thickness tox for equivalent oxide capacitance, which in turn reduces gate leakage but not drive current, i.e., maintains the edge in the electrical performance comparable to SiO<sub>2</sub>.