## **Copyright Warning & Restrictions**

The copyright law of the United States (Title 17, United States Code) governs the making of photocopies or other reproductions of copyrighted material.

Under certain conditions specified in the law, libraries and archives are authorized to furnish a photocopy or other reproduction. One of these specified conditions is that the photocopy or reproduction is not to be "used for any purpose other than private study, scholarship, or research." If a, user makes a request for, or later uses, a photocopy or reproduction for purposes in excess of "fair use" that user may be liable for copyright infringement,

This institution reserves the right to refuse to accept a copying order if, in its judgment, fulfillment of the order would involve violation of copyright law.

Please Note: The author retains the copyright while the New Jersey Institute of Technology reserves the right to distribute this thesis or dissertation

Printing note: If you do not wish to print this page, then select "Pages from: first page # to: last page #" on the print dialog screen

The Van Houten library has removed some of the personal information and all signatures from the approval page and biographical sketches of theses and dissertations in order to protect the identity of NJIT graduates and faculty.

#### **ABSTRACT**

## H-SIMD MACHINE: CONFIGURABLE PARALLEL COMPUTING FOR DATA-INTENSIVE APPLICATIONS

## by Xizhen Xu

This dissertation presents a hierarchical single-instruction multiple-data (H-SIMD) configurable computing architecture to facilitate the efficient execution of data-intensive applications on field-programmable gate arrays (FPGAs). H-SIMD targets data-intensive applications for FPGA-based system designs. The H-SIMD machine is associated with a hierarchical instruction set architecture (HISA) which is developed for each application. The main objectives of this work are to facilitate ease of program development and high performance through ease of scheduling operations and overlapping communications with computations.

The H-SIMD machine is composed of the host, FPGA and nano-processor layers. They execute host SIMD instructions (HSIs), FPGA SIMD instructions (FSIs) and nano-processor instructions (NPIs), respectively. A distinction between communication and computation instructions is intended for all the HISA layers. The H-SIMD machine also employs a memory switching scheme to bridge the omnipresent large bandwidth gaps in configurable systems. To showcase the proposed high-performance approach, the conditions to fully overlap communications with computations are investigated for important applications. The building blocks in the H-SIMD machine, such as high-performance and area-efficient register files, are presented in detail. The H-SIMD machine hierarchy is implemented on a host Dell workstation and the Annapolis Wildstar II FPGA board. Significant speedups have been achieved for matrix multiplication (MM), 2-dimensional discrete cosine transform (2D DCT) and 2-dimensional fast Fourier transform (2D FFT) which are used widely in science and engineering.

In another FPGA-based programming paradigm, a high-level language (here ANSI C) can be used to program the FPGAs in a mode similar to that of the H-SIMD machine in terms of trying to minimize the effect of overheads. More specifically, a multi-threaded overlapping scheme is proposed to reduce as much as possible, or even completely hide, runtime FPGA reconfiguration overheads. Nevertheless, although the HLL-enabled reconfigurable machine allows software developers to customize FPGA functions easily, special architecture techniques are needed to achieve high-performance without significant penalty on area and clock frequency. Two important high-performance applications, matrix multiplication and image edge detection, are tested on the SRC-6 reconfigurable machine. The implemented algorithms are able to exploit the available data parallelism with independent functional units and application-specific cache support. Relevant performance and design tradeoffs are analyzed.

## H-SIMD MACHINE: CONFIGURABLE PARALLEL COMPUTING FOR DATA-INTENSIVE APPLICATIONS

by Xizhen Xu

A Dissertation

Submitted to the Faculty of

New Jersey Institute of Technology

in Partial Fulfillment of the Requirements for the Degree of

Doctor of Philosophy in Electrical Engineering

**Department of Electrical and Computer Engineering**

May 2006

Copyright © 2006 by Xizhen Xu ALL RIGHTS RESERVED

## APPROVAL PAGE

# H-SIMD MACHINE: CONFIGURABLE PARALLEL COMPUTING FOR DATA-INTENSIVE APPLICATIONS

## Xizhen Xu

| <del></del>                                                                                                | <del></del> |

|------------------------------------------------------------------------------------------------------------|-------------|

| Dr. Sotirios G. Ziavras, Dissertation Advisor<br>Professor of Electrical and Computer Engineering, NJIT    | Date        |

| Dr. Edwin Hou, Committee Member Associate Professor of Electrical and Computer Engineering, NJIT           | Date        |

| Dr. Jie Hu, Committee Member Assistant Professor of Electrical and Computer Engineering, NJIT              | Date        |

| Dr. Roberto Rojas-Cessa, Committee Member Assistant Professor of Electrical and Computer Engineering, NJIT | Date        |

| Dr. Alexandros V. Gerbessiotis, Committee Member Associate Professor of Computer Science, NJIT             | Date        |

### **BIOGRAPHICAL SKETCH**

**Author:** Xizhen Xu

**Degree:** Doctor of Philosophy

**Date:** May 2006

## **Undergraduate and Graduate Education:**

- Doctor of Philosophy in Electrical Engineering New Jersey Institute of Technology, Newark, NJ, 2006

- Master of Science in Electrical Engineering Northwestern Polytechnic University, Xi'an, China, 1996

- Bachelor of Science in Electrical Engineering Northwestern Polytechnic University, Xi'an, China, 1993

Major: Electrical Engineering

## **Presentations and Publications:**

- X. Xu and S. G. Ziavras, "A Coarse-Grain Hierarchical Technique for 2-Dimensional FFT on Configurable Parallel Computers," *IEICE Trans. on Information and Systems, Special Issue on Parallel/Distributed Computing and Networking*, vol. E89-D, no. 2, pp. 639-646, Feb. 2006.

- X. Xu, S. G. Ziavras, and T.-G. Chang, "An FPGA-Based Parallel Accelerator for Matrix Multiplications in the Newton-Raphson Method," *IFIP International Conference on Embedded and Ubiquitous Computing*, Nagasaki, Japan, pp. 458-468, Dec. 2005.

- X. Xu and S. G. Ziavras, "H-SIMD Machine: Configurable Parallel Computing for Matrix Multiplication," *IEEE International Conference on Computer Design*, San Jose, CA, pp. 671-676, Oct. 2005.

- X. Xu and S. G. Ziavras, "A Hierarchically-controlled SIMD Machine for 2D DCT on FPGAs," *IEEE International Conference on Systems-on-Chip*, Herndon, VA, pp. 276-279, Sept. 2005.

- X. Xu and S. G. Ziavras, "A Configurable and Scalable SIMD Machine for Computation-Intensive Applications," *WSEAS Trans. on Computers*, vol. 2, no. 4, pp. 1021-1029, Oct. 2003 (invited paper).

X. Xu and S. G. Ziavras, "Iterative Methods for Solving Linear Systems of Equations on FPGA-Based Machines," 18th International Conference on Computers and Their Applications, Honolulu, Hawaii, pp. 472-475, Mar. 2003.

to Yun & Andy for all the love you gave to me

### **ACKNOWLEDGMENT**

First of all, I own my deepest gratitude to my advisor, Dr. Sotirios G. Ziavras, for his visionary guidance and endless encouragement through my PhD study at NJIT. Greatest appreciation gives to his motivation, creativity, and rich knowledge that always inspire me to move forward in my dissertation research. His strong support and invaluable advisement were always there for me whenever I needed. Greatest thanks give to his enduring patience. From his answer to each of my question to his suggestion to every writing improvement in my dissertation, what I learned is not just a technical concept or an English word; I learned important personal characters as an excellent professor that will continue to guide me in the future.

I also would like to thank Dr. Jie Hu for his technical guidance and insightful comments to this dissertation and for serving on my dissertation committee. My thanks also extend to Dr. Alexandros V. Gerbessiotis, Dr. Edwin Hou and Dr. Roberto Rojas-Cessa for their technical suggestions and for serving on my dissertation committee. I would like to thank the Hashimoto family and fellowship program. Their generosity allowed me to receive a Hashimoto Fellowship for the 2005-2006 academic year. My sincere thanks go to all my friends and colleagues in the CAPPL lab for the help you gave and the friendship we shared. I wish everybody from CAPPL great achievements in the future.

The love, support and encouragement from my family was essential in completing this dissertation. I am extremely grateful for all the sacrifices my parents made to raise me up. My deep thanks to my beloved wife, Yun Teng, for her support, encouragement, tolerance, and patience from anywhere I needed. Without your love and understanding, I would not be here today.

## TABLE OF CONTENTS

| Cl | hapte | r     |                                        | Page |

|----|-------|-------|----------------------------------------|------|

| 1  | INT   | RODU  | CTION                                  | . 1  |

|    | 1.1   | Resea | rch Background and Problem Statement   | . 1  |

|    |       | 1.1.1 | Research Background                    | . 1  |

|    |       | 1.1.2 | Motivation and Problem Statement       | . 4  |

|    | 1.2   | Resea | rch Objectives                         | . 5  |

|    | 1.3   | Organ | ization of the Dissertation            | . 7  |

| 2  | CSC   | C PLA | TFORMS                                 | . 8  |

|    | 2.1   | COTS  | FPGA Technology                        | . 8  |

|    |       | 2.1.1 | On-chip Memory                         | . 9  |

|    |       | 2.1.2 | Clock Tree Distribution and Management | . 10 |

|    |       | 2.1.3 | I/O Technology                         | . 12 |

|    |       | 2.1.4 | Multiplier                             | . 13 |

|    |       | 2.1.5 | Configurable Logic Blocks              | . 13 |

|    | 2.2   | COTS  | FPGA-Based Computing Systems           | . 13 |

|    | 2.3   | Custo | m CSOC Studies                         | . 16 |

|    |       | 2.3.1 | MorphoSys                              | . 16 |

|    |       | 2.3.2 | PipeRench                              | . 16 |

|    |       | 2.3.3 | MATRIX                                 | . 18 |

|    |       | 2.3.4 | RAW                                    | . 18 |

|    |       | 2.3.5 | Garp                                   | . 19 |

| 3  | THE   | H-SIM | MD MACHINE                             | . 21 |

|    | 3.1   | The H | I-SIMD Machine                         | . 21 |

|    |       | 3.1.1 | H-SIMD Architecture                    | . 22 |

|    |       | 3.1.2 | Memory Switching Schemes               | . 23 |

# TABLE OF CONTENTS (Continued)

| Cl | hapte | r      |                                                        | Page |

|----|-------|--------|--------------------------------------------------------|------|

|    |       | 3.1.3  | H-SIMD Machine Features                                | 27   |

|    | 3.2   | Size-A | Adjustable Register File Design                        | 29   |

| 4  | CAS   | E STU  | DIES ON THE H-SIMD MACHINE                             | 32   |

|    | 4.1   | Examp  | ple 1: Matrix Multiplication                           | 32   |

|    |       | 4.1.1  | HSIs, FSIs, and NPIs for MM [1]                        | 32   |

|    |       | 4.1.2  | General-purpose Nano-processor ISA                     | 34   |

|    |       | 4.1.3  | Assembler Design and Data Initialization               | 35   |

|    |       | 4.1.4  | Task Partitioning Analysis for Matrix Multiplication   | 37   |

|    |       | 4.1.5  | Matrix Multiplication: Implementation and Test Results | 40   |

|    | 4.2   | Examp  | ple 2: 2D Fast Fourier Transform                       | 43   |

|    |       | 4.2.1  | HISA for 2D FFT [2]                                    | 43   |

|    |       | 4.2.2  | Task Partitioning in 2D FFT: Performance Analysis      | 45   |

|    |       | 4.2.3  | Implementation Results for 2D FFT                      | 47   |

|    | 4.3   | Examp  | ple 3: 2D Discrete Cosine Transform                    | 50   |

|    |       | 4.3.1  | HISA ISA for DCT2 [3]                                  | 50   |

|    |       | 4.3.2  | Task Partitioning for DCT2: Performance Analysis       | 52   |

|    |       | 4.3.3  | DCT2: Implementation and Test Results                  | 53   |

| 5  | HLL   | -SUPP  | ORTED RECONFIGURABLE COMPUTING                         | 62   |

|    | 5.1   | SRC-6  | 6 General Purpose Reconfigurable Computer              | 62   |

|    |       | 5.1.1  | Hardware Architecture                                  | 62   |

|    |       | 5.1.2  | SRC Programming Model                                  | 64   |

|    | 5.2   | Case S | Studies                                                | 65   |

|    |       | 5.2.1  | Matrix Multiplication                                  | 65   |

|    |       | 5.2.2  | Image Edge Detection                                   | . 70 |

|    |       | 5.2.3  | Operation Overlapping via Multithreading               | . 74 |

# TABLE OF CONTENTS (Continued)

| Cl | Chapter                         |    |  |

|----|---------------------------------|----|--|

| 6  | CONCLUSIONS AND FUTURE RESEARCH | 78 |  |

| RF | EFERENCES                       | 80 |  |

## LIST OF TABLES

| Table | e P                                                                                                                                   | age |

|-------|---------------------------------------------------------------------------------------------------------------------------------------|-----|

| 1.1   | Relationship Summary of ASICs, Microprocessors and FPGAs                                                                              | 3   |

| 2.1   | Comparison of Configurable Systems                                                                                                    | 20  |

| 3.1   | FPGA Resource Consumption for Different Types of Register File Designs .                                                              | 31  |

| 4.1   | General-Purpose NPIs                                                                                                                  | 36  |

| 4.2   | Characteristics of the Quixilica FPU and H-SIMD MAC                                                                                   | 41  |

| 4.3   | Execution Time of MM for Various Test Cases                                                                                           | 42  |

| 4.4   | Performance Comparison between H-SIMD and Other Works                                                                                 | 43  |

| 4.5   | Performance Comparison of the H-SIMD Machine and a 2.8GHz Xeon Workstation for 2D FFT                                                 | 49  |

| 4.6   | Cost-Performance Comparison of the H-SIMD Machine and the Xeon Processor                                                              | 50  |

| 4.7   | Frame Rates for Various Frame and Matrix Block Sizes                                                                                  | 54  |

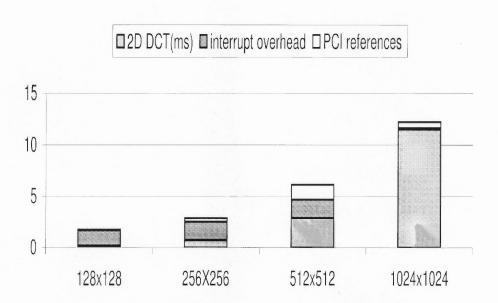

| 4.8   | Performance Comparison for the $1024 \times 1024$ -point DCT2                                                                         | 54  |

| 5.1   | Experimental MM Results on a Dual-FPGA MAP Processor for Single-precision and Double-precision Floating-point Implementations (Square |     |

|       | Matrices)                                                                                                                             | 69  |

| 5.2   | The MAP FPGA Resource Utilization Results on XC2VP100                                                                                 | 70  |

| 5.3   | Comparison with Other MM Approaches on FPGAs                                                                                          | 71  |

| 5.4   | FPGA Resource Utilization for Prewitt Edge Detection                                                                                  | 73  |

| 5.5   | MAP Performance for Prewitt Edge Detection                                                                                            | 74  |

| 5.6   | Performance Comparison for $512 \times 512$ Prewitt Edge Detection                                                                    | 75  |

| 5.7   | Workload Characteristics of the T1 and T2 tasks                                                                                       | 77  |

| 5.8   | Overlapped Task Execution Time for Multithreading-based MM                                                                            | 77  |

## LIST OF FIGURES

| Figu | re                                                                                                                        | Page |

|------|---------------------------------------------------------------------------------------------------------------------------|------|

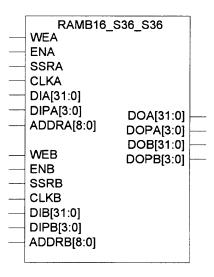

| 2.1  | Virtex II on-chip block SelectRAM memory.                                                                                 | 10   |

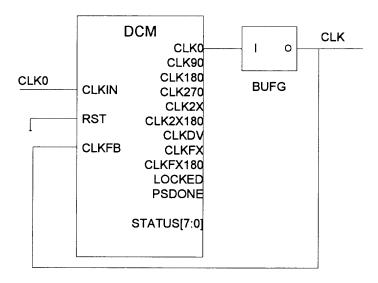

| 2.2  | Configuration of DCM and BUFG for the clock deskew and current driving                                                    | 11   |

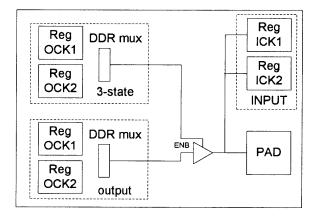

| 2.3  | Virtex-II IOB diagram.                                                                                                    | 12   |

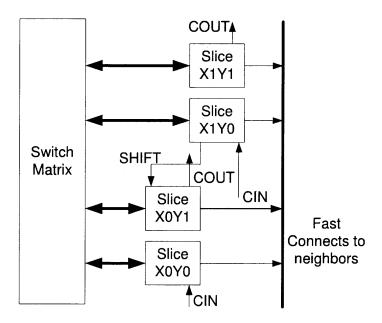

| 2.4  | Xilinx Virtex-II CLB                                                                                                      | 14   |

| 2.5  | SPLASH-2 computing platform (adapted from [4])                                                                            | 15   |

| 2.6  | Components of MorphoSys implementations (adapted from [5])                                                                | 17   |

| 3.1  | H-SIMD machine architecture.                                                                                              | 24   |

| 3.2  | The HISA ISA for the H-SIMD architecture                                                                                  | 25   |

| 3.3  | HC-level memory switching in H-SIMD.                                                                                      | 26   |

| 3.4  | Nano-processor datapath and control unit.                                                                                 | 27   |

| 3.5  | Dual-port BRAM-based size-adjustable register file                                                                        | 30   |

| 4.1  | General-purpose NP instruction format                                                                                     | 37   |

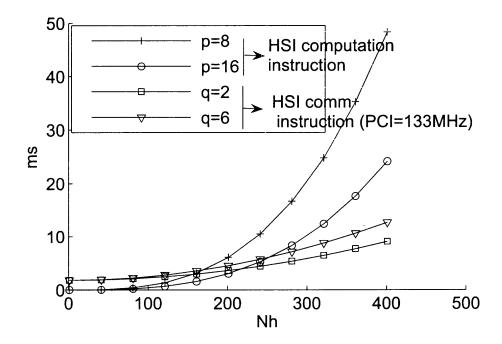

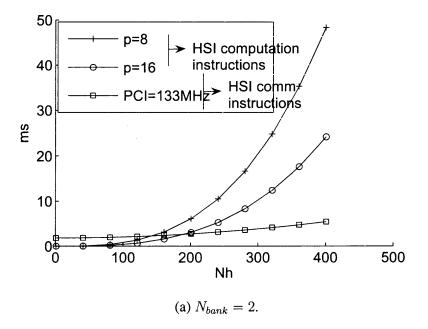

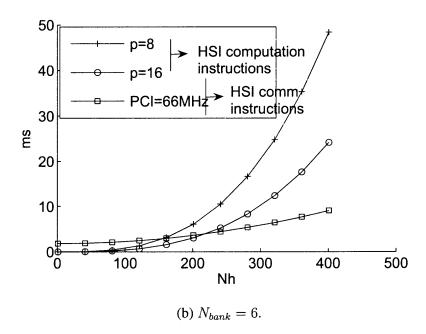

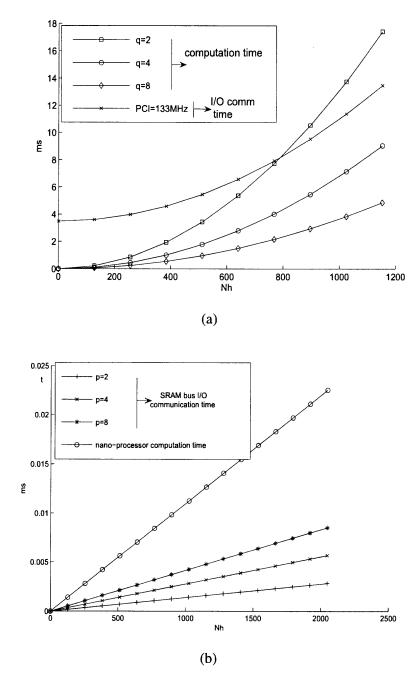

| 4.2  | Execution times of the computation and communication HSIs as a function of $N_h$ , $p$ and $q$                            | 39   |

| 4.3  | Execution times of the computation and communication FSIs as a function of $N_f$ , $p$ , and $N_{bank}$                   | 55   |

| 4.4  | $1024 \times 1024$ MM execution time as a function of $N_h$                                                               | 56   |

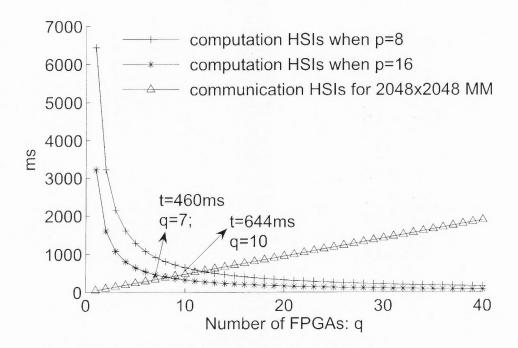

| 4.5  | Execution time vs. number of FPGAs (2048×2048 MM)                                                                         | 56   |

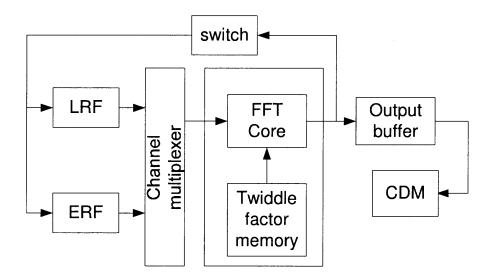

| 4.6  | Nano-processor FFT datapath.                                                                                              | 57   |

| 4.7  | Computation and I/O communication times with (a) host PCI bandwidth and (b) SRAM bandwidth.                               | 58   |

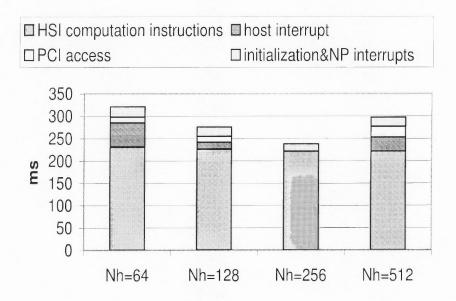

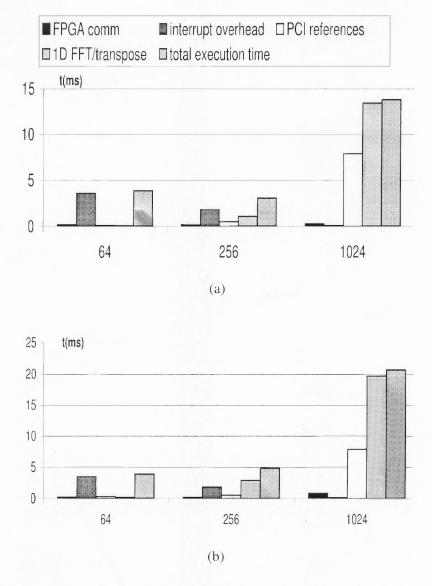

| 4.8  | Execution time breakdown of 2D FFT on (a) 16-bit complex numbers and (b) IEEE754 single-precision floating-point numbers. | 59   |

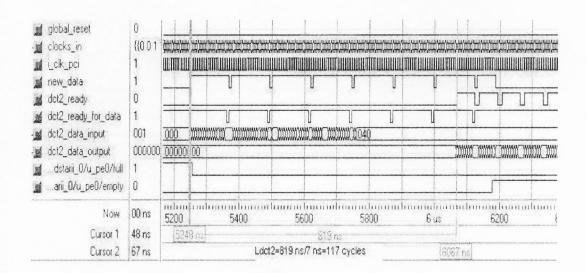

| 4.9  | $8\times8\text{-point}$ 2D DCT engine's simulation result and its latency                                                 | 60   |

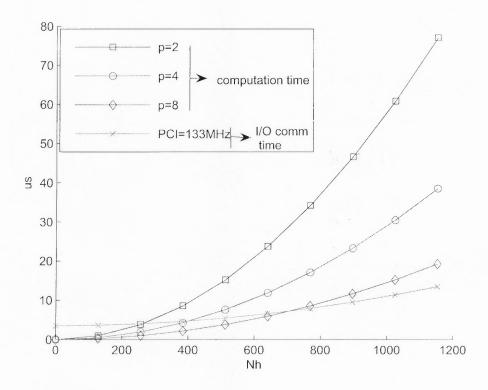

| 4.10 | Computation vs I/O communication times as a function of $N_h$ and $p. \dots$                                              | 60   |

| 4.11 | Execution time breakdown of DCT2 for six input frames                                                                     | 61   |

# LIST OF FIGURES (Continued)

| Figu | re                                                                                                                                                                | Page  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

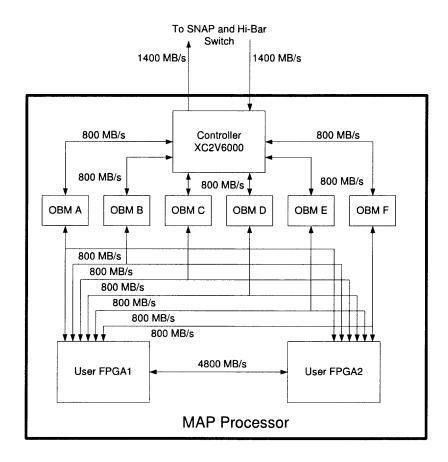

| 5.1  | The architecture of the MAP processor in the SRC-6 machine [6]                                                                                                    | 63    |

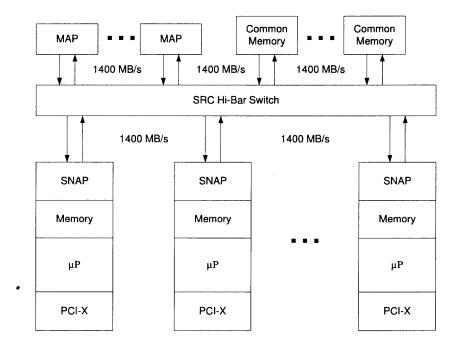

| 5.2  | SRC-6 high end configuration with SNAP and a Hi-Bar switch                                                                                                        | 64    |

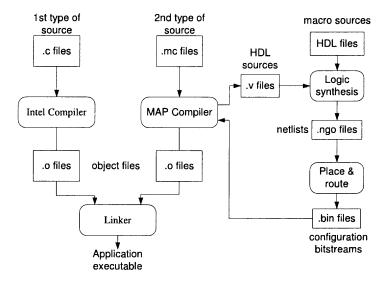

| 5.3  | Carte compilation process.                                                                                                                                        | 65    |

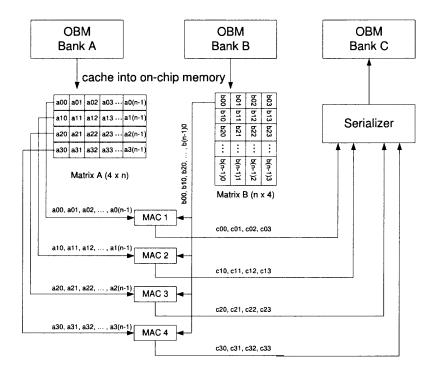

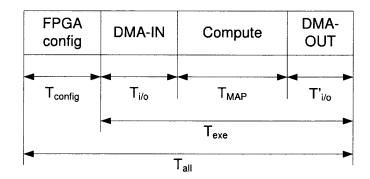

| 5.4  | Illustration of MM computations and data movements                                                                                                                | 67    |

| 5.5  | Run time schedule.                                                                                                                                                | 68    |

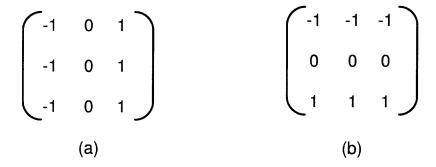

| 5.6  | Convolution masks for Prewitt edge detection. (a) X gradient; (b) Y gradient.                                                                                     | 70    |

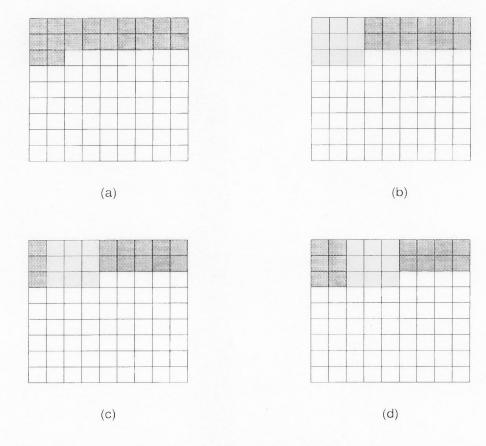

| 5.7  | Applying $3 \times 3$ sliding window on SRC with delay queue support. (a) the startup latency; (b) the first, (c) the second, and (d) the third processing cycles | s. 72 |

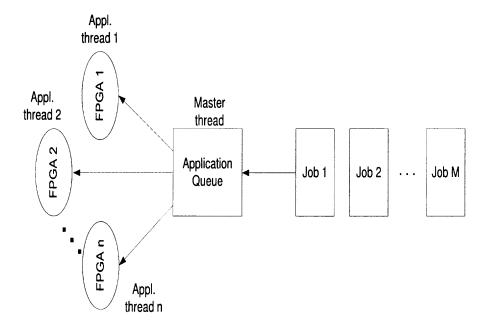

| 5.8  | Multithreading-based operation overlapping scheme                                                                                                                 | 76    |

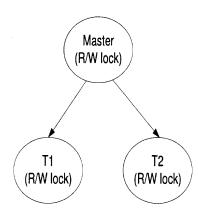

| 5.9  | Thread relationship with R/W lock                                                                                                                                 | 77    |

### **CHAPTER 1**

## INTRODUCTION

## 1.1 Research Background and Problem Statement

This section presents a research background for this dissertation as it stems from current mainstream computing paradigms. It involves general-purpose microprocessors, application-specific integrated circuits (ASICs) and configurable systems implemented with FPGAs. The motivations for this dissertation are also stated.

## 1.1.1 Research Background

Conventionally, custom ASICs and general-purpose microprocessors are the two primary hardware technologies used to implement application algorithms [7] [8]. The choice of the specific technology is based on a tradeoff between the contradictory design forces of generalization and specialization. With temporal computing, general-purpose microprocessors can provide adequate performance, reasonable efficiency and reduced costs for many applications but often fail to meet the most demanding performance requirements. ASICs can provide excellent performance by carrying out spatial computing but at the cost of greater non-recurring engineering (NRE) expenses and inflexibility. Obviously, neither ASICs nor general-purpose microprocessors can provide a very good balance among performance, flexibility and cost.

In order to meet these challenges, configurable computing emerged in the past decade as a significant computing paradigm [9]. It attempts to combine the advantages of both ASICs and general-purpose microprocessors. The relationship among ASICs, microprocessors and FPGAs is shown in Table 1.1. Specifically, a configurable computer is characterized by hardware programmability which is not available in other computing paradigms.

The idea of configurable computing was first proposed in 1960 by the computer pioneer Gerald Estrin [10], and yet the technology to realize Estrin's configurable computer did not exist at that time. However, the vision was kept intact and has recently become possible with the development of new-generation FPGA technology. Implemented with programmable logic that can be organized and structured to fit the natural dataflow of an application, configurable computing refers to customizing the system logic functionality and interconnect connectivity through post-fabrication and user-defined configuration once before an application is run. This definition can be further extended to also include runtime configurable computing (run-time reconfiguration, on-line reconfiguration or adaptive computing) by which the functionality of the configurable hardware can be modified during application execution, as needed to fit the latter. The run-time configurable computer can better exploit underutilized hardware and properly partition a large application into the limited set of configurable resources. However, the run-time configuration overhead still remains a big challenge for this computing paradigm to be accepted in mainstream configurable computing.

Configurable computers, such as SPLASH-2 [4], RENCO [11], PAM [12], Chimaera [13], PRISM [14] and DISC [15], have proven to be capable of speeding up a wide variety of applications, such as data encryption [16] [17], system acquisition [18], image processing [19] and artificial intelligence [20] [21]. Typically, a configurable computer consists of the host and the configurable system-on-a-chip (CSOC) components. The host performs the operations that cannot be done efficiently on the CSOC, such as data-dependent control and variable-length loops, while the computation-intensive parts of the application are mapped to the CSOC(s). The FPGAs are the most widely deployed CSOC hardware because of their configurability, ease of application development and recently rich resource provision, making them increasingly popular.

High-performance parallel computers have been the driving force throughout the computing history and have accomplished a great deal of success in solving

Table 1.1 Relationship Summary of ASICs, Microprocessors and FPGAs

|                    |          | ASICs | Microprocessor | FPGAs |

|--------------------|----------|-------|----------------|-------|

| Programmability    | Software | No    | Yes            | No    |

|                    | Hardware | No    | No             | Yes   |

| Spatial computing  |          | Yes   | No             | Yes   |

| Temporal computing |          | No    | Yes            | No    |

computation-intensive problems. To distinguish among different types, we can first classify computers as follows according to Flynn's notions of the instruction and data streams [22]: 1) SISD (single instruction stream over a single data stream); 2) SIMD (single instruction stream over multiple data streams); 3) MIMD (multiple instruction streams over multiple data streams); 4) MISD (multiple instruction streams over a single data stream). The SISD computer is the most widely used computer model corresponding to serial machines. The other three classes represent parallel-processing types of computers. The SIMD architecture involves multiple processors simultaneously executing the same instruction on different data. "General-purpose" parallel computers are generally reserved for MIMD machines in which each processor fetches its own instruction and operates on its own data. The MISD architecture is often deemed impractical and may represent systolic arrays. The SIMD computing paradigm for distributed-memory parallel machines is well-known for its scalability, data parallelism and high throughput [23] [24] [25] [26]. It will be employed as the underlying architecture for the proposed configurable computing system. Nevertheless, the further development of supercomputers has been recently affected adversely by high prices, long development cycles, difficulties in programming and high maintenance costs [27]. Thus, system architects have been motivated to consider alternatives. An effective approach to this problem is to implement the high-performance computing architecture by employing one or more configurable components because of a significant cost reduction in prototyping and rather efficient execution on the CSOCs. Particularly this is true for platform FPGAs that have capacity of up to 10 million system gates with 90nm VLSI technologies [28].

### 1.1.2 Motivation and Problem Statement

Currently most of the FPGA design tools use a design methodology which fits into the ASIC development model. First, they implement the design using a Hardware Description Language (HDL) and carry out functional simulations; then, logic optimization is employed for logic synthesis and technology mapping; finally, the synthesized design is placed and routed for the vendor's FPGA architecture. Although the ability to program the configurable hardware in such a manner gives the user access to more functionality, it discourages the acceptance of configurable computing platforms due to more arduous design efforts that only a few application designers can deal with. Prior work has taken on this challenge and made some progress. The Garp [29], System C [30], Handle-C [31] and Streams C [32] languages made efforts to extract the hardware realization from a high-level behavioral specification presented in a HLL (such as C/C++). However, the corresponding compilers often require manual hardware/software partitioning which may deteriorate the quality of the results in terms of area, power and system frequency [33]. JBits [34] and JHDL [35] exploit the Java language to facilitate FPGA application development at the hardware level and do not enable high-level synthesis. Additionally, all these tools are difficult to use in exploring the data parallelism inherent in application algorithms.

Another challenge is to bridge bandwidth gaps between the various levels in configurable systems. Generally, there are three types of connections between a host and the CSOCs. First, like the Altera Nios SOPC [36] embedded systems, the CSOCs can serve as functional units tightly coupled with the host processor data path. They could implement an extension of the host processor's ISA (Instruction Set Architecture), such as custom instructions [37] [38]. Second, the CSOCs may be used as coprocessors [29] [39] [40] [41]

which can be larger than a functional unit and less tightly interfaced to the host. They can then provide more resources to take advantage of the existing parallelism in applications. Third, the CSOCs can be used as attached processing units that communicate with the loosely connected host through I/O interfaces [4] [42] [43]. Each scheme has its own pros and cons. The tighter the integration is, the more efficient the communications and yet the fewer the available programmable hardware resources. On the other hand, a more loosely coupled style allows for greater parallelism while it may suffer from higher communication overheads. Extrapolating from Amdahl's Law, the speedup benefits gained from a CSOC implementation can be significantly reduced or even removed if a bandwidth bottleneck exists. Recent work [4] [44] [45] [46] acknowledges the bandwidth bottlenecks in configurable machines, however, without taking them into account in a solution. Usually, either a complete SOC or a reduction in the host access frequency can be employed to solve this problem, but at the expense of lower overall performance. The former solution embeds the host in the CSOC(s), thus increasing tremendously the required configurable resources. The latter can not be applied to applications that require very frequent host accesses.

#### 1.2 Research Objectives

In order to meet the above challenges, the objectives in this dissertation are as follows:

• The notion of a Hierarchical SIMD (H-SIMD) architecture is proposed to facilitate the efficient execution of data-intensive applications on a configurable computer. The target is data-parallel applications. The application is partitioned into different granularities corresponding to the layers in the H-SIMD machine. The enabling SIMD architecture exploits the inherent data parallelism at the application implementation layer. An ISA is to be developed for each application area to facilitate ease of program development and data communication overlapping with

computation operations. This is similar to a technique proposed in [47] for PC clusters.

- The bandwidth bottleneck in the configurable computer is put into perspective. Taking advantage of the hierarchical program coding for H-SIMD, as described above, a memory switching scheme is employed to overlap communications with computations as much as possible. The conditions to achieve a complete overlap are studied for applications running on the H-SIMD machine. This scheme can be applied at run-time, where part of the memory is loaded with new operands while another part is used at that time to run the application.

- An innovative large-sized register file is designed to take advantage of the FPGA

on-chip memory with minimal resource consumption. Thus, more functional units

can fit in a single CSOC as compared to a conventional approach.

- Typical data-intensive applications are implemented on the target Annapolis Wildstar II FPGA board that resides in our laboratory, in order to evaluate the performance of the H-SIMD design methodology. These applications are used widely in engineering and science. The computation time, the consumed FPGA resources and the performance of the H-SIMD machine are measured to facilitate performance comparisons with other computing platforms.

- A HLL-enabled reconfigurable machine is finally used to exploit the available data parallelism in programs with independent functional units and application-specific cache support. The purpose is to demonstrate that the overlapping technique can also be applied to reduce the effect of runtime reconfiguration. For this purpose, a multithreaded overlapping scheme is proposed to reduce as much as possible, or even completely hide, runtime FPGA reconfiguration. High-performance can be achieved

without significant penalty on area and clock frequency. Relevant performance and design tradeoffs are analyzed.

## 1.3 Organization of the Dissertation

Chapter 2 examines state-of-the-art CSOC platforms in detail. Their features and shortcomings for configurable system development are analyzed. Commercial-off-the-Shelf (COTS) platform FPGAs are the chosen research platforms in this dissertation.

Chapter 3 presents the H-SIMD machine and the philosophy for the development of the associated Hierarchical Instruction Set architecture (HISA). Each layer in this hierarchy is studied according to its function and granularity. A memory switching scheme is discussed to overlap communications with computations as much as possible.

Chapter 4 implements three applications on the H-SIMD machine for the purpose of performance evaluation. The three applications are matrix multiplication, 2-dimensional fast Fourier transform and 2-dimensional discrete cosine transform. Test results are presented and analyzed to verify the effectiveness of the proposed H-SIMD machine.

Chapter 5 employs the HLL-enabled SRC-6 reconfigurable machine to exploit the available data parallelism with independent functional units and application-specific cache support. Two important high-performance applications, matrix multiplication and image edge detection, are tested on the SRC-6 machine. The implemented algorithms are able to achieve high-performance without significant penalty on area and clock frequency. Relevant performance and design tradeoffs are analyzed. A multi-threaded overlapping scheme is also proposed to reduce as much as possible, or even completely hide, runtime FPGA reconfiguration.

Chapter 6 draws conclusions and presents future directions.

### **CHAPTER 2**

#### **CSOC PLATFORMS**

Configurable-System-on-a-Chip (CSOC) platforms are the workhorse behind configurable computers. Many projects have been launched to study high-performance architectures for CSOCs. The core technology of CSOCs is generally classified into two categories: COTS FPGAs and custom FPGAs. The former are widely deployed because of their rich resources, low cost and standard development process. Mainstream products in this category are made by leading FPGA companies such as Actel, Altera, Lattice and Xilinx. Although a wide variety of COTS FPGA-based computing platforms have been constructed and reported in the literature, two such systems stand out to exemplify what can be achieved: SPLASH-2 [4] and DECPeRLE [12]. Custom FPGA-based configurable systems are mainly developed in research institutions to customize FPGA techniques for specific applications. Prominent projects in this category include MorphoSys [5], PipeRench [48], MATRIX [49], RAW [50], and Garp [29]. Each of these projects proposes a distinctive framework for configurable hardware/software development.

#### 2.1 COTS FPGA Technology

The FPGA technology was invented in the mid 1980's by Xilinx Inc. and developed rapidly into a mainstream technology. It has evolved from logic glue devices to heterogeneous coarse-grain platform FPGAs. The implementation of IEEE single precision floating-point multipliers on a single FPGA was even impratical in 1994 [51] whereas current state-of-the-art FPGAs can easily implement 32 such functional units in parallel [52]. Since FPGAs were initially designed as bit-level fine-grain devices, a large consumption of logic and routing resources may be required for high bandwidth applications. In order to make up for these disadvantages, platform FPGAs have recently become the focus in this field. These

advanced devices feature coarse-grain components such as built-in hardwired processors (e.g., the IBM PowerPC or ARM core), substantial amount of on-chip SRAM, digital clock management (DCM), and support for some of the latest I/O signaling techniques [28]. This section presents the coarse-grain components which are embedded into Xilinx platform FPGAs, the target of our implementations.

## 2.1.1 On-chip Memory

There are two types of on-chip memory in Xilinx platform FPGAs: distributed SelectRAM and block SelectRAM. According to the Xilinx Virtex-II datasheet [28], there are four slices in each configurable logic block (CLB) and each slice contains two 4-input LUTs (Look-Up Tables), carry logic, arithmetic logic gates, multiplexers, and two flip-flops. LUTs are also referred to as function generators because they can be configured as a 4-inpt LUT, 16 bits of distributed SelectRAM memory, or a 16-bit variable-tap shift register element. The LUT elements within a CLB can be configured to implement memory modules of up to 128 bits. However, the implementation of the distributed SelectRAMs is extremely LUT-consuming because it is done at the fine-grain level. In order to get bigger capacity for on-chip memory without consuming the precious LUT and routing resources, FPGA manufacturers embed coarse-grain block SelectRAMs in platform FPGAs which can be used for large memory storage with the help of a few LUT and routing resources. Xilinx Virtex-II devices, for example, incorporate a large amount of block SelectRAMs containing up to 4704Kbits. These block RAMs supplement the distributed SelectRAMs that consume lots of LUT resources.

Additionally, each Virtex-II block SelectRAM is a true dual-port RAM with two independently clocked and independently controlled synchronous ports that access a common storage area. Both ports are functionally identical. The block SelectRAM diagram is shown in Figure 2.1. The read operation is fully synchronous: the stored data in the given address is loaded into the output register when the rising or falling edge takes

place (depending on the configuration of the clock polarity). A write operation carries out a simultaneous read operation which is performed in one of three configurations [28]: WRITE\_FIRST, READ\_FIRST, or NO\_CHANGE. The WRITE\_FIRST option is a transparent mode; the input data is written into the memory and also transferred into the output register on the same clock edge. The READ\_FIRST option is used to push the prior content of the memory cell to the output register and write the input data into the memory cell on the same clock edge. The NO\_CHANGE option maintains the content of the output register regardless of the write operation. During the NO\_CHANGE mode, only the read operation can change the output register.

Figure 2.1 Virtex II on-chip block SelectRAM memory.

## 2.1.2 Clock Tree Distribution and Management

All platform FPGAs have their own well-designed clock trees, which are used to drive the synchronous components within the chip. Xilinx Virtex-II devices have 16 clock input pins. Eight clock pins are in the upper part of the device while the other eight are located in the lower part. Each Xilinx Virtex-II device is divided into four quadrants: North-West,

.

South-West, North-East, and South-East. The clock distribution is based on a scheme of eight clock trees per quadrant [28].

Clock skew and current driving become major issues due to the long latencies in the clock tree. Correspondingly, platform FPGAs contain a clock buffer and embedded digital clock management modules (DCMs). The clock buffer, such as BUFG, can generate the global clock signal whenever an input signal drives a clock signal or whenever an internal clock signal reaches a certain fanout.

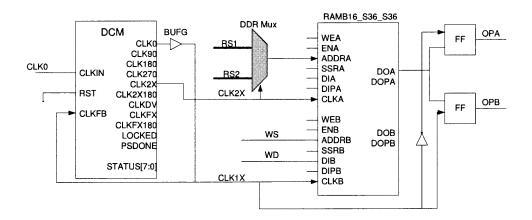

Figure 2.2 Configuration of DCM and BUFG for the clock deskew and current driving.

DCM is another multi-functional clock resource in a platform FPGA [28]. It features de-skew, frequency synthesis and phase shifting functions. The de-skewed clock tree is essential to the functions of all digital circuit designs. Frequency synthesis provides great design flexibility. The phase shifting function is especially useful for multi-chip DDR SRAM burst reading operations. A typical configuration of DCM and BUFG is shown in Figure 2.2. CLK0 is the clock source which is first routed through DCM and then amplified by BUFG. The BUFG output is used to drive the synchronous design inside the FPGAs as well as feed back the DCM component to keep CLK0 and CLK in phase.

## 2.1.3 I/O Technology

In order to meet a wide variety of I/O standards and speed challenges, each user pin on platform FPGAs is programmable for all the frequently-used single-ended or differential-ended I/O standards. In the Xilinx Virtex-II platform FPGA family, 19 single-ended and 6 differential-ended I/O standards are supported such as LVTTL, LVCMOS33, LVCMOS15, LVDS, SSTL, HSTL, GTL+, etc. All these programmable I/O blocks greatly facilitate interface designs. For example, low voltage differential signaling (LVDS) with a double data rate (DDR) register is capable of delivering 840Mbps performance. Each IOB (input-output block) includes six storage elements, as shown in Figure 2.3 [28]. Each storage element can be configured either as an edge-triggered D-type flip-flop or as a level-sensitive latch. On the input, output, and 3-state path, one or two DDR registers are available. The double data rate is directly accomplished by the two registers on each path, clocked by the rising edges (or falling edges) from two different clock nets. The two clock signals are generated by the DCM and must be 180 degrees out of phase. The DDR register splitter/merger is very useful for high-speed data transmission and conserves FPGA pin usage.

**Figure 2.3** Virtex-II IOB diagram.

## 2.1.4 Multiplier

Multiplication is a common arithmetic operation in scientific applications. If conventionally implemented with fine-grain LUTs, a high bandwidth multiplier will consume too many FPGA resources. To avoid this problem, platform FPGA devices feature a large number of embedded high-bandwidth multipliers. For example, there are 144 two's-complement embedded multipliers in Xilinx Virtex-II FPGA devices [28]. These embedded multipliers offer fast, efficient means to create multiplication products for 18-bit signed inputs. Also, cascading the multipliers with additional logic resources can yield larger multipliers of higher bandwidth.

### 2.1.5 Configurable Logic Blocks

The backbone of Xilinx FPGA devices is an array of configurable logic blocks (CLBs). They are used to build combinatorial and synchronous logic designs. Each CLB element is tied to a switch matrix to access the general routing framework and contains four similar slices with fast local feedback within the CLB as shown in Figure 2.4. Each slice includes two 4-input LUTs, carry logic, arithmetic logic gates, multiplexers, and two flip-flops. Each 4-input LUT can be programmed as a 4-input LUT, 16 bits of distributed SelectRAM memory, or a 16-bit variable-tap shift register.

From the above analysis of state-of-the-art programmable technology, the clear trend for COTS CSOCs can be observed: from fine-grain PLDs (Programmable Logic Devices) to heterogeneous coarse-grain platform configurable devices.

## 2.2 COTS FPGA-Based Computing Systems

There is a wide variety of COTS FPGA-based computing systems that have been reported in the literature. TM-2 is based on Altera FPGAs running as an attached functional unit to a SUN workstation [53]. Researchers at Brown University have developed PRISM [54]. Chameleon is based on Algotronix CAL FPGAs [55]. BORG and BORG II are built with

Figure 2.4 Xilinx Virtex-II CLB.

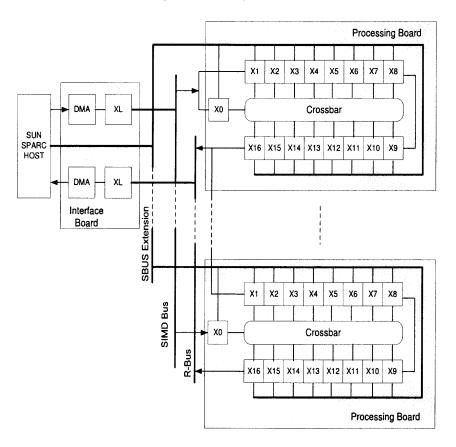

Xilinx FPGAs [56]. SPYDER and RENCO are designed for run-time configuration [11]. Here, the focus is put on SPLASH-2 [4], an exemplary configurable computing system built at the Supercomputer Research Center for defense analysis. The SPLASH-2 system connects Xilinx 4010 FPGAs in a linear systolic array. Figure 2.5 shows a system-level view of the SPLASH-2 architecture. SPLASH-2 is designed as an attached functional unit to the host processor, which is typically a SUN SPARC-II. It is connected to the host through an interface board that extends the address and data buses. The SUN host can access memories and memory-mapped control registers via these buses. Each SPLASH-2 processing board contains 16 Xilinx FPGAs as processing elements (PEs), say X1 - X16. In addition, the 17th Xilinx FPGA (X0) controls the data flow into the processor board. Each PE has 256K 16-bit memory that is also mapped into the address space of the host processor. The PEs are connected through a crossbar that is programmed by X0. The SPLASH-2 system supports several models of computation, including PEs running in the SIMD mode or MIMD mode. SPLASH-2 uses commercial VHDL synthesis tools for

application development. A VHDL model of the complete system is provided that includes all board-level interconnects, memories, and the host interface. Applications are manually partitioned into blocks for each used FPGA. Each block is designed individually, and the integration of the results of all the blocks gives the solution for the application running on SPLASH-2. Significant speedups have been reported for a wide variety of applications, such as image processing [57] [58] and genetic programming [59]. SPLASH-2 has been partially commercialized by Annapolis Micro Systems.

Figure 2.5 SPLASH-2 computing platform (adapted from [4]).

### 2.3 Custom CSOC Studies

Many research projects have proposed uncommon architectures for FPGAs. Most of them have demonstrated performance success for specific applications and favor run-time configurability. Broadly speaking, custom CSOCs can be classified as either coarse-grain or fine-grain. For example, MATRIX [49], PipeRench [48], MorphoSys [5], and RAW [50] are coarse-grain prototypes of configurable computing systems whereas Garp [29] features fine granularity.

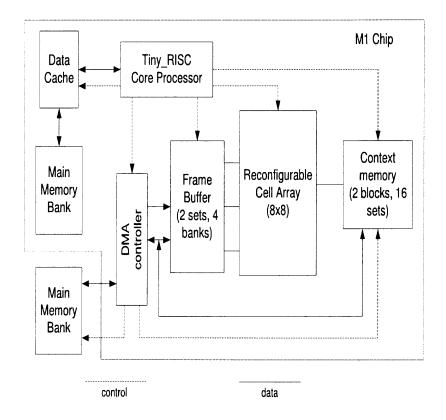

## 2.3.1 MorphoSys

MorphoSys is a novel model for configurable computing targeting applications with inherent data parallelism and high regularity, and high throughput requirements. Examples of such applications are video compression, graphics and image processing, data encryption, and DSP transforms. The MorphoSys architecture is composed of a CSOC, a general-purpose processor, and a high-bandwidth memory interface, as shown in Figure 2.6. Given the nature of the target applications, the configurable component is organized in the SIMD fashion as an array of reconfigurable cells (RCs). Since most of the target applications possess word-level granularity, the RCs are also coarse-grain. The core (RISC) processor controls the operation of the configurable cell array. The high-bandwidth data interface consists of a specialized streaming buffer to handle data transfers between the external memory and the configurable cell array. The intent of the MorphoSys project is to study the viability of the integrated configurable computing model in satisfying the increasing demand for low cost stream or frame data processing needed for data-intensive applications.

## 2.3.2 PipeRench

PipeRench has a striped FPGA architecture suitable for run-time configuration. The striped FPGA differs from traditional FPGAs in two ways. First, PipeRench is configured at a granularity that corresponds to the chosen basic unit of configuration, the pipeline stage. An

Figure 2.6 Components of MorphoSys implementations (adapted from [5]).

on-chip configuration cache allows pipeline stages to be loaded into FPGA cells at a very high speed. Second, the striped FPGA has special interconnects for the implementation of pipelined applications. The most important idea behind this striped architecture is to virtualize an application with v virtual pipeline stages on a device with a capacity of p physical stages (p < v). An FPGA stripe can be configured in one clock cycle from the data stored in a wide, on-chip configuration cache. This provides high speed configuration and allows the unused configuration information to be stored in a single, large on-chip RAM. Modification of the configuration cache can take place concurrently with execution, so there is no hardware constraints to the amount of virtual hardware that can be emulated. This greatly eases compiler development. The compiler begins by reading a description of the architecture from a dataflow intermediate language (DIL) input. PipeRench claims

that its compiler will run two or three orders of magnitude faster than commercial tools because of its deterministic, linear-time, greedy place-and-route algorithm. Yet, designed as an attached coprocessor, PipeRench has limited bandwidth between the main memory and the processor. This places significant limitations on the types of applications that can realize a speedup.

## **2.3.3 MATRIX**

The MATRIX architecture proposes the design of a basic functional unit (BFU) for a configurable system. MATRIX is composed of an array of identical, 8-bit BFUs overlaid with a configurable network. The coarse-grain 8-bit BFUs contain a 256 × 8 memory, an 8-bit ALU and reduction control logic including a 20 × 8bit NOR plane. The BFUs assume a three-level interconnection network and may be configured for operation in the VLIW (Very Long Instruction Word) or SIMD fashion. The configurable network is a hierarchical collection of 8-bit busses for both data and instruction distribution. Unlike traditional FPGA interconnects, MATRIX has the option to dynamically switch the network connections. The MATRIX port configuration is one of the keys to the architecture's flexibility. Each port in MATRIX can be configured in one of three modes: the static value mode, static source mode, and dynamic source mode. These modes are useful for dataflow or control flow to BFUs. The 100MHz frequency was estimated for the prototype MATRIX chip since a complete system organization based on the BFU is not available yet. The MATRIX approach is too generic and at least one potential problem is the complexity and overhead of the BFU control unit.

#### 2.3.4 RAW

This design implements a highly parallel architecture in the form of a Reconfigurable Architecture Workstation (RAW). The architecture is organized in the MIMD manner with multiple instruction streams. It has multiple RISC processors, each having fine-grain

logic as the configurable component. RAW exposes wire delays at the ISA level. This allows the compiler to explicitly manage gates in a scalable fashion. RAW provides a direct, parallel interface to all of the chip resources: gates, wires, and pins. However, the architecture has a distributed nature and the RISC processors do not exhibit the close coupling present in the RC Array elements. This may have an adverse effect on the performance for high-throughput applications that involve many data exchanges.

## 2.3.5 Garp

Garp is the architecture of a general-purpose processor tightly coupled with a configurable array. The loading and execution of configurations on the configurable array is always under the control of a program running on the main processor. The main processor is a modified MIPS-II processor whose floating-point unit is replaced with a configurable array. Garp's goal is to execute data-intensive operations on the configurable array and leave general-purpose operations to the processor. Garp's configurable array is composed of entities called blocks. One block on each row is known as a control block. The rest of the blocks in the array are logic blocks that correspond roughly to the CLBs of the Xilinx Virtex series. Software tools have been created that make it possible to write C programs for Garp and then simulate them with approximate clock-cycle accuracy. The major constraint on Garp is the limited amount of configurable resources that can only speedup the application by implementing custom instructions. Table 2.1 summarizes the characteristics of the CSOCs described in this section.

Table 2.1 Comparison of Configurable Systems

|                 | COTS | Granularity | Contexts | Run-time configuration |

|-----------------|------|-------------|----------|------------------------|

| Commercial FPGA | Yes  | Fine        | Single   | Dynamic/static         |

| MorphoSys       | No   | Coarse      | Multiple | Dynamic                |

| MATRIX          | No   | Coarse      | Multiple | Dynamic                |

| PipeRench       | No   | Coarse      | Multiple | Dynamic                |

| RAW             | No   | Coarse      | Single   | Static                 |

| Garp            | No   | Fine        | Multiple | Static                 |

## **CHAPTER 3**

## THE H-SIMD MACHINE

Several applications that became mainstream in the last decade are characterized by their need for high throughput and data-intensive computations. Such examples are automatic target recognition [5], power-flow solution [60], digital processing [61], and image processing [19]. For this reason, mainstream computer architecture designs have become performance-driven. Many such tasks that are data-intensive can be performed efficiently on SIMD architectures. This trend can be seen even in the Intel Pentium series processors, and Motorola's MPC7400 and Sony's Playstation2 [62]. Additionally, VLSI technology has made such big progress that systems involving dozens of boards a few decades ago can now fit in a single chip. On the other hand, the NRE cost of SOC solutions is so prohibitive that many designs need to hedge the risks [63]. As COTS FPGAs continue to grow in size and complexity, they provide an ideal configurable and cost-efficient solution for prototyping, and even implementing custom parallel computing architectures. This chapter presents the H-SIMD hierarchical architecture and its building blocks for data-intensive applications.

## 3.1 The H-SIMD Machine

The H-SIMD machine is designed to aid in the task of programming applications targeting configurable systems and attempting to fully overlap communications with computations. Therefore, ease of programming and high performance can be achieved.

H-SIMD consists of two parts: the host PC and the CSOC array. The former is in charge of task partitioning and is programmed with high-level languages such as C/C++ while the latter is designed to speed up the computation-intensive parts in the applications.

The SIMD architecture exploits the inherent data parallelism in the corresponding algorithms.

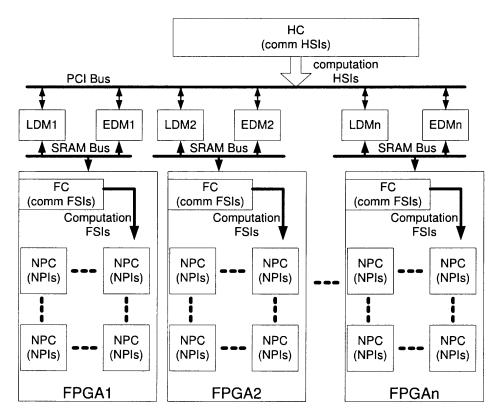

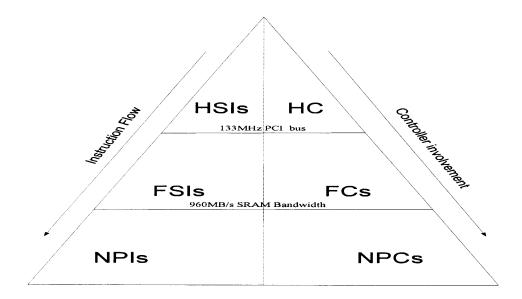

# 3.1.1 H-SIMD Architecture

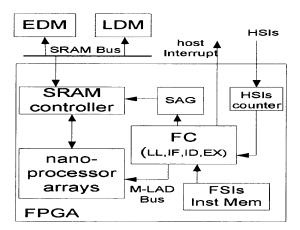

The H-SIMD control hierarchy is composed of three layers, as shown in Figure 3.1. It comprises the host controller (HC), the FPGA controllers (FCs), and the nano-processor controllers (NPCs). The HC lies in the host machine and controls all the FPGA chips in the SIMD mode. Inside each FPGA, an FC is designed to run all the on-chip NPCs in the SIMD mode as well. The NPCs control the execution of machine-level code. Similar to the approach for PC clusters in [47], an effective instruction set architecture (ISA) needs to be developed at each layer for each application domain. Therefore, a hierarchical instruction set architecture (HISA) is created to facilitate the logical interconnection of the three layers. This allows to logically partition the application into the HC, FC, and NPC layers that can be handled efficiently at run time to balance the pipeline running from the host down to the on-chip nano-processors. Task scheduling and the coarse-grain dataflow control of the application are left to the HC.

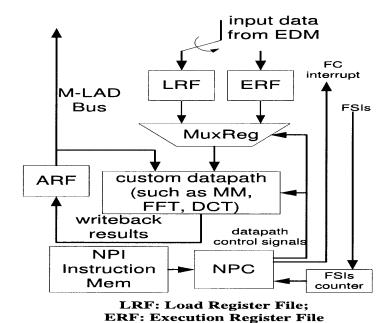

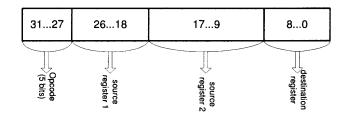

HISA instructions are classified into communication instructions and computation instructions. The former are executed by the local controller while the latter are issued to the lower level. As shown in Figure 3.2, the HC runs the coarse-grain host SIMD instructions (HSIs) which are classified into host-FPGA communication HSIs and time-consuming computation HSIs. The HC executes the communication HSIs only and issues the computation HSIs to the FCs to execute. Inside each FPGA, the FC further decomposes the received computation HSIs into a sequence of medium-grain FPGA SIMD instructions (FSIs). The FC runs them in a manner similar to the HC: executing the communication FSIs and issuing the computation FSIs to the nano-processor array. The NPCs finally decode the received computation FSIs into fine-grain nano-processor instructions (NPIs)

and then sequence them for execution. Additionally, the HC, the FCs, and the NPCs run at different frequencies. The HC is the slowest component while the NPCs are the fastest.

The H-SIMD machine configures one of the FPGA chips as the master FPGA which is responsible for sending an interrupt signal back to the HC once the previously executed HSI has been completed at the FPGA level. Similarly, one NP within each FPGA is configured as the master NP that sends an interrupt signal back to its FC so that a new FSI can be issued. The combination of the HC and FCs, however, is different from the conventional SIMD controller scheme because the former does not actually monitor the execution. Decentralized control in the H-SIMD machine allows the execution of instructions at one layer to be transparent to higher layer(s). On the contrary, centralized control requires the handling of pipeline stalls and exceptions. It is one of the most complex parts in the design and is very hard to be scalable. To summarize, the control flow in the H-SIMD machine is two-way asynchronous instead of the conventional one-way synchronous.

## 3.1.2 Memory Switching Schemes

The communication overhead between the host and the FPGA cluster is very high due to the nature of the non-preemptive operating system on the host. Based on tests in our laboratory, the one-time interrupt latency for a Windows-XP installed Dell Precision 650 host workstation running the PCI bus at 66MHz is about 5 ms. This penalty is intolerable in high-performance computing because, for example,  $60 \times 60$  floating-point matrix multiplication takes about 1.3 ms on a single MAC (multiply accumulator) running at 160 MHz (which is within range of current FPGA technology) [64] [65]. If the host frequently intervenes in FPGA operations, the speedup benefits gained from the parallel FPGA implementation can be significantly reduced or even removed. Thus, a design objective of the H-SIMD machine is to hide host communication latencies. Yet, given the system configuration of the host machine, the latency is fixed and cannot be reduced unless a

EDM: execution data memory; LDM: loaded data memory

Figure 3.1 H-SIMD machine architecture.

preemptive operating system or special PCI hardware interface are enlisted. In order to overcome the latency problem, a data prefetching scheme involving memory switching is designed for the H-SIMD machine to overlap communications with computations as much as possible.

The HC-level memory switching scheme is shown in Figure 3.3. The SRAM banks on the FPGA board are organized into two functional memory units: the execution data memory (EDM) and the loaded data memory (LDM). Both the EDMs and LDMs are functionally interchangeable. At one time, the FCs access the EDMs to fetch operands for the execution of received computation HSIs while the LDMs are referenced by the host for the execution of communication HSIs. When the FCs finish their current computation

Figure 3.2 The HISA ISA for the H-SIMD architecture.

HSI, they will switch between the EDM and LDM to begin a new iteration. The FC is a finite-state machine responsible for the execution of the computation HSI. The FCs have access to the NP array over a modified LAD (M-LAD) bus. The LAD bus was originally developed by the Annapolis company and used for on-chip memory references [42]. The M-LAD bus controller is changed from the PCI controller to the FCs. The HSI counter is used to calculate the number of finished computation HSIs. The SRAM address generator (SAG) is used to calculate the SRAM load/store addresses for the EDM banks. The FC is pipelined and sequentially traverses the states LL (Load LRFs), IF (Instruction Fetch), ID (Instruction Decode), and EX (Execute). The transition condition from EX to LL is triggered by the master NP's interrupt signal. The interrupt request/response latency is one cycle only as opposed to the tens of thousands of cycles between the host and FPGAs, thus enhancing the H-SIMD's performance.

The nano-processors (NPs) form the execution units of the H-SIMD machine datapath. Their functionality can be customized according to the application. The NPs reside at the lowest layer of the H-SIMD machine hierarchy. Each nano-processor has

two large-sized register files: the load register file (LRF) and the execution register file (ERF) as shown in Figure 3.4. Both register files work in a "memory" switching capacity, similarly to the LDMs and EDMs; i.e., they alternate the execution of FSIs with data loading from the FCs. After the nano-processor finishes data processing with the ERF, its datapath will configure another LRF as an ERF and will then begin a new program flow. At the same time, the just switched-out ERFs will be configured as LRFs to be loaded with new operands from the EDMs controlled by the FCs; these operands will then be ready to be processed. The benefits are obvious here: the "memory" switching scheme involving the register files and the SRAM modules can be used to highly or completely overlap communications with computations. Additionally, the large-sized register file reduces significantly the frequency of nano-processor load/store operations and can get rid of a nano-processor's local data memory. This way, higher performance and the conservation of hardware resources can be achieved.

**Figure 3.3** HC-level memory switching in H-SIMD.

Figure 3.4 Nano-processor datapath and control unit.

## 3.1.3 H-SIMD Machine Features

The H-SIMD machine's programming capabilities are based on the HISA hierarchy. Much research has shown the big challenges in bridging bandwidth gaps for loosely coupled configurable computing systems [29] [41] [66]. [66] presented a hybrid system architecture model for bridging such gaps in configurable computing systems; it is a heterogeneous system-on-chip platform. [29] demonstrated the usefulness and effectiveness of tightly coupled processing between the microprocessor and the configurable logic array. The H-SIMD machine is designed to meet such challenges in loosely coupled host-CSOC systems.

Based on Amdahl's Law, the overall speedup gained by employing a configurable computing system diminishes if the bandwidth between the host and the configurable computing system becomes a bottleneck. The H-SIMD machine assumes a conventional host and a CSOC array; the latter is implemented with FPGAs. In general, this model

consists of a general-purpose host, a configurable logic array, on-chip memory, off-chip memory, and an interconnection network. At each level, significant speedups are only achieved with configurations where the time to execute the computation instructions is relatively large compared to the overhead required for the communication instructions. To quantify this relative measure, one must consider the following equations:

$$T_{H\_exe} = T_{H\_comp} + (1 - \alpha_H)T_{H\_comm} \tag{3.1}$$

$$T_{F\_exe} = T_{F\_comp} + (1 - \alpha_F)T_{F\_comm} \tag{3.2}$$

$$T_{H\_comp} = T_{F\_exe} \tag{3.3}$$

where  $T_{H\_exe}$  and  $T_{F\_exe}$  are the execution times for the host and the FPGAs, respectively;  $T_{H\_comp}$  and  $T_{F\_comp}$  are the times spent for computations by the host and the FPGAs, respectively;  $T_{H\_comm}$  and  $T_{F\_comm}$  represent the times for communication instructions running on the host and the FPGAs, respectively;  $\alpha_H$  and  $\alpha_F$  are assumed to represent the overlap factors for such instructions involving the host and the FPGA levels, respectively. The overlap factors indicate the degree of overlap between computations and communications, and their range is  $0 \le \alpha_H \le 1$  and  $0 \le \alpha_F \le 1$ . The speedup on the H-SIMD machine over a traditional software implementation is expressed as:

$$speedup = \frac{T_{soft}}{T_{H,exe}} > 1 \tag{3.4}$$

where  $T_{soft}$  is the time to execute the function in software running on the host. Equations 3.1, 3.2, 3.3 and 3.4 imply that the following condition must be met for any speedup (> 1) to occur on the H-SIMD machine:

$$\frac{T_{F\_comp}}{T_{soft}} + (1 - \alpha_F) \frac{T_{F\_comm}}{T_{soft}} + (1 - \alpha_H) \frac{T_{H\_comm}}{T_{soft}} < 1$$

(3.5)

The first fraction represents the inverse of the ideal speedup without any overheads; the second and third terms are indicative of the percentage of communication overheads that diminish the speedup. The sum of the three fractions is indicative of the overall speedup: the smaller this sum, the larger the overall speedup for a particular application on the H-SIMD machine. The potential overlaps discussed earlier for program execution on the H-SIMD machine can improve the overall speedup as confirmed by Amdahl's Law: if an enhancement is only usable for a fraction of an application, we cannot expect a speedup by more than the reciprocal of 1 minus that fraction [67].

# 3.2 Size-Adjustable Register File Design

The H-SIMD machine is implemented on the Xilinx Virtex-II FPGAs in the target Annapolis Wildstar II FPGA board [42]. The number of nano-processors (NPs) in the H-SIMD machine is determined each time by the available FPGA resources for the running application. Each NP's datapath is comprised of the register file, custom datapath, and data memory I/O interface. In a conventional way, the register file is designed with HDL and mapped onto FPGA LUTs. A 32-bit register, however, is inefficiently mapped onto LUTs. Test results are shown in Table 3.1. 0.5% of the LUT resources are used for 32 registers. 29% of the LUTs are used by the 512-register configuration, and thus it is impossible to deploy more than three such register files in one FPGA chip. In the H-SIMD machine, however, a large-sized register file is preferred in order to reduce the number of load/store operations and simultaneously fit many functional units.

Here, a size-adjustable register file is designed with even less consumption of LUT resources. In fact, the number of registers is scalable ranging from 16 to 512. This range meets the requirements of various applications. This design exploits the dual-port block SelectRAMs and the DCM inside the platform FPGA upon which the NP register file is built. In the Xilinx Virtex-II FPGA devices [28], there are 144 18Kbit dual-port BlockRAM (BRAM) cells which are customized as coarse-grain components. The designed register file

Figure 3.5 Dual-port BRAM-based size-adjustable register file.

diagram is shown in Figure 3.5. One port of the BRAM is used as the writeback port from the NP datapath; the other is used as the output to furnish two operands to the FPU in each cycle. Generally, one port of the BRAM can load one addressed item into the output register in each cycle. But the FPU input requires two operands in each cycle. In order to solve this problem, the register file design takes advantage of the double-speed synchronous clock from the DCM. Two synchronous clocks are used to drive each port. The clock for driving the output operands to the FPU is twice as fast as the one for writing back data which is also identical to the system clock. Once the serialized operands are available on the output port, they are split into two operand streams for datapath execution. With this register file design, one data result from the datapath can be written into the register file and two operands can be read out within one system cycle. Additionally, the write mode of the BRAM cell for the register file is configured as "Write First" (or "Read after Write"), that is, the write data is loaded simultaneously into the output port as well as written into the addressed storage cell. If one port attempts a read of a memory cell while the other one simultaneously writes into that cell, and the clocks of the two ports violate the clock-to-clock setup requirement, then a location conflict occurs and the following policy takes effect [28]:

- The write succeeds.

- The data out on the writing port accurately reflects the data written.

- The data out on the reading port is invalid.

- Conflicts do not cause any physical damage.

The above conflict resolution may result in a Read-After-Write (RAW) data hazard, which has been taken care of by the pipeline forward unit. As shown in Table 3.1, the dual-clock register file design results in a large-sized register file with the smallest LUT consumption.

Table 3.1 FPGA Resource Consumption for Different Types of Register File Designs

|                       | Size | BlockRAM | LUTs*      |

|-----------------------|------|----------|------------|

| Case 1 (conventional) | 32   | 0        | 392(0.5%)  |

| Case 2 (conventional) | 512  | 0        | 19663(29%) |

| Case 3 (Dual-Clock)   | 512  | 1        | 80(0.1%)   |

<sup>\*</sup>Total LUTs: 67584

#### **CHAPTER 4**

## CASE STUDIES ON THE H-SIMD MACHINE

Case studies are shown in this chapter for the purpose of performance evaluation. The implementation and related experimental results are described for matrix multiplication (MM), 2-dimensional fast Fourier transform (2D FFT), and 2-dimensional discrete cosine transform (2D DCT). These applications are representative of data-intensive computations and are used widely in engineering and science.

## 4.1 Example 1: Matrix Multiplication

Matrix multiplication (MM) is used widely in scientific and engineering computations where matrix operations are rich [68]. In this section, the development of MM on the H-SIMD machine is presented.

# 4.1.1 HSIs, FSIs, and NPIs for MM [1]

The HC is programmed using the host API functions for the FPGA board. They are to set up the board, configure the FPGAs, reference the on-board/on-chip memory resources, and handle interrupts [42]. The tailoring of the HSIs for the block-based MM algorithm is presented here. Assume the problem C = A \* B, where A, B, and C are  $N \times N$  square matrices. When N becomes large, block matrix multiplication is used to divide the matrix into smaller blocks to exploit data reusability. Then, the multiplication of these smaller matrix blocks is performed on the FPGA array. In the H-SIMD machine, only a single FPGA or NP is employed to multiply and accumulate the results of one block of the product matrix at the HC and FC levels, respectively. Coarse-grain workloads can keep the NPs busy on MM computations while the HC and FCs load operands into the FPGAs and NPs sequentially. This simplifies the design of the hierarchical architecture and eliminates the need for inter-FPGA and inter-NP communications at the expense of extra memory

reference time. According to the H-SIMD architecture, the HC issues  $N_h \times N_h$  sub-matrix blocks to all the FPGAs to multiply.  $N_h$  is the block matrix size for the HSIs. Three HSIs are designed:

- $host\_matrix\_load(i, S_{LDM}, N_h)$ : Through the PCI bus, this HSI will load an  $N_h \times N_h$  matrix block into the LDM of FPGA i with the starting address  $S_{LDM}$  in the host memory (host-based DMA control is applied).

- $host\_matrix\_store(i, S_{LDM}, N_h)$ : The computation results in the LDM of FPGA i can be retrieved by the host through the PCI bus when the computation is done.  $host\_matrix\_load/store$  are communication HSIs executed on the host.

- $host\_matrix\_mul\_accum(H_A, H_B, H_C, N_h)$ : For matrix multiplication of size  $N_h \times N_h$ ,  $H_A$ ,  $H_B$  and  $H_C$  are the starting addresses of source matrix A, source matrix B and product accumulation matrix C, respectively. This computation HSI is coded in 32 bits, issued by the HC and executed by the FCs.

The FC is in charge of executing the computation HSIs. It will decompose the operation corresponding to  $host\_matrix\_mul\_accum$  for size  $N_h \times N_h$  into FSIs for size  $N_f \times N_f$ , where  $N_f$  is the sub-block matrix size for the FSIs. Enlisted is the same block matrix multiplication algorithm as the one for the HC. The  $host\_matrix\_mul\_accum$  code is pre-programmed in the form of FSIs and is stored into the FC instruction memory. The FSIs are 32-bit instructions with mnemonics as follows:

- $FPGA\_matrix\_load(i, S_{LRF}, N_f)$ : the FC will execute this instruction by loading the LRF of NP i with a matrix of size  $N_f \times N_f$ .  $S_{LRF}$  is the starting address in the EDM.

- $FPGA\_matrix\_store(i, S_{ARF}, N_f)$ : The NP computation results are stored into the accumulation register file (ARF) and retrieved into the FPGA's EDM at starting address  $S_{ARF}$  when the accumulation of the partial products is done.  $FPGA\_matrix\_load/store$  are communication FSIs executed by the FCs.

- $FPGA\_matrix\_mul\_accum(F_a, F_b, F_c, N_f)$ : For matrix multiplication of size  $N_f \times N_f$ ,  $F_a$ ,  $F_b$  and  $F_c$  are the starting addresses of source matrix a, source matrix b and product accumulation matrix c, respectively. This computation FSI is issued by the FCs and executed by the NPCs.

The NPIs are designed for the execution of the computation FSI  $FPGA\_matrix\_mul$   $\_accum$ . The code for  $FPGA\_matrix\_mul\_accum$  is pre-programmed by the NPIs and stored into the NPC instruction memory. There is only one NPI to be implemented for MM, corresponding to floating-point multiply accumulation:  $NP\_MAC(R_{s1}, R_{s2}, R_d)$ , where  $R_{s1}$ ,  $R_{s2}$ , and  $R_d$  are registers for the function  $R_d = R_{s1} * R_{s2} + R_d$ . The NPI code for the computation FSIs needs to be scheduled carefully to avoid data hazards. They occur when operands are delayed in the addition pipeline with latency  $L_{adder}$ . Thus, the condition to avoid data hazards is  $N_f^2 > L_{adder}$ .

## 4.1.2 General-purpose Nano-processor ISA

In order to exploit the configurability of the FPGAs, additional general-purpose NPIs are developed to augment the general-purpose scientific computations on the H-SIMD machine. Their implementation is based on a tradeoff between application demands and FPGA resource consumption. All these instructions are listed in Table 4.1.

Arithmetic Instructions The arithmetic instructions  $NP\_MAC/ADD/SUB/PSUB/MUL/DIV$  include MAC, addition, subtraction, absolute value subtraction, multiplication, and division. They are executed on the SIMD NP array. Division is very expensive not only in execution cycles but also in FPGA resource consumption. If the division operation is very rare in the application algorithms, only one NP is configured with a divider circuit.

**Routing Instructions** The SIMD nano-processor array needs to communicate values between the NPs. Based on the NEWS grid interconnection [46], the data needed by an NP can be routed from its north/east/west/south neighbors by using an NR/ER/WR/SR instruction.

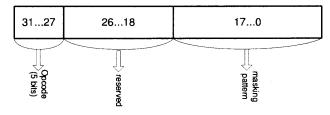

Mask Instruction The same operation is normally applied to all the NPs simultaneously in the SIMD architecture. There are ways to nullify the effects of an instruction on the

selected NPs. The mask instruction can be used to load a masking pattern into each NP's mask bit in order to enable/disable the NP.

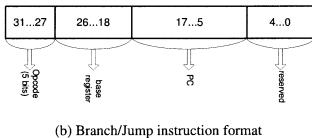

**Branch Instruction** There are two branch instructions: conditional and unconditional.  $BR_{-}P$  is a conditional branch instruction which puts a new instruction address into the Program Counter (PC) if the content of the source register is greater than zero. JMP is an unconditional branch instruction that puts a new value directly into the PC.