## **Copyright Warning & Restrictions**

The copyright law of the United States (Title 17, United States Code) governs the making of photocopies or other reproductions of copyrighted material.

Under certain conditions specified in the law, libraries and archives are authorized to furnish a photocopy or other reproduction. One of these specified conditions is that the photocopy or reproduction is not to be "used for any purpose other than private study, scholarship, or research." If a, user makes a request for, or later uses, a photocopy or reproduction for purposes in excess of "fair use" that user may be liable for copyright infringement,

This institution reserves the right to refuse to accept a copying order if, in its judgment, fulfillment of the order would involve violation of copyright law.

Please Note: The author retains the copyright while the New Jersey Institute of Technology reserves the right to distribute this thesis or dissertation

Printing note: If you do not wish to print this page, then select "Pages from: first page # to: last page #" on the print dialog screen

The Van Houten library has removed some of the personal information and all signatures from the approval page and biographical sketches of theses and dissertations in order to protect the identity of NJIT graduates and faculty.

#### **ABSTRACT**

## DESIGN AND RESOURCE MANAGEMENT OF RECONFIGURABLE MULTIPROCESSORS FOR DATA-PARALLEL APPLICATIONS

#### by Xiaofang Wang

FPGA (Field-Programmable Gate Array)-based custom reconfigurable computing machines have established themselves as low-cost and low-risk alternatives to ASIC (Application-Specific Integrated Circuit) implementations and general-purpose microprocessors in accelerating a wide range of computation-intensive applications. Most often they are *Application-Specific Programmable Circuits* (ASPCs), which are developer programmable instead of user programmable. The major disadvantages of ASPCs are minimal programmability, and significant time and energy overheads caused by required hardware reconfiguration when the problem size outnumbers the available reconfigurable resources; these problems are expected to become more serious with increases in the FPGA chip size. On the other hand, dominant high-performance computing systems, such as PC clusters and SMPs (Symmetric Multiprocessors), suffer from high communication latencies and/or scalability problems.

This research introduces low-cost, user-programmable and reconfigurable *MultiProcessor-on-a-Programmable-Chip* (*MPoPC*) systems for high-performance, low-cost computing. It also proposes a relevant resource management framework that deals with performance, power consumption and energy issues. These semi-customized systems reduce significantly runtime device reconfiguration by employing user-programmable processing elements that are reusable for different tasks in large, complex applications. For the sake of illustration, two different types of MPoPCs with hardware *FPUs* (*floating-point units*) are designed and implemented for credible performance evaluation and modeling: the coarse-grain MIMD (Multiple-Instruction,

Multiple-Data) CG-MPoPC machine based on a processor IP (Intellectual Property) core and the mixed-mode (MIMD, SIMD or M-SIMD) variant-grain HERA (*HEterogeneous Reconfigurable Architecture*) machine. In addition to alleviating the above difficulties, MPoPCs can offer several performance and energy advantages to our data-parallel applications when compared to ASPCs; they are simpler and more scalable, and have less verification time and cost. Various common computation-intensive benchmark algorithms, such as matrix-matrix multiplication (MMM) and LU factorization, are studied and their parallel solutions are shown for the two MPoPCs. The performance is evaluated with large sparse real-world matrices primarily from power engineering. We expect even further performance gains on MPoPCs in the near future by employing ever improving FPGAs. The innovative nature of this work has the potential to guide research in this arising field of high-performance, low-cost reconfigurable computing.

The largest advantage of reconfigurable logic lies in its large degree of hardware customization and reconfiguration which allows reusing the resources to match the computation and communication needs of applications. Therefore, a major effort in the presented design methodology for mixed-mode MPoPCs, like HERA, is devoted to effective resource management. A two-phase approach is applied. A mixed-mode weighted Task Flow Graph (w-TFG) is first constructed for any given application, where tasks are classified according to their most appropriate computing mode (e.g., SIMD or MIMD). At compile time, an architecture is customized and synthesized for the TFG using an Integer Linear Programming (ILP) formulation and a parameterized hardware component library. Various run-time scheduling schemes with different performance-energy objectives are proposed. A system-level energy model for HERA, which is based on low-level implementation data and run-time statistics, is proposed to guide performance-energy trade-off decisions. A parallel power flow analysis technique based on Newton's method is proposed and employed to verify the methodology.

## DESIGN AND RESOURCE MANAGEMENT OF RECONFIGURABLE MULTIPROCESSORS FOR DATA-PARALLEL APPLICATIONS

by Xiaofang Wang

A Dissertation

Submitted to the Faculty of

New Jersey Institute of Technology

in Partial Fulfillment of the Requirements for the Degree of

Doctor of Philosophy in Computer Engineering

Department of Electrical and Computer Engineering, NJIT

January 2006

Copyright © 2006 by Xiaofang Wang

ALL RIGHTS RESERVED

## **APPROVAL PAGE**

# DESIGN AND RESOURCE MANAGEMENT OF RECONFIGURABLE MULTIPROCESSORS FOR DATA-PARALLEL APPLICATIONS

## **Xiaofang Wang**

| Dr. Sotirios G. Ziavras, Dissertation Advisor and Committee Chair<br>Professor of Electrical and Computer Engineering, NJIT | Date' |

|-----------------------------------------------------------------------------------------------------------------------------|-------|

| Dr. Alexandros V. Gerbessiotis, Committee Member<br>Associate Professor of Computer Science, NJIT                           | Date  |

| Dr. Jie Hu, Committee Member<br>Assistant Professor of Electrical and Computer Engineering, NJIT                            | Date  |

| Dr. Durgamadhab Misra, Committee Member Professor of Electrical and Computer Engineering, NJIT                              | Date  |

| Dr. Roberto Rojas-Cessa, Committee Member Assistant Professor of Electrical and Computer Engineering, NJIT                  | Date  |

#### BIOGRAPHICAL SKETCH

Author: Xiaofang (Maggie) Wang

**Degree:** Doctor of Philosophy

Major: Computer Engineering

#### **Undergraduate and Graduate Education:**

• Doctor of Philosophy in Computer Engineering, New Jersey Institute of Technology, Newark, NJ, January 2006.

- Master of Science in Electrical Engineering,

Beijing University of Technology (formerly Beijing Polytechnic University),

Beijing, P. R. China, 1994.

- Bachelor of Science in Microelectronics, Nankai University, Tianjin, P. R. China, 1991.

#### **Publications:**

X. Wang and S. G. Ziavras,

"Exploiting Mixed-Mode Parallelism for Matrix Operations on the HERA Architecture through Reconfiguration,"

IEE Proceedings, Computers and Digital Techniques, accepted in 2005.

X. Wang and S. G. Ziavras,

"A Multiprocessor-on-a-Programmable-Chip Reconfigurable System for Matrix Operations with Power-Grid Case Studies,"

International Journal of Computational Science and Engineering, Special Issue on Parallel and Distributed Scientific and Engineering Computing, accepted in 2005.

X. Wang and S. G. Ziavras,

"Parallel LU Factorization of Sparse Matrices on FPGA-Based Configurable Computing Engines,"

Concurrency and Computation: Practice and Experience, Vol. 16, No. 4, pp. 319-343, 2004.

X. Wang, S. G. Ziavras, and J. Hu,

"Energy-Performance Optimization through Resource Management in Reconfigurable Mixed-Mode Single-Chip Multiprocessors," submitted in December 2005.

X. Wang and S. G. Ziavras,

"A Framework for Dynamic Resource Management and Scheduling on Reconfigurable Mixed-Mode Multiprocessors,"

IEEE International Conference on Field-Programmable Technology (FPT'05), Singapore, Dec. 11-14, 2005.

X. Wang and S. G. Ziavras,

"Adaptive Scheduling of Array-Intensive Applications on Mixed-Mode Reconfigurable Multiprocessors,"

IEEE 39th Asilomar Conference on Signals, Systems, and Computers, Pacific Grove, California, Oct. 30-Nov.2, 2005.

S. G. Ziavras, X. Wang, and M. Z. Hasan,

"Intra- and Inter-FPGA Programmable Multiprocessor Designs with Emphasis on Large-Scale Matrix Operations,"

Workshop on Architecture Research using FPGA Platforms (in conjunction with the 11<sup>th</sup> International Symposium on High-Performance Computer Architecture), February 2005.

X. Wang and S. G. Ziavras,

"Mixed-Mode Scheduling for Parallel LU Factorization of Sparse Matrices on the Reconfigurable HERA Computer,"

International Conference on Advances in Computer Science and Technology (ACST 2004), St. Thomas, U.S. Virgin Islands, November 2004.

X. Wang and S. G. Ziavras,

"HERA: A Reconfigurable and Mixed-Mode Parallel Computing Engine on Platform FPGAs," *The 16th International Conference on Parallel and Distributed Computing and Systems* (PDCS 2004), MIT, Cambridge, MA, November 9-11, 2004.

X. Wang and S. G. Ziavras,

"A Configurable Multiprocessor and Dynamic Load Balancing for Parallel LU Factorization,"

The 5<sup>th</sup> Workshop on Parallel and Distributed Scientific and Engineering (Proc. of the 18<sup>th</sup> IEEE International Parallel and Distributed Processing Symposium (IPDPS2004)), Santa Fe, New Mexico, April 2004.

X. Wang and S. G. Ziavras,

"Performance Optimization of an FPGA-Based Configurable Multiprocessor for Matrix Applications,"

IEEE International Conference on Field-Programmable Technology (FPT'03), pp. 303-306, Dec. 2003.

X. Wang and S. G. Ziavras,

"Parallel Direct Solution of Linear Equations on FPGA-Based Machines,"

The 11<sup>th</sup> Workshop on Parallel and Distributed Real-Time Systems (Proc. of the 17<sup>th</sup> IEEE International Parallel and Distributed Processing Symposium (IPDPS2003)), Nice, France, pp. 113-120, April 22-26, 2003.

## X. Wang, S. G. Ziavras, and J. Savir,

"Efficient LU Factorization on FPGA-Based Machines," The 7th International Multi-Conference on Power and Energy Systems, Palm Springs, CA, pp. 459-464, February 2003. To my beloved parents and husband.

#### **ACKNOWLEDGMENT**

As an international student, I have been very fortunate to get help from many people in many aspects during this important and rewarding phase of my professional life. I thank all of them.

In particular, I would like to express my deepest and sincere gratitude to my dissertation advisor, Dr. Sotirios G. Ziavras, for many things: his constant encouragement strengthened me in delving into this research and finding solutions when I was confused; his great insight and perspectives inspired me toward completing successfully this thesis; he spent countless hours on advisement, discussion, and revising our papers; he was always there when I had a problem to discuss; ... What I have learned from him will benefit me in my lifetime as a professional. Special thanks are also given to the other members of my dissertation committee, Dr. Alexandros V. Gerbessiotis, Dr. Jie Hu, Dr. Durga Misra and Dr. Roberto Rojas-Cessa, for their suggestions, comments and beneficial discussions.

I am grateful to several funding sources that supported my Ph.D work. They involve a *Teaching Assistant* position in the ECE department at NJIT, multi-year research grants for the U. S. Dept. of Energy *PowerGrid* project, and the ECE *Phonetel* and *Hashimoto Fellowships*.

The valuable and prompt support from Altera and Xilinx engineers during my implementation of the multiprocessors is highly appreciated.

My father always encouraged me to challenge my talents and to pursue the Ph.D. degree. Finally, I am very happy in fulfilling his hope and making him happy.

## TABLE OF CONTENTS

| C | hapter                                                    | Page |

|---|-----------------------------------------------------------|------|

| 1 | INTRODUCTION                                              | . 1  |

|   | 1.1 High-Performance Applications                         | . 1  |

|   | 1.2 Current High-Performance Computing Systems            | 1    |

|   | 1.2.1 Proprietary Supercomputers                          | . 2  |

|   | 1.2.2 Shared-Memory Multiprocessors                       | . 3  |

|   | 1.2.3 Message-Passing Multicomputers                      | 5    |

|   | 1.2.4 Distributed Shared-Memory Multicomputers            | . 5  |

|   | 1.2.5 Cluster-Based Computers                             | 5    |

|   | 1.2.6 Grid Computing                                      | 6    |

|   | 1.3 Reconfigurable Computing                              | 7    |

|   | 1.3.1 Current Trends in Reconfigurable Systems            | 8    |

|   | 1.3.2 New Opportunities                                   | . 11 |

|   | 1.4 Motivations                                           | 12   |

|   | 1.5 Objectives and Contributions                          | . 14 |

|   | 1.6 Dissertation Organization                             | . 17 |

| 2 | RECONFIGURABLE COMPUTING                                  | . 19 |

|   | 2.1 Field-Programmable Gate Arrays                        | . 19 |

|   | 2.2 Recent Advances in FPGAs                              | . 21 |

|   | 2.3 Examples of Coarse-Grain Reconfigurable Architectures | . 23 |

|   | 2.4 Design Methodology for Reconfigurable Machines        | . 24 |

| C | hapter                                                          | Page |

|---|-----------------------------------------------------------------|------|

| 3 | MULTIPROCESSORS ON A PROGRAMMABLE CHIP                          | 28   |

|   | 3.1 A Coarse-Grained IP-based MPOPC (CG-MPOPC)                  | 30   |

|   | 3.1.1 Multiprocessor Architecture                               | 30   |

|   | 3.1.2 Processing Element                                        | 31   |

|   | 3.1.3 Memory Hierarchy Design                                   | 32   |

|   | 3.1.4 Implementation Results                                    | 34   |

|   | 3.2 HERA: A Reconfigurable Mixed-Mode Parallel Computer         | 34   |

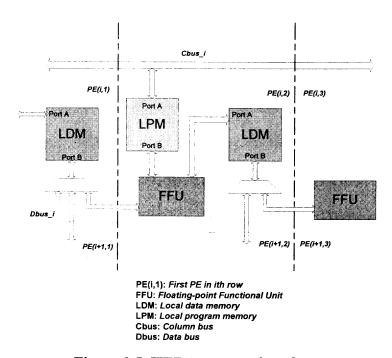

|   | 3.2.1 System Organization                                       | 35   |

|   | 3.2.2 PE Architecture                                           | 37   |

|   | 3.2.3 Memory Configuration                                      | 39   |

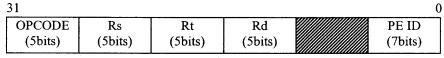

|   | 3.2.4 Instruction Set                                           | 40   |

|   | 3.2.5 Implementation Results                                    | 43   |

| 4 | APPLICATION STUDY                                               | 44   |

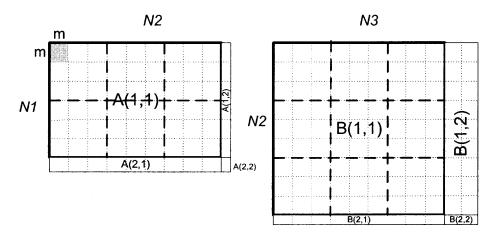

|   | 4.1 Generalized Cannon's Matrix-Matrix Multiplication Algorithm | 44   |

|   | 4.1.1 Data Partitioning and Mapping                             | 44   |

|   | 4.1.2 Dynamic Mixed-Mode Scheduling on HERA                     | 45   |

|   | 4.2 Parallel LU Factorization of Large Sparse Matrices          | . 47 |

|   | 4.2.1 Overview of LU Factorization                              | . 47 |

|   | 4.2.2 Near-Optimal Ordering Selection                           | . 50 |

|   | 4.2.3 Minimum Degree Ordering                                   | . 53 |

| C | hapter                                                       | Page |

|---|--------------------------------------------------------------|------|

|   | 4.2.4 Dynamic Task Scheduling                                | 53   |

|   | 4.2.4.1 Task Definition                                      | 54   |

|   | 4.2.4.2 State Information                                    | 55   |

|   | 4.2.4.3 Dynamic Scheduling Procedure                         | 56   |

|   | 4.2.4.4 Theoretical Performance Analysis                     | 58   |

|   | 4.2.5 Dynamic Mixed-Mode Scheduling on HERA                  | 63   |

|   | 4.3 Parallel Direct Solution of Sparse Linear Equations      | . 65 |

|   | 4.4 Parallel Solution of Newton's Power Flow Equations       | . 67 |

|   | 4.4.1 Newton's Solution to the Power Flow Problem            | 69   |

|   | 4.4.2 Parallel LU Factorization of Jacobian Matrices         | . 72 |

|   | 4.4.3 Parallel Solution of Newton's Power Flow Equations     | 77   |

|   | 4.4.4 Relevance to Other Work                                | . 78 |

| 5 | PERFORMANCE RESULTS AND ANALYSIS                             | 80   |

|   | 5.1 Mixed-Mode Scheduling of MMM on HERA                     | . 80 |

|   | 5.2 Parallel LU Factorization of Sparse Matrices on CG-MPoPC | 82   |

|   | 5.2.1 MPoPC Customization and Configuration                  | . 83 |

|   | 5.2.2 Experiments and Analysis                               | 86   |

|   | 5.3 Parallel LU Factorization of Sparse Matrices on HERA     | . 93 |

|   | 5.4 Parallel Power Flow Analysis on CG-MPoPC                 | 97   |

| 6 | SYSTEM I EVEL ENEDGY MODELING                                | 100  |

| C | hapter                                                              | Page  |

|---|---------------------------------------------------------------------|-------|

|   | 6.1 Related Work                                                    | 101   |

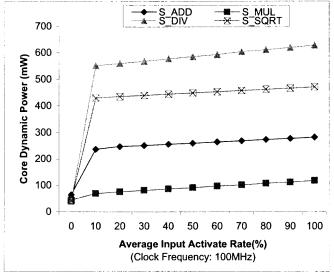

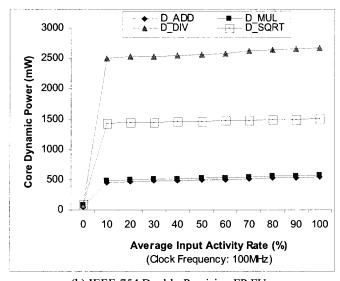

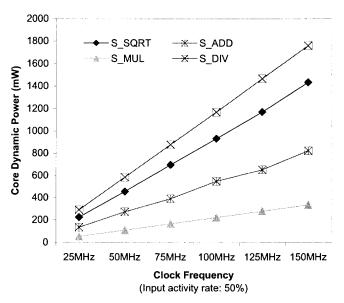

|   | 6.2 Power Characterization of Library Function Units                | 103   |

|   | 6.3 HERA System-Level Energy Model.                                 | 109   |

| 7 | A FRAMEWORK FOR RESOURCE MANAGEMENT ON MPOPCs                       | 113   |

|   | 7.1 Related Work                                                    | 114   |

|   | 7.2 Problem Definition and Objectives                               | 115   |

|   | 7.3 Framework Overview                                              | . 116 |

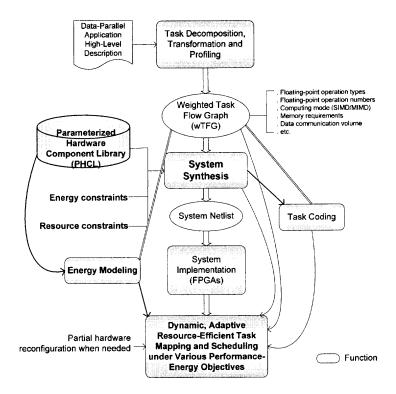

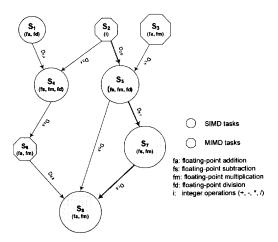

|   | 7.4 Application Model                                               | 117   |

|   | 7.4.1 Task Flow Graph                                               | . 117 |

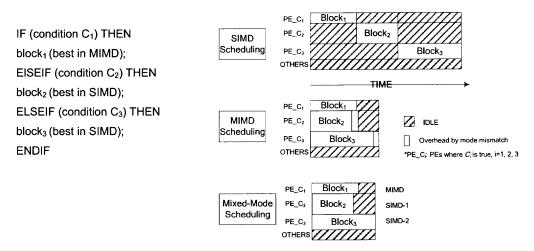

|   | 7.4.2 IF-THEN-ELSE                                                  | 119   |

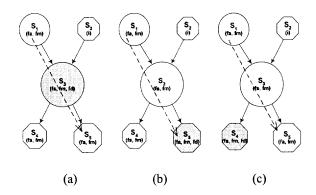

|   | 7.4.3 Loops                                                         | . 120 |

|   | 7.5 Architecture Synthesis and Reconfiguration                      | . 122 |

|   | 7.5.1 Parameterized Hardware Component Library                      | 123   |

|   | 7.5.2 Application-Specific System Synthesis                         | . 124 |

|   | 7.6 Dynamic Resource Scheduling for Performance-Energy Optimization | . 131 |

|   | 7.6.1 Related Work                                                  | 131   |

|   | 7.6.2 Loop Partitioning.,                                           | . 134 |

|   | 7.6.3 PE Search                                                     | . 135 |

|   | 7.6.4 Dynamic Resource Scheduling Schemes                           | . 137 |

|   | 7.6.4.1 Optimize the Performance without Energy Constraints         | . 139 |

| Chapter                                                              | Page  |

|----------------------------------------------------------------------|-------|

| 7.6.4.2 Optimize the Performance with an Energy Constraint           | 141   |

| 7.6.4.3 Optimize the Energy Cost under an Allowable Performance Loss | 142   |

| 7.7 Experimental Results                                             | 143   |

| 7.7.1 Singular Value Decomposition                                   | 143   |

| 7.7.2 Parallel Power Flow Analysis                                   | 147   |

| 8 CONCLUSIONS AND FUTURE WORK                                        | 153   |

| 8.1 Conclusions                                                      | 153   |

| 8.2 Future Work                                                      | 156   |

| BIBLIOGRAPHY                                                         | . 158 |

## LIST OF TABLES

| Tab | le                                                                                                                | Page |

|-----|-------------------------------------------------------------------------------------------------------------------|------|

| 2.1 | Comparison of Previous Coarse-Grain Reconfigurable Systems                                                        | 25   |

| 3.1 | The Instruction Set of HERA                                                                                       | 41   |

| 4.1 | Sparsity of Benchmark Power Matrices                                                                              | 48   |

| 4.2 | Sparsity of the Benchmark Matrices for Power Flow Analysis                                                        | 72   |

| 4.3 | The Sizes of the Blocks in the Jacobian Matrix                                                                    | 74   |

| 5.1 | HERA Execution Times for Irregular Matrices under Different Execution Modes                                       | 82   |

| 5.2 | Characteristics of the Test Matrices ordered into the DBBD Form                                                   | 88   |

| 5.3 | Execution times (seconds) for the benchmark matrices on the two MPoPCs                                            | 90   |

| 5.4 | IEEE Single-Precision Floating-Point Performance and Resource Utilization                                         | 94   |

| 5.5 | Latency Comparison also Involving a DSP Processor                                                                 | 97   |

| 5.6 | Optimal Partitioning of the Y <sub>bus</sub> Matrices of the Benchmark Systems                                    | 98   |

| 5.7 | Execution Times (msec) to Solve the Linear Equations for the Benchmark Systems on our Configurable Multiprocessor | 99   |

| 5.8 | Execution Times (sec) for Newton's Power Flow Equations with Seven Processors                                     | 99   |

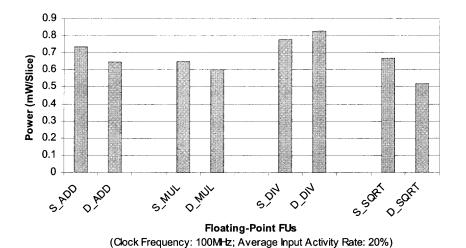

| 6.1 | Resource Usage (in slices) of Floating-Point FUs on XC2V6000-5                                                    | 105  |

| 6.2 | Total power consumption (mW) of the IEEE-754 Single- and Double-Precision FP FUs                                  | 105  |

| 7.1 | Major Parameters of an FP FU in PHCL                                                                              | 124  |

| 7.2 | SVD Task Information.                                                                                             | 145  |

| 7.3 | Task Information of the Parallel DBBD Power Flow Algorithm                                                        | 150  |

| 7.4 | Optimal Partitioning of the Y <sub>bus</sub> Matrices for the Benchmark Systems                                   | 151  |

# LIST OF TABLES (Continued)

| Table |                                                                        | Page |  |

|-------|------------------------------------------------------------------------|------|--|

| 7.5   | The Parallelism Profile during the Execution                           | 151  |  |

| 7.6   | Execution Times for the Benchmark Matrices                             | 151  |  |

| 7.7   | Comparison between the Modeled and XPower-Reported Energy Consumption. | 152  |  |

| 7.8   | Performance-Energy Optimization for the 7917-Bus System                | 152  |  |

### LIST OF FIGURES

| Figu | ıre                                                                                     | Page |

|------|-----------------------------------------------------------------------------------------|------|

| 1.1  | Temporal computing vs. spatial computing                                                | 8    |

| 1.2  | Conventional methodology in reconfigurable computing                                    | 10   |

| 2.1  | A CLB in Virtex II FPGAs                                                                | 21   |

| 2.2  | Slice configuration in Virtex FPGAs                                                     | 21   |

| 2.3  | Virtex 4 FPGA [Xilinx]                                                                  | 22   |

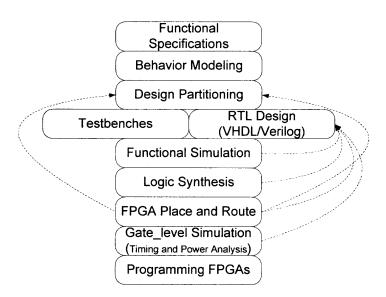

| 2.4  | Conventional development flow for FPGA-based systems                                    | 24   |

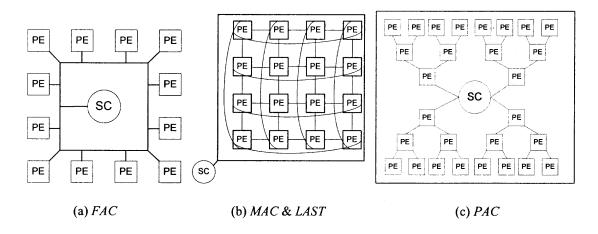

| 3.1  | The CG-MPoPC architecture                                                               | 31   |

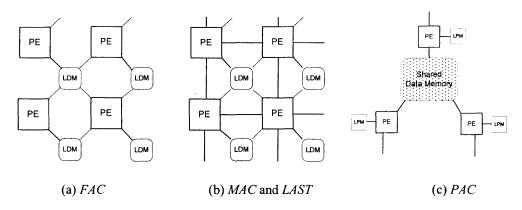

| 3.2  | CG-MPoPC memory configuration                                                           | 33   |

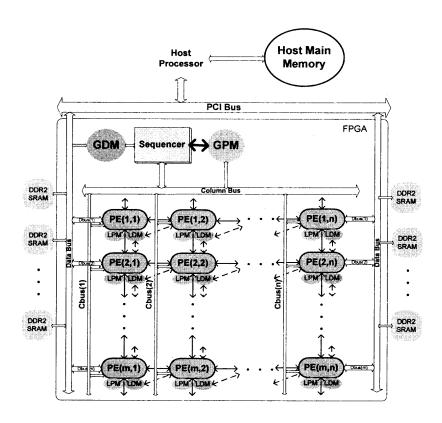

| 3.3  | HERA system architecture                                                                | 36   |

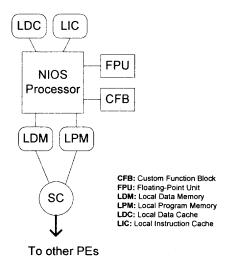

| 3.4  | A HERA PE                                                                               | 38   |

| 3.5  | HERA memory interface.                                                                  | 40   |

| 3.6  | HERA general instruction format                                                         | 41   |

| 4.1  | A partitioning example for matrices A and B $(q = 3, p1 = 2, p2 = 3, p3 = 3)$           | 45   |

| 4.2  | Sparse DBBD matrix format                                                               | 49   |

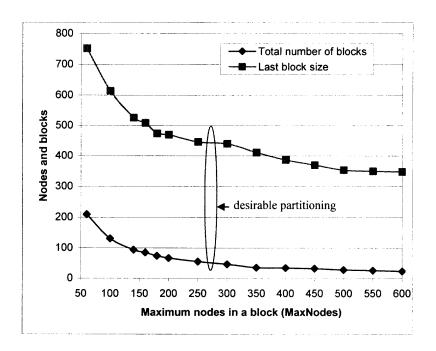

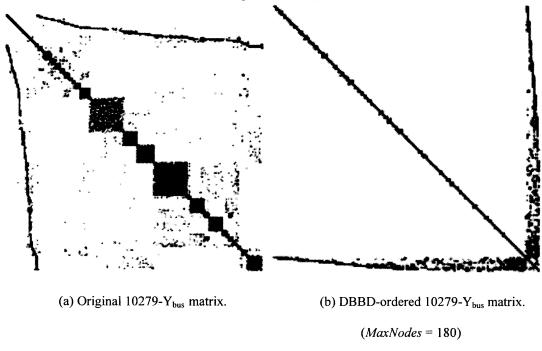

| 4.3  | DBBD ordering for a matrix of size 10279 x 10279                                        | 52   |

| 4.4  | The non-zero elements in the 10279-Y <sub>bus</sub> and the corresponding DBBD matrices | 52   |

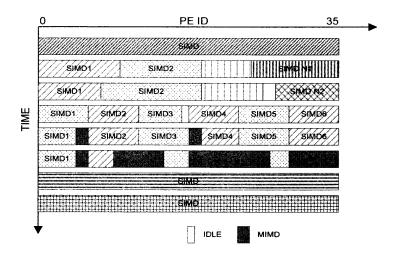

| 4.5  | Typical PE mode assignment for large DBBD matrices                                      | 65   |

| 4.6  | Sparse DBBD Y <sub>bus</sub> matrix                                                     | 72   |

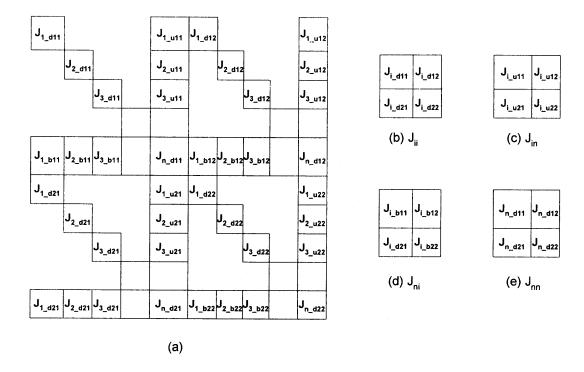

| 4.7  | The Jacobian matrix produced from the DBBD Y <sub>bus</sub> matrix                      | 74   |

| 4.8  | Nonzero elements for the 7917-bus system                                                | 75   |

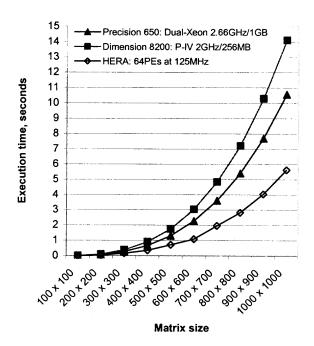

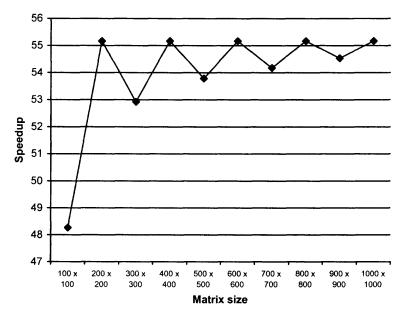

| 5.1  | Performance comparison of MMM on HERA and two Dell PCs                                  | 81   |

# LIST OF FIGURES (Continued)

| Figu | re                                                                                                                                     | Page |

|------|----------------------------------------------------------------------------------------------------------------------------------------|------|

| 5.2  | HERA speedup of parallel over uni-PE execution                                                                                         | 82   |

| 5.3  | PE and SC connectivity                                                                                                                 | 84   |

| 5.4  | MPoPC configurations for the tasks in DBBD-based parallel LU factorization                                                             | 85   |

| 5.5  | Interconnecting on-chip data memories for the MPoPC configurations of Fig.5.4                                                          | 86   |

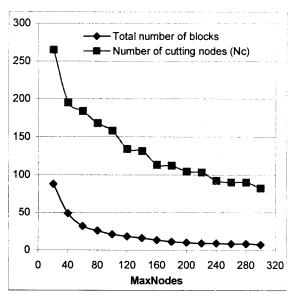

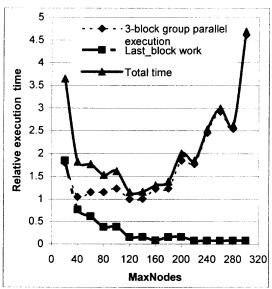

| 5.6  | Impact of network partitioning on the execution time of parallel LU factorization for a DBBD matrix of 2582 x 2582                     | 89   |

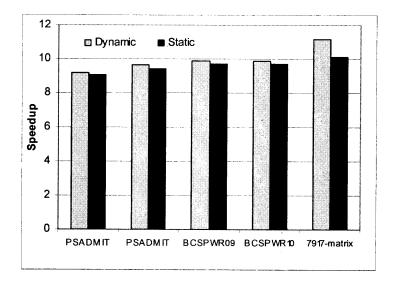

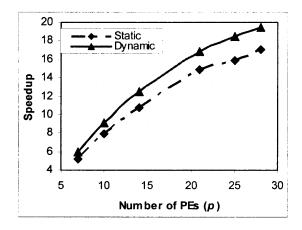

| 5.7  | Speedup comparison of the run-time and static scheduling policies on the customized MPoPC                                              | 90   |

| 5.8  | Speedup (over the uni-processor) of the static and dynamic scheduling policies for the 10279-Y <sub>bus</sub> matrix. No hardware FPUs | 91   |

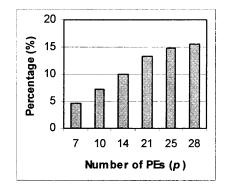

| 5.9  | Percentage of time needed to factor the last block in the 10279- $Y_{bus}$ matrix                                                      | 92   |

| 5.10 | Comparing the predicted and real performance for the 7917-matrix                                                                       | 92   |

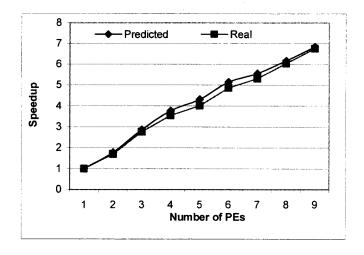

| 5.11 | Execution time for the 10279-Y <sub>bus</sub> matrix affected by pre-fetching                                                          | 93   |

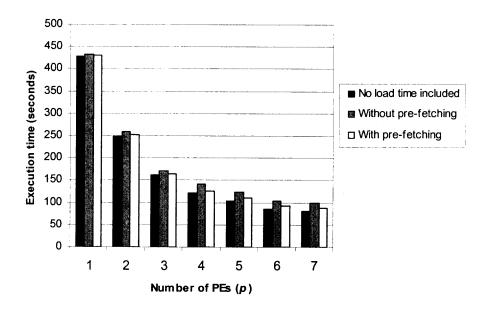

| 5.12 | Execution times on HERA under the SIMD, MIMD and mixed modes (HERA system frequency: 125MHz)                                           | 95   |

| 6.1  | Dynamic power consumption (per slice) of the single- and double-precision FP FUs                                                       | 105  |

| 6.2  | Impact of the average input activity rate on the core dynamic power consumption                                                        | 107  |

| 6.3  | Relationship between the core dynamic power consumption and the clock frequency                                                        | 109  |

| 7.1  | Design methodology overview/flowchart                                                                                                  | 117  |

| 7.2  | A typical task flow graph                                                                                                              | 118  |

| 7.3  | SIMD, MIMD and mixed-mode mapping of conditional blocks                                                                                | 120  |

# LIST OF FIGURES (Continued)

| Figu | Figure                                                                   |     |

|------|--------------------------------------------------------------------------|-----|

| 7.4  | Special examples of FOR loops                                            | 122 |

| 7.5  | An example of function selection for PEs                                 | 131 |

| 7.6  | Cross-iteration dependence.                                              | 135 |

| 7.7  | PE search path                                                           | 136 |

| 7.8  | Execution times with and without partial runtime reconfiguration (RTR)   | 146 |

| 7.9  | Normalized execution times for our strategy and naive dynamic scheduling | 147 |

#### **CHAPTER 1**

#### INTRODUCTION

### 1.1 High-Performance Applications

Many large-scale scientific and engineering problems appearing in areas such as bioinformatics, power engineering, astrophysics, high-energy physics and chemistry, structural analysis, circuit simulation, traffic simulation, and fluid dynamics can be formulated as the recurring solution of a system of equations [Bailey, 1998; Fox, et. al., 1988]. The corresponding matrix-based algorithmic solutions are often computation intensive and present major challenges to current computing systems. For example, the complexity of two common algorithmic cores in the above applications, namely LU factorization and matrix multiplication, require  $O(N^3)$  time for an  $N \times N$  is the matrix. Besides these classic high-end applications, many algorithms in newly emerging areas, such as wireless communications, data-intensive internet applications also present greedy demands for computing power in order to provide real-time services. Parallel computing has been recognized as an effective and viable solution to accelerate such problems and significant research has been ongoing for decades. New exciting frontiers in bioinformatics in the past few years, such as the sequencing of the human genome, rely heavily on parallel computers [Grama, et al., 2003].

## 1.2 Current High-Performance Computing Systems

After tremendous investment and decades of experimentation, clusters of Cray-like vector supercomputers, distributed shared-memory multicomputers employing crossbar

or multistage interconnection networks, and clusters of scalar uni- and multi-processor systems dominate the high-performance computing field [Bell, et al., 2002; Simon, 2003; Kuck, 1996]. Steady advances in related technologies provide the possibility and flexibility to mix features found in these systems, so many hybrid computing systems have been developed. Our taxonomy of parallel architectures is based on the programmer's, or more specifically, the compiler's view.

#### 1.2.1 Proprietary Supercomputers

Supercomputers typically follow custom designs and fall into one of these computing architectures: vector supercomputers, and shared-memory (SM) SIMD, distributedmemory (DM) SIMD, SM-MIMD and DM-MIMD machines [Hwang, 2003]. The performance of these machines largely depends on their architecture and proprietary compilers. Traditional supercomputers have accomplished a great deal of success in solving computation-intensive problems and represent the top end of stand alone computing systems in terms of high computing power, high bandwidth and low latency interconnects, very fast memories and high I/O rates. Representative supercomputers, some of them still in use, include the Earth Simulator from NEC, the T3D and T3E from Cray, the SX-4/5 from NEC, the Challenge XL and Origin 2000 from Silicon Graphics, and the CM-5 from Thinking Machines Corporation. The performance of the best performing 500 (TOP500 list) supercomputers in the world can be found at http://www.top500.org, where the term "supercomputer" is used in a broader scope. Most state-of-the-art custom supercomputers are vector based or contain a cluster of vector components and off-the-shelf RISC processors, such as the Opteron, PowerPC or

PA-RISC. The traditional supercomputer industry has languished in recent years [Bell, et al., 2002; Vaughan-Nichols, et al., 2004]; besides reduced government and industry spending on supercomputer technology, the high price, the long design and development cycles, the difficulty of programming them, the high cost of maintaining them and their huge power consumption, limit the application of supercomputers to many diverse fields. Although PC clusters have demonstrated increased performance (as shown in the TOP500 list), their long interconnect latencies still require custom supercomputers in numerous capacity and mission-critical problems or problems characterized by fine-grain parallelism. Some areas often requiring custom supercomputers are weather forecasting, climate research, molecular modeling (computing the structures and properties of chemical compounds, biological macromolecules, polymers, and crystals), physical simulations (such as simulation of airplanes in wind tunnels, simulation of the detonation of nuclear weapons, and research into nuclear fusion), and cryptanalysis.

#### 1.2.2 Shared-Memory Multiprocessors

The most common architecture employed in current shared-memory multiprocessors is non-uniform memory access (NUMA) symmetrical multiprocessing (SMP) [Tosic, 2004]. Multiprocessors used to be present in high-end mainframes and servers and they appear now in many kinds of systems, including high-end PCs and workstations. Examples include the Sun Enterprise 6000, the SGI Challenge and the Intel SystemPro. The SMP systems are usually small due to their nature of shared memory.

Recent advances in integrated circuit technology have fueled another opportunity: multiprocessor-on-a-chip. Single-chip multiprocessors based on fixed logic have recently emerged as the result of major hurdles in superscalar microprocessor design [Ronen, et al., 2001]. Two major categories of multiprocessors have attracted intensive interest in the academic and industrial settings. The first category utilizes advanced superscalar cores with a shared memory [Krashinsky, et al., 2004; Hammond, et al., 2000; Barroso, et al., 2000] whereas the other integrates a large number of simple. pipelined cores, like MPSoCs (MultiProcessor-Systems-on-a-Chip) [Power4: Hofstee, et al., 2005; Wolf, 2004; Stolberg, et al., 2005; Henkel, et al., 2004; Jerraya, et al., 2004]. Recent research category in the first group include, among others, Hydra [Olukotun, et al., 1996], SCMP [Baker, et al., 2002] and SCALE [Krashinsky, et al., 2004]. Hydra is designed around complex superscalar processors. SCALE combines vector processing and multithreading. SCMP is a multiprocessor organized in a 2-D mesh without global communication channels. Current MPSoC implementations have optimized for real-time been applications in networking, multimedia communications using heterogeneous processors and custom function units [Jerraya, et al., 2004]. For chip multiprocessors based on custom logic, a high volume is required to amortize the high development and NRE (nonrecurring engineering) costs, especially for deep sub-micron designs. Also, the ever-shortening product cycles and the high design complexity of such solutions limit their viability [Bergamaschi, et al., 2001]. We have also seen some reconfigurable single-chip multiprocessors based on custom reconfigurable logic instead of commercial FPGAs, e.g., PACT XPP [Becker, et al., 2003].

#### 1.2.3 Message-Passing Multicomputers

Message-passing multipcomputers are normally implemented with a distributed-memory architecture. They consist of multiple computers, often called *nodes*, interconnected by a uniform point-to-point network [Hwang, 2003]. Each node is an autonomous computer consisting of a processor, local memory, and sometimes attached disks or I/O peripherals. The boundary between multiprocessors and multicomputers has become blurred in recent years. Examples falling into this category include the Intel Paragon and iPSC/2, Transputer-based systems and nCube machines. Multicomputer design and implementation have been declining since the mid-1990s with the increasing popularity of cluster-based systems and distributed shared-memory systems.

#### 1.2.4 Distributed Shared-Memory Multicomputers

These are systems normally implemented with a point-to-point interconnection network but there is often both hardware and software support to implement shared memory [Hwang, 1993].

### 1.2.5 Cluster-Based Computers

A computer cluster is viewed as a single computing system comprising interconnected stand-alone computers that communicate with one another either via message passing or shared memory [Bell, et al., 2002]. Taking advantage of exponential advances in commercial off-the-shelf (COST) components since the mid-1990s, such as general-purpose microprocessors and Ethernet technologies, clusters of open architecture systems quickly entered the mainstream of the high-performance computing (HPC) world as the specialist supercomputer market shrank. They have much lower cost than

the latter and are also rather scalable in hardware. More than half of the TOP500 supercomputers released in November 2004 are labeled as clusters [TOP500], making them the most common architecture on the list. They bring the benefits of parallel processing at reduced cost to a broader scope, and provide an easy-to-use and accessible parallel processing alternative to the majority of high-performance applications. The ease of implementing standard programming models on them is a tremendous advantage. However, although it is easy to scale up and upgrade the hardware configuration of clusters, the performance of many parallel algorithms does not scale well on these machines primarily due to high communication latencies [Lan, et al., 2003]. They are more effective for loosely-coupled tasks lacking frequent communications [Vaughan-Nichols, et al., 2004].

### 1.2.6 Grid Computing

While computer clusters are often groups of dedicated homogeneous computers administrated as a single system, grid systems focus on integrating, virtualizing and coordinating computing resources and services within distributed heterogeneous systems that are in separate administrative domains [OGSA-WG]. Grids share advantages with cluster-based systems, such as low-cost and stand-alone nodes easy to maintain. They also share exaggerated disadvantages, such as very high communication costs. TeraGrid [Reed, 2003] is the largest research grid in this category.

#### 1.3 Reconfigurable Computing

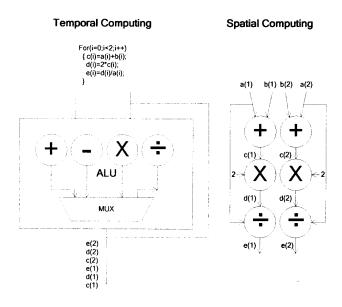

At the physical level, two primary approaches have been employed in the implementation of applications: programmable microprocessors and customized hardware utilizing ASIC chips. Programmable microprocessors have a general-purpose, fixed architecture that implements applications temporally via atomic operations dictated by machine instructions (temporal computing). They can also support very limited spatial execution of operations with multiple functional units. However, the price of the programming flexibility is rather low performance, which can be far below that of an ASIC design. Also, microprocessors consume more power than ASICs. In contrast, ASICs are designed and manufactured explicitly for specific applications by spatially decomposing operations that can be implemented directly by dedicated functional units like adders or multipliers (spatial computing) and modification requires re-design and re-fabrication of the chip, which is an expensive process, especially with multi-million-gate chips in sub-micron processes. ASICs are designed to perform a specific algorithm quickly and efficiently, but cannot be altered after fabrication. Figure 1.1 illustrates the two computing approaches for the execution of a small loop.

Reconfigurable computing [Compton, et al., 2002] sits between the extremes of general-purpose microprocessors and specialized ASICs, and allows a high degree of both spatial and temporal execution of the operations. A reconfigurable system usually employs reconfigurable devices, such as FPGAs, and works closely with one or more general-purpose processors to accelerate computation-intensive or highly parallel applications. The reconfigurable logic can be adapted (reprogrammed) for different application. Hence, reconfigurable systems are flexible due to field programmability

after fabrication and are much less expensive than ASIC designs; but they are less efficient in terms of power and resource consumption, and are usually slower than the latter. On the other hand, they can offer much better performance due to their (semi-) customization for a wide range of applications as compared to general-purpose microprocessors. However, their adaptation requires hardware expertise.

Figure 1.1 Temporal computing vs. spatial computing.

#### 1.3.1 Current Trends in Reconfigurable Systems

FPGA-based computing machines have recently demonstrated considerable performance gains over general-purpose microprocessors for many computation-intensive applications [Compton, et al., 2002; Bondalapati, et al., 2002]. Most of them take advantage of the fine-grain architecture in earlier FPGAs and are fully customized for a specific class of applications, like ASIC designs, but with much lower costs and more flexibility than ASIC designs. Most machines target bit-level multimedia and DSP applications where floating-point operations are not often necessary. Because *floating*-point operations

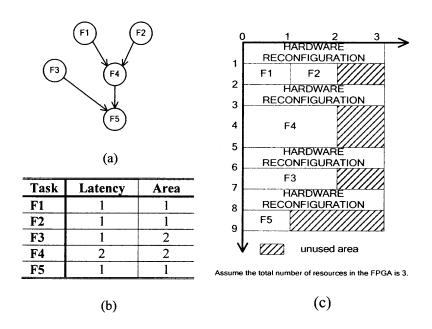

point units (FPUs) consume a very large portion of the resources in earlier FPGAs, very few such machines support floating-point arithmetic. Due to the limited resources in prior FPGAs, the fine-grain functional units in such machines most often are not program accessible and their overall processing capabilities are rather limited. These FPGAs are developer-, rather than user-programmable. A small change in the algorithm requires full reconfiguration of the hardware, which takes significant time. Moreover, full hardware reconfiguration is required when the problem size exceeds the available resources on the FPGAs, which is a major overhead in terms of time and energy during the application execution. Each reconfiguration consumes tens to hundreds of milliseconds. Figure 1.2 shows the general idea of such approaches. Figure 1.2 (a) is the application data flow graph, and the resource requirements and execution times of the tasks are shown in Figure 1.2 (b). Task mapping and scheduling on the FPGA is shown in Figure 1.2 (c). Let the configuration time of the FPGA be 1 unit of time. It is clear that the required hardware configuration time is rather significant compared to the computation time. Also, many resources are wasted during execution, as the figure shows. In an application shown for the Dynamic Instruction Set Computer (DISC), the configuration overhead contributes more than 25% of the total execution time [Wirthlin, et al., 1996].

In contrast to the ever increasing speed of logic resources, the configuration overhead for SRAM-based FPGAs becomes more serious with increases in the chip size [Pan, et al., 2004] since the size of the configuration data is proportional to the total number of on-chip resources. For example, the configuration time of the device we use,

Figure 1.2 Conventional methodology in reconfigurable computing.

the XC2V6000-5, is at least 50 msec [Xilinx Virtex II]. In comparison, we can multiply two matrices of size 1000 x 1000 in about 5 msec and perform the LU factorization a matrix of size 1000 x 1000 in about 50 msec on the same FPGA chip [Wang, et al., 2005]. The power required to reconfigure the device is another serious issue that cannot be ignored. The aforementioned device requires at least 29.7 W (800 mA \* 3.3 V + 100 mA \* 1.65 V + 100 mA \* 1.65 V) [Xilinx Virtex II] power consumption during each configuration, which results in a total 1485 mJ of energy consumption. Research efforts trying to alleviate both problems include reducing the number of reconfigurations [Ghiasi, et al., 2004], increasing the sharing of function units [Cardoso, 2003], compression of the configuration bits [Pan, et al., 2004; Li, et al., 2001] and alternative architectures, such as multi-context FPGAs [DeHon, 1997]. The reconfiguration of such devices is carried out by switching from one configuration (context) to another one stored in the device by replicating the configuration memory; this is known as *context switching* [Scalera,et al., 1998]. Additional storage resources are needed in such devices

to store multiple configurations and intermediate results between reconfigurations. This causes serious power issues and these choices do not appeal to most FPGA vendors.

Further discussion about the conventional design methodology and its disadvantages is presented in detail in Chapter 2. However, we expect this approach to continue playing a major role in application areas where field programmability by the user is not required or is needed rarely and the problem size is small enough and full reconfiguration is not required.

## 1.3.2 New Opportunities

With the recent achievement of multi-million-gate platform FPGAs to contain richer embedded feature sets, such as plenty of on-chip memory, DSP blocks and embedded microprocessor IP cores, FPGA-based reconfigurable computing is going through a revolution. New FPGAs employ coarse-grain architectures to facilitate more powerful coarse-grain datapaths. The peak floating-point performance of FPGAs has outnumbered in the last two years that of modern microprocessors and is growing much faster than the latter [Underwood, 2004]. Recent research efforts in the design and implementation of FPUs [Zhuo, et al., 2004; Liang, et al., 2003] and computation-intensive algorithms on state-of-the-art FPGAs provide evidence to this effect. However, they follow the traditional approach where the circuitry is only applicable to the specific algorithms invented by the developer and the studied problems were of very small size. It is now viable for FPGAs to accommodate some high-performance applications. Even supercomputer manufacturers have recently incorporated FPGAs in their designs. For example, Cray incorporates six Xilinx Virtex 4 FPGAs per chassis in its XD1<sup>™</sup>

supercomputers that can be used as coprocessors to accelerate computation-intensive applications. The advent of soft IP configurable processors from FPGA vendors, such as Microblaze from Xilinx and Nios from Altera, have inspired some multiprocessor implementations on FPGAs [Hung, et al., 2005; Salminen, et al., 2005; Hoare, et al., 2004; Ravindran, et al. 2005]. However, we have not seen FPGA-based single-chip multiprocessors that incorporate hardware FPUs.

#### 1.4 Motivations

From the above discussion we can see that PC-based cluster systems and SMP multiprocessors are the dominant high-performance platforms for the majority of computation-intensive applications. Nevertheless, their shared-memory nature limits the size of SMP systems and the high communication latencies in cluster systems make them more effective for loosely-coupled tasks lacking frequent communications. Both of them are based on general-purpose COTS components and are only effective on certain classes of applications. Due to the different characteristics of general-purpose and high-performance computing, we cannot rely solely on COTS components to improve the latter. Moreover, conventional (micro)architectures are fast approaching a performance limit due to the limited ILP (Instruction Level Parallelism) in real programs [Ronen, et al., 2001]; their large power dissipation is a major problem as well. Also, wire delays decrease much slower than transistor switching times for deep submicron processes. As a result, a major shift from ILP to TLP (Thread Level Parallelism) is present in the industry and research communities. To this extent, AMD, Intel, Sun, and IBM, among others, have recently introduced multicore chips.

The author is among the very few who observed very early that FPGAs provide a new opportunity to the high-performance computing field. State-of-the-art FPGAs have made it feasible to build high performance computing systems at affordable costs with hardware support for floating-point operations. High-performance applications often involve complex matrix-based algorithms where software programmability and standard FP representation are indispensable. Scalability and portability are also essential to performance due to the variant size of matrices and the ever changing parameters of various applications. These systems can leverage system level concepts from high-performance computing and can dynamically tune their architecture to fit the applications. They are also accessible to applications due to their low cost. However, this new approach requires extensive expertise in computer architecture, parallel processing, and digital and FPGA-based designs in order to yield high performance. The majority of the FPGA community still follows the conventional approach of designing and implementing acceleration circuitry for specific algorithms, as discussed in Section 1.3. To the best of our knowledge, we have not seen yet major research efforts in the new MPoPC direction and very few FPGA-based computing systems incorporating FPUs have been published.

The programming of reconfigurable systems for high performance can be quite challenging as it essentially involves hardware design. Although several groups have recognized that the success of such systems will highly depend on high-level design tools to efficiently map applications onto the hardware, they focus their efforts on developing more general, software-oriented approaches that resemble traditional compilers for general-purpose microprocessors; they assume simplified and regular

models for reconfigurable systems, or no specific architecture at all. Due to their difficulty in implementing hardware, most of the published results are based on simulation only. This is a major drawback as it is indeed important to implement such systems in order to evaluate the performance accurately. Reconfigurable systems are more diverse than conventional high-performance computing systems due to their reconfiguration flexibility and the eventual (semi-)customization of hardware to run application code. It is hence very important for the mapping tools to be hardware-oriented and take into account the specific idiosyncrasies, features and constraints of the target systems in order to achieve the high performance they are designed for; this is often accomplished by fully utilizing the hardware resources.

#### 1.5 Objectives and Contributions

The first objective of this research is to propose a design methodology for high-performance, low-cost reconfigurable systems targeting large data-parallel applications [Hills, et. al., 1986] and utilizing new-generation FPGAs. The focus here is on high-performance and reconfigurable MPoPCs implemented with state-of-the-art platform FPGAs. A major contribution is the pioneering nature of reconfigurable MPoPCs, and the system-oriented approach to design and implement them for data-parallel applications. No related major efforts have been published.

Two different types of MPoPCs with hardware FPUs were designed and implemented to provide a base for further study: (a) a coarse-grain MPoPC (CG-MPoPC) based on a configurable IP processor core from Altera (i.e. Nios) that was implemented on the Altera SoPC FPGA board, and (b) the HERA mixed-mode variant-

grain machine that was implemented on Xilinx FPGAs. CG-MPoPC is designed to run in the MIMD mode while HERA can be reconfigured at runtime to support a variety of independent or cooperating computing modes, such as SIMD, MIMD and M-SIMD. Therefore, HERA can potentially match better in the time spectrum all subtask characteristics of a given application. The PEs in both systems are equipped with large data and instruction on-chip memories. Platform FPGAs also provide substantial flexibility to integrate many features found in conventional high-performance computing systems. In contrast to previous FPGA-based custom computing machines, these systems are also user-programmable by general-purpose instructions. To save on reconfiguration time, full hardware reconfiguration during execution is eliminated by employing user-programmable PEs. Parallel solutions for two computation-intensive benchmark applications, namely matrix-matrix multiplication (MMM) and LU factorization, which require  $O(N^3)$  floating point operations (N x N is the matrix size), are studied and implemented on the two MPoPCs. Large sparse real-world matrices from power engineering, with size of up to 10279 x 10279, are employed in the evaluation process. A large, complex real-world application, namely power flow analysis based on Newton's method [Tinney, et al., 1967] was parallelized and mapped onto the two MPoPCs. Its real-time solution is of critical importance to the security of any power grid and current solutions on cluster systems suffer many limitations [IEEE, 1992]. Efficient application mapping, dynamic task scheduling and load balancing techniques are proposed and analyzed on my MPoPCs. The innovative nature of this work has the potential to guide research in this arising field of high-performance reconfigurable computing.

MPoPCs sit between the two categories of chip multiprocessors (Section 1.2.2) by taking advantage of the field reprogramability of FPGAs: they are similar to the first category in that all PEs share the same microarchitecture and ISA (Instruction Set Architecture); it also shares MPSoC features since the PEs are simple and yet highly (but not fully) optimized for target applications. HERA targets data-intensive, matrix-based applications in general; however, the end user can choose certain features for the PEs as shown later. A distinct advantage of MPoPCs is that it can be customized in the field by the end user due to the presence of reconfigurable logic; in addition, this can be done at a very low cost and risk of design, implementation and verification. The PE configuration is closely customized and reconfigured to match application's characteristics and, hence, increase the resource utilization for high-performance. The author also emphasizes the importance of on-chip local memory due to the ever increasing memory-processor latency gap. This is similar to the recently announced Cell processor, where PEs are interconnected by a bus [Hofstee, 2005].

On the software side, programming reconfigurable MPoPCs, especially heterogeneous systems like HERA, is very challenging given the tremendous flexibility provided by MPoPCs. The performance of computing systems highly depends on a good match of the hardware system with the application. Efficient resource management is essentially the key to achieve high performance for designs based on reconfigurable logic. Based on the HERA design, a resource-oriented and architecture-conscious framework for mapping data-parallel applications (described at a high level) is proposed, in addition to dynamic resource management and reconfiguration schemes. The applications are profiled and then expressed using weighted task flow graphs

(wTFGs) consisting of SIMD and MIMD tasks associated; several parameters denote the complexity of each task. At static time, an application-specific HERA configuration based on an in-house designed parameterized hardware component library (PHCL) is synthesized for various performance-energy objectives. The architecture can be reconfigured at runtime as needed by the tasks. Then, a proposed runtime management approach takes advantage of HERA's mixed-mode parallelism in order to increase the resource utilization while at the same time optimizing the performance and/or consumed energy. During the execution of an application, this approach may dynamically repartition and redistribute active SIMD tasks among the available PEs (Processing Elements) in the system. Experiments with the parallel power flow analysis algorithm and singular value decomposition (SVD), which requires at least 20 times more FP operations than LU factorization, are performed to test the proposed framework. A HERA system-level energy model which is based on physical-level implementation data and run-time application statistics is proposed to guide the runtime scheduling decisions.

### 1.6 Dissertation Organization

Chapter 2 provides a technical background on FPGA devices and reconfigurable computing. Chapter 3 presents the design and implementation details of the two MPoPCs. The development of MMM, parallel LU factorization of large sparse matrices, parallel direct solution of sparse linear equations and parallel processing for power flow analysis on the MPoPCs, as well as related issues for mapping and scheduling are discussed in Chapter 4. Chapter 5 contains experiments and performance analysis.

Power characterization and system-level energy modeling are presented in Chapter 6. The resource management framework for HERA and experimental results are presented in Chapter 7. Finally, conclusions of this research and suggestions for future work are presented in Chapter 8.

### **CHAPTER 2**

### RECONFIGURABLE COMPUTING

FPGAs are the most common devices employed in reconfigurable computing. This chapter provides a technical background on FPGAs and discusses the most recent advances in FPGA architectures. It also contains some examples of coarse-grain reconfigurable systems. The current FPGA development approaches are also discussed in order to provide an introduction for our compilation methodology in Chapter 7.

### 2.1 Field-Programmable Gate Arrays

FPGAs are a class of integrated circuits (ICs) that contain arrays of pre-fabricated logic and interconnection modules whose functions are electrically configurable to meet specific design requirements by the user; this is done by using system development software after the ICs have been manufactured and delivered. FPGAs were introduced in the mid-1980s as alternatives to custom-designed MPGAs (Mask-Programmable Gate Arrays) in order to reduce dramatically the high NRE costs, long design cycles, and inherent risks associated with the latter, and provide the benefits of customized ASIC designs. Most modern FPGAs employ SRAM (Static Random Access Memory) technology to achieve programmability and comprise a matrix of configurable components, such as logic blocks, distributed and/or block memories, hierarchical fast routing resources and/or microprocessor(s) [Altera; Xilinx]. Both of the functions performed in the logic blocks and the routing of signals in the interconnection fabric are programmable by the SRAM bits connected to them; programming the SRAM bits

configures the FPGA. Most applications often require that FPGAs be configured only once. This is known as *static reconfiguration*. *Runtime reconfiguration* allows applications to dynamically change the configuration of FPGAs at runtime. An important feature in modern FPGAs is the support of partial runtime reconfiguration. The penalty resulting for this flexibility of FPGAs is larger signal delay and a lower system frequency compared to ASIC designs implemented with similar silicon processes.

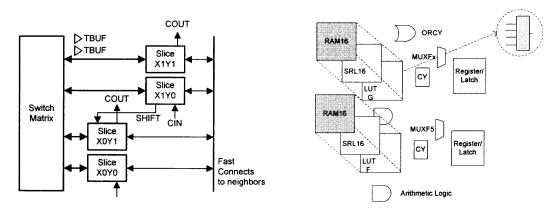

The basic computational cell in a Xilinx Virtex II FPGA is a Configurable Logic Block (CLB) [Xilinx], shown in Figure 2.1, which is made up of four similar slices tied to a switch matrix for accessing the general routing fabric, with fast local feedback within the CLB. The output from the function generator in each slice drives both the slice output and the D input of the storage element. Figure 2.2 shows a detailed view of a single slice. Each slice includes two 4-input lookup tables, carry logic, arithmetic logic gates, wide function multiplexers and two storage elements. As the diagram illustrates, the lookup tables can be configured and accessed in three different ways, including: 4-input LUT, 16 bits of distributed SelectRAM+ memory, or a 16-bit variable-tap shift register element. These LUTs are essentially 16 x 1 (with four inputs) or 32 x 1 (with five inputs) memory blocks used as universal function generators capable of serving as truth tables for the implementation of any arbitrary 4- or 5-input logic function. The extra multiplexers (MUXFx and MUXF5 in Figure 2.2) can be used to combine LUTs to realize functions with up to eight inputs.

When reconfigurable computing (RC) was introduced in the late 1980's, the largest FPGAs had only 2K gates of reconfigurable logic, far from enough real estate to

build computing systems. By the mid-90's, the size of reconfigurable devices increased to 50K gates of reconfigurable logic; but the continued low gate count, poor programming architectures, lack of partial reconfigurablity and high cost of these devices restricted the use of RC architectures for research and experimentation purposes. They were mainly used as highly integrated glue logic tying together the intelligent parts of systems or emulation engines for ASIC designs before they were fabricated.

Figure 2.1 A CLB in Virtex II FPGAs [Xilinx]. Figure 2.2 Slice configuration in Virtex FPGAs [Xilinx].

### 2.2 Recent Advances in FPGAs

With the arrival of million plus gates of reconfigurable logic on a chip in 2001 and the addition of high-performance RISC CPUs, block RAM, multi-gigabit high-speed serial I/Os, dedicated DSP logic, and other system enhancements, FPGAs have increasingly become system oriented (Systems-On-a-Programmable-Chip, SOPC) [Xilinx; Altera]. They have quickly taken over innumerable ASIC SoC designs with their flexible device integration capability, programmable I/O, very capable clock speed, and significantly lower overall design cost.

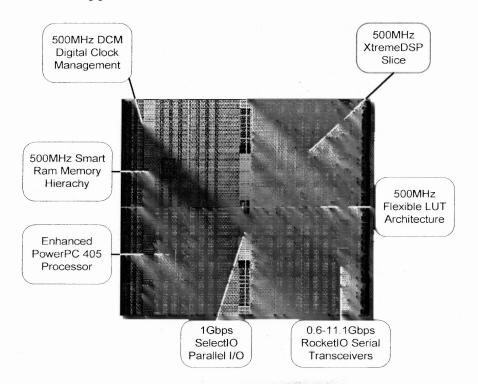

To give an idea of the state-of-the-art in FPGAs, let us consider the recently released Xilinx Virtex 4 FPGAs [Xilinx] shown in Figure 2.3. Virtex 4 employs a highly modularized architecture called the application-specific modular block (ASMBL), where the reconfigurable logic is structured into long, narrow stripes. Each stripe can be defined during the silicon manufacturing stage to contain either standard configurable logic elements or a function-specific block with specialized elements to handle DSP operations, memory, high-speed I/O, mixed-signal functions, or some other generic, yet application-optimized function. Its logic fabric and fixed blocks can all operate at 500-MHz clock rates. The largest available Virtex 4 device, XC4VFX140, is embedded with 63,168 slices and 9,936 Kbits of BlockRAM. Designers now have additional axis of flexibility to choose parts with varying mixures of special features more appropriate to their application.

Figure 2.3 Virtex 4 FPGA [Xilinx].

### 2.3 Examples of Coarse-Grain Reconfigurable Architectures

Earlier FPGA-based reconfigurable computing systems were mostly fine-grain systems, where processing elements (PEs) typically comprised logic gates, flip-flops and LUTs operating at the bit level [Compton, et al., 2002; Prasanna, et al., 2002]. Fine-grain systems are difficult to program, inefficient in application mapping and take significant time to compile and reconfigure [Venkataramani, et al., 2003], which is required in these approaches for applications oversizing the available hardware. The most important reason was insufficient resources in the FPGAs at that time. On the other hand, as more and more resources were allowed on a single die, coarse-grain systems (where the PEs contain complete functional units like ALUs and/or multipliers operating upon multiple-bit words), have become more common [Singh, et al., 2000]. While overcoming the disadvantages of fine-grain systems, coarse-grain systems tend to have fewer long-distance control signals and more regular localized modules; these features favor multi-million-gate devices where wire delay is more of a limiting factor to the system frequency than gate delay. New FPGA architectures also favor coarsegrain designs. We are only interested in coarse-grain designs in this work. Table 2.1 shows a comparison of available coarse-grain reconfigurable systems.

Most of these coarse-grain systems appeared as coprocessors to offload the main processor of computation intensive cores, mostly from signal and image processing. Only Raw included a 4-stage pipelined FPU in its PEs. As the table shows, only a very small amount of memory was included and no general-purpose instructions were provided in these systems. Finally, all of them were implemented by ASIC processes, although some of them were initially designed for FPGAs. Thus they are not flexible

enough like FPGA-based reconfigurable systems to support significant resource management. We did not find comparable systems on FPGAs.

### 2.4 Design Methodology for Reconfigurable Machines

Traditionally, FPGA-based designs follow a very similar flow as that for ASIC designs, as shown in Figure 2.4. Hence, mapping applications to FPGAs have mostly considered a hardware expertise.

Figure 2.4 Conventional development flow for FPGA-based systems.

The entire procedure can be very time-consuming for multi-million-gate devices and the resulting configuration data can be used only for a fixed-size, specific device. The entire FPGA implementation procedure (from the *design partitioning*) is repeated if the target device changes. Runtime reconfiguration has made possible the concept of "Virtual Hardware" [Ling, et al., 1993], where the FPGA resources are assumed unlimited and applications are partitioned into function blocks that are then executed by time-sharing the same hardware in a specific order. Hardware virtualization allows to

Table 2.1 Comparison of Previous Coarse-Grain Reconfigurable Systems

|                        | Comput.<br>model | DataPath          | Interconnect                                 | Local on-chip<br>memory                           | Program.                    | Application Domain                                |

|------------------------|------------------|-------------------|----------------------------------------------|---------------------------------------------------|-----------------------------|---------------------------------------------------|

| RaPiD <sup>1</sup>     | Pipelined        | 16-bit            | 1-D Linear array                             | Small data<br>memory                              | Rapid-C                     | Signal and image processing                       |

| $RAW^2$                | MIMD             | 32-bit, Pipelined | X routers                                    | 32KB Instruction<br>memory and<br>32KB Data Cache | RAWCC                       | General-purpose and embedded computing            |

| REMARC <sup>3</sup>    | SIMD             | 16-bit            | 2-D mesh                                     | 16-entry data<br>memory                           | N/A                         | Multimedia                                        |

| MATRIX <sup>4</sup>    | SIMD/MIMD        | 8-bit             | 2-D mesh,<br>hierarchical buses              | 256 x 8-bit                                       | N/A                         | General-purpose                                   |

| MorphoSys <sup>5</sup> | SIMD             | 8- or 16-bit      | 2-D mesh,<br>configurable<br>segmented buses | No                                                | SA-C                        | Data-parallel, compute-<br>intensive applications |

| Chimaera <sup>6</sup>  | SIMD             | 32-bit            | Dynamic buses,<br>crossbar                   | 32bit memory                                      | C-SIDE<br>(Mixed<br>C/VHDL) | Wireless communication, multimedia                |

<sup>1:</sup> Ebeling, et al., 1996; 2: Taylor, et al., 2002; 3: Miyamori, et al., 1999;

<sup>4:</sup> Mirsky, et al., 1996; 5: Singh, et al., 2000; 6: Ye, et al., 2000;

implement applications that are too large to fit on an FPGA. The major obstacle to its practical application is the significant overhead of reprogramming the hardware, which is typically on the order of tens to hundreds of milliseconds for current FPGAs [Xilinx; Altera]; this overhead may be larger than the actual computation time for small function blocks.

As expected advances in technology (Moore's Law) increase the resources on single programmable chips, the above design procedure becomes more and more timeconsuming and cumbersome, and requires extensive expertise in both hardware and software. Motivated by this problem, the past few years have seen an increasing interest in developing tools to compile applications written in high-level programming languages for target FPGAs; such languages are C/C++ and Java [Gokhale, et al., 2000; Cardoso, et al., 2003; Najjar, et al., 2003, Venkataramani, et al., 2003]. These tools typically take the user application code and produce corresponding VHDL code (RTL level) or a circuit netlist (the output of Logic Synthesis in Figure 2.4), and then FPGA place-and-route tools map the design to FPGAs. They still follow the same design philosophy of APSCs, as discussed in Section 1.3. The major problem with most of these approaches that try to mimic conventional compilers in allocating and configuring silicon resources is the extreme difficulty in identifying required components and their interconnectivity. It is crucial to take into account the idiosyncrasies of the underlying reconfigurable system while these approaches often apply generic techniques. Moreover, their time-consuming procedure has to be to be repeated every time a change is made to the source code. Most of them implicitly or explicitly assume the concept of virtual hardware which requires full or partial run-time reconfiguration. While these

approaches can bring FPGAs closer to more users who are not familiar with hardware design methodology, their performance in terms of area and speed are still unsatisfactory compared to the VHDL-based manual designs.

#### **CHAPTER 3**

### MULTIPROCESSORS ON A PROGRAMMABLE CHIP

Although the customization of hardware can lead to high-performance, it also limits the use of such systems due to the lack of elasticity in reusing and reprogramming functional units for various applications. Increasing the reusability of functional units is an effective way in reducing the number of required reconfigurations [Ghiasi, et.al., 2004; Cardoso, 2003]. Also, the continuous success of processor-based temporal computing platforms, including most current high-performance parallel systems, owes a great deal to their standard general-purpose and backward compatible architectures, and their standard programming environments; they protect and encourage long-term efforts and investments. It gives us a hint that in order to make reconfigurable computing machines mainstream computing platforms, standard architectures and microarchitectures, and corresponding development methodologies like those for microprocessors are absolutely essential.

This chapter discusses two approaches to FPGA-based MPoPC designs that I have implemented: CG-MPoPC, a reconfigurable IP-based MIMD MPoPC based on Altera FPGA devices, and HERA, a mixed-mode MPoPC machine based on the Xilinx Virtex II devices. Our target applications are matrix-based data-parallel and stem from the high-performance engineering and scientific fields. A pipelined IEEE-754 standard FPU was designed and implemented, and employed on both systems. The first MPoPC employs a configurable processor IP core from Altera optimized for platform FPGAs. Such RISC configurable soft cores have recently become available to greatly empower FPGA-based system implementations. Conventional processors gain in performance by

increasing the clock frequency; this results in intolerable high power consumption and the physical limits are often reached. IP configurable processors, on the other hand, provide extra opportunities in lower power consumption, higher transistor utilization, programmability and flexibility. The processor can be tailored to better meet the requirements of the application. The instruction set architecture (ISA), register file, software development APIs (Application Programming Interfaces), memory hierarchy and size, and communication channels can all be configured and extended as deemed appropriate. Also, standard and user customized logic engines can be easily added, modified or extended, as needed. We can identify critical instructions in the application code that affect performance the most and implement them in hardware. Configurable processor cores also provide us with substantial flexibility in SOPC integration. Such configurable IP cores are designed with a general-purpose microarchitecture and instruction set to achieve good performance for a large range of possible applications. Hence, the first system is intended for many diverse applications. However, the generality of such systems to provide the provisions for many scenarios leads to a rather low utilization of hardware resources and lower performance than a custom designed solution to any particular application. In contrast, a fully-customized and reconfigurable PE is designed and implemented for HERA in order to meet more stringent performance requirements. Moreover, HERA can be reconfigured dynamically at runtime to support a variety of independent or cooperating computing modes, such as SIMD, MIMD and M-SIMD, to best match in the time spectrum all subtask characteristics of a given single application. More discussion about mixed-mode computing follows in Section 3.2. In order to evaluate and compare the performance of

different interconnection networks, the PEs in the first MPoPC are interconnected via an X-tree network where HERA employs a 2-D mesh organization. The first approach takes much less time to develop and implement, and is easier to program than the HERA custom approach. We also employ FPGAs from the two major vendors, i.e., Altera and Xilinx, in order to compare the architecture capabilities and performance of different devices.

## 3.1 A Coarse-Grained IP-based MPoPC (CG-MPoPC)

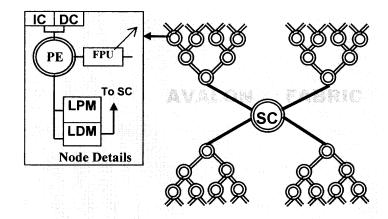

## 3.1.1 Multiprocessor Architecture

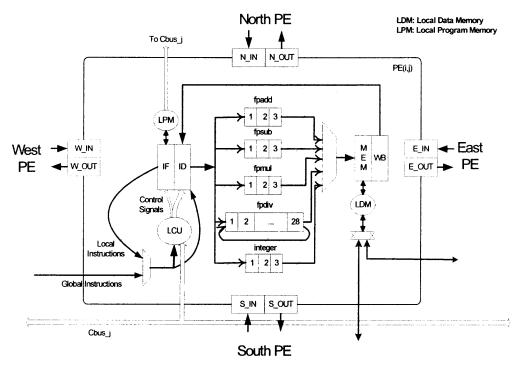

We customize the MPoPC configuration to better match applications. Figure 3.1 shows one configuration of the CG-MPoPC. The PEs form multiple binary trees to support communication patterns in a matrix-based algorithm (details follow in Chapter 4). Each PE is guided by the SC (system controller) that utilizes the boot up code stored in the PE's private memory. An interrupt-driven control channel in a star configuration connects the SC to every PE. There is also a direct communication channel between the SC and the root of every binary tree. As the feature size of silicon processes enters the submicron range, wire delay becomes significant compared to logic delay. The routing of chip-level and clock signals tends to become more cumbersome in complex multimillion gate SOPC designs. In contrast, our binary tree network for data communications eliminates global transfers and is also scalable in size. The serial and TCP connections were implemented between the multiprocessor and the host PC. TCP

provides a flexible, quick and efficient communication channel in our parallel system, which can be accessed by all other hosts in the network.

SC: System Controller

IC: Instruction Cache

IDM: Local Data Memory

LDM: Local Data Memory LPM: Local Program Memory

**PE**: Processing Element **DC**: Data Cache

**SDM**: Shared on-board memory **FPU**: Floating-point Unit

**Figure 3.1** The CG-MPoPC architecture.

## 3.1.2 Processing Element

We employed a 32-bit Nios® [Altera] IP processor core from Altera to implement each PE and the SC. The Nios® RISC processor is fully configurable and its implementation yields over 200 DMIPS (Dhrystone MIPS) in the Altera Stratix II FPGA. It utilizes a 5-stage pipeline and conforms to a modified Harvard memory architecture. Configurable processors necessitate trade-offs between performance and the resources consumed. A typical Nios® processor in our machine consumes about 1600 logic elements (LEs). A pipelined IEEE 754 single-precision FPU and some trigonometric functions, such as sine and cosine, were implemented in hardware with every PE. They are needed by our target applications. These functions take considerable time if implemented in software. All these hardwired functions can be accessed by application code via custom-made instructions. The FPU runs at 128.3MHz for the 3-stage adder/subtractor, 150.8MHz for

the 5-stage multiplier and 165.4MHz for the 28-stage divider. These efficient realizations result in significant performance improvements for matrix operations [Wang, et al., 2004]. Taking advantage of the high density of new generation FPGAs, we are among the first ones to implement IEEE 754 FPUs in FPGA-based configurable parallel systems.

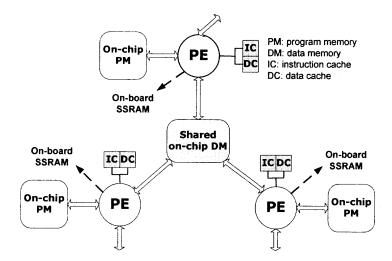

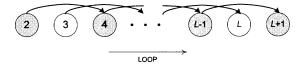

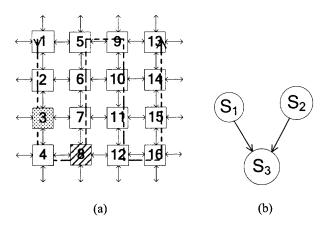

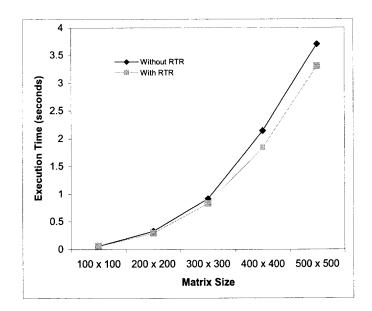

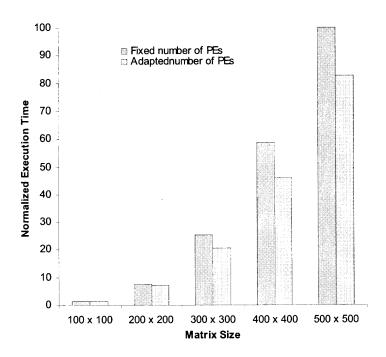

## 3.1.3 Memory Hierarchy Design