# **Copyright Warning & Restrictions**

The copyright law of the United States (Title 17, United States Code) governs the making of photocopies or other reproductions of copyrighted material.

Under certain conditions specified in the law, libraries and archives are authorized to furnish a photocopy or other reproduction. One of these specified conditions is that the photocopy or reproduction is not to be "used for any purpose other than private study, scholarship, or research." If a, user makes a request for, or later uses, a photocopy or reproduction for purposes in excess of "fair use" that user may be liable for copyright infringement,

This institution reserves the right to refuse to accept a copying order if, in its judgment, fulfillment of the order would involve violation of copyright law.

Please Note: The author retains the copyright while the New Jersey Institute of Technology reserves the right to distribute this thesis or dissertation

Printing note: If you do not wish to print this page, then select "Pages from: first page # to: last page #" on the print dialog screen

The Van Houten library has removed some of the personal information and all signatures from the approval page and biographical sketches of theses and dissertations in order to protect the identity of NJIT graduates and faculty.

#### ABSTRACT

# DESIGN AND STABILITY ANALYSIS OF HIGH PERFORMANCE PACKET SWITCHES

## by Zhen Guo

With the rapid development of optical interconnection technology, high-performance packet switches are required to resolve contentions in a fast manner to satisfy the demand for high throughput and high speed rates. Combined input-crosspoint buffered (CICB) switches are an alternative to input-buffered (IB) packet switches to provide high-performance switching and to relax arbitration timing for packet switches with high-speed ports.

A maximum weight matching (MWM) scheme can provide 100% throughput under admissible traffic for IB switches. However, the high complexity of MWM prohibits its implementation in high-speed switches. In this dissertation, a feedback-based arbitration scheme for CICB switches is studied, where cell selection is based on the provided service to virtual output queues (VOQs). The feedback-based scheme is named round-robin with adaptable frame size (RR-AF) arbitration. The frame size in RR-AF is adaptably changed by the serviced and unserviced traffic. If a switch is stable, the switch provides 100% throughput. Here, it is proved that RR-AF can achieve 100% throughput under uniform admissible traffic.

Switches with crosspoint buffers need to consider the transmission delays, or round-trip times to define the crosspoint buffer size. As the buffered crossbar switch can be physically located far from the input ports, actual round-trip times can be non-negligible. To support non-negligible round-trip times in a buffered crossbar switch, the crosspoint buffer size needs to be increased. To satisfy this demand, this dissertation investigates how to select the crosspoint buffer size under non-negligible round trip times and under uniform traffic. With the analysis of stability margin, the relationship between the crosspoint buffer size and round-trip time is derived.

Considering that CICB switches deliver higher performance than IB switches and require no speedup, this dissertation investigates the maximum throughput performance that these switches can achieve. It is shown that CICB switches without speedup achieve 100% throughput under any admissible traffic through a fluid model. In addition, a new hybrid scheme, based on longest queue-first (as input arbitration) and longest column occupancy first (as output arbitration) is proposed, which achieves 100% throughput under uniform and non-uniform traffic patterns.

In order to give a better insight of the feedback nature of arbitration scheme for CICB switches, a frame-based round-robin arbitration scheme with explicit feedback control (FRE) is introduced. FRE dynamically sets the frame size according to the input load and to the accumulation of cells in a VOQ. FRE is used as the input arbitration scheme and it is combined with RR, PRR, and FRE as output arbitration schemes. These combined schemes deliver high performance under uniform and nonuniform traffic models using a buffered crossbar with one-cell crosspoint buffers. The novelty of FRE lies in that each VOQ sets the frame size by an adjustable parameter,  $\Delta_{i,j}$ , which indicates the degree of service needed by VOQ(i,j). This value is adjusted according to the input loading and the accumulation of cells experienced in previous service cycles.

This dissertation also explores an analysis technique based on feedback control theory. This methodology is proposed to study the stability of arbitration and matching schemes for packet switches. A continuous system is used and a control model is used to emulate a queuing system. The technique is applied to a matching scheme. In addition, the study shows that the dwell time, which is defined as the time a queue receives service in a service opportunity, is a factor that affects the stability of a queuing system. This feedback control model is an alternative approach to evaluate the stability of arbitration and matching schemes.

# DESIGN AND STABILITY ANALYSIS OF HIGH PERFORMANCE PACKET SWITCHES

by Zhen Guo

A Dissertation

Submitted to the Faculty of

New Jersey Institute of Technology

in Partial Fulfillment of the Requirements for the Degree of

Doctor of Philosophy in Computer Engineering

**Department of Electrical and Computer Engineering**

January 2006

# APPROVAL PAGE

# DESIGN AND STABILITY ANALYSIS OF HIGH PERFORMANCE PACKET SWITCHES

# Zhen Guo

| Dr. Roberto Rojas-Cessa, Dissertation Advisor<br>Assistant Professor, Department of Electrical and Computer Engineering, New Jerse       | Date         |

|------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| Institute of Technology                                                                                                                  |              |

| Dr. Nirwan Ansari, Committee Member Professor, Department of Electrical and Computer Engineering, New Jersey Institute Technology        | Date<br>e of |

| Dr. Aleksandar Kolarov, Committee Member Technical Leader, Cisco Systems                                                                 | Date         |

| Dr. Edwin Hou, Committee Member Associate Professor, Department of Electrical and Computer Engineering, New Jers Institute of Technology | Date<br>ey   |

| Dr. Jie Hu, Committee Member Assistant Professor, Department of Electrical and Computer Engineering, New Jerse Institute of Technology   | Date         |

### **BIOGRAPHICAL SKETCH**

**Author:** Zhen Guo

**Degree:** Doctor of Philosophy

Date: January 2006

## **Undergraduate and Graduate Education:**

Doctor of Philosophy in Computer Engineering,

New Jersey Institute of Technology, Newark, NJ, January 2006

- Master of Science in Computer Engineering,

New Jersey Institute of Technology, Newark, NJ, August 2003

- Master of Science in Computer Engineering,

Chinese Academy of Space Technology, Beijing, China, July 1997

- Bachelor of Science in Computer Science,

Institute of Astronautics, Beijing Union University, Beijing, China, July 1991

Major: Computer Engineering

### **Presentations and Publications:**

Guo, Z. Rojas-Cessa, R. and Ansari, N. "Packet Switches with Internally-Buffered Crossbars" to appear as a book chapter

Guo, Z. and Rojas-Cessa, R.

"A Control Theoretic Analysis of Scheduling and Arbitration Schemes for Packet Switches,"

accepted by IEEE Sarnoff Symposium'06

Guo, Z. and Rojas-Cessa, R.

"Framed Round Robin Arbitration with Explicit Feedback Control for Combined Input-Crosspoint Buffered Packet Switches,"

submitted to IEEE International Conference on Communications (ICC'06)

Rojas-Cessa, R. Guo, Z. and Ansari, N.

"On the Maximum Throughput of a Combined Input-Crosspoint Queued Packet Switches."

under review in IEICE Transactions on Communications

Rojas-Cessa, R. and Guo, Z.

"Round-Robin Selection with Adaptable Frame-Size for Combined Input-Crosspoint Buffered Packet Switches,"

accepted by IEICE Transactions on Communications

Rojas-Cessa, R. Dong, Z. and Guo, Z.

"Load-Balanced Combined Input-Crosspoint Buffered Packet Switch and Long Round-Trip Times,"

IEEE Communications Letters, Vol. 4, No. 7, pp. 661-663, July 2005

Rojas-Cessa, R. Guo, Z. and Ansari, N.

"Combining Distributed and Centralized Arbitration Schemes for Combined Input-Crosspoint Queued Packet Switches,"

IEEE International Conference on Networks (ICON'05), Nov. 2005

Guo, Z. and Rojas-Cessa, R.

"Analysis of a Flow Control System for a Combined Input-Crosspoint Buffered Packet Switch,"

*IEEE Workshop on High Performance Switching and Routing (HPSR'05)*, pp. 336-340, May 2005

Guo, Z. and Rojas-Cessa, R.

"Stability Analysis of a Flow Control System for a Combined Input-Crosspoint Buffered Packet Switch,"

Conference on Information Sciences and Systems (CISS'05), March 2005

Guo, Z. and Savir, J.

"Analog Circuit Test using Transfer Function Coefficient Estimates," accepted and to appear in *IEEE Transactions on Instrumentation and Measurement*, Vol. 55, No. 1, Feb. 2006

Guo, Z. and Savir, J.

"Analog Circuit Test using Transfer Function Coefficient Estimates,"

*IEICE Transactions on Information and Systems Special Issue on Test and Verification of VLSI*, Vol. E87-D, No. 3, pp. 642-646, March 2004

Savir, J. and Guo, Z.

"Test Limitations of Parametric Faults in Analog Circuits,"

*IEEE Transactions on Instrumentation and Measurement*, Vol. 52, No. 5, pp. 1444-1454, October 2003

Guo, Z. and Savir, J.

"Analog Circuit Test using Transfer Function Coefficient Estimates," *IEEE International Test Conference (ITC'03)*, pp. 1155-1163, October 2003

Guo, Z. and Savir, J.

"Coefficient-Based Test of Parametric Faults in Analog Circuit," *IEEE Instrumentation and Measurement Technology Conference (IMTC'03)*, Vol. 1, pp. 71-75, May 2003

Savir, J. and Guo, Z.

"Test Limitation of Parametric Faults in Analog Circuits," *IEEE Asian Test Symposium (ATS'02)*, pp.39-44, Nov. 2002

Savir, J. and Guo, Z.

"On the Detectability of Parametric Faults in Analog Circuits," *IEEE International Conference on Computer Design (ICCD'02)*, pp. 273-276, Sept. 2002

Guo, Z. and Savir, J.

"Observer-Based Test of Analog Linear Time-Invariant Circuits," *IEEE Electronic Design, Test and Applications (DELTA'02)*, pp. 13-17, 2002

Guo, Z., Zhang, X., Savir, J. and Shi, Y.

"On Test and Characterization of Analog Linear Time-Invariant Circuits using Neural Networks,"

IEEE Asian Test Symposium (ATS'01), pp. 338-343, 2001

Guo, Z. and Savir, J.

"Algorithm-Based Fault Detection of Analog Linear Time-Invariant Circuits," *IEEE Instrumentation and Measurement Technology Conference (IMTC'01)*, Vol. 1, pp. 49-54, 2001

| To my parents who made me realize anything can be achieved if you put forth the effort. |

|-----------------------------------------------------------------------------------------|

|                                                                                         |

| To my beloved wife for her always believing in me.                                      |

|                                                                                         |

|                                                                                         |

|                                                                                         |

|                                                                                         |

|                                                                                         |

|                                                                                         |

|                                                                                         |

|                                                                                         |

|                                                                                         |

|                                                                                         |

#### ACKNOWLEDGMENT

First and foremost, I would like to express my sincere appreciation to my advisor and mentor, Professor Roberto Rojas-Cessa, for his understanding, encouragement, invaluable instructions. I deeply appreciate his advice, guidance and academic insight. I treasure the opportunities he created for me to continue and complete my doctoral research. His advice is essential to the completion of this dissertation. I will never forget his help.

I am deeply grateful to Professor Nirwan Ansari, Associate Chair and Academic Advisor, for his tireless help, encouragement, guidance and support. I respect him and I am fortunate to get help from him.

I am deeply grateful to Dr. Ronald Kane, Dean of Graduate Studies, for his timely, continuous and invaluable support and encouragement. Without his help, it would be harder for me to complete my doctoral research.

I am deeply grateful to Professor Atam Dhawan, Chair of ECE Department, for his understanding and encouragement.

I acknowledge the valuable comments and discussion with my committee members: Dr. Aleksandar Kolarov (Technical Leader, Cisco Systems), Professor Edwin Hou and Professor Jie Hu. I would like to give thanks for their comments and helpful reviews on my dissertation. I also extend my special thanks to Professor Kenneth S. Sohn for his help, Professor Timothy N. Chang and Professor Durga Misra for their encouragement.

The friendship of Zhiyun Yang, Ying Li, Kun Li, Puttiphong Jaroonsiriphan, Qiming He, Yingqin Yuan, Chuanbi Lin, Ziqian Dong, Zhen Qin, Chen Fang, Hong Zhang, Jun Jiang, Li Zhu, and Amey B. Shevtekar is much appreciated.

Finally, I express my special gratitude to my parents for their dedicated and endless love to me, without their love and guidance I would be lost. I would like to thank my beloved wife, Yueling Li, for her patient understanding, help, support and love. I cherish and enjoy the happiness which my lovely daughter brings to me during these years. Last, but not least, I would like to thank my brother for his faith in me.

# TABLE OF CONTENTS

| Cl | Chapter Page |                                                                                                                                   |         |

|----|--------------|-----------------------------------------------------------------------------------------------------------------------------------|---------|

| 1  | INT          | RODUCTION                                                                                                                         | 1       |

|    | 1.1          | Introduction to Packet Switches                                                                                                   | 1       |

|    | 1.2          | Development of Combined Input-Crosspoint Buffered Packet Switches                                                                 | 2       |

|    | 1.3          | Research Challenges and Motivations                                                                                               | 11      |

| 2  | R            | BILITY ANALYSIS OF FRAME-BASED ARBITRATION WITH ROUND-<br>OBIN SELECTION FOR A COMBINED INPUT-CROSSPOINT BUFFERED<br>ACKET SWITCH | 16      |

|    | 2.1          | Introduction                                                                                                                      | 16      |

|    |              | 2.1.1 Combined Input-Crosspoint Buffered Switch Model                                                                             | 17      |

|    |              | 2.1.2 Round-Robin with Adaptable-Size Frame (RR-AF) Arbitration Scheme                                                            | 18      |

|    | 2.2          | Stability Study                                                                                                                   | 24      |

|    | 2.3          | Conclusions                                                                                                                       | 30      |

| 3  |              | ALYSIS OF A FLOW CONTROL SYSTEM FOR A COMBINED INPUT-<br>ROSSPOINT BUFFERED PACKET SWITCH                                         | 31      |

|    | 3.1          | Introduction                                                                                                                      | 31      |

|    | 3.2          | Flow Control Mechanism and Stability Analysis                                                                                     | 32      |

|    | 3.3          | Design of an Input Shaper                                                                                                         | 36      |

|    | 3.4          | Conclusions                                                                                                                       | 39      |

| 4  |              | OUGHPUT OF A COMBINED INPUT-CROSSPOINT BUFFERED PACKET WITCH WITHOUT SPEEDUP                                                      | Γ<br>42 |

|    | 4.1          | Introduction                                                                                                                      | 42      |

|    | 4.2          | CICB Switch and Fluid Model                                                                                                       | 44      |

|    | 4.3          | Throughput Analysis of a CICB Switch                                                                                              | 46      |

|    | 4.4          | Arbitration Scheme for 100% Throughput                                                                                            | 52      |

|    | 4.5          | Simulation Study of LQF+LCO                                                                                                       | 55      |

|    |              | 4.5.1 Uniform Traffic                                                                                                             | 56      |

# TABLE OF CONTENTS (Continued)

| C  | Chapter Pa |        |                                                                                                    | Page |

|----|------------|--------|----------------------------------------------------------------------------------------------------|------|

|    |            | 4.5.2  | Nonuniform Traffic: Unbalanced                                                                     | . 56 |

|    |            | 4.5.3  | Nonuniform Traffic: Diagonal                                                                       | . 57 |

|    |            | 4.5.4  | Nonuniform Traffic: Power of Two (PO2)                                                             | . 58 |

|    | 4.6        | Concl  | usions                                                                                             | . 58 |

| 5  | C          | ONTRO  | ROUND-ROBIN ARBITRATION WITH EXPLICIT FEEDBACK OL FOR COMBINED INPUT-CROSSPOINT BUFFERED PACKET ES |      |

|    | 5.1        |        |                                                                                                    |      |

|    |            |        | uction                                                                                             |      |

|    | 5.2        |        | Switch Model                                                                                       |      |

|    |            | 5.2.1  | Controlling the Service Rate by Explicit Feedback                                                  | 62   |

|    | 5.3        | FRE A  | Arbitration Scheme                                                                                 | 67   |

|    | 5.4        | Perfor | mance Evaluation                                                                                   | 69   |

|    |            | 5.4.1  | Uniform Traffic                                                                                    | 69   |

|    |            | 5.4.2  | Nonuniform Traffic: Unbalanced                                                                     | 71   |

|    |            | 5.4.3  | Nonuniform Traffic: Diagonal                                                                       | 72   |

|    |            | 5.4.4  | Nonuniform Traffic: Chang's and Asymmetric                                                         | 72   |

|    | 5.5        | Concl  | usions                                                                                             | 73   |

| 6  |            |        | THEORETIC ANALYSIS OF ARBITRATION AND MATCHING S FOR PACKET SWITCHES                               | 75   |

|    | 6.1        | Introd | uction                                                                                             | 75   |

|    | 6.2        | Switch | Modeling in a Continuous System                                                                    | 76   |

|    | 6.3        | Select | ion of a Queue in a Minimum System                                                                 | 77   |

|    | 6.4        | Examp  | ole: Analysis of a Matching Scheme of an IB Switch                                                 | 82   |

|    | 6.5        | Conclu | usions                                                                                             | 87   |

| 7  | CON        | ICLUSI | ONS                                                                                                | 88   |

| RE | EFERI      | ENCES  |                                                                                                    | 91   |

# LIST OF FIGURES

| Figu | Tigure Pag                                                                     |    |  |

|------|--------------------------------------------------------------------------------|----|--|

| 1.1  | Output-buffered crossbar switch.                                               | 4  |  |

| 1.2  | Input-buffered crossbar switch                                                 | 5  |  |

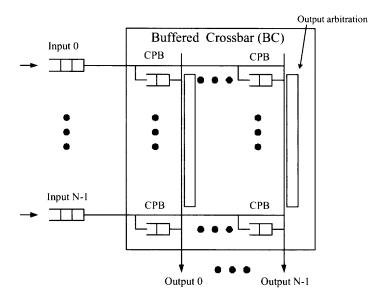

| 1.3  | Combined input-crosspoint buffered crossbar switch                             | 7  |  |

| 1.4  | Scalable distributed-arbitration switch structure.                             | 8  |  |

| 1.5  | Combined input-crosspoint buffered crossbar switch with FIFO input buffers.    | 9  |  |

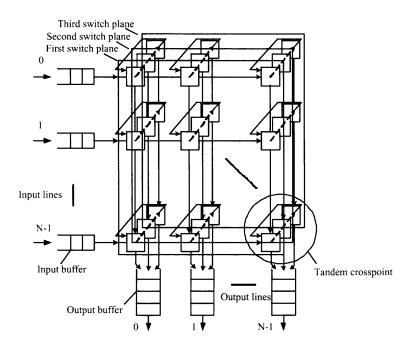

| 1.6  | Tandem-crosspoint (TDXP) switch with three planes                              | 10 |  |

| 2.1  | $N \times N$ buffered crossbar with VOQs                                       | 17 |  |

| 2.2  | Example of RR-AF among three queues in a $3 \times 3$ switch                   | 20 |  |

| 2.3  | Example of VOQs missing opportunities for cell forwarding                      | 21 |  |

| 2.4  | Average delay of RR-AF arbitration under Bernoulli and bursty uniform traffic. | 22 |  |

| 2.5  | Throughput performance of RR-AF under unbalanced traffic                       | 24 |  |

| 2.6  | Average cell delay of RR-AF under Chang's and asymmetric traffic               | 24 |  |

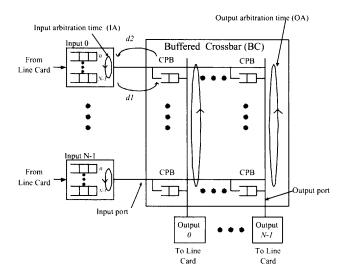

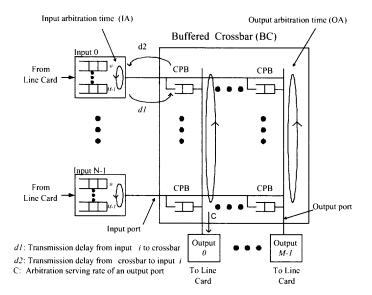

| 3.1  | Combined input-crosspoint buffered crossbar switch                             | 33 |  |

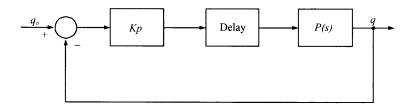

| 3.2  | Block diagram of P control in a VOQ-CPB closed loop                            | 35 |  |

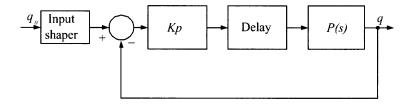

| 3.3  | Block diagram of P control with input shaper in a VOQ-CPB closed loop          | 37 |  |

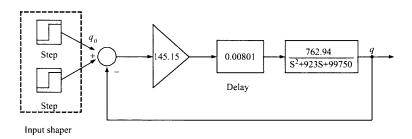

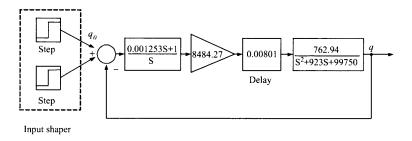

| 3.4  | Diagram of a P control with input shaper                                       | 39 |  |

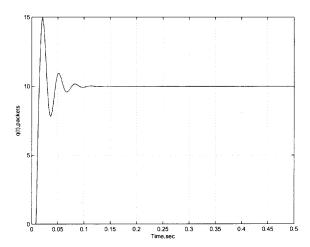

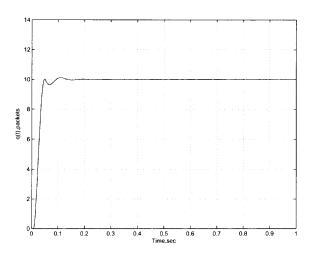

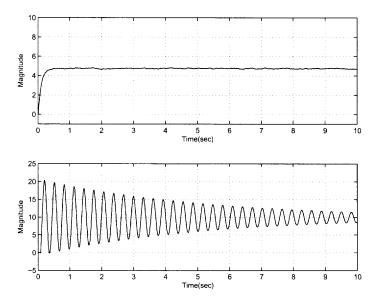

| 3.5  | Simulation result on a P control without input shaper                          | 39 |  |

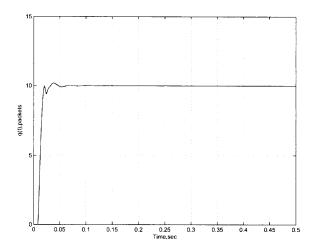

| 3.6  | Simulation result on a P control with input shaper                             | 40 |  |

| 3.7  | Diagram of a PI control with input shaper.                                     | 40 |  |

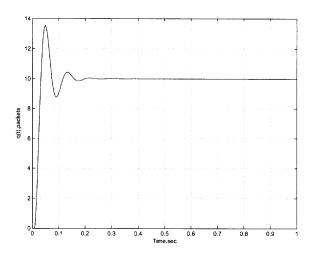

| 3.8  | Simulation result on a PI control without input shaper                         | 41 |  |

| 3.9  | Simulation result on a PI control with input shaper                            | 41 |  |

| 4.1  | Scheduling in a CIOB crossbar switch                                           | 47 |  |

| 4.2  | Scheduling in a one-cell buffered crossbar switch.                             | 48 |  |

| 4.3  | Example of a decomposed matrix for a $4 \times 4$ switch                       | 51 |  |

| 4.4  | Illustration on the LCO scheme                                                 | 52 |  |

# LIST OF FIGURES (Continued)

| Figu | re                                                                                                              | Page |

|------|-----------------------------------------------------------------------------------------------------------------|------|

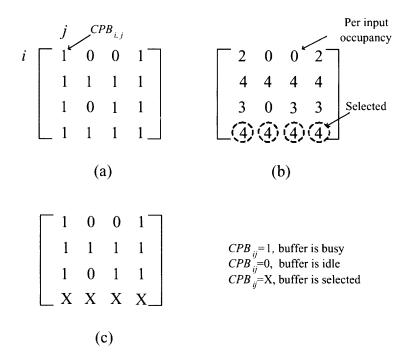

| 4.5  | Example of selection by performing LCO in a $4 \times 4$ switch                                                 | 54   |

| 4.6  | A counter example of crosspoint-buffer selection by MCBF in a $4 \times 4$ switch.                              | 55   |

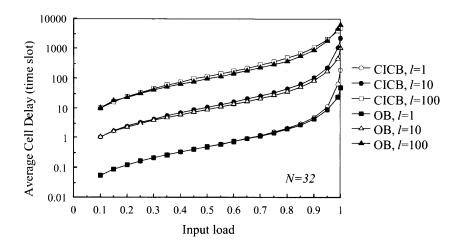

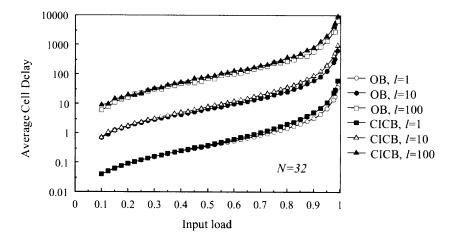

| 4.7  | Average delay of a $32 \times 32$ switch under uniform traffic                                                  | 56   |

| 4.8  | Average delay of a $32 \times 32$ switch under unbalanced traffic with $w=0.5$                                  | 57   |

| 4.9  | Average delay of a $32 \times 32$ switch under diagonal traffic                                                 | 58   |

| 4.10 | Average delay of a $30 \times 30$ switch under PO2 traffic                                                      | 59   |

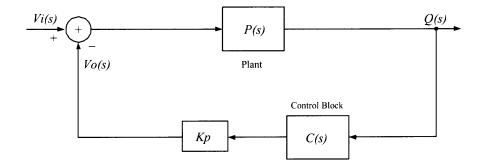

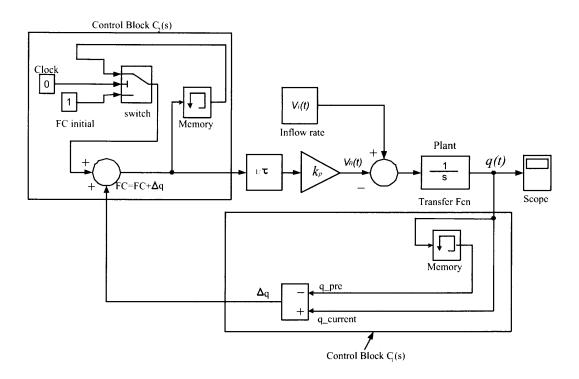

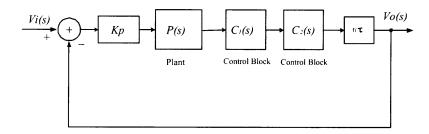

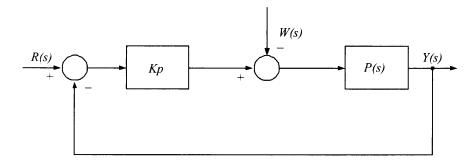

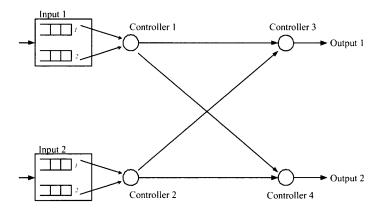

| 5.1  | Block diagram of a feedback control system                                                                      | 62   |

| 5.2  | Block diagram of the explicit feedback control system                                                           | 63   |

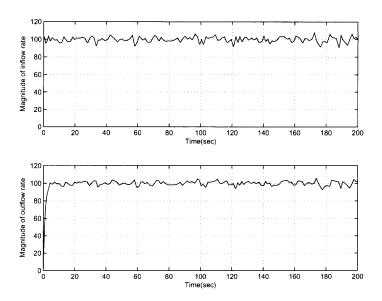

| 5.3  | Simulink results of the outflow rate tracking the inflow rate                                                   | 64   |

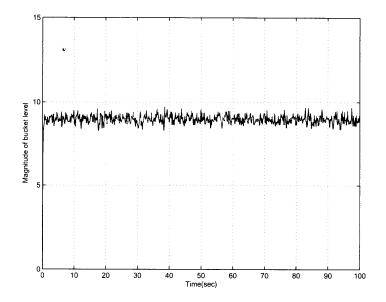

| 5.4  | Simulation result on fluid level of the example                                                                 | 65   |

| 5.5  | Block diagram of the fluid level control with a proportional control                                            | 65   |

| 5.6  | Example of FRE arbitration                                                                                      | 69   |

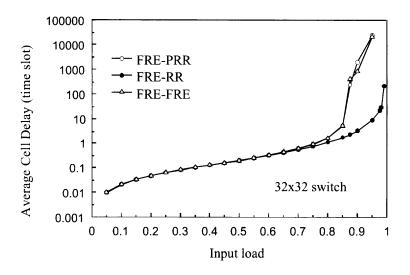

| 5.7  | Performance with Bernoulli and bursty arrivals                                                                  | 70   |

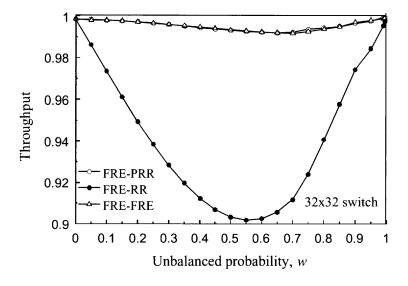

| 5.8  | Performance under unbalanced traffic                                                                            | 71   |

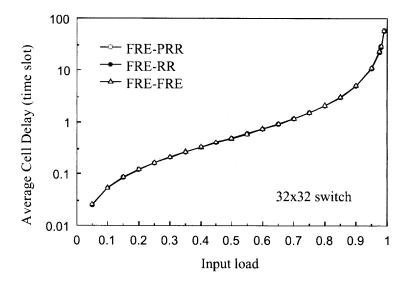

| 5.9  | Performance under diagonal traffic                                                                              | 72   |

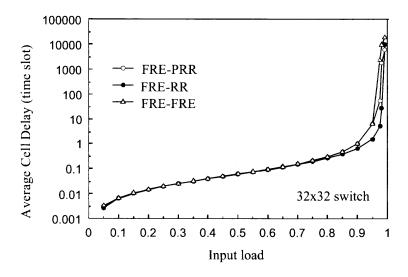

| 5.10 | Performance under Chang's traffic                                                                               | 73   |

| 5.11 | Performance under asymmetric traffic                                                                            | 74   |

| 6.1  | Block diagram of a queue occupancy control system with disturbance                                              | 76   |

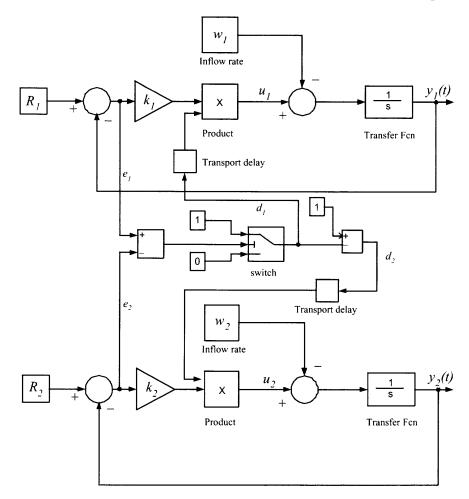

| 6.2  | Block diagram of a two-queue control system with on/off control                                                 | 78   |

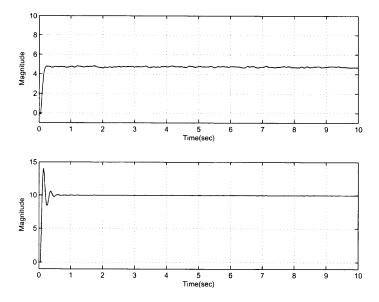

| 6.3  | Simulation result for a two-queue queue occupancy control system with on/off control and dwell time of 0.04 sec | 82   |

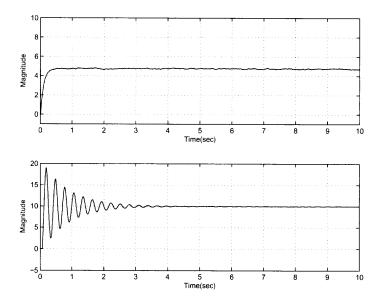

| 6.4  | Simulation result for a two-queue queue occupancy control system with on/off control and dwell time of 0.06 sec | 83   |

| 6.5  | Simulation result for a two-queue queue occupancy control system with on/off control and dwell time of 0.07 sec | 84   |

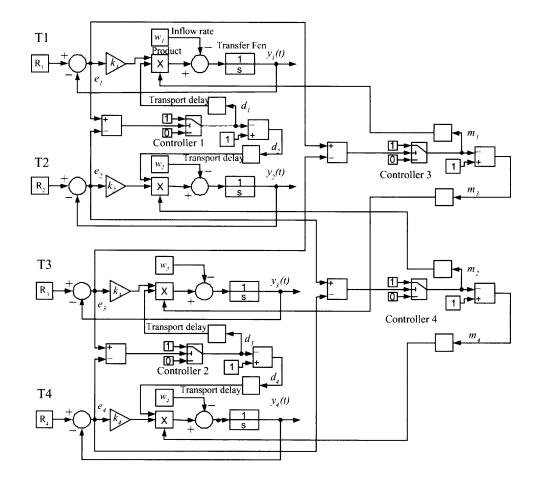

| 6.6  | Block diagram of a $2 \times 2$ IB switch                                                                       | 84   |

| 6.7  | Block diagram of a four-queue control model in a $2 \times 2$ IB switch                                         | 85   |

#### **CHAPTER 1**

### INTRODUCTION

#### 1.1 Introduction to Packet Switches

The exchange of information within the Internet is made possible by the switches and routers interconnecting networks. These routers facilitate networks to communicate by using a shared language or protocol. An example of such protocols employed at different network layers are Ethernet, asynchronous transfer mode (ATM), or the popular TCP/IP suite. These protocols determine the packet formats and the way to find a route from the source host to the destination host.

In the remainder of this dissertation, the IP protocol is considered to define the packet term. Therefore, switches and routers are required to process IP packets. However, a large number of packet switches base their architecture on ATM technology, where different from IP packets, ATM packets have fixed lengths, called cells. IP packets, however, can be handled by cell-based switches as variable-length packets are segmented at the input ports, and switched from input to output in a cell-based fashion. Variable-length IP packets are re-assembled at the output ports, before they depart to another switches. Here, fixed-length packets are referred as cells, which are not necessarily ATM cells.

Packet switches identify the destination of packets at the input ports and forward them to the appropriate output ports, completing in this way the packet processing at layer 2 of the open system interconnection (OSI) model. Those switches that find out information about the connectivity between networks and paths to reach different possible destinations are referred to as routers. This information is summarized in a forwarding table that is used to determine the output port of the switch according the destination of the traversing packet. These routers are devices performing tasks of layers 2 and 3. Once output ports are defined in a forwarding table, a switch performs the scheduling and forwarding of packets.

As interconnection technologies mature, such as those base on optical technology, data rate increases and routers need to keep up with that by processing packets fast. The functions that require high performance in routers is identifying the packet type, so that the packet can be processed accordingly (including forwarding), and switching the packet from an input to an output port. Here, switching a packet means the packet is transferred from the input port to an output port. The task seems simple; however, it gets complex as there is the possibility that several packets need to go from different inputs to the same output. Therefore, this creates the necessity of interconnecting input and output ports, buffering packets and scheduling the packet switching time. A scheduler selects the time a packet is switched to the output. The complexity of the scheduler depends on the buffering strategy and on the selection scheme used.

A packet switch is comprised of input port cards and a switch fabric. An input port card, also known as a line interface card (LIC), determines the processing the switch performs on each packet. Some of these functions are: packet classification, destination lookup (IP lookup for IP packets), buffering, packet modification, and packet interfacing for internal switching. The switch fabric is an interconnection network used by the LICs. The way a switch operates internally depends on the switch fabric used. A plethora of switch fabrics have been developed for packet switches. Many of them have been incepted for the telephone network and are now applied to packet networks.

### 1.2 Development of Combined Input-Crosspoint Buffered Packet Switches

The internet continues to experience extraordinary growth. By any measure, the growth is remarkable on all fronts: the number of hosts, the number of users, the amount of traffic, the number of links, the bandwidth of individual links. In order to keep pace with the growth of Internet usage, higher capacity packet switches are needed with aggregate data rates of multiple terabits per second, and forwarding rates of billions of packets per second. However, after 10-years' booming development on switch, some people wander

how far can switch go forward in face of this big challenge? Novel switch architectures and arbitration schemes might provide the answer [10, 63].

Crossbar switching fabrics are very popular for switch implementation due to their non-blocking capability, simplicity, and their market availability. The performance of a switch can be analyzed according to the adopted buffering strategy.

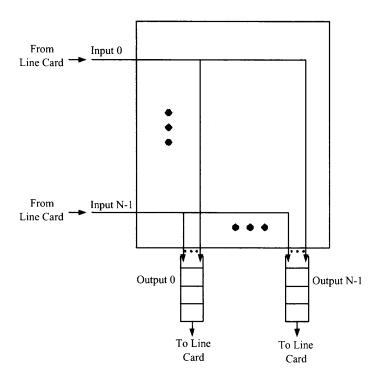

An OB switch has no queues at the input ports. All arriving cells must be immediately delivered to their outputs. A major disadvantage is that simultaneously delivery of all arriving cells to the outputs require high internal interconnection bandwidth and memory bandwidth. For an  $N \times N$  OB switch, the memory has to support N write accesses (to write N cells into output buffer) and one read access (to send one cell to the outgoing link) in one-cell time. This means that an OB switch must operate N+1 times faster than the line rate. This requirement is known as internal speedup of a switch which is defined as the number of times that the switch core works faster than the input line rate. To ensure that there are no packets queued at the input ports, it is widely believed that an OB switch has to have an internal speedup of N. Unfortunately, the increase in the line rate and/or switch size makes it extremely difficult and impractical to build memories with adequate capacity for such high-bandwidth. However, this architecture has been used as a comparison reference for any switch model because of its high throughput and low delay. A switch with buffers\* at the inputs, named input-buffered (IB) switch. IB switches are desirable because of their scalability and low hardware requirement. The IB switch has an internal speedup of 1 (also considered as no speedup) because the crossbar fabric has the same speed as that of the external line. It is well-known that, if first-in first-out (FIFO) input queues are used to hold arriving packets, head-of-line (HOL) blocking problem limits the throughput of only 58.6%. To eliminate HOL blocking, virtual output queuing (VOQ) can be used, each input buffer is partitioned into N queues with one queue for each output

<sup>\*</sup>This dissertation uses the terms queue and buffer interchangeably.

Figure 1.1 Output-buffered crossbar switch.

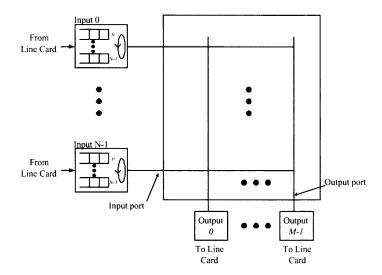

port (hence the name virtual output queuing). Each arriving packet is classified and then queued into the appropriate VOQ according to its destination output port.

However, IB switches need to resolve input and output contentions before cells are forwarded to the outputs. Arbiters at input and outputs perform the contention resolution by means of a matching process. Furthermore, the switching performance of an IB switch requires complex matching schemes to provide high-switching performance. This high complexity limits the switch port speeds. The requirements for arbiters to be feasible and to provide a high performance are: (a) low complexity, (b) fast contention resolution, (c) fairness and, (d) high matching efficiency. As an example, the matching scheme must perform input or output arbitration within 8 ns in an IB switch with 40 Gbps (OC-768) ports and 80-byte cells, assuming that input and output arbitrations may use up to half of a time slot and that the transmission delays are decreased to negligible amounts (e.g., the arbiters are implemented in the same chip, in a centralized way).

Figure 1.2 Input-buffered crossbar switch.

A matching can be classified as maximum or maximal. A maximum match is a maximum cardinality bipartite matching of input with packets queued to N outputs. A maximal match is a matching that cannot be improved without removing some input-output matches. A maximum weight matching (MWM) algorithm provides 100% throughput for any no-overbooking traffic theoretically. However, the scheme's complexity prevents its implementation for fast speeds. Maximal matching schemes have been considered as an alternative to maximum matching schemes [17]; iSLIP [14, 16], dual round-robin matching (DRRM), and longest output occupancy first algorithm (LOOFA) are some examples. To make up for the lack of efficiency that a maximal scheme has (compared to a maximum type), a number of iterations (where the number of iterations is the number of times that an algorithm is performed to obtain a cumulative result), speedup, or the number of both is used, as in LOOFA. iSLIP is a typical example of an iterative matching scheme. iSLIP provides 100% throughput for uniform traffic, but because of the arbitration time, it has been proposed for a small number of ports due to its centralized implementation. The transmission of phases such as request, grant and acknowledge are performed within a cell slot between input and output arbiters. This transmission of information reduces the

available time for arbitration because transmission phases are performed during the cell slot in serial with input and output arbitration, even when the transmission is done within a single chip.

Speedup is another approach to tackle the lack of efficiency by scheduling on IB switch, when the internal speedup is between 1 and N-1, buffering is required at both the inputs and outputs [82]. Hence, a combination of an input buffered and an output buffered switch is required, which is combined input and output buffered switch (CIOB). With a speedup of 2, it is proved that any maximal matching algorithm can achieve 100% throughput under any admissible traffic. However, speedup shortens the schedule time. Iterative-based algorithm may have no time to find a maximal matching.

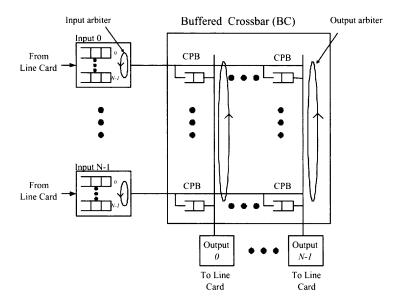

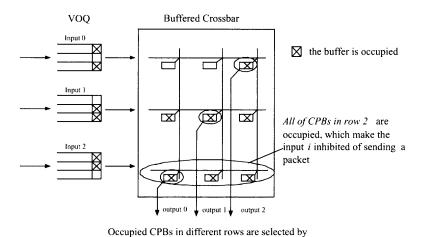

The arbitration in a crosspoint buffered (CB) switch is only performed for input selection at each output of the buffered crossbar, where packets stored in the crosspoint buffers are considered. A CB switch is called a pure buffered crossbar because in this architecture buffering is only at the crosspoints. A large crosspoint buffer has been utilized to minimize cell loss rate. However, the number of buffers in a crossbar grows in the same order as the number of crosspoints,  $O(N^2)$ . This makes implementation costly for a large buffer size or large N. One way to keep the buffer complexity feasible is to use crosspoint buffers that are small in size.

An example of a CB switch was proposed in [1], where a  $2 \times 2$  crossbar chip with a crosspoint memory of 16 Kbytes was implemented to provide an acceptable cell loss. In order to reduce the crosspoint buffer size, input buffers can be used.

Buffered crossbar switches need output arbiters to select a cell, which is stored in the crosspoint buffer, to be sent to the output port. Therefore, the performance of this switch depends on the output arbitration. The output arbitration scheme considers all crosspoint buffers and selects one according to a selection policy. Therefore, the time and computation complexity of an output arbitration scheme is in function of the number of crosspoint buffers (or inputs, N) at an output, or O(N).

Figure 1.3 Combined input-crosspoint buffered crossbar switch.

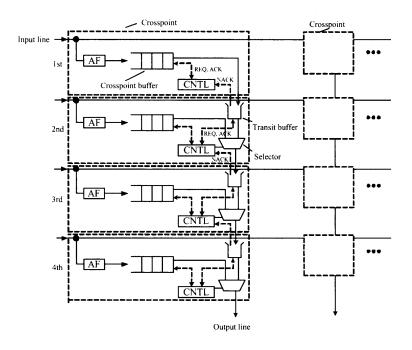

An example of a BC switch that emphasizes on the output arbitration is found in the scalable distributed arbitration (SDA) switch [8]. The SDA switch reduces the arbitration time by using a distributed approach for the output arbitration in each output. Instead of considering N input at any given time, an arbiter is partitioned into N-1 selectors, where each selector considers two buffers. This switch performs random selection of cells (crosspoints) at each output. The SDA switch has a crosspoint buffer, a transit buffer, an arbitration-control block (CNTL), and a selector at every crosspoint. A crosspoint buffer sends a request (REQ) to CNTL if there is at least one cell stored in the crosspoint buffer. A transit buffer stores several cells that are sent from either the upper crosspoint buffer or upper transit buffer. The transit buffer has a size of one or a few cells. The transit buffer size is determined by the round-trip delay of control signals between two adjacent crosspoints. The longest control signal transmission distance for arbitration within one cell time is the distance between two adjacent crosspoints. In a switch with an implementation of the output arbiters in a centralized fashion, the control signal for arbitration must pass through all the crosspoint buffers, belonging to the same output line to complete the selection

each time slot, and therefore, the arbitration time depends on the number of inputs (or crosspoints). In this way, the arbitration time in the SDA switch is independent of the number of input ports.

Figure 1.4 Scalable distributed-arbitration switch structure.

The SDA switch was tested under uniform traffic with Bernoulli arrivals with an input load of 0.95 for different switch sizes ( $N = \{4, ..., 32\}$ ). This switch delivers a cell average delay of less than 100 time slots. Another feature of the SDA switch is fairness. This is achieved by the nature of the distribute selection scheme using different selection probabilities for different inputs at a crosspoint, such that the total selection probability by an output is the same for any input.

In order to reduce the crosspoint buffer size, input buffers can be used with larger capacity as these buffers are located in the input ports, and the amount of memory at the input ports (outside of the buffered crossbar) can be of large size (e.g., several memory

Figure 1.5 Combined input-crosspoint buffered crossbar switch with FIFO input buffers.

chips). CICB switches that use the FIFO policy in their input buffers are the simplest of them, and are called FIFO-CICB.

In [6], an input and crosspoint buffering matrix switching architecture with FIFO input buffers, or FIFO CICB switch, was proposed. In [7], a FIFO-CICB switch input buffers and random selection policy at the output was proposed and shown to provide high throughput. CICB switches with single-cell crosspoint buffers were proposed in [2, 3]. These switches also used FIFO input buffers at the input ports, or FIFO-CICB switches. The switches provide a throughput of 91%, where, however, the HOL blocking [5] was still present. The FIFO buffers at the inputs limit the maximum throughput in that switch because the HOL blocking can not be completely eliminated. These switches showed the need to remove the HOL blocking that was present in IB switch and then, inherited by FIFO CICB switches.

Another example of a FIFO-CICB switch, with a different architecture approach, a multiple-plane architecture, is the tandem-crosspoint (TDXP) switch [9]. The main purpose of the TDXP switch is to overcome HOL blocking by using the parallel switch technology.

This switch has multiple crossbar switch planes as shown in Figure 1.6. The switch planes are connected in tandem at each crosspoint. There is a one-cell buffer in the crosspoint. The internal speedup in each plane is the same as the input/output line speed. Each switch plane can transmit only one cell to each output port within one cell time slot. The HOL blocking phenomenon occurs at the input buffers, where the FIFO policy is used.

Figure 1.6 Tandem-crosspoint (TDXP) switch with three planes.

The TDXP switch improves the switching performance by using multiple planes. In this way, cells will not cause HOL blocking as there is room for a cell in each switch plane. This is similar to letting the first K cells of a FIFO participate in the output arbitration process, where K is the number of planes in the TDXP switch. In a  $32 \times 32$  switch, the throughput provided is above 95%, which is a significant improvement over an IB switch with FIFO input buffers.

As in IB switches, the HOL blocking problem for FIFO buffers can be overcome in CICB switches by using VOQs, or VOQ-CICB switches. For the sake of brevity, VOQ-CICB switches are referred as CICB switches in the remainder of this dissertation.

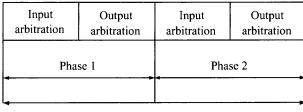

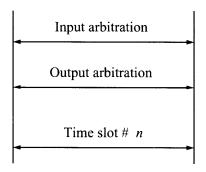

CICB switches use time efficiently as input and output port selections are performed separately. For each input, there is one input scheduler which separately deals with input contention, i.e. to decide which VOQ in this input is allowed to transfer a cell into the switch core. In a similar way, there is an output scheduler which independently deals with output contention for each output, i.e. to decide which crosspoint buffer is allowed to transfer a cell out of the switch core. Back to the example of the stringent timing, a CICB switch with 40-Gbps and 80-byte packets can perform input (or output) arbitration within 16 ns, therefore, the timing for arbitration is extended.

### 1.3 Research Challenges and Motivations

In CICB switches, high matching efficiency is achieved with simpler arbitration schemes than those used in bufferless crossbars (i.e., IB switches) at the expense of having to accommodate buffers in the crosspoints.

A CICB switch with timestamp-based arbitration and VOQs at the input ports showed that the crosspoint-buffer size can be small if the VOQs are provided with enough storing capacity [12]. Furthermore, it has been shown that a CICB switch using one-cell crosspoint buffers (CIXB-1), a simple round-robin arbitration (RR) scheme for input/output arbitration, and a credit-based flow control provide 100% throughput for uniform traffic [42]. However, as actual traffic may present nonuniform distributions, it is necessary to provide arbitration schemes that provide 100% throughput for admissible traffic. Admissible traffic is defined as: Let us denote  $\lambda_{i,j}$  to the cell arrival rate at input i for output j that is received in  $VOQ_{i,j}$ . Let us consider admissible traffic such that

$$\sum_{i} \lambda_{i,j} \le 1 \tag{1.1}$$

and

$$\sum_{i} \lambda_{i,j} \le 1. \tag{1.2}$$

One way to provide 100% throughput under nonuniform traffic patterns is by using weight-based arbitration schemes, where weights are assigned to input queues proportionally to their occupancy or HOL cell age. It has been shown that weight-based [46] and prioritybased [48] schemes in buffered crossbars can provide high throughput under various traffic patterns. Two schemes were presented in [46]: one is based on the selection of the longest VOQ occupancy at inputs and round-robin selection at the outputs; the other scheme is based on the selection of the oldest cell first (OCF) instead of VOQ occupancy. However, weight-based schemes need to perform comparisons among all contending queues, which can be a large number, thus increasing the implementation complexity. Moreover, weightbased schemes (e.g., queue-occupancy based) may starve some queues for very long time to provide more service to the congested ones, presenting unfairness. On the other hand, RR algorithms have been shown to provide fairness and implementation simplicity, as no comparisons are needed among queues, and high-performance under uniform traffic [14]. However, schemes based on round-robin selection have not been shown to provide nearly 100% throughput under nonuniform traffic patterns with a buffered crossbar that have crosspoint buffers of small size. It has been shown that a switch using RR needs a large crosspoint buffer to provide high throughput under admissible unbalanced traffic [15], where the unbalanced traffic model is a nonuniform traffic pattern [42]. This large buffer can make the implementation of a switch costly.

A question arises: is it possible to provide an arbitration scheme based on roundrobin selection for buffered crossbars such that a switch can deliver high throughput under admissible traffic with nonuniform distributions, such as unbalanced traffic, with a small crosspoint buffer size? Frame-based matching have been shown to have improved switching performance under different traffic scenarios [59]. However, how to set the frame size is a complex issue. In Chapter 2, an arbitration scheme is introduced for buffered crossbars, it is based on round-robin selection, which uses the concept of adaptable-size frame. The studied scheme is named round-robin arbitration with adaptable frame size (RR-AF) selection [60], [61]. The frame size is called adaptable as it is determined by the amount of service that a queue receives. In this chapter, it is shown that this arbitration scheme can achieve nearly 100% throughput under several nonuniform traffic patterns with one-cell crosspoint buffers. The performance results presented in this chapter shows that this switch retains the high performance, 100% throughput, of simple round-robin arbitration under uniform traffic.

In Chapter 3, it is investigated how to select the crosspoint buffer size under non-negligible round trip times. With the analysis of stability margin, the relationship between the crosspoint buffer size and round trip time  $(R_0)$  is derived.

A flow control mechanism is considered, where the parameter in observation is the queue occupancy. In this case, control theory can be applied to analyze and design queue management schemes. Most of AQM work focuses on supporting congestion management for the transmission control protocol (TCP) flows. However, only a few of the previous works are applied to switches. The main focus of this chapter is to apply control theory to analyze a flow control mechanism for a CICB switch. It is considered that credit-based flow control is used for avoiding buffer overflow [21]. This flow control mechanism has been applied to CICB switches with a negligible transmission delay [42], where the transmission delays are the propagation delays of sending a cell from the input port to a crosspoint, and of sending the flow control information from the crosspoint buffer to the input port. The sum of the transmission delays plus the selection delays at inputs (VOQ selection) and outputs (crosspoint buffer selection) is called round-trip time. As the buffered crossbar switch can be physically located far from the input ports, actual round trip times can be non-negligible. To support non-negligible round-trip times in a buffered-crossbar switch,

the crosspoint-buffer size needs to be increased, such that up to  $R_0$  cells can be buffered. Non-negligible round trip delays have been considered for practical implementations [35, 36].

However, in a credit-based flow control mechanism, the stability of the switch, as a product of the round-trip times and crosspoint-buffer size, might be difficult to analyze. Therefore, a proportional (P) controller is used for a flow control mechanism for a CICB switch. The relationship between the round-trip times and crosspoint buffer size and the effect on stability is analyzed.

Stability is of utmost importance in switch design. Stability of a switch determines its throughput. If a switch is stable, it can provide 100% throughput. It has been shown that CICB switches are stable under uniform admissible traffic. In Chapter 4, it is shown that a CICB switch achieves 100% throughput without speedup under any admissible traffic and prove its stability through a fluid model. In addition, a new hybrid scheme with longest queue first as input arbitration and longest column occupancy first as output arbitration is proposed, which can achieve 100% throughput under uniform and non-uniform traffic patterns.

The intuition of this result lies on the knowledge that CICB switches provide higher performance than IB switches [42, 46], and that IB switches can provide 100% throughput under admissible traffic with no speedup [44], although with a high-complexity matching scheme.

In RR-AF scheme, the frame size increases by a constant number, independently of the actual size needed, each time a frame is completely served. The frame size decreases each time a VOQ misses an opportunity to be served. Although this scheme provides high performance, it is difficult to analyze. To give a better insight into the feedback nature of arbitration schemes for CICB switches, Chapter 5 introduces a frame-based round-robin arbitration scheme with explicit feedback control (FRE) for CICB packet switches. This scheme adopts a frame-based arbitration scheme that dynamically sets

the frame size according to the input load and to the number of cells accumulated in the input queues. The scheme is analyzed with control theory and the switching performance is studied by computer simulations. The combination of FRE (as the input arbitration scheme) with other weightless arbitration schemes (as output arbitrations) are tested. It is shown that FRE provides high throughput under several admissible traffic patterns using a CICB switch with one-cell crosspoint buffers.

The existent stability analysis approaches concentrate on the evolution of the queue length. If no overflow occurs to any queue, then the switch is stable. In fact, each queue is one subsystem of the whole switch, one important factor in the switch system is the arbitration scheme as this decides which queue can obtain the opportunity to transfer packets and also determines how often and how soon the queue can be served.

A question arises: what is the degree in a scheduling scheme affects the stability of the whole system, and how to analyze these issues using a control-theoretical technique?

In Chapter 6, a queuing system is modeled and it is shown that the dwell time, defined as the time a queue receives service in a service opportunity, is a factor that affects the stability of a queuing system. Furthermore, a case study of an arbitration scheme on a  $2 \times 2$  switch is used to show that the feedback control model is an alternative approach to evaluate the stability of an arbitration scheme.

### **CHAPTER 2**

# STABILITY ANALYSIS OF FRAME-BASED ARBITRATION WITH ROUND-ROBIN SELECTION FOR A COMBINED INPUT-CROSSPOINT BUFFERED PACKET SWITCH

### 2.1 Introduction

Here, a frame is related to VOQ. A frame is the set of one or more cells in a VOQ that are eligible for matching in successive time slots. However, how to set the frame size is a complex issue [19, 20, 77]. The studied scheme is named round-robin arbitration with adaptable frame size selection (RR-AF) [60, 61]. There are two novelties associated with RR-AF. First, it is an arbitration scheme for a CICB switch. Secondly, it is based on a round-robin selection and uses the concept of adaptable-size frame. RR-AF is different from a common frame-based scheme. The frame size is called adaptable as it is determined by the amount of service that a queue receives. Stability of a switch determines its throughput. If a switch is stable, it can provide 100 % throughput.

In this chapter, we present the stability analysis of the RR-AF arbitration scheme and prove that under admissible uniform traffic, a CICB switch can provide 100% with the RR-AF arbitration scheme. The appeal of RR-AF scheme lies on that RR-AF as a round-robin based scheme can achieve 100% throughput.

This chapter is organized as follows. Section 2.1.1 presents the switch model under study, Section 2.1.2 introduces the RR-AF arbitration scheme and shows a simulation study of throughput under uniform and nonuniform traffic patterns. Section 2.2 presents a stability analysis of the RR-AF arbitration scheme. Section 2.3 presents the conclusions.

Figure 2.1  $N \times N$  buffered crossbar with VOQs.

### 2.1.1 Combined Input-Crosspoint Buffered Switch Model

Consider a CICB switch with N inputs and outputs. In this switch model, there are N VOQs at each input. A VOQ at input i, where  $0 \le i \le N-1$ , that stores cells for output j, where  $0 \le j \le N-1$ , is denoted as  $VOQ_{i,j}$ . A crosspoint (CP) element in the CICB that connects input port i to output port j is denoted as  $CP_{i,j}$ . The buffer at  $CP_{i,j}$  is denoted as  $CPB_{i,j}$ . The size of  $CPB_{i,j}$ , k, is indicated by the number of cells that can be stored. A credit-based flow-control mechanism indicates to input i whether  $CPB_{i,j}$  has room available for a cell or not, as described in [42].  $VOQ_{i,j}$  is said to be eligible for selection if the VOQ is not empty and the corresponding  $CPB_{i,j}$ , at buffered crossbar (BC), has room to store a cell.

The round trip (RT) time, as in [42], is defined as the sum of the delays of the input arbitration (IA), the transmission of a cell from an input to the crossbar (d1), the output arbitration (OA), and the transmission of the flow-control information back from the crossbar to the input (d2). Figure 2.1 shows an example of RT for input 0 by showing the transmission delays for d1 and d2, and arbitration times, IA and OA. Cell and bit alignments are included in the transmission times. The condition for this switch to avoid

underflow, is such that:

$$RT = d1 + OA + d2 + IA \le k$$

(2.1)

where k is the crosspoint buffer size, in time slots, which is equivalent to the number of cells that can be stored. In other words, the crosspoint buffer must be able to store a number of cells to keep the buffer busy (i.e., transmitting cells) during at least one RT time.

### 2.1.2 Round-Robin with Adaptable-Size Frame (RR-AF)

### **Arbitration Scheme**

The studied arbitration scheme is round-robin based. Each time a VOQ (or a CPB at an output) is selected by the arbiter, the VOQ gets the right to forward a frame, where a frame is formed by one or more cells. Each cell of a frame is dispatched in one time slot. The frame size is determined by the serviced and unserviced traffic, such that no intervention is needed to select the frame size. We call this arbitration round-robin with adaptable-size frame (RR-AF). The amount of serviced (and unserviced) traffic depends on the experienced load by queues.

In each VOQ (and CPB) there are two counters: a frame-size counter,  $FSC_{i,j}(t)$ , and a current service counter,  $CSC_{i,j}(t)$ . The value of  $FSC_{i,j}(t)$ ,  $|FSC_{i,j}(t)|$ , indicates the frame size; that is, the maximum number of cells that  $VOQ_{i,j}$  can send in back-to-back time slots to the buffered crossbar, one cell per time slot. The initial value of  $|FSC_{i,j}(t)|$  is one cell (i.e., its minimum value). It is considered that  $|FSC_{i,j}(t)|$  can be as large as needed, although practical results have shown that its value does not reach large numbers.  $CSC_{i,j}(t)$  counts the number of serviced cells at time slot t in a frame corresponding to a VOQ, where the frame size is indicated by FSC, in a regressive fashion. A regressive-fashion count is used in CSC as CSC only considers FSC at the end of a serviced frame. The initial value of  $CSC_{i,j}(t)$ ,  $|CSC_{i,j}(t)|$ , is one cell (i.e., its minimum value).

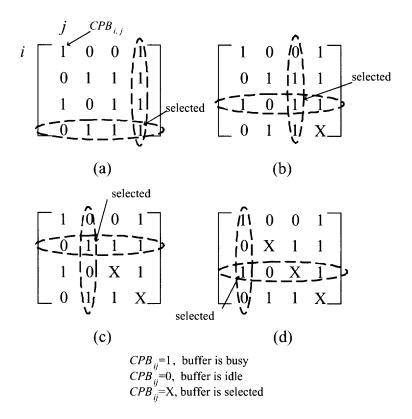

The input arbitration process is as follows. An input arbitre selects an eligible  $VOQ_{i,j'}$  in round-robin fashion, starting from the pointer position, j. For the selected  $VOQ_{i,j'}$ , if  $|CSC_{i,j'}(t)| > 1$ ,  $|CSC_{i,j'}(t+1)| = |CSC_{i,j'}(t)| - 1$ , and the input pointer remains at  $VOQ_{i,j'}$ , so that this VOQ has the higher priority for service in the next time slot and the frame transmission can continue. If  $|CSC_{i,j'}(t)| = 1$ , the input pointer is updated to (j'+1) modulo N,  $|FSC_{i,j'}(t)|$  is increased by f cells, and  $|CSC_{i,j'}(t)| = |FSC_{i,j'}(t)|$ . For any other  $VOQ_{i,h}$ , where  $h \neq j'$ , which is empty or inhibited by the flow-control mechanism, and it is positioned between the pointed  $VOQ_{i,j}$  and the selected  $VOQ_{i,j'}$ : if  $|FSC_{i,h}(t)| > 1$ ,  $|FSC_{i,h}(t+1)| = |FSC_{i,h}(t)| - 1$ . If there exist one or more VOQs that fit the description of  $VOQ_{i,h}$  at a given time slot, it is said that those VOQs missed a service opportunity at that time slot. The increment of the frame size, done by f cells, is performed each time the previous complete frame of a VOQ has been serviced. The value of f has to be chosen as discussed in the following section.

For the sake of clarity, the following pseudo-code describes the input arbitration scheme, as seen at an input:

-At time slot t, starting from the pointer position j, find the nearest eligible  $VOQ_{i,j'}$  in a round-robin fashion.

-Send the HOL cell from  $VOQ_{i,j'}$  to  $CPB_{i,j'}$  time slot t+1.

-If

$$|CSC_{i,j'}(t)| > 1$$

then

$$|CSC_{i,j'}(t+1)| = |CSC_{i,j'}(t)| - 1,$$

the pointer points to j'.

-else

$$|FSC_{i,j'}(t+1)| = |FSC_{i,j'}(t)| + f$$

,

$$|CSC_{i,j'}(t+1)| = |FSC_{i,j'}(t+1)|$$

,

the pointer points to (j'+1) modulo N.

-For VOQ(i, h), where

$$j \le h < j'$$

for  $j < j'$ , or  $0 \le h < j'$  and  $j \le h \le N - 1$  for  $j > j'$ :

$$FSC_{i,h}(t+1) = FSC_{i,h}(t) - 1.*$$

<sup>\*</sup>Note that when j' = j, there is no VOQ(i, h).

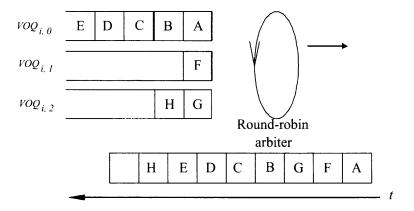

**Figure 2.2** Example of RR-AF among three queues in a  $3 \times 3$  switch.

#### - Go to the next time slot.

Note that f may be equal to a constant or a variable value. In general, f assumes the finite value of N, unless otherwise stated. The value of f affects the performance of RR-AF in different traffic scenarios. Note that when f=0, RR-AF becomes RR.

The output arbitration works in a similar way to the input arbitration, considering  $CPB_{i,j}$  and the corresponding counters in each crosspoint. Figure 2.2 shows an example of RR-AF at an input. Assume that the queues shown in the figure are the VOQs of input i in a  $3 \times 3$  switch. Initially, all queues have three cells each, as Figure 2.2 shows. Assuming that the FSC for each queue has the initial value of one, a cell from each queue is served in a round-robin fashion. Then, each frame is increased by N cells; therefore, the remaining two cells in each queue are served back-to-back. The cells leave the input as the figure shows.

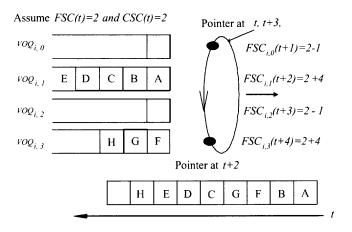

Figure 2.3 shows an example of the adjustment of  $FSC_{i,j}$ . In this example,  $VOQ_{i,1}$  and  $VOQ_{i,3}$  have cells, five and three, respectively, and no VOQ is inhibited by the flow-control mechanism. The highest priority is given to  $VOQ_{i,0}$  at time slot t. During this time slot, the input arbiter selects  $VOQ_{i,1}$  to be the next that sends a cell to the buffered crossbar. Then  $VOQ_{i,0}$  misses an opportunity to send cells as it is empty, and its FSC value decreases by one cell. Since  $VOQ_{i,1}$  has five cells and  $FSC_{i,1}=2$ , the VOQ holds the

priority (or token) so that it receives service in the next time slot. Since the VOQ has three cells, it completes frame service and at time slot t+2 its FSC value is increased by four, and the arbiter selects  $VOQ_{i,2}$  as the next VOQ to receive service, but  $VOQ_{i,2}$  misses an opportunity to send cells as it is empty and its FSC value decreases by one cell. Then, the priority is given to  $VOQ_{i,3}$  at time slot t+3.

The performance evaluations of two CICB switches, one using RR-AF arbitration and the other using RR arbitration, are presented. In addition, an OB switch is also considered in the evaluations for comparison purposes. The performance evaluations are produced by computer simulation. The traffic models considered have destinations with uniform and nonuniform distributions, the latter is called unbalanced. Both models use Bernoulli arrivals. The simulation does not consider the segmentation and re-assembly delays. The simulation results are obtained with a 95% confidence interval, not greater than 5% for the average cell delay.

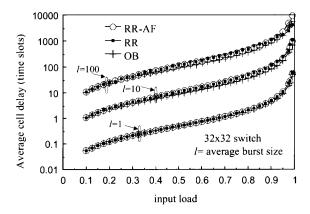

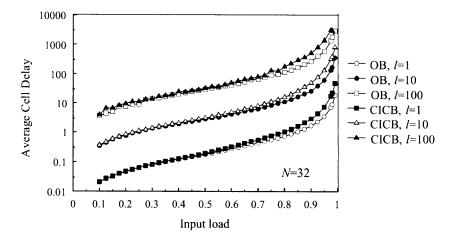

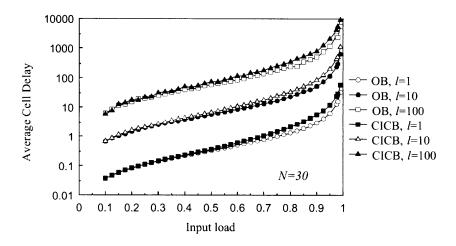

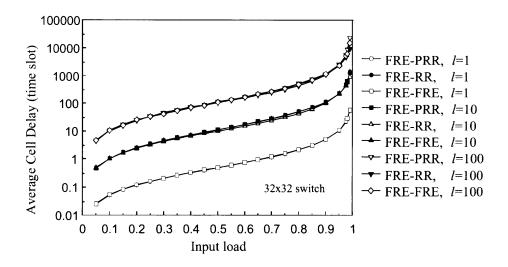

Figure 2.4 shows simulation results of two  $32 \times 32$  CICB switches with RR-AF, RR, and an OB switch under uniform traffic with Bernoulli arrivals (l=1) and bursts with average lengths of 10 and 100 cells (l=10 and l=100). The burst length is exponentially distributed. The buffered crossbars have crosspoint buffers with a size of one cell each.

Figure 2.3 Example of VOQs missing opportunities for cell forwarding.

The simulation shows that the RR-AF arbitration scheme provides 100% throughput under uniform traffic.

This figure also shows that the average delay performance of RR-AF under Bernoulli arrivals is close to that of RR, and therefore, to that of an OB switch. The adaptable frame-size condition in the arbitration does not degrade the throughput performance, neither does it increase the average delay under this traffic model. As the RR-AF uses the history of serviced and unserviced traffic from the queues (i.e., VOQ and CPB), the switch practically adapts itself to uniform traffic.

RR-AF was simulated with different sizes of k. The result of the simulation shows that there is no measurable improvement by increasing the size of k. This result is expected as the average delay of RR-AF with k=1 is close to that of an OB switch. Therefore, the increasing of k negligibly affects the results. As in [42], the size of k needs to be determined by the RT time. As the size of k does not affect the performance of RR-AF, k is assigned the value of one cell, (i.e., k=1), in the remainder of the chapter, unless otherwise stated.

RR-AF and RR arbitrations were simulated under a nonuniform traffic model, the unbalanced traffic model [42]. The unbalanced traffic model uses a probability, w, as the

Figure 2.4 Average delay of RR-AF arbitration under Bernoulli and bursty uniform traffic.

fraction of input load directed to a single predetermined output, while the rest of the input load is directed to all outputs with uniform distribution. Let us consider input port s, output port d, and the offered input load for each input port  $\rho$ . The traffic load from input port s to output port d,  $\rho_{s,d}$  is given by,

$$\rho_{s,d} = \begin{cases} \rho\left(w + \frac{1-w}{N}\right) & \text{if } s = d\\ \rho\frac{1-w}{N} & \text{otherwise.} \end{cases}$$

(2.2)

When w = 0, the offered traffic is uniform. On the other hand, when w = 1, it is completely directional, from input s to output d, where s = d.

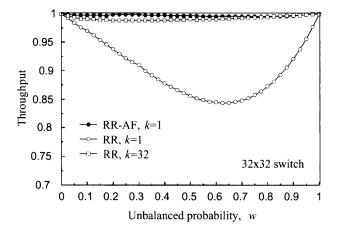

Two combined input-crosspoint buffered switches of size N=32, one with RR-AF and the other with RR, were simulated under unbalanced traffic. The switch with RR-AF uses k=1 and for comparison, RR uses k=1 and k=N=32. Figure 2.5 shows that RR-AF, with k=1 and f=N, provides well above 99% throughput under the complete range of w. It is considered that this throughput is nearly 100% for practical purposes. These results show that RR-AF with k=1 outperforms RR with k=32. This results in a feasible implementation of buffered crossbars as the size of the crosspoint buffer is reduced. In this example, RR, with k=32 and a cell size of 64 bytes, would need 16 Mb of memory, while RR-AF, with k=1, would need 512 Kb of memory. Furthermore, the switch with RR-AF can provide nearly 100% throughput under unbalanced traffic.

RR-AF with f=N, is also tested under other nonuniform traffic models: Chang's [51] and asymmetric [56].

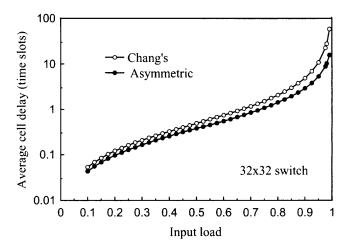

Chang's traffic model can be defined as  $\rho=0$  for i=j and  $\rho=\frac{1}{N-1}$ , otherwise. Figure 2.6 shows the average cell delay experienced by a  $32\times32$  switch using RR-AF under these traffic models. As the figure shows, the throughput of RR-AF is 100% under Chang's and Asymmetric traffic models. The average delay under Chang's traffic is larger than that of the asymmetric's traffic; however, the difference is small. RR-AF adapts the frame size to the different loads offered to each input and output.

Figure 2.5 Throughput performance of RR-AF under unbalanced traffic.

Figure 2.6 Average cell delay of RR-AF under Chang's and asymmetric traffic.

# 2.2 Stability Study

RR-AF arbitration is based on round-robin and it aims to improve the throughput under non-uniform traffic. The attractiveness of RR-AF lies on keeping the property of round-robin based schemes to deliver stability, and therefore, 100% throughput under uniform traffic. We use the definition of stability as presented in [18].

The high throughput of RR-AF is the product of increasing or decreasing service for a queue in proportion to its received and missed service, respectively. RR-AF ensures

service to the queues with high load by increasing the frame size, and to the other queues by using round-robin selection. In addition, the decreasing policy (i.e., FSC is decremented by one unit each time the VOQ misses service) for the frame-size counter ensures that the counter does not increase infinitely, as observed experimentally.

In this section, we prove that RR-AF, with f in a general sense, provides 100% throughput under admissible traffic, despite the use of the adaptable-size frame concept. We focus this proof on the input arbitration and VOQs. However, the result applies to the output arbitration and crosspoint buffers [64].

In order to analyze the stability of RR-AF, the queue length evolution by every time slot is not enough in analyzing the changing of the frame size.

In this analysis, the following definitions are used.

**Definition 1.** A cycle is the service opportunity given to a VOQ where the number of cells that can be sent in consecutive time slots to the crosspoint can be up to the frame size. The cycle length is given in the number of time slots that the VOQ receives service. The start of a cycle is determined when a VOQ is selected to receive service at time slot t if that VOQ received service at time t-1.

**Definition 2.** The completion service rate  $R_{i,j}^c$  is the rate at which  $VOQ_{i,j}$  finishes frame service per cycle.

**Definition 3.** The miss service rate  $R_{i,j}^m$  is the rate at what  $VOQ_{i,j}$  misses service per cycle, including the following two reasons of the service miss: i) when the number of cells in a VOQ is smaller than the frame size, and ii) when a VOQ cannot send cells to the crosspoint for lacking of room in the crosspoint buffer. Therefore,  $R_{i,j}^m = 1 - R_{i,j}^c$ .

In addition, we use the following notations:

$m_{i,j}$  denotes the accumulative total number of time slots that  $VOQ_{i,j}$  receives service from  $t_0$  to any time t, where  $t_0$  is the starting time and t is any time slot such that  $t > t_0$ .

$\sigma_{i,j}$  is the cumulative number of opportunities a VOQ receives for service from cycle  $n_0$ , the time before VOQ receives any service during the switch working time, to cycle  $n_0$ .

$C_{i,i}^{inc}$  is the cumulative number of cycles where FSC increases until cycle n.

$C_{i,j}^{min}$  is the cumulative number of cycles where FSC has no changed because it has reached the minimum of one cell.

In this section, we denote the value of FSC at the end of cycle n as  $FSC_{i,j}(n)$ . Notice that FSC(n) is different from FSC(t) in section 2.1.2.

In addition, let  $E[FSC_{i,j}(n)]$  denote the expected frame size of any VOQ at the end of  $n^{th}$  cycle. Since the average arrival rate is  $\lambda_{i,j}$ , let  $\lambda_{i,j}E(x)$  be the number of cell arrivals per cycle (based on Little's theorem), where E(x) is the average number of time slots that a VOQ receives service. Also, we denote the occupancy of a VOQ at the end of cycle n as  $L_{i,j}(n)$ .

Under traffic with uniform distribution among all outputs, the stability of the switch is directly related to the stability of the frame size of each queue. The stability of RR-AF is then based in the proof of the following claim:

**Theorem 1.** A CICB switch using RR-AF scheduling algorithm is stable under traffic with uniform distribution.

*Proof.* We assume that all inputs receive traffic independently and identically distributed. Therefore, identical service should be expected in each VOQ.

Since the service that a VOQ (or CPB) receives is determined by FSC, then we define the following lemma.

**Lemma 1.** In a CICB packet switch using RR-AF as input arbitration,  $VOQ_{i,j}$  is stable if  $FSC_{i,j}$  is stable, under uniform traffic.

*Proof.* When  $FSC_{ij}(n)$  is stable,  $L_{i,j}(n)$  can be either cases:

- (i)  $\lim_{n\to\infty} L_{i,j}(n) = \infty$ .

- (ii)  $\lim_{n\to\infty} L_{i,j}(n) = a$ , where a is a finite value and  $a \ge 1$ .

Let's consider the case (i) first: in a cycle, the service to  $VOQ_{i,j}$  always complete because  $\lim_{n\to\infty} L_{i,j}(n) = \infty$ .  $FSC_{i,j}(n)$  will be increased by f each time. Therefore  $FSC_{i,j}(n)$  can not be bounded by a finite value, which contradicts with the assumption that  $FSC_{ij}(n)$  is stable.

Now let's consider the case (ii):  $\lim_{n\to\infty} L_{i,j}(n) = a$  means that  $VOQ_{i,j}$  receives service all the time and  $L_{i,j}(n)$  will never go to infinity. Since we have already proved that case (i) is impossible, so only case (ii) stands.

Summing up the cases above, if FSC(n) is stable then L(n) is stable.

For completeness, we state the following corollary:

**Corollary 1.** Under uniform traffic, if  $FSC_{i,j}(n)$  is unstable then  $L_{i,j}(n)$  is unstable.

*Proof.* We prove that the following state is false: if  $\lim_{n\to\infty}FSC_{i,j}(n)=\infty$  then  $L_{i,j}(n)$  is stable. Let's assume that the statement is true. There must be that  $L_{i,j}(n)$  is bounded by a finite value b (i.e.,  $\lim_{n\to\infty}L(n)=b$ ) and therefore  $FSC_{i,j}(n)$  increases its value by f each cycle until it reaches the value of b. At this point FSC(n) cannot continue increasing its value at each cycle, and therefore  $FSC_{i,j}(n)$  converges to a finite value b, which contradicts the initial assumption. Therefore, if  $FSC_{i,j}(n)$  is unstable, and  $L_{i,j}(n)$  cannot be stable under uniform traffic.

Now, it remains to prove that  $FSC_{i,j}(n)$  is stable. For this, let's consider the behavior of  $FSC_{i,j}(n)$ , and by stating the following lemma:

**Lemma 2.** A CICB switch using RR-AF and under traffic with uniform distribution has  $R_{i,j}^m > \frac{f}{f+1}$ .

*Proof.* The accumulated FSC value from cycles  $n_0$  to n, where  $n > n_0$ , is

$$FSC_{i,j}(n) = FSC_{i,j}(0) + fC^{inc} - (\sigma_{i,j} - C_{i,j}^{inc} - C_{i,j}^{min}),$$

(2.3)

where  $FSC_{i,j}(0)$  is the initial FSC value at  $n_0$ .

Let's assume that a frame is completely served at this cycle. The inequality involving the stationary state follows:

$$FSC_{i,j}(0) + fC_{i,j}^{inc} - (\sigma_{i,j} - C_{i,j}^{inc} - C_{i,j}^{min}) \le \lambda_{ij}E(x) + \delta_{i,j},$$

(2.4)

where  $\delta_{i,j}$  is the discrepancy between the actual and the expected values. Then, we can express  $C^{inc}$  as:

$$C_{i,j}^{inc} \le \frac{\lambda_{ij} \frac{m}{\sigma_{i,j}} + \sigma_{i,j} + \delta_{i,j} - C_{i,j}^{min} - FSC_{i,j}(0)}{f+1}.$$

(2.5)

Recalling that  $R_{i,j}^c = \frac{C_{i,j}^{inc}}{\sigma_{i,j}}$  and using (2.5), we have:

$$\frac{C_{i,j}^{inc}}{\sigma_{i,j}} \le \frac{1}{f+1} + \frac{\lambda_{ij} \frac{m}{\sigma_{i,j}} + \delta_{i,j} - C_{i,j}^{min} - FSC_{i,j}(0)}{\sigma_{i,j}(f+1)}.$$

(2.6)

Let's consider that the switch has been functioning for a very long period of time, such that  $\sigma_{i,j}$  has a very large value. Therefore, we have:

$$R_{i,j}^c \le \frac{1}{f+1},$$

(2.7)

or

$$R_{i,j}^m > \frac{f}{f+1}.$$

(2.8)

Now, with Lemma 2 proved, the dynamics of FSC are used to define the value of the frame size at time cycle n+1,  $FSC_{i,j}(n+1)$ , as:

$$E[FSC_{i,j}(n+1)] = (FSC_{i,j}(n) + f)(1 - R_{i,j}^m) + (FSC_{i,j}(n) - 1)R_{i,j}^m,$$

(2.9)

where  $E[FSC_{i,j}(n+1)]$  is the expected value of FSC at cycle n+1. This equation considers an increment and a decrement of the FSC with probabilities  $1 - R_{i,j}^m$  and  $R_{i,j}^m$ , respectively, at time slot n.

Considering that  $FSC_{i,j}(n+2) = FSC_{i,j}(n+1+1)$ :

$$E[FSC_{i,j}(n+2)] - E[FSC_{i,j}(n+1)] = f - R_{i,j}^m(f+1).$$

(2.10)

According to the definition of stability in the sense of Lyapunov [62], if  $E[FSC_{i,j}(n+l+1)] - E[FSC_{i,j}(n+l)] = -\varepsilon < 0$ , which indicates that the expected FSC drift is negative, the FSC exhibits an overall downward drift, and will not become unbounded, therefore FSC is stable.

Recalling the value of  $R_m$  from Lemma 2, and substituting  $R_m = \frac{f+\mu}{f+1}$  in (2.8), where  $0 < \mu < 1$ , it is clear that:

$$R_m = \frac{f + \mu}{f + 1} > \frac{f}{f + 1}.\tag{2.11}$$

Considering that l = 1 and n can be any service cycle, we substitute (2.11) in (3.4):

$$E[FSC_{i,j}(n+2)] - E[FSC_{i,j}(n+1)] = f - (\frac{f+\mu}{f+1})(f+1),$$

(2.12)

which is:

$$E[FSC_{i,j}(n+2)] - E[FSC_{i,j}(n+1)] = -\mu, \tag{2.13}$$

for any cycle n during steady state. This equality shows the stability of FSC of any VOQ. Therefore, a packet switch using RR-AF arbitration under uniform traffic is stable.

# 2.3 Conclusions

The RR-AF scheme use the concept of round-robin selection and adaptable-size frame. The frame size depends on the service received by a queue. This chapter proved that the round-robin scheme with adaptable-size frame arbitration delivers 100% throughput under uniform traffic.

The analytical result can be extended to nonuniform traffic patterns. The result also shows that a buffered crossbar with one-cell crosspoint buffers is sufficient to provide high throughput with the proposed round-robin based arbitration.

This chapter shows that it is possible to provide an arbitration scheme based on round-robin selection for buffered crossbars such that a switch can deliver high throughput under admissible traffic with nonuniform distributions with a small crosspoint buffer size.

#### **CHAPTER 3**

# ANALYSIS OF A FLOW CONTROL SYSTEM FOR A COMBINED INPUT-CROSSPOINT BUFFERED PACKET SWITCH

### 3.1 Introduction