### **Copyright Warning & Restrictions**

The copyright law of the United States (Title 17, United States Code) governs the making of photocopies or other reproductions of copyrighted material.

Under certain conditions specified in the law, libraries and archives are authorized to furnish a photocopy or other reproduction. One of these specified conditions is that the photocopy or reproduction is not to be "used for any purpose other than private study, scholarship, or research." If a, user makes a request for, or later uses, a photocopy or reproduction for purposes in excess of "fair use" that user may be liable for copyright infringement,

This institution reserves the right to refuse to accept a copying order if, in its judgment, fulfillment of the order would involve violation of copyright law.

Please Note: The author retains the copyright while the New Jersey Institute of Technology reserves the right to distribute this thesis or dissertation

Printing note: If you do not wish to print this page, then select "Pages from: first page # to: last page #" on the print dialog screen

The Van Houten library has removed some of the personal information and all signatures from the approval page and biographical sketches of theses and dissertations in order to protect the identity of NJIT graduates and faculty.

### **ABSTRACT**

## CHARACTERIZATION OF ULTRATHIN GATE DIELECTRICS AND MULTILAYER CHARGE INJECTION BARRIERS

by

### Edwin M. Dons

Since the invention of the first integrated circuit, the semiconductor industry has distinguished itself by a phenomenally rapid pace of improvements in device performance. This trend of ever smaller and faster devices is a result of the ability to exponentially reduce feature sizes of integrated circuits, a trend commonly known as "scaling". A reduction of overall feature sizes requires a simultaneous reduction in the thickness of the gate dielectric, SiO<sub>2</sub>, of a MOSFET. Gate oxides in the ultrathin regime (<35 Å) feature a large direct tunneling leakage current. The presence of this leakage current requires a reevaluation of standard characterization techniques as well as a reevaluation of the continued usefulness of SiO<sub>2</sub> as the gate dielectric of choice for future applications. On the other hand, a thorough understanding of the dynamics of ultrathin oxides opens up a range of future device applications that were not possible with thicker oxides.

Capacitance-voltage characterization has been the standard technique to study the electrical properties and interface quality of MOS devices. However, the presence of a large leakage current in ultrathin oxides distorts standard C-V measurements, rendering this technique no longer useful. In this work, a leakage compensated charge measurement is developed to overcome this difficulty. This technique produces static C-V curves, even for oxides as thin as 24 Å, thereby permitting C-V characterization well into the direct tunneling regime.

As an extension of this leakage problem, the usefulness of SiO<sub>2</sub> as the gate dielectric of choice for future CMOS devices has been called into question. One solution – but not the only – calls for a new dielectric to replace SiO<sub>2</sub> for future gate applications. This research presents some of the earliest results ever on the electrical properties of MOCVD and ALCVD hafnium oxides as a potential candidate. Electrical characterization revealed that the devices have characteristics such as large leakage currents, dielectric charging under stress, hysteresis and a large flatband voltage shift that is commonly found in materials such as the one that was investigated in this work.

As one example of future device applications that become possible due to the scaling of ultrathin oxides, silicon-based multilayer charge injection barriers have been investigated. These barriers consist of alternating layers of ultrathin SiO<sub>2</sub> and Si. The electrical properties of these structures were studied in detail and revealed that they can be used as an active tunnel dielectric in nonvolatile memory devices.

## CHARACTERIZATION OF ULTRATHIN GATE DIELECTRICS AND MULTILAYER CHARGE INJECTION BARRIERS

by Edwin M. Dons

A Dissertation

Submitted to the Faculty of

New Jersey Institute of Technology and

Rutgers, The State University of New Jersey-Newark,

in Partial Fulfillment of the Requirements for the Degree of

Doctor of Philosophy in Applied Physics

**Federated Physics Department**

**May 2004**

Copyright © 2004 Edwin M. Dons

ALL RIGHTS RESERVED

### APPROVAL PAGE

## CHARACTERIZATION OF ULTRATHIN GATE DIELECTRICS AND MULTILAYER CHARGE INJECTION BARRIERS

### Edwin M. Dons

| Pr. K. R. Farmer II, Dissertation Advisor<br>Associate Professor of Physics, New Jersey Institute of Technology<br>Chief Technology Officer, TSI Incorporated     | Date' |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Dr. K. K. Chin, Committee Member Professor of Physics, New Jersey Institute of Technology Director, NJIT-Rutgers (Newark) Joint Applied Physics M.S./Ph.D Program | Date  |

| Dr. G. S. Tompa, Committee Member President, Structured Materials Industries, Inc.                                                                                | Date  |

| Dr. Z. Wu, Committee Member<br>Associate Professor of Physics and Department Chair, Rutgers University                                                            | Date  |

| Dr. Z. Xiao, Committee Member                                                                                                                                     | Date  |

Assistant Research Professor, New Jersey Institute of Technology

### **BIOGRAPHICAL SKETCH**

**Author:** Edwin M Dons

**Degree:** Doctor of Philosophy

**Date:** May 2004

### Undergraduate and Graduate Education:

- Doctor of Philosophy in Applied Physics

New Jersey Institute of Technology, Newark, NJ, 2004

- Bachelor of Science in Applied Physics University of Utrecht, Utrecht, The Netherlands, 1994

Major: Applied Physics

### **Presentations and Publications:**

E.M. Dons, C.S. Skowronski and K.R. Farmer,

"Electrical characterization of a double barrier direct tunneling diode structure," Proceedings of the Materials Research Society Symposium, San Fransisco, CA, May 1999.

E. M. Dons, C. S. Skowronski and K. R. Farmer,

"Direct tunneling diode structure with a multilayer charge injection barrier," Applied Physics Letters **73**, 3712 (1998).

Hui Song, Edwin Dons, Xi Qing Sun and K.R. Farmer,

"Leakage compensated charge method for determining static C-V characteristics of ultrathin MOS capacitors,"

AIP Conference Proceedings, Gaithersburg, MD, October 1998.

- A. Weber, R. Nikulski, C.P. Klages, M.E. Gross, W.L. Brown, E. Dons, R.M. Charatan, "Low Temperature Deposition of TiN Using Tetrakis(dimethylamido)-Titanium in an Electron Cyclotron Resonance Plasma Process"

Journal of the Electrochemical Society, 141, 849 (1994).

- A. G. Schins, E. M. Dons, A. F. M. Arts, "Aging in two-dimensional Ising spin glasses" Physical. Review B **48**, 16524 (1993).

Dedicated to my wife, Nelly

### **ACKNOWLEDGMENT**

I would like to thank my advisor, Dr. Kenneth R. Farmer, for his never ending support, patience and confidence. I also want to thank the members of my committee, Dr. Tompa, Dr. Chin, Dr. Xiao and Dr. Wu for their participation.

In addition, I would like to express my appreciation to Dr. Veena Misra and her students for helping me during my cleanroom work at NC State. I would also like to acknowledge the staff of Structured Materials Industries, Inc. for their collaboration on the hafnium processing.

My former lab mates deserve special thanks for their help and advice, especially the funny young man Michael Beggans.

This work was partially supported by the National Science Foundation, ECS-9624798.

### **TABLE OF CONTENTS**

| C | Chapter                                                        | Page |

|---|----------------------------------------------------------------|------|

| 1 | INTRODUCTION                                                   | . 1  |

|   | 1.1 Scope of Research                                          | . 2  |

|   | 1.2 Statement of Purpose                                       | . 3  |

|   | 1.3 Dissertation Outline                                       | . 3  |

| 2 | REVIEW OF CMOS TECHNOLOGY                                      | . 5  |

|   | 2.1 Overview                                                   | . 5  |

|   | 2.2 Introduction to CMOS Technology                            | . 5  |

|   | 2.3 History of CMOS Technology                                 | . 6  |

|   | 2.4 Moore's Law and Scaling                                    | . 8  |

|   | 2.4.1 MOSFET Operation                                         | . 9  |

|   | 2.4.2 MOSFET Characteristics                                   | . 11 |

|   | 2.4.3 Why Scaling?                                             | . 14 |

|   | 2.5 Ultrathin Silicon Dioxide                                  | . 15 |

|   | 2.5.1 Fundamental limits?                                      | . 17 |

|   | 2.5.2 Electrical Characterization                              | . 19 |

|   | 2.5.3 Oxide Degradation and Breakdown during Electrical Stress | . 24 |

|   | 2.5.4 Fabrication of Ultrathin Oxides                          | . 25 |

# TABLE OF CONTENTS (Continued)

| C | Chapter [                                          | Page |

|---|----------------------------------------------------|------|

| 3 | C-V CHARACTERIZATION OF ULTRATHIN SiO <sub>2</sub> | 29   |

|   | 3.1 Overview                                       | 29   |

|   | 3.2 The MOS System                                 | . 29 |

|   | 3.3 The MOS System under Bias Voltage              | . 32 |

|   | 3.4 Leakage Compensated Capacitance Measurement    | . 36 |

|   | 3.5 Experimental Details                           | 39   |

|   | 3.6 Experimental Results                           | 40   |

|   | 3.6.1 LCCV on a 3.5 nm Oxide                       | 40   |

|   | 3.6.2 LCCV on a 2.4 nm Oxide                       | 44   |

|   | 3.7 Summary                                        | 47   |

| 4 | CHARACTERIZATION OF HAFNIUM OXIDE GATE DIELECTRICS | . 48 |

|   | 4.1 Overview                                       | . 48 |

|   | 4.2 Materials Properties Considerations            | . 49 |

|   | 4.3 Status of Alternative Gate Dielectrics         | . 53 |

|   | 4.4 Experimental Details                           | . 56 |

|   | 4.5 Results and Discussion                         | . 57 |

|   | 4.5.1 Hafnium Oxide Thickness                      | . 57 |

|   | 4.5.2 Electrical Characterization                  | 59   |

|   | 4.6 Summary                                        | 64   |

# TABLE OF CONTENTS (Continued)

| C | Chapter [1]                                                             | Page |

|---|-------------------------------------------------------------------------|------|

| 5 | THE MULTILAYER CHARGE INJECTION BARRIER                                 | . 65 |

|   | 5.1 Overview                                                            | . 65 |

|   | 5.2 Introduction                                                        | . 66 |

|   | 5.3 Double Barrier on n-Type Substrate                                  | . 67 |

|   | 5.3.1 Device Fabrication                                                | 67   |

|   | 5.3.2 Current-Voltage Characterization                                  | . 69 |

|   | 5.3.3 Capacitance-Voltage Characterization                              | . 73 |

|   | 5.3.4 Degradation                                                       | . 76 |

|   | 5.3.5 Double Barrier as Tunnel Dielectric in Nonvolatile Memory Devices | . 78 |

|   | 5.4 Double Barrier on p-Type Substrate                                  | . 78 |

|   | 5.5 Summary                                                             | 84   |

| 6 | NONVOLATILE MEMORY TRANSISTOR                                           | . 85 |

|   | 6.1 Overview                                                            | . 85 |

|   | 6.2 Introduction                                                        | . 86 |

|   | 6.2.1 Principle of Nonvolatile Memory                                   | 86   |

|   | 6.2.2 Program Operation                                                 | . 88 |

|   | 6.2.3 Erase Operation                                                   | . 89 |

|   | 6.2.4 Cycling Endurance                                                 | . 89 |

|   | 6.2.5 Data Retention                                                    | . 90 |

## TABLE OF CONTENTS (Continued)

| Chapter                                                   | Page |

|-----------------------------------------------------------|------|

| 6.3 Alternative Device Structures                         | 91   |

| 6.4 Multilayer Charge Injection Barriers                  | 93   |

| 6.5 Device Fabrication                                    | 94   |

| 6.6 Results and Discussion                                | 96   |

| 6.7 Summary                                               | 101  |

| 7 CONCLUSIONS AND FUTURE WORK                             | 102  |

| 7.1 Leakage Compensated Charge Measurement                | 102  |

| 7.1.1 Conclusions                                         | 102  |

| 7.1.2 Future Work                                         | 103  |

| 7.2 Alternative Gate Dielectrics                          | 103  |

| 7.2.1 Conclusions                                         | 103  |

| 7.2.2 Future Work                                         | 104  |

| 7.3 Silicon-based MLCIBs                                  | 105  |

| 7.3.1 Conclusions                                         | 105  |

| 7.3.2 Future Work                                         | 106  |

| APPENDIX A Processing Conditions Hafnium Oxide Deposition | 107  |

| APPENDIX B Processing Conditions Tunnel Stack             | 108  |

| REFERENCES                                                | 109  |

### LIST OF TABLES

| Table | Pa                                                          | age |

|-------|-------------------------------------------------------------|-----|

| 2.1   | Scaling trends                                              | 8   |

| 2.2   | Properties of silicon dioxide                               | 15  |

| 4.1   | Properties of the most studied alternative gate dielectrics | 53  |

### LIST OF FIGURES

| Figure | · Pa                                                                                                                       | ıge |

|--------|----------------------------------------------------------------------------------------------------------------------------|-----|

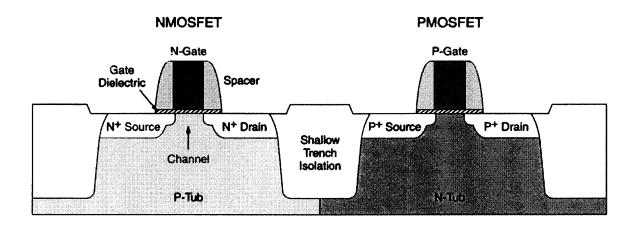

| 2.1    | Cross-section of a Complementary Metal Oxide Semiconductor Field Effect Transistor (CMOSFET)                               | 6   |

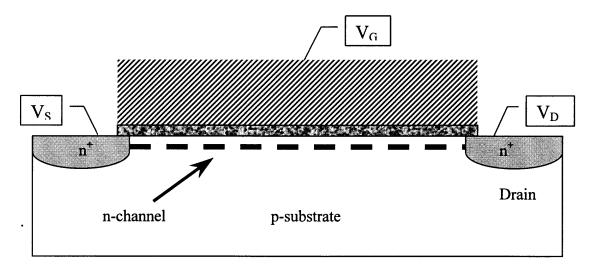

| 2.2    | Cross-section of an n-channel MOSFET                                                                                       | 10  |

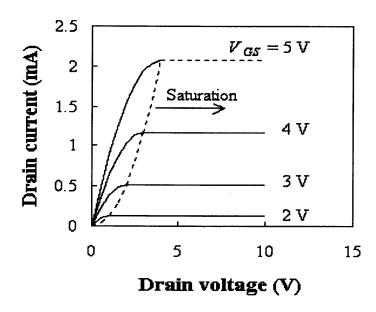

| 2.3    | Drain current I <sub>D</sub> vs. Drain voltage for different gate voltages                                                 | 13  |

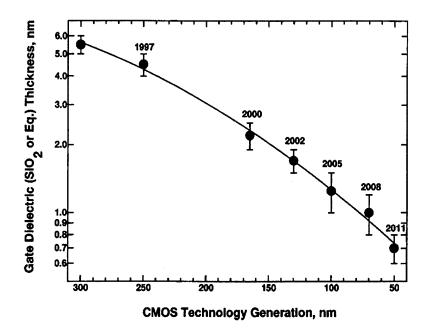

| 2.4    | Scaling of gate dielectric thickness                                                                                       | 16  |

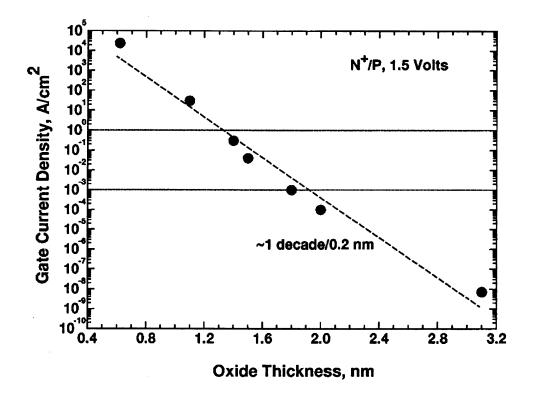

| 2.5    | Gate leakage current density as a function of oxide thickness                                                              | 18  |

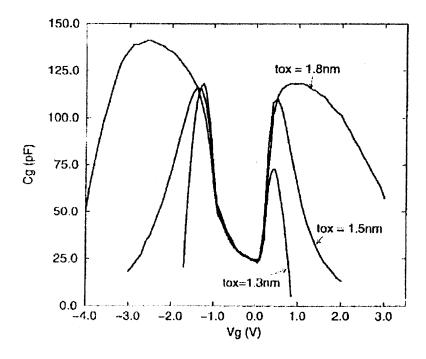

| 2.6    | C-V characteristics distorted by leakage currents through the ultrathin gate oxide                                         | 22  |

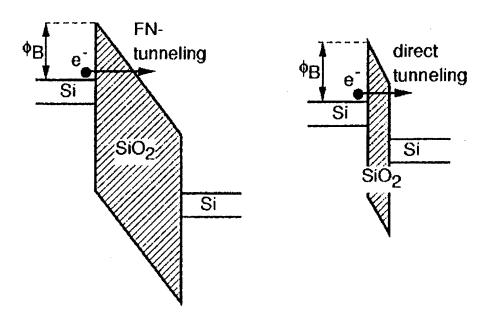

| 2.7    | Conduction mechanisms through SiO <sub>2</sub> : Fowler-Nordheim tunneling  (a) and direct tunneling (b)                   | 23  |

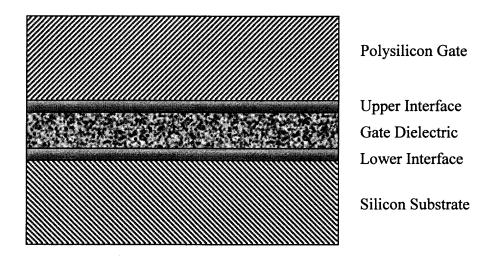

| 3.1    | Cross-section of the gate stack in a MOSFET structure                                                                      | 30  |

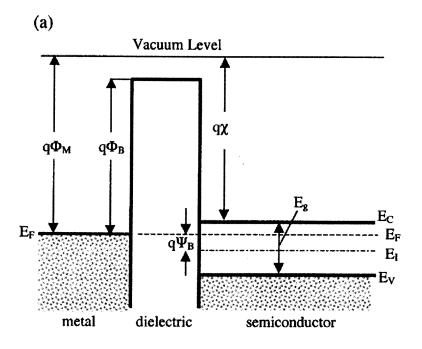

| 3.2    | Energy band diagrams for an ideal MOS structure with zero applied voltage; (a) on n-type silicon and (b) on p-type silicon | 31  |

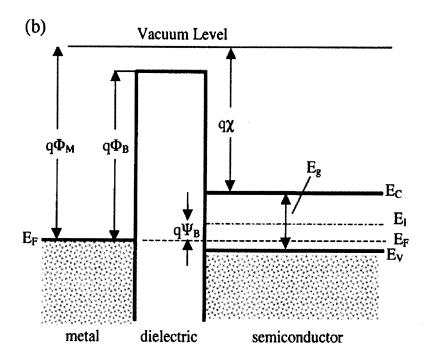

| 3.3    | A p-type MOS system under bias: (a) accumulation mode ( $V < 0V$ ), (b)depletion mode and (c) inversion mode ( $V > 0V$ )  | 33  |

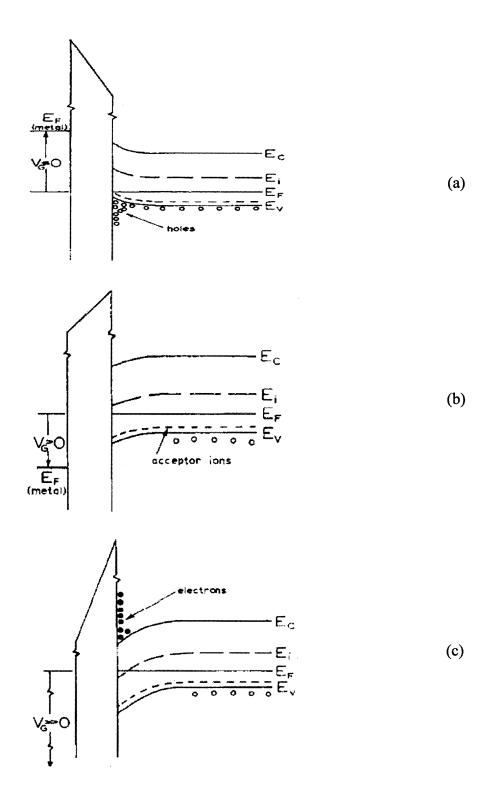

| 3.4    | Typical frequency dependence of C-V characteristics for a p-type MOS                                                       | 35  |

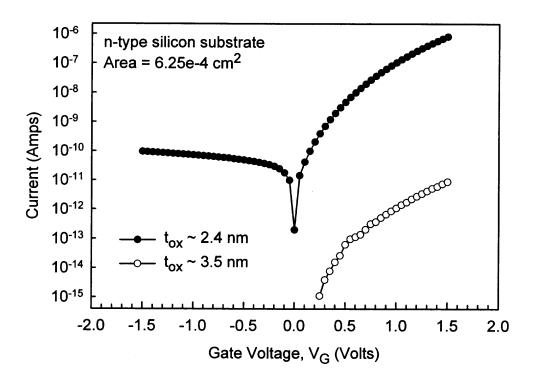

| 3.5    | Leakage current through a 2.4nm and 3.5 nm ultrathin oxide                                                                 | 36  |

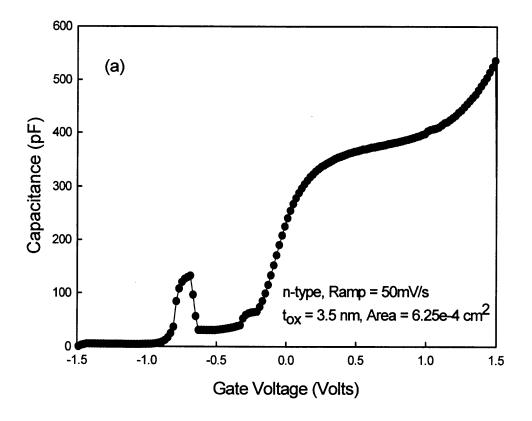

| 3.6    | Severely distorted Low Frequency C-V curve of a 3.5 nm oxide due to leakage current                                        | 37  |

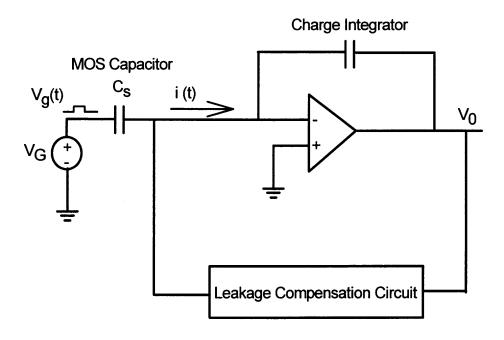

| 3.7    | Principle of a Leakage Compensated Charge Measurement                                                                      | 39  |

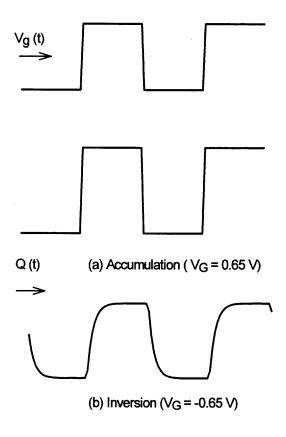

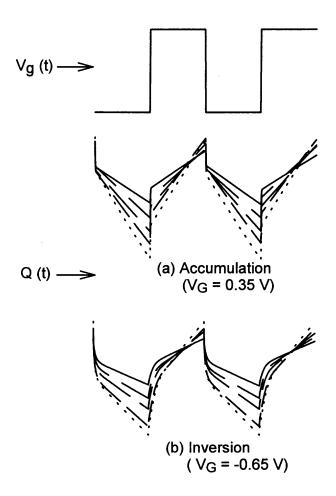

| 3.8    | Transient waveforms Q(t) in accumulation and inversion for a 50mV, 1 Hz excitation signal on a 3.5 nm oxide                | 41  |

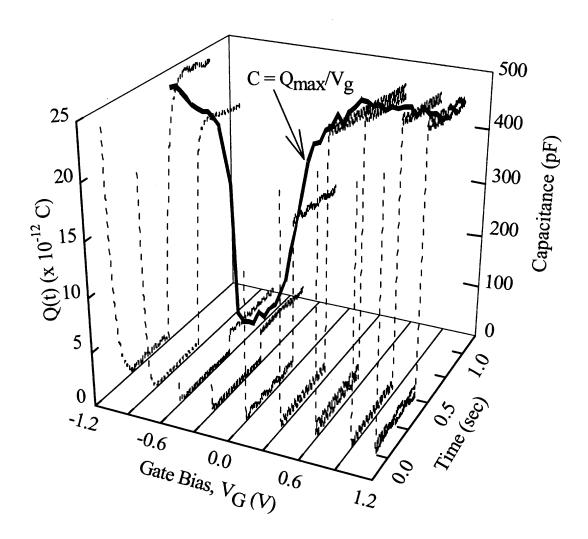

| 3.9    | 3-D graph of transient waveforms Q(t) as a function of bias voltage V <sub>G</sub>                                         | 42  |

# LIST OF FIGURES (Continued)

| Figure | Pa                                                                                                  | age |

|--------|-----------------------------------------------------------------------------------------------------|-----|

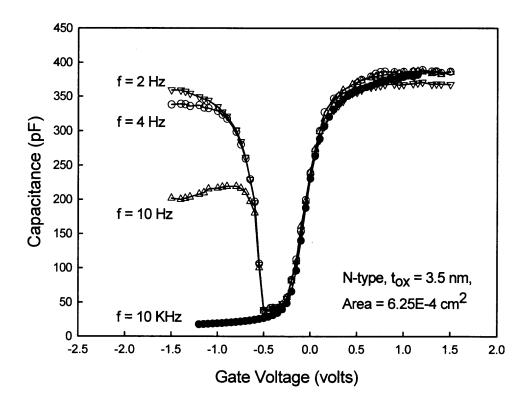

| 3.10   | Frequency dependence of C-V characteristics of 3.5 nm oxide measured by LCCV method                 | 43  |

| 3.11   | Transient waveforms Q(t) in accumulation and inversion for a 2.4nm oxide                            | 44  |

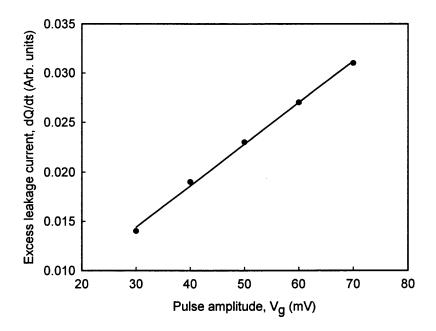

| 3.12   | Excess leakage current dQ/dt as a function of pulse amplitude $V_g \ \dots \dots$                   | 45  |

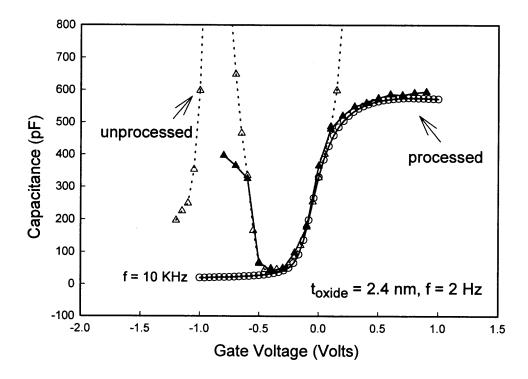

| 3.13   | C-V characteristics of 2.4 nm oxide before and after numerical processing of excess leakage current | 46  |

| 4.1    | Picture of wafer after MOCVD deposition of hafnium oxide                                            | 58  |

| 4.2    | Picture of wafer after MOCVD deposition of hafnium oxide                                            | 58  |

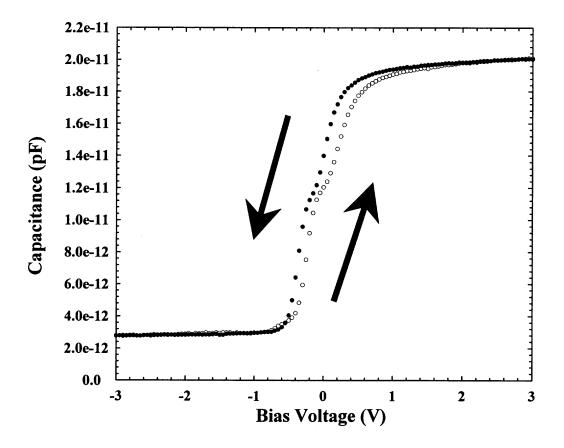

| 4.3    | C-V characteristics of a 140 Å hafnium oxide film                                                   | 60  |

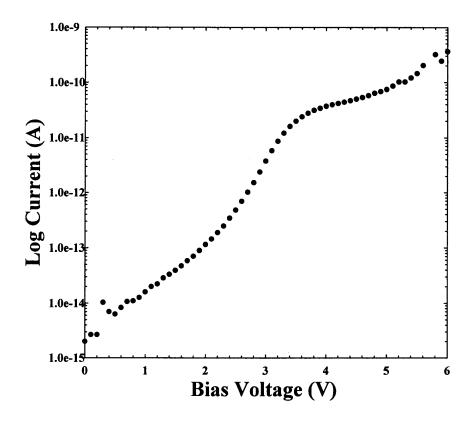

| 4.4    | I-V characteristics of a 140 Å hafnium oxide film                                                   | 62  |

| 4.5    | Sequential I-V runs showing the charging dynamics of the dielectric                                 | 63  |

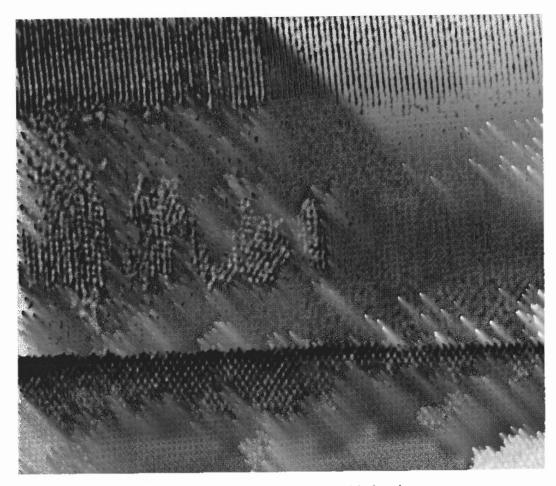

| 5.1    | High resolution TEM of SiO <sub>2</sub> /nc-Si/SiO <sub>2</sub> double barrier structure            | 68  |

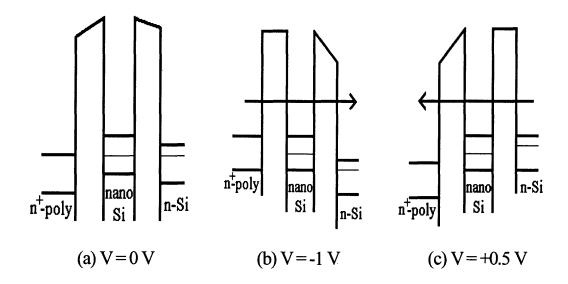

| 5.2    | Energy band diagrams for a double barrier structure on an n-type substrate                          | 69  |

| 5.3    | Current vs. Voltage for double barrier on n-type substrate                                          | 71  |

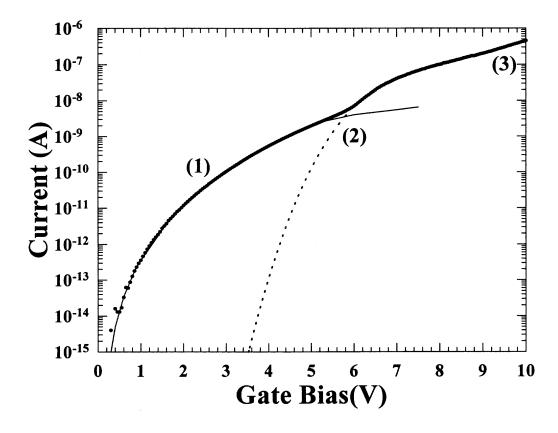

| 5.4    | Current vs. Voltage for double barrier on n-type substrate between 0 V and 10 V                     | 72  |

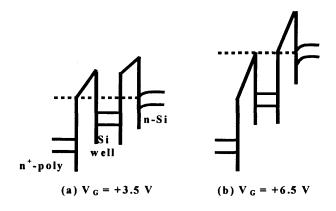

| 5.5    | Schematic energy band diagrams for $V = 3.5 \ V$ and $V = 6.5 \ V$                                  | 73  |

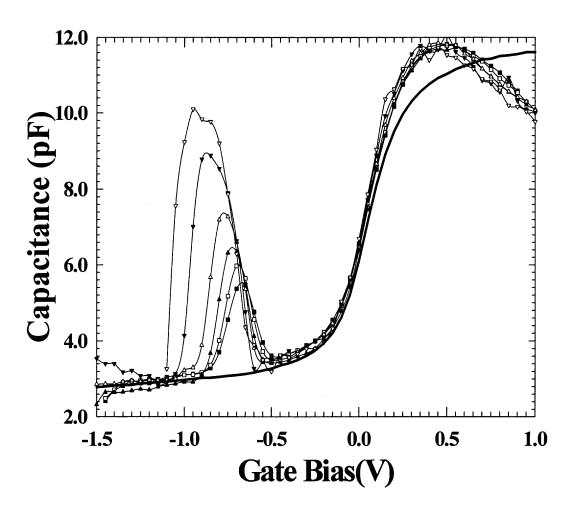

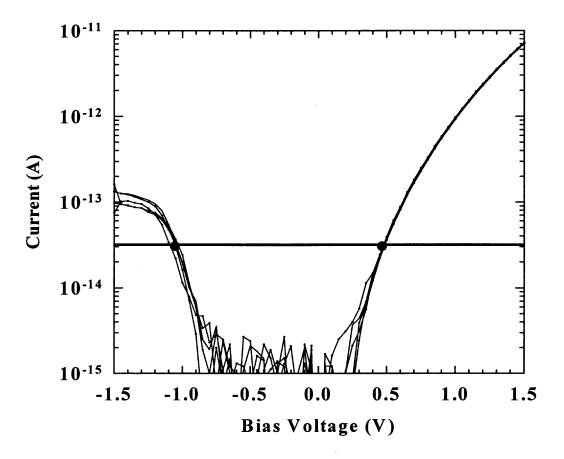

| 5.6    | C-V characteristics of double barrier on n-type substrate                                           | 75  |

| 5.7    | Degradation I-V curves                                                                              | 76  |

| 5.8    | Width of the window vs. number of cycles                                                            | 77  |

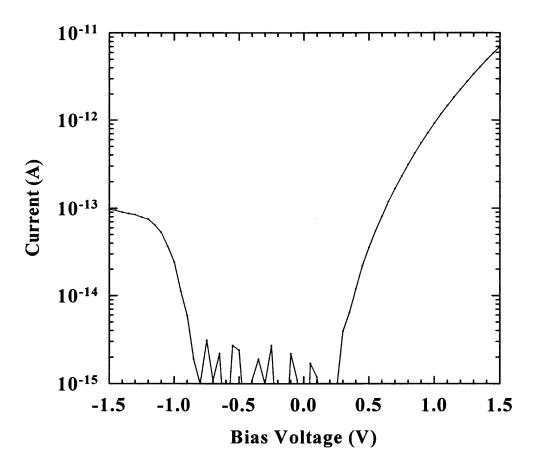

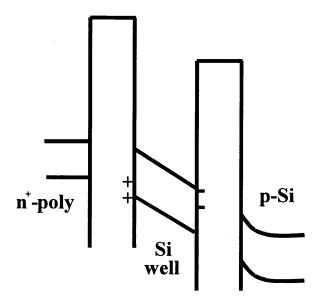

| 5.9    | Energy band diagram for a double barrier structure on an p-type substrate                           | 78  |

| 5.10   | Current vs. Voltage for double barrier on p-type substrate                                          | 80  |

# LIST OF FIGURES (Continued)

| Figure | Pa                                                                                                                          | age |

|--------|-----------------------------------------------------------------------------------------------------------------------------|-----|

| 5.11   | C-V characteristics of double barrier on p-type substrate                                                                   | 81  |

| 5.12   | Sequential I-V curves for negative voltages                                                                                 | 82  |

| 5.13   | Energy band diagram after the interfaces have been charged                                                                  | 84  |

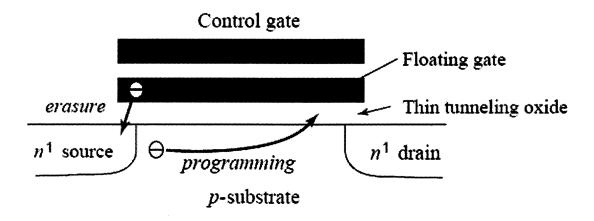

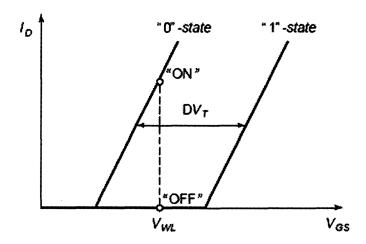

| 6.1    | Schematic cross-section of a traditional floating gate memory transistor                                                    | 86  |

| 6.2    | Threshold voltage shift in I-V curve of a non-volatile memory transistor as a result of charge storage on the floating gate | 87  |

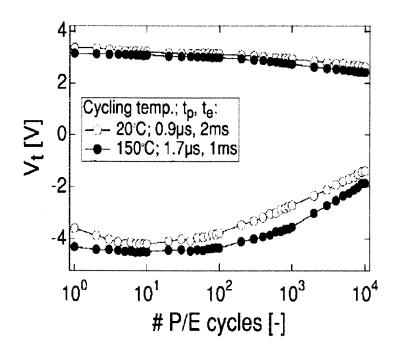

| 6.3    | Threshold voltage window closing as a result of program/erase cycles                                                        | 90  |

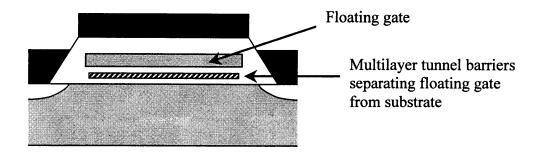

| 6.3    | Nonvolatile memory transistor with a multilayer tunnel barrier acting as the active dielectric                              | 94  |

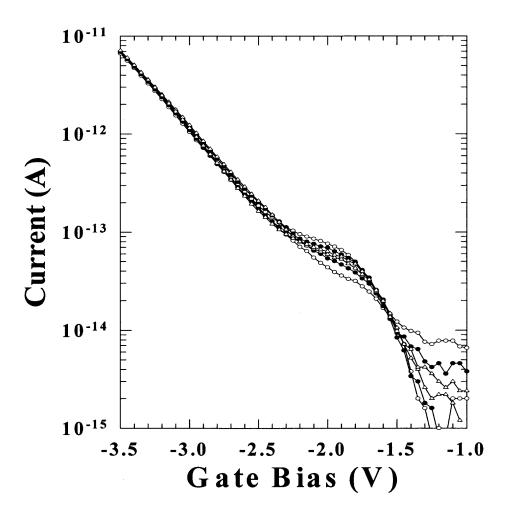

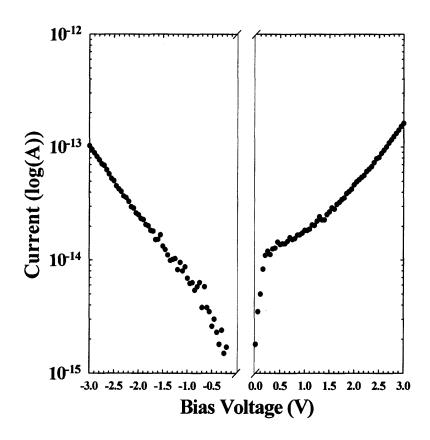

| 6.5    | Current-voltage characteristics of a multilayer tunnel dielectric on transistor Wafer                                       | 97  |

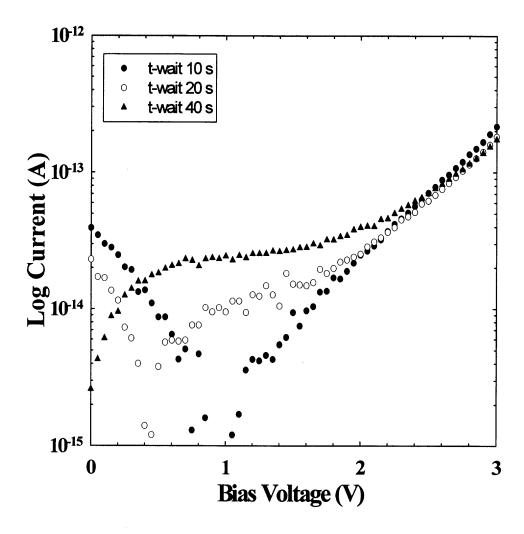

| 6.6    | Sequential I-V curves after different waiting times at 3 V                                                                  | 99  |

### **CHAPTER 1**

#### INTRODUCTION

Since the invention of the first integrated circuit, the semiconductor industry has seen a phenomenally rapid pace of improvements in device performance. This trend of ever smaller and faster devices is a result of the ability to exponentially reduce feature sizes of integrated circuits, a trend commonly known as "scaling". An indication of the pace at which devices are scaled down is known as Moore's Law. It was first introduced as an observation that the number of transistors per chip seemed to double every 24 months, but Moore's Law has been remarkably accurate in predicting the scaling trend for future device generations.

There are two very clear-cut reasons for scaling: smaller is cheaper and smaller is faster. There is no doubt that an important reason behind the scaling of transistor devices is an economic one; more transistors per wafer makes each individual transistor cheaper to produce. But a more important reason for scaling is the fact that the basic building block of CMOS technology, the MOSFET, operates faster when the overall size is shrunk.

Fundamental road blocks for continued scaling are appearing, calling into question the sustainability of the trend towards ever faster devices. On the other hand, scaling may also reveal device properties that were unknown. This offers opportunities to develop new devices and applications that were either unimaginable or impossible before.

### 1.1 Scope of Research

A reduction in overall feature sizes of a MOSFET requires a simultaneous reduction in the thickness of its gate dielectric, SiO<sub>2</sub>. As the thickness of the gate oxide is already in the ultrathin regime (<35 Å), and is expected to shrink even further, quantum mechanical tunneling, or direct tunneling, through the gate oxide becomes prohibitively large. As a result, characterization techniques need to be reevaluated. One particularly important technique, capacitance-voltage measurements, is the de facto industry standard to determine the electrical properties and integrity of the gate oxide. However, the presence of the direct tunnel leakage current renders this technique useless in the ultrathin regime. Characterization of ultrathin oxides is still crucial because of the importance of the properties of the gate dielectric on overall device performance. A new technique called leakage compensated charge measurement is introduced to that end.

Besides making characterization of ultrathin oxides problematic, the direct tunnel leakage current has obvious adverse effects on battery life (mobile applications) as well. Continued scaling of the dielectric thickness may well make the presence of the leakage current prohibitively large, endangering a further scaling down of feature sizes and, therefore, device performance. A large body of research exists that has reported on materials with a high dielectric constant as possible candidates to replace the gate dielectric of choice, silicon dioxide. One particularly promising candidate is hafnium oxide; this work will present one of the earliest research efforts into evaluating the properties of this material for such applications.

These first two topics dealt with the adverse effects of scaling and potential solutions to it. Scaling also offers opportunities. One such opportunity is the emergence

of new device applications based on the properties of ultrathin layers, in particular ultrathin layers of silicon and ultrathin layers of silicon dioxide. This research will focus on one particular system based on alternating layers of ultrathin silicon and ultrathin silicon dioxide. One example of new device applications that are possible with this system will be developed, a nonvolatile memory structure.

### 1.2 Statement of Purpose

The purpose of the research presented here has been to (1) develop a leakage compensated charge measurement for characterization of ultrathin silicon dioxides, (2) investigate the electrical properties of hafnium oxide as a possible candidate for advanced gate dielectric applications, (3) investigate the electrical properties of a silicon-based multilayer charge injection barrier and (4) develop a novel nonvolatile memory transistor that incorporates this barrier as the active tunnel dielectric.

### 1.3 Outline of the Dissertation

The dissertation is divided into seven chapters and two appendices. Chapter 2 presents a review of CMOS technology, a brief history, scaling and a review of the properties of ultrathin silicon dioxide. Chapter 3 describes the principle of a leakage compensated charge measurement and results of such measurements on ultrathin silicon dioxide devices that exhibit a large leakage current. Chapter 4 presents some of the earliest results ever obtained on the electrical properties of hafnium oxide as a candidate for future gate dielectric applications. Chapter 5 introduces a silicon-based multilayer structure and discusses the electrical properties the system has. Chapter 6 describes the fabrication and characterization results of a new application that was made possible by the properties of silicon-based multilayer barriers, a nonvolatile memory transistor.

Chapter 7 presents the conclusions drawn from this research and finishes with suggested future work. Appendix A contains a table of the process parameters used for the deposition of thin hafnium oxide layers discussed in Chapter 4. Finally, Appendix B contains a table of the process parameters used to fabricate the tunnel stack that is incorporated as the active dielectric in the nonvolatile memory transistor fabrication run of Chapter 6.

### **CHAPTER 2**

### REVIEW OF CMOS TECHNOLOGY

### 2.1 Overview

This chapter covers a review of CMOS technology and ultrathin silicon oxides. First it gives a brief introduction and history of CMOS technology; then it will describe the operation and device characteristics of the basic building block of CMOS, the MOSFET. This leads to Moore's Law, the scaling of devices to smaller sizes and its effect on device performance. The final section of this chapter reviews the properties, characterization techniques and fabrication of ultrathin silicon oxide layers.

### 2.2 Introduction to CMOS Technology

Complementary MOS is so-named because it uses both p- and n-type (complementary) MOS transistors in its circuits. Figure 2.1 depicts a schematic illustration of the basic building block of integrated circuits, the CMOSFET, the Complementary Metal Oxide Semiconductor Field Effect Transistor. The left part of the illustration shows the n-doped source and drain regions in a p-type tub, as well as the n-gate separated from the channel region by a gate dielectric. Applying a positive voltage to the gate electrode will set up an electric field in the semiconductor and induce the forming of an n-type channel underneath the gate dielectric, allowing electrons to travel from the source to the drain. Hence, the name NMOSFET. The right part of the illustration shows the same configuration with the role of electrons now being played by holes, hence PMOSFET. The heart of the structure, the gate dielectric between the gate and the channel is arguably the most important part of the entire transistor structure and is typically formed by a

silicon dioxide layer. It is the unique properties of this silicon – silicon dioxide interface that is solely responsible for the existence of the silicon based microelectronics industry we know today, as will be explained later in this chapter.

**Figure 2.1** Cross-section of a Complementary Metal Oxide Semiconductor Field Effect Transistor (CMOSFET).

### 2.3 History of CMOS Technology

It is important to note that even though CMOS was introduced in 1963 [1], it was not the technology of choice even as late as the late 1970's; NMOS was. The popularity of NMOS over PMOS was due to the fact that it was cheap to fabricate and faster than PMOS because of the higher electron mobility. However, NMOS gates draw dc power even when no signal is applied, hence an integrated circuit will draw a steady current in the standby mode. Consequently, as the number of transistors on the chip grows, the power being dissipated also increases. Although this was always a limitation of NMOS, it did not represent a drawback for most applications when the number of devices was relatively small. Such was the situation at the level of device integration that existed up

to 1978 when Intel introduced the 8086 processor which was the last processor to be built in NMOS. It had 29,000 devices and dissipated 1.5 W of power at 8 MHz. However, when this same processor was later reintroduced in CMOS technology as the 80C86 the power dissipation dropped to 250 mW.

So why this decrease in power consumption for CMOS technology? In a CMOS transistor only one of the two transistors is driven at any one time. This means that a high impedance path exists from the supply voltage to ground, regardless of whether the transistor is in the on- or off-mode. Hence, very little current flows and almost no dc-power is dissipated. CMOS thus allows the manufacturing of circuits that need very little standby power.

The problem of power dissipation can also be considered from both a chip perspective and a system perspective. From the chip perspective, if microprocessors of the 32-bit generation — which only now are starting to be replaced by 64-bit microprocessors for high-end applications — were built in NMOS, they would dissipate 5 to 6 W of power. This would lead to severe heating and reliability concerns. In addition, expensive packages would be needed to house such chips. However, building these same microprocessors in CMOS reduces power consumption to about 1 W. From the system perspective, let's consider memory chips. Although a 1-Mbit DRAM may consume only 120 mW of power in NMOS, it consumes even less, ~ 50 mW, in CMOS. Since there may be thousands of memory chips in a system, the ramifications of lower power dissipation are significant. Smaller power supplies and smaller cooling fans are two important ramifications.

Even though the most important advantage of CMOS is its significantly reduced power density and dissipation, there are other advantages as well, such as device performance, reliability, circuit design and cost [2].

### 2.4 Moore's Law and Scaling

For four decades, the semiconductor industry has distinguished itself by the rapid pace of improvement in its products. The principal categories of improvement trends are shown in the table below with an example of each.

Table 2.1 Scaling trends

| TREND             | EXAMPLE                           |

|-------------------|-----------------------------------|

| Integration Level | Components/Chip (Moore's Law)     |

| Cost              | Cost per function                 |

| Speed             | Clock Rate, GHz                   |

| Power             | Laptop or cell phone battery life |

| Compactness       | Small and light-weight products   |

| Functionality     | Nonvolatile memory                |

Source: International Technology Roadmap for Semiconductors (Semiconductor Industry Association), Santa Clara, CA, 2003 [3].

All of these trends, sometimes referred to as "scaling" have resulted principally from the industry's ability to exponentially decrease the minimum feature sizes used to fabricate integrated circuits. Of course, the most frequently cited trend is in integration

level, which is usually expressed as Moore's Law [4,5], i.e. the number of components per chip doubles every 24 months. The most significant trend for society is the decreasing cost per function, which has led to significant improvements in productivity and quality of life through proliferation of computers, communication devices and consumer electronics. The author would like to point out that, even though he is fully aware of the near sanctified status that the phrase "Moore's Law" has attained in the semiconductor community, the term Moore's Law is a misplaced term, since it describes merely an observation made by Mr. Moore in December 1975, not a law in the mathematical sense of the word that there is a proof for it. As a matter of fact, Moore's Law is very often erroneously described as a doubling of components per chip every 18 months.

### 2.4.1 MOSFET Operation

As noted previously, the Metal Oxide Semiconductor Field Effect Transistor (MOSFET) forms the basic building block of the microelectronics industry. As a matter of fact, more than 99% of all integrated circuits are MOSFETs used for random-access memory (RAM), flash memory, microprocessors and application specific integrated circuits (ASIC). Figure 2.2 shows a cross-sectional view of an n-channel MOSFET and will be used to illustrate the operation of the device [6].

Figure 2.2 Cross-section of an n-channel MOSFET

The device has a gate terminal to which the input signal is applied as well as source and drain terminals across which the output voltage is developed and through which the output current flows. A channel region in the silicon substrate under the gate electrode separates the source and the drain. The substrate is also physically separated from the gate electrode by an insulating layer – typically SiO<sub>2</sub> – so that no current flows between the gate electrode and the semiconductor.

In simplest terms, the operation of a MOSFET involves the application of an input voltage to the gate, which sets up a transverse electric field in the channel region of the device. By varying this transverse electric field, it is possible to modulate the conductance in the channel region. Since an electric field controls current flow, such devices are called *field effect transistors*. If no gate bias is applied, the electrical path between source and drain consists of two back-to-back pn junctions in series, one of which will be in reverse direction. The channel current I<sub>D</sub> will only consist of the reverse-bias diode leakage current and hence will be considered negligibly small.

When positive bias is applied to the gate electrode, electrons will be attracted to the channel region and holes (the majority carriers in a p-type substrate) will be repelled. Once enough electrons have been drawn into the channel by the positive gate voltage to exceed the hole concentration, the region behaves like an n-type semiconductor. Under these circumstances, an n-type channel connects the source and the drain regions. Current will flow if a voltage  $V_{DS}$  is applied between the source and the drain terminals. The voltage-induced n-type channel does not form unless the voltage applied to the gate exceeds a certain threshold voltage  $V_T$ . A device as is described above is referred to as an enhancement mode (or normally OFF) transistor. It is also possible to build MOSFETs in which a conducting channel region exists when  $V_G = 0$  V. Such devices are referred to as depletion mode (or normally ON) transistors, since a bias voltage is needed to deplete the channel region of majority carriers.

### 2.4.2 MOSFET Characteristics

This section will show the equations that describe the current-voltage characteristics of an NMOSFET. In the simplest model, if  $V_G$  is smaller than  $V_T$ , no channel exists and no current is assumed to flow between the source and the drain. If  $V_G$  is greater than  $V_T$ , a conducting channel is present and  $V_{DS}$  causes a drain current  $I_D$  to flow from source to drain. For small values of  $V_{DS}$ , the drain current  $I_D$  is linearly related to  $V_{DS}$ . In this so-called *linear region* of operation, the equation for the drain current is:

$$I_{D} = \frac{1}{2} \cdot \mu_{n} \cdot C_{ox} \cdot \frac{W}{L} \left[ 2(V_{G} - V_{T})V_{DS} - V_{DS}^{2} \right]$$

(Equation 2.1)

where  $\mu_n$  is the mobility of electrons in the channel,  $C_{ox}$  the oxide capacitance, W the width of the channel region and L the length of channel region between source and drain, or *gate length*. This expression is valid when  $V_G > V_T$  and  $V_{DS} < V_G - V_T$ .

As the value of  $V_{DS}$  increases, the induced conducting-channel charge decreases near the drain. When  $V_{DS}$  equals or exceeds  $V_G - V_T$ , the channel is said to be pinched off. Increases above this critical voltage produce little change in  $I_D$  and Eq. 2.1 no longer applies. The value of  $I_D$  in this region is given by the following expression:

$$I_D = \frac{1}{2} \cdot \mu_n \cdot C_{ox} \cdot \frac{W}{L} (V_G - V_T)^2$$

(Equation 2.2)

This is the so-called *saturation region* of operation.

A plot of  $I_D$  versus  $V_{DS}$  (with  $V_G$  as parameter) for a NMOSFET as described by the previous two equations is depicted in Figure 2.3. If the value of  $V_G$  is smaller than  $V_T$ , the transistor is said to be in *cutoff*. In the simplified model given here,  $I_D$  is assumed to be zero in cutoff. It is important to note that this model does not take into account two very important factors that can significantly affect device performance, namely short-channel effects and subthreshold currents. Discussion of these effects lies outside of the scope of this work.

Another important parameter is the so-called saturation transconductance  $g_m$  and is defined as  $g_m = dI_D / dV_G$ . As such, it can be viewed as a measure of the easiness with which charge carriers can drift from the source to the drain. From the previous equation it can be shown that the transconductance follows this expression:

$$g_{m} = 2 \cdot \mu_{n} \cdot C_{ox} \cdot \frac{W}{L} (V_{G} - V_{T})$$

(Equation 2.3)

Figure 2.3 Drain current  $I_D$  vs. Drain voltage for different gate voltages. The drain current saturates at a value that is described by Equation 2.2.

A critical metric for transistor speed is the intrinsic switching frequency  $f_i$ . It can be shown that this is not limited by the time it takes the charge carriers to cross the channel from source to drain, the channel transit time, but rather by the intrinsic delay time  $\tau_i$  required to charge and discharge the load capacitance of the transistor that exists between device electrodes and between the interconnecting lines of the circuit. The equation that describes the intrinsic delay time  $\tau_i$  is as follows:

$$\tau_{i} = \frac{1}{f_{i}} = \frac{C_{L} \cdot V_{dd}}{I_{D}}$$

(Equation 2.4)

where  $C_L$  is the load capacitance of the transistor and  $V_{dd}$  the power supply voltage.

The equations described in this section are instructive in explaining how a reduction in transistor size will increase device performance as will become clear in the following section.

### 2.4.3 Why Scaling?

As mentioned earlier in this chapter, Moore's Law describes a historic observation of a doubling of components per chip every 24 months. Even though the economic reasons behind this endless effort to ever smaller devices can not be dismissed – smaller is cheaper – it has really been the quest for ever faster devices as described by Equation 2.4 that has been the driver behind the steady performance improvement of CMOS devices.

From Equation 2.4 it is clear that there are three ways to reduce the delay time  $\tau_i$ , and therefore increase the speed of the transistor: a reduction in the load capacitance  $C_L$ , a reduction in the power supply voltage  $V_{dd}$  and an increase in the drive current  $I_D$ . While all three trends occur simultaneously and are important parameters in the scaling of transistors, it is the increase in  $I_D$  that is the most instructive in showing that in order to improve the performance of the device, one has to reduce the device in size.

Equation 2.2 predicts that in order to increase  $I_D$ , one can simply increase the dimension of the gate width W. However, when minimum-sized devices are preferred for economic reasons, this is not an option. The drive current  $I_D$  also is inversely proportional to the channel length L and minimum channel lengths are therefore required. From the dependence of  $I_D$  on the electron mobility  $\mu_n$  it is clear that the electron mobility must be as high as possible. Since the mobility of carriers decreases as the doping concentration of the channel increases, lightly doped channel regions are important. In addition, many efforts are under way to increase the carrier mobility through alternative means such as using strained-silicon substrates [7].

Equation 2.2 also shows that the gate oxide capacitance  $C_{ox}$  is proportional to  $I_D$ . Since  $C_{ox}$  is inversely proportional to the gate oxide thickness  $t_{ox}$ , as thin a gate oxide as

possible is needed, commensurate with oxide breakdown and reliability considerations. However, continued scaling of gate oxide thicknesses results in a significant increase in gate leakage current due to a sharply increasing direct tunneling leakage current which has adverse effects on device performance, in particular for low-power applications.

Even though all the factors mentioned here are important aspects of device scaling, it is the issues related to the scaling of the gate oxide that will be discussed in detail in this work.

### 2.5 Ultrathin Silicon Dioxide

From the previous section it has become clear that the gate dielectric, usually silicon dioxide, is perhaps the most critical part of a MOSFET. It is largely the wonderful characteristics of silicon dioxide that have enabled an aggressive scaling of MOSFETs to ever smaller devices. The table below shows some selected properties of SiO<sub>2</sub>.

**Table 2.2** Properties of silicon dioxide

| Selected properties of SiO2 gate dielectric layers                                                           |  |  |

|--------------------------------------------------------------------------------------------------------------|--|--|

| Native to silicon (SiO <sub>2</sub> is the only stable phase on Si)                                          |  |  |

| Low interfacial (Si/SiO <sub>2</sub> ) defect density (~10 <sup>10</sup> eV <sup>-1</sup> cm <sup>-2</sup> ) |  |  |

| High melting point (1730 °C)                                                                                 |  |  |

| Large energy band gap (9 eV)                                                                                 |  |  |

| High resistivity ( $10^{15} \Omega$ cm)                                                                      |  |  |

| High dielectric strength (15 MV/cm)                                                                          |  |  |

| Dielectric constant = 3.9                                                                                    |  |  |

SiO<sub>2</sub> is native to silicon, and with it, forms a low defect density interface. It also has high resistivity, excellent dielectric strength, a large band gap, and a high melting point. These properties of SiO<sub>2</sub> are in large part responsible for enabling the microelectronics revolution. Indeed, the first transistor made in 1947 was not made with silicon but with germanium. It was not selected as the semiconducting material of choice, mainly due to the lack of a stable native oxide and a low defect density interface. The ease of fabrication of SiO<sub>2</sub> gate dielectrics and the well passivated Si/SiO<sub>2</sub> interface that have made this possible. SiO<sub>2</sub> has been and continues to be the gate dielectric of choice for the MOSFET. In spite of its many attributes, however, SiO<sub>2</sub> suffers from a relatively low dielectric constant,  $\kappa = 3.9$ . Since high gate dielectric capacitance is necessary to produce the required drive currents for submicron devices [8], and further, since capacitance is inversely proportional to gate dielectric thickness, the SiO<sub>2</sub> layers have of necessity been scaled to ever thinner dimensions, as is shown in Figure 2.4.

Figure 2.4 Scaling of gate dielectric thickness [9].

This gives rise to a number of problems, including impurity penetration through the SiO<sub>2</sub>, enhanced scattering of carriers in the channel, possible reliability degradation, high gate leakage current, the need to grow ultrathin and uniform SiO<sub>2</sub> layers and the need to devise characterization techniques that can be used for these ultrathin layers. Any of these effects may ultimately pose a fundamental limit to the continued scaling of SiO<sub>2</sub>.

### 2.5.1 Fundamental limits?

Due to the large band gap of  $SiO_2$ ,  $\sim 9$  eV, and the low density of traps and defects in the bulk of the material, the carrier current passing through the dielectric layer is normally very low. For ultrathin films this is no longer the case. When the physical thickness between the gate electrode and doped Si substrate becomes thinner than  $\sim 30$  Å, direct tunneling through the dielectric barrier dominates leakage current [10,11] According to fundamental quantum mechanical laws, the tunneling current increases exponentially with decreasing oxide thickness. Figure 2.5 depicts gate leakage currents for oxide thicknesses ranging from 32 Å to 6 Å:

Figure 2.5 Gate leakage current density as a function of oxide thickness ranging from 32 Å to 6 Å [12].

The leakage current is seen to increase by one order of magnitude for each 2 Å thickness decrease. Assuming a maximum allowable gate current density of 1 A/cm<sup>2</sup> for desktop computer applications, and 10<sup>-3</sup> A/cm<sup>2</sup> for portable applications, minimum acceptable SiO<sub>2</sub> physical thicknesses would be approximately 13 and 19 Å, respectively.

Reliability, which is the lifetime to breakdown, of ultrathin SiO<sub>2</sub> is a major concern for oxide scaling into the sub-20 Å regime. Electrons traveling through the SiO<sub>2</sub> layer may create defects such as electron traps and interface states [13] that in turn, upon accumulation to some critical density, degrade the insulating properties of the oxide. It has been predicted that reliability may attain unacceptable levels at thicknesses as low 10 Å [14], but considerable work is still being done in this field.

In addition, a reduced drive current has been reported in small transistors with ultrathin gate dielectrics less than 13 Å [15]. Thus for SiO<sub>2</sub> layers thinner than 13 Å there is no advantage in performance for incurring the additional burden of an ever increasing gate leakage current. The cause of the decreased drive current is not fully understood. One possibility is an additional scattering component from the upper SiO<sub>2</sub>/Si interface. Another cause could be a universal mobility effect, i.e. a lowered mobility due to enhanced scattering because of carrier confinement in the inversion layer of the ultrathin oxide layer.

Thus, the fundamental limits imposed on SiO<sub>2</sub> are excessively high leakage current, reduced drive current and reliability. All three effects suggest that the fundamental scaling limit is somewhere in the range from 10 to 13 Å. In any case, it is important to point out that it has been reported that the fundamental physical limit to SiO<sub>2</sub> is believed to be 8 Å [16]. Oxides thinner than 8 Å can no longer be considered SiO<sub>2</sub>, just two interfacial layers sandwiched in between the silicon substrate and the polycrystalline silicon gate. Thus, layers this thin will no longer have the same properties as bulk SiO<sub>2</sub>.

### 2.5.2 Electrical Characterization

There are many analytical techniques available to study both the physical as well as the electrical properties of SiO<sub>2</sub>. Physical characterization techniques can be grouped in optical techniques (e.g. ellipsometry), X-ray techniques (e.g. X-ray photoemission spectroscopy (XPS)), ion beam based techniques (e.g. medium energy ion scattering spectroscopy (MEIS) and secondary ion mass spectroscopy (SIMS)), electron microscopy (e.g. transmission electron microscopy (TEM)) and scanning probe microscopic

techniques (e.g. scanning tunneling microscopy (STM)). While all of these physical characterization techniques have been and continue to be very valuable in understanding the properties of ultrathin SiO<sub>2</sub> and the Si/SiO<sub>2</sub> interface, it is the electrical properties that have been a focus of this work. In this section, the application of electrical characterization techniques to ultrathin SiO<sub>2</sub> will be discussed.

The most frequently used electrical technique to assess the properties of both the thin oxide layer and its interface with Si is the C-V measurement. In thicker oxide layers C-V curves can be fitted satisfactorily with classical models[17] The C-V technique can be used to determine flatband and threshold voltage, fixed charge, and interface state density. It is also often used to determine the oxide thickness. In sub-40 Å oxide layers, C-V measurements provide the same information, but the interpretation of the data requires considerable caution. The assumptions needed to construct the "classical model" are no longer valid, and quantum mechanical corrections become mandatory, thus increasing the complexity of the analytical treatment. First, several authors have demonstrated that for ultrathin layers, Maxwell-Boltzman statistics no longer describe the charge density in the inversion and accumulation layers satisfactorily, and should be replaced by Fermi-Dirac statistics. In addition, band bending in the inversion layer near the semiconductor-insulator interface becomes very strong, and a potential well is formed by the interface barrier and the electrostatic potential in the semiconductor. This potential well may be narrow enough to give rise to electron confinement at discrete energy levels [18,19]. One of the main effects of the quantum mechanical treatment of the inversion layer is a considerable shift of the inversion charge centroid away from the

semiconductor-insulator interface and can be treated as an additional capacitor in series with the oxide capacitance.

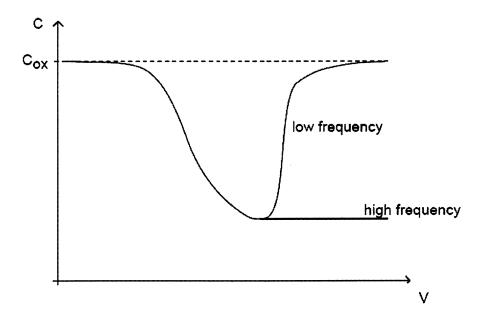

A similar effect is generated by polycrystalline Si depletion on the gate side of the capacitor of a MOS transistor [20]. This effect is related to both the high fields at the insulator surface as well as the incomplete activation of the dopants near the polycrystalline Si/SiO<sub>2</sub> interface. A carrier concentration profile with a finite width, having a centroid several tenths of a nanometer away from this interface, results. This effect can also be modeled as an additional capacitance in series with the oxide capacitance. As a consequence of quantum mechanical effects and polycrystalline Si depletion, the measured capacitance is smaller than the expected "physical" oxide capacitance, and the difference becomes very significant for ultrathin layers. This also implies that oxide thickness extraction from C-V measurements becomes more difficult. For very thin oxides, typically sub-30 Å, the huge leakage current through the oxide, due to direct tunneling of electrons creates an additional complication in the interpretation of C-V curves. A sharp drop in the capacitance is observed as the voltage increases. This effect is illustrated in Figure 2.6 below. As a matter of fact, the next chapter provides an answer to this problem through a new C-V technique that utilizes a tunnel leakage compensation circuit, allowing the use of standard C-V characterization even for ultrathin layers.

Figure 2.6 C-V characteristics distorted by leakage currents through the ultrathin gate oxide.

Another critical technique to study the bulk and interfacial properties of these layers is the measurement of the tunnel current. When a voltage V is applied across an oxide layer with thickness  $t_{ox}$ , the resulting oxide field,  $E_{ox} = V_{ox} / t_{ox}$ , gives rise to a current flow through the oxide. This current originates from electrons that tunnel quantum mechanically through the Si/SiO<sub>2</sub> potential barrier from the Si conduction band to the SiO<sub>2</sub> conduction band as illustrated in the figure below. When tunneling occurs through a triangular barrier, Figure 2.7(a), the conduction mode is called Fowler-Nordheim (FN) tunneling and the measured current density,  $J_{FN}$ , can be described by the following formula:

$$J_{FN} = A \cdot E_{ox}^{2} \cdot e^{\left(-\frac{B}{E_{ox}}\right)}$$

(Equation 2.5)

where A and B are constants given by:

$$A = \frac{q^3}{8\pi\varphi_b} \frac{m}{m^*}$$

(Equation 2.6)

$$B = 4\sqrt{2m^*} \frac{\phi b^{3/2}}{3\hbar q}$$

(Equation 2.7)

in which q is the charge of a single electron  $(1.6x10^{-19} \text{ C})$ , m the mass of a free electron  $(9.1x10^{-31} \text{ kg})$ , m\* the effective mass of a free electron in the bandgap of SiO<sub>2</sub> (0.42m), h Planck's constant and  $\phi_b$  the energy barrier at the interface  $(3.2 \text{ eV for Si/SiO}_2)$ .

When the oxide voltage drops below 3.2 V, the electron barrier height, electrons can no longer enter the oxide conduction band, but tunnel directly from the gate to the silicon substrate as can be seen in Figure. 2.7(b). In state-of-the art CMOS technology, direct tunneling is the dominant current conduction mechanism at operating voltage. The direct current density cannot be described easily in a closed analytical form, but several approximate formulas and simulations have been proposed [21].

Figure 2.7 Conduction mechanisms through SiO<sub>2</sub>: (a) Fowler-Nordheim tunneling and (b) direct tunneling.

In addition there are other electrical characterization techniques such as charge pumping, conductance measurements and inelastic tunneling spectroscopy. Since these techniques have not been used in this research, it is outside the scope of this document to discuss them here.

### 2.5.3 Oxide Degradation and Breakdown during Electrical Stress

In this section oxide degradation during electrical stress, ultimately leading to breakdown, is briefly discussed. Oxide degradation is defined as the continuous, gradual deterioration of the oxide properties, resulting from structural damage generated in the oxide by electrical stress. Breakdown is triggered when the accumulated damage reaches a critical level.

Degradation can manifest itself in a variety of phenomena. During high field oxide stressing, interface traps are created at the Si/SiO<sub>2</sub> interface [22.]. Their density D<sub>it</sub> can be obtained from either C-V or charge pumping measurements. It has been claimed that the interface trap density reaches a critical density at the moment of oxide breakdown. In addition, traps are created in the bulk of the oxide that that can be filled with either holes or electrons. This leads to a net positive or negative charging of the oxide. This net charging manifests itself in a net increase of the tunnel current for positive charging or a net decrease for negative charging.

Another phenomenon that occurs during oxide degradation is the generation of stress induced leakage current (SILC) through the gate [23]. It manifests itself as a current that is obtained at ever decreasing applied voltages when the fluence of injected charge carriers increases. The SILC is caused by trap-assisted tunneling from the gate to the substrate. The traps act as "stepping stones" for electrons to tunnel through the oxide.

This SILC itself is in some cases an important reliability problem. Leakage current through the gate translates in a power waste problem in MOSFETs, resulting in reduced battery life. It is also detrimental to the performance of traditional floating gate nonvolatile memory devices, since it causes the charged that is stored on the floating gate to leak off after continuous cycling. This is a problem that will be addressed in more detail in later chapters.

It is clear that trap generation is the key factor in determining oxide degradation and breakdown. Different models have been proposed that describe this process, but the exact physical nature of trap generation is still under considerable debate.

### 2.5.4 Fabrication of Ultrathin Oxides

The gate dielectric's ultimate electrical performance is determined not only by its composition and fabrication method (growth or deposition), but also by pregrowth surface preparation and postfabrication processing such as plasma etching of the gate stack. The interdependence between the various steps, especially surface preparation, becomes more prominent for ultrathin gate dielectric layers, since the Si/SiO<sub>2</sub> interface is a more significant part of the layer as it gets thinner.

Surface preparation is a more appropriate term than cleaning, since preparation of the Si surface for subsequent oxidation is far more involved than merely removing contamination. In fact, conditioning of the surface to result in its smoothest and cleanest state is just as important a step as the actual dielectric fabrication. Among the important physical attributes of ultrathin SiO<sub>2</sub> and the Si/SiO<sub>2</sub> interface that can be influenced by surface preparation are interfacial roughness, interfacial transition layer width, contamination level of the SiO<sub>2</sub> and the interface and chemical bonding structure at the

interface. Wet cleaning currently dominates pregate oxidation clean applications. The so-called "RCA clean" is the most widely used clean for removing organic compounds and metals from Si wafers. Subsequent processing in HF removes the chemical oxide that results from the RCA clean. Dry cleaning technology, so called because it involves vapor or gas, and not liquid cleaning of the wafer surfaces, is presently the subject of much research. This is driven primarily by the drive towards *in situ*, cluster tool processing. Some research has already demonstrated oxide reliability increases due to dry pregate oxide cleans.

Fabrication of ultrathin dielectric layers may be accomplished by growth or deposition. Growth refers to thermal oxidation of the silicon. Deposition usually refers to chemical or physical generation of the layer, not involving a reaction with the Si substrate. The utter simplicity of growing thermal SiO<sub>2</sub> by exposing Si to O<sub>2</sub> at elevated temperatures, as well as the perfection of the resulting interface, are in large part responsible for the success of Si as the integrated circuit material of choice. Virtually all SiO<sub>2</sub> gate dielectrics are grown by thermal oxidation, using O<sub>2</sub> or H<sub>2</sub>O as the oxidant species. Since oxidation in H<sub>2</sub>O enhances oxidation kinetics, it is not generally used for the growth of ultrathin films. Thermal oxides consume Si during growth, thereby continuously creating a new and fresh interface. Thermal growth usually takes place at a higher temperature than chemical or physical deposition, and higher fabrication temperature has been associated with improved dielectric properties.

While the seminal paper by Deal and Grove [24] laid out the mechanism for silicon oxidation, much still remains under debate, especially in the ultrathin regime. The Deal-Grove model treats Si oxidation as the reaction of Si and O at the Si/SiO<sub>2</sub> interface,

accomplished by diffusion of  $O_2$  through the growing oxide. For thick films, the model predicts a parabolic dependence of oxidation time on thickness because the growth is limited by diffusion. In thinner films, the model shows that the reaction rate at the interface governs the growth and results in a linear relationship between the oxidation time and thickness.

There are currently two primary thermal techniques for growing SiO<sub>2</sub>, furnace or rapid thermal oxidation, RTO. Oxidation usually takes place in the temperature range of 750–1100 °C. Furnace technology is still the manufacturing standard for ultrathin oxide growth. Furnaces are robust and reliable and offer excellent thickness uniformity. In addition it allows wafers to be processed in "batches". On the other hand, RTO offers better absolute thickness control for oxides <20 Å, a greater processing temperature range, and is "cluster-friendly," i.e. processing chambers can be integrated for control of interfaces. However, wafers are processed individually instead of in batches.

Chemical deposition processes are usually used when a lower thermal budget for the dielectric growth step is desired. Since deposition kinetics are slow at such temperatures (typically 350–600 °C), a plasma source is commonly used to activate the reaction. Chemical deposition methods do not consume the substrate, unlike thermal oxidation, and interfacial properties are usually inferior to those of thermal oxides. High temperature anneals (>750 °C) are usually necessary to bring the electrical performance up to the level of thermal oxides. SiO<sub>2</sub> layers have been deposited by chemical vapor deposition (CVD). However, their application to ultrathin gate dielectrics will be limited due to difficulties in controlling deposited layer thickness uniformity across large wafers.

Atomic layer deposition (ALD), in which films are grown approximately one monolayer at a time, has been used to grow ultrathin SiO<sub>2</sub> layers. This may be an important technique to grow <5 Å SiO<sub>2</sub> layers, useful as buffer layers between Si and high- k gate dielectrics. ALD has the outstanding advantages of superb conformal coverage as well as precise thickness control.

Crucial electrical performance parameters such as mobility and interface state density are directly related to physical structure and chemical bonding at the Si/SiO<sub>2</sub> interface. This interface does not reach its final configuration after oxidation, but rather after all postoxidation processing has been completed. Since the interface is defined by the last SiO<sub>2</sub> to form and the last thermal treatment it is exposed to, postoxidation processing, which involves among other steps implant activation annealing, polycrystalline Si deposition, and plasma etching and deposition, greatly impacts the properties of the gate dielectric. It is generally agreed that annealing parameters play an important role in device manufacturing. However, in most cases these parameters are chosen empirically and not optimized.

#### **CHAPTER 3**

## C-V CHARACTERIZATION OF ULTRATHIN SIO<sub>2</sub>

#### 3.1 Overview

For over two decades, capacitance-voltage (C-V) measurements of MOS structures have been a key analysis tool for the semiconductor industry in understanding the electrical properties of silicon dioxide as well as the properties of the Si/SiO<sub>2</sub> interface. However, with continued scaling of the gate dielectric thickness into the direct tunneling regime, <3.5 nm, the transport of carriers through the dielectric distorts the C-V characteristics, rendering this technique no longer useful for future device characterization [25-33]. This chapter describes an approach to overcome this difficulty using a leakage-compensated charge method (LCCV) which can produce true static C-V curves even when the leakage current is over five orders of magnitude larger than the displacement current that would be expected in a corresponding quasistatic measurement.

In the first part of this chapter, the MOS system is introduced and its capacitance behavior under a bias voltage. The following section explains the principle of the leakage compensated charge measurement. Experimental results on oxides as thin as 2.4 nm will be presented as well as a discussion of the results.

## 3.2 The MOS System

Figure 3.1 provides a schematic overview of the various regions associated with the gate stack of a MOSFET.

Figure 3.1 Cross-section of the gate stack in a MOSFET structure.

The gate dielectric (typically SiO<sub>2</sub>) insulates the gate electrode from the silicon substrate. Gate electrodes in modern CMOS technology are composed of highly doped polycrystalline silicon. The interfacial regions between the gate dielectric and the gate (upper interface) and between the gate dielectric and the substrate (lower interface) are typically around 0.5 nm thick. These interfaces are particularly important with respect to device performance. For instance, they represent a capacitance that can be relevant if the thickness of the interface is substantial to the overall thickness of the dielectric. The lower interface must be of high quality, i.e. low interface trap density in order to minimize scattering in the top layer of the substrate, the channel region. Scattering in the channel region adversely affects the mobility of charge carriers in the channel and therefore the transistor drive current.

It is instructive to consider the energy band diagrams for an ideal MOS structure with zero applied voltage depicted in Figure. 3.2.

Figure 3.2 Energy band diagrams for an ideal MOS structure with zero applied voltage; (a) on n-type silicon and (b) on p-type silicon.

Figure 3.2(a) shows the energy band diagram for an MOS structure on an n-type substrate, Figure 3.2(b) for a p-type substrate. For these ideal structures, at V=0 applied voltage on the gate, the work function difference between the gate and semiconductor substrate,  $\Phi_{ms}$ , is zero. Or,

$$\Phi_{ms} = \Phi_m \cdot \left( \chi + \frac{E_g}{2q} - \Psi_B \right) \qquad \text{(n-type)}$$

(Equation 3.1)

and

$$\Phi_{ms} = \Phi_{m} \cdot \left( \chi + \frac{E_{g}}{2q} + \Psi_{B} \right)$$

(p-type) (Equation 3.2)

where  $\Phi_m$  is the metal work function,  $\chi$  the electron affinity,  $E_g$  the bandgap of the semiconductor (1.1 eV for Si) and  $\psi_B$  the potential difference between the Fermi level  $E_F$  and the intrinsic Fermi level  $E_i$ . Under these conditions, the energy bands are flat across the structure. A more typical case is that the Fermi levels of the gate and substrate are misaligned by an energy difference and a voltage  $V_{FB}$ , the flatband voltage, must be applied to bring the Fermi levels into alignment. Many dielectrics, including  $SiO_2$ , exhibit a fixed charge in the oxide,  $Q_F$ , however, resulting in a required  $V = V_{FB} \neq 0$  to achieve a flat band condition.

# 3.3 The MOS System under Bias Voltage

Under a bias voltage the MOS structure acts as a nonlinear capacitor, i.e. the capacitance varies with the applied voltage. There are three basic regimes of operation: accumulation, depletion and inversion. An MOS structure on p-type silicon (Figure 3.2 (b)) will be used to illustrate the different regimes.

Figure 3.3 A p-type MOS system under bias: (a) accumulation mode (V < 0V), (b).depletion mode and (c) inversion mode (V > 0V).

When a bias voltage V < 0 V is applied to the gate, holes will be attracted to the interface between the gate dielectric and the substrate. The conduction and valence bands bend upwards (Figure 3.3(a)) and since the majority carrier density (holes) depends exponentially on the energy difference  $E_F - E_v$ , holes will accumulate at the substrate side of the gate dielectric. This is the "accumulation" mode. In this case, the gate dielectric acts as a straightforward parallel plate capacitor whose capacitance is fully determined by the gate dielectric.

$$C = \frac{\varepsilon \cdot A}{t_{ox}}$$

(Equation 3.3)

Upon increasing the bias voltage – making it less negative at first, then slightly positive – the energy bands will start bending downwards (Figure 3.3(b)). This effectively increases the energy difference  $E_F - E_v$ , causing the substrate region immediately adjacent to the gate dielectric to be depleted of majority carriers. Hence the term "depletion mode". Further increases in applied voltage will increase the width of the depletion region. In this mode the gate dielectric no longer acts as a parallel plate capacitor. Rather, the capacitance decreases with voltage as a result of an increasing width of the depletion region. The capacitance of the MOS structure reaches its minimum at a voltage at which maximum depletion is reached.

Further increases to larger positive gate voltages will bend the bands even further (Figure 3.3(c)), so that the Fermi level will cross over the intrinsic level E<sub>i</sub>. At this point, the minority carriers (electrons) in the region immediately next to the gate dielectric will outnumber the majority carriers and the surface will become inverted. Hence the term "inversion mode". The minority carriers appear at the surface by ways of a thermal generation process that is time dependent. It is in this regime that the frequency

dependence of the MOS capacitance primarily occurs since a certain time is needed to generate the minority carriers in the inversion layer. Thermal equilibrium is therefore not immediately obtained.

If the frequency of the AC signal with which the capacitance is measured, is low enough, the minority carriers will be able to respond to the changing gate bias. As a result, the inversion layer will be built up and the measured capacitance is equal to the capacitance of the oxide. On the other hand, if the frequency of the AC signal is high, the minority carriers will not be able to respond and the inversion layer will not build up. Consequently, the measured capacitance will remain at the minimum value it achieved in depletion mode. The voltage dependence of the capacitance of a p-type MOS structure as described here, is shown in Fig. 3.4. Obviously, a similar behavior will be obtained for an n-type MOS structure, with a C-V curve that is a mirrored curve of the one shown below.

Figure 3.4 Typical frequency dependence of C-V characteristics for a p-type MOS structure.

# 3.4 Leakage Compensated Capacitance Measurement

The capacitance characteristics for MOS structures as described in the previous section are valid as long as the oxide is relatively thick, > 3.5 nm. However, as CMOS technologies have evolved to include gate dielectrics that extend into the ultrathin regime, < 3.5 nm, a significant direct tunneling current severely distorts the C-V characteristics of the device, as will become clear from the next two figures. As can be seen in Figure 3.5, the direct tunnel current through a  $6.25 \times 10^{-4}$  cm<sup>2</sup>, 3.5 nm thick oxide reaches 10 pA at 1.5 V, a bias voltage where capacitance would be measured for the purpose of characterization. In a 2.4 nm oxide of the same area, the leakage is more than five orders of magnitude higher.

Figure 3.5 Leakage current through a 2.4nm and 3.5 nm ultrathin oxide.

Figure 3.6 demonstrates the effect that this direct tunnel leakage has on the capacitance characteristics. The graph shows the quasistatic C-V curve of a  $6.25 \times 10^{-4}$  cm<sup>2</sup>, 3.5 nm thick oxide measured at the relatively fast sweep rate of 50 mV/s, i.e. the same device whose I-V characteristics are represented by the open bullets in the previous figure. It is apparent that even a leakage current of several pA severely distorts the C-V characteristics. It is obvious that the significantly higher leakage current of the 2.4 nm oxide, as shown in the previous figure, will lead to an even greater distortion, making C-V characterization of such oxides all but impossible.

Figure 3.6 Severely distorted Low Frequency C-V curve of a 3.5 nm oxide due to leakage current.

This problem can be overcome by using a new measurement method that makes use of electronic circuitry to compensate for the leakage current. As will become clear from the rest of this chapter, this measurement method produces true static C-V curves, even for oxides as thin as the ones that have been discussed above.

The principle of a leakage compensated charge measurement is illustrated in Figure 3.7. A small amplitude square wave signal  $V_g(t)$  is applied across a MOS capacitor at DC bias level  $V_G$ . The total device current contains both a displacement current component responding to the square wave and a DC tunnel leakage current component. The device current is integrated, with the DC component being eliminated using a feedback leakage compensation scheme. The output of the circuit  $V_0$  is thus a transient charge response waveform, Q(t) generated by the applied small excitation signal. If the response waveform is allowed to saturate, then the amplitude of the waveform at a given bias is proportional to the static device capacitance, that is  $C(V) = Q_{max}(V)/V_g$ , where  $V_g$  is the amplitude of the excitation square wave and  $Q_{max}$  is the maximum or saturation value of the transient charge response curve. Therefore, a C-V curve is obtained by measuring  $Q_{max}$  as a function of a varying bias voltage that sweeps the MOS structure from accumulation, through depletion into inversion, or vice versa.

Figure 3.7 Principle of a Leakage Compensated Charge Measurement.

# 3.5 Experimental Details

To fabricate the devices used in this work, active SiO<sub>2</sub> tunnel oxides of thickness 2.4, 2.8 and 3.5 nm are formed at 700 °C in dry O<sub>2</sub> in windows opened in a field oxide grown on <100> oriented, 0.005-0.05 ohm-cm, n-type silicon wafers. The active oxide is then immediately covered by depositing polycrystalline silicon, which is phosphorous doped approximately to degeneracy. Devices exhibit current-voltage (I-V) characteristics which scale well both with device area and oxide thickness. Experimental data were acquired using a standard personal computer that was equipped with a National Instruments AT-MIO-16E-10 analog-digital/digital-analog converter board. LabVIEW was used to develop fully automated measurement procedures. In particular, LabVIEW-based programs were developed for the generation of the analog excitation signal and the

acquisition of the digital response waveform. The test devices were mounted in a HP16055A test box. High frequency C-V curves were measured using a HP4285 LCR meter.

# 3.6 Experimental Results

## 3.6.1 LCCV on a 3.5 nm Oxide

This first section will discuss the results of a leakage compensated charge measurement on an MOS structure with a 3.5 nm oxide. Figure 3.8 illustrates the transient waveforms Q(t) in response to a 50 mV square waveform with a frequency of 1 Hz. As is clear from the figure, the shape and amplitude of the output waveform vary with  $V_G$ , for example displaying a slow rise time in inversion where the minority carrier response time is long, and conversely a fast rise time in accumulation where majority carriers can easily follow the applied square wave signal. It must also be pointed out that the saturation of minority carrier response is easily obtained as can be seen from the flatness at the end of each section of the charge waveform. This assures that the measured curve is a static C-V curve, instead of "quasistatic" as in the conventional approach.

Figure 3.8 Transient waveforms Q(t) in accumulation and inversion for a 50mV, 1 Hz excitation signal on a 3.5nm oxide.

Figure 3.9 is a 3-D graph of these transient waveforms Q(t) as a function of applied bias voltage  $V_G$ , with the "front axis" being  $V_G$  and the second planar axis being time. The transient waveforms Q(t) are represented by the dashed curves. The "right" part of the graph depicts the device in accumulation as can be seen from the square wave transient responses. The "left" part depicts the device in inversion as can be seen from the slow rise time of the waveform. It is clear that the amplitude of the waveform in the center of the graph is significantly smaller than that in accumulation or inversion. This is expected since this part of the graph corresponds to the depletion regime of the device. As explained in the previous section, the amplitude of the waveforms is proportional to the capacitance (the vertical axis). Against the backwall of the graph these amplitudes

are traced out for each bias voltage (the solid curve). This curve, therefore, traces out the static C-V curve of the device.

Figure 3.9 3-D graph of transient waveforms Q(t) as a function of bias voltage V<sub>G</sub>.

The C-V curve displays the expected static characteristics. In accumulation and inversion, the capacitance saturates at a value that is typically the oxide capacitance, but can also include quantum effects due to the finite width of the inversion layer as well as polycrystalline silicon depletion when the substrate is in accumulation. As expected, the

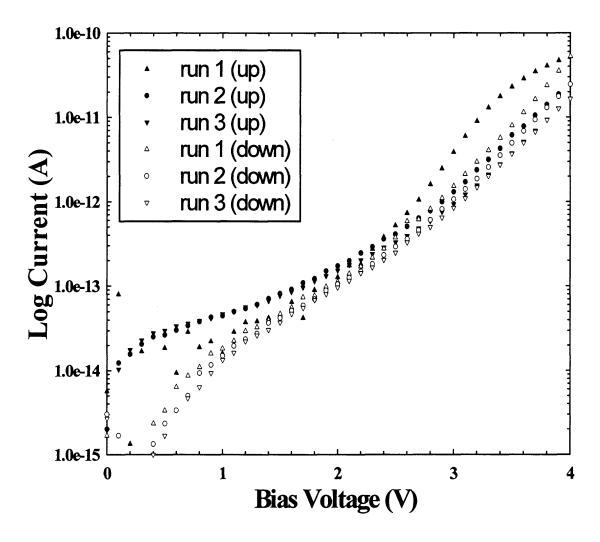

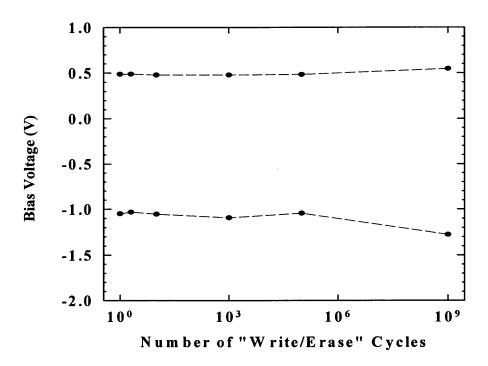

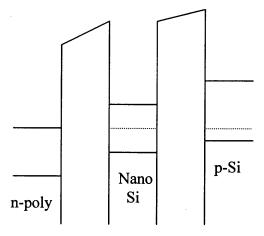

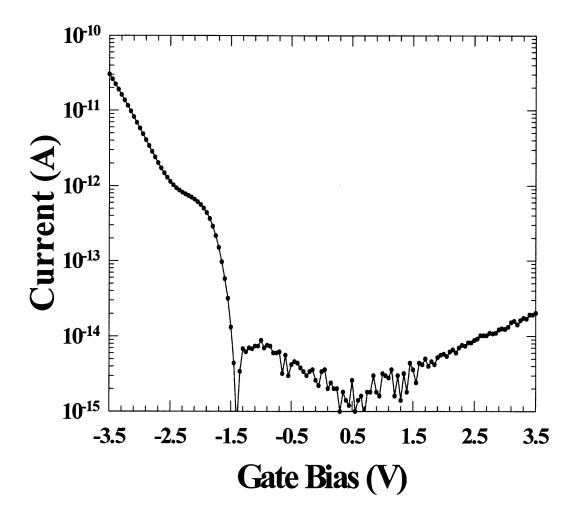

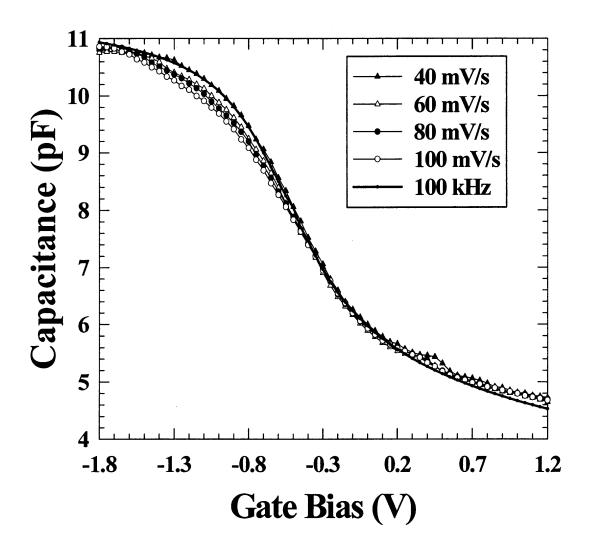

capacitance goes through a minimum when the silicon is swept through depletion. It is quite remarkable that this C-V curve can be obtained despite the presence of a large leakage current.