# **Copyright Warning & Restrictions**

The copyright law of the United States (Title 17, United States Code) governs the making of photocopies or other reproductions of copyrighted material.

Under certain conditions specified in the law, libraries and archives are authorized to furnish a photocopy or other reproduction. One of these specified conditions is that the photocopy or reproduction is not to be "used for any purpose other than private study, scholarship, or research." If a, user makes a request for, or later uses, a photocopy or reproduction for purposes in excess of "fair use" that user may be liable for copyright infringement,

This institution reserves the right to refuse to accept a copying order if, in its judgment, fulfillment of the order would involve violation of copyright law.

Please Note: The author retains the copyright while the New Jersey Institute of Technology reserves the right to distribute this thesis or dissertation

Printing note: If you do not wish to print this page, then select "Pages from: first page # to: last page #" on the print dialog screen

The Van Houten library has removed some of the personal information and all signatures from the approval page and biographical sketches of theses and dissertations in order to protect the identity of NJIT graduates and faculty.

#### ABSTRACT

### SPARSE MATRIX PRODUCT IMPLEMENTATION ON FIELD PROGRAMMABLE GATE ARRAYS (FPGAS)

#### by Amit Mahendra Sheth

If dense matrix multiplication algorithms are used with sparse matrices, they can result in a large number of redundant calculations, as numerous elements in sparse matrices are zero valued, thus available resources and time may be wasted. The algorithm discussed here aims to take advantage of the sparseness of the matrices by multiplying only nonzero elements.

The NIOS development board from Altera is used for implementing the above algorithm. First a sequential program in the C programming language is downloaded onto the FPGA and run by the NIOS soft-processor. Then the same board is also used for a parallel implementation of the above algorithm using three NIOS soft-processors within the same FPGA.

Such an approach is very critical because current FPGAs do not contain enough resources to solve large problems. For example, we cannot build large memory systems within FPGAs so we need to employ algorithms that have rather limited memory requirements. Our proposed matrix multiplication algorithm for sparse matrices uses the available memory space very cautiously and also results in good execution times. Performance results testify to this fact.

### SPARSE MATRIX PRODUCT IMPLEMENTATION ON FIELD PROGRAMMABLE GATE ARRAYS (FPGAS)

by Amit Mahendra Sheth

A Thesis Submitted to the Faculty of New Jersey Institute of Technology in Partial Fulfillment of the Requirements for the Degree of Master of Science in Electrical Engineering

**Department of Electrical and Computer Engineering**

May 2003

$\langle$

### **APPROVAL PAGE**

## SPARSE MATRIX PRODUCT IMPLEMENTATION ON FIELD PROGRAMMABLE GATE ARRAYS (FPGAS)

### Amit Mahendra Sheth

Ďate

Dr. Sotirios Ziavras, Thesis Advisor

| Professor of Electrical and Computer Engineering, and<br>Computer and Information Science, Associate Chair for Graduate Studies, NJI                                           | (T   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Dr. Vishwani D. Agrawal, Phesis Co-advisor<br>Visiting Professor of Electrical and Computer Engineering, and<br>Center for Advanced Information Processing, Rutgers University | Date |

| Dr. John D. Carpińelli, Committee Member<br>Associate Professor of Electrical and Computer Engineering, and<br>Computer and Information Science, NJIT                          | Date |

| Dr. Roberto Rojas-Cessa, Committee Member<br>Associate Professor of Electrical and Computer Engineering, NJIT                                                                  | Date |

### **BIOGRAPHICAL SKETCH**

Author: Amit Mahendra Sheth

Degree: Master of Science

Date: May 2003

### **Undergraduate and Graduate Education:**

- Master of Science in Electrical Engineering, New Jersey Institute of Technology, Newark, NJ, 2003

- Bachelor of Engineering in Electronics, Father Conceicao Rodrigues College of Engineering, Mumbai, India, 2001

- Diploma in Digital Electronics Bombay Institute of Technology, Mumbai, India, 1998

Major: Electrical Engineering

### **Presentations and Publications:**

Amit M. Sheth and Jacob Savir

"Single Clock, Single Latch, Scan Design,"

The IEEE Instrumentation and Measurement Technology Conference (IMTC/02), Anchorage, Alaska, USA, May 2002.

### Scholarships and awards:

- Research assistantship for 3 semesters under Dr. Sotirios G. Ziavras, Department of Electrical and Computer Engineering, N.J.I.T. (Newark), USA, for the Power Grid Project.

- Research Assistantship under Dr. S. S. S. P. Rao, Department of Computer Science and Engineering, I.I.T. (Bombay), India, for Vikram Sarabhai Space Center project

- Travel Grant for presenting a research paper titled "Single Clock Single Latch Scan Design", IEEE-IMTC-02, Anchorage, AK, USA, May 2002

To my beloved family, friends and teachers

#### ACKNOWLEDGMENT

I would like to express my deepest appreciation to my advisor, Dr. Sotirios G. Ziavras for his valuable guidance and support throughout the research work. Without his timely and valuable suggestions, it would not have been possible to accomplish the work that I have done which to me has been a very satisfactory experience.

My deepest gratitude to Prof. Jacob Savir who was the catalyst for me to work on this project and provided me with a wonderful opportunity to become involved with this highly prestigious project.

I also would like to express my sincere thanks to my co-advisor, Dr. Vishwani D. Agrawal, who despite his busy schedule took time out to provide me with valuable guidance and suggestions which proved very helpful.

I also appreciate the efforts and suggestions of the committee members, Dr. John Carpinelli and Dr. Roberto Rojas-Cessa. I would like to thank them too.

I thank the distinguished faculty of the ECE department who have been excellent guides throughout my graduate study and have provided me with the skills and expertise to be a successful professional in my field of study in future.

And last but not the least, I take this opportunity to thank my Family and also my dear friends for their unflinching support and encouragement throughout my Graduate study and who have been a great source of inspiration for me at every step of my academic career. I shall remain indebted to them for this and my success would not have been possible without their ceaseless efforts.

| Chapter | I                                                | Page |

|---------|--------------------------------------------------|------|

| 1       | INTRODUCTION                                     | 1    |

|         | 1.1 Matrix Multiplication                        | 1    |

|         | 1.2 Why FPGAs over Traditional Computers         | 2    |

|         | 1.3 Motivation and Objectives                    | 3    |

| 2       | MATRIX MULTIPLICATION ON FPGAs                   | 5    |

|         | 2.1 SOPC Board                                   | 5    |

|         | 2.2 Algorithm                                    | 8    |

|         | 2.3 Parallel Implementation                      | 12   |

|         | 2.4 System Development                           | 15   |

| 3       | PERFORMANCE RESULTS                              | 27   |

|         | 3.1 Sequential Implementation Results            | 27   |

|         | 3.2 Parallel Implementation Results              | 30   |

| 4       | CONCLUSIONS                                      | 34   |

| APPE    | NDIX A Source Code For Sequential Implementation | 35   |

| APPE    | NDIX B Source Code For Parallel Implementation   | 41   |

### **TABLE OF CONTENTS**

### LIST OF TABLES

| Table | Page                                                                 |

|-------|----------------------------------------------------------------------|

| 3.1   | Performance Results for Sequential Implementation (8 X 8 matrices)27 |

| 3.2   | Performance Results for Parallel Implementation                      |

| Figur | es                                               | Page |

|-------|--------------------------------------------------|------|

| 1.1   | Inner product of row and column vectors          | 1    |

| 1.2   | Matrix multiplication example                    | 2    |

| 1.3   | Sparse matrix                                    | 3    |

| 1.4   | Sparse matrix                                    | 3    |

| 2.1   | SOPC Board                                       | 6    |

| 2.2   | Flowchart of our matrix multiplication algorithm | 10   |

| 2.3   | Flowchart (continued)                            | 11   |

| 2.4   | Parallel architecture                            | 12   |

| 2.5   | Parallel architecture interconnections           | 15   |

| 2.6   | NIOS processor CPU architecture                  | 16   |

| 2.7   | NIOS processor hardware configuration            | 17   |

| 2.8   | NIOS processor software configuration            | 18   |

| 2.9   | NIOS processor local RAM                         | 19   |

| 2.10  | Global RAM                                       | 20   |

| 2.11  | Boot ROM configuration                           | 21   |

| 2.12  | GERMS monitor                                    | 21   |

| 2.13  | UART configuration                               | 22   |

| 2.14  | Hardware timer configuration                     | 23   |

| 2.15  | Priorities                                       | 24   |

| 2.16  | Programmer                                       | 25   |

### **LIST OF FIGURES**

# Figures

# Page

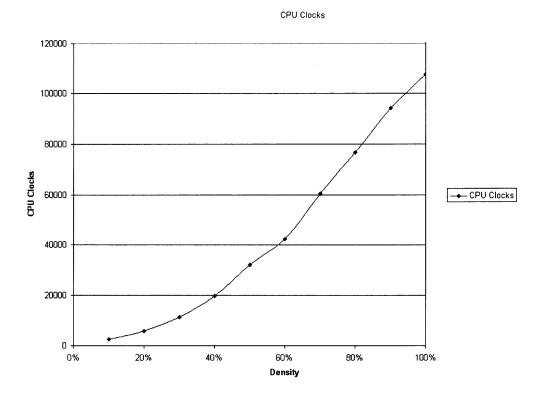

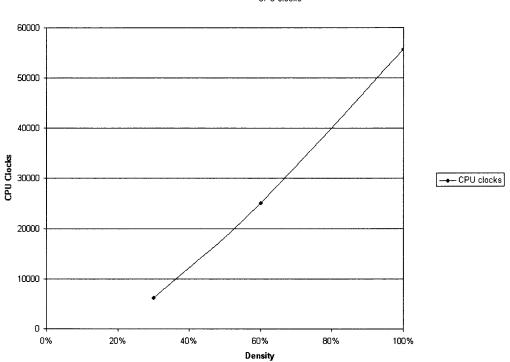

| 3.1 | Graph of CPU clock cycles versus matrix density                               |

|-----|-------------------------------------------------------------------------------|

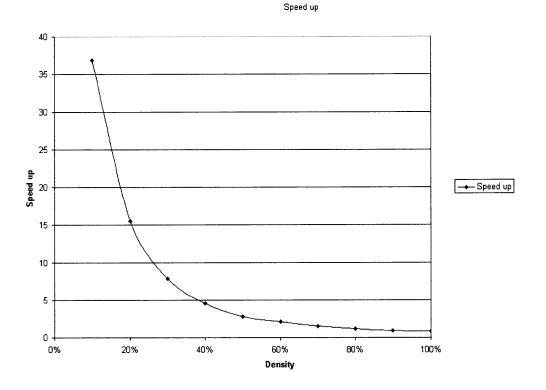

| 3.2 | Graph of speed up versus matrix density compared to the conventional matrix   |

|     | multiplication algorithm29                                                    |

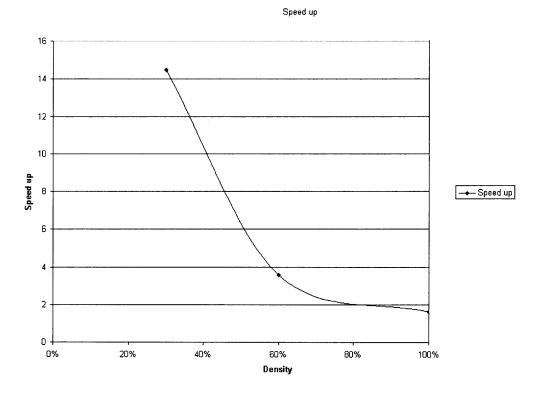

| 3.3 | Graph of CPU clock cycles versus matrix density for parallel implementation31 |

| 3.4 | Graph of speed up versus matrix density for parallel implementation           |

#### CHAPTER 1

#### **INTRODUCTION**

#### **1.1 Matrix Multiplication**

Matrix multiplication is a very useful operation in mathematics. It involves innervector product implementations. Let us now see how we multiply a row vector with a column vector of the same length - that is, with the same number of entries. The result is a number (which can be viewed as a 1x1 vector if one insists that the product of two vectors must be a vector).

#### Step 1: Row vector times column vector

$$\begin{bmatrix} 1 & 2 & 3 & 4 \\ 5 & 6 \\ 7 & 8 \end{bmatrix} = (1 \times 5) + (2 \times 6) + (3 \times 7) + (4 \times 8) = 70$$

Figure 1.1 Inner product of row and column vectors

In this example, the row and the column both have length 4, but the same pattern obviously works whenever they are of the same length; just multiply the corresponding entries and sum up the products.

#### **Step 2: The General Case**

Assume now two general matrices, say A and B. The matrix product C=A\*B is formed by multiplying every row of A with every column of B, in the way described in Step 1 above. Assume n\*n matrices, for the sake of simplicity. The elements  $C_{ij}$  of matrix C is calculated as

$$C_{ij} = \sum_{k=1}^{n} a_{ik} * b_{kj}$$

where  $1 \le i, j \le n$ .

The time required for this matrix multiplication is  $O(n^3)$

$$\left(\begin{array}{cccc}1&2&3&4\\5&6&7&8\end{array}\right)\left(\begin{array}{cccc}1&2&3\\4&5&6\\7&8&9\\10&11&12\end{array}\right) == \left(\begin{array}{cccc}70&80&90\\158&184&210\end{array}\right)$$

#### **Figure 1.2 Matrix multiplication example**

#### **1.2 Why FPGAs Over Traditional Computers?**

Large matrices (e.g. of the order of 1000 X 1000 and higher) are traditionally solved by large super-computers such as CRAY. Workstations have also been used to solve the above problem by, first improving the algorithm, such as for Strassen's algorithm [6] that has a time complexity of O ( $n^{2.376}$ ).

FPGAs are primarily used in application development because:

- 1) They can be configured as and when required by the application.

- They are reprogrammable and can be conditioned to give hardware acceleration by offering the best of both software and hardware.

- 3) They are also becoming relatively inexpensive, at less than \$20 per million gates.

#### **1.3 Motivation and Objectives**

To multiply two 3000 X 3000 matrices using the conventional method requires on the order of O ( $n^3$ ),  $3000^3 = 27,000,000,000$  floating-point multiplications and additions.

#### **Sparse Matrices:**

#### Figure 1.3 Sparse matrix

**Figure 1.4 Sparse matrix**

Figures 1.3 and 1.4 show examples of sparse matrices. As we can see, most of the elements in the above matrices are zero-valued. In other words, the above matrices are sparse in nature. This implies that most of the multiplications would result in zeroes and hence are redundant. These redundant calculations can be avoided by using an algorithm in which only the required elements are multiplied.

If sparse matrices are stored as regular matrices in two dimensional arrays, they will consume a lot of space in memory. Various formats are used to store sparse matrices; among them, which a popular one is the matrix market file format [4] which only stores the non-zero elements along with their row and column indices.

A sample file saved in the matrix market format is shown below:

| 5 | 5 | 8       |

|---|---|---------|

| 1 | 1 | 4.7e12  |

| 2 | 2 | 3.5e-11 |

| 3 | 2 | 3.9e14  |

| 2 | 3 | 6.2e21  |

| 3 | 3 | 2.7e-05 |

| 4 | 3 | 1.3e-1  |

| 4 | 4 | 7.5e18  |

| 5 | 5 | 4.9e14  |

The first line specifies the maximum number of rows, columns and the total number of non-zero elements, respectively. From the next line onwards, the first column specifies the row index, the second column specifies the column index and the third column specifies the corresponding value of the matrix element.

#### CHAPTER 2

#### MATRIX MULTIPLICATION ON FPGAs

#### 2.1 SOPC Board [5]

We have used an Altera board which serves as a development and prototyping platform that provides system designers with an economical solution for hardware verification. The system-on-a-programmable chipboard supports a variety of microprocessor-based designs incorporating memory, debugging, and interface resources. The development board is primarily designed for implementing microprocessor functions and other standard IP (Intellectual Property) functions in the on-board APEX FPGA device. The board includes physical interfaces for widely used standard interconnects. Control logic for the interconnects can be implemented in the device. Some of the available IP solutions include:

- Processor cores (MIPS, RISC, and Harvard architectures).

- Peripheral and I/O cores (PCI, SDRAM controllers, UART, USB, Ethernet, IEEE1394, IEEE 1284).

- Other cores developed by Altera and other Altera Mega function Partners.

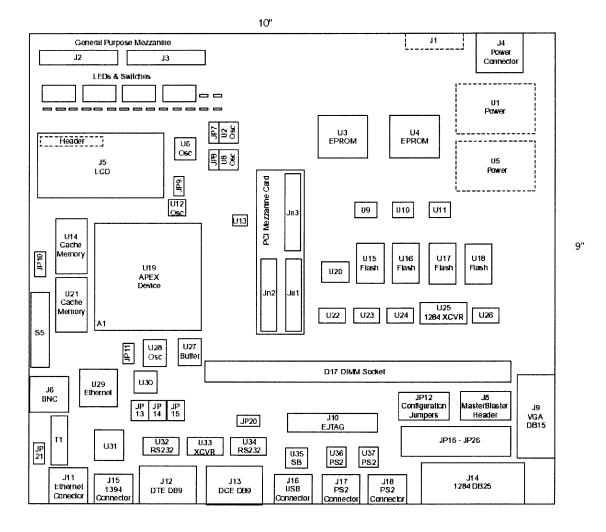

The board also supports EJTAG for development and debugging of MIPS-like microprocessor functions, as well as JTAG for system testing. For additional analysis, the JTAG port can be used with the Signal Tap embedded logic analyzer available with the Quartus® II development software. Figure 2.1 shows a layout diagram of the development board.

Figure 2.1 SOPC Board [5]

#### **APEX Device**

The on-board APEX EP20K1500E device features 1,500,000 ASIC-equivalent gates in a 652-pin BGA package. The device has 51,840 logic elements (LEs) and 442,368 RAM bits.

#### Clocks

The board supports up to six unique clocks that can be selected by the designer. The board has two BNC connectors to support communications systems designs. The APEX global clock input is driven by a 66-MHz oscillator or by an external clock via a BNC

connector. The second global clock signal is connected to an oscillator that can drive a PCI function at either 33 or 66 MHz.

### Memory

To support processor functions implemented in the APEX device, the board includes a memory system consisting of the following:

- Volatile memory: 64 Mbytes of synchronous DRAM, organized as 8 Mbytes X 64 Mbytes.

- Non-volatile memory: 4 Mbytes of Flash memory and a 256-Kbyte EPROM memory.

- Pipelined cache memory with burst SRAM organized as 256 Kbytes X 32 Kbytes.

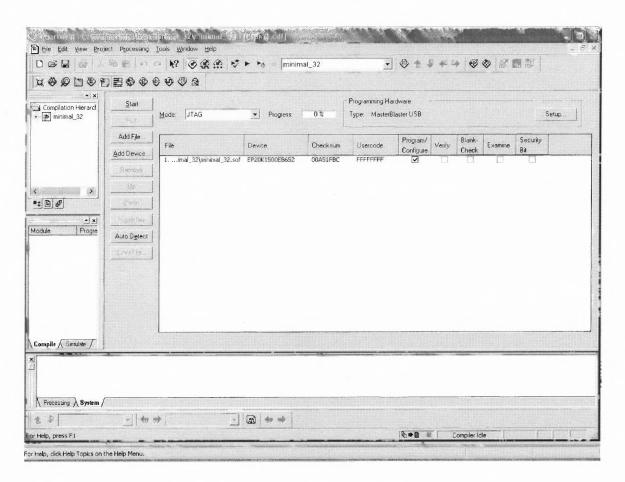

### **Programming the APEX Device**

The EP20K1500E board cannot store configuration data for the APEX device; you must configure the device directly via the JTAG interface. You can program the APEX device directly using the Quartus software version 2000.02 and higher, any version of the Quartus II software[9], or the MAX+PLUS® II software version 9.5[9] and higher using either the MasterBlaster<sup>TM</sup> or ByteBlasterMV<sup>TM</sup> cable.

### 2.2 Matrix Multiplication Algorithm

The algorithm comprises three main parts:

- 1) Pre-conditioning

- 2) Main program

- 3) Post conditioning

Assume that matrix A has m rows and n columns, and matrix B has prows and q columns. [Note that n must equal p.]

Then each of the above parts is as explained below:

### 1) Pre-conditioning:

- a) This involves sorting matrix A in column order and matrix B in row order.

- b) Matrices in the matrix market format for sparse matrices are already sorted in the column order. So matrix A need not be sorted.

- c) Matrix B, however, needs to be sorted in row order.

- d) The Quick sort algorithm is used to sort matrix B in column order..

### 2) Main program:

- a) The inputs are two matrices in the matrix market format for sparse matrices.

- b) The resultant matrix is obtained as a two dimensional array with m rows and q columns.

The idea is as explained in brief:

a) For a particular element in the A matrix in column 'i', all the elements of the B matrix in row 'i' are multiplied and stored in the result matrix C.

b) The above step is repeated for all the non-zero elements in matrix A.However, in subsequent iterations the result of the multiplication is added to the previous result for the corresponding element in the C matrix.

### 3) Post processing:

The resultant matrix C is represented as a two dimensional array. It may be required to have the resultant matrix in the matrix market format, in which case some post processing will be required.

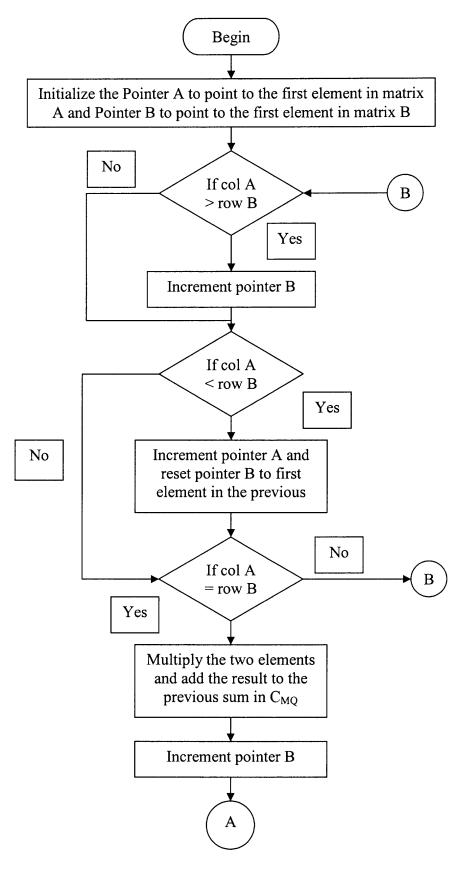

Figure 2.2 shows a flowchart for this algorithm.

Figure 2.2 Flowchart of our matrix multiplication algorithm

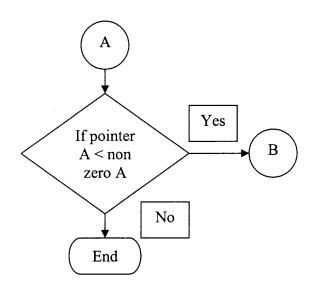

Figure 2.3 Flowchart (continued)

#### **2.3 Parallel Implementation**

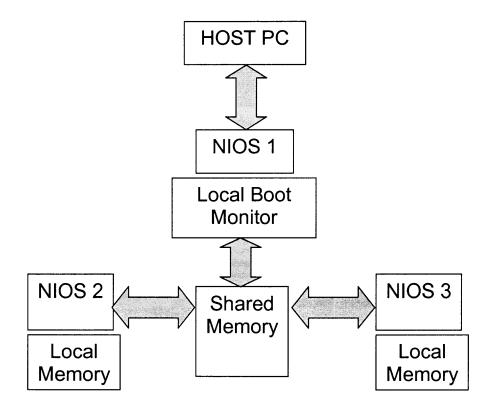

A parallel architecture[7] [8] has been designed for the implementation of the matrix multiplication algorithm described earlier. A block diagram is shown in figure 2.4.

**Figure 2.4 Parallel architecture**

More details of the architecture follow:

- The above architecture contains three NIOS soft processors. The restriction on a maximum of three processors is mainly due to the size of the FPGA on the current development board.

- 2) The NIOS 1 processor contains the Boot ROM and is also connected to the UART for communication with the host PC. It is used to download programs as well as data from the host PC into its own internal memory as well as that of the of the other two processors. It also takes part in the matrix multiplication process.

- 3) The NIOS 2 and NIOS 3 processors only take part in the matrix multiplication process. These processors have their own local memory (on chip) and they also share a common global on-chip memory (which is the referred to as the Global RAM).

- 4) These processors get information from NIOS 1 processor regarding the location of the program to be run and data to be operated on. This information is passed using semaphores.

- 5) In the current implementation, the matrix multiplication program along with the data is first downloaded in to the NIOS 2 and NIOS 3 processor's internal memories.

- 6) Using the external reset switch both the processors (NIOS 2 and NIOS 3) are reset to their starting address from which they start running the downloaded program. This program waits in an infinite loop until the main controlling program is downloaded into internal memory of NIOS 1 processor.

- 7) Once the program is downloaded, the NIOS 1 processor starts running the program. This program initializes the hardware timer and sets a flag which brings NIOS 2 and NIOS 3 out of their wait loops; then they both start operating on their respective elements of the matrix.

- 8) The NIOS 1 processor also starts multiplying matrix elements assigned to it. The assignment of elements to be multiplied by each NIOS processor is done on the host PC.

- Each sub-program generates its own output matrix in a separate area in its own local memory, so there are no write conflicts.

- 10) Each NIOS processor sets a flag when they have finished generating their output.The NIOS 1 processor checks for these flags after it has completed generating its own output.

- 11) Once all the output sub-matrices are generated, the main program combines them all to obtain the final resultant matrix. The main program also uses the hardware timer to time the entire operation.

- 12) The above architecture has been successfully implemented and tested for small matrices. We are still in the process of running matrix multiplication on large matrices.

#### **2.4 System Development**

The Quartus II<sup>®</sup> version 2.0 software from Altera<sup>®</sup> [9] was used for hardware design. An already existing minimal configuration file provided by Altera among a set of sample files was used as the starting point for our project; the remaining modules were added to it.

| Avalon Modules                                                                                                                                          |                               |                                                                                                                                                                                                                                        | C                                    | stem Clock Frequency: 33.33 MHz |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|---------------------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|----------|

| Altera Nios 2.0 CPU                                                                                                                                     |                               |                                                                                                                                                                                                                                        |                                      |                                 |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |          |

| <ul> <li>Interface to User Logic</li> </ul>                                                                                                             |                               |                                                                                                                                                                                                                                        | master (avalon)                      |                                 |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |          |

| Bridges  cput / deta_master (avaion)  cput / deta_master (avaion)                                                                                       |                               |                                                                                                                                                                                                                                        |                                      |                                 |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |          |

| Avalon Tri-State Bridge                                                                                                                                 | - cnul) (data martar (avalon) |                                                                                                                                                                                                                                        |                                      |                                 |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |          |

| <ul> <li>O PLD Applications Nios-PCI</li> </ul>                                                                                                         |                               |                                                                                                                                                                                                                                        | - cpu3 / instruction_master (avalon) |                                 |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |          |

| - Communication                                                                                                                                         |                               |                                                                                                                                                                                                                                        | - cpu3 / data_master (avalon)        |                                 |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |          |

| <ul> <li>SPI (3 Wire Serial)</li> <li>UART (RS-232 serial port)</li> </ul>                                                                              | Use                           |                                                                                                                                                                                                                                        | Module Name                          | Description                     | Bus Type | Base                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | End          | IR       |

| O M16550S Enhanced UART                                                                                                                                 | USC                           |                                                                                                                                                                                                                                        |                                      | On-Chip Memory (RAM or ROM)     | avaion   | ▲ 0×000100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0x000133FF   | a marine |

| O CAN 2.0 Network Controlle                                                                                                                             | H-                            |                                                                                                                                                                                                                                        | → → iocal_ram1                       | On-Chip Memory (RAM or ROM)     | avalon   | 0x00000000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0x000027FF   | 1        |

| - Memory                                                                                                                                                | -                             |                                                                                                                                                                                                                                        |                                      | UART (RS-232 serial port)       | avalon   | 0x00000000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0x0000D01F   | 21       |

| On-Chip Memory (RAM or I                                                                                                                                | angusen -                     |                                                                                                                                                                                                                                        | E cpu1                               | Altera Nios 2.0 CPU             | avalon   | Section and the section of the secti | 1. 1. Carlos | 1        |

| SDRAM Controller                                                                                                                                        | 7                             |                                                                                                                                                                                                                                        | ⊕ cpu2                               | Altera Nios 2.0 CPU             | avalon   | 1191216                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | all all all  | 1        |

| SSRAM (Micron MT58L25E                                                                                                                                  |                               |                                                                                                                                                                                                                                        |                                      | On-Chip Memory (RAM or ROM)     | avalon   | 0x00004000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0×000067FF   | 1        |

| - Slash Memory                                                                                                                                          | 17                            |                                                                                                                                                                                                                                        | ⊡ cpu3                               | Altera Nios 2.0 CPU             | avalon   | 12110112                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1111111111   | 1        |

| SRAM (one or two IDT71V)                                                                                                                                | 7-0                           |                                                                                                                                                                                                                                        |                                      | On-Chip Memory (RAM or ROM)     | avalon   | 0x0000C000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0x0000CFFF   | 1        |

| Other                                                                                                                                                   | 7                             | $\rightarrow \rightarrow $ | 🗕 🛨 clk_timer                        | Interval timer                  | avaion   | 0x00000020                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0x0000D03F   | 1        |

| - 🛛 DMA                                                                                                                                                 | 1-0                           | $\rightarrow \phi \rightarrow \phi$                                                                                                                                                                                                    | + tocal_ram3                         | On-Chip Memory (RAM or ROM)     | avalon   | 0x00008000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0×0000A7FF   | 1        |

| PCI O Altera PCI32 Nios Target M O Altera PCI32 Nios Target M O PLD Applications Nios-PCI USB O USB 1,1 Full Speed Functic O USB 2,0 High/Full Speed Fi |                               |                                                                                                                                                                                                                                        |                                      |                                 |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |          |

|                                                                                                                                                         |                               |                                                                                                                                                                                                                                        |                                      |                                 |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |          |

Figure 2.5 Parallel architecture interconnections

Figure 2.5 shows the interconnections for the 3-CPU configuration. It also shows the various modules included in the above system. Each of the modules is described below in more detail:

CPU: The above system contains three identical CPUs. Each one of the three CPUs comprises a NIOS soft-processor core whose architecture, hardware as well as software can be customized. Snapshots of the processor configuration are shown below:

| Altera Nios - cpu1     Architecture     Hardware Configuration | Software Configuration Custom Instructions |

|----------------------------------------------------------------|--------------------------------------------|

| Nios<br>Version 2.0                                            |                                            |

| Processor Architecture                                         |                                            |

| C Nios- <u>1</u> 6                                             |                                            |

| 16-bit ALU, registers, and da<br>16 k% addressing (maximum)    |                                            |

| Preset Configurations: Custom                                  |                                            |

| Frable ac                                                      | vanced configuration controls              |

| <ol> <li>~1950 LEs, ~4 ESBs</li> </ol>                         |                                            |

| Cancel                                                         | Prev Next > Finish                         |

Figure 2.6 NIOS processor CPU architecture

As seen above we have selected the 32-bit NIOS configuration. This includes a 32-bit Arithmetic and Logic Unit (ALU), registers and data bus. The addressing scheme used is also 32 bits.

The next snapshot in Figure 2.7 shows the hardware configuration setup of the above CPU. A discussion of the various parameters selected is as given below:

1. 128 registers in the register file are selected, which is the lowest available option. Other options available are 256 and 512. The lowest option is selected to save ESBs (Embedded System Blocks) which can then be used for the on-chip memory implementation.

| 4 Aftera Nios - cpul                                                                                               |                                                                          |

|--------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|

| Architecture Hardware Configuratio                                                                                 | □ Software Configuration   Custom Instructions                           |

| Preset Configurations:<br>Register Options<br>Register File Size 128 -                                             | Custom                                                                   |

| Multiplier                                                                                                         | Pipeline Optimization  More Stalls / Fewer LEs C Fewer Stalls / More LEs |

| Decoder Logic<br>Instruction Decoder Implemented As:<br>C ESBs (On-chip memory resource<br>C LEs (Logic resources) |                                                                          |

| 1) ~1950 LEs, ~4 ESBs                                                                                              |                                                                          |

| <u>C</u> ancel                                                                                                     | < Prev Next > Finish                                                     |

Figure 2.7 NIOS processor hardware configuration

- 2. A hardware multiplier is used primarily speed up operations compared to software solutions. This option consumes many LEs (Logic Elements); however, as the primary goal is to obtain good performance and multiplications constitute the major portion in our algorithm, some on-chip logic resources are sacrificed for better performance.

- 3. To compensate for the extra LEs used by the hardware multiplier, the "More stalls/ Fewer LEs" option is selected in the Pipeline Optimizations category.

| Altera Nos - cput.                                                                                                     | and the second | nen X                                 |