## **Copyright Warning & Restrictions**

The copyright law of the United States (Title 17, United States Code) governs the making of photocopies or other reproductions of copyrighted material.

Under certain conditions specified in the law, libraries and archives are authorized to furnish a photocopy or other reproduction. One of these specified conditions is that the photocopy or reproduction is not to be "used for any purpose other than private study, scholarship, or research." If a, user makes a request for, or later uses, a photocopy or reproduction for purposes in excess of "fair use" that user may be liable for copyright infringement,

This institution reserves the right to refuse to accept a copying order if, in its judgment, fulfillment of the order would involve violation of copyright law.

Please Note: The author retains the copyright while the New Jersey Institute of Technology reserves the right to distribute this thesis or dissertation

Printing note: If you do not wish to print this page, then select "Pages from: first page # to: last page #" on the print dialog screen

The Van Houten library has removed some of the personal information and all signatures from the approval page and biographical sketches of theses and dissertations in order to protect the identity of NJIT graduates and faculty.

#### ABSTRACT ·

## PLASMA INDUCED DAMAGE TO SI AND SIGE DEVICES AND MATERIALS

## by Wei Zhong

This thesis studied the plasma-induced damage to Si and strained Si<sub>1-x</sub>Ge<sub>x</sub>, and the resulting change in device characteristics. The energetic particles (ions, electrons and photons) in plasma reactor present a potentially hostile environment for processing VLSI devices. An inductively coupled plasma (ICP) reactor was used to study its damage effects to thin gate oxides. Electrical characterizations by C-V, ramped voltage breakdown (RVB) and deep-level transient spectroscopy (DLTS) measurement, and x-ray photoelectron spectroscopy (XPS) analysis were employed to investigate the damages to thin gate oxides and Si/SiO<sub>2</sub> interface. The shift of flat band voltage, the reduction of breakdown voltage and the creation of high interface trap density were found to be in good agreement with the creation of suboxidation states at Si/SiO<sub>2</sub> interface. It is observed that device damage is well associated with the reactor operating conditions. The major mechanism responsible for damage appeared to be high-energy electron charging which occurred when only the ICP power was activated, without any rf bias to the wafercarrying electrode. Energetic particle bombardment damage was dominant when the wafer-carrying electrode was biased and the damage was considerably higher for rf bias power grater than 35W.

The effect of plasma processing to the strained  $Si_{1-x}Ge_x$  layer of  $p^+$ - n diode has been investigated. The effect of  $SF_6$  plasma, used to etch an overlying Si film stopping at the strained  $Si_{1-x}Ge_x$  film, on the electrical properties of an underlying  $Si_{1-x}Ge_x/Si$  heterojunction device was studied. The changes of C-V and I-V characteristics, such as

higher depletion capacitance and lower diffusion current were attributed to ion bombardment and radiation-induced bonding change, such as creation of interface charges and recombination centers. The TEM analysis revealed the dislocation loops in  $Si/Si_{1-x}Ge_x$  /Si outside the aluminum contact region due to the ion bombardment stress. The  $O_2$  plasma ashing has moderate effect to  $Si_{1-x}Ge_x$  device when the device was protected by aluminum contact layer.

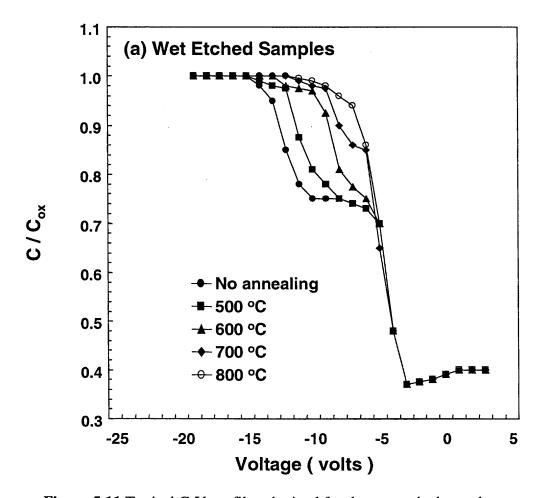

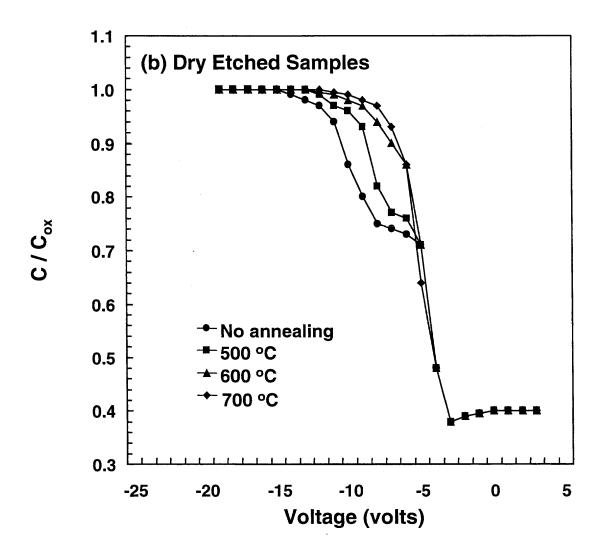

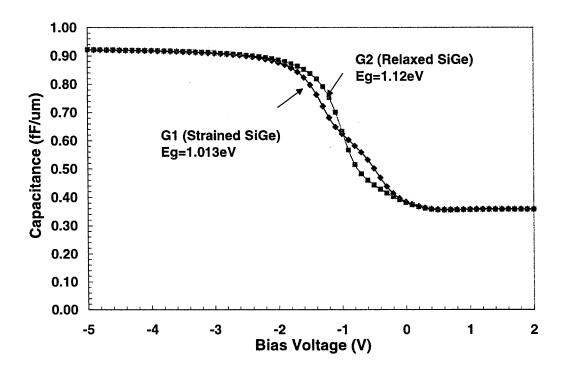

The C-V profiling techniques on SiGe MOS structures were used to investigate the change of valence band discontinuity ( $\Delta E_V$ ) at the Si/SiGe interface before and after plasma exposure and high temperature annealing. Wet and plasma etched samples were annealed at 500, 600, 700 and 800 °C for 60 seconds. It was observed that the accuracy of extracting the changes of  $\Delta E_V$  using the C-V profiling was strongly influenced by the release of electrons from the traps at SiO<sub>2</sub>/Si interface, which were created during the low-pressure CVD SiO<sub>2</sub> deposition. The device simulations have been used to confirm this finding. By carefully analyzing the C-V profile at slight depletion region the band gap modifications at back Si/SiGe interface due to process-induced damage could be evaluated. The dry etched sample was partially relaxed after 700 °C annealing while wet etched sample was partially relaxed after 800 °C annealing. Dry etched sample demonstrated a faster relaxation mechanism as compared to its wet etched counterpart due to the creation of dislocation loops by dry etching process. The C-V method is a simple, fast and efficient approach to estimate any band-gap modification in SiGe due to process-induced damage, but the measurements and simulations in slight depletion region should be carried out with special care and high resolution.

## PLASMA INDUCED DAMAGE TO Si AND SiGe DEVICES AND MATERIALS

by Wei Zhong

A Dissertation

Submitted to the Faculty of

New Jersey Institute of Technology

In Partial Fulfillment of the Requirements for the Degree of

Doctor of Philosophy in Electrical Engineering

Department of Electrical & Computer Engineering

May 2001

Copyright © 2001 by Wei Zhong

ALL RIGHTS RESEARVED

## APPROVAL PAGE

## PLASMA INDUCED DAMAGE TO SI AND SIGE DEVICES AND MATERIALS

## Wei Zhong

| Dr. D. Misra, Dissertation Advisor<br>Associate Professor of Electrical and Computer Engineering, NJIT | (Date) |

|--------------------------------------------------------------------------------------------------------|--------|

| Dr. M. Sosnowski, Committee Member Associate Professor of Electrical and Computer Engineering, NJIT    | (Date) |

| Dr. R. Cornely, Committee Monber Professor of Electrical and Computer Engineering, NJIT                | (Date) |

| Dr. K. Sohn, Committee Member<br>Professor of Electrical and Computer Engineering, NJIT                | (Date) |

| Dr. P. K. Swain, Committee Member Technology Leader, Sarnoff Corporation                               | (Date) |

#### **BIOGRAPHIC SKETCH**

Author: Wei Zhong

**Degree:** Doctor of Philosophy in Electrical Engineering

**Date:** May 2001

### **Undergraduate and Graduate Education:**

- Doctor of Philosophy in Electrical Engineering New Jersey Institute of Technology, Newark, NJ, 2001

- Master of Science in Electrical Engineering New Jersey Institute of Technology, Newark, NJ, 1992

- Bachelor of Science in Electronics Engineering Fudan University, Shanghai, P. R. China, 1985

Major: Electrical Engineering

#### **Presentations and Publications:**

- D. Misra, W. Zhong, B. Bartynski, V. Patel and B. Singh, "Etch Induced Damage in High Density Inductively Coupled Plasma Etching Reactor," Semiconductor Science and Technology, Vol. 11, No. 5, p. 816-821, May 1996.

- W. Zhong, D. Misra, B. Bartynski, V. Patel and B. Singh, "Etch Induced Damage in High Density Inductively Coupled Plasma Etching Reactor", Proceeding of the Tenth Symposium on Plasma Processing, G. S. Mathad and D. W. Hess, Editor, Electrochemical Society Proceeding, Vol. PV-94-20, p. 120-131, 1994.

- W. Zhong, D. Misra, J. Gaudani, M. W. Cole, T. P. Monaha and R. T. Lareau, "Electrical studies on SF<sub>6</sub> and O<sub>2</sub> plasma etched SiGe/Si p<sup>+</sup>-n heterojunction," Proceedings of the Symposium on the degradation of electronic device due to device operation as well as crystalline and process-induced defects, p. 149-156, 1994.

- W. Zhong, D. Misra, H. Amin, "Electrical studies on SF<sub>6</sub> and O<sub>2</sub> plasma etched SiGe/Si p<sup>+</sup>-n heterojunction,"

Electrochemical Society Interface, Vol. 2, No. 3, p. 122, 1993.

## W. Zhong and D. Misra,

"Reactive Ion Etching Damage to Strained SiGe Heterojunction Diode," *Proceedings of the 23<sup>rd</sup> European solid State Device Research Conference*, Grenoble, France, p321-324, September 13-16, 1993.

## W. Zhong, H. Amin, J. Gaudani and D. Misra,

"Damage to SiGe strained layers due to reactive ion etching," *The Microelectronic Processing '93*, SPIE Symposium Monterey, California, September 27-29, 1993.

This thesis is dedicated to my wife Hong, daughter Teresa and my parents Yikuang & Wenying.

## ACKNOWLEDGEMENT

First and foremost, thanks to Prof. D. Misra, who not only served as my research advisor, providing valuable and countless resources, insights, and intuitions, but also constantly gave me encouragement, supports and assurances.

Special thanks are due to Dr. M. Sosnowski, Dr. R. Cornely, Dr. P. K. Swain, Dr. K. Sohn for actively participating in my committee. Financial support from National Science Foundation (grant No. ECS-9207665) is acknowledged.

My wife, Hong, provided me continuous care, love and understanding. My daughter, Teresa, brought me everlasting smiles and joys.

Thanks to the Hashimoto Awards committee to select this research work for the Annual Hashimoto Award.

## TABLE OF CONTENTS

| Ch | apter   | ${f P}_{i}$                                                                                | age |

|----|---------|--------------------------------------------------------------------------------------------|-----|

| 1  | INTRODU | JCTION                                                                                     | 1   |

|    | 1.1     | Motivation                                                                                 | 1   |

|    | 1.2     | Objectives of the Research                                                                 | 3   |

|    | 1.3     | Thesis Organization                                                                        | 5   |

| 2  | PLASMA  | ETCHING PROCESS AND PLASMA DAMAGE                                                          | 7   |

|    | 2.1     | Basic Physical Phenomena in RF Discharges                                                  | 7   |

|    | 2.2     | General Description of Plasma Etch Tools                                                   | 12  |

|    | 2.3     | Plasma Induced Damage to Silicon Devices                                                   | 17  |

|    |         | 2.3.1 Plasma Damage to Si/SiO <sub>2</sub> System                                          | 17  |

|    | 2.4     | Plasma Damage to Si/Si <sub>1-x</sub> Ge <sub>x</sub> Heterojunction Systems               | 20  |

|    |         | 2.4.1 Si <sub>1-x</sub> Ge <sub>x</sub> Material and Devices                               | 20  |

|    |         | 2.4.2 Physical and Electrical Damage to Strained Si <sub>1-x</sub> Ge <sub>x</sub> Devices | 26  |

| 3  | EXPERIN | MENTAL TECHNIQUES                                                                          | 27  |

|    | 3.1     | Electrical Characterization                                                                | 27  |

|    |         | 3.1.1 I-V & C-V Measurements to Evaluate MOS System                                        | 27  |

|    | 3.2     | Deep Level Transient Spectroscopy (DLTS) Techniques                                        | 33  |

|    | 3.3     | Physical Characterization                                                                  | 41  |

|    |         | 3.3.1 Secondary Ion Mass Spectroscopy (SIMS)                                               | 41  |

|    |         | 3.3.2 X-Ray Photoelectron Spectroscopy (XPS)                                               | 42  |

|    |         | 3.3.3 Transmission Electron Microscopy (TEM)                                               | 44  |

|    | 3.4     | Simulation of Si <sub>1-x</sub> Ge <sub>x</sub> Device for Damage Estimation               | 46  |

|    |         | 3.4.1 Overview of Device Simulator                                                         | 46  |

# **TABLE OF CONTENTS** (Continued)

| CI | iapter |        | r                                                                                                      | age |

|----|--------|--------|--------------------------------------------------------------------------------------------------------|-----|

|    |        | 3.4.2  | Important Physics and Equations in SiGe MOS Simulation                                                 | 47  |

|    |        | 3.4.3  | Simulation of Si <sub>1-x</sub> Ge <sub>x</sub> MOS Capacitor                                          | 50  |

| 4  |        |        | D DAMAGE TO MOS DEVICE IN HIGH-DENSITY ICP                                                             | 55  |

|    | 4.1    | Introd | uction                                                                                                 | 55  |

|    | 4.2    | Experi | imental Details                                                                                        | 56  |

|    | 4.3    | Measu  | rement Results                                                                                         | 60  |

|    |        | 4.3.1  | C-V Measurements                                                                                       | 60  |

|    |        | 4.3.2  | Breakdown Measurements ·                                                                               | 64  |

|    |        | 4.3.3  | DLTS Analysis                                                                                          | 65  |

|    |        | 4.3.4  | XPS Characterization                                                                                   | 67  |

|    | 4.4    | Discu  | ssion of Results                                                                                       | 70  |

|    | 4.5    | Sumn   | nary                                                                                                   | 71  |

| 5  | PLASMA | INDU   | CED DAMAGE TO STRAINED Si <sub>1-x</sub> Ge <sub>x</sub>                                               | 72  |

|    | 5.1    |        | ical Studies on SF6 and O2 Plasma Etched Si <sub>1-x</sub> Ge <sub>x</sub> p <sup>+</sup> -n ojunction | 72  |

|    |        | 5.1.1  | Sample Preparation                                                                                     | 73  |

|    |        | 5.1.2  | Current-Voltage Measurements                                                                           | 76  |

|    |        | 5.1.3  | C-V Measurements                                                                                       | 77  |

|    |        | 5.1.4  | TEM Analysis                                                                                           | 77  |

|    |        | 5.1.5  | Effects of O <sub>2</sub> Plasma Ash Process                                                           | 78  |

# **TABLE OF CONTENTS** (Continued)

| Chapter   |       |                                                                                                                                 | Page  |

|-----------|-------|---------------------------------------------------------------------------------------------------------------------------------|-------|

|           | 5.1.6 | Summary                                                                                                                         | . 79  |

| 5.2       |       | ation of Plasma Process-Induced Bandgap Modification of ed Si <sub>1-x</sub> Ge <sub>x</sub> Heterojunction Using MOS Capacitor | 80    |

|           | 5.1.1 | Sample Preparation                                                                                                              | . 80  |

|           | 5.1.2 | C-V Measurements                                                                                                                | . 82  |

|           | 5.1.3 | Device Simulation                                                                                                               | . 84  |

|           | 5.1.4 | Discussion of Results                                                                                                           | . 95  |

|           | 5.1.5 | Summary                                                                                                                         | . 97  |

| 6 CONCLU  | SIONS |                                                                                                                                 | . 98  |

| 6.1       | Sugge | stions for Future Work                                                                                                          | . 100 |

| APPENDIX  | EXAN  | MPLE OF ATLAS INPUT FILE                                                                                                        | . 101 |

| REFERENCE | ES    |                                                                                                                                 | . 103 |

## LIST OF TABLES

| Table |                                             |    |

|-------|---------------------------------------------|----|

| 4.1   | A list of the various processing conditions | 57 |

| 5.1   | List of simulated SiGe MOS structures       | 85 |

## LIST OF FIGURES

| Figure | Pa                                                                                                                                                                                                     | age |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2.1    | Schematic view of a dc glow discharge showing the most prominent regions of the discharge                                                                                                              | 8   |

| 2.2    | Schematic view of rf discharge                                                                                                                                                                         | 10  |

| 2.3    | Schematic diagram of (a) diode and (b) triode reactor configurations                                                                                                                                   | 13  |

| 2.4    | Basic steps in a dry-etching processing                                                                                                                                                                | 15  |

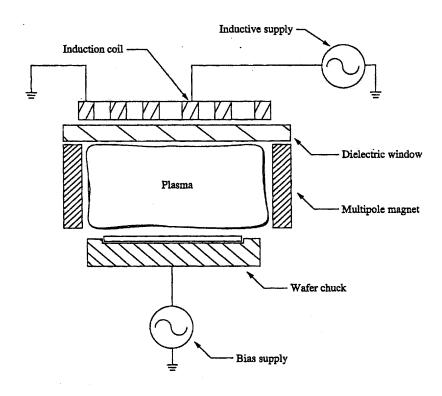

| 2.5    | Illustration of an inductively coupled plasma reactor                                                                                                                                                  | 16  |

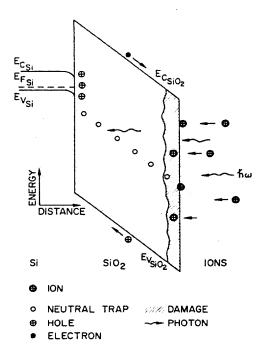

| 2.6    | Energy band diagram for thermal SiO <sub>2</sub> layer on an underlying Si substrate exposed to low-energy ions and photos which are present in an RIE                                                 | 18  |

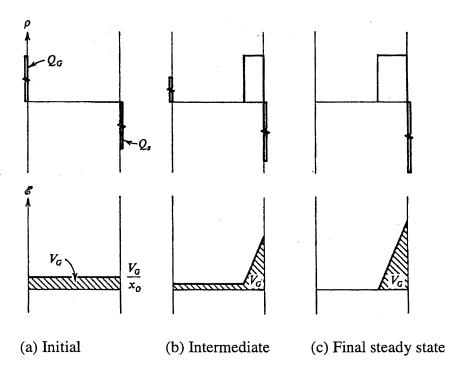

| 2.7    | Idealized model for the space-charge build-up as a function of time during Irradiation of a MOS structure under a positive gate bias                                                                   | 19  |

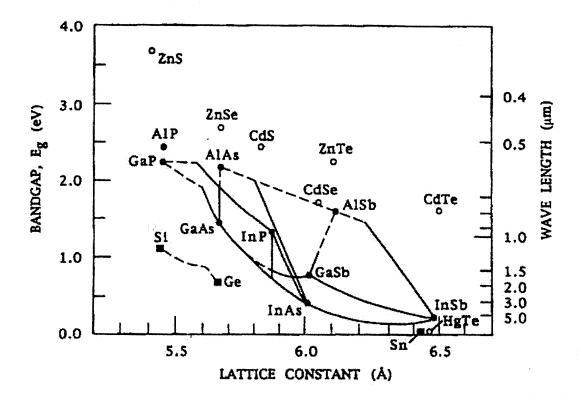

| 2.8    | Energy bandgap versus lattice constant                                                                                                                                                                 | 20  |

| 2.9    | Strained and unstrained SiGe layer                                                                                                                                                                     | 21  |

| 2.10   | Critical thickness versus Ge content                                                                                                                                                                   | 22  |

| 2.11   | Energy band diagram of graded-base SiGe HBT compared to a Si BJT                                                                                                                                       | 24  |

| 2.12   | (a) A fully pseudomorphic pMOS layer configuration with typical design parameter. (b) The quantum well for holes and inversion of the n-SiGe layer under a sufficiently high negative gate voltage     | 24  |

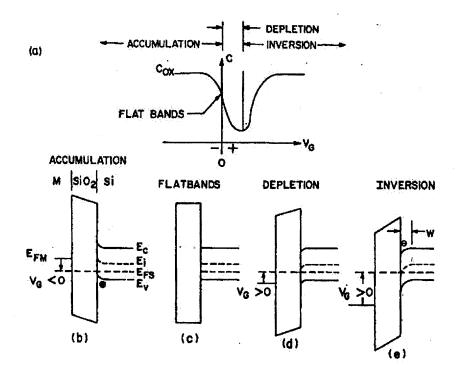

| 3.1    | To illustrate the operation of an MOS capacitor, capacitance as a function of bias, and the corresponding energy-band diagrams are shown in accumulation, depletion, inversion, and at flatband        | 29  |

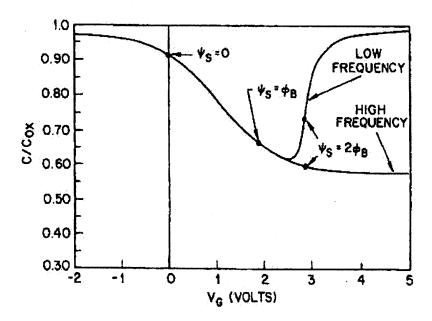

| 3.2    | Normalized high frequency and low frequency capacitance as a function of gate bias calculated for and acceptor concentration of $2\times10^{16}$ cm <sup>-3</sup> , oxide thickness 100nm, and T=300 K | 30  |

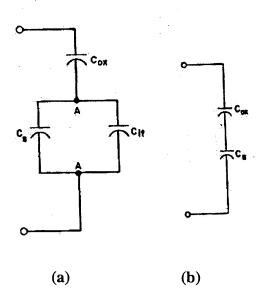

| 3.3    | (a) Low frequency equivalent circuit of MOS, (b) high frequency equivalent circuit of MOS.                                                                                                             | 31  |

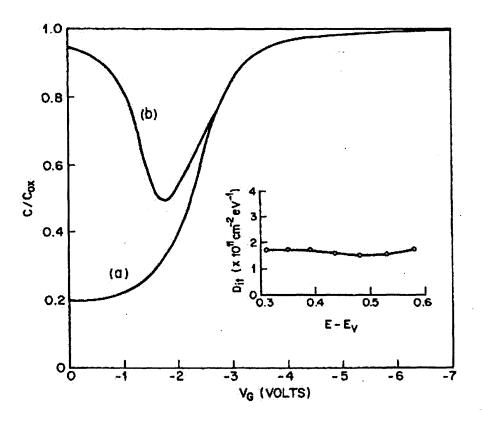

| 3.4    | Combined (a) high frequency (1MHz) and (b) low frequency C-V curves for a MOS capacitor                                                                                                                | 32  |

# LIST OF FIGURES (Continued)

| Figure | e P                                                                                                                                                            | age |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

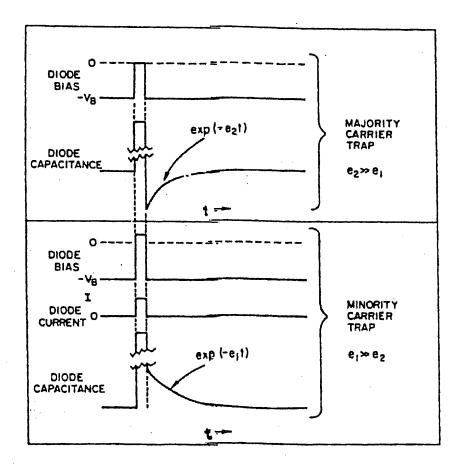

| 3.5    | Typical time dependence involved in pulsed bias capacitance transients for majority- and minority carrier traps                                                | 35  |

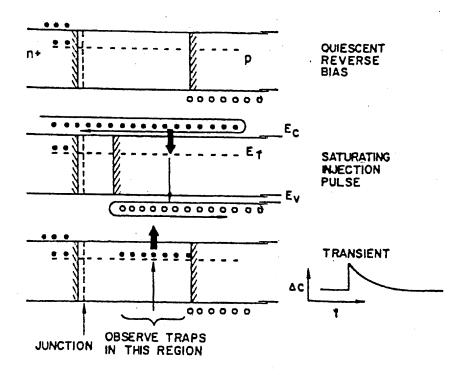

| 3.6    | Injection pulse sequence which is used to produce a capacitance transient for a minority-carrier trap                                                          | 36  |

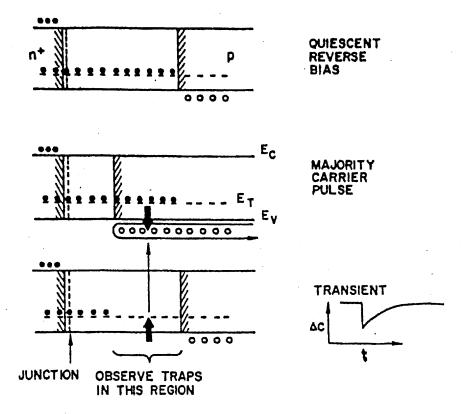

| 3.7    | Majority-carrier pulse sequence which is used to produce a capacitance transient for a majority-carrier traps                                                  | 36  |

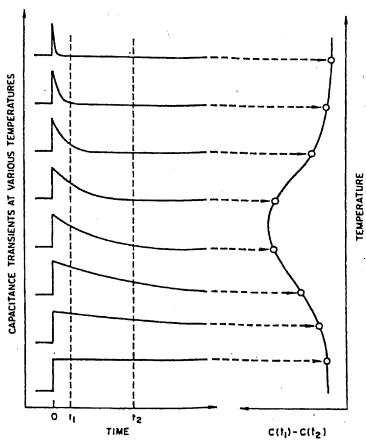

| 3.8    | Illustration of how a double boxcar is used to define the rate window                                                                                          | 38  |

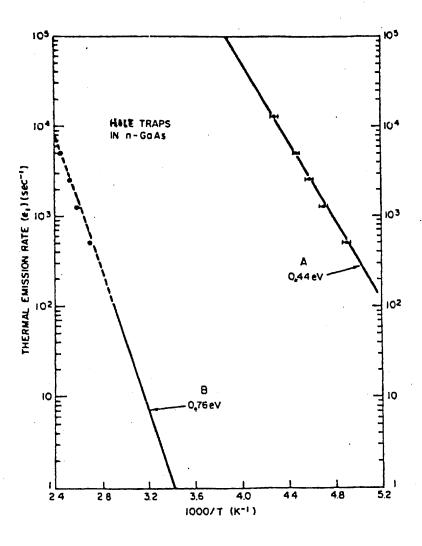

| 3.9    | Thermal emission rates vs 1000/T determined from the DLTS spectra                                                                                              | 39  |

| 3.10   | Schematic diagram of a secondary ion mass spectrometer                                                                                                         | 41  |

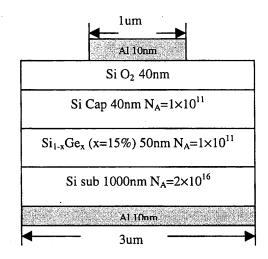

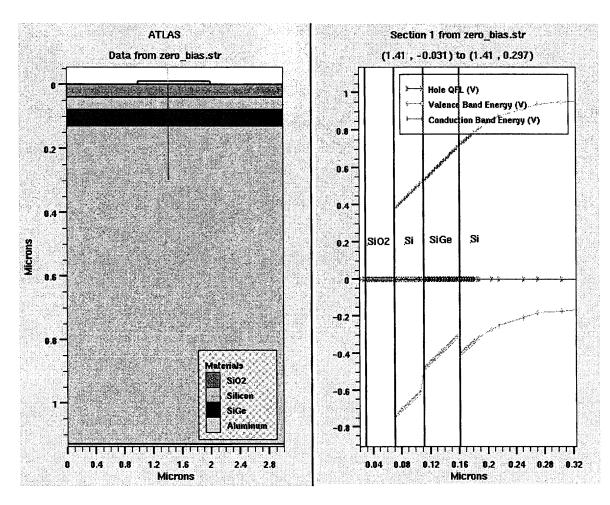

| 3.11   | SiGe MOS capacitor structure used for simulation                                                                                                               | 51  |

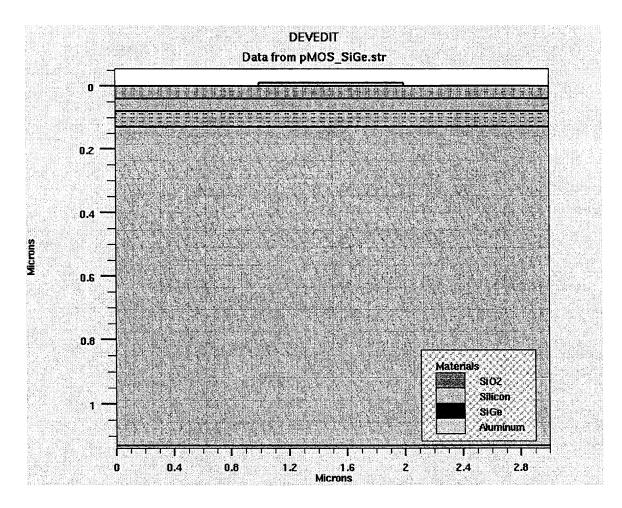

| 3.12   | Simulated device structure with mesh                                                                                                                           | 51  |

| 3.13   | Atlas command group with primary statements in each group                                                                                                      | 52  |

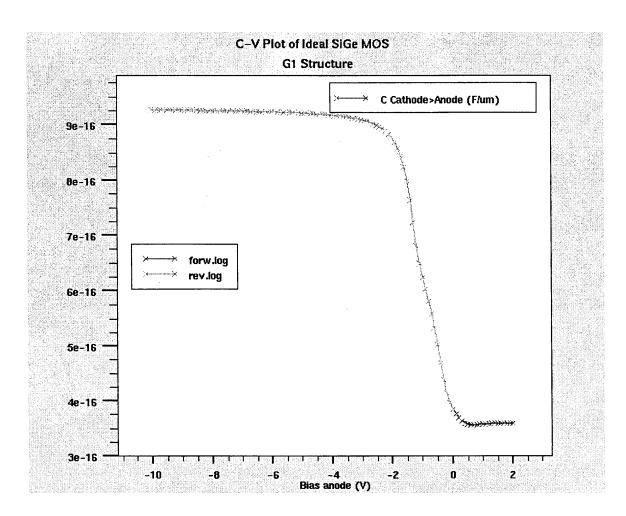

| 3.14   | Use Tonyplot to display the C-V plot                                                                                                                           | 53  |

| 3.15   | Use Tonyplot to display the energy diagram cross the MOS capacitor under certain bias condition                                                                | 54  |

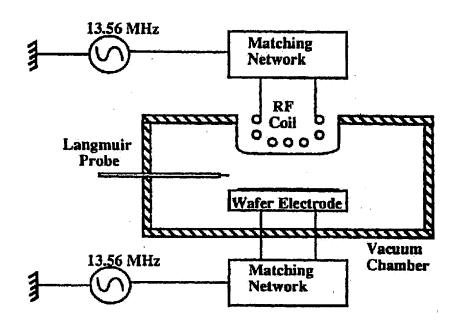

| 4.1    | A schematic diagram of the ICP reactor                                                                                                                         | 57  |

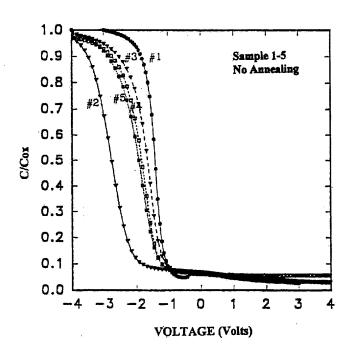

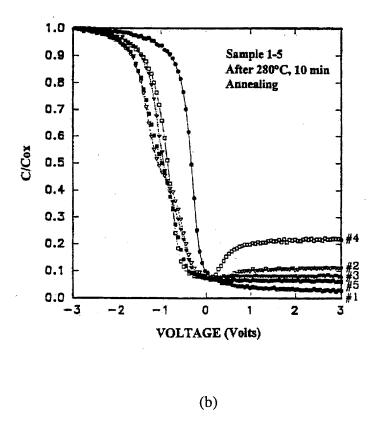

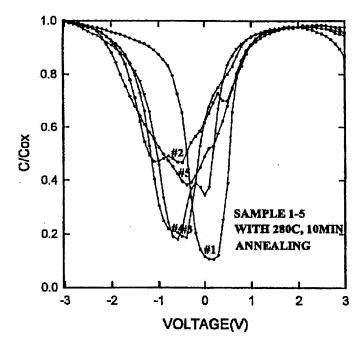

| 4.2    | Normalized C-V characteristics of various samples: (a) immediately after metal deposition; (b) after a 10 minutes annealing at 280°C in N <sub>2</sub> ambient | 62  |

| 4.3    | Quasi-static C-V curves for MOS capacitors after plasma etching in an ICP reactor with different process conditions                                            | 63  |

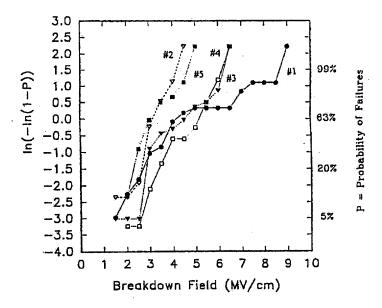

| 4.4    | The breakdown distribution of various samples                                                                                                                  | 64  |

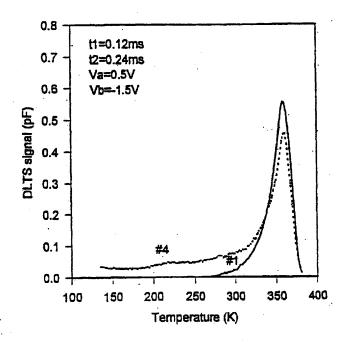

| 4.5    | DLTS spectra for the control sample #1 and the plasma etched sample #4                                                                                         | 66  |

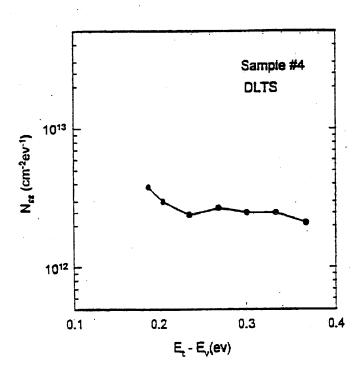

| 4.6    | Interface traps density $N_{ss}$ in the plasma etched sample (#4) as a function of energy                                                                      | 66  |

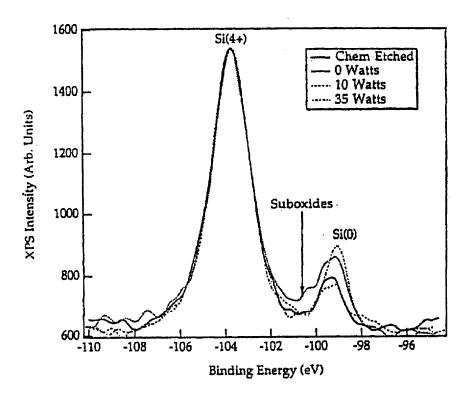

| 4.7    | XPS spectra of various samples                                                                                                                                 | 68  |

# LIST OF FIGURES (Continued)

| Figure | e I                                                                                                                                                                                         | Page |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

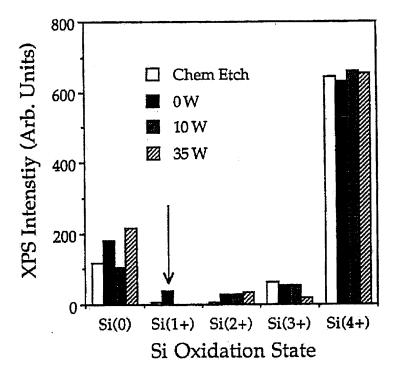

| 4.8    | XPS counts for various suboxide states                                                                                                                                                      | 69   |

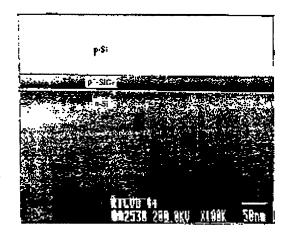

| 5.1    | Scanning electron micrograph of the RTCVD wafer                                                                                                                                             | 72   |

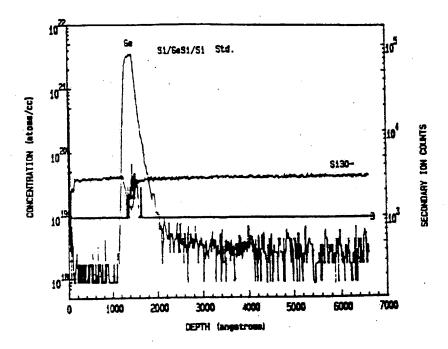

| 5.2    | SIMS profiles for as-grown RTCVD sample                                                                                                                                                     | . 74 |

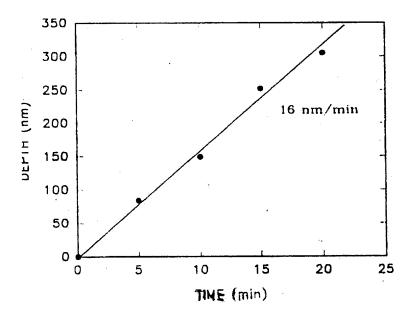

| 5.3    | Wet etching results                                                                                                                                                                         | . 74 |

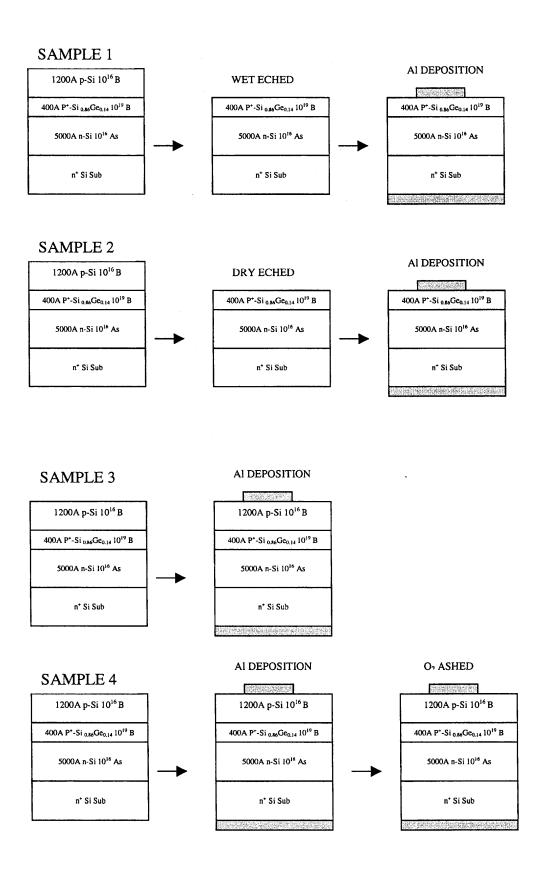

| 5.4    | Device structures were used for study and comparison                                                                                                                                        | . 75 |

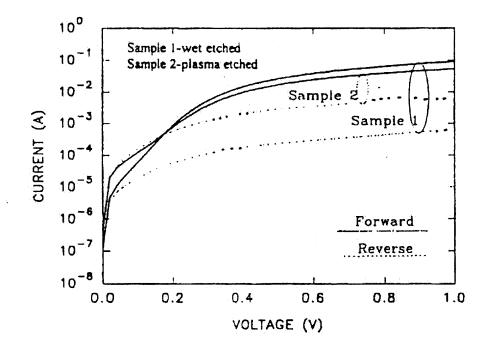

| 5.5    | The I-V characteristics of wet etched sample #1 and SF6 plasma etched sample #2                                                                                                             | 76   |

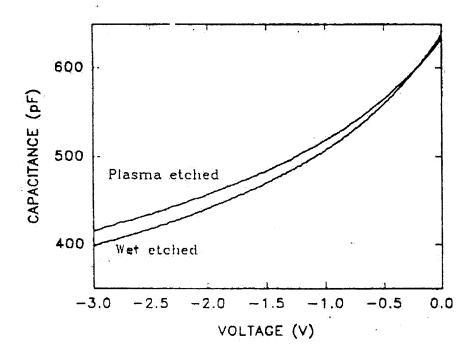

| 5.6    | The C-V characteristics of wet etched sample and SF <sub>6</sub> plasma etched sample                                                                                                       | . 77 |

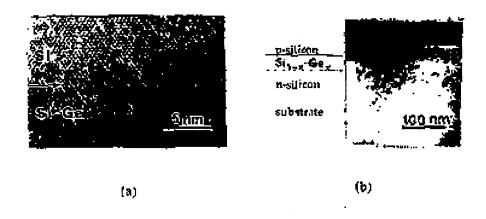

| 5.7    | <ul> <li>(a) High resolution TEM of Si/ Si<sub>1-x</sub>Ge<sub>x</sub> /Si interface after plasma</li> <li>(b) Weak beam dark field TEM micrograph showing the dislocation loops</li> </ul> | . 78 |

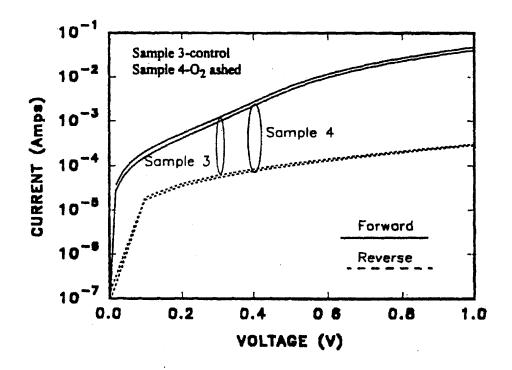

| 5.8    | The I-V characteristics of unetched sample#3 and O <sub>2</sub> plasma ashed sample#4.                                                                                                      | . 79 |

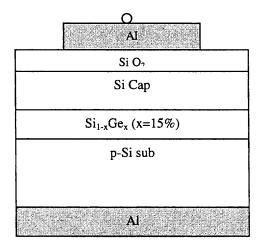

| 5.9    | Typical structure of MOS capacitor used in this study                                                                                                                                       | 80   |

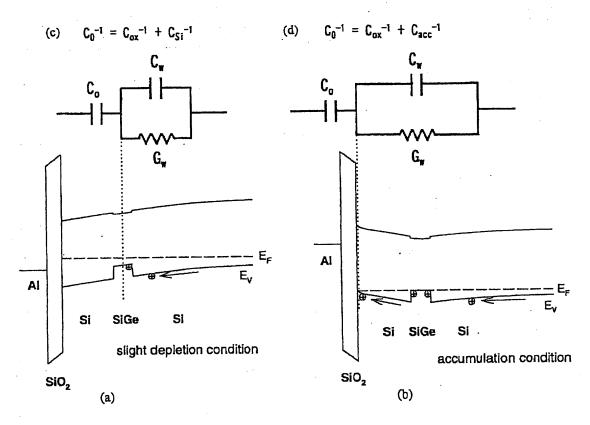

| 5.10   | Schematic band diagram under the slight depletion condition (a) and the accumulation condition (b)                                                                                          | 81   |

| 5.11   | Typical C-V profiles obtained for the wet etched samples                                                                                                                                    | . 83 |

| 5.12   | Typical C-V profiles obtained for the dry etched samples                                                                                                                                    | . 84 |

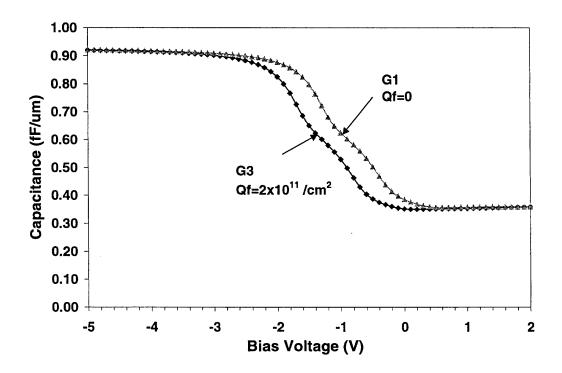

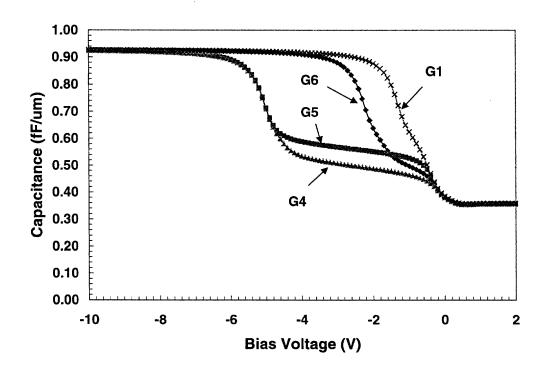

| 5.13   | Simulated C-V plots of SiGe MOS capacitors with different energy bandgap values                                                                                                             | . 87 |

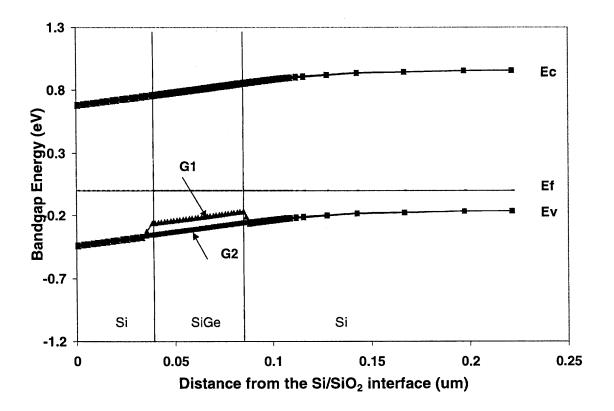

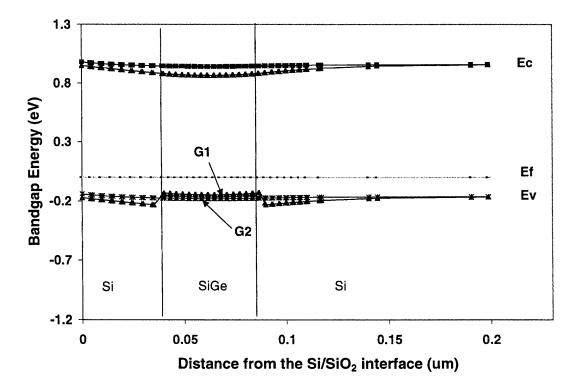

| 5.14   | Energy band diagram in G1 and G2 under -0.5V bias                                                                                                                                           | . 88 |

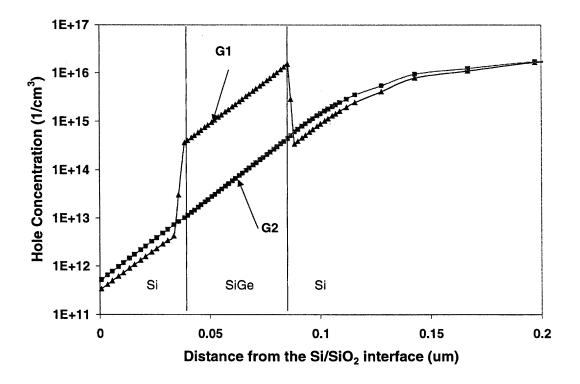

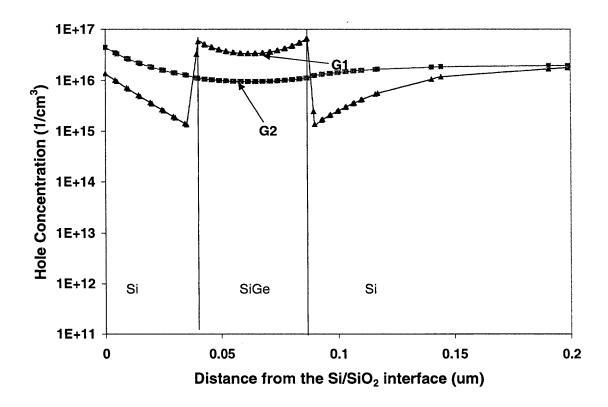

| 5.15   | Hole concentration in G1 and G2 under -0.5V bias                                                                                                                                            | 89   |

| 5.16   | Energy band diagram in G1 and G2 under -1.25V bias                                                                                                                                          | . 89 |

| 5.17   | Hole concentration in G1 and G2 under –0.5V bias                                                                                                                                            | . 90 |

# LIST OF FIGURES (Continued)

| Figure |                                                                                                                                                     | Page |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 5.18   | Simulated C-V plots of SiGe MOS capacitor with SiO <sub>2</sub> fixed positive charge                                                               | s 91 |

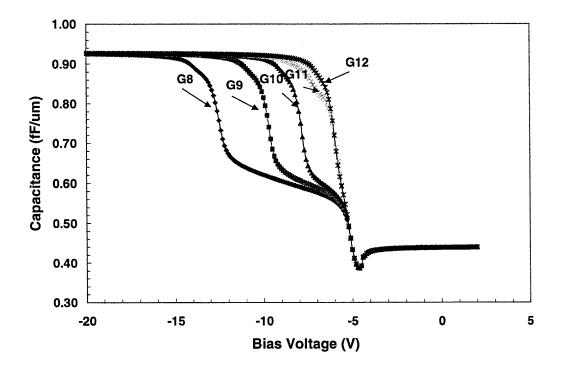

| 5.19   | Simulated C-V plots of SiGe MOS capacitor with SiO <sub>2</sub> interface traps (with different trap densities and different trap energy levels)    | 93   |

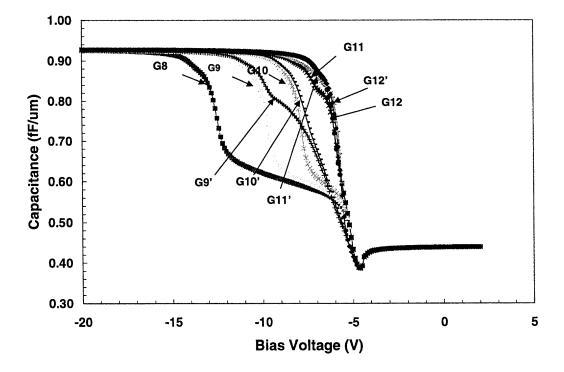

| 5.20   | Simulated C-V plots of SiGe MOS capacitor with SiO <sub>2</sub> fixed positive charge and interface traps to match Figure 5.11                      |      |

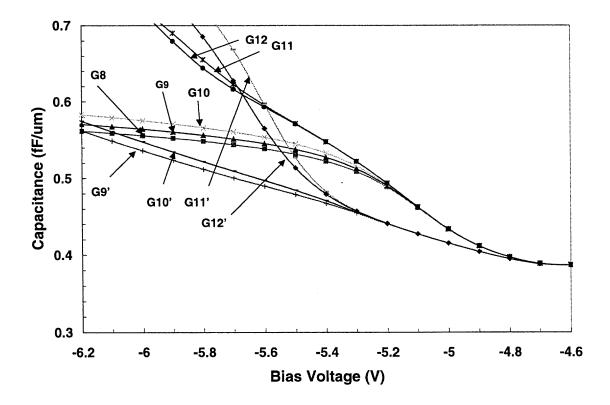

| 5.21   | Simulated C-V plots of Si <sub>1-x</sub> Ge <sub>x</sub> MOS capacitor with additional relaxed structures (G9', G10', G11' and G12') for comparison | . 94 |

| 5.22   | Zoomed plot of Figure 2.1 at slight depletion region                                                                                                | . 96 |

#### CHAPTER 1

### INTRODUCTION

### 1.1 Motivation

This is a silicon world. Greater than 95% of today's \$200 billion plus global semiconductor market uses the semiconductor silicon (Si) to realize a host of integrated circuits (IC) ranging from 1 GHz microprocessors to 64 Mb dynamic random-access memory (DRAM) chips. Si has a number of practical advantages over the other numerous semiconductors, including: 1) an extremely high-quality dielectric (SiO<sub>2</sub>) can be easily grown on Si and used for isolation, passivation, or as an active layer (e.g., gate oxide); 2) Si can be grown in very large, virtually defect-free single crystal (200 mm in production today, rapidly moving to 300 mm), yielding many (low-cost) IC's per wafer; 3) Si has excellent thermal properties allowing for the efficient removal of dissipated heat; 4) Si can be controllably doped with both n- and p-type impurities with extremely high dynamic range (10<sup>12</sup>-10<sup>22</sup> cm<sup>-3</sup>); 5) Si has excellent mechanical strength, facilitating ease of handling and fabrication; 6) it is easy to make very low-resistance ohmic contacts to Si, thus minimizing device parasitics; and 7) Si is extremely abundant and easily purified. Thus, from IC manufacturing standpoint, Si is a dream come true.

Introducing Ge into Si has a number of consequences. First and most importantly, because Ge has a larger lattice constant than Si, the energy bandgap of Ge is smaller than that of Si (0.66 eV versus 1.12 eV), thus Si<sub>1-x</sub>Ge<sub>x</sub> has a bandgap smaller than that of Si, making it a suitable candidate for bandgap engineering in Si. In addition, the compressive strain lifts the conduction and valence band degeneracies at the band extremes, effectively reducing the density of states and improving the carrier mobility with respect

to pure Si (the latter due to a reduction in carrier scattering). The Si<sub>1-x</sub>Ge<sub>x</sub> heterojunction combines heterojunction device performance with silicon manufacturability. It has been the subject of many investigations in recent years.

A series of Si-compatible hetero-structure devices, based on epitaxial growth in the Si/Si<sub>1-x</sub>Ge<sub>x</sub> system, has stirred a strong interest for high-speed devices. The narrow band gap of strained Si<sub>1-x</sub>Ge<sub>x</sub> has been used to fabricate heterojunction bipolar transistors (HBT's) [1, 2], modulation-doped field effect transistors (MODFET's) [3], long wavelength optoelectronics devices [4, 5], and tunneling and superlattice devices. Due to the lattice mismatch between silicon and germanium, the Si<sub>1-x</sub>Ge<sub>x</sub> film gown on silicon is strained up to a critical thickness. It is very important to preserve the quality of these heterojunctions throughout the fabrication process.

Dry etching techniques such as reactive ion etching (RIE), magnetron reactive ion etching (MRIE), plasma etching (PE), ion beam etching (IBE), electron cyclotron resonance (ECR) etching, reactive ion beam etching (RIBE) and inductively coupled plasma (ICP) etching can cause damage and contamination effects in exposed materials [6-18]. In fact, damage is often inherent in these processes due to the presence of ion bombardment, which can create bonding damage in semiconductors and insulators [6-14, 16, 18], as well as due to the presence of UV radiation, which can create bonding damage in insulators [15]. Contamination is also often inherent in these processes due to the presence of residue layers made up of reactant species and reaction products and due to the presence of impurities which may permeate the etched material during the dry etching exposure [8, 9, 16-22]. Inductively coupled plasma sources have emerged as the most used in plasma etchers. They are capable of uniform etching of anisotropic features over

large area wafers at etch rates comparable to conventional high-pressure capacitively coupled reactive ion etching tools. The ion energies incident on the wafers can be effectively decoupled from plasma generation by independently applying rf power to the wafer chuck.

The reliability and electrical performance of these Si devices and strained Si/Si<sub>1-x</sub>Ge<sub>x</sub> hetero-structure devices may be significantly affected by plasma processing during device manufacturing. Creation of strain-relieving misfit dislocation and/or threading dislocations [23] may be possible when strained Si<sub>1-x</sub>Ge<sub>x</sub> films are processed using reactive ion etching. Though reactive ion etching of Si has been studied the impact of inductively coupled plasma on Si device are still unfolding. Besides not much is known about the modifications to electrical characteristics of strained Si<sub>1-x</sub>Ge<sub>x</sub>. It is very important to show that how the plasma process affects the strained Si<sub>1-x</sub>Ge<sub>x</sub> heterostructure material and devices.

## 1.2 Objectives of the Research

The overall goal of the research carried out for this thesis has been to obtain a basic understanding of plasma induced electrical and physical damages to Si and SiGe devices leading to the optimization of plasma etch process and development of next generation plasma etch tools suitable for sub-micro heterojunction devices. The investigation has been focused on studying the issues related to device physics with the objective of gaining a fundamental understanding of the damage mechanisms of the associated plasma etching.

This broad objective of this program has been achieved by carrying out research in two key areas. Firstly, by using well known Si MOS device to evaluate the plasma induced damage in advanced ICP reactor; and secondly by applying the similar testing techniques and the device simulations to SiGe p<sup>+</sup>-n diode and SiGe MOS devices.

Electrical and physical characterizations, such as I-V, C-V, Deep Level Transient Spectroscopy (DLTS), Transmission Electron Microscopy (TEM), X-Ray Photoelectron Spectroscopy (XPS), were used to study the plasma induced damages in ICP reactor. These studies were aimed at establishing the correlation between and electrical and physical damage, and developing basic understanding of damage mechanisms.

C-V profiling on Si<sub>1-x</sub>Ge<sub>x</sub> MOS capacitor is potentially powerful method to estimate plasma process-induced band-gap modifications. The presence of interface trap has significantly influenced the measurement result. In this thesis, the utility of device simulator is demonstrated by the insights gained into the underlying mechanisms of space charge and surface-state charge between heterojunction semiconductor and insulator. The finding of the influence of interface traps has been simulated and it correlates with the measurement result well.

The results of this work have significant technological consequences and applications. For example, the fundamental understanding of etch induced damage to thin gate oxide in ICP reactors will enable their widespread usage by integrated circuit manufactures. In addition, the testing and simulation results of Si<sub>1-x</sub>Ge<sub>x</sub> device in this thesis will help to develop new methods of detection and approaches of damage control of plasma induced damage in Si<sub>1-x</sub>Ge<sub>x</sub> materials and devices.

#### 1.3 Thesis Organization

Chapter 2 reviews basic physic phenomena in RF glow discharges, plasma etching tools, and the fundamental understanding of plasma induced damage to Si and SiGe devices. The background of SiGe technology is also described in that chapter.

Chapter 3 describes electrical and physical measurement techniques that have been used for this research. That includes I-V, C-V, DLTS developed as a part of this thesis work, SIMS, XPS and TEM. The knowledge of these techniques will lead to understand and interpret the research results in this thesis. In addition an overview of device simulation relevant to this work is presented in that chapter.

The research results of etch induced damage to thin oxide in ICP reactor have been described in Chapter 4. This work was done as part of project funded by SEMATECH Center of Excellence in New Jersey. It is observed that device damages are well associated with the operating conditions of the reactor.

Chapter 5 outlines the research results of process induced damage to strained Si<sub>1</sub>.  $_x$ Ge<sub>x</sub> material and devices. This work was done as part of project funded by the National Science Foundation (grant No. ECS-9207665). It is found that SF<sub>6</sub> plasma used to etch an overlying Si film stopping at the SiGe strained film can cause electrical damage to Si/SiGe heterojunction device. The O<sub>2</sub> photo-resistor strip process has no strong effect on the SiGe device due to the protection from its aluminum contact layer. The presence of interface trap at SiO<sub>2</sub> deposited by low-pressure CVD process creates big kink at C-V profile at accumulation region of SiGe MOS capacitor. The C-V curves were affected by the reduction of trap densities as well as the reduction of  $\Delta E_v$  due to relaxation after

annealing. Dry etched sample demonstrates a faster relaxation mechanism as compared to its wet etched counterpart due to the creation of dislocation loops by dry etching process.

Chapter 6 is the conclusions of this research and the suggestions for future works.

An example of Atlas input file of an ideal SiGe MOS capacitor is presented in Appendix.

For the purpose of clarity, Chapters 5 and 6 have their own introduction and summary sections.

#### **CHAPTER 2**

#### PLASMA ETCHING PROCESS AND PLASMA DAMAGE

A plasma is defined as a partially ionized gas composed of ions, electrons and a variety of neutral species. It contains approximately equal concentrations of positively charged particles (positive ions) and negatively charged particles (electrons and negative ions). The plasma useful to ULSI processing is a weakly ionized plasma, called a "glow discharge", containing a significant density of neutral particle - more than 90% in most etchers.

### 2.1 Basic Physical Phenomena in RF Discharges

When an electric field of sufficient magnitude is applied to a gas, the dissociation of gas occurs. The process begins with release of an electron by some means such as photo-ionization or field emission. The released electron is accelerated by applied field and gains kinetic energy, but in the course of its travel through the gas, it loses energy in collision with gas molecules. There are two types of collisions, elastic and inelastic. Elastic collisions deplete very little of electron's energy, because of the great mass difference between electrons and molecules. Ultimately the electron energy becomes high enough to excite or ionize a molecule by inelastic collisions. In ionizing collisions the electrons loses essentially all of its energy. Ionization frees another electron, which is accelerated by the field, and so the process continues. If the applied voltage exceeds the breakdown potential, the gas rapidly becomes ionized through its volume.

Electrons released in ionizing collisions and by secondary processes are lost from the plasma by drift and diffusion to the boundaries, by recombination with positive ions, and, in certain electronegative gases, by attachment to neutral molecules to form negative ions. The discharge reaches a self-sustained steady state when electron generation and loss processes balance each other. Non-ionizing, inelastic collisions between electrons and gas molecules or atoms also occur. Two important types of nonionizing collision are electronic excitation of molecules (or atoms) and molecular fragmentation. Electronically excited molecules and atoms account for much of the luminous glow of the plasma by emitting photons as they relax to lower-lying electronic states. Molecular fragments are often highly reactive atoms and free radicals. A free radical is a molecular fragment having an unpaired electron.

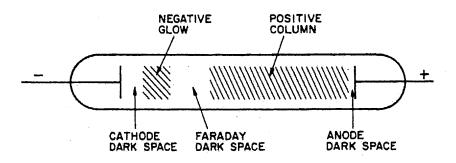

The simplest discharge to produce is the glow discharge, in which a dc potential is applied between two metal electrodes in a partially evacuated enclosure. The discharge is visibly non-uniform between the electrodes and is composed of a series of luminous light and dark zones, shown in Figure 2.1.

Figure 2.1 Schematic view of a dc glow discharge showing the most prominent regions of the discharge (after S. M. Sze, Ref. 24).

If a low-frequency alternating field is applied across the electrodes in Figure 2.1 their polarity changes every half-cycle so that each electrode alternates as cathode. The ions and electrons can both follow the filed and establish a glow discharge identical to

that of dc discharge, except for periodic polarity reversal. As the frequency of the applied field is increased, the ions created during breakdown cannot be fully extracted from the gap prior to field reversal. As the frequency is increased further, a large fraction of the electrons have insufficient time to drift to the positive electrode during a half-cycle. These electrons then oscillate in the inter-electrode gap and undergo collision with gas molecules. The lower limit of frequency for oscillation depends on the electron mobility, the electrode spacing, and the amplitude of the applied field. The frequency limit is typically the rf range.

Three advantages are realized with rf discharges, which make their use widespread. First, electrons can pick up sufficient energy during their oscillation in the gap to cause ionization. The discharge can thus be sustained independent of the yield of secondary electrons form the walls and electrodes, Second, the probability of ionizing collisions is enhanced by electrons allowing operation at pressures as low as ~10<sup>-3</sup> Torr. The third advantage is that electrodes within the discharge can be covered with insulating material. This permits sputter etching and reactive sputter etching of insulators, and also eliminates problems due to the build-up of insulating material on metal electrodes that can occur when reactive gases are employed in plasma etching.

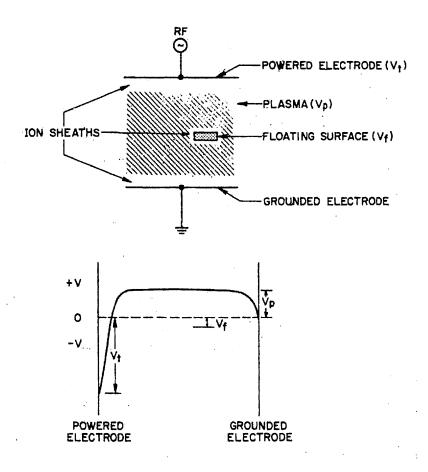

The potentials that develop at various points in the rf discharge are important in determining the energies of ions incident on surface in the plasma. Three potentials pertinent to various etching techniques are labeled in Figure 2.2.  $V_t$  is the potential at the surface of the rf-powered electrode measured with respect to ground.  $V_p$  is the plasma potential with respect to ground,  $V_f$  is the potential (relative to ground) of an electrically floating surface, such as an insulating wall or a substrate isolated form ground by an

insulating film. The potential of the surface with respect to the plasma determines the maximum possible energy of ions bombarding that surface. To a first approximation, the rf coupling across the ion sheaths is capacitive, with the area and thickness of a sheath determining the capacitance. For this reason, the ratio R of the area of the rf-powered electrode to the area of all ground surfaces in contact with the plasma is a key parameter in determining how the applied voltage is distributed among the ion sheaths. The potential  $V_p$ - $V_t$  increases as R decreases. As a practical consequence, this relationship means that sputter etching which requires relatively large  $V_p$ - $V_t$ , is most efficient when R is small and the substrate forms or is attached to the rf-powered electrode (the target).

Figure 2.2 Schematic view of rf discharge (after S. M. Sze, Ref. 24).

Under the same conditions the ground-electrode ion sheath has a comparatively small potential drop  $V_p$  across it. Therefore very little or no sputtering occurs there. Plasma-etching system tend to be more symmetric (R ~0.5) and operated at higher pressure (usually in the 0.1- to 1.0-torr range). Hence the potential across the ion sheaths, including the powered electrode, are on the order of  $V_p$  (less than 100 V). The floating potential,  $V_f$  is usually only a few volts below ground. Therefore, ions bombarding on a floating surface do not usually have energies much greater than  $V_p$ .

### 2.2 General Description of Plasma Etch Tools

In the plasma etching literature, various terms such as plasma etching (referred to etching wafer placed on ground electrode in a relative high pressure plasma) and reactive ion etching or reactive sputter etching (referred to etching wafer placed on powered electrode in a relatively low pressure plasma) are used extensively to describe various process conditions. However, plasma etching term is widely used today to describe all process conditions because it is a well accepted fact now that ions are rarely the etchant and neutrals are responsible for almost all reactive etching [25]. In this thesis, the term plasma etching is used instead of reactive ion etching to describe low pressure etching processes.

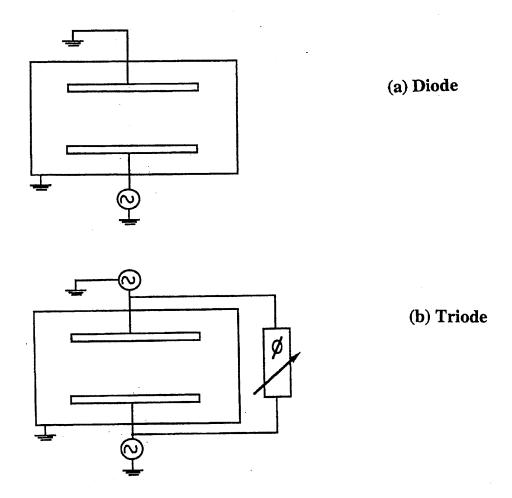

Parallel-plate configurations are widely used in a single wafer etcher due to their simplicity and ability to direct energetic ions normal to the surface being etched. Production etching systems can have a variety of configurations depending on the parameters of a process needed to be controlled as well as the specific applications of the system. The most common, commercially used, single wafer etching tool configuration today is the parallel-plate planer diode (Figure 2.3 (a)). One of the two electrodes of the diode configuration is capacitively coupled to the rf power supply through an impedance matching network and the other electrode is grounded. The frequency of the rf power supply can range from several kHz to several MHz [26]. However, the most common commercially used frequency is 13.56 MHz (an industry standard reflecting FCC regulations) and discussion in this thesis is limited only to the plasma process occurring in a 13.56 MHz discharge. The major limitation of the diode configuration is the strong coupling between the plasma generation and the induced bias. As the power is increased

to enhance ionization in plasma, the induced bias also increases and can cause substantial substrate damage.

Triodes, as their name implies, are tri-electrode discharge systems. In triodes (see Figure 2.3b), two of the three electrodes are powered while the third electrode is normally at the ground potential. The plasma parameters (ion energy, electron temperature and charged particle concentrations) can be somewhat independently varied in a triode relative to an equivalent diode system [27].

**Figure 2.3** Schematic diagram of (a) diode and (b) triode reactor configurations (after V. Patel, Ref. 28).

The extensive use of plasmas to active etch processes derives from two major features of low-temperature non-equilibrium discharge. The first of these is the existence of energetic electrons with average energies in the range of 2 to 10 eV in the plasma volume. These electrons break bonds to form chemically active etchant species or their precursors. The electrons are also responsible for ionization, which sustains the discharge and creates ions. These ions are often essential to the etch process. The second important feature of plasmas for etching applications is the acceleration of ions at the plasma boundary. In many configurations, the ions are accelerated by the electric field in the sheath region between the plasma boundary and wafer. This field can accelerate ions, normal to the wafer surface, with typical energies in the range of 50 to 1000 eV. The ion bombardment often results in mechanisms that allow lithographic patterns to be etched anisotropically with little or no lateral removal of materials. This feature is essential to realization of increasing device density in modern integrated circuits, and is perhaps, the major reason why plasma activated etching is used so extensively.

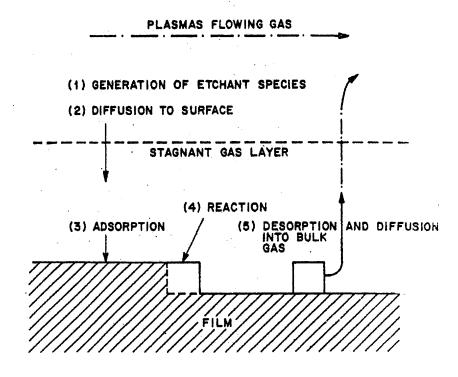

The plasma etching process proceeds in five steps as illustrated in Figure 2.4 (1). The process begins with generation of the etchant species in the plasma. (2) The reactant is then transported by diffusion through a stagnant gas layer to the surface. (3) The reactant is adsorbed on the surface. (4) This is followed by chemical reaction (along with physical effects such as ion bombardment) to form volatile compounds. (5) These compounds are desorbed from the surface, diffused into the bulk gas, and pumped out by the vacuum system.

Figure 2.4 Basic steps in a dry-etching processing (after S. M. Sze, Ref. 29).

As the features for ULSI continue to decrease, the limits of the conventional rf capacitive-coupled parallel system are being approached. Other types of high-density plasma sources, such as inductively coupled plasma (ICP) sources or helicon plasma sources, may become the main plasma sources for future ULSI processing. An inductively coupled plasma source, shown in Figure 2.5, generates high-density, low-pressure plasma that is decoupled for the wafer, and it allows independent control of ion flux and ion energy [73]. Plasma is generated by a flat spiral coil that is separated from the plasma by a dielectric plate on the top of the reactor. The wafer is located several skin depths away from the coil, so it is not affected by the electromagnetic field generated by the coil. There is little density loss because plasma is generated only a few mean free paths away from the wafer surface. Therefore, a high-density plasma and high etch rates

are achieved. The ion potential in ICP is more than 20 eV while the average electron temperature is about 3-6 eV [74].

**Figure 2.5** Illustration of an inductively coupled plasma reactor (after Keller, Forster, and Barnes, Ref. 73).

### 2.3 Plasma Induced Damage to Silicon Devices

Due to its advantages mentioned in previous chapter, plasma etching is a key process in VLSI circuit fabrication. Unfortunately plasma exposure also deleteriously affects semiconductors and insulators since it can result in (1) intrinsic bonding damage, (2) etching species and impurity permeation, and (3) residue or surface film formation. These damages and contamination effects lead to anomalous electrical behavior for metal/silicon contacts to etched Si surface and increased neutral trap density, increased positive charge, and increased interface state density for SiO<sub>2</sub>. This section will mainly focus on the plasma induced damages to SiO<sub>2</sub> and Si/SiO<sub>2</sub> interface, while the damages induced in Si by dry etching can be found in Ref. 30 and its references.

### 2.3.1 Plasma Damage to Si/SiO<sub>2</sub> System

The variety of energetic particles (ions, electrons, and photons) present in a plasma creates a potentially hostile environment for processing VLSI devices. The gate oxide and the SiO<sub>2</sub>-Si interface are particularly susceptible to damage by irradiation with these particles [31,32].

The damage can take several forms (as shown in Figure 2.6): (1) atomic displacement resulting from energetic ion impact; for reactive etching this usually limited to a region no more than 10 nm below the exposed surface; (2) primary ionization where Si-O bonds are broken and electron-hole pairs formed; this process is caused mainly by deep UV photons and soft x-rays, and (3) secondary ionization where electrons created by atoms displacement or primary ionization interact with defects in the Si-O network. Each of these forms of damage produces similar electronic defects-trapped positive charge and

neutral traps [33]. These damages will be fatal in long terms to thin insulators such as MOSFETs gate dielectrics and capacitor insulators.

Figure 2.6 Energy band diagram for thermal SiO<sub>2</sub> layer on an underlying Si substrate exposed to low-energy ions and photos which are present in an RIE (Ref. 33).

An idealized model for the build-up of such positive space charge in the oxide under ionizing radiation exposure is as follows in Figure 2.7 [35]. During irradiation, electron-hole pairs will be generated in the oxide. If there is no electric field present in the oxide, the electrons and holes will recombine, resulting in no net charge building up in the oxide. However, if there is an electric field present in the oxide, this field will tend to separate the electrons and holes. In particular, a field corresponding to a positive gate voltage will tend to pull electrons toward the gate electrode, where most flow out into the external circuit. Very few electrons become trapped in the oxide. Holes drift much more slowly toward the negative electrode. If no electron can enter interface from the silicon into the oxide, trapping of the holes near the oxide-silicon interface will result in a

gradual build-up of a space charge. Due to the increased electric field, an increasing fraction of the total applied voltage will be dropped across this space-charge region. Thus as the space charge grows, eventually the field in the rest of the oxide layer is brought to zero.

**Figure 2.7** Idealized model for the space-charge build-up as a function of time during irradiation of a MOS structure under a positive gate bias. [Ref. 35]

High-temperature annealing (1000 °C in N<sub>2</sub>) removes the atomic displacement damage, but trapping sites related to the implanted ions are still present [34]. Photo damage is manifested as trapped holes and neutral traps. The trapped holes can be removed by annealing at 400 °C, whereas removal of the neutral traps requires annealing at 600 °C or more. Therefore they can not be removed when Al electrodes or contacts are already in place. It has also been demonstrated that the latent damage will reappear easily by hot carriers and the device performance will be degraded soon [36].

# 2.4 Plasma Damage to Si/Si<sub>1-x</sub>Ge<sub>x</sub> Heterojunction Systems

# 2.4.1 Si<sub>1-x</sub>Ge<sub>x</sub> Material and Devices

Figure 2.8 shows the energy bandgap as a function of lattice constant for several elemental and compound semiconductors. Since AlAs and GaAs have similar lattice constant, the ternary alloy AlGaAs has essentially the same lattice constant over the entire range of compositions from AlAs to GaAs. As a result, one can choose the composition x of the ternary compound Al<sub>x</sub>Ga<sub>1-x</sub>As to fit the particular device requirement and grow this composition on a GaAs wafer. The resulting epitaxial layer will be lattice matched to the GaAs substrate.

Figure 2.8 Energy bandgap versus lattice constant (after Jalali and Pearton, Ref. 37).

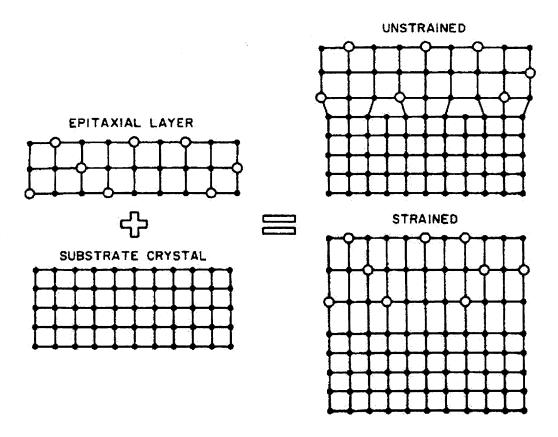

In addition to the widespread use of lattice-matched epitaxial layer, the advanced epitaxial growth techniques allow for the growth of very thick layer of lattice-mismatched crystal. If the mismatch is only a few percent and the layer is thin, the epitaxial layer grows with a lattice constant in compliance with that of the seed crystal. The resulting layer is in compression or tension along the surface plane as its lattice constant adapts to the substrate crystal. Such a layer is called *psedomorphic* because it is not lattice matched to the substrate without strain. An unstrained SiGe layer is compared with a strained SiGe layer on the Si substrate shown in Figure 2.9. For the relaxed layer there will be many dislocations at the interface.

### STRAINED LAYER EPITAXY

Figure 2.9 Strained and unstrained SiGe layer (Ref. 38).

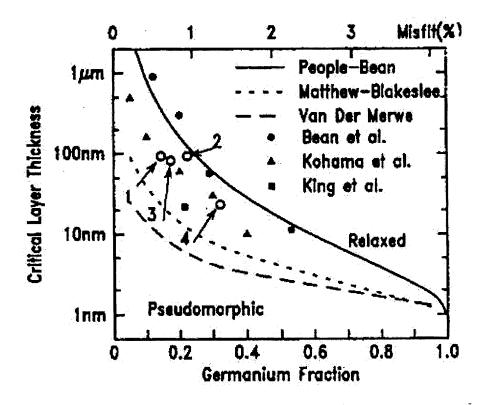

The thickness of the Si<sub>1-x</sub>Ge<sub>x</sub> layer is important device design consideration. The maximum thickness for psedomorphic growth (the critical thickness) of Si<sub>1-x</sub>Ge<sub>x</sub> alloys is an important property of the system. Van der Merwe [39] introduced the concept of critical thickness based on equilibrium theory. He defined critical thickness as the film thickness below which it was energetically favorable to contain the misfit by elastic energy stored in the distorted crystal and above which it was favorable to store part of energy in misfit dislocation at the heteroepitaxial interface. Figure 2.10 shows the critical thickness versus Ge content.

Figure 2.10 Critical thickness versus Ge content (after Iyer et al., Ref. 40).

The experimental observation of the onset of strain relaxation is limited by the experimental techniques used. Conventional x-ray diffraction and transmission electron

microscopy (TEM) can detect relaxation only when it exceeds 0.1%. Refinements of these techniques, such as triple-crystal x-ray diffraction, may be enable resolution of strain below 0.01%. Electron-induced-current (EBIC) can be used to image dislocations because of the increased carrier recombination in the vicinity of dislocation. Other electrical evaluation methods for the quality of heterojunction include measurement of the reverse leakage current across p-n junction, the ideality factor of the forward injection, and measurement of band discontinuities.

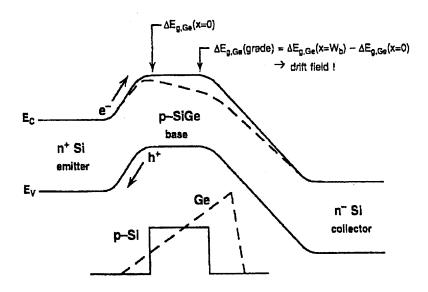

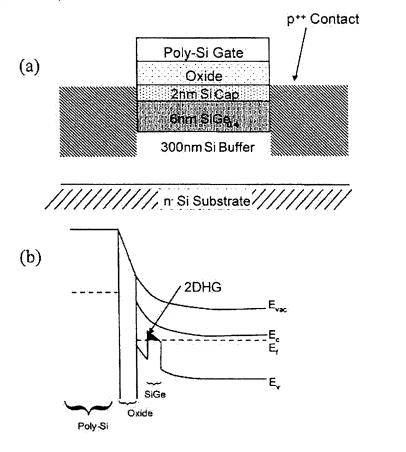

In the SiGe HBT, most of the bandgap reduction results from shift in valence-band edge. The conduction-band discontinuity is usually a small fraction of the total bandgap difference. The experimental data indicate that valence-band discontinuity between Si and  $Si_{1-x}Ge_x$  can be approximated by  $\Delta E_V=6.4x$  meV for 0< x<17.5%. The essential differences between the SiGe HBT and the Si Bipolar Transistor are best illustrated by considering a schematic energy band diagram. Observe in Figure 2.11 [41] that Ge-induced reduction in base bandgap that occurs at EB edge of the quasi-neutral base induces a quasi-drift field in the neutral base. Figure 2.12 shows a suitable layer configuration for a fully pseudomorphic Si/ Si<sub>1-x</sub>Ge<sub>x</sub> pMOS [42].

Figure 2.11 Energy band diagram of graded-base SiGe HBT compared to a Si BJT (after J. D. Cressler, Ref. 41).

**Figure 2.12** (a) A fully pseudomorphic pMOS layer configuration with typical design parameters. (b) The quantum well for holes and inversion of the n- SiGe layer under a sufficiently high negative gate voltage (after T. E. Whall, Ref. 42).

Because of the mismatch between the pseudomorphically grown SiGe layer and the underlying silicon substrate, strained SiGe alloy changes carrier mobility due to the strain-induced energy shifts and dislocation in the energy-band spectrum. The effective drift mobility of holes in a strained MOS gate SiGe/Si heterostructure inversion layer shows 50% enhancement in mobility over that of silicon at room temperature. Results calculated for the lattice drift mobility of strained SiGe also show increase in the mobility relative to that of silicon.

Vapor-phase epitaxy and molecular beam epitaxy technologies are capable of growing epitaxial layer with high crystalline perfection and purity. Highly controlled doping level up to 10<sup>19</sup> cm<sup>-3</sup> or more can be achieved, and highly controlled changes in the doping level are possible during growth with minor adjustment in growth parameters. With MOCVD, layer thickness below 5 nm has been achieved. With MBE, thickness below 1 nm has been reached.

### 2.4.2 Physical and Electrical Damage to Strained Si<sub>1-x</sub>Ge<sub>x</sub> Devices

The fabrication of heterojunction structures often requires to make contact to a buried SiGe or Si layer, e.g. in Si/SiGe/Si heterostructures used to form Si-Based HBT where the base region consists of the SiGe alloy whereas the emitter and collector region are made of Si. Making contact to the SiGe base region requires etching Si and stopping on the SiGe base. In other application etching SiGe and stopping on a Si underlayer is required. The dry etching characteristics of strained SiGe in terms of etch rates, etch profiles and surface-chemical aspects have been studied [43, 44], but the research on plasma induced damage to the SiGe underlayer after etching the Si is very limited. In this

study, the electrical measurements I-V & C-V characteristics of wet etched,  $SF_6$  plasma etched, un-etched and  $O_2$  ashed samples of  $Si_{1-x}Ge_x$  p<sup>+</sup>-n heterojunction were presented. These electrical evaluation methods can serve as very sensitive qualitative measurements of heterojunction quality. In addition, the material characterizations of these samples by SIMS and TEM have been performed. It has been reported that plasma etching may create strain-relieving misfit dislocation and/or threading dislocation to strained SiGe material and can relax the strain of coherently strained SiGe after subsequent annealing [23, 45]. This thesis explores this area further, using the device simulation to verify these findings and show the limitation of C-V profiling as a detection method.

### **CHARPTER 3**

# **EXPERIMENTAL TECHNIQUES**

#### 3.1 Electrical Characterization

## 3.1.1 I-V & C-V Measurements to Evaluate MOS System

There are several different ways of investigating semiconductor surfaces and oxide-semiconductor interfaces. The MOS capacitor is the most powerful for investigating nearly all the electrical properties of the MOS system [46]. The superiority of the MOS capacitor rests on its simplicity of analysis results because thermal equilibrium conditions are obtained and because a one-dimensional treatment is accurate. Using the MOS capacitor, nearly all of the properties of interest in the SiO<sub>2</sub>, at the Si-SiO<sub>2</sub> interface, and in the silicon can be measured. The MOS capacitor is simpler to use for these studies than actual devices used in integrated circuits. Any change in process that improves the electrical properties of the MOS capacitor makes the same improvement on the actual device.

Using MOS capacitor for measuring properties of the MOS system, the following properties can be obtained:

- 1 Doping profile in the silicon

- 2 Conductivity type of the silicon

- 3 Dielectric constant of SiO<sub>2</sub>

- 4 Work function differences between silicon and gate

- 5 Oxide breakdown field

- 6 Interface trap level density (Qit) as a function of the energy in the bandgap

- Charge configurations in the oxide such as oxide fixed charge  $(Q_f)$  and the charge at the interface between  $SiO_2$  and another insulator deposited on top of it.

- 8 Mobile ionic charge Q<sub>m</sub> and oxide-trapped charge Q<sub>ot</sub> in SiO<sub>2</sub>

- 9 Interface trap capture probability for both electrons and holes as a function of energy in the bandgap

- 10 Surface recombination velocity

#### **I-V Measurement**

Ramped voltage breakdown (RVBD) and time dependent breakdown (TDBD) are the most important gate oxide integrity (GOI) tests. A good number is a breakdown field of 12 MV/cm or more. The I-V characteristics of Schottky barriers (leakage) are sensitive to lifetime and interface states i.e. sensitive to surface damage. The I-V test is not as straightforward in interpretation as GOI and C-V but is a "best" electrical method for detecting lattice damage.

#### **C-V Measurement**

C-V tests are necessary to determine mobile and trap concentrations. The MOS capacitor is at thermal equilibrium at all values of gate bias below the oxide breakdown field. That is, no dc current flows when gate bias is applied. Thus the Fermi level in the silicon always is flat all the way to the Si-SiO<sub>2</sub> interface as shown Figure 3.1. Energy values Ec and Ev are the conduction and valence band edges, respectively; Ei is the intrinsic Fermi level;  $E_{FS}$  is the Fermi level in the silicon;  $E_{FM}$  is the Fermi level in the metal; and W is depletion layer width. At low frequencies the MOS capacitor also is in

thermal equilibrium under small-signal excitation, provided that minority carriers can respond to variation in the ac field.

Figure 3.1 To illustrate the operation of an MOS capacitor, capacitance as a function of bias, and the corresponding energy-band diagrams are shown in accumulation, depletion, inversion, and at flatbands (after E. H. Nicollian and J. R. Brews, Ref. 46, p. 82).

Minority carriers follow an applied gate voltage as long as the period of the applied ac voltage is much longer than the minority carrier response time  $\tau_R$ . Response time for minority carriers in silicon at room temperature is typical 0.01-1sec in strong inversion. Because this response time is very long, inversion layer capacitance will be frequency dependent, except at very low frequencies. This frequency dependence is illustrated in Figure 3.2 which shows capacitance measured as function of gate bias at  $27^{\circ}$ C with frequency of the ac gate voltage as parameter. At high frequencies, where  $\omega^{-1} > \tau_R$ , minority carries do not follow the ac gate voltage but do follow gate bias changes. The low and high frequency C-V curves are practically identical in accumulation,

depletion, and most of weak inversion because in these regions, minority carrier concentration in the depletion layer is negligibly small compared to majority carrier concentrate. Therefore, it does not matter whether minority carriers respond to the ac voltage. The major difference between low and high frequency C-V curves occurs in weak to strong inversion where minority carrier concentration in the depletion layer becomes comparable to and exceeds majority carrier concentration. Minority carrier effects cannot be neglected in these regions.

**Figure 3.2** Normalized high frequency and low frequency capacitance as a function of gate bias calculated for and acceptor concentration of  $2\times10^{16}$  cm<sup>-3</sup>, oxide thickness 100 nm, and T=300 K (after E. H. Nicollian and J. R. Brews, Ref. 46, p. 156).

Figure 3.3 (a) Low frequency equivalent circuit of MOS, (b) high frequency equivalent circuit of MOS.

Castange and Vapaille [47] were the first to combine high and low frequency C-V curves to obtain a measured Cs. The step eliminates the need for a theoretical computation of  $C_s$  and for measurement of the doping profile of the device. From figure 3.3 it can yield

$$C_{LF} = (C_s + C_{it}) \frac{C_{ox}}{C_{ox} + C_s + C_{it}}$$

(3.1)

$$C_{HF} = \frac{C_{ox}C_s}{C_s + C_{ox}} \tag{3.2}$$

Therefore

$$C_{it} = \left(\frac{1}{C_{LF}} - \frac{1}{C_{ox}}\right)^{-1} - \left(\frac{1}{C_{HF}} - \frac{1}{C_{ox}}\right)^{-1}$$

(3.3)

where  $C_{ox}$  is the oxide capacitor per unit area,  $C_s$  is the silicon surface capacitor per unit area and  $C_{it}$  is interface trap capacitor per unit area. In this way  $C_{it}$  is obtained directly from the measured C-V curves, without the uncertainty introduced by a theoretical  $C_s$  and without uncertainty as to whether  $C_s$  has been calculated for the correct band bending.

Figure 3.4 Combined (a) high frequency (1MHz) and (b) low frequency C-V curves for a MOS capacitor (after E. H. Nicollian and J. R. Brews, Ref. 46, p. 331).

In this thesis, MOS capacitors using Si as well as SiGe were fabricated for studying the plasma induced damage to Si/SiO<sub>2</sub> interface in Si and misfit dislocations strained SiGe material. The high frequency and quasi-static C-V measurements were performed. The plasma induced damages and the interface state densities were derived from C-V measurement results.

# 3.2 Deep Level Transient Spectroscopy (DLTS) Techniques

Luminescence has been widely used with great success in the study of shallow centers. But it misses the deeper non-radiative centers. The deep-level transient spectroscopy (DLTS) is a high-frequency capacitance transient thermal scanning method useful for observing a wide variety of traps in semiconductors. It is sensitive, rapid, and easy to analyze [48]. The DLTS measurement system consists of a sensitive capacitance measurement apparatus with good transient response, one or two pulse generators to make rapid changes in the diode bias, a dual-gated signal integrator, and x-y recorder, and a variable temperature cryostat. The presence of each trap is indicated by a positive or negative peak on a flat baseline plotted as a function of temperature. The heights of these peaks are proportional to their respective trap concentrations. The sign of each peak indicates whether it is due to a majority- or minority-carrier trap, and the positions of the peaks are simply and uniquely determined by the integrator gate setting and the thermal emission properties of the respective traps. By the proper choice of the experimental parameters it is possible to measure the thermal emission rate, activation energy, concentration profile, and capture rate of each trap.

For simplicity, only the situation in p-type material and in an asymmetric  $n^+$ -p diode will be described here. In the quiescent state of the system the diode is reverse biased and observable traps are within the depletion region. Thus the capture rates are zero and the occupation of the level is determined by the thermal emission rates  $e_1$  and  $e_2$  of minority and majority carriers respectively. The steady electron occupation of a level

$$\overline{n_1} = [e_1/(e_1 + e_2)]N \tag{3.4}$$

where N is the concentration of the trap. The capture and thermal emission rates for minority carriers (electrons in this example) are  $c_1$  and  $e_1$  respectively. The capture and thermal emission rates for majority carriers (holes in this example) are  $c_2$  and  $e_2$  respectively. An electron trap has to have  $e_1 >> e_2$  and a hole trap  $e_2 >> e_1$ . The emission rates are proportional to a Boltzman factor and thus depend exponentially on the energy difference between the trap level and the conduction band (electron emission) and the trap level and the valence band (hole emission). Because of this, electron traps tend to be in the upper half of the gap and the hole traps in the lower half.

There are two main types of bias pulses (see Figure 3.5), namely, an injection pulse which momentarily drives the diode into forward bias and injects minority carriers into the region of observation shown in Figure 3.6, and a majority-carrier pulse which momentarily reduces the diode bias and introduces only majority carriers into the region of observation shown in Figure 3.7.

The steady-state electron occupation during a bias pulse is

$$\overline{n_1} = [c_1 / (c_1 + c_2)] N \tag{3.5}$$

where  $c_1$  is the minority-carrier (electron) capture rate proportional to the concentration of injected minority carriers and  $c_2$  is the majority-carrier (hole) recombination rate proportional to the majority-carrier concentration. In all the situations considered, the capture rates are much larger than the emission rates, which can be neglected during the

bias pulse. An injection pulse which introduces a large enough number of electrons so as to make  $c_1 >> c_2$  and overwhelm the trap emptying process will completely fill the trap with electrons; such a pulse is called a saturation injection pulse. A majority-carrier pulse, on the other hand, introduces only holes, and thus tends to empty all traps of electrons, i.e., fill them with holes.

Figure 3.5 Typical time dependence involved in pulsed bias capacitance transients for majority- and minority carrier traps. The upper half is a majority-carrier pulse sequence while the lower half is an injection-pulse sequence (after D. V. Lang, Ref. 48).

Figure 3.6 Injection pulse sequence which is used to produce a capacitance transient for a minority-carrier trap (after D. V. Lang, Ref. 48).

Figure 3.7 Majority-carrier pulse sequence which is used to produce a capacitance transient for a majority-carrier traps (after D. V. Lang, Ref. 48).

The concentration of a trap can be obtained directly from the capacitance change corresponding to completely filling the trap with a saturating injection pulse (in the case of minority-carrier trap) or the largest possible majority-carrier pulse (in the case of a majority-carrier trap). The relationship for an electron trap in a  $n^+$ -p step junction is simply

$$N = 2(\Delta C/C)(N_A - N_D) \tag{3.6}$$

where N is the trap concentration,  $\Delta C$  is the capacitance change at t=0 due to a saturating injection pulse, C is the capacitance of the diode under quiescent reverse-biased condition, and  $N_A$ - $N_D$  is the net acceptor concentration on the p side of the junction where the trap is observed.

The essential feature of DLTS is the ability to set an emission rate window such that the measurement apparatus only responds when it sees a transient with a rate within this window. Thus if the emission rate of a trap is varied by varying the sample temperatures, the instrument will show a response peak at the temperature where the trap emission rate is within the window. The emission rates are thermally activated and by the principle of detailed balance can be given as

$$e_1 = (\sigma_1 \langle v_1 \rangle N_{D1} / g_1) \exp(-\Delta E / kT)$$

(3.7)

where  $\sigma_l$  is the minority-carrier cross section,  $\langle v_l \rangle$  is the mean thermal velocity of minority carriers,  $N_{Dl}$  is the effective density of states in the minority-carrier band,  $g_l$  is

the degeneracy of the trap level, and  $\Delta E$  is the energy separation between the trap level and the minority-carrier band. An exactly similar equation holds for  $e_2$  with subscripts changed from 1 to 2 and with all quantities referring to majority carriers. A standard means of characterizing the depth of a trap is to construct a plot of  $\log e_1$  or  $\log e_2$  vs. 1000/T and to report the slope of the resulting straight line as the activation energy of the trap.

Figure 3.8 Illustration of how a double boxcar is used to define the rate window. The left-hand side shows capacitance transient at various temperatures, while the right-hand side shows the corresponding DLTS signal resulting from using the double boxcar to display the difference between the capacitance at time  $t_1$  and the capacitance at time  $t_2$  as a function of temperature (after D. V. Lang, Ref. 48).

The emission rate corresponding to the maximum of a trap peak observed in a DLTS thermal scan is

$$\tau_{\text{max}} = (t_1 - t_2) [\ln(t_1 / t_2)]^{-1}$$

(3.8)

This can generate one point of  $\log e_1$ - or  $\log e_2$ - vs -1000/T plot. Other points can simply be obtained from other scans made with different gate settings and thus different values of  $\tau_{max}$  and different trap peak positions.

Figure 3.9 Thermal emission rates vs 1000/T determined from the DLTS spectra (after D. V. Lang, Ref. 48).

The DLTS technique has been used in this research for Si MOS capacitor and SiGe/Si p<sup>+</sup>-n diode. It provides the information about process induced electrical defects at the silicon and silicon dioxide interface and detects any process induced defects and misfit dislocations at the Si/SiGe interface. The equations described here have been applied to calculate the trap concentrations and the energy level of these traps.

#### 3.3 Physical Characterization

## 3.3.1 Secondary Ion Mass Spectroscopy (SIMS)

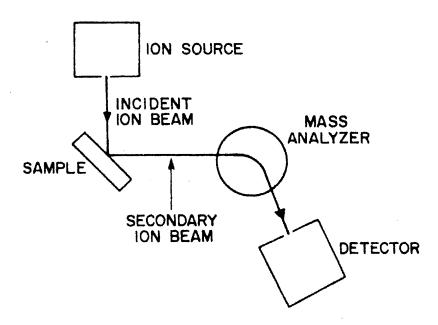

In the SIMS method, an ion beam sputters material off the surface of a sample, and the ionic component is mass analyzed and detected (Figure 3.10). Sputtered ions are extracted and mass analyzed with a magnetic prism or quadrupole analyzer. In a system that uses a magnetic prism, a two-dimensional image of the distribution of an ionic species across the surface can be obtained by directing the secondary ion beam onto a channel plate. In quadrupole instruments the image is formed by recording the changing secondary ion-beam current as primary beam is rastered across the sample surface. The intensity of the detected signal is related to the mass concentration. The mass spectrum can be displayed as a function of time, giving a depth profile of the chemical species.

**Figure 3.10** Schematic diagram of a secondary ion mass spectrometer. (After S. M. Sze. Ref. 24, p. 527).