# **Copyright Warning & Restrictions**

The copyright law of the United States (Title 17, United States Code) governs the making of photocopies or other reproductions of copyrighted material.

Under certain conditions specified in the law, libraries and archives are authorized to furnish a photocopy or other reproduction. One of these specified conditions is that the photocopy or reproduction is not to be "used for any purpose other than private study, scholarship, or research." If a, user makes a request for, or later uses, a photocopy or reproduction for purposes in excess of "fair use" that user may be liable for copyright infringement,

This institution reserves the right to refuse to accept a copying order if, in its judgment, fulfillment of the order would involve violation of copyright law.

Please Note: The author retains the copyright while the New Jersey Institute of Technology reserves the right to distribute this thesis or dissertation

Printing note: If you do not wish to print this page, then select "Pages from: first page # to: last page #" on the print dialog screen

The Van Houten library has removed some of the personal information and all signatures from the approval page and biographical sketches of theses and dissertations in order to protect the identity of NJIT graduates and faculty.

#### ABSTRACT

## MODELING, DESIGN, AND SCHEDULING OF COMPUTER INTEGRATED MANUFACTURING AND DEMANUFACTURING SYSTEMS

## by Ying Tang

This doctoral dissertation work aims to provide a discrete-event system-based methodology for design, implementation, and operation of flexible and agile manufacturing and demanufacturing systems. After a review of the current academic and industrial activities in these fields, a Virtual Production Lines (VPLs) design methodology is proposed to facilitate a Manufacturing Execution System integrated with a shop floor system. A case study on a back-end semiconductor line is performed to demonstrate that the proposed methodology is effective to increase system throughput and decrease tardiness. An adaptive algorithm is proposed to deal with the machine failure and maintenance. To minimize the environmental impacts caused by end-of-life or faulty products, this research addresses the fundamental design and implementation issues of an integrated flexible demanufacturing system (IFDS). In virtue of the success of the VPL design and differences between disassembly and assembly, a systematic approach is developed for disassembly line design. This thesis presents a novel disassembly planning and demanufacturing scheduling method for such a system. Case studies on the disassembly of personal computers are performed illustrating how the proposed approaches work.

# MODELING, DESIGN, AND SCHEDULING OF COMPUTER INTEGRATED MANUFACTURING AND DEMANUFACTURING SYSTEMS

by Ying Tang

A Dissertation Submitted to the Faculty of New Jersey Institute of Technology In Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy in Electrical Engineering

**Department of Electrical and Computer Engineering**

May 2001

Copyright © 2001 by Ying Tang

# ALL RIGHTS RESERVED

## **APPROVAL PAGE**

# MODELING, DESIGN, AND SCHEDULING OF COMPUTER INTEGRATED MANUFACTURING AND DEMANUFACTURING SYSTEMS

## **Ying Tang**

Dr. MengChu Zhou, Dissertation Advisor Professor of Electrical and Computer Engineering, NJIT

Dr. Reggie J. Caudill, Dissertation Co-Advisor Professor of Industrial and Manufacturing Engineering, NJIT

Dr. John D. Carpinelli, Committee Member Associate Professor of ECE & CIS, NJIT

Dr. Edwin Hou, Committee Member Associate Professor of Electrical and Computer Engineering, NJIT

Dr. Robin Qiu, Committee Member Sr. Computer Scientist, GHR Systems, PA

Date

Date

Date

Date

Date

## **BIOGRAPHICAL SKETCH**

Author: Ying Tang

Degree: Doctor of Philosophy

Date: May 2001

## **Undergraduate and Graduate Education:**

- Doctor of Philosophy in Electrical Engineering New Jersey Institute of Technology, Newark, NJ, 2001

- Master of Engineering in Electrical Engineering Northeastern University, Shengyang, P. R. China, 1998

- Bachelor of Engineering in Electrical Engineering Northeastern University, Shengyang, P. R. China, 1996

Major:Electrical Engineering

## **Presentations and Publications:**

- Tang, Y., Zhou, M. C. and Caudill, R., "An Integrated Approach to Disassembly Planning and Demanufacturing Operation," *IEEE Transaction on Robotics & Automation* (accepted), April 2001.

- Tang, Y., Zhou, M. C., Zussman, E. and Caudill, R., "Disassembly modeling, planning, and application", submitted to *Journal of Manufacturing Systems* (in review), revised version, Jan., 2001.

- Tang, Y., Zhou, M. C and R. Qiu, "Virtual Production Line Design for Back-end Semiconductor Manufacturing System," submitted to *IEEE Transaction on Semiconductor Manufacturing* (in review), Jan. 2001

#### **Presentations and Publications:**

- Tang, Y., Zhou, M. C., Zussman, E. and Caudill, R., "Disassembly modeling, planning, and application: a review," *Proceedings of IEEE International Conference on Robotics & Automation*, San Francisco, CA, April 22-28, 2000, pp. 2197-2202.

- Tang, Y., Zhou, M. C. and Caudill, R., "An Integrated Approach to Disassembly and Demanufacturing Operation," *Proceedings of IEEE International Conference on Electronics & the Environment*, San Francisco, CA, May 8-10, 2000, pp. 354-359.

- Tang, Y., Zhou, M. C. and Qiu, R., "Design of Virtual Production Lines in Back-end Semiconductor Manufacturing Systems," *Proceedings of IEEE International Conference on System, Man & Cybernetics*, Nashville, TN, Oct. 8-11, 2000, pp. 1733-1738 (The Best Student Paper Award).

- Tang, Y. and Zhou, M. C., "Design of Reconfigurable Semiconductor Manufacturing Systems with Maintenance and Failure," to appear in *Proceedings of IEEE International Conference on Robotics & Automation*, Seoul, Korea, May 21-26, 2001.

- Tang, Y., Zhou, M. C. and Caudill, R., "A systematic approach to disassembly line design," to appear in *Proceedings of IEEE International Conference on Electronics & the Environment*, Denver, CO, May 7-9, 2001.

- Caudill, R., Zhou, M. C., Hu, J. J., Tang, Y., and Limaye, K., "Demanufacturing System Simulation and Modeling," in *Lifecycle Engineering: A Handbook for Mechanical Engineers*, Chapter 17, pp. 405-428, 2001.

To my beloved family and Gou Gou

#### ACKNOWLEDGEMENT

I would like to express my genuine appreciation to my advisor, Professor MengChu Zhou, and co-advisor, Professor Reggie J. Caudill, for their guidance, support, and friendship through this research.

Special thanks are due to Professor John D. Carpinelli, Professor Edwin Hou, and Dr. Robin Qiu to serve as my doctoral committee.

I would also acknowledge the support of the New Jersey Commission on Science and Technology and such industrial firms as AT&T, IBM, Lucent Technology and Panasonic etc. through the Multi-lifecycle Engineering Research Center (MERC) in NJIT.

This is a perfect opportunity to thank all of these fellows in the Discrete Event System Laboratory and the Multi-lifecycle Engineering Research Center for their assistance, collaboration and friendship in the past three years. Among them are Jianlin Gao, Congzhe Zhang, Meimei Gao, Lori E. Nanton, Lorietta Barnes, and Yanchun Luo.

# TABLE OF CONTENTS

| Cł | lapter | Pa                                              | age |

|----|--------|-------------------------------------------------|-----|

| 1  | INT    | RODUCTION                                       | 1   |

|    | 1.1    | Background                                      | 1   |

|    |        | 1.1.1 Automation for Manufacturing              | 1   |

|    |        | 1.1.2 Environmental Problems and Responses      | 4   |

|    | 1.2    | Motivation                                      | 5   |

|    | 1.3    | Objectives                                      | 7   |

|    | 1.4    | Organization                                    | 8   |

| 2  | LITI   | ERATURE REVIEW                                  | 9   |

|    | 2.1    | Issues in Manufacturing Line Design             | 9   |

|    |        | 2.1.1 Production Planning and Scheduling        | 10  |

|    |        | 2.1.2 Shop-Floor Control                        | 12  |

|    |        | 2.1.3 Manufacturing Execution Systems (MES)     | 14  |

|    | 2.2    | Collection Issues                               | 16  |

|    | 2.3    | Disassembly Process Modeling                    | 17  |

|    |        | 2.3.1 Connection Graph/Component-Fastener Graph | 17  |

|    |        | 2.3.2 Direct Graph                              | 19  |

|    |        | 2.3.3 AND/OR Graph                              | 19  |

|    |        | 2.3.4 Disassembly Petri net                     | 20  |

|    | 2.4    | Disassembly Process Planning (DPP)              | 23  |

|    |        | 2.4.1 Reverse Assembly Approach                 | 25  |

# TABLE OF CONTENTS (Continued)

| Cl | napte | r Pa                                                                                    | age      |

|----|-------|-----------------------------------------------------------------------------------------|----------|

|    |       | 2.4.2 Disassembly Leveling                                                              | 27       |

|    |       | 2.4.3 Optimal Disassembly Sequence                                                      | 29       |

|    | 2.5   | Disassembly System Design                                                               | 38       |

|    | 2.6   | Summary                                                                                 | 40       |

| 3  |       | TUAL PRODUCTION LINE DESIGN FOR BACK-END SEMICONDUCTONUFACTURING SYSTEMS                | )R<br>42 |

|    | 3.1   | Problem Statement in Back-end Semiconductor Manufacturing Systems                       | 43       |

|    | 3.2   | VPL Design                                                                              | 45       |

|    | 3.3   | VPL Operation                                                                           | 50       |

|    | 3.4   | Case Study                                                                              | 53       |

|    |       | 3.4.1 Implementation Method                                                             | 53       |

|    |       | 3.4.2 Simulation Results                                                                | 57       |

|    | 3.5   | Summary                                                                                 | 63       |

| 4  |       | IGN OF RECONFIGURABLE SEMICONDUCTOR MANUFACRUREING<br>TEMS WITH MAINTENANCE AND FAILURE | 64       |

|    | 4.1   | VPL With Periodic Maintenance                                                           | 64       |

|    | 4.2   | VPL With Failure and Maintenance                                                        | 65       |

|    | 4.3   | Adaptive Reconfiguration for VPL                                                        | 67       |

|    | 4.4   | An Example                                                                              | 73       |

|    | 4.5   | Summary                                                                                 | 74       |

# TABLE OF CONTENTS (Continued)

| Chapter |     |       | Page                                                            |      |

|---------|-----|-------|-----------------------------------------------------------------|------|

| 5       |     |       | GRATED APPROACH TO DISASSEMBLY PLANNING AND FACTURING OPERATION | . 76 |

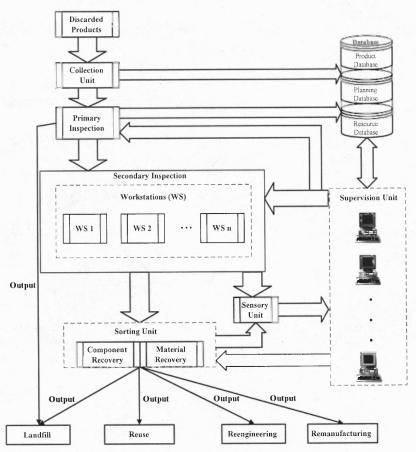

|         | 5.1 | Gener | ric Model for Integrated Flexible Demaufacturing Systems        | . 77 |

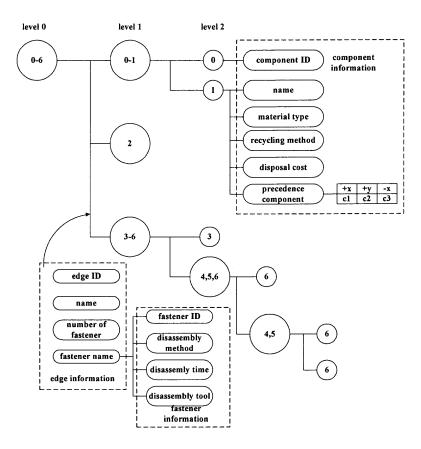

|         |     | 5.1.1 | Database                                                        | . 78 |

|         |     | 5.1.2 | Collection Unit                                                 | . 78 |

|         |     | 5.1.3 | Inspection Unit                                                 | . 79 |

|         |     | 5.1.4 | Disassembly Workstation                                         | . 79 |

|         |     | 5.1.5 | Sorting Unit                                                    | . 80 |

|         |     | 5.1.6 | Sensory Unit                                                    | . 81 |

|         |     | 5.1.7 | Supervision Unit                                                | . 81 |

|         | 5.2 | Mode  | ling Disassembly Processes                                      | . 81 |

|         |     | 5.2.1 | Petri nets (PNs)                                                | . 82 |

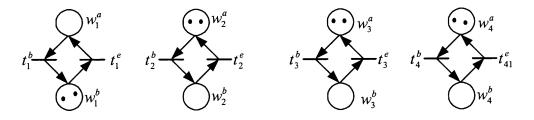

|         |     | 5.2.2 | Workstation Petri net (WPN)                                     | . 83 |

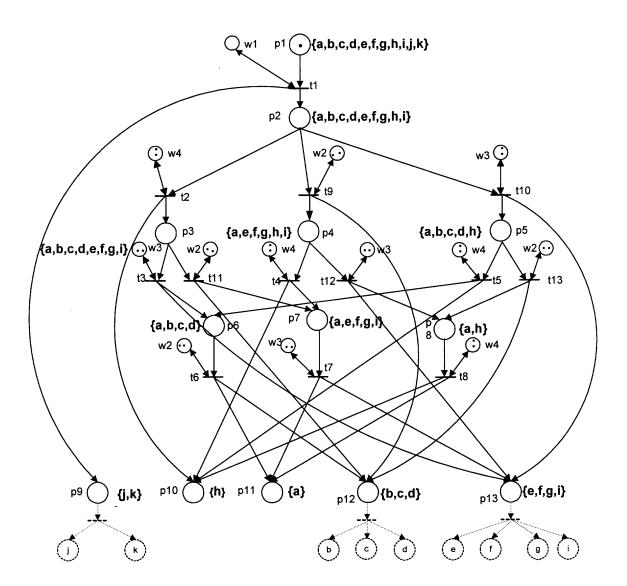

|         |     | 5.2.3 | Product Petri net (PPN)                                         | . 84 |

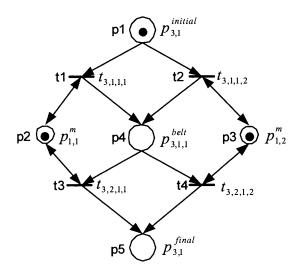

|         |     | 5.2.4 | Scheduling Petri net (SPN)                                      | . 86 |

|         | 5.3 | Disas | sembly Process Planning and Machine Scheduling                  | . 89 |

|         |     | 5.3.1 | Planning Algorithm                                              | . 91 |

|         |     | 5.3.2 | Scheduling Algorithm                                            | . 94 |

|         | 5.4 | Case  | Study                                                           | . 96 |

|         |     | 5.4.1 | Implementation Method                                           | . 96 |

# TABLE OF CONTENTS (Continued)

| Cł            | Chapter |                                               | Page |

|---------------|---------|-----------------------------------------------|------|

|               |         | 5.4.2 Simulation Results                      | 102  |

|               | 5.5     | Summary                                       | 106  |

| 6             | A S     | YSTEMATIC APPROACH TO DISASSEMBLY LINE DESIGN | 109  |

|               | 6.1     | Problem Statement                             | 110  |

|               | 6.2     | Disassembly Line Design                       | 111  |

|               | 6.3     | An Example                                    | 115  |

|               | 6.4     | Summary                                       | 117  |

| 7             | CON     | NCLUSIONS AND FUTURE RESEARCH                 | 119  |

|               | 7.1     | Contributions and Limitations                 | 119  |

|               | 7.2     | Future Research                               | 123  |

| REFERENCES 12 |         |                                               | 126  |

# LIST OF TABLES

| Tab | le                                                            | Page |

|-----|---------------------------------------------------------------|------|

| 2.1 | The comparison of methodologies for modeling disassembly      | 24   |

| 2.2 | Rules in the Component-Fastener graph                         | 32   |

| 2.3 | Definition in WP methodology                                  | 36   |

| 2.4 | Constitution and function of a robotic system for disassembly | 40   |

| 3.1 | The input data for ten work-orders                            | 61   |

| 3.2 | The comparison of the system throughput                       | 62   |

| 4.1 | The input data for two work-orders                            | 73   |

| 4.2 | The input data for workstations                               | 74   |

| 4.3 | The computation results                                       | 75   |

| 5.1 | Component List for a PERSONAL COMPUTER                        | 86   |

| 5.2 | Explanation for typical places and transitions in SPN         | 90   |

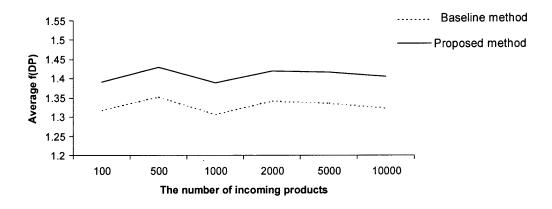

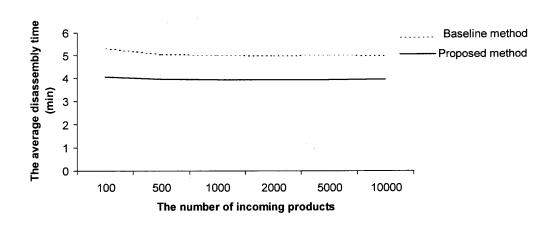

| 5.3 | The comparison of the average disassembly time                | 107  |

| 5.4 | The comparison of the value gain                              | 107  |

| 6.1 | The input data for three demands                              | 116  |

| 6.2 | The input inventory information                               | 116  |

| 6.3 | The input data for workstations                               | 116  |

| 6.4 | The comparison of the system throughputs and value gains      | 117  |

|  | LIST | OF | FIGURES |  |

|--|------|----|---------|--|

|--|------|----|---------|--|

| Figu | ire                                                                                            | Page |

|------|------------------------------------------------------------------------------------------------|------|

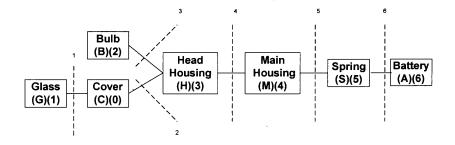

| 2.1  | A handlight and Its connection graph                                                           | 18   |

| 2.2  | Directed Graph of feasible disassembly sequences for a handlight                               | 20   |

| 2.3  | The AND/OR graph for a handlight                                                               | 21   |

| 2.4  | Disassembly Petri Net for a handlight                                                          | 22   |

| 2.5  | The cut-sets of the graph of connections for the handlight                                     | 26   |

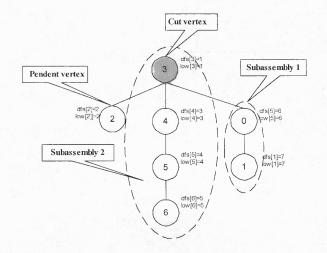

| 2.6  | Depth first tree with subassemblies' identification for the graph in Fig. 2.1                  | 31   |

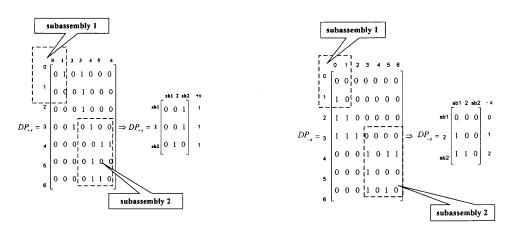

| 2.7  | Disassembly precedence matrix for the handlight                                                | 32   |

| 2.8  | Final disassembly tree                                                                         | 33   |

| 2.9  | Removal influence graph at $t = 1$ and $t = 2$ for a handlight with $C_x = \{4\}$              | 36   |

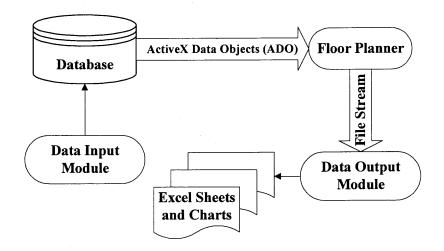

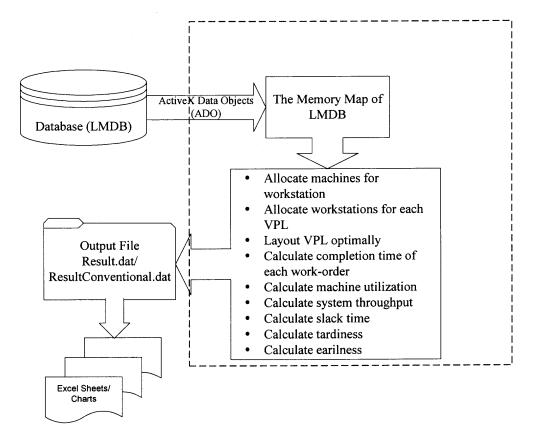

| 3.1  | The system software modules                                                                    | 54   |

| 3.2  | Simulation software interface                                                                  | 55   |

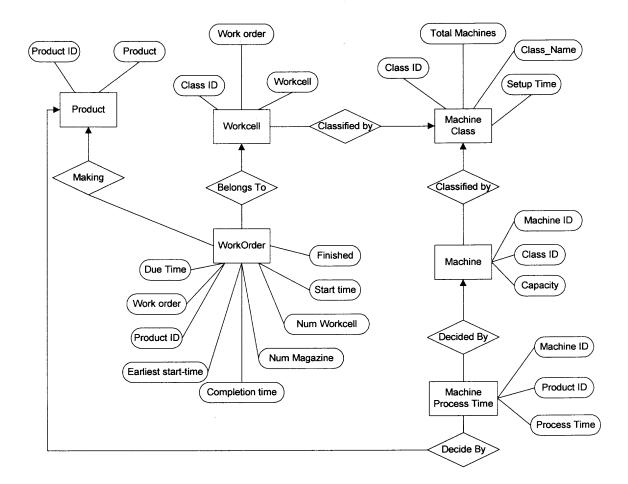

| 3.3  | E-R schema diagram of database (LMDB)                                                          | 56   |

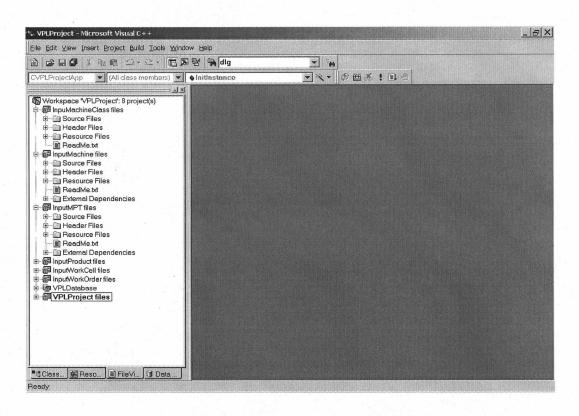

| 3.4  | VPL simulation software workspace                                                              | 57   |

| 3.5  | VPLDatabase Project                                                                            | 58   |

| 3.6  | The diagram of VPLProject (in dashed box)                                                      | 59   |

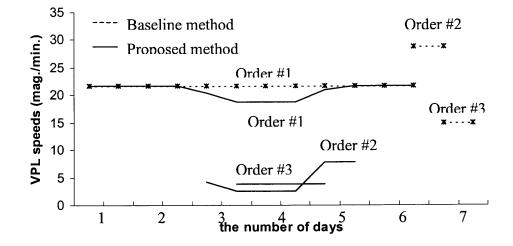

| 3.7  | VPL speeds for different cases when the system processes three work-orders                     | 61   |

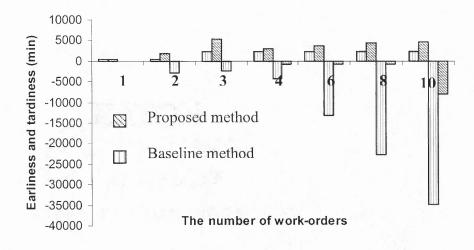

| 3.8  | Earliness and tardiness comparsion between proposed and baseline ethods                        | 62   |

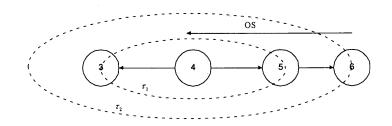

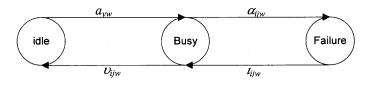

| 4.1  | State transition model of the $i^{th}$ machine in the $j^{th}$ workstation of the $w^{th}$ VPL | 66   |

| 5.1  | A Generic Model for Integrated Flexible Demanufacturing System (IFDS)                          | 80   |

| 5.2  | A simple example of WPN with four workstations                                                 | 84   |

| 5.3  | A simple example of PPN for a personal computer                                                | 87   |

# LIST OF FIGURES (Continued)

| Figu | re P                                                                                  | age |

|------|---------------------------------------------------------------------------------------|-----|

| 5.4  | SPN <sub>31</sub> for a personal computer                                             | 89  |

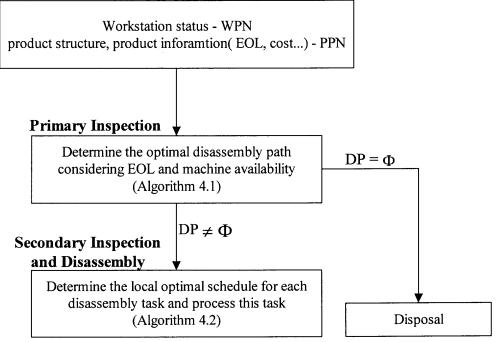

| 5.5  | Logic of disassembly planning and machine scheduling                                  | 90  |

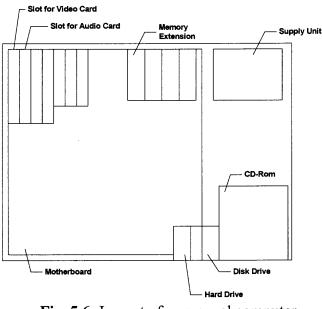

| 5.6  | Layout of a personal computer                                                         | 98  |

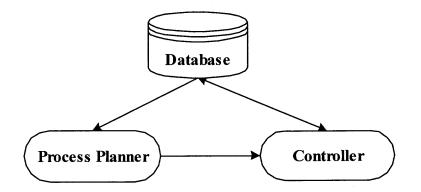

| 5.7  | The System Software Module                                                            | 99  |

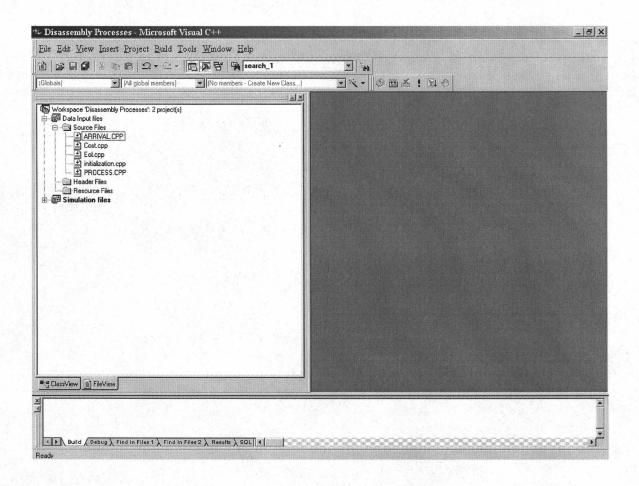

| 5.8  | Disassembly Processes Simulation software workspace                                   | 100 |

| 5.9  | Simulation Project                                                                    | 101 |

| 5.10 | Experimental results of J <sub>3</sub> process plan                                   | 104 |

| 5.11 | Value gain for 10000 personal computers through the proposed and the baseline methods | 105 |

| 5.12 | Disassembly time for 10000 personal computers through the proposed                    | 106 |

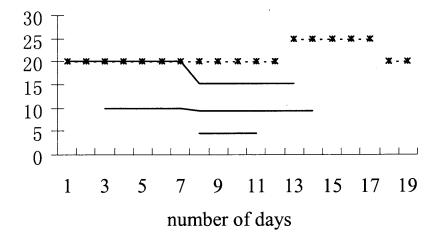

| 6.1  | DLs' speed for baseline (dotted lines) and proposed cases (solid lines)               | 117 |

# LIST OF ABBREVIATIONS

| DFX:     | design for X                               |

|----------|--------------------------------------------|

| DL:      | disassembly line                           |

| DP:      | disassembly path                           |

| $DP_d$ : | disassembly precedence matrices            |

| DPN:     | disassembly Petri nets                     |

| DPP:     | disassembly process planning               |

| DS:      | disassembly sequence                       |

| EOL:     | end-of-life                                |

| E-R      | entity-relationship                        |

| IFDS:    | Integrated flexible demanufacturing system |

| LMDB:    | lot manager database                       |

| MES:     | manufacturing execution systems            |

| MFC:     | microsoft fundation class                  |

| VC:      | visual C++                                 |

| PN:      | Petri nets                                 |

| PPN:     | product Petri nets                         |

| SPN:     | scheduling petri nets                      |

| SQL:     | structured query language                  |

| VPL:     | virtual production line                    |

| WP:      | wave propagation                           |

| WPN:     | workstation Petri nets                     |

|          |                                            |

#### LIST OF SYMBOLS

- $\hat{\theta}$ : The point estimate of output variable Y based on n observations

- $\hat{V}(\hat{\theta})$ : standard error of the point estimate  $\hat{\theta}$

- $\Lambda(p)$ : delay time associated with resource place p in SPN, where p represents a product, assembly or part

- $\pi(p)$ : EOL value function assigned to place p in PPN

- $\lambda(t)$ : a conservative time function associated with transition *t* in *PPN*, where *t* represents a disassembly operation

- $\rho(t)$ : probability value assigned to transition t in DPN, meaning the success rate of the operation represented by t

- $\delta(t)$ : a decision value associated with transition t in DPN/PPN

- $\Gamma(t)$ : processing time associated with transition t in SPN

- $\sigma(w)$ : the cost value for the time delay caused by workstation w

- $\varsigma$ : a firing vector of the transition

- $\pi^{B}_{ijw}$ : the probabilities of the busy condition of the *i*<sup>th</sup> machine in the *j*<sup>th</sup> workstation of the *w*<sup>th</sup> VPL

- $\pi^{F}_{ijw}$ : the probabilities of the failure condition of the *i*<sup>th</sup> machine in the *j*<sup>th</sup> workstation of the *w*<sup>th</sup> VPL

- $\pi^{I}_{ijw}$ : the probabilities of the idle condition of the  $i^{th}$  machine in the  $j^{th}$  workstation of the  $w^{th}$  VPL

- $\xi_i$ : the priority of the *i*<sup>th</sup> input inventory

- $\xi_{ik}$ : the priority of the *i*<sup>th</sup> machine in the *k*<sup>th</sup> class of machine pool (*M<sub>k</sub>*)

| $\eta_i$ :          | the total disassembly time for the $i^{th}$ job                                                |

|---------------------|------------------------------------------------------------------------------------------------|

| $	au_{ijw}$ :       | the $i^{th}$ machine/worker's processing time in the $j^{th}$ workcell of the $w^{th}$ VPL/DL  |

| t <sub>ijw</sub> :  | the maintenance rate of the $i^{th}$ machine in the $j^{th}$ workstation of the $w^{th}$ VPL   |

| $lpha_{ijw}$ :      | the failure rate of the $i^{th}$ machine in the $j^{th}$ workcell of the $w^{th}$ VPL          |

| $\beta_{ijw}$ :     | the percentage time of the $i^{th}$ machine/worker dedicated to the $j^{th}$ workstation of    |

|                     | the w <sup>th</sup> VPL                                                                        |

| D <sub>ijw</sub> :  | the speed of the $i^{th}$ machine in the $j^{th}$ workstation of the $w^{th}$ VPL              |

| Yik:                | the execution time of the disassembly process for the $i^{th}$ job in the $k^{th}$ workstation |

| $\mathcal{G}_{j}$ : | Number of machines assigned to the $j^{th}$ workstation                                        |

| Ejw:                | number of machines and workers in the $j^{th}$ workstation of the $w^{th}$ VPL/DL              |

| $\sigma_{jw}$ :     | maintenance periodicity of machines in the $j^{th}$ workstation of the $w^{th}$ VPL            |

| $\phi_k$ :          | number of idle machines/workers of the $k^{th}$ class                                          |

| $\psi_w(t)$ :       | earliness of the $w^{th}$ VPL/DL at time $t$                                                   |

| $\zeta_w(t)$ :      | slack time of the $w^{th}$ VPL/DL at time $t$                                                  |

| $\varphi_w(t)$ :    | tardiness of the $w^{th}$ VPL/DL at time $t$                                                   |

| $\overline{a}_w$ :  | the maximal real-time speed of workstations in the $w^{th}$ VPL/DL                             |

| $\underline{a}_w$ : | the minimal real-time speed of workstations in the $w^{th}$ VPL/DL                             |

| <i>Y</i>  :         | the cardinality of set Y                                                                       |

|                     |                                                                                                |

| <i>A</i> :         | incidence matrix                                                                                    |

|--------------------|-----------------------------------------------------------------------------------------------------|

| $a_{jw}$ :         | average speed of the $j^{th}$ workstation in the $w^{th}$ VPL/DL                                    |

| $a_w$ :            | the desired speed of the $w^{th}$ VPL/DL                                                            |

| <i>B</i> :         | exchange rate between cost and time delay                                                           |

| <i>c</i> :         | a cost vector corresponding to all disassembly tasks or transitions                                 |

| $C_i$ :            | set of final parts after the disassembly of each product in the $i^{th}$ input inventory            |

| C <sub>ijw</sub> : | the $i^{th}$ machine/worker's capacity in the $j^{th}$ workstation of the $w^{th}$ VPL/DL           |

| <i>ck</i> :        | the cost of the disassembly activity $k$ or its corresponding transition                            |

| END(w):            | completion time of the w <sup>th</sup> work-order/demand                                            |

| <i>d(p)</i> :      | disassembly value of a place $p$ in $PPN$                                                           |

| d(t):              | disassembly value of a transition t in PPN                                                          |

| <i>D</i> :         | set of VPLs/DLs with tardiness                                                                      |

| Date(t):           | check time of the $w^{th}$ work-order/demand                                                        |

| $D_{ijw}$ :        | the transition rate matrix for the $i^{th}$ machine in the $j^{th}$ workstation of the $w^{th}$ VPL |

| $d_{ik}$ :         | the mean failure rate of the $i^{th}$ machine in the $k^{th}$ class                                 |

| Due(w):            | due time of the $w^{th}$ work-order/demand                                                          |

| $D_w$ :            | set of parts in the $w^{th}$ demand                                                                 |

| <i>E</i> :         | set of VPLs/DLs with earliness except that it means a node-adjacency matrix in                      |

|                    | Chapter 2                                                                                           |

| EST(w):            | earliest start time of the $w^{th}$ work-order/demand                                               |

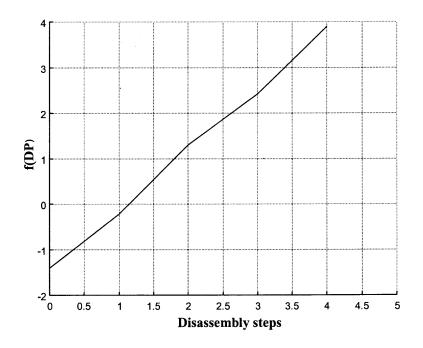

| <i>f(DP)</i> :     | the value gain in a DP                                                                              |

| f: machine utilization | n |

|------------------------|---|

|------------------------|---|

- *F*: a fastener matrix

- $F_i$ : the value gain in the disassembly path for the products in the *i*<sup>th</sup> input inventory

- $g_{\alpha/2,(n-1)}$  the 100(1- $\alpha$ )% percentage point of a t-distributed with (n-1) degrees of freedom

- g: system throughput

- G: directed/undirected graph

- h(t): cost value function associated with transition t in PPN

- *H:* the set of workstations a product goes through

- *I*: input function that defines the set of directed arcs from places to transitions in PN

- $I_k$ : the  $k^{th}$  class of idle machine pools

- J: a set of jobs

- k: machine/worker class index

- $K_{jw}$ : the allowed maximum failure rate of machines in the  $j^{th}$  workstation of the  $w^{th}$ VPL before its removal from the system for repair

- M: marking vector in PN

- $m_{ik}$ : the mass of input

- $M_k$ : the  $k^{th}$  class of machine pools

- $m_{ok}$ : the mass of output

- $m_w$ : the number of types of parts in the  $w^{th}$  DL

- $N_{jw}$ : total number of the  $j^{th}$  type of parts in the  $w^{th}$  DL

- $n_w(t)$ : number of finished magazines in VPL or product in DL in the  $w^{th}$  workorder/demand at time t

- $N_w$ : total number of magazines in VPL or product in DL in the  $w^{th}$  work-order/demand

- O: output function that defines the set of directed arcs from places to transitions in PN

- $O_i$ : the number of parts in the  $i^{th}$  output inventory

$$O_{ijkz}$$

: the j<sup>th</sup> task of the i<sup>th</sup> job being performed by the k<sup>th</sup> machine in the z<sup>th</sup> workstation

- P: a finite set of places in PN

- $p_{ik:}$  specific price of input

- $p_{ok:}$  specific price of output

- Q: A set of places standing for product, subassemblies or components in PPN

- q: a place in PPN

- r(w): time delay function associated with a workstation-available place w

- *R*: set of resource places in *SPN*

- $r_{ijw}$ : the repair rate of the  $i^{th}$  machine in the  $j^{th}$  workstation of the  $w^{th}$  VPL

- $R_k$ : the  $k^{th}$  class of repair machine pools

- $r_k$ : the revenue of activity k

- S: set of status places in SPN

- ST(w): actual start time of the  $w^{th}$  work-order/demand

- *t*: a transition in *PN*

- *T*: a finite set of transitions in *PN*

- $T^b$ : the set of the transitions whose firings begin the operations in a WPN

- $T^e$ : the set of the transitions whose firings end operations in a WPN

- $T_w$ : production time for the  $w^{th}$  work-order/demand

- *u*: the number of VPLs/DLs in the system

- U: set of edges

- *v*: bottlenck workstation index

- *V*: set of verticies

- $V^2$ : sample variance of output variable Y based on n obseavations

- w VPL/DL index

- W: available machine pools in PPN

- $W^a$ : available machine pools in WPN

- $W^b$ : busy machine pools in WPN

- *x:* VPL index

- $x_{ijw}$  the maintenance (repair) time for the *i*<sup>th</sup> machine in the *j*<sup>th</sup> workstation of the *w*<sup>th</sup> VPL

- $X_w$ : number of workstations in the  $w^{th}$  VPL/DL

- Y output variable

- *y:* Workstation index

- Z: input inventory set for products received VPL without getting immediate repair

## **CHAPTER 1**

#### **INTRODUCTION**

#### 1.1 Background

#### **1.1.1** Automation for Manufacturing

Manufacturing is a vital source of wealth in every industrialized nation [Rembold *et al.*, 1993]. Technically, it is the application of physical and chemical processes to alter the geometry, properties, and/or appearance of a given starting material to make parts or products [Groover, 1996]. From the economic point of view, manufacturing adds value to the material by changing its shape or properties or by combining it with other materials that may have been similarly altered.

Over the past decades, a widely diverse array of developments and inventions laid the groundwork for modern-day automation. Economic and social considerations also encourage the adoption of advanced industrial automation, where the design and production operations are integrated into a completely computerized manufacturing system [Ouellette *et al.*, 1983].

Several factors act together to make production automation a viable and attractive alternative to manual methods of manufacture [Groover, 1980]:

(1) Increased productivity: Automation of manufacturing operations holds the promise of increasing the productivity of labor. Without automation, the practical and realistic output is directly limited by the capabilities of the manufacturing personnel. High production rates are achieved with advanced technology.

- (2) High cost of labor: Automation has frequently been used to replace humans in tasks that are monotonous, physically tiring, dangerous or harmful to health. As a result, higher investment in automated equipment has become economically justifiable to replace manual operations.

- (3) Labor shortage: In many advanced nations there has been a general shortage of labor. Labor shortage also stimulates the development of automation as a substitute for labor.

- (4) Safety: Automation can meet social needs by permitting machines to perform unpleasant jobs, where a human operator would be exposed to hazardous conditions or toxic fumes etc.

- (5) High cost of energy: The high cost of energy in manufacturing results in the need for greater efficiency in using the energy. Automated manufacturing processes may be operated at the optimum conditions for energy conservation. This is especially meaningful considering human beings' requirements for a sustainable economy.

- (6) High cost of raw materials: Automated manufacturing operations can reduce scrap losses and maximize efficient use of the feedstock and raw materials.

- (7) Improved product quality: Automated operations not only produce parts at faster rates than their manual counterparts do, but also they produce parts that are consistently of a high standard of quality.

- (8) Reduced manufacturing lead-time: Automation allows a manufacturer to reduce the time between customer order and product delivery.

- (9) Reduction of in-process inventory: Holding large inventories of work-in-process represents a significant cost to a manufacturer because it ties up capital. Automation

makes it possible to reduce work-in-process to a minimum by reducing the time a workpiece spends in the factory.

With the invention of computers, it was quickly realized that computers had an enormous potential for becoming the focal point in future automation endeavors. Conventional automation was based primarily on sophisticated mechanical machinery controlled by cams and levers or electrical switching gear [Rembold *et al.*, 1985]. In general, the equipment was conceived to perform fixed manufacturing assignments, so the degree of automation that can be achieved with these tools was rather limited. The original automation endeavors were directed primarily toward the improvement of the machining capabilities of the manufacturing equipment, where computers play an ever-increasing role.

Within the last few years, competitive pressure has forced many companies to adapt a plant quickly to changing market conditions. This problem led to the concept of computer-integrated manufacturing (CIM). CIM comprises product design, production planning, production control, production processes, quality control, production equipment, and plant facilities [Rembold *et al.*, 1985]. A conceived CIM system can be built well through the following developments [Rembold *et al.*, 1993]:

- The development of universal models of a product, manufacturing system and manufacturing operations;

- The development of simulation systems for all manufacturing processes and configuration means to set up a desired manufacturing environment;

- The investigation of new management information systems to support the decisionmaking functions of management to control and operate a plant; and

• The exploitation of artificial intelligence (AI) methods for manufacturing.

#### **1.1.2 Environmental Problems and Responses**

During the industrial revolution, environmental issues were not well addressed when products were designed, manufactured and consumed. This gives rise to environmental problems, the first of which is a deteriorating natural resource base [Reijnders, 1995]. Today's information society requires thousands of different products that ultimately result in billions of tons of materials discarded, most of which end up in landfills [Gungor and Gupta, 1998]. Rapid technological advances, especially in the area of information technology, make more and more otherwise functioning-well products obsolete in an accelerated pace. Many types of pollution are increasing. In practice over-exploitation of renewable resources, like the massive burning of woods and soil erosion, contributes substantially to pollution, giving rise to, among other things, greenhouse warming and eutrophication of surface wasters [Reijnders, 1995].

As a consequence of both fast depletion of the raw materials and an increasing amount of different forms of waste, customers have become aware of their environment and the potential problems that can be created by neglecting it. Therefore, they have started to show more interest in "green products" and taken their environmentally responsible use and consumption of the products. This has become an incentive for manufacturers to design and market environmentally friendly products to gain advantage in the marketing platform against their competitors.

The manufacturers and consumers are also forced by government laws and legislation to pay more attention to the environmental issues. In many countries, the environmental protection laws, regulations, and tax implications are already in effect [Crognale, 1996]. For example, a German legislation mandated that as of January 1, 1994, manufacturers and retailers must take back and salvage products at the end of their lives and must design new ones with recycling in mind [Owen, 1993]. The European community has passed laws prohibiting the disposal more than 15% of an automotive product by the year 2002 and this percentage drops to 5% in the year 2015 [Nasr, 1997]. Japan proposed take-back legislation for electronic products, which was enacted in 1998 and comes into force on April 1<sup>st</sup> 2001 [Furuhjelm *et al.*, 2000].

#### **1.2 Motivation**

As shown in Section 1.1, with the fast development of computers and information technologies, computer-integrated manufacturing was coined to provide a new concept and direction to grow automatic manufacturing [Harrington, 1973]. As industry progresses, more products are made available for consumers. At the same time, more and more diversified models are appearing to suit individual tastes. This environment places a premium on agile manufacturing methods, which allow new manufacturing systems to be designed and planned within shorter and shorter lead-times and have quick reaction to a new market situation. In addition, product lifecycles are becoming shorter as a result of rapid technological advancement and international competition [Nof *et al.*, 1997]. This accelerating trend requires the redesign and re-planning of manufacturing systems more frequently and within shorter lead-times. The flexibility of manufacturing systems can take a number of forms, including [O'Grady, 1986]:

(1) Volume flexibility: the ability to handle changes in the production volume of a part;

- (2) Re-routing flexibility: the ability to have a number of routes through the system for each part in order to enable, for example, machine breakdowns to be dealt with; and

- (3) Part flexibility: the ability to handle a wide variety of parts including the ability quickly to adopt the system to handle a new part.

Due to the mammoth needs of the semiconductor market, semiconductormanufacturing systems have been given a special attention. Since it is a business of high investment, high technology, and fierce competition, there is a significant amount of risk involved in the industry [Liao *et al.*, 1996]. The current manufacturing systems in semiconductor industries are designed based on a clustering of all of the equipment on the shop floor into predefined physical production lines, where each production line is capable of fabricating a group of products. If the part-mix for a production line changes, the system has to accommodate the change by making relevant adjustments in the production line [Qiu and Wysk, 1999]. Moreover, there exist high uncertainties in operations due to machine failures and fluctuation of yield rates [Liao *et al.*, 1996]. Thus, agility of production lines is a fundamental requirement for semiconductor manufacturers to stay competitive, which is a part of our focus in this research.

During the industrial revolution, environmental issues were not well addressed when products were designed, manufactured and consumed. Over the last few years, industries, governments and academia have paid much more attention on environmentally conscious manufacturing and product recovery because of the escalating deterioration of the environment. Some of efforts focus on the design stage of products, and is referred to as Design for 'X' (DFX) where X stands for a design under consideration such as Manufacturability, Testability, Installability, Compliance, Reliability, and Disassembly. [Gatenby and Foo, 1990]. Since the biggest damage to the environment often occurs when products complete their useful life, understanding and developing techniques for end-of-life (EOL) management of the products by means of product/material recovery are extremely crucial [Thierry *et al.*, 1995]. Such companies as IBM, Sony, Phillips, Panasonic, and Lucent Technologies have made their significant research and technology effort, and made EOL product recovery economically profitable and environmentally responsible. As an integral part of a product life cycle, the demanufacturing, a process to disassemble products and then reuse, remanufacture, reengineer, or dispose of them, has been introduced [Shyamsundar *et al.*, 1997]. Disassembly gains much attention in demanufacturing processes. It serves to extract hazardous substances out of the systems, to reutilize valuable raw materials and components in products, and to minimize the amount of waste that must be disposed of in special purpose landfills. Disassembly modeling, process planning and system design are all considered in our work.

#### 1.3 Objectives

The goal of this research is to provide a discrete-event system-based methodology for design, implementation, and operation of flexible and agile manufacturing and demanfacturing systems. Specific objectives are to:

- Provide formal and mathematical models for products, manufacturing and demanufacturing processes problems;

- (2) Provide systematic and efficient methodologies to solve these problems;

- (3) Perform case studies for semiconductor manufacturing systems; and

- (4) Perform case studies for demanufacturing of obsolete consumer electronic products.

#### **1.4 Organization**

This dissertation is organized as follows. Chapter 2 makes a literature review for the current research issues in automated semiconductor manufacturing and demanufacturing systems. Chapter 3 develops a virtual production line (VPL) design methodology for back-end semiconductor manufacturing systems. In order to deal with the uncertainties in operations due to machine maintenance and failures, an adaptive methodology for the reconfiguration of VPLs is addressed in Chapter 4.

To obtain the better tradeoff between the benefit of disassembly processes and the resource requirement, an integrated approach to disassembly planning and demanufacturing operation is presented in Chapter 5. Important concepts of the methodology are defined and a case study on the disassembly of a batch of obsolete personal computers is provided to demonstrate the significance of this method. Based on the concept of virtual production line design in manufacturing systems and the similarity between manufacturing and demanufacturing, a solution methodology for the disassembly line-balancing is proposed and demonstrated in Chapter 6. Finally, the conclusions and some future research directions are presented in Chapter 7.

#### **CHAPTER 2**

#### LITERATURE REVIEW

As mentioned in Chapter 1, due to the growing demands from the markets and customers, the basic ideas of automatic operation have merged with more and more new concepts and technologies for manufacturing and demanufacturing systems today. Significant research effort is being carried out in industries and academia addressing various problems in these areas. This chapter reviews the major issues in these fields.

#### 2.1 Issues in Manufacturing Line Design

Increasing global competition has made many business leaders and policy makers turn their attention to such critical issues as productivity and quality [Zhou and Venkatesh, 1998a]. One of the frequently prescribed remedies for the problem of decreased productivity and declining quality is the automation of factories. More specifically, technologies such as computer integrated manufacturing, robotics, and flexible manufacturing systems are the focal points of much research and exploration.

In order to meet customers' preferences and changing market demands, how to improve the flexibility and agility of manufacturing systems becomes extremely crucial. This involves two important issues: line balancing and resource planning. Bartholdi and Eisenstein (1996) introduced the concept of "operation of bucket brigades" for manual lines, used for example in the automotive industry. Rekiek *et al.* (1998) proposed the balance for ordering to treat line balancing and order variants simultaneously. Ham

9

(1996) presented a model for determining the optimal routing that maintains workload balance for flexible flow lines. A recent survey of balancing and resource planning for assembly lines was presented in [Rekiek *et al.*, 1999]. The University of Michigan Engineering Research Center has been developing a science base for a new generation of manufacturing systems-Reconfigurable Manufacturing Systems. This system is the one designed at the outset for rapid change in its structure, as well as its hardware and software components, in order to accommodate rapid adjustment of production capacity and functionality needed in response to new market demands [Koren *et al.*, 1998]. The National Research Council (1998) identified Reconfigurable Manufacturing Systems as the number one priority technology in manufacturing for the Year 2020.

Although the history of the semiconductor industry is not long compared with other manufacturing industries, semiconductor manufacturing has become one of the most competitive fields [Kim *et al.*, 1998]. It requires extremely high capital investment. Moreover, in the risky environment of semiconductor manufacturing systems, it is quite complicated and difficult for the production planning and shop-floor control because of reentrant product flows, diverse types of equipment, complex production processes and unpredictable yield and equipment downtime [Uzsoy, *et al.*, 1992].

#### 2.1.1 Production Planning and Scheduling

Wein (1998) has pointed out that scheduling has a significant impact on the performance of semiconductor wafer fabrication. Liao *et al.* (1996) presented the development of a daily scheduling tool for a research and development pilot line of semiconductor wafer fabrication using Lagrangian relaxation and network flow techniques. Golovin (1986) discussed issues in production planning and scheduling in the semiconductor industry and pointed out the difficulty of selecting an appropriate objective function. A hierarchical approach such as that suggested by Bitran *et al.* (1981, 1982) was advocated. Their approach is to solve an aggregate production planning problem on a rolling horizon basis, implementing only the first period decisions that are then disaggregated into decisions for the shorter-term operational scheduling problems such as what particular products to run and what order to run them in.

A planning system developed by Siemens that has been implemented in a development wafer fab was described in [Hadavi, 1994]. Their system explicitly addresses the dynamic nature of the production environment by localizing rescheduling as much as possible and making minimal resource commitments to maintain maximum flexibility. Order due dates and workcenter capacities are both embedded into constraint sets that correspond to particular time windows. When a new order arrives, a feasibility analysis module examines the resources required by the order and determines whether or not it is possible to produce the order. Then, the order is passed to a detailed scheduling module that works down the hierarchy of time windows to schedule the order into specific quarters, months, days and shifts.

Leachman (1986) gave a corporate-level production planning model for the semiconductor industry. The manufacturing process is divided into the stages of fab, probe, assembly and test, linked by inventories. The model includes multiple facilities, and treats entire production processes in each plant as integral entities. Computerized routines create the input files of an aggregate planning model and generate the linear programming formulation. The solution to this linear program yields a production plan at the process level of detail, which is validated by management. If it is invalid, the input

data is revised and the process repeated until an acceptable plan is generated. Once an aggregate plan has been obtained, it is disaggregated by solving a number of linear programs to divide the volume of production planned for each product family over the individual products. The output from the model is a capacity-feasible weekly start schedule for the various facilities in a company.

Based on work initiated by Kimemia and Gershwin (1983), Bai *et al.* (1990) proposed a hierarchical production planning and scheduling system for a semiconductor wafer fab. The key issue of their methodology is classifying the events that take place in a wafer fab according to the frequency of their occurrence and whether or not they are controllable. At each level, decisions are made in a way that satisfies the capacity constraints that are appropriate to that level and that meets objectives determined at a higher level.

#### 2.1.2 Shop-Floor Control

Due to their complexity, the most common approach to shop-floor control problems in practice has been the use of dispatching rules [Uzsoy *et al.*, 1994]. Kim *et al.* (1998) considered multiple products with different due dates and different process flows. New dispatching rules for the objective of minimizing the mean tardiness of the orders were developed. Glassey and Resende (1988) pointed out that due to the extensive use of computer-aided manufacturing systems dispatching and lot release decisions can be made based on global information. They also developed a dispatching rule to complement the Starvation Avoidance input regulation policy. To minimize the average queue in front of the bottleneck, the method uses dynamically updated estimates of lead times and queue sizes, and gives higher priority to lots that are expected to encounter a shorter queue at

their next visit there. Focusing on the effect of lot sizes on cycle time performance, an order release policy for a semiconductor packaging line was proposed [Chandra and Gupta, 1992]. They also suggested a pull type synchronization mechanism to link the assembly and burn-in operations. The effects of these procedures on system behavior were analyzed using a simulation model and managerial implications of the results were discussed.

Adams *et al.* (1988) proposed the shifting bottleneck procedure for a job-shop scheduling problem. The entire approach can be outlined as follows: (a) divide the facility into a number of workcenters that consist of individual machines, set of parallel identical machines, or batch processing machines; (b) use a disjunctive graph to represent the problem; (c) schedule each workcenter and rank the workcenters in order of criticality; (d) capture the interactions between the workcenters already scheduled and not yet scheduled; and (e) resequence workcenters that have already scheduled using the new information obtained in Step (d). If all workcenters are scheduled, stop. Else, go to Step (c). The approximation approach is efficient to solve the minimum makespan problem of job shop scheduling and capable of handling re-entrant product flows, sequence-dependent setup times and different types of machines.

Ikura and Gimple (1986) provided an algorithm to determine whether there is a schedule in which all jobs are completed by their due dates for the cases where jobs arriving later have later due dates and all jobs have identical processing times. Ahmadi *et al.* (1992) considered the problems of minimizing mean flow time and makespan in flowshops containing batch and unit-capacity machines, assuming that all jobs have identical provided polynomial-time

algorithms as the solutions to these problems. Lee *et al.* (1992) considered tardiness problems and presented polynomial-time algorithms for minimizing the number of tardy jobs on a single batch processing machine under such assumptions as constant processing time, agreeable release times and due dates.

Based on optimal control policies for two-machine flowshops, Lou and Kager (1989) proposed a two-boundary control methodology in which the fab is modeled as a virtual flowshop and each processing step is represented by workstation. This method is found to be more robust to changes in demand and to maintain low working-in-process and production surplus.

# 2.1.3 Manufacturing Execution Systems (MES)

A salient point emerging from the above review is that the relationship between production planning and shop floor control has been almost ignored. However, production-planning decisions that set goals for the shop affect the effectiveness of shop floor control policies with each other [Uzsoy, *et al.*, 1994]. Manufacturing Execution Systems (MES) fill the gap between production planning and shop floor control and have drawn increasing attention from the manufacturing industry for its success in reducing cycle time, lowing inventory, and increasing on-time delivery. MES includes a rich set of products [Scott, 1996] for:

- Factory and process modeling;

- Specification management;

- Work in process tracking;

- Resource management;

- Quality monitoring and control;

- Plant management decision support;

- Distribution of manufacturing instruction and equipment recipes for operators and machines;

- Real-time dispatching;

- Shop floor data collection;

- Production reporting, performance analysis and query tools;

- Corporate-wide planning;

- Cost analysis; and

- Final capacity scheduling.

Use the distributed object-oriented technique, Cheng *et al.* (1998) proposed a systematic approach to develop a computer-integrated MES framework that is open, modularized, distributed, configurable, interoperable, collaborative, and maintainable. Each of components of the MES framework is developed by inheriting a proper design pattern that is considered as the basic designs for the architecture, framework messages, and interfaces of this component to interoperate and collaborate with the other components.

Kane (1996) presented an Advanced Manufacturing Systems, to reconstruct manufacturing process flows in Xilinx, Inc. Programmed logic encoded in the application as part of business rules, lot characteristic, and flow input requirements allows the system to dynamically associate lots to process flows while taking advantage of real time changes in process flow designs and the current accumulation of lots characteristics. The generic design of the higher level flows using subroutine calls to lower levels preserves the reusability of a large body of flow designs. Baliga (1998) pointed out that the winning strategy for semiconductor manufacturing companies was to implement highly responsive and efficient production lines using advanced management, computer, and control technologies. A synthesis of the advantages of MES was addressed in [Scott, 1996].

# 2.2 Collection Issues

With the rapid development of the industrial society, environmental issues received more and more attention in the recent years. The collection of the used items and/or their packages is one of the major issues in a product recovery environment [Livingstone and Sparks, 1994; Rembert, 1997]. Collection decisions involve location selection of collection centers (where retired products are collected and stored prior to distribution to demanufacturing facility); layout design of collection centers (including material handling and storage); and transportation (designing the transportation networks to bring used products from many origins to a single collection center) [Gungor and Gupta, 1999a]. Flow of used products back into the product demanufacturing facility is known as reverse distribution [Kooi et al., 1996]. The high degree of uncertainty inherent in the collection activities makes it more complicated. The life cycle of distribution items and their environmental, financial and operational effects are analyzed in [Flapper, 1996, 1995; Lambert and Splinter, 1996]. Some researchers considered returnable distribution items in their studies [Goh and Varaprasad, 1986; Kelle and Silver, 1989; Kroon and Vrijens, 1995].

# 2.3 Disassembly Process Modeling

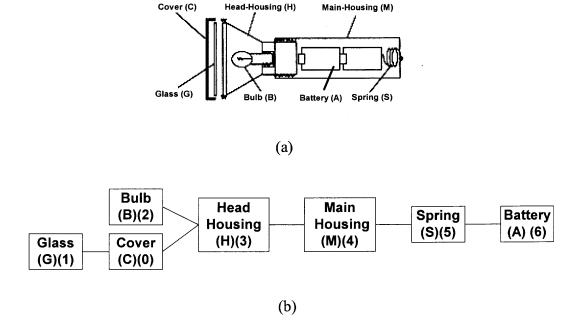

In a product disassembly process, choosing the representation of disassembly sequences is an important decision not only in creating a disassembly sequence planner but also in designing an intelligent control system for a disassembly system. The objective is to efficiently represent all feasible and complete disassembly sequences with correct precedence relations. Recently, a number of modeling strategies have been proposed. They can be categorized into four types, Component-Fastener Graph [Zhang, H. C. and Kuo, T. C., 1996, 1997], directed graph [Homem de Mello and Sanderson, 1990], AND/OR graph [Homem de Mello and Sanderson, 1990, 1991], and Disassembly Petri Net (DPN) [Cao and Sanderson, 1995, 1998; Moore *et al.*, 1998a, 1998b; Suzuki *et al.*, 1993; Zussman and Zhou, 1998-2000]. This work uses a handlight shown in Fig. 2.1 (a) as an example to illustrate these representations and concepts. To compare them, |Y| is used to denote the cardinality of set Y, and n to the number of components in a product.

## 2.3.1 Connection Graph/Component-Fastener Graph

The component-fastener graph is an undirected graph, which can be generated according to the information from CAD packages. In such a graph G=(V, U), vertices  $V=\{v_1, v_2, ..., v_n\}$  represent components; and edges  $U=\{u_1, u_2, ..., u_m\}$  denote a group of assembly relationships among components where m is the number of edges. It is clear that the upper bound for |V| is n. A node-adjacency matrix E and a fastener matrix F are obtained as follows:

$E = (E_{ij})_{n \times n}$ , where  $E_{ij} = 1$  if component i is connected with component j; otherwise 0.

$F = (F_{ij})_{n \times n}$ , where  $F_{ij} = k$  if component i is connected with component j by k fasteners; otherwise 0.

Fig. 2.1: (a) A handlight and (b) Its connection graph

With such a graph representation, the problem of identifying the optimal disassembly sequence is easily transformed into a graph search problem, which is addressed in Section II. The component-fastener graph for a handlight is essentially identical to the connection graph in Fig. 2.1(b). Its E and F matrices are shown below. Note that the node-adjacency matrix E is redundant.

|     | 0 | 1 | 0 | 1 | 0 | 0 | 0 |     | [0 | 2 | 0 | 2 | 0 | 0 | 0] |

|-----|---|---|---|---|---|---|---|-----|----|---|---|---|---|---|----|

|     | 1 | 0 | 0 | 0 | 0 | 0 | 0 |     | 2  | 0 | 0 | 0 | 0 | 0 | 0  |

|     | 0 | 0 | 0 | 1 | 0 | 0 | 0 |     | 0  | 0 | 0 | 1 | 0 | 0 | 0  |

| E = | 1 | 0 | 1 | 0 | 1 | 0 | 0 | F = | 2  | 0 | 1 | 0 | 1 | 0 | 0  |

|     | 0 | 0 | 0 | 1 | 0 | 1 | 0 |     | 0  | 0 | 0 | 1 | 0 | 1 | 0  |

|     | 0 | 0 | 0 | 0 | 1 | 0 | 1 |     | 0  | 0 | 0 | 0 | 1 | 0 | 1  |

|     | 0 | 0 | 0 | 0 | 0 | 1 | 0 |     | 0  | 0 | 0 | 0 | 0 | 1 | 0  |

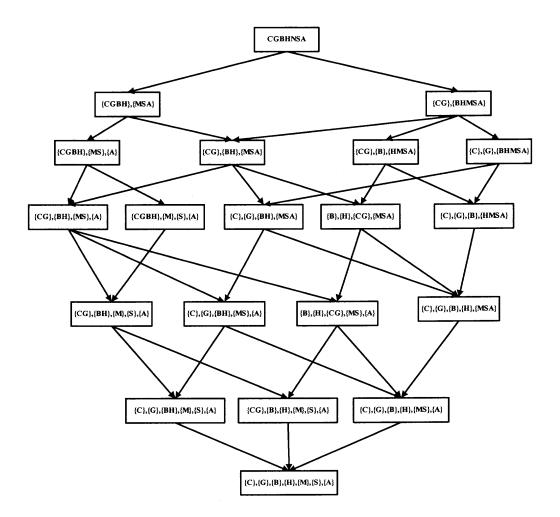

# 2.3.2 Direct Graph

A directed graph can be used to represent the set of all disassembly sequences, and formally defined as G=(V, U). The nodes in V correspond to the possible states of the disassembly process; the edges in U corresponding to disassembly tasks are ordered pairs of nodes. The worst case to configure this graph happens when every part is connected to every other part. Thus, the size of this graph is [Homem de Mello and Sanderson, 1990]:

$$|V| = partitions (n) = \sum_{i=0}^{n-1} partitions (n-1-i) \binom{n-1}{i}$$

where partitions (0) = 1

Fig. 2.2 shows the directed graph of feasible disassembly sequences for the product shown in Fig. 2.1 and |V| = 20.

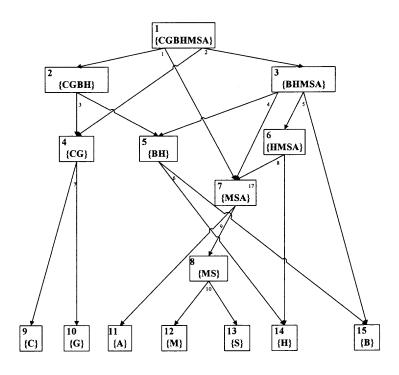

# 2.3.3 AND/OR Graph

The AND/OR graph of feasible disassembly sequences is also a directed graph, which is represented by G=(V, U), where each node in V can be a product, part or subassembly, and hyperarcs in U represent the set of feasible disassembly tasks. A node i representing a product or subassembly can have k (k≥1) disassembly methods, forming an OR-relation; if a method disassembles i into u (u>2) nodes (parts and/or subassemblies), u arcs link node i to those u nodes, forming an AND-relation. The maximum number of nodes in this graph is  $|V| = 2^n$ -1 when every component is connected with every other component. Figure 2.3 shows the AND/OR graph for a handlight. Figures. 2.2-2.3 give a simple proof that the AND/OR graph needs less storage space for nodes and edges than the directed graph. In fact, Fig. 2.2 has 20 nodes and 33 edges while Fig. 2.3 has 15 nodes and 20 edges. This advantage of AND/OR graphs becomes greater as the number of parts increases [Homem de Mello and Sanderson, 1990].

Fig. 2.2: Directed Graph of feasible disassembly sequences for a handlight

Based on the previous work [Homem de Mello and Sanderson, 1990, 1991], Cao and Sanderson proposed the AND/OR net, which extends the AND/OR graph representation to incorporate system mechanisms and devices [Cao and Sanderson, 1998].

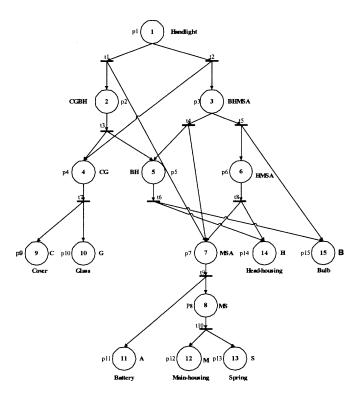

# 2.3.4 Disassembly Petri Net

For the purpose of the analysis of the network, it is convenient to represent each disassembly process and system resources respectively. Bipartite multi-folded

Disassembly Petri Nets (DPN) have such advantages. The below definition is due to [Zussman and Zhou, 1998].

Fig. 2.3: The AND/OR graph for a handlight

DPN=(P, T, I, O,  $m_0$ ,  $\pi$ ,  $\tau$ ,  $\delta$ ,  $\rho$ ) where:

- P-places. There is a place called a product or root denoted by  $p_1$  with no input arc, a set of places called subassembly, a set of places called leaves denoted by P', each of which has no output arcs.

- T-transitions, each of which represents disassembly and has at most one input arc and at least two output arcs.

- I:  $P \times T \rightarrow \{0, 1\}$  is an input function that defines the set of directed arcs from P to T.

- O:  $P \times T \rightarrow \{0, 1\}$  is an input function representing directed arcs from T to P.

- $m_0: P \rightarrow \{0, 1, 2, \ldots\}$  is an initial marking,  $m_0 (p_1)=1$  and  $m_0 (p)=0, \forall p \in P-\{p_1\}$ .

$\pi$ -a value/cost function assigned to a place (end-of-life value or cost of the product, part or subassemblies a place represents).

h-a cost function assigned to a transition.

- $\delta$ -a decision value associated with a transition.

- $\rho$ -[0,1] probability value associated with a transition representing the success rate of its corresponding disassembly operation.

Figure 2.4 gives an example DPN for a handlight. Compared to Fig. 2.3, it is clear that the DPN is a variant of an AND/OR graph. A token game and association of pre-firing and post-firing values with transitions facilitate adaptive dynamic disassembly planning.

Fig. 2.4: Disassembly Petri Net for a handlight

Cao and Sanderson (1998) presented a method for mapping an AND/OR net to a Petri net. They also proposed Fuzzy Petri nets by introducing fuzzy members and complex fuzzy reasoning functions into the ordinary Petri nets to facilitate the search for correct operation sequences [Cao and Sanderson, 1995].

Through analysis of these four methodologies, the comparison results for their advantages and disadvantages are concluded in Table 2.1. It is clear that each method has its special application, and a representation framework itself is not sufficient for automatic disassembly because an intelligent system must be able to supervise these plans and derive new and vital information for further disassembly plans and operations.

## 2.4 Disassembly Process Planning (DPP)

Disassembly process planning (DPP) finds a sequence of disassembly tasks that begins with a product to be disassembled and terminates with all of the parts of interest disconnected. Since a sequence can drastically affect the efficiency of a disassembly process, for instant, some sequences require less change of tools and disassembly time, and include simpler and more reliable operations than others, disassembly planning is an important research issue. In the earliest studies, some researchers treated the disassembly problem as an assembly one to derive the best strategies in review of disassembly as the logic reverse of a feasible assembly regardless of whether the reverse operation itself is feasible or not [Cao and Sanderson, 1995, 1998; Homem de Mello and Sanderson, 1991; Suzuki *et al.*, 1993]. Even though the similiar approach may be used for the disassembly planning, the changes of products during the utilization phase can result in great uncertainty about product structures and conditions, which sometimes disables such approaches valid for assembly planning making disassembly automation more difficult.

| Table 2.1 The | comparison | of methodo | logies for | r modeling | disassembly |

|---------------|------------|------------|------------|------------|-------------|

|               |            |            |            |            |             |

| Models                               | Advantages                                                                 |                                                                                                                                                                                                                                            |                                                                                   |                                                        | Disadvantages                                          |                         |

|--------------------------------------|----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|-------------------------|

| Component-                           |                                                                            | rectly from the CAD package.                                                                                                                                                                                                               |                                                                                   | Be incapabl                                            | le of modeling                                         | [116]                   |

| fastener graph                       |                                                                            | to show the fastener information.                                                                                                                                                                                                          |                                                                                   | disassembly t                                          | disassembly tasks                                      |                         |

|                                      | 3.Use graph sear                                                           | ch algorithm to get optimal DS.                                                                                                                                                                                                            |                                                                                   |                                                        |                                                        |                         |

| Directed graph                       | Contain both disassembly                                                   | 1. Represent the set of all disassembly sequence                                                                                                                                                                                           |                                                                                   | Require large<br>space for nodes<br>and edges          | [49]                                                   |                         |

| AND/OR graph                         | and assembly<br>tasks where all<br>disassembly<br>tasks are<br>reversible. | <ol> <li>1.Encompass all possible disassembly sequence<br/>number of nodes and edges.</li> <li>2.Explicitly shows the possibility of simultaneo<br/>disassembly tasks.</li> <li>3.Use the heuristic algorithm to get optimal DS</li> </ol> | Require<br>component<br>and fastener<br>information                               | Difficult to<br>integrate with<br>resource<br>modeling | [48]<br>[49]<br>[64] <sup>*</sup><br>[75] <sup>*</sup> |                         |

| Disassembly PN-1<br>[Suzuki et al.]  |                                                                            | 1.Represent each subassembly and each task<br>respectively.Use LP to derive<br>the optimal plan.2.It is easy to integrate with resources to form                                                                                           |                                                                                   | to construct<br>the graph.                             | No end-of-life<br>value<br>incorporated                | [15]<br>[16]<br>[100]   |

| Disassembly PN-2<br>[Zussman et al.] |                                                                            | <ul> <li>a comprehensive model for process<br/>planning and control.</li> <li>3.Explicitly shows the possibility of<br/>simultaneous execution of disassembly<br/>tasks.</li> </ul>                                                        | Consider the end-<br>of-life value and<br>easy to implement<br>adaptive planning. |                                                        | Lacking LP<br>formulation and<br>solution              | [122]<br>[123]<br>[124] |

\* The disassembly graph in [64] and the product tree in [75] are based on AND/OR graph + In this column, the paper numbers correspond to the numbers in the REFERENCE List to save space.

Thus, there is a growing need to develop new methodologies to specifically address the disassembly characteristics. This includes two important decisions: (1) how far to disassemble a certain product; and (2) how to find an optimal or near-optimal DS.

# 2.4.1 Reverse Assembly Approach

Homem de Mello and Sanderson (1991) transformed the problem of generating assembly sequences into that of generating disassembly sequences and presented a correct and complete algorithm as a solution. The basic idea underlying the approach is to enumerate the decompositions of an assembly and to select those decompositions which are feasible and correspond to a hyperarc in the AND/OR graph connecting a node to two nodes. The decompositions are obtained by enumerating the cut-sets of the assembly's graph of connection.

Using the handlight example shown in Fig. 2.1, two algorithms *Get-Feasible-Decomposition* and *Generate-And-Or-Graph* are examined [Homem de Mello and Sanderson, 1991b]. First, *Get-Feasible-Decomposition* computes the graph of connections shown in Fig. 2.1(b) and all its cut-sets indicated in Fig. 2.5. The analysis of those cut-sets indicates the feasible decompositions. The first cut-set does not yield a feasible decomposition since it is impossible to extract the glass before the cover is disassembled. The second cut-set yields a feasible decomposition since it is feasible to separate the subassembly consisting of glass and cover, and the subassembly made up of the other five parts. Similarly, the fourth cut-set yields feasible decomposition while the others not. Then, with such information, the AND/OR graph of disassembly sequences can be obtained as shown in Fig. 2.3 by using algorithm *Generate-And-Or-Graph*, which

takes the relational model of an assembly, and returns AND/OR graph representation of all disassembly sequences for that assembly.

Homem de Mello and Sanderson (1991) also presented a heuristic-search algorithm to derive the optimal disassembly process plans by weighting hyperarcs in proportional to the difficulty of their corresponding operations. It is clear that each plan corresponds to a tree in the AND/OR graph. Thus to get the best disassembly plan is just to compute the total cost of each tree from a node, recursively, as

- Zero, if the node has no leaving hyperarcs; or

- The sum of the weights of the hyperarc leaving the node and the cost of the trees from the successor nodes.

Then, the less the cost of a tree, the better the plan corresponding to such a tree. For this evaluation function, the search for the best DS can be conducted using algorithms such as AO<sup>\*</sup> [Nilsson, 1980]. The amount of computation involved in disassembly planning depends not only on the number of parts and how they are interconnected, but also on the structure of the AND/OR graph. At the worst case, such search algorithms have the exponential computational complexity in terms of n.

Fig. 2.5: The cut-sets of the graph of connections for the handlight

Suzuki et al. (1993) assumed assembly operations and disassembly operations are invertible each other. Then, they modeled the disassembly network using Petri net and

proved that Linear Programming technique can be used to find the optimal task sequences for DPN as follows:

**Minimize:**  $c^{T} \varsigma$

subject to:  $A\varsigma = M - M_0$

where c is a cost vector corresponding to each disassembly task or a transition,  $\varsigma$  is a transition vector, A is the incidence matrix of a DPN, M is a final marking and M<sub>0</sub> is an initial marking. The (0, 1)-solution-constrain can be removed owing to the graph structural properties of DPN. This illustration made it possible for us to use more powerful algorithms (e.g., simplex algorithm and interior point algorithm) than AO<sup>\*</sup> to find an optimal DS. Note that interior or point algorithm runs at polynomial time with respect to the number of variables (i.e., the number of transitions in this case). Since the number of transitions is exponential to n, the algorithm still has the exponential complexity in terms of n.

# 2.4.2 Disassembly Leveling

While complete disassembly may provide the best way of minimizing the damage to the environment, some studies has concluded that with the current recycling techniques and market prices, complete disassembly is not always profitable since the cost of disassembly may be more than the market and environment benefit. Thus, disassemblyleveling problem becomes an important issue. It decides a disassembly level to which the product of interest is disassembled to keep profitability and environmental features of the process at a desired level. In the literature, qualitative and quantitative knowledge of the disassembly processes are combined with economic factors to obtain the good tradeoff between the benefit of a disassembly process and the resource requirement [Gungor and Gupta, 1998].

Lambert (1997) discussed the determination of disassembly level and sequence for a product. A criterion for the optimum disassembly is the maximum revenue of the activities. The revenue  $r_k$  of activity k is defined as:

$$r_k = \sum_{o} (p_{ok} \cdot m_{ok}) - (p_{ik} \cdot m_{ik}) - c_k$$