## **Copyright Warning & Restrictions**

The copyright law of the United States (Title 17, United States Code) governs the making of photocopies or other reproductions of copyrighted material.

Under certain conditions specified in the law, libraries and archives are authorized to furnish a photocopy or other reproduction. One of these specified conditions is that the photocopy or reproduction is not to be "used for any purpose other than private study, scholarship, or research." If a, user makes a request for, or later uses, a photocopy or reproduction for purposes in excess of "fair use" that user may be liable for copyright infringement,

This institution reserves the right to refuse to accept a copying order if, in its judgment, fulfillment of the order would involve violation of copyright law.

Please Note: The author retains the copyright while the New Jersey Institute of Technology reserves the right to distribute this thesis or dissertation

Printing note: If you do not wish to print this page, then select "Pages from: first page # to: last page #" on the print dialog screen

The Van Houten library has removed some of the personal information and all signatures from the approval page and biographical sketches of theses and dissertations in order to protect the identity of NJIT graduates and faculty.

#### ABSTRACT

## GATED MULTI-CYCLE INTEGRATION (GMCI) FOR FOCAL PLANE ARRAY (FPA) APPLICATIONS

### by Haijiang Ou

In this thesis, the model and the theory of gated multi-cycle integration (GMCI) were first developed specifically for focal plane array dealing with repetitive or modulated image. The operational modes of GMCI include gated integration (GI), phase sensitive integration (PSI), multi-point summation, multi-point subtraction, multi-sample averaging and some of their combinations. Thus, the analytic theory of GMCI somehow unifies the theories of gated integration, phase sensitive detection, multiple summation and average. PSI works with background and/or dark current subtraction. As a result, the storage well of a pixel is mainly used for signal integration even if there exists a strong background. Thus, the signal-to-noise ratio, the dynamic range, the sensitivity of the detection and the noise equivalent temperature are greatly improved. For a storage well of  $10^6$  electrons, the sensitivity of the FPA operated at PSI mode could be improved by 3 orders. In addition, the transmission windows of PSI peak at odd harmonics of the modulation frequency, and therefore, the detector's 1/f and other low frequency noise can be attenuated.

A switched capacitor integrator was designed and fabricated with HP-0.5µm CMOS processing to demonstrate the feasibility of GMCI. The primary experimental results showed that the minimum detectable signal could be 5 orders less than the background, which is impossible for the conventional readout methods employed by current staring FPAs. The fixed patterns associated with switching charge injection,

feedthrough, offset voltage of operational amplifier were addressed and suppressed by taking the differentia of two sampled voltages that correspond to signal integrations with 180° phase difference while keeping the same fixed pattern. GMCI, operated at PSI with multiple averages, is expected to become a powerful method in dealing with repetitive weak image swamped by strong background.

## GATED MULTI-CYCLE INTEGRATION (GMCI) FOR FOCAL PLANE ARRAY (FPA) APPLICATIONS

By Haijiang Ou

A Dissertation

Submitted to the Faculty of

New Jersey Institute of Technology and

Rutgers, the State University of New Jersey-Newark

In Partial Fulfillment of the Requirements for the Degree of

Doctor of Philosophy in Applied Physics

**Federated Physics Department**

May 2001

Copyright © 2001 by Haijiang Ou ALL RIGHTS RESERVED

### APPROVAL PAGE

## GATED MULTI-CYCLE INTEGRATION (GMCI) FOR FOCAL PLANE ARRAY APPLICATIONS

Haijiang Ou

| Dr. Ken K. Chin, Dissertation Advisor<br>Professor of Physics, NJIT                                   | Date |

|-------------------------------------------------------------------------------------------------------|------|

| Dr. Haiming Wang, Committee Member<br>Professor of Physics, NJIT                                      | Date |

| Dr. John Hensel, Committee Member Distinguished Research Professor of Physics, NJIT                   | Date |

| Dr. Zheng Wu, Committee Member<br>Professor of Physics, Rutgers University-Newark, NJ                 | Date |

| Dr. Clyde Bethea, Committee Member Member of Technical Staff, Lucent Bell Laboratory, Murray Hill, NJ | Date |

#### **BIOGRAPHCAL SKETCH**

Author:

Haijiang Ou

Degree:

Doctor of Philosophy

Data:

May 2001

### **Undergraduate and Graduate Education:**

- Doctor of Philosophy in Applied Physics, New Jersey Institute of Technology and Rutgers, Newark, NJ, 2001

- Master of Science in Electrical Engineering, Columbia University, NY, 1998

- Master of Science in Applied Physics,

Shanghai Institute of Metallurgy,

Chinese Academy of Sciences, Shanghai, P. R. China, 1987

- Bachelor of Science in Physics Hangzhou University, Hangzhou, P. R. China, 1984

Major:

**Applied Physics**

#### Presentation, Publications, and Patent:

Haijiang Ou, and Ken K. Chin,

"Gated multi-cycle integrator (GMCI): a readout circuit for repetitive imaging of FPA," *SPIE*, Vol. 4369, *symp*. on infrared technology and applications XXVII, Orlando, Florida, 16-20 April 2001

Ken K. Chin and Haijiang Ou,

"Correlated modulation imaging (CMI)," patent filed, 2000

Ken K. Chin and Haijiang Ou,

"Circuitries for multi-cycle integration focal plane array (MIFPA)," patent filed, 2000

Wei Long, Haijiang Ou, Jame M. Kuo, and Ken K. Chin, "Dual-material gate (DMG) field effect transistor," *IEEE Trans. Electron Devices*, Vol. ED-46, p.865, 1999

To my family

#### ACKNOWLEDGMENT

The work presented in this dissertation was initially suggested, continually supported, and frequently inspired by my advisor, Ken K. Chin. I am deeply grateful for his guidance, his perseverance, his encouragement and his friendship.

I have greatly benefited from the access to the L-Edit and Top-Spice owned by discovery semiconductors, Inc., NJ. Only with these softwares could I smoothly go through the simulation and layout of the switched capacitor integrator. I would like to thank Mr. Abhay Joshi, the CEO, and Mr. Xinde Wang, my former colleague and a senior Engineer of the company, for their kind help in layout and simulation and encouragement in the research of getting image swamped by strong background. Furthermore I am strongly indebted to Mr. Xinde Wang for his guidance in the chip's measurement.

I owe many thanks to Prof. Durga Misra, Department of Electrical and Computer Engineering, NJIT, for his kindness in allowing me to use his MOSIS account for the chip fabrication.

Thanks also go to Mr. Peter Sabato, my current colleague in AOC, for his help in revising the final version of this dissertation.

I benefited greatly from the advice and insights of the members of my Dissertation and Oral Examination Committees-Profs. Zheng Wu from Rutgers, Clyde Bethea from Bell Labs, John Hensel, Haiming Wang and Ken Chin from NJIT.

Last, but not least, I would especially like to thank my wife Jie You, my daughter Amy Ou and the rest of my friends and family for being there when I need them.

## **TABLE OF CONTENTS**

| Cł | hapter Page |         |                                                | Page |

|----|-------------|---------|------------------------------------------------|------|

| 1  | RES         | EARCH   | H BACKGROUND                                   | 1    |

|    | 1.1         | Introdu | uction                                         | 1    |

|    | 1.2         | Structu | ure of FPA                                     | 3    |

|    | 1.3         | A Brie  | f History of FPAs                              | 5    |

|    | 1.4         | Perform | mance of FPA                                   | 9    |

|    |             | 1.4.1   | Array Format                                   | 10   |

|    |             | 1.4.2   | Pixel Size                                     | 10   |

|    |             | 1.4.3   | Storage Capacity                               | 10   |

|    |             | 1.4.4   | Signal Conversion Gain.                        | 10   |

|    |             | 1.4.5   | Noise                                          | 11   |

|    |             | 1.4.6   | Dynamic Range                                  | 12   |

|    |             | 1.4.7   | Integration Time                               | 12   |

|    |             | 1.4.8   | Noise Equivalent Temperature Difference (NEΔT) | 12   |

|    |             | 1.4.9   | Maximum Frame Rate                             | 13   |

|    |             | 1.4.10  | Maximum Data Rate                              | 13   |

|    |             | 1.4.11  | Operating Temperature                          | 13   |

|    |             | 1.4.12  | Power Dissipation                              | 14   |

|    | 1.5         | Comm    | nonly Used Input Cell Readout Circuits         | 14   |

|    |             | 1.5.1   | Direct Detector Integration (DDI)              | 15   |

|    |             | 1.5.2   | Direct Injection (DI)                          | 16   |

| Cł | apter | •      | P                                                          | age |

|----|-------|--------|------------------------------------------------------------|-----|

|    |       | 1.5.3  | Buffered Direct Injection (BDI)                            | 18  |

|    |       | 1.5.4  | Gate Modulation Input (GMI)                                | 19  |

|    |       | 1.5.5  | Capacitive Transimpedance Amplifier (CTIA)                 | 20  |

|    | 1.6   | Resear | rches on Background Subtraction                            | 21  |

|    |       | 1.6.1  | Skimming and Partitioning                                  | 22  |

|    |       | 1.6.2  | Dynamic Current Mirror Buffered Direct Injection (DCM-BDI) | 23  |

|    |       | 1.6.3  | Current Memory                                             | 24  |

|    |       | 1.6.4  | Correlated Readout (CR)                                    | 26  |

|    | 1.7   | Demai  | nds for Repetitive Imaging                                 | 28  |

|    | 1.8   | Outlin | e of This Thesis                                           | 29  |

| 2  | THE   | ORY C  | OF GATED MULTI-CYCLE INTEGRATION (GMCI)                    | 30  |

|    | 2.1   | Introd | uction                                                     | 30  |

|    | 2.2   | Basic  | Concept of Lock-in Amplifier                               | 32  |

|    | 2.3   | Gated  | Integration                                                | 36  |

|    | 2.4   | Theor  | y of Gated Multi-Cycle Integration                         | 37  |

|    |       | 2.4.1  | General Model of GMCI                                      | 38  |

|    |       | 2.4.2  | Demodulation Function and Its Fourier Transform            | 39  |

|    |       | 2.4.3  | General Output of GMCI                                     | 40  |

|    |       | 2.4.4  | Base Gain Function of GMCI                                 | 42  |

|    |       | 2.4.5  | Transmission Window of GMCI                                | 43  |

|    |       | 2.4.6  | Average Signal under the Synchronized Integration          | 45  |

| Cl | hapter | •         |                                                      | Page |

|----|--------|-----------|------------------------------------------------------|------|

|    |        | 2.4.7     | Power Noise and the Equivalent Bandwidth             | 46   |

|    |        | 2.4.8     | Signal-to-Noise Ratio                                | . 47 |

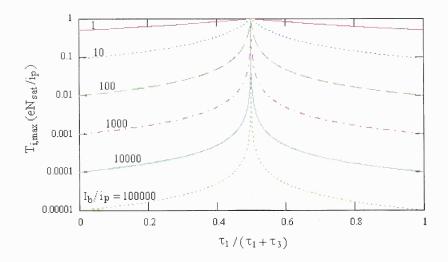

|    |        | 2.4.9     | Maximum Integration Time                             | . 48 |

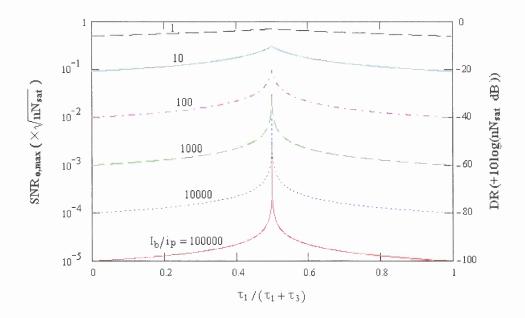

|    |        | 2.4.10    | Maximum SNR <sub>o</sub> and Dynamic Range           | . 49 |

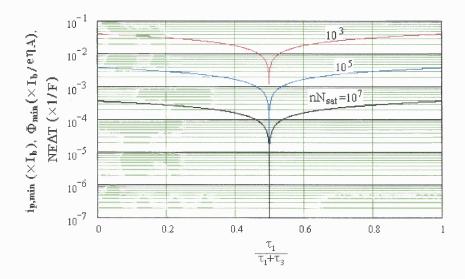

|    |        | 2.4.11    | Optimum Sensitivity                                  | . 50 |

|    |        | 2.4.12    | Special Integration Modes                            | . 53 |

|    | 2.5    | Summ      | ation                                                | . 66 |

| 3  | A SW   | /ITCHE    | ED-CAPACITOR INTEGRATOR (SCI); ONE VERSION OF GMCI   | . 67 |

|    | 3.1    | Introdu   | action                                               | . 67 |

|    | 3.2    | Circuit   | tries of GMCI                                        | . 68 |

|    | 3.3    | Injection | on Efficiency and Output of SCI                      | . 73 |

|    |        | 3.3.1     | Injection Efficiency                                 | . 73 |

|    |        | 3.3.2     | Output of SCI.                                       | . 74 |

|    | 3.4    | Operat    | tional Modes of the SCI                              | 79   |

|    |        | 3.4.1     | Single Cycle Integration (Equivalent to CTIA)        | . 79 |

|    |        | 3.4.2     | Gated Integration with Multi-Point Summation (MGI)   | 80   |

|    |        | 3.4.3     | Gated Integration with Background Subtraction (BSGI) | . 81 |

|    |        | 3.4.4     | Phase-Sensitive Detection (PSD)                      | 82   |

|    | 3.5    | Summ      | ation                                                | . 83 |

| 4  | DES    | IGN OI    | F SWITCHED-CAPACITOR INTEGRATOR                      | . 84 |

|    | 4.1    | Introdu   | uction                                               | . 84 |

| Cl | hapter | •       | J                                                   | Page |

|----|--------|---------|-----------------------------------------------------|------|

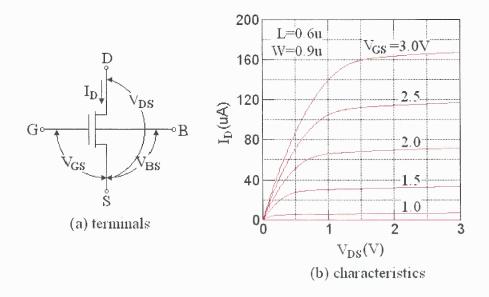

|    | 4.2    | Charac  | eteristics of MOSFET                                | 85   |

|    |        | 4.2.1   | DC Characteristics                                  | 85   |

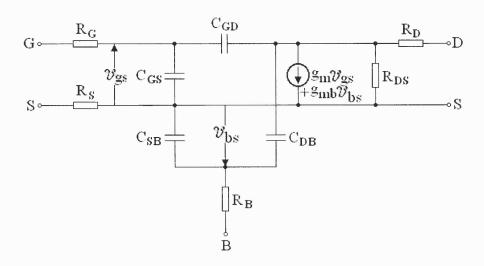

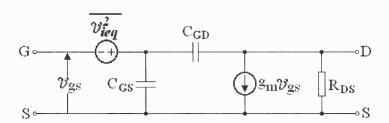

|    |        | 4.2.2   | Small AC Model                                      | 87   |

|    |        | 4.2.3   | Noise Sources of MOSFET                             | 88   |

|    | 4.3    | Design  | of the Switched Capacitor Integrator                | 90   |

|    |        | 4.3.1   | Characteristics of MOS Switch                       | 90   |

|    |        | 4.3.2   | Operational Amplifier                               | 99   |

|    |        | 4.3.3   | SCI Circuit                                         | 106  |

|    | 4.4    | Sample  | e & Hold or Average Circuit                         | 107  |

|    | 4.5    | Shift R | Register                                            | 108  |

|    | 4.6    | Linear  | Array of SCI                                        | 110  |

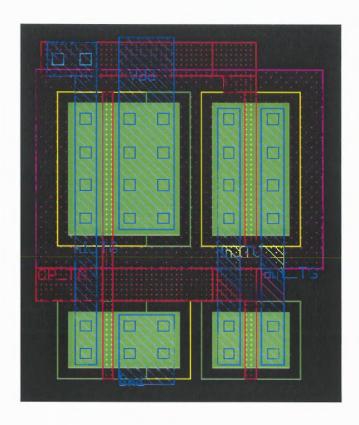

|    | 4.7    | Layou   | t                                                   | 112  |

|    | 4.8    | Summ    | ation                                               | 114  |

| 5  | EXP    | ERIME   | NTAL RESULTS                                        | 115  |

|    | 5.1    | Introdu | action                                              | 115  |

|    | 5.2    | Experi  | mental System                                       | 115  |

|    | 5.3    | Signal  | Injection                                           | 116  |

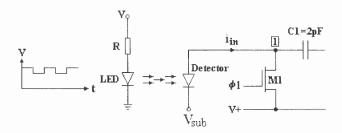

|    |        | 5.3.1   | Optical Injection                                   | 117  |

|    |        | 5.3.2   | Electric Injection                                  | 119  |

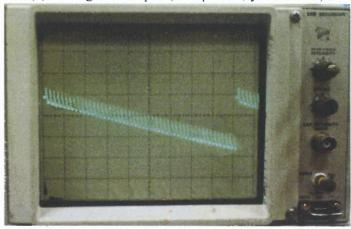

|    | 5.4    | Output  | t of Differential Signal with 180° Phase Difference | 120  |

|    | 5.5    | Experi  | mental Results                                      | 121  |

| Chapte | Chapter 1 |                                               |       |

|--------|-----------|-----------------------------------------------|-------|

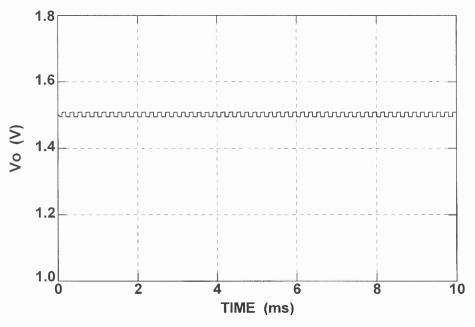

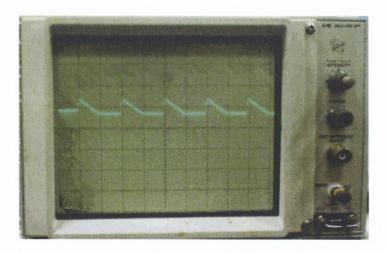

|        | 5.5.1     | Zigzag Output of SCI                          | . 121 |

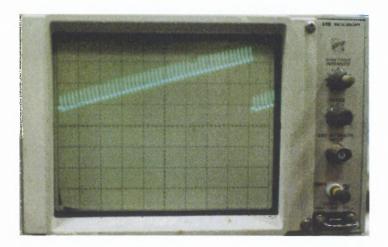

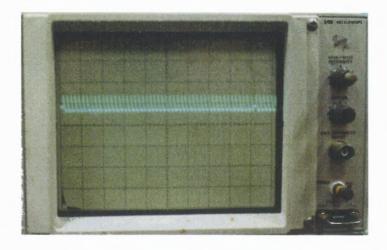

|        | 5.5.2     | Linearity                                     | . 125 |

| 5.6    | Concl     | usions                                        | . 126 |

| 6 CO   | NCLUS     | IONS AND FURTHER WORKS                        | . 127 |

| 6.1    | Sumn      | nation                                        | . 127 |

| 6.2    | Furthe    | er Researches                                 | . 130 |

| 6.3    | Concl     | usions                                        | 130   |

| APPEN  | DIX A     | PROCESSING PARAMETERS FROM HP-0.5μm TECHNIQUE | 132   |

| APPEN  | DIX B     | ELECTRICAL INJECTION                          | . 136 |

| REFER  | ENCES     | S                                             | . 141 |

### LIST OF TABLES

| Table |                                                                           | age |

|-------|---------------------------------------------------------------------------|-----|

| 4.1   | MOSFET capacitances                                                       | 88  |

| 4.2   | Transistor sizes and the characteristics of the Miller CMOS OTA           | 104 |

| 4.3   | Transistor sizes and the characteristics of the symmetric Miller CMOS OTA | 105 |

## **LIST OF FIGURES**

| Figu | re P                                                                        | age |

|------|-----------------------------------------------------------------------------|-----|

| 1.1  | Block diagram of a FPA                                                      | 4   |

| 1.2  | Schematic of a direct-detector integration                                  | 16  |

| 1.3  | Schematic of a direct injection unit                                        | 17  |

| 1.4  | Schematic of a buffered direct injection unit                               | 19  |

| 1.5  | Schematic of a gate modulation input                                        | 19  |

| 1.6  | Schematic of a CTIA                                                         | 21  |

| 1.7  | Schematic of skimming and partitioning                                      | 23  |

| 1.8  | Schematic of a DCM-BDI                                                      | 24  |

| 1.9  | Schematics of current mode background subtraction                           | 25  |

| 1.10 | The principle of correlated readout.                                        | 26  |

| 1.11 | Correlated capacitive transimpedance amplifier                              | 27  |

| 2.1  | Block diagram of a basic lock-in amplifier                                  | 32  |

| 2.2  | Transmission windows of a switching PSD                                     | 35  |

| 2.3  | The transmission window of Lock-in                                          | 36  |

| 2.4  | Schematic of a gated integrator                                             | 37  |

| 2.5  | Block diagram of gated multi-cycle integration                              | 38  |

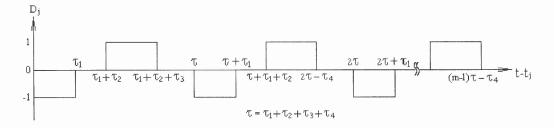

| 2.6  | The jth demodulation function                                               | 39  |

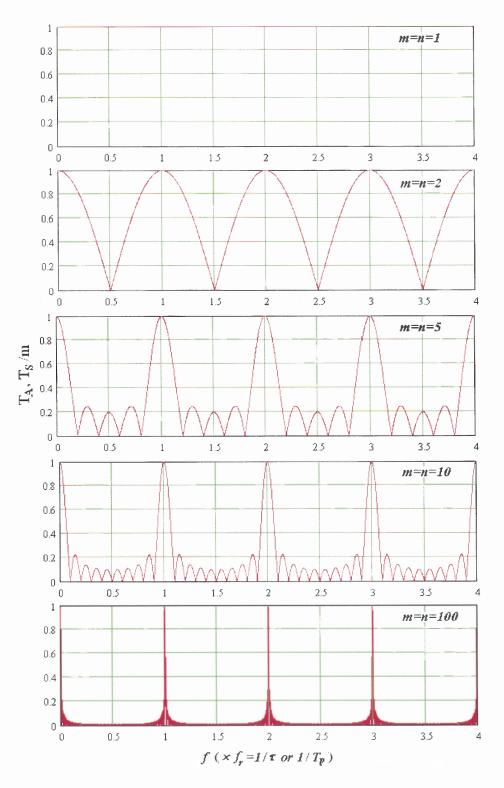

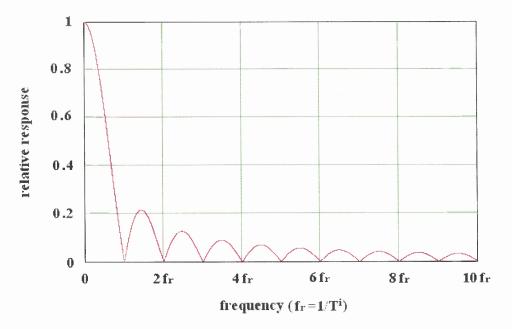

| 2.7  | Transmission windows of multipoint summation or average                     | 44  |

| 2.8  | Maximum integration time versus the ratio of two window lengths of charging |     |

|      | and discharging                                                             | 49  |

# LIST OF FIGURES (Continued)

| Figu | re                                                                            | age |

|------|-------------------------------------------------------------------------------|-----|

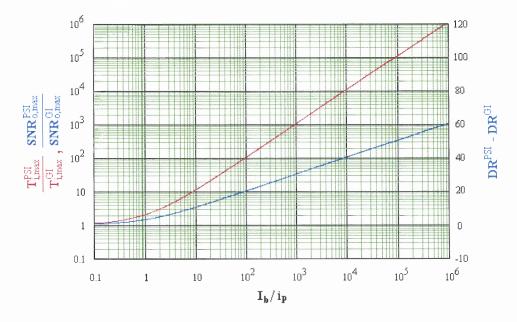

| 2.9  | Maximum SNR and DR as a function of the ratio of two gated lengths of         |     |

|      | charging and discharging.                                                     | 50  |

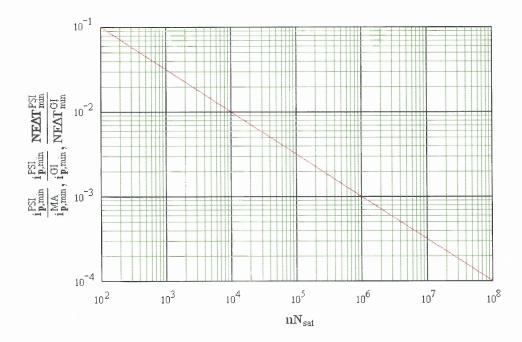

| 2.10 | Background-limited optimum sensitivity vs. the ratio of two gated lengths     |     |

|      | of charge and discharge                                                       | 51  |

| 2.11 | The transmission function of GI                                               | 54  |

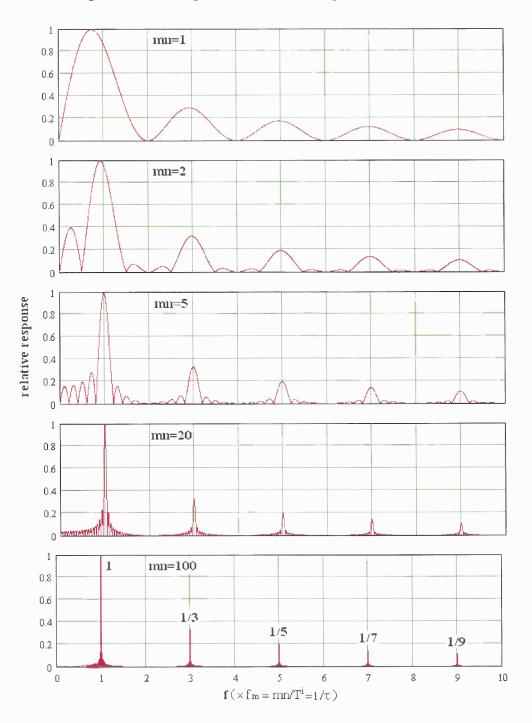

| 2.12 | Transmission windows of PSI with different mn but same $\tau$                 | 57  |

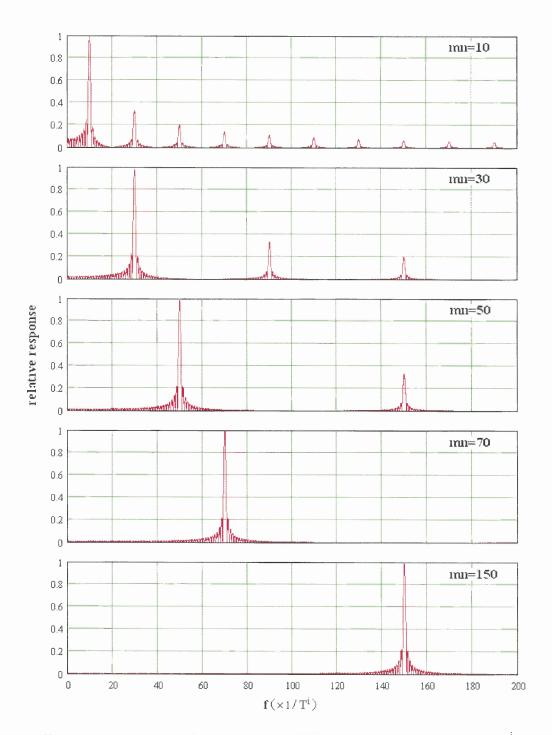

| 2.13 | Transmission windows of PSI with different mn but same T <sup>i</sup>         | 58  |

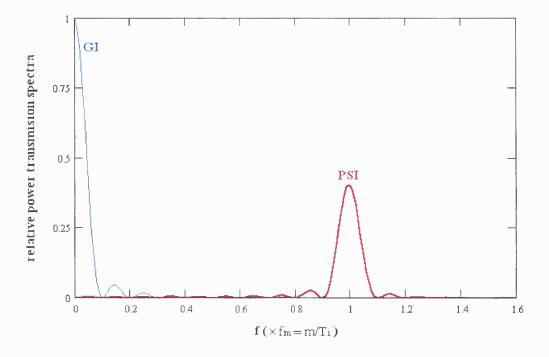

| 2.14 | Comparison of power transmission windows of PSI and GI                        | 59  |

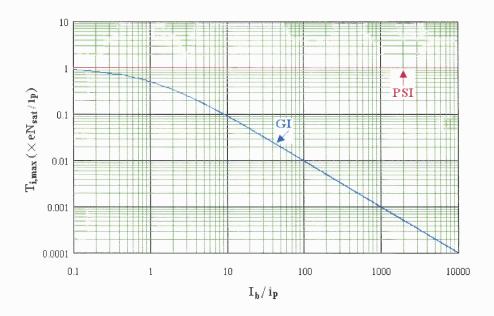

| 2.15 | Maximum integration times with and without background subtraction             | 61  |

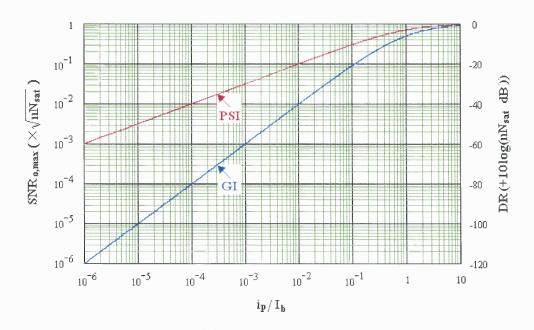

| 2.16 | Maximum SNRs and DRs in cases of PSI and GI                                   | 61  |

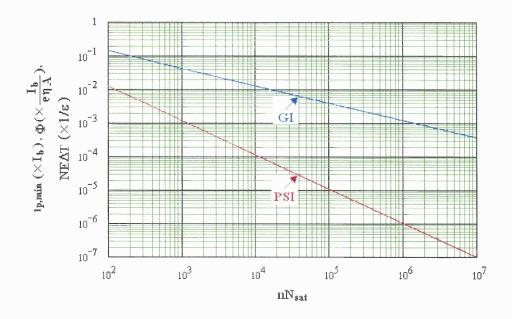

| 2.17 | Sensitivities as a function of storage capacity in cases of GI and PSI        | 62  |

| 2.18 | Comparison of the maximum integration time and dynamic range with and without |     |

|      | DC subtraction as a function of the current ratio of background over signal   | 64  |

| 2.19 | Comparison of sensitivities with and without dc subtraction                   | 64  |

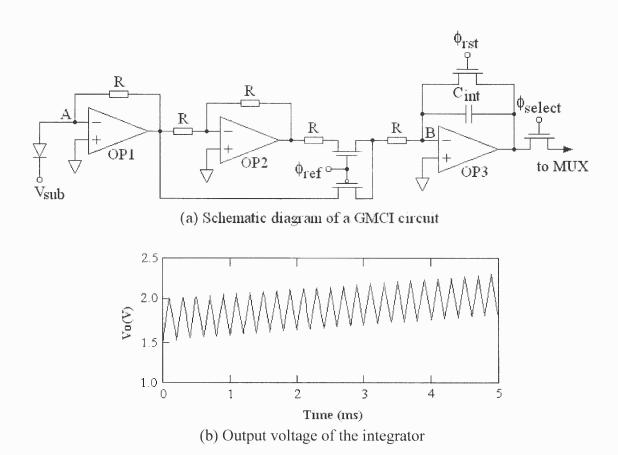

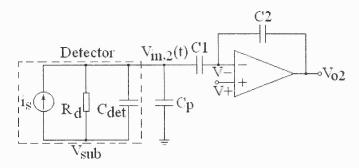

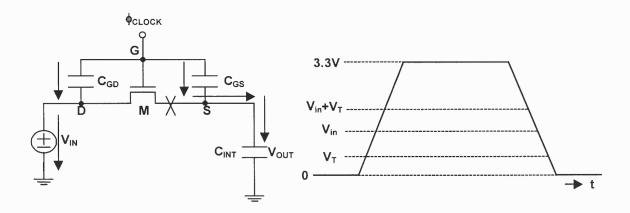

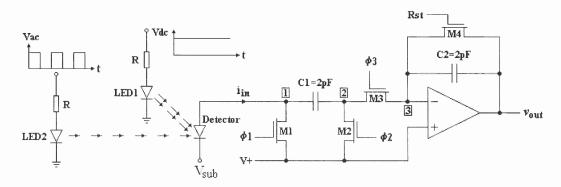

| 3.1  | Schematic diagram of a GMCI circuit and its output                            | 69  |

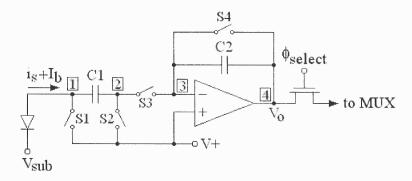

| 3.2  | The switched-capacitor-gated integrator                                       | 69  |

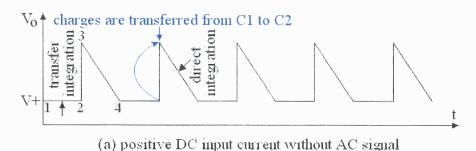

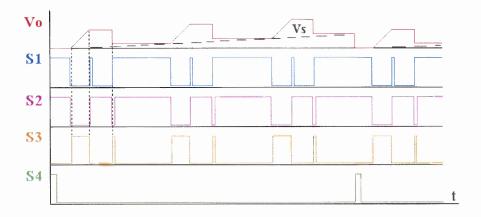

| 3.3  | Outputs of SCI under different situations                                     | 72  |

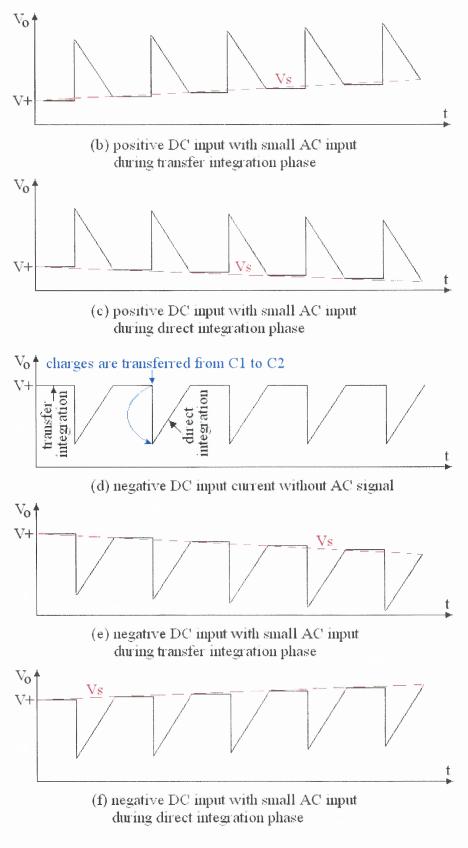

| 3.4  | The Equivalent circuit used for calculation of injection efficiency           | 73  |

| 3.5  | Equivalent circuits of SCI at two different phases                            | 74  |

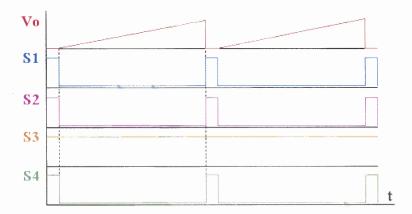

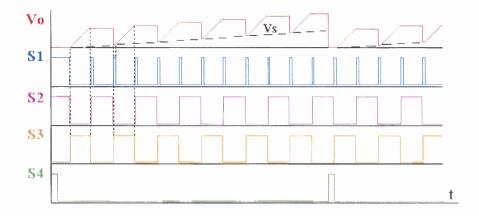

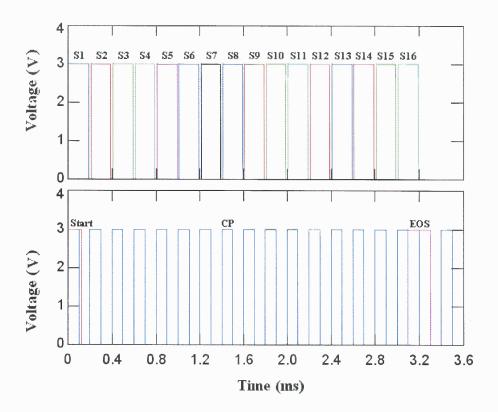

| 3.6  | Waveforms of the switches and the output of integrator for CTIA mode          | 79  |

| 3.7  | Waveforms of the switches and the output of integrator for MGI mode           | 81  |

## LIST OF FIGURES (Continued)

| Figu | re                                                                   | age |

|------|----------------------------------------------------------------------|-----|

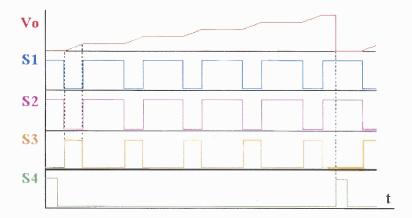

| 3.8  | Waveforms of the switches and the output of integrator for BSGI mode | 82  |

| 3.9  | Waveforms of the switches and the output of integrator for PSD mode  | 83  |

| 4.1  | A MOSFET's four terminals and its characteristics                    | 86  |

| 4.2  | A small ac model for a MOSFET                                        | 87  |

| 4.3  | A simplified noise model of a MOSFET                                 | 90  |

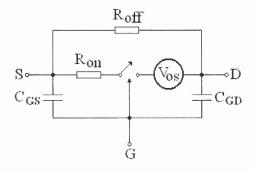

| 4.4  | A model of a MOS switch.                                             | 92  |

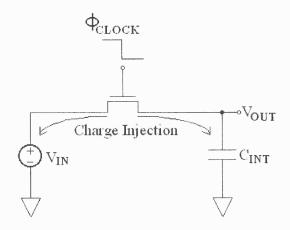

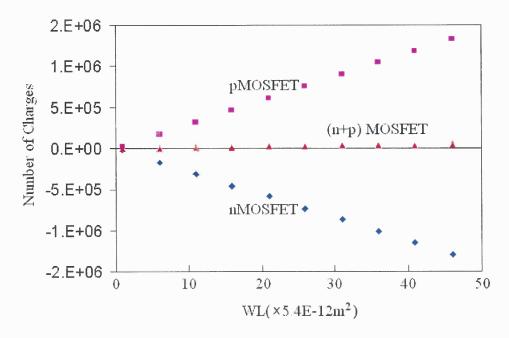

| 4.5  | The illustration for charge injection.                               | 93  |

| 4.6  | The number of charges in channel versus the area of gate             | 93  |

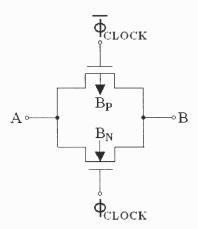

| 4.7  | A transmission gated switch.                                         | 94  |

| 4.8  | The illustration of capacitive feedthrough and the clock waveform    | 95  |

| 4.9  | Layout of a transmission-gated switch                                | 97  |

| 4.10 | Charge injection and feedthrough due to switching                    | 98  |

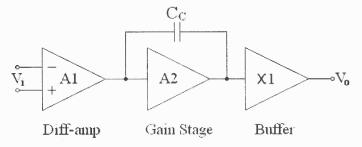

| 4.11 | Block diagram of basic op-amp                                        | 99  |

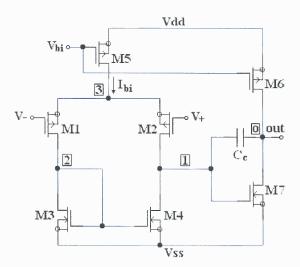

| 4.12 | Schematic diagram of the two-stage op-amp                            | 100 |

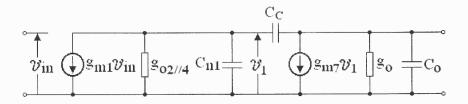

| 4.13 | An equivalent circuit of the two-stage op-amp                        | 101 |

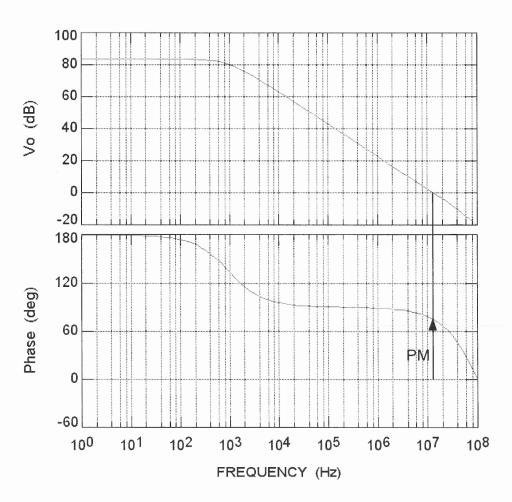

| 4.14 | The amplitude and phase response of a two-stage op-amp               | 103 |

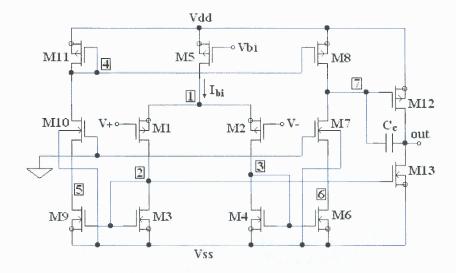

| 4.15 | Schematic diagram of the symmetric Miller CMOS OTA                   | 104 |

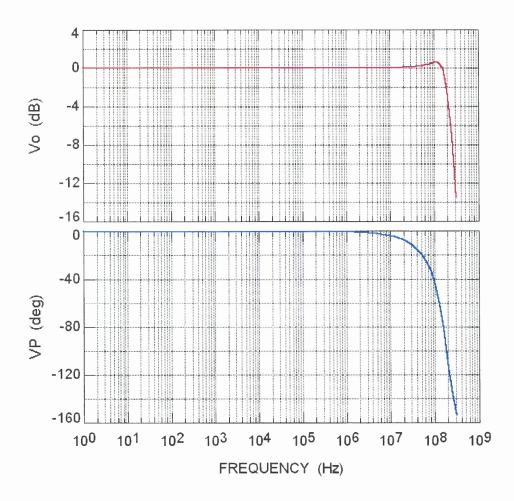

| 4.16 | The frequency response of the unity-gain of the op-amp buffer        | 105 |

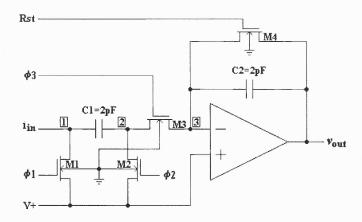

| 4.17 | Schematic diagram of the SCI circuit                                 | 106 |

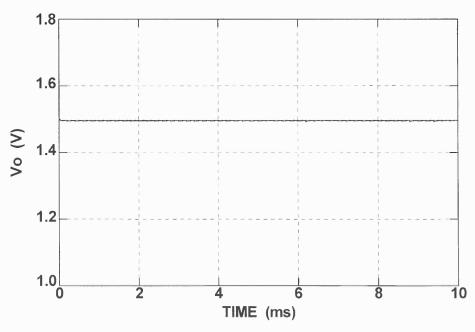

| 4.18 | Simulation result of SCI                                             | 107 |

| 4.19 | Basic sample-and-hold circuitries                                    | 108 |

# LIST OF FIGURES (Continued)

| Figu | re                                                                 | age |

|------|--------------------------------------------------------------------|-----|

| 4.20 | Schematic diagram of the shift register                            | 109 |

| 4.21 | Schematic diagram of the D flip-flop                               | 109 |

| 4.22 | Simulation results of the shift register                           | 110 |

| 4.23 | Block diagram of a linear array                                    | 111 |

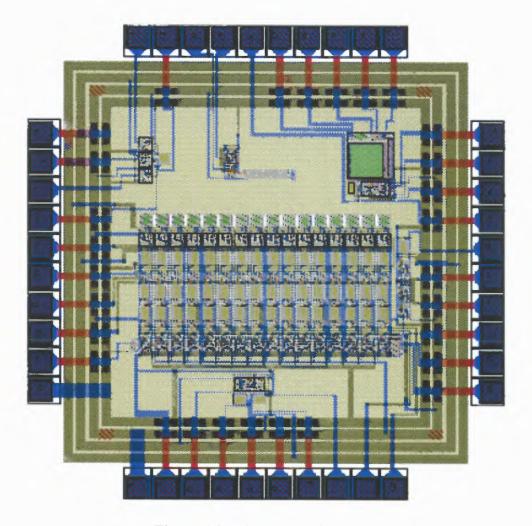

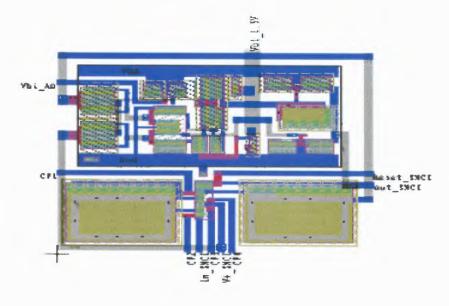

| 4.24 | The layout of the chip                                             | 113 |

| 4.25 | The layout of a SCI unit                                           | 113 |

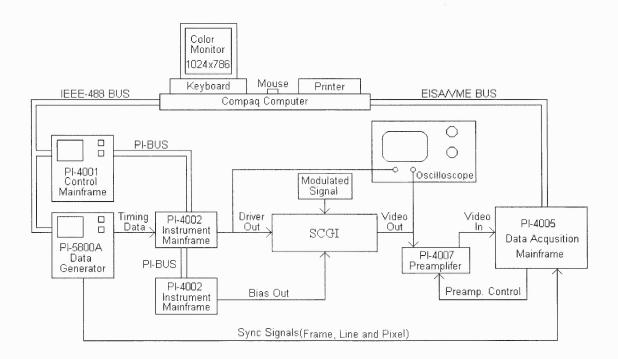

| 5.1  | The PI-4001 measurement system                                     | 116 |

| 5.2  | Optical injection.                                                 | 117 |

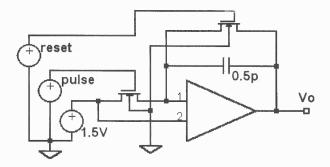

| 5.3  | Electric injection                                                 | 119 |

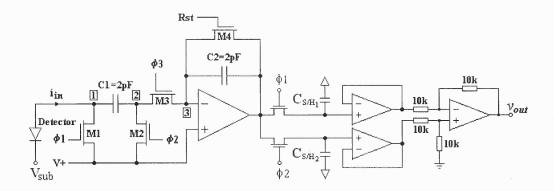

| 5.4  | Schematic diagram used for measuring differential signals          | 120 |

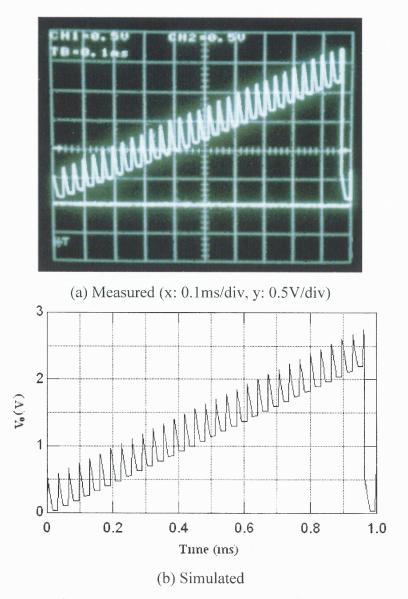

| 5.5  | Zigzag outputs of SCI with background subtraction                  | 123 |

| 5.6  | Experiment and simulation results of the zigzag outputs of the SCI | 124 |

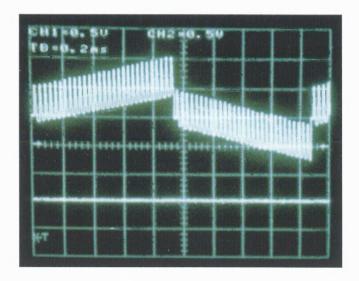

| 5.7  | The output of SCI under input signals with 180° phase difference   | 125 |

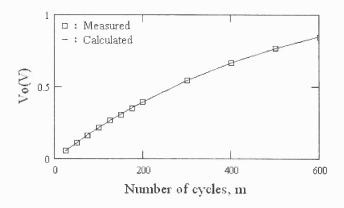

| 5.8  | The differential output as a function of cycle number              | 125 |

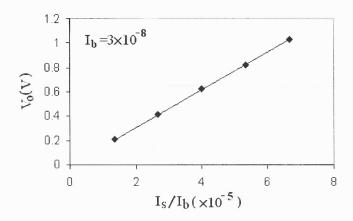

| 5.9  | Measured differential output vs. input signal                      | 126 |

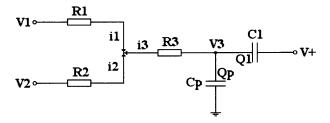

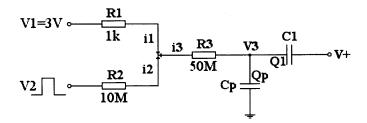

| B1   | Schematic diagram of the circuitry for electrical injection        | 136 |

#### **CHAPTER 1**

#### RESEARCH BACKGROUND

#### 1.1 Introduction

The term Focal Plane Array (FPA) is used to refer to an imaging system having its optical focal plane placed with a large number of detectors simultaneously integrating signals from an image projected onto the array. Visible and infrared FPAs have found a variety of rapidly growing industrial, commercial, military, and scientific applications. Current trends of solid-state focal plane array are pursuing high pixel density for high resolution, much more on-chip processing for more function and high efficiency, low power consumption for space application, room temperature IR operating for hand-held use, new detector materials for covering more spectral bands, and multi-color imaging for more information. Widely used imaging systems such as Si CCD (charge coupled device), CMOS APS (complementary metal-oxide field effect transistor active pixel sensor), Schottky-barrier detector (SBD), InGaAs, InSb, and HgCdTe FPAs are all based on the concept of current integration to accumulate signal in the purpose of improving signal-to-noise ratio, dynamic range and sensitivity. Small unit area but high performance integrators such as detector direct integration (DDI) or source- follower per detector (SPD), direct injection (DI), buffered direct injection (BDI), gate modulation input (GMI), and capacitive transimpedance amplifier (CTIA) are well known in the FPA community. They are very successful in the applications with low to high backgrounds given the signal is not far lower than background. The integration, however, includes both the signal-induced and background-associated (including detector's dark current) currents at same time. Consequently, present single integration FPA technology encounters intrinsic difficulty when dealing with repetitive images and weak images buried in strong backgrounds. Examples are pulse laser-induced fluorescence or Raman imaging in biosciences [1,2], solar magnetography where signal is four orders less than background [3], and very long wavelength IR FPA [4] where the detector's dark current is significant.

Alternate integrators such as current memory [4,5], dynamic current mirror buffered direct injection (DCM-BDI) [6], and correlated capacitive transimpedance amplifier (CCTIA) [7] were proposed to solve the difficulty. However, the requirement of a calibration phase made the CM and DCM-BDI impracticable. CCTIA will not properly work since it requires the detector forwardly biased. Nevertheless, the concept is worth for further consideration.

Current technologies for pulse laser-induced imaging are confocal laser scanning microscopy [8] and gated intensifier CCD [9]. The former takes an image point by point by using a photomultiplier tube. The later uses CCD to form the second image from the primary image captured by the gated intensifier, thus, the resolution is limited by the primary image of the intensifier. In both cases, the image signal from each pixel is acquired through a single integration.

It is well known that boxcar averaging, lock-in amplifier and photon counting are powerful technologies used to detect weak repetitive signals. They have played very important roles in developing modern sciences. However, their applications are limited to a single detector due to the complexity of the systems.

In dealing with the weak repetitive image (if the image is not repetitive, it can be modulated) buried in strong background, the theory of an alternate integration method, called gated multi-cycle integration [10-12], is developed. It unifies the basic concepts of phase sensitive detection, gated integration, multiple summation and averaging. Before presenting the theory of multi-cycle integration, the basic concepts of FPA and some related background information are briefly reviewed.

#### 1.2 Structure of FPA

A FPA usually refers to a solid-state imaging system with array detectors placed on the optical focal plane where an object is imaged. A FPA could be scanning or staring. To take an image, a scanning FPA uses a linear array detector, which scans in the direction perpendicular to the array. The advantage of scanning array is its relative simple configuration and low cost. The disadvantage is that it needs an additional scanning system. Therefore most scanning FPAs are used on satellites or airplanes for mapping clouds, ground, or resources on the ground while the scanning is automatically carried out by the flight of the satellites or airplanes. A staring FPA uses an area array. Its advantage is its efficiency to take images, since it does not need scanning, and is therefore more compact.

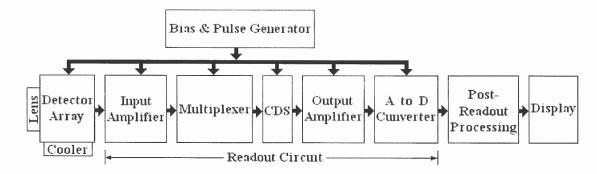

A complete digital FPA system usually includes a photon-sensing array, signal preamplifiers or input unit cells, multiplexer, correlated double sampling (CDS) circuit, output or video amplifiers, analog-to-digital converter (ADC), post readout processing circuit, bias and pulse generator, optical lens, display, and sometimes cryogenic set for cooling detectors. CDS circuit may be put in the unit cell or after multiplexing or just

calculated in the post readout processing. Fig.1.1 shows the block diagram of a FPA system.

Figure 1.1 Block diagram of a FPA

A chip that at least includes the input unit cells and multiplexer is called readout circuit. The most important two components in a FPA are the detector array and the readout circuit. FPAs can be fabricated in two basic configurations, monolithic and hybrid. For a monolithic FPA, the detector array and the readout circuit are integrated in the same chip. Because they are fully integrated, they are potentially inexpensive. For a hybrid FPA, the two are fabricated on separate substrates and are connected together by certain bonding technique such as In-bump bonding. Readout circuit is almost always fabricated on Si substrate in order to take the advantages of the well-developed Si technologies. Silicon is highly sensitive to visible but insensitive to infrared light. Si monolithic FPAs are dominant in visible range. Two well-known visible FPAs are Si CCD and CMOS APS. By contrast, narrow-band-gap materials are highly sensitive to infrared wavelengths. Hence infrared FPA usually is hybrid, except PtSi SBD FPA, to take advantages of both detector material and Si. Commercial IR FPAs with high performance are InGaAs photovoltaic (PV) FPA operating at 1.3~1.7um, InSb PV FPA

working at  $3\sim5\mu m$ , GaAs/AlGaAs MQW photoconductor (PC) FPA functioning at  $8\sim20\mu m$ , and HgCdTe PV FPA performing at  $1\sim14\mu m$ . They are all hybrid.

#### 1.3 A Brief History of FPAs

The development of FPA is a history of finding and improving both detector materials and readout methods. People used thermal and photon detectors for a long time. However detector array and readout circuit were not available until micro-electronic technologies were developed. In fact, FPA actually is an integrated circuit. It started with the invention of Si integrated circuit.

As early as in 1800, Sir Frederick William Herschel first found infrared radiation when he used a thermometer to measure the spectrum of the sun. More sensitive photon infrared detectors were not developed until 1940's, mainly due to their military applications. The first practical IR detector was PbS, which can detect IR radiation with wavelength up to 3μm. Intrinsic Si and Ge covered the visible and near infrared (NIR). Beginning in the late 1940's and continuing into 1950's, PbSe, PbTe, and InSb extended the spectral range beyond that of PbS, providing sensitivity in the 3-5 μm medium wavelength infrared (MWIR) atmospheric window. The important HgCdTe detector was introduced in late 1950's with high sensitivity up to 14 μm long wavelength infrared (LWIR) spectral window. At the same time extrinsic impurity doped Ge and Si conductive detectors extended the wavelength to very long wavelength (VLWIR) of 14-30 μm.

Linear detector arrays were first demonstrated with PbS, PbSe, and InSb in the early 1960's when photolithography became available. Photovoltaic (PV) detector

development began with the availability of single crystal InSb material. The discovery in the early 1960's of extrinsic Hg-doped germanium led to the first forward looking imaging radiometer (FLIR) system operating in the LWIR spectral window using linear array. However it required a two-stage cooler to operate at 25K because it was an extrinsic detector. Later on intrinsic HgCdTe photoconductor linear array were developed in the late 1960's and early 1970's. These allowed LWIR FLIR systems to operate at 80K in a dewar with liquid nitrogen.

First generation IR imaging systems used liner arrays coupled with room temperature preamplifiers. Consequently, each detector element in the array had an individual conductive signal lead, which had to feed through the cryogenic vacuum dewar wall. This approach limited first generation linear arrays to less than two hundred elements.

The important concept of signal integration, suggested by Weckler [13] in 1967, began the second generation of scanning FPAs. In his approach, photon flux induced photocurrent was integrated on a reverse-biased junction capacitance. Integrated charges were read out through pMOS switches. Thus, multi-pixels can be read out one by one through a multiplexer. The advantages of this approach were revolutionary. First, it increases the signal-to-noise ratio by accumulating more photons through increasing integration time. Previous instant signal voltages were usually less than  $0.1~\mu\text{V}$ , which were quite susceptible to noise. Second, it reduced tremendously the complexity of the signal readout. One pixel one lead was replaced by a single integrated multiplexer. Third, integrated readout circuit can be directly coupled to sensor array, making the imaging system more compact and more resistant to the interference from electronic and magnetic

fields nearby. Following the integration concept are different basic integration methods such as direct integration (DI), source-follower per detector (SFD), buffered direct injection (BDI), gated modulation input (GMI), and capacitive transimpedance amplifier (CTIA). However, at that time, MOS switch readout circuits suffered from fixed pattern noise (FPN) [14].

In 1970, charge-coupled device (CCD) [15] was first reported with attractive features of freedom of FPN and small pixel pitch. Since then CCD has dominated the visible FPA for 40 years. Array size of 5120×5120 [16] has been demonstrated with dynamic noise level of 3 to 5 electrons and a dynamic range of over 80dB. CMOS imaging, beginning in early 1970's and rapidly re-growing after early of 1990's, shows its urgent ambitious trying to take over the visible market due to its much lower power consumption [17]. Camera on a single chip is only realized by CMOS technology. However, today's scientific instruments are still embracing CCD because of its better overall performance.

In IR region, early hybrid FPAs used conventional CCD as readout circuits. This has all the advantages of low noise, high storage capacity and linear response. This approach showed that photovoltaic (PV) detectors such as InSb, PtSi, and HgCdTe detectors or high impedance photoconductors such as PbSe, PbS, and extrinsic silicon detectors were promising candidates because they had impedances suitable for interfacing with readout multiplexers. Monolithic extrinsic silicon detectors were demonstrated first in the middle of 1970's. Later on it was set aside because the process of integrated circuit fabrication degraded the detector quality. Monolithic PtSi Schottky detectors, however, in

which the detector can be formed after the readout is processed, are now widely available.

Since the invention of the CCD, it had taken nearly two decades to develop the technology of integration of IR detectors and electronic readout circuits. A milestone in the development of readout history is the correlated double sampling (CDS) method [18], which can effectively reduce kTC noise of reset, low-frequency noise of detectors and FPN due to switching. By using CDS, CMOS readout circuit has gradually replaced CCD multiplexer for hybrid FPA system, because CMOS readout has better performance at low temperature and can integrate more functional circuitries such as self scanning address and analog-to-digital converter (ADC) in the same chip.

The first high performance second-generation hybrid array was demonstrated in 1978 using InSb PV detectors in a 32×32 array format. Second generation devices have now been demonstrated with many detector materials and devices types. These materials and devices include PbS, PbSe, InSb, extrinsic Si bulk devices, PtSi Schottky, HgCdTe PV and GaAs/AlGaAs MQW PC detectors with array size up to 2048×2048.

In late 1980's, with advance molecular beam epitaxy (MBE) and metal-organic chemical vapor deposition (MOCVD) epitaxial growth techniques available, tailored InGaAs/InP PV and AlGaAs/GaAs QWIP materials became the new members in the infrared community covered the wavelength in the NIR and LWIR, respectively. With maturated material and processing technologies of GaAs/AlGaAs, plus the high performance of the Sterling cryostat, hand-held GaAs/AlGaAs QWIP FPA camera become dominate in commercial LWIR market. With advanced micro electro-mechanical system (MEMS) and submicron technologies becoming available, uncooled thermal

detector FPA made great progress in 1990's. NEΔT of 20 mK° was reported in a recent SPIE conference [19].

Before 1990, the development of infrared sensors had mainly centered on the growth, fabrication, measurement, and optimization of IR materials and detectors. The signal readout of the detector had been given less attention since IR sensor performance was limited by materials at that time. With rapid advancement in material growth and in micro-chip processing, detector arrays became well suited. In addition, with sub-micron technology available in 1990s, readout methodologies started to gather attention. That is reflected in four specific conference proceedings on the readout circuit [20-23] organized by the International Society for Optical Engineering (SPIE) during 1990s. Recent pursuit of readout tends to build more functional circuitries, such as for A/D converter, edge enhancement, non-uniformity correction, towards the third generation of "smart" FPA. Now FPA technology seems quite mature from visible to LWIR, except in the case of weak image signal buried in strong background. With background several orders stronger than image signal, it is the readout electronics rather than the detectors that limit FPA performance.

#### 1.4 Performance of FPA

The general feature of a FPA falls into broad categories of array format, pixel size, storage capacity, input interface, signal conversion gain, minimum readout noise, dynamic range, integration time, noise equivalent temperature difference, maximum frame rate, maximum data rate, operating temperature and power dissipation.

#### 1.4.1 Array Format

Array size usually follows the format of 2<sup>n</sup>×2<sup>n</sup>, such as 128×128, 256×256,..., 2048×2048 or VGA format, such as 640H×480V, ..., 1600H×1200V. Larger array provides better spatial resolution at cost of lower yield and higher price. Commercial FPAs usually have array sizes from 128×128 to 1024×1024.

#### 1.4.2 Pixel Size

Pixel pitches are around 15 to 50 µm for hybrid FPAs and 5 to 15 µm for monolithic FPAs. With array size becoming larger, the pixel pitch tends to shrink smaller. However, the minimum pixel size is limited either by input unit circuit or optical diffraction. For hybrid FPAs, it may also be limited by the interconnection between the sensor array and the readout chip.

#### 1.4.3 Storage Capacity

Charge storage capacity is determined by the capacitance of the integrator circuit, which is limited by the real estate of a chip, as well as the saturation voltage of the readout circuit. It varies from 10<sup>5</sup> to 10<sup>7</sup> electrons. Large storage capacity means large pixel pitch and higher kTC noise (see 1.4.5). Here k is the Boltzman constant, T the temperature, C the capacitance of the integrator. Large capacity is only necessary for high dynamic range or strong background applications. Most FPAs have capacities in the order of 10<sup>6</sup> electrons.

#### 1.4.4 Signal Conversion Gain

The signal conversion gain is defined as the integrated voltage per input charge. It is dependent on the quantum efficiency of the detector and the capacitance of the integrator.

Higher quantum efficiency and lower integrating capacitance result in a higher signal conversion gain. The gain can vary from 0.1 to 20  $\mu$ V/e<sup>-</sup>.

#### 1.4.5 Noise

General noise in a FPA system includes fluctuations related to photon flux (both signal and background), detector, readout electronic circuitry and its nonuniformity. Photon related noise is called photon shot noise measured as the square root of the number of integrated photo-induced electrons. Thermal, dark current shot, and 1/f noises are the main detector associated noise sources [24]. Electronics noise includes the unit cell integrator noise, as well as the downstream multiplexer, driver amplifier and analog-todigital converter noises. The unit cell electronics is the main electronics noise source, which includes the transistor white noise, 1/f noise and reset noise. Reset noise is also called kTC noise, since the resetting of an integrator through a transistor switch has an uncertain residual charge, the rms (root mean square) value of which is equal to (kTC)<sup>1/2</sup>. 1/f and kTC noises can be reduced through the well-known correlated double sampling (CDS) methodology. Readout noise is directly related to the readout method. A normal FPA system has readout noise from tens to hundreds of electrons. Carefully designed FPA may have minimum readout noise less than 10 electrons by using CDS. CCD readout has minimum readout noise around a few electrons. However, CCD readout has been abandoned by the hybrid infrared FPA due to its performance degradation at low temperature and its process incompatibility with CMOS technology. Finally, the fixed pattern noise (FPN) is associated with randomly distributed, time-invariant offsets in unit cell circuits. Generally, it is feasible to control readout noise at a level lower than detector

noise or photon shot noise. Hence, readout noise will become critically important when signal photon flux is extremely low.

#### 1.4.6 Dynamic Range

Dynamic range is defined as  $20\log_{10}(SNR_{max})$ , where the maximum signal-to-noise ratio  $(SNR)_{max}$  is defined as the ratio of the maximum signal that can be integrated to the noise floor.  $SNR_{max}$  can be understood as the ratio between the brightest feature to be observed and the weakest detectable one. The dynamic range of a normal FPA is usually limited by the charge storage capacity, typically 60-70 dB for consumer products and 70-80 dB for scientific applications.

### 1.4.7 Integration Time

Integration time is one of the most important parameters for the application of a FPA. The longer the integration time, the better the signal-to-noise ratio. Consequently, the higher the dynamic range and the better the sensitivity. Integration time is not only determined by the capacity of the FPA, it is also determined by the photon flux of the application. When the background or dark current is dominant compared to the signal, current readout methods will fail to obtain meaningful SNR. A good FPA has an integration time close to the frame time.

## 1.4.8 Noise Equivalent Temperature Difference (NEΔT)

In IR thermal imaging, NEΔT represents the temperature variation from incident radiation source, which gives an output signal equal to the rms noise level. System NEΔT usually is inferior compared to that of a single detector because there the exists system

loss and the nonuniformity of pixels. Another more preferred figure of merit for IR FPAs is the minimum resolvable temperature (MRT). MRT is a function of spatial resolution and is defined as the signal-to-noise ratio required for an observer to resolve a series of standard four-bar targets. It includes the effect of human eye's response.

#### 1.4.9 Maximum Frame Rate

Frame rate is usually inversely proportional to the integration time. Maximum frame rate gives the shortest integration time an FPA can provide. When the scene is bright, the integration time needs to be short. The integration time could be as short as  $0.1~\mu s$  and as long as tens of hours.

#### 1.4.10 Maximum Data Rate

Maximum data rate is the maximum output data transfer rate and is usually determined by the main clock rate and may be limited by the speed of ADC. For a large FPA, e.x., 2048×2048, output data must be quite fast. With multi-video-output architecture, maximum data rate of 800 MHz is commercially available for CMOS camera.

## 1.4.11 Operating Temperature

Visible and thermal IR detector FPAs usually operate at room temperature, while photon detector FPAs usually need a cooler to suppress detector dark current to increase the integration time. The operating temperature of IR FPAs is set by the detector cutoff wavelength. The longer the cutoff wavelength of the detector is, the larger the thermally generated dark current, resulting in a mandatory colder operating temperature.

#### 1.4.12 Power Dissipation

Low power dissipation is always preferred for hand-held cameras and for IR imaging systems operating at low temperature. In a FPA, most power is consumed by the readout circuit. This is one of the main reasons why CMOS readout circuits become the predominant player for hybrid FPAs, and why CMOS APS camera becomes a strong competitor to CCD camera.

The performance requirements vary with applications. For example, astronomical observation usually requires low noise, long integration time and high bit ADC due to low background flux. High background or LWIR needs precise control of detector bias, large charge capacity and snap shot function. Digital camera for family use pursues high resolution, low power, and large memory at low price. The performance of a FPA also varies with the type of detectors and the input readout method.

### 1.5 Commonly Used Input Unit Cell Readout Circuits

In a FPA construction, readout circuit is a signal processing circuit that accumulates signals from every detector in the array and transfers the integrated signals to the video output. First generation FPAs used the same number of AC amplifiers as the number of pixels, as well as the number of leads that connect detectors to the amplifier. This approach has been replaced by second-generation FPA technology, which uses unit cell readout circuit plus one or a few multiplexer to process signals. For photon detector FPAs, a unit cell readout circuit or a unit cell input amplifier circuit becomes a unit cell integrator, which integrates the signal current as well as the background and dark currents. Thus, the unit cell integrator is an important topic in the FPA community. The

requirements for the unit cell integrator are: 1. The layout of the unit integrator must be limited within the pixel area. This means that the integrator cannot be composed of more than a few transistors, say less than 5 transistors for a large 2D array. 2. The noise of the integrator should be less than that from the detector. 3. The integrator must be matched with the detector at the operating temperature: the integrator should have good linearity and responsibility, and can effectively integrate the signal with the given background and impedance of the detector. 4. The power consumption should be low. Since the first proposal of the signal integration in late 1960s, integrator has been sufficiently studied and practiced. There are only a few matured integrators that satisfy the above requirements and represent the state-of-the-art FPA readout technology. These input unit cell integrators are direct detector integration (DDI) [25] (also called source follower per detector), direct injection (DI) [26], buffered direct injection (BDI) [27], gate modulation input (GMI) [28] (also called current mirror integration), and capacitive transimpedance amplifier (CTIA) [29]. They will be briefly reviewed in this section.

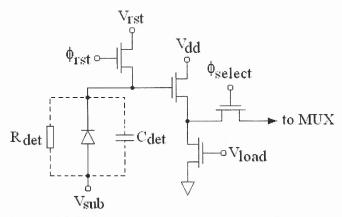

#### 1.5.1 Direct Detector Integration (DDI)

A readout integrator must have at lease one capacitor to collect signal-induced charges. The most simplified integrator is the direct detector integration, which utilizes the junction capacitance of the detector. Fig. 1-2 illustrates the schematic of DDI. At the starting time of a frame, the reset switch pre-charges the junction at certain voltage level. The current (includes the signal-induced current) passes through the detector will then discharge the capacitor. By the end of the frame, the buffered voltage signal will be sensed to the output amplifier by enabling the selecting switch. DDI is an RC discharging circuit. In order to get a good linearity of a RC circuit, the RC time constant must be

much larger than the integration time. Thus, DDI is only suited for high impendence of detector and low background application. In DDI, the detector must be heavily reversely biased in order to obtain adequate dynamic range. The noise sources of DDI are the reset kTC noise and the input MOSFET's 1/f and channel thermal noises. The advantage of DDI lies in its simplicity. In fact DDI construction uses a minimum number of transistors among all the input integrators. This is why the DDI is widely employed in today's large format FPAs from visible to MWIR range.

Figure 1.2 Schematic of a direct-detector integration

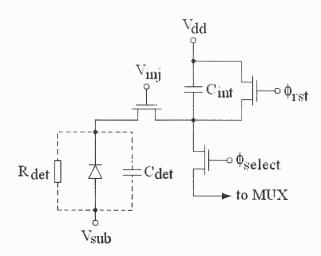

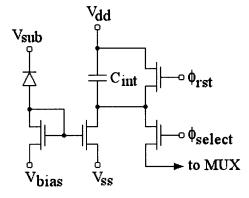

#### 1.5.2 Direct Injection (DI)

Instead of using the detector junction capacitor as the integrator, direct injection scheme uses a separate integration capacitor C<sub>int</sub> as shown in Fig. 1.3. The unit cell consists of an active injection transistor, a reset transistor, an output selection transistor, and an integration capacitor. The photon current from detector is injected, via the active injection transistor, onto the integration capacitor that has been reset prior to the beginning of integration. After integration, the charges accumulated on the capacitor is either dumped

on to the column selection line or is buffered by a source follower to provide voltage mode output.

Figure 1.3 Schematic of a direct injection unit

Since the photocurrent is input through the injection transistor, the DI scheme yields somewhat better bias control during integration compared to DDI. However, the nonuniformity of the threshold voltage of the injection transistor will cause FPN directly. Since the detector is not directly reset, residual charges from one frame can be integrated into the next frame, resulting in frame-to-frame crosstalk.

The input of the DI should provide a low impendence to the detector. This provides a stable detector bias and a high photocurrent injection efficiency. If the input impendence is too high, a fraction of photocurrent will be bypassed across the detector and not injected to the capacitor, resulting in a loss of SNR. This injection efficiency, which represents the percentage of detector current that can be stored, is

$$\eta_{inj,DI} = \frac{g_m R_{\text{det}}}{1 + g_m R_{\text{det}}} \tag{1.1}$$

where  $R_{det}$  is the detectors' dynamic resistance,  $g_m$  the transconductance of the injection transistor.

g<sub>m</sub> is a strong function of the drain current of the MOSFET, which is typically very low since it directly comes from the detector. In many injection applications, the injection transistor operates in weak inversion. The transconductance is given by

$$g_m = \frac{qI_D}{mkT} \tag{1.2}$$

where  $I_D$  is the drain current of the input transistor, q the charge of an electron, m the subthreshold ideality of the input transistor. It is clear that  $g_m$  and  $R_{det}$  must be large in order to get high injection efficiency. This limits the DI applications to medium and high photon flux and detectors with cutoff wavelength not beyond MWIR. This in turn means that the integration capacitance should not be made too small. The overall advantage of DI is its small unit area. Comparing to DDI, DI extends the photon flux to medium and high.

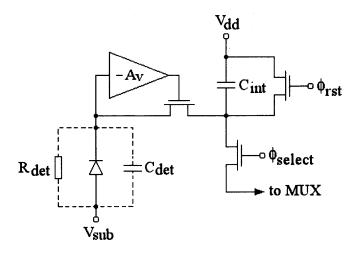

### 1.5.3 Buffered Direct Injection (BDI)

The poor injection efficiency of DI can be overcome by buffered direct injection (BDI) configuration as shown in Fig. 1.4. The injection transistor is controlled by an inverting amplifier with open-loop gain  $-A_v$ . The effective  $g_m$  is increased by a factor of  $(1+A_v)$ . Consequently, the injection efficiency and the minimum photon flux are improved by a factor of  $(1+A_v)$ . Another benefit from BDI is that the inverted gain provides feedback to yield a better control over the detector bias at different photocurrent levels. BDI is not suited for extreme low photon flux.

Figure 1.4 Schematic of a buffered direct injection unit

# 1.5.4 Gate Modulation Input (GMI)

In a gate modulation input scheme as shown in Fig.1.5, the detector is connected in series with a load, either a passive resistor load or an active transistor load. The voltage across the load is used to modulate the gate voltage of an input MOSFET. The output current of the input transistor is then to discharge a capacitor previously reset to a reference level. When the load is a transistor, the configuration of the GMI actually is a current mirror (CM).

Figure 1.5 Schematic of a gate modulation input

The main advantage of the GMI is the current gain that can be set through adjusting the detector bias  $V_{\text{bias}}$ , the source voltage of the input transistor  $V_{\text{ss}}$ . For active load the current gain is given by

$$A_{I} = (\eta + I_{det} / I_{p}) \frac{(W / L)_{lnput}}{(W / L)_{load}} \exp\left[\frac{q}{mkT} (V_{bias} - V_{ss})\right]$$

(1.3)

where I<sub>det</sub> is the dark current of the detector, I<sub>p</sub> the photon-induced current. Thus, the integration current can be scaled up or down several orders by adjusting biases and the dimensions of the transistors. A large current gain lead to higher charge detection sensitivity and reduced input-referred noise levels. A fraction gain is useful for the application of strong background. However, the signal is also scaled down. For this reason, the capability of the background suppression is susceptible.

The nonuniformity of detector's dark current as well as the threshold voltage variation in the input transistor causes the current gain to vary from one cell to another, resulting in big FPN. The detector as the input of the GMI must have a high impendence in order to keep high injection efficiency. CM has been used for low background application of InGaAs FPAs and for LWIR of GaAs/AlGaAs QWIP FPAs.

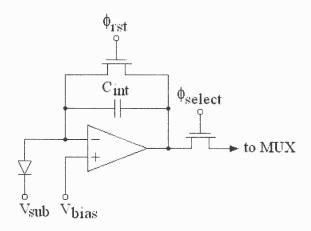

# 1.5.5 Capacitive Transimpedance Amplifier (CTIA)

Figure 1.6 shows the configuration of CTIA. It consists of an inverting amplifier, an integration capacitor C<sub>int</sub> placed in a feedback loop, and a reset transistor in parallel with the integration capacitor. The amplifier could be a simple CMOS inverter, a simple cascade amplifier or a more elaborate differential amplifier. The choice of the amplifier is considerably upon with the respect to open-loop voltage gain, bandwidth, power dissipation, linearity, and unit cell real estate.

Figure 1.6 Schematic of a CTIA.

Due to the high open-loop gain of the amplifier, the voltage at input node of the CTIA is virtually fixed, resulting in a tight control on the detector's bias. It also maintains an almost 100% collection of the photocurrent to the feedback capacitor, yielding a high injection efficiency. A good linearity is another advantage of CTIA. Since the capacitance can be made very small, say a few fF, the transimpendence of the CTIA can be extremely high, yielding a higher detector sensitivity and excellent low noise performance. CTIA has overall best performance characteristics [29] among the conventional input integrators and is an ideal readout circuit embraced with many circumstances.

### 1.6 Researches on Background Subtraction

Conventional input integrators, as discussed in previous subsections, integrate both signal-induced current and background (including detector dark current). In this thesis, background is used to indicate both the current due to background radiation and the

detector dark current. It is difficult for these integrators to deal with weak image buried in strong background. There are special applications that need to recover weak images swamped by strong background. There are cases when the integrator is saturated by the background while the accumulated signal level is still less than the background related noise. Pedestal removal in FPA readout has been studied for many years. From the earlier "skimming", "partitioning" to recent "dynamic current mirror buffered direct injection", "current memory" and "correlated readout", yet there is still no convincing approach that is widely accepted. The remaining useful technology to deal with weak image swamped by strong background is the post-readout averaging. However, the accuracy of multiframe averaging is limited by the least step of ADC and it also suffers from the background drift and low frequency noise.

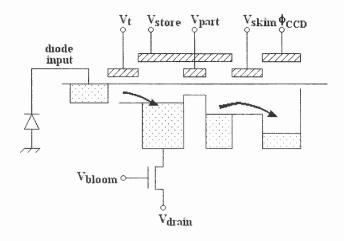

# 1.6.1 Skimming and Partitioning

Skimming and Partitioning [30] were fulfilled in a CCD readout circuit. The principles of skimming and partitioning are illustrated in Fig. 1.7. Photo-generated charge is integrated in a potential well formed under gates  $V_{\text{store}}$  and  $V_{\text{part}}$ . Charge skimming is a process of setting the  $V_{\text{skim}}$  potential barrier at an appropriate level and skimming only the overflowing charge into the integrating  $\phi_{\text{CCD}}$  well. Charge partitioning is a process of dividing the input charge into two packets by raising the  $V_{\text{part}}$  potential. The small charge packet is passed to the transport CCD, with or without skimming. The large packet is dumped through the drain diode  $V_{\text{drain}}$ . In this way, a gain reduction is realized.

Skimming and partitioning requires integrating the complete signal prior to background suppression and would not alleviate the recovery of weak image.

Figure 1.7 Schematic of skimming and partitioning

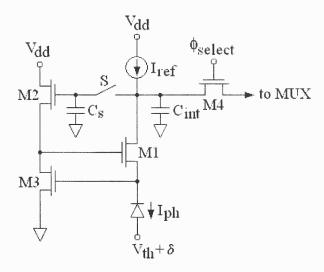

# 1.6.2 Dynamic Current Mirror Buffered Direct Injection (DCM-BDI)

Figure 1.8 shows the schematic of DCM-BDI [6]. It operates in two phases, calibration phase and integration phase. During the calibration phase, signal flux is blocked and switch S is on. The gate voltage of M2 is maintained at a level necessary to sink the reference current through the readout M1 and the photodiode. At same time the integration capacitor is reset. This is possible if the detector substrate is held at the level slightly above the threshold of the active M3. At integration cycle, only the signal-induced current is integrated through the way of BDI because the detector current is compensated during calibration.

There are several drawbacks of this approach. First, detector dark current is forced to be the reference current. It is dangerous to the diode if the dark current is lower than the reference current. Second, the reference current can hardly keep constant if the M1's drain voltage is going down due to integration. A transistor biased at a reference voltage

usually provides the reference current source of this scheme. The lowering voltage at this node will increase the reference current, yielding the loss of signal.

Figure 1.8 Schematic of a DCM-BDI

There are several drawbacks of this approach. First, detector dark current is forced to be the reference current. It is dangerous to the diode if the dark current is lower than the reference current. Second, the reference current can hardly keep constant if the M1's drain voltage is going down due to integration. A transistor biased at a reference voltage usually provides the reference current source of this scheme. The lowering voltage at this node will increase the reference current, yielding the loss of signal.

# 1.6.3 Current Memory

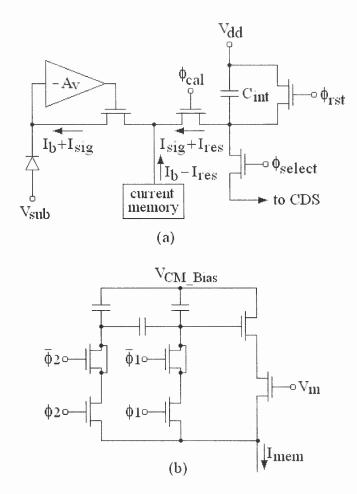

Current memory also operates in two phases, calibration phase and imaging phase. During calibration, signal flux is blocked and background related current is led to an analog current memory circuit. During imaging, the background is sunk to the current memory circuit except for a small error current  $I_{res} = I_b - I_{mem}$  that flows into the integration node. Thus, the signal current plus the error current are fed to the integrator. In order to

eliminate the error current, the error current is also integrated on the integration capacitor after the current memorization is finished at calibration phase. By using correlated double sampling one can virtually eliminate the background. Fig.1.9 shows the schematic of current mode background subtraction (CMBS) [4].

**Figure 1.9** Schematic of current mode background subtraction (a) Circuit implementation of CMBS and (b) Circuit schematic of current memory with feedback suppression.

However, the sources of error current are the losing of the memory current due to using an analog memory and the current injection at the time of turning on the calibration switch (initial voltages are different at the integration node and the input node of the memory circuit). The worst feature of the method is that the error current could be a

function of the integration node voltage. In this case, the error current cannot be eliminated completely even CDS is employed lately, resulting in a FPN in the image.

## 1.6.4 Correlated Readout (CR)

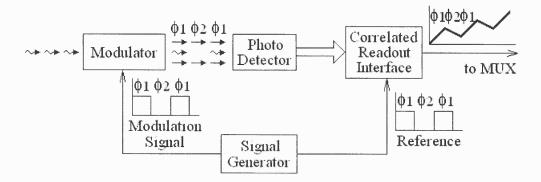

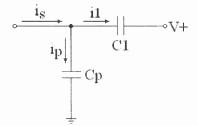

Correlated readout [7,10-12] has been studied since 1996 when Prof. Ken K. Chin and Prof. Haiming Wang at NJIT discussed about the solar magnetography where the signal due to Zeeman splitting is four orders less than background. CR integrates modulated signal by using a correlated integrator while rejecting unmodulated background. The principle of CR is shown in Fig.1.10. Photon flux is chopped by a modulator. Signal current plus background current will charge the integrator in one phase (when the modulator is on). Then background current will discharge the integrator in another phase (signal is blocked) with same duration time. Through charging and discharging the integrator many times, the background is cancelled out while the small signal can be gradually accumulated. Due to the increased integration time, the signal-to-noise ratio and dynamic range can be improved. An additional benefit is its capability of attenuating low frequency noise. In fact, correlated readout is the extension of phase sensitive detection (lock-in amplifier) to FPA area.

Figure 1.10 The principle of correlated readout

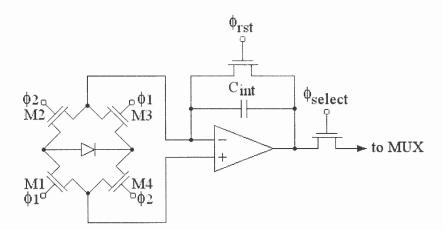

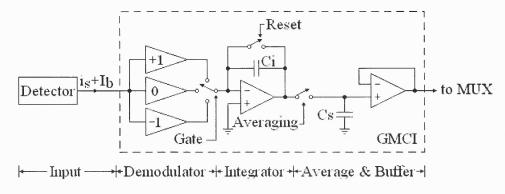

Figure 11 shows the correlated capacitive transimpedance amplifier (CCTIA) initially proposed to fulfill the function of CR. When \$\phi\$1 is enabled and \$\phi\$2 is disenabled, M1 and M3 turn on while M2 and M4 stay off. The detector is responding to the source signal as well as background so that all the current will be integrated in the integration capacitor. When \$\phi\$2 is enabled and \$\phi\$1 is disenabled, M2 and M4 turn on while M1 and M3 become off, and the capacitor will be discharged by the background related current only. This process can be repeated until significant signal charges are accumulated. However, this scheme has fetal drawback. The detector is not symmetrically biased in the two phases. In fact a detector is slightly reversely biased in one phase while it is slightly forward biased in another phase. For LWIR applications, it is not allowed to bias a detector forwardly. Another drawback of this approach is it cannot be used for array detectors since array detectors usually have a common subtraction node while the two terminals of a detector in CCTIA case are independent.

Figure 1.11 Correlated capacitive transimpedance amplifier

Correlated readout reads modulated AC signal and rejects DC and unrelated AC background. This is a preferred way for the measurement of single detector. Since AC

measurement needs to modulate the image source, this is what the second generation FPA tries to avoid because most natural scenes are unmodulated. For the special case of weak image under strong background, however, AC measurement will be the most effective method because the modulated weak image can be separated from the strong background. Furthermore, there are urgent growing requirements of capturing laser-induced weak repetitive images in bioscience.

The readout circuits have been briefly reviewed. More discussion about readout circuitries can be found in some review papers [31-33]. This thesis will focus to construct the general model and the theory of gated multi-cycle integration (GMCI) FPA for repetitive images and to demonstrate the functions of GMCI with a switched capacitor integrator.

### 1.7 Demands for Repetitive Imaging

Pulsed laser-induced fluorescence or Raman imaging plays an important role in the studies of biology, biochemical and biomedicine samples. Issues such as cancer-related tumors or lesions, spectra of a single molecule, the sequence of DNA are needed to trace. Current technologies of spectroscopic imaging are confocal laser scanning microscopy and gated intensifier CCD. The former takes image point by point through a photomultiplier tube (PMT), lacks of efficiency, although it has the great advantage of imaging with fine depth resolution. The latter uses a CCD to form the second image from the primary image captured by the intensifier, losing the resolution that the CCD can provide. The wavelength in both cases is limited by the responses of PMT and intensifier. Their cutoff wavelength could be up to 1.1 μm. Since the image signal is usually weak and

repetitive, current high performance FPA systems cannot directly take image due to the way of readout.

#### 1.8 Outline of this Dissertation

In the next chapter, the general model and the theory of gated multi-cycle integration is presented for FPA taking repetitive image with any duty of cycle. The general model includes multi-point summation, multi-point subtraction and multi-sample averaging. The analytic theory of (GMCI) unifies the theories of gated integration, phase-sensitive detection, multiple summations and averaging. In Chapter 3, a version of GMCI–a switched capacitor integrator (SCI)—is proposed to fulfill the function of GMCI. Chapter 4 deals with the design issue of SCI. Experimental results are presented in Chapter 5. Extremely weak signal 5 orders less than background is measured through multi-cycle integration. Conclusions, including proposed further work are discussed in Chapter 6.

#### **CHAPTER 2**

### THEORY OF GATED MUTI- CYCLE INTEGRATION (GMCI)

#### 2.1 Introduction

The signal or imaging source may be modulated or unmodulated. When an unmodulated source is measured, the signal must compete with the total low-frequency noise sources. However, when the source is modulated, the signal may be measured at the modulation frequency, far away from those large noise sources. Thus, the ratio of signal to noise (S/N) can be greatly improved by using modulated sources.

The lock-in amplifier [34-36], invented by Dicke [34] in 1946, is a powerful technique for the recovery of modulated weak signal, which may be swamped by the interference of noise that is much larger than the signal of interest. The invention of the lock-in amplifier has had a huge impact in modern science and technology. The core of lock-in amplification is the concept of phase sensitive synchronous detection or phase sensitive detection (PSD).

In order to recover the modulated signal, a demodulator must be used in the measurement system. The demodulator recovers the modulated signal and suppresses background and interference. In the case of the lock-in, the demodulator opens half window for signal and half window for background subtraction.

The repetitive signal, however, may appear briefly during each cycle, as in the measurement of the spin-lattice relaxation time (T<sub>1</sub>) in nuclear magnetic resonance imaging (MRI) [37]. The boxcar averaging [37-40], also called gated integration (GI), is employed to deal with the recovery of repetitive signal with low cycle duty. A typical

application of boxcar integration is the measurement of fluorescence induced by laser pulses. It becomes a powerful tool in the research fields of biology, biophysics, biochemistry and biomedicine.

Photon counting [41] is another technique used to record very low signal intensities with very high sensitivity and a large dynamic range. It can detect a single incident photon or particle with energy not less than visible light by using a high-gain photo-multiplier tube (PMT) and a discriminator. The discriminator is used to reject most low-level noise by setting a threshold.

However, the lock-in amplifier, gated integrator and photon counting are developed for a single detector. Modulated images have never been directly taken by solid-state camera so far. It is virtually impossible to put the quite sophisticated lock-in amplifier, boxcar averaging, or photon counting circuitry into a pitch of around  $50\times50$   $\mu\text{m}^2$ .

In practice, the need for taking the modulated or repetitive image is becoming urgent in the fields of biotechnology. The well-developed FPA is hardly involved due to its single-cycle integration. With the advanced microelectronic technologies in hand, it is time to develop gated multi-cycle integrator for signal modulated FPAs.

By introducing a general model of gated multi-cycle integration (GMCI), a concept containing PSD and GI, the theory of GMCI will be developed specifically for FPA dealing with pulsed or modulated image sources in this chapter. Before this is done, a brief review of the lock-in and the gated boxcar-averaging techniques of measuring modulated signals is given for the purpose of a better understanding GMCI technology.

In the next chapter, a simple switched capacitor integrator circuit, which can be operated in modes of PSD and GI, will be employed to fulfill the functions of GMCI.

# 2.2 Basic Concepts of Lock-in Amplifier

A lock-in amplifier uses phase-sensitive detection to improve the signal-to-noise ratio. The analytical signal to be measured is modulated at some reference frequency. The lock-in-amplifier then amplifies only the component of the input signal at the reference frequency, and filters out all other frequencies, i.e., noise.

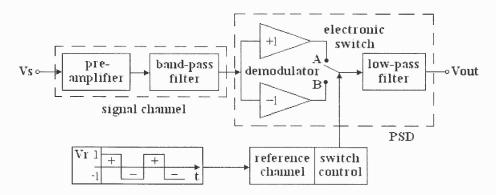

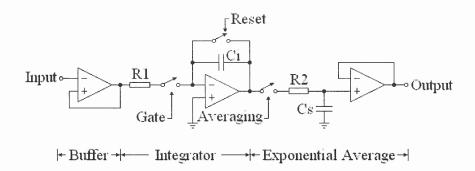

The diagram of a basic lock-in amplifier is shown in Fig. 2.1. The basic requirements for look-in amplifier are the pre-amplifier followed by a band-pass filter, then the phase sensitive detector. A pre-amplifier is necessary to bring the small signal to a level sufficient to overcome the noise induced by the amplifier, band-pass filter and PSD. The band-pass filter rejects unnecessary noise and interference from higher odd harmonics of reference frequency.

Figure 2.1 Block diagram of a basic lock-in amplifier

The main components of PSD are the demodulator and the low pass filter as shown in Fig. 2.1. The key to the operation of the demodulator is the two-state switch,

which is controlled electronically from a reference voltage. The switch changes position between points A and B as the reference changes polarity. This action gives a systematic change of gain between +1 and -1 in the signal path, resulting in demodulation of the signal at the reference frequency to a DC component. The low pass filter recovers the dc component. The PSD passes only the signal at the reference frequency if all the higher harmonic frequencies are filtered before they go through it.

An intuitive way to understand the operation of lock-in amplifier can be found in reference [36]. Here the mathematical language is presented to describe the system. Assume that the frequency-response functions for the pre-amplifier plus band-pass filter and low-pass filter are  $H_P(j\omega)$  and  $H_L(j\omega)$ , respectively. From symmetry  $H_P(j\omega) = H_P(-j\omega)$ , and  $H_L(j\omega) = H_L(-j\omega)$ . The reference angular frequency is  $\omega_r$ . Moreover, consider the reference waveform with equal time in its two phases. By using Fourier series representation, the functioning of the demodulator can be expressed by:

$$V_r(t) = \frac{2}{\pi i} \sum_{k=-\infty}^{\infty} \frac{1}{2k+1} e^{j(2k+1)\omega_r t}$$

(2.1)

Now if the input signal is

$$V_i(t) = e^{j\omega t} (2.2)$$

Then, the voltage at the output of the band-pass filter can be written as

$$V_{po}(t) = H_p(j\omega)e^{j\omega t}$$

(2.3)

Therefore, the voltage input at the low-pass filter is

$$V_{Li}(t) = \frac{2}{\pi j} H_P(j\omega) \sum_{k=-\infty}^{\infty} \frac{1}{2k+1} e^{j[(2k+1)\omega_r + \omega]t}$$

(2.4)

The Fourier transform of  $V_{Li}(t)$  is found by

$$F_{Li}(j\varpi) = \frac{2}{\pi j} H_P(j\omega) \sum_{k=-\infty}^{\infty} \frac{1}{2k+1} \delta[\varpi - \omega - (2k+1)\omega_r]$$

(2.5)

The Fourier transform at output is

$$F_{Lo}(j\varpi) = \frac{2}{\pi j} H_P(j\omega) \sum_{k=-\infty}^{\infty} \frac{1}{2k+1} \delta[\varpi - \omega - (2k+1)\omega_r] H_L(j\varpi)$$

(2.6)

The output voltage of the lock-in is obtained by the inverse Fourier transform of (2.6)

$$v_{o}(t) = \frac{2}{\pi i} H_{P}(j\omega) \left\{ \sum_{k=-\infty}^{\infty} \frac{1}{2k+1} H_{L} \{ j[\omega + (2k+1)\omega_{r}] \} e^{j(2k+1)\omega_{r}t} \right\} e^{j\omega t}$$

(2.7)

In this thesis, a base gain function of a system is defined by its output corresponding to the base input of  $e^{j\omega t}$ . A base gain function differs from a transfer function by that it is a function of both frequency and time in general case. Hence, the base gain function of the lock-in is

$$G_{Lock-in}(j\omega,t) = H_{P}(j\omega) \left\{ \frac{2}{\pi i} \sum_{k=-\infty}^{\infty} \frac{1}{2k+1} H_{L} \{ j[\omega + (2k+1)\omega_{r}] \} e^{j(2k+1)\omega_{r}t} \right\} e^{j\omega t}$$

(2.8)

Obviously, the base gain function of the PSD is in the form of

$$G_{PSD}(j\omega,t) = \frac{2}{\pi i} \sum_{k=1}^{\infty} \frac{1}{2k+1} H_L\{j[\omega + (2k+1)\omega_r]\} e^{j[(2k+1)\omega_r + \omega]t}$$

(2.9)

Now, for any input V<sub>in</sub>(t), the output will be given by

$$V_o(t) = \int_{-\infty}^{\infty} F_{in}(j\omega) G_{Lock-in}(j\omega, t) d\omega$$

(2.10)

where,  $F_{in}(\omega)$  is the Fourier transform of  $V_{in}(t)$ , which is given by

$$F_{in}(j\omega) = \frac{1}{2\pi} \int_{-\infty}^{\infty} V_{in}(t)e^{-j\omega t}dt$$

(2.11)

A typical example of input is

$$V_{in}(t) = \sin(\omega_r t + \varphi) \tag{2.12}$$

From (2.11), (2.10) and (2.8), it can be found

$$F_{in}^{*}(j\omega) = \frac{1}{2j} \left[ \left( \delta(\omega - \omega_r) e^{j\varphi} - \delta(\omega + \omega_r) e^{-j\varphi} \right) \right]$$

(2.13)

$$V_{o,\sin}^{Lock-in}(t) = \frac{2}{\pi} \left| H_p(j\omega_r, t) \right| H_L(0) \left| \cos(\varphi) \right|$$

(2.14)

For a lock-in system, the equivalent bandwidth is determined by the bandwidth of the low-pass filter, which usually is much narrower than  $\omega_r$ . Therefore, the following approximation is always satisfied

$$|H_L\{j[\omega + (2k+1)\omega_r]\}| H_L\{j[\omega + (2k'+1)\omega_r]\}| \approx 0 \quad \text{if} \quad k \neq k'$$

(2.15)

In this thesis, the transmission windows or the transmission function of a system is defined by  $\sqrt{G_x G_x^*}$ . For the lock-in system and the PSD, they are given by

$$T_{PSD}(\omega) = \sum_{k'=0}^{\infty} \frac{2}{(2k'+1)\pi} \left| H_L\{j[\omega - (2k'+1)\omega_r]\} \right|$$

(2.16)

$$T_{Lock-in}(\omega) = \sum_{k'=0}^{\infty} \frac{2}{(2k'+1)\pi} |H_{L}\{j[\omega - (2k'+1)\omega_{r}]\}| |H_{P}(j\omega)|$$

(2.17)

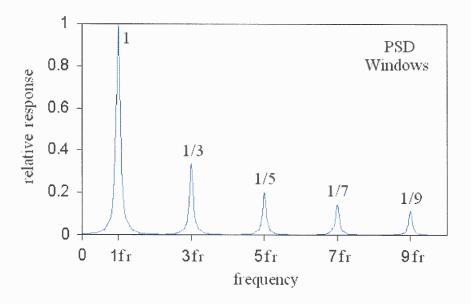

**Figure 2.2** Transmission windows of a switching PSD

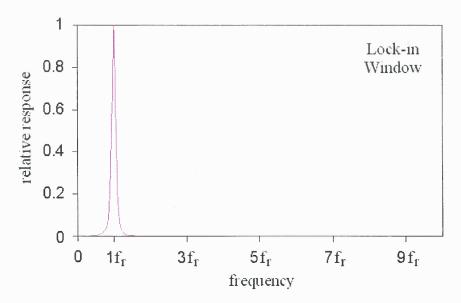

Figures 2.2 and 2.3 depict these windows. Obviously, PSD is not only sensitive to the signal at the reference frequency, but is also susceptible to interference from higher odd harmonic frequencies. For this reason, the band-pass filter is put before the PSD in order to suppress these windows.

Figure 2.3 The transmission window of Lock-in

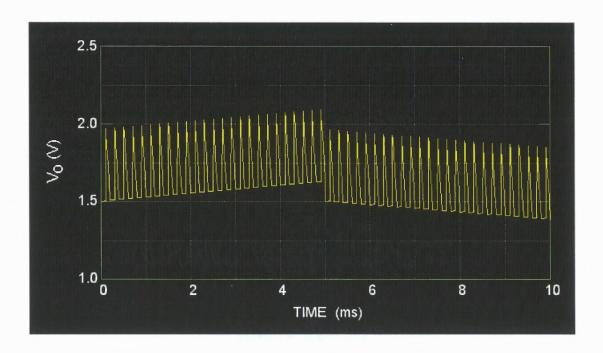

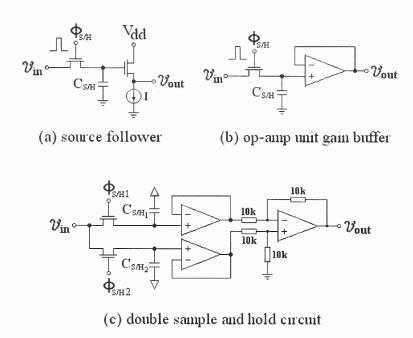

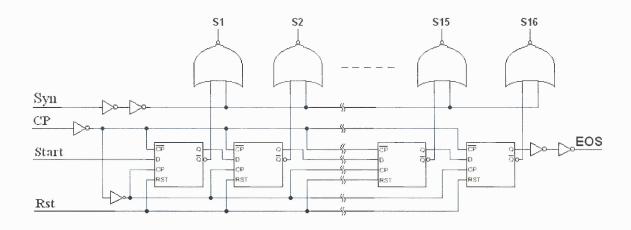

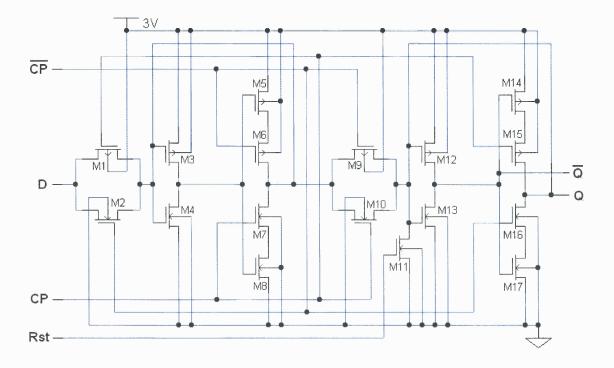

#### 2.3 Gated Integration