# **Copyright Warning & Restrictions**

The copyright law of the United States (Title 17, United States Code) governs the making of photocopies or other reproductions of copyrighted material.

Under certain conditions specified in the law, libraries and archives are authorized to furnish a photocopy or other reproduction. One of these specified conditions is that the photocopy or reproduction is not to be "used for any purpose other than private study, scholarship, or research." If a, user makes a request for, or later uses, a photocopy or reproduction for purposes in excess of "fair use" that user may be liable for copyright infringement,

This institution reserves the right to refuse to accept a copying order if, in its judgment, fulfillment of the order would involve violation of copyright law.

Please Note: The author retains the copyright while the New Jersey Institute of Technology reserves the right to distribute this thesis or dissertation

Printing note: If you do not wish to print this page, then select "Pages from: first page # to: last page #" on the print dialog screen

The Van Houten library has removed some of the personal information and all signatures from the approval page and biographical sketches of theses and dissertations in order to protect the identity of NJIT graduates and faculty.

#### ABSTRACT

### **BROADBAND WHOLE PACKAGE FDTD SIMULATION**

by

### Shenjun (Peter) Li

Whole package analysis is becoming more and more important with the rapid expansion of high frequency electronics. The motivation of this thesis is to find and implement a new method for broadband whole package simulation. 3-dimension (3-D) whole package Finite Difference Time Domain (FDTD) simulation result was first reported in detail in this thesis.

The FDTD method is a widely used full-wave time-domain simulation method used in the design and analysis for electromagnetic (EM) systems, such as antennas, wave propagating, and microwave circuits. Absorbing boundary condition (ABC), such as the perfect matched layer (PML) method, makes it possible to accurately analyze an EM structure involving complicated wave propagation in three-dimensional domain. Instead of running simulation at each frequency, time-domain solution gives complete frequencydomain response including coupling and dispersion effects. Chapter2 introduces the principle of FDTD and two important boundary condition methods. It also discusses the nonuniform grid numerical error, and gives the FDTD simulation and theoretical result.

Flip chip package is one of the most important package types. Chapter 3 presents a wide band approach for characterizing multiple flip chip interconnects by the FDTD method. Detailed analysis for electrical performance for frequencies up to 40 GHz has been performed with variations of interconnect bumps (ball cross section and via cross section). Flip chips of three sizes are studied using FDTD method in detail. The relationship between reflection loss, via pad length, ball cross-section and via cross

section is tabulated for future packaging design. Based on the simulation results, some design approaches are proposed for packaging structure operating at near 40 GHz.

FDTD whole package simulation method is introduced at the beginning of Chapter 4, followed by discussion how to implement this method to specific packages. The packages used to host circuit in chapter 4 are microstrip line and flip chip interconnects. The embedded circuits are ideal transmission line and an HP amplifier. Transient effects are observed when an amplifier is hosted in a package. Most of the simulations are processed under three-dimensional environment; two-dimensional simulation is used for reference standard. All these results were first reported by the author of this thesis and his collaborators.

### **BROADBAND WHOLE PACKAGE FDTD SIMULATION**

by

Shenjun (Peter) Li

A Dissertation Submitted to the Faculty of New Jersey Institute of Technology and Rutgers, The State University of New Jersey – Newark In Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy in Applied Physics

**Federated Physics Department**

May 2001

Copyright ©2001 by Shenjun (Peter) Li

ALL RIGHT RESERVED

### **APPROVAL PAGE**

### **BROADBAND WHOLE PACKAGE FDTD SIMULATION**

### Shenjun (Peter) Li

| Dr. Ken Chin, Dissertation Advisor                                             | Date |

|--------------------------------------------------------------------------------|------|

| Chair of Doctoral Committee                                                    |      |

| Professor of Physics                                                           |      |

| Director for the Joint NJIT-Rutgers(Newark) Applied Physics M.S./Ph.D. Program |      |

| Acting Director for Materials Science and Engineering Program, NJIT            |      |

Dr. Wenquan Sui, Dissertation Co-Advisor Senior Scientist, Conexant Systems

Dr. Zhen Wu Associate Professor of Physics Rutgers, The State University of New Jersey – Newark

Dr. John C. Hensel Distinguished Research Professor Applied Physics, NJIT

Dr. Hui Wu Technical Stuff Lucent Technology

Date

Date

Date

Date

### **BIOGRAPHICAL SKETCH**

| Author: | Shenjun (Peter) Li                      |

|---------|-----------------------------------------|

| Degree: | Doctor of Philosophy in Applied Physics |

| Date:   | May 2001                                |

### **Undergraduate and Graduate Education**

- Doctor of Philosophy in Applied Physics

Federated Physics Department

New Jersey Institute of Technology and Rutgers,

The State University of New Jersey Newark, NJ, 2001

- Bachelor of Science in Materials Science University of Science and Technology of China, P.R. China 1990

### Major: Applied Physics

### **Publications:**

- Li, P., Wu, H., Li, T, Chin, K., Sui, W., "Broadband Time-Domain Characterization of Multiple Flip-Chip Interconnects," accepted, *The IEEE MTT-S International Microwave Symposium* 2001 (IMS2001) May, 2001

- Li, P., Li, T, Wu, H., Chin, K., Sui, W.," FDTD Simulation of Multiple Flip Chip Interconnects", accepted, 2001 Asia-Pacific Radio Conference, August, 2001

- Tang, L., Li, S., Chapter One of Science and Technology of Crystal Growth, China Science Press, 1997

- Li, S., Liu, L., Wang, Z., "Growth and characteristics of Mg<sub>2</sub>SiO<sub>4</sub> :Ti crystal", Journal of Crystal Growth V139, pp327-331, 1994

- Li, S. et al "Optical Properties of LaMgAl11019:Ti Crystal", Journal of Synthetic Crystals, Vol. 23, 1994

- Liu, L., Wang, Z., Li, S. "Growth and Characteristics of Mg2SiO4:Cr crystal", *The* 11<sup>th</sup> International Conference of Crystal Growth, 1991

To my daughter Denice, my wife and my parents

### ACKNOWLEDGEMENT

First, I would like to express my appreciation and thankfulness to my co-advisor, Dr. Wenquan Sui, who has been helping me from the beginning of my FDTD research work. Dr Tong Li is an expert on FDTD simulation, who has given me a lot of suggestions during my graduate study. I could not finish my research study without Dr Sui and Dr Li's help. With Dr. Hui Wu's help, I can finish part of the research study in Bell Labs, and I express my thanks to him for giving me this opportunity.

Many people have also helped with the production of this thesis, in particular, Dr. Fangjun Wu, Mr. Zhenxiang Pan and Bill Wang.

Dr. Zhen Wu and Dr. John C. Hensel gave me knowledge on quantum mechanics and classical mechanics when I took their courses. I really enjoyed the time when I attended their lectures. Thanks to them to serve as members of my doctoral committee.

Last but not least, I would like to thank Dr. Chin. Without his constant guidance and encouragement it would not have been possible for me to complete this dissertation.

### **TABLE OF CONTENTS**

| Cł | napter                                                 | Pa                                                                   | age |

|----|--------------------------------------------------------|----------------------------------------------------------------------|-----|

| 1  | 1 OVERVIEW OF FDTD AND BROAD BAND PACKAGE SIMULATION 1 |                                                                      |     |

|    | 1.1                                                    | ntroduction of Numerical Electromagnetic Modeling Techniques         | 1   |

|    | 1.2                                                    | Finite Difference Time Domain Technique                              | 2   |

|    | 1.2                                                    | 2.1 The Prototype of FDTD                                            | 2   |

|    | 1.2                                                    | 2.2 Development of FDTD                                              | 3   |

|    | 1.3 l                                                  | Planar Package Simulation                                            | 5   |

|    | 1.3                                                    | 3.1 Flip Chip Interconnect and FDTD Method                           | 5   |

|    | 1.3                                                    | 3.2 Whole Package Simulation                                         | 6   |

| 2  |                                                        | CIPLES OF THE FDTD METHOD AND NON-UNIFORM GRID<br>ERICAL ERROR       | 9   |

|    | 2.1                                                    | Introduction                                                         | 9   |

|    | 2.2                                                    | The Yee FDTD                                                         | 10  |

|    | 2.3                                                    | Boundary Condition Techniques                                        | 14  |

|    |                                                        | 2.3.1 Mur's ABCs                                                     | 15  |

|    |                                                        | 2.3.2 Perfect Matched Layer (PML)                                    | 16  |

|    | 2.4                                                    | PEC Cell Type                                                        | 21  |

|    | 2.5                                                    | Numerical Error for Non-uniform Grid of Electromagnetic System       | 23  |

| 3  |                                                        | DBAND TIME-DOMAIN CHARACTERIZATION OF MULTIPLE FLIP<br>INTERCONNECTS | 29  |

|    | 3.1                                                    | Introduction                                                         | 29  |

|    | 3.2                                                    | Using FDTD Method on The Flip Chip Simulation                        | 29  |

|    | 3.3                                                    | Simulation and Discussion                                            | 31  |

### **TABLE OF CONTENTS**

### (Continued)

| Chapter |         | Page                                                 |    |

|---------|---------|------------------------------------------------------|----|

|         | 3.3.1   | Small Size Flip Chip                                 | 31 |

|         | 3.3.2   | Middle Size Flip Chip                                | 36 |

|         | 3.3.3   | Large Size Flip Chip                                 | 41 |

| 3.4     | Conclu  | isions                                               | 52 |

|         |         | KAGE SIMULATION WITH LUMPED ELEMENT                  | 53 |

| 4.1     | Introdu | uction                                               | 53 |

| 4.2     | Lumpe   | ed Current Algorithm                                 | 54 |

| 4.3     | Broad   | Band Package with Lumped Elements                    | 56 |

|         | 4.3.1   | S parameter of Embedded Circuit                      | 56 |

|         | 4.3.2   | Absorbing Cube                                       | 58 |

|         | 4.3.3   | Equation Derivation of Whole Package Simulation      | 58 |

| 4.4     | 3-D N   | fulti-Port Circuit Modeling in FDTD Field Simulation | 64 |

|         | 4.4.1   | Microstrip Line 3D Simulation                        | 64 |

|         | 4.4.2   | Flip Chip 3D Simulation                              | 70 |

| 4.5     | Conclu  | isions                                               | 76 |

| REFERE  | NCES    |                                                      | 83 |

### LIST OF TABLE

7

| Tabl | e P      | age |

|------|----------|-----|

| 2.1  | PEC type | 21  |

### LIST OF FIGURES

| Figu | re P                                                                                                                        | age |

|------|-----------------------------------------------------------------------------------------------------------------------------|-----|

| 2.1  | Non-Uniform FDTD grid                                                                                                       | 12  |

| 2.2  | Three layers: vacuum, PML, conducting wall                                                                                  | 19  |

| 2.3  | Thin conductor rectangle's PEC type                                                                                         | 22  |

| 2.4  | TM mode wave propagates in the interface of two different media                                                             | 24  |

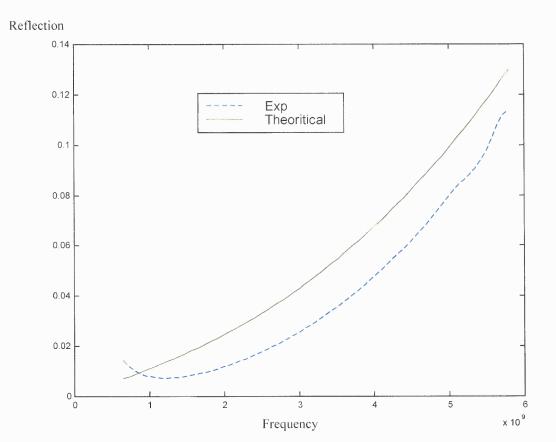

| 2.5  | FDTD simulation result against theoretical result for non-uniform grid 1mm to 10mm                                          | 27  |

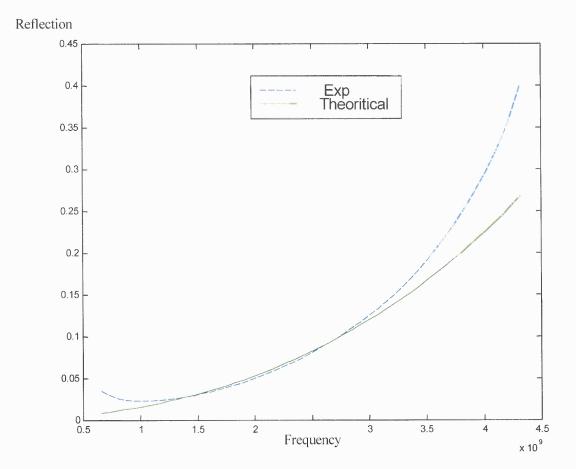

| 2.6  | FDTD simulation result against theoretical result for non-uniform grid 1mm to 20mm                                          | 28  |

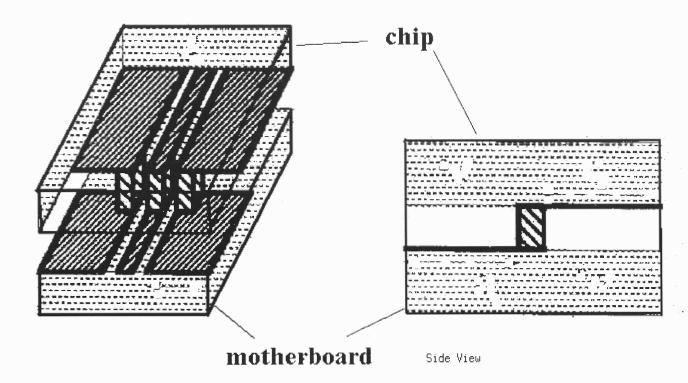

| 3.1  | Small size flip chip structure                                                                                              | 32  |

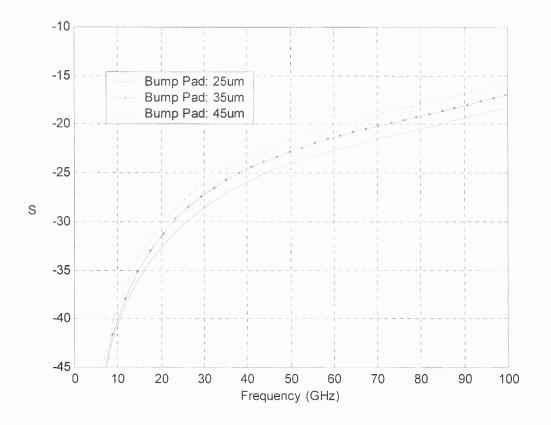

| 3.2  | Return Loss of small size CPW with dielectric constant =12.3, bump pad =25, 35 and 45 um                                    | 33  |

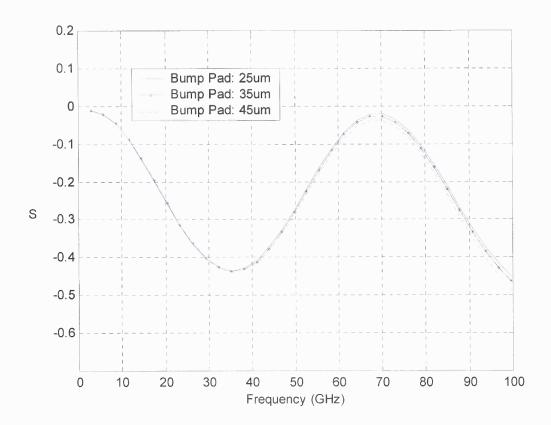

| 3.3  | Insertion loss of small size CPW                                                                                            | 34  |

| 3.4  | Small size CPW with dielectric filler, which dielectric constant=9.6                                                        | 35  |

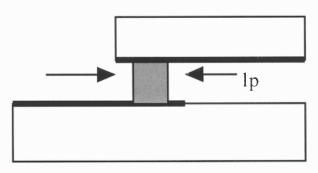

| 3.5  | Flat flip chip structure                                                                                                    | 37  |

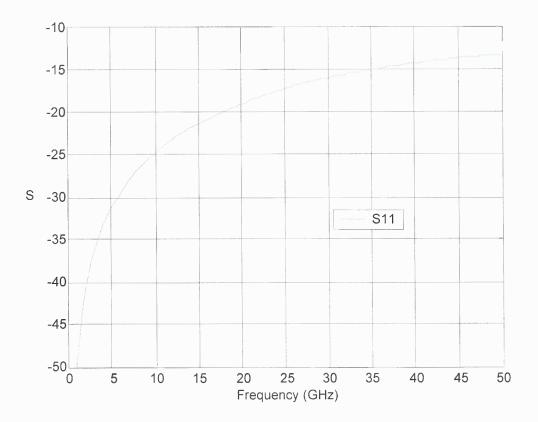

| 3.6  | FDTD simulation result for flat structure                                                                                   | 38  |

| 3.7  | Top view of single resonant structure                                                                                       | 39  |

| 3.8  | Single resonance flip chip transition design                                                                                | 40  |

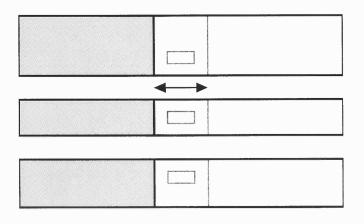

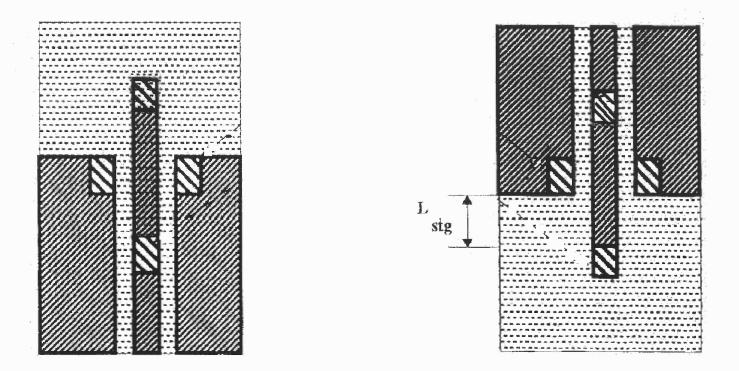

| 3.9  | Staggered flip chip structure                                                                                               | 42  |

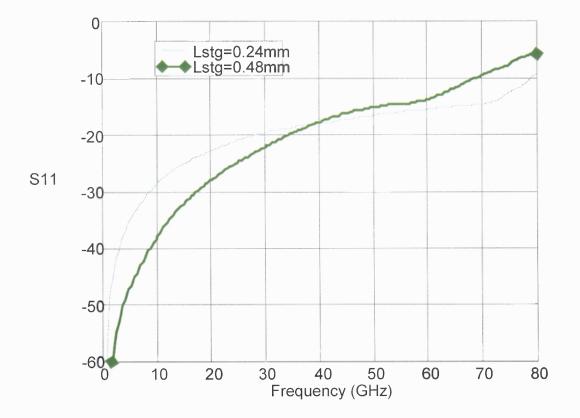

| 3.10 | FDTD simulation result of staggered structure with staggered distance 0.24 and 0.48mm                                       | 43  |

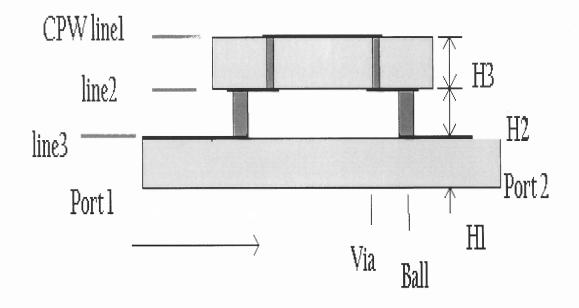

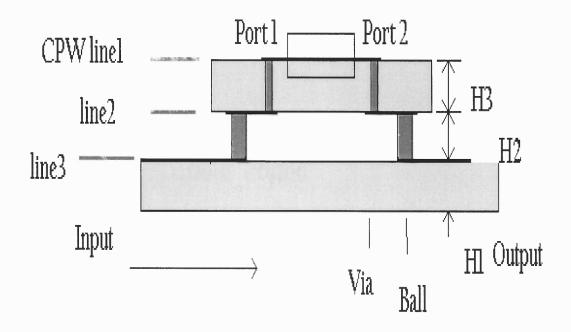

| 3.11 | Side view of the three layer structure. H1, H2 and H3 are 15 mils. The single arrow stands for the signal feeding direction | 44  |

### LIST OF FIGURES (Continued)

| Figure | Participant Partic | age |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

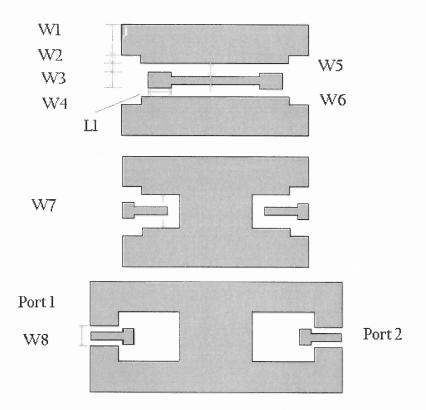

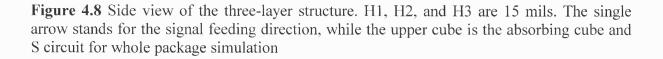

| 3.12   | Top view of three CPW layers. W1, W2, W3 and W4 are 30, 10, 6, and 16 mils, respectively                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 46  |

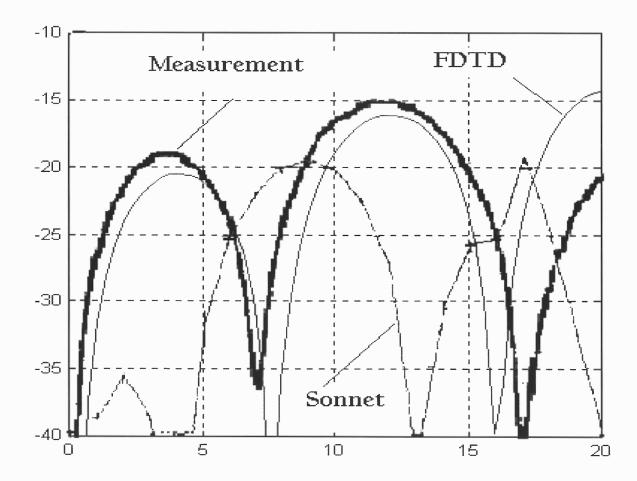

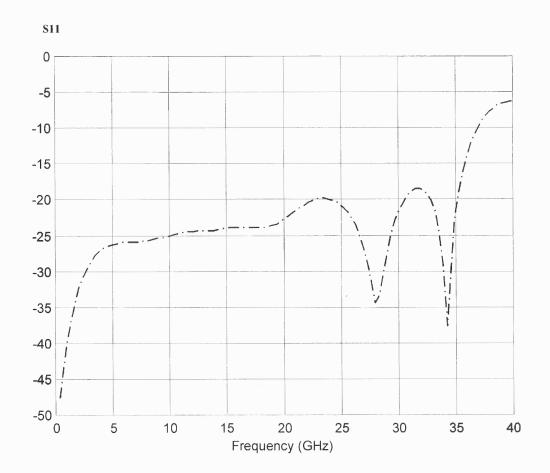

| 3.13   | Comparison of $S_{11}$ , in dB vs. frequency in unit of GHz, from measurement<br>and Sonnet simulation with FDTD result. W5, W6, W7, W8 and L1 are 4,<br>8, 24, 16 and 40 mils, respectively                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 47  |

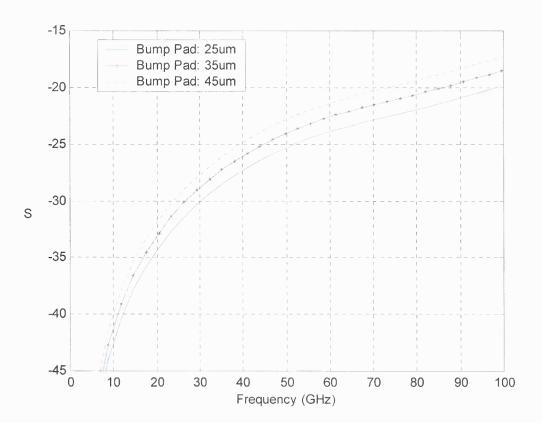

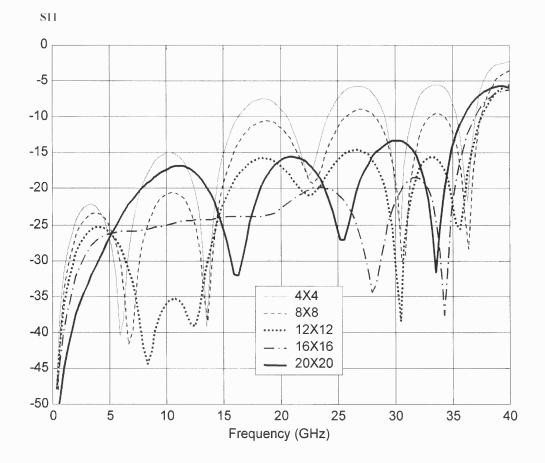

| 3.14   | Reflection Loss for Different ball cross section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 48  |

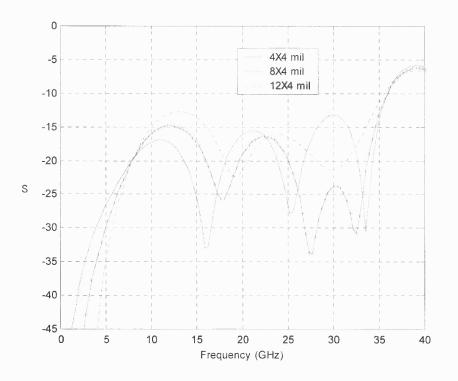

| 3.15   | S <sub>11</sub> for different via size along propagating direction. Via sizes are 4 x 4,<br>8 x 4 and 12 x 4 mil                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 50  |

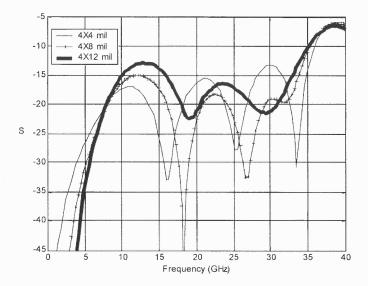

| 3.16   | S <sub>11</sub> for different via size perpendicular to propagating direction. Via sizes are 4x4, 4 x 8 and 4 x 12 mil                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 51  |

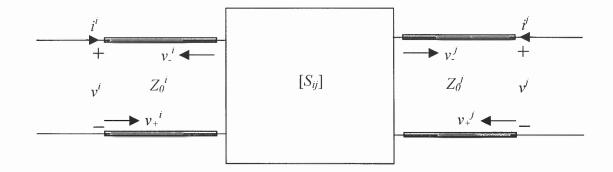

| 4.1    | Illustration of voltage and current at each port of an n-port system, where subscript + and – represent incident and reflected signal, respectively                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 57  |

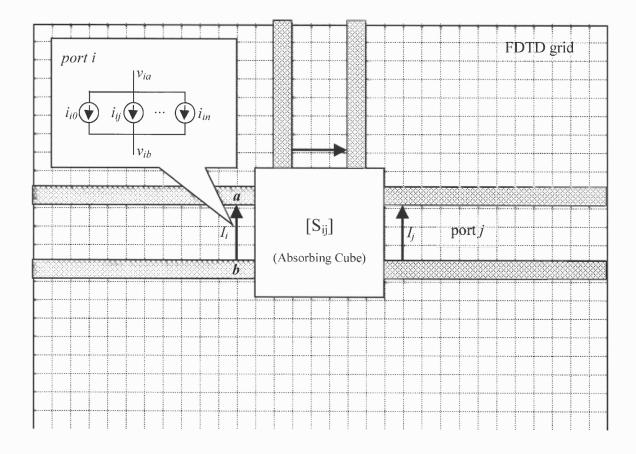

| 4.2.   | An n-port system is connected within a FDTD grid through sections of transmission line. Nodes $a$ and $b$ are the connecting points for port $i$ . The inlet shows the sum of current at this port where $i_{ij}$ is current contribution from port $j$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 59  |

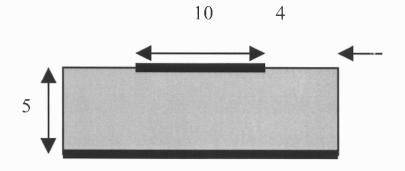

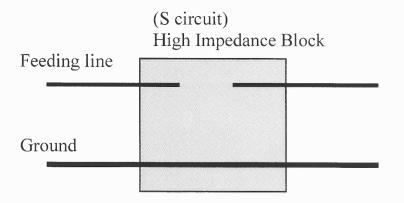

| 4.3    | The cross section of microstrip structure, top metal layer is feeding line,<br>bottom metal is ground layer, unit is cell size, one cell = 0.001m,<br>dielectric constant =14.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 66  |

| 4.4    | Side view of microstrip line whole circuit simulation structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 66  |

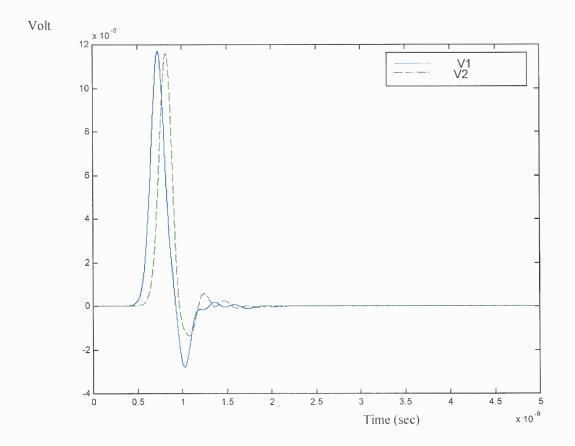

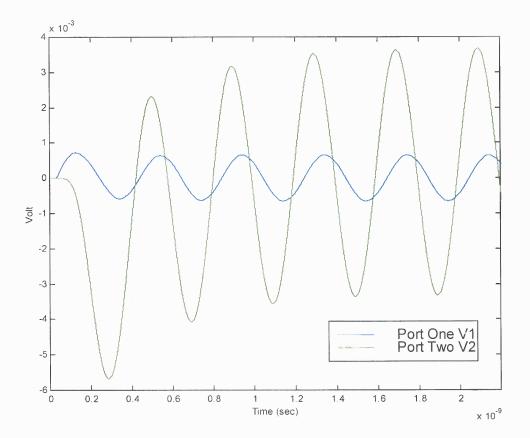

| 4.5    | Voltage at two circuit port of Microstrip line with ideal transmission line                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 67  |

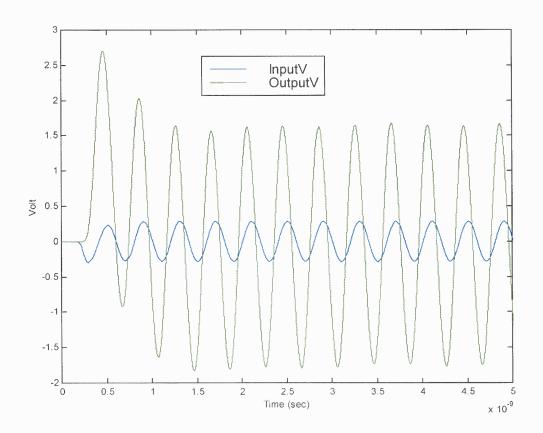

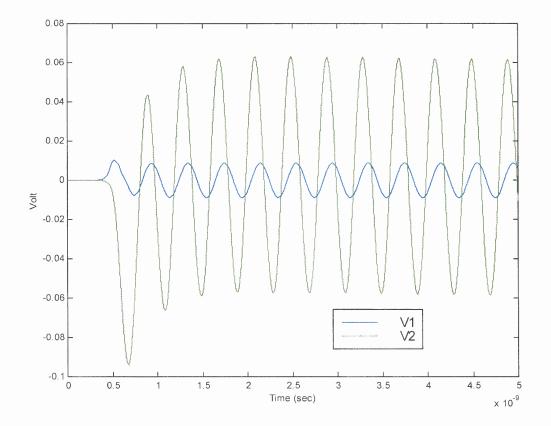

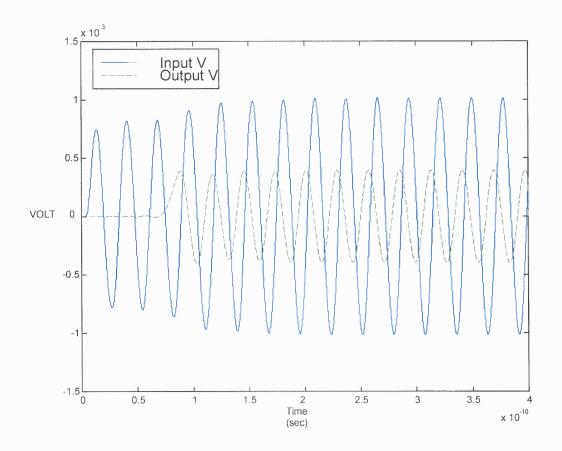

| 4.6    | Two dimension simulation for two port with Amplifier Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 68  |

| 4.7    | Microstrip line with sine wave hard source, 0.4 x 10-9, S circuit is an amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 69  |

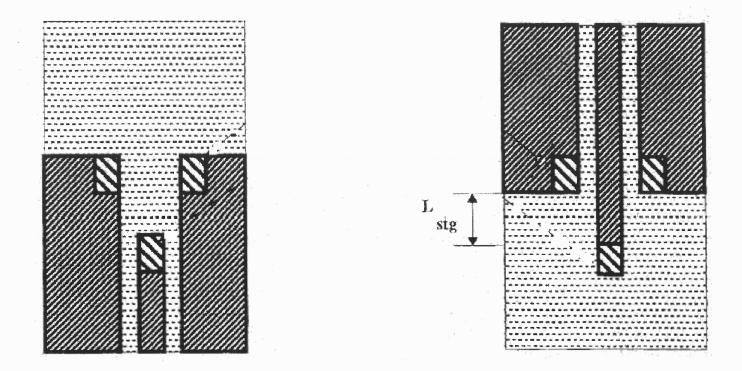

| 4.8    | Side view of the three-layer structure. H1, H2, and H3 are 15 mils. The single arrow stands for the signal feeding direction, the upper cubic is the absorb cubic for whole package simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 71  |

### LIST OF FIGURES (Continued)

| Figure | Pa Pa                                                                                                                                       | ige |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.9    | Top view of three CPW layers. W1, W2, W3 and W4 are 30, 10, 6, and 16 mils, respectively, the upper cubic is the absorbing cubic            | 72  |

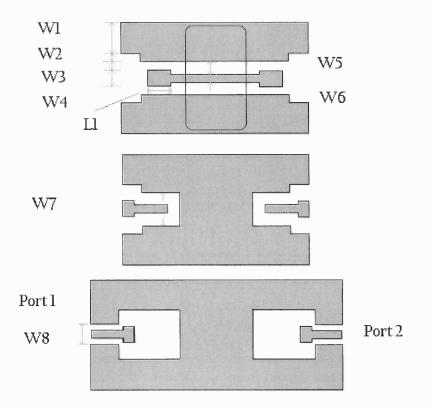

| 4.10   | The circuit port on flip chip interconnect, I <sub>port</sub> is the port current                                                           | 73  |

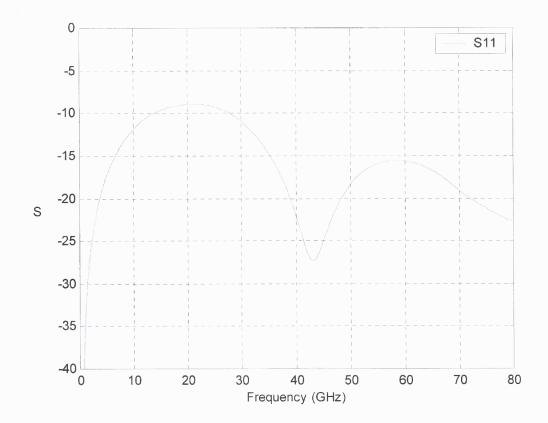

| 4.11   | FDTD simulation of flip chip package without embedded circuit                                                                               | 74  |

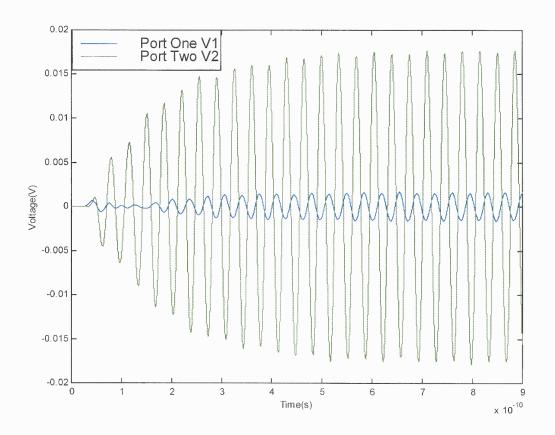

| 4.12   | Voltage distribution on the two ports of embedded amplifier circuit mounted<br>on flip chip package                                         | 75  |

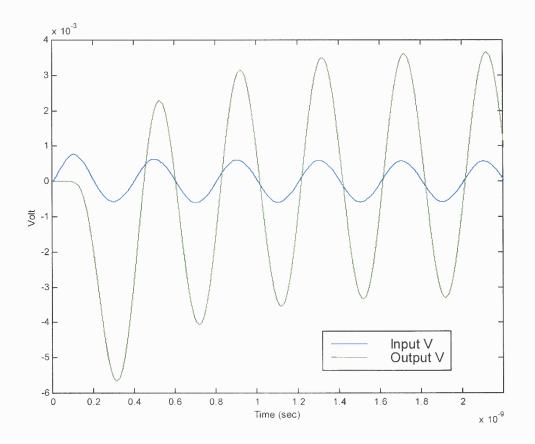

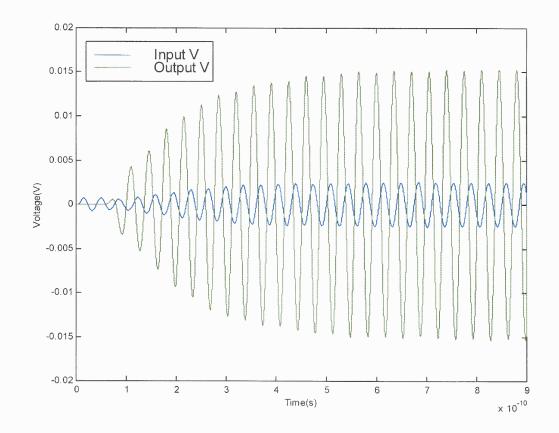

| 4.13   | Input and output simulation of whole flip chip package with mounted amp                                                                     | 77  |

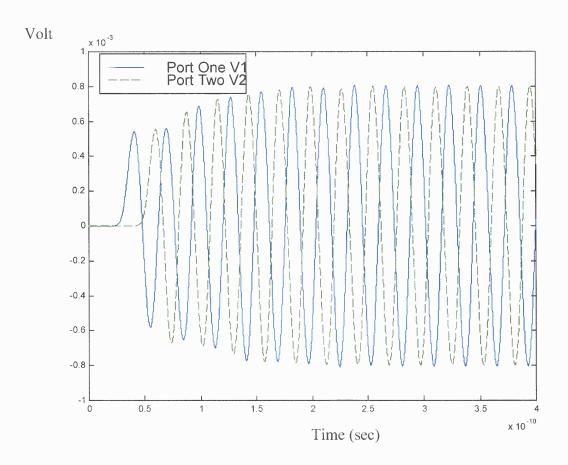

| 4.14   | Voltage distribution at port one and two of ideal transmission line embedded<br>in flip chip package with sine wave source, frequency=36GHz | 78  |

| 4.15   | Package with embedded ideal transmission line, the frequency of sine wave form , the frequency =36GHz                                       | 79  |

| 4.16   | Port Voltage of HP amplifier embedded in flip chip package with 28GHz sine wave source                                                      | 80  |

| 4.17   | Input and output voltage of whole flip chip package with embedded HP amplifier, sine wave source frequency is 28GHz                         | 81  |

### **CHAPTER 1**

#### **OVERVIEW OF FDTD AND BROAD BAND PACKAGE SIMULATION**

#### **1.1 Introduction of Numerical Electromagnetic Modeling Techniques**

Modeling of planar microwave structure has developed at an outstanding speed in the past decade. Current computer hardware and software technology makes it possible to implement algorithms based closer to the governing Maxwell equations of the EM system of interest. These algorithms have found widespread application in the areas of microwave devices and guiding structures, such as waveguides, resonators, junctions, microstrip, vias, interconnects, and transmission lines.

Computer methods for analyzing problems in EM generally fall into one of three categories, analytical techniques, numerical techniques, and expert systems. Their detailed definitions are as follows by Hubing [22].

Numerical techniques are the most accurate and important methods. They analyze the entire geometry which encloses the simulation domain as input. These numerical techniques can be broadly classified as frequency and time domain methods. The FDTD technique is a major time domain method. The FDTD method discretizes Maxwell's equations in space and time in a straightforward manner. FDTD results lend themselves well to scientific visualization methods since they tracks the time-varying fields throughout a volume of space. The FDTD method is a widely used full-wave timedomain simulation method used in the design and analysis for EM systems, such as antennas, wave propagating, and microwave circuits [50]. Berenger's PML method [5] makes it possible to accurately analyze an EM structure involving complicated wave propagation in three-dimensional domain. Instead of running simulation at each designs

1

frequency like a frequency-domain EM method, a time-domain solution gives full frequency-domain response up to the frequency of  $1/(2\Delta t)$ , where  $\Delta t$  is the minimum time difference. The response includes coupling and dispersion effects [49].

Finite difference frequency domain (FDFD) method and Method of Moments are frequency domain numerical techniques. FDFD technique results from a finite difference approximation of Maxwell's curl equations. In this case the time-harmonic versions of these equations are employed. Method of Moments uses basis and testing functions to discretize integral equations of electromagnetics. This numerical technique is based on weighted residuals method. It is not well-suited to the analysis of complex inhomogeneous geometries. The shortcoming for the frequency domain method is that one simulation can only obtain the system performance at one frequency. It should be run for numerous times if the system performance at different frequencies needs to be obtained.

Analytical techniques and expert systems are the other two computer methods for analyzing EM problems. Analytical techniques make simplifying assumptions about the geometry of a problem in order to apply a closed-form (or table look-up) solution. Expert systems estimate values for the parameters of interest based on a rules database. As system design and board layout procedures become more automated, analytical technique and expert system EM software will become more and more important.

### **1.2 Finite Difference Time Domain Technique**

#### 1.2.1 The Origin of FDTD

The Finite-Difference Time-Domain method, first proposed by Yee [57], is a simple and elegant way to discretize the differential form of Maxwell's equations. Maxwell (differential form) equations are simply modified to central-difference equations, discretized, and implemented in software. The equations are solved in a leap-frog manner; that is, the electric field is solved at a given instant in time, then the magnetic field are solved at the next instant in time, and the process is repeated over and over again. Although FDTD was simple, elegant and can be easily implemented, it did not gain much attention immediately after its publication. One reason was its high computational cost, and the others were the inherent limitations at that time, such as boundary conditions and numerical error.

#### **1.2.2 The Development of FDTD**

FDTD was initially used to solve the EM scattering problem by Taflove [49] in 1975, which is the first break-through in FDTD history. Taflove was among the first to rigorously analyze FDTD numerical errors [49]. Taflove was also the first to present the correct stability criteria for the original orthogonal-grid Yee algorithm [49]. In his papers, some critical problems were solved or improved. The correct derivation of the stability criterion was demonstrated; the lattice truncation conditions were proposed to handle the unbounded boundary.

ABC is often used to truncate the computational domain in space since the tangential components of the electric field along the outer boundary of the computational domain

cannot be updated using the basic Yee algorithm. The early ABC technique is radiation conditions [2]. ABC's can be grouped into those that are derived from differential equation based or material absorber. Mur [32] first applied an ABC technique of acoustic wave equations used by Engquist and Majda [13] in time domain electromagnetic field equations. Microstrip line was modeled with Mur's ABCs by Sheen [39]. Mur's ABCs and Berenger's PML [5] are differential and materials ABCs respectively, which essentially solved the problems of boundary conditions in FDTD.

PML gained attention immediately after Berenger's publication in 1993 [5]. Waveguide and multilayered planar circuit structure were studied with PML technique by Bahr [1], Reuter [38] and Verdu [55]. Berenger [4] used PML to solve interaction problems. Afterwards, he also reported evanescent waves in PML's [6] [3]. Katz [25] extended 2-D PML to 3-D PML, gave 3-D PML expression. Li [29] reported microstrip modeling by PML in non-uniform FDTD grid. Veihl [54], Fang [14], Sullivan [47] and Zhao [60] worked to improve PML performance by various formulations. PML makes it possible for high accuracy simulation and therefore has a major impact upon the FDTD modeling community.

Lumped elements were modeled into the FDTD formulation by adding an additional current term, named lumped current, in the Ampere's Law [44]. Dumey [12] and Picket-May [37] have extended Sui's 2D analysis to model full wave propagation in 3D circuits containing both active and passive elements. Based on Sui and Picket-May's work, SPICE-like circuit simulator can interface with FDTD simulation in time domain seamlessly, yielding stable and accurate result for nonlinear and active circuit [29,30]. Zheng [61] and Namiki [33] reported new algorithms that overcame the time step

restriction in FDTD calculation, thus further enhancing the incorporation of FDTD with SPICE-like simulator. Kuo [28] reported another lumped elements method, which was named as lumped voltage approach. This approach employs voltage sources to represent the lumped devices and generate electromagnetic fields based on Faraday's Law.

### **1.3 Planar Package Simulation**

#### 1.3.1 Flip chip interconnect and FDTD method

Flip-chip interconnect is a popular surface mount packaging technique because it does not have lateral leads or pins and has advantages, such as low electrical parasitic and low-cost, easy assembly through self-alignment, the smallest footprint, and the thinnest profile and weight [17][34][35].

One important topic for flip-chip package is how to enhance the transition performance at operating frequency range. There are many parameters which affect the performance, such as the interconnect bump length and width, the conductor on the board below the chip, the feeding line width of coplanar waveguide (CPW), and the ground to ground distance of CPW. Various methods have been applied to tune these parameters for optimal packaging performance [15][19][20][34], but they were limited to few structural variations. Solution of electromagnetic (EM) field is required for most of the packaging analyses, preferably broadband technique for high-speed circuitry. Flip-chip interconnect was studied by Sonnet simulation in comparison with experimental measurements [34]. The simulation result was quite different from measured results, probably because incomplete modeling of the contributing factors to the transition performance, such as via pad size, via cross section and height, and dielectric layer. Two CPW lines with one interconnect was analyzed recently [15]. They also gave broadband solutions. However, the structure with three CPW layers connected by two sets of interconnects (via and ball), which is more complicated and close to actual design, has not been studied in detail.

This thesis presents a wideband approach for characterizing multiple flip-chip interconnects by the FDTD method. Three different flip chip interconnects are studied in chapter 3. Detailed analysis for electrical performance for frequency up to 40 GHz has been performed with variations of interconnect bumps (ball cross section and via cross section). A three-layer CPW connected by two sets of interconnects (via and ball) is studied using FDTD method in detail. The relationship between reflection loss, via pad length, ball cross-section and via cross section is tabulated for future packaging design. Based on the simulation results, some design approaches are proposed for packaging structures operating at near 40 GHz.

#### **1.3.2 Whole Package Simulation**

Whole package simulation is the most import part of this thesis. Circuit designers are faced with the problem of devising packages with sufficient electrical properties for mounting circuits that perform at high speed. The accurate prediction of the electrical performance prior to fabrication has been difficult because of its fully three dimensional structure. The FDTD whole package simulation is strongly expected to aid in designing the packages more efficiently.

From the point of view of electromagnetic modeling a microwave package is not only a considerably complex structure. There are different simulation segments. The first is the simulation of the embedded circuit. To deal with package simulation it needs not to go into details of the circuit. The chip is treated as an n-port whereby its global interaction with the surrounding package is considered. A current flow from one port of the circuit to another leads to a global EM coupling to the environment. There is no need to register the local current distribution due to the internal circuitry as long as the chips are small compared to the package. The second is the package itself containing the carrier, sealing, feedthrough, and interconnects. Optimization of interconnects is another important question that is also concerned with different connecting techniques inside and outside the package. Chapter 3 focuses on how to optimize interconnects by adjusting some package parameters. Chapter 4 concentrates on whole package simulation.

Circuit simulation was reported by Shibata [39], but he focused more on circuit than whole package. Pereda [36] also reported linear RLC lumped network FDTD simulation. A break through of whole package simulation was reported by Sui [45]. A general method to integrate s-parameter and behavioral block, along with lumped circuit components, into standard FDTD simulation, was presented by Sui. The convolution algorithm for s-parameter block requires inverse Fourier series calculation for impulse response function. The concept of absorbing cube is introduced, in addition to the induced current to Maxwell's equations, to clearly define the interface between distributed and lumped circuit. It also revolves the uncertainty of the size and location of the added subcircuits, either s-parameter block or other lumped components. Since the sparameter and behavioral model integration approach follows the same paradigm for modeling lumped elements, it greatly extended FDTD capability to include both lumped components and s-parameter block into full-wave time-domain simulation. Accuracy and stability of the method are verified by excellent comparisons for some two-dimensional test circuits. The formulation is derived for three dimensions and its implementation is straightforward. This method includes industrial standard s-parameter circuit representation and behavioral module in FDTD simulation and it should find its application in full-wave solution for RF integrated circuits, chip packaging and many

other high-frequency system designs.

### **CHAPTER 2**

## PRINCIPLES OF THE FDTD METHOD AND NON-UNIFORM GRID NUMERICAL ERROR

### 2.1 Introduction

The first part of this chapter introduces the principles of the FDTD method. The FDTD equations for the field components are presented, and the locations of the electric and magnetic field components on Yee cells are illustrated. The stability condition and relationship among the spatial and temporal discretization are also discussed.

The second part of this chapter demonstrates the relationship between the nonuniform grid and numerical error. The non-uniform grid can be used to describe accurately the complicated geometrical shape of the electromagnetic system. The nonuniform FDTD grid provides us with flexibility to improve its accuracy. The characteristics of a plane wave on the boundary of two adjacent media with non-uniform FDTD rectangular grids are analyzed. The reflection and refraction characteristics of the wave propagation at the boundary or two adjacent media due to the numerical dispersion of The FDTD method are demonstrated. In the FDTD simulation, these characteristics are different from the theoretical solution and cause numerical errors. The magnitude of numerical errors depends on the FDTD simulation parameters. Knowing these characteristics would help us manipulate the FDTD cell size distribution in order to achieve the desired simulation accuracy within the requirement.

Li [29] derived non-uniform numerical error equations in the TE mode when electrical field is in parallel to the plane of incidence. In this chapter, the non-uniform numerical error equations when the electrical field is perpendicular to the plane of

9

incidence were derived. The FDTD simulation results are also given in comparison with the theoretical ones.

### 2.2 The Yee FDTD

Kane Yee reported a set of finite difference equations for the time dependent Maxwell's curl equations system [57]. The Yee algorithm solves for both electric and magnetic fields in time and space using the coupled Maxwell's curl equations rather than solving for the electric field alone or magnetic field alone with a wave equation. This is analogous to the combined-field integral equation formulation of Maxwell, where both E and H boundary conditions are enforced on the surface of a material structure.

Using information of both E and H, the solution is more liable than using either alone. Both electric and magnetic material properties can be modeled in a straightforward manner. This is especially important when modeling radar cross-section migration. Features unique to each field such as tangential H singularities near edges and corners, azimuthal (looping) H singularities near thin wires, and radial E singularities near points, edges and thin wires can be individually modeled if both electric and magnetic fields are available.

The original Maxwell's curl equations:

$$\frac{\partial D}{\partial t} - \nabla \times \mathbf{H} = -J \tag{2.1}$$

$$\frac{\partial \mathbf{B}}{\partial t} + \nabla \times \mathbf{E} = 0 \tag{2.2}$$

In linear, isotropic, time invariant, non dispersive media, the Maxwell's curl equations can be written as

$$\varepsilon \frac{\partial \mathbf{E}}{\partial t} = \nabla \times \mathbf{H} - J \tag{2.3}$$

$$\mu \frac{\partial \mathbf{H}}{\partial t} = -\nabla \times \mathbf{E} \tag{2.4}$$

In Cartesian coordinates, equations (2.3-2.4) can be rewritten as a system of equations for all the electromagnetic field components

$$\varepsilon \frac{\partial E_x}{\partial t} = \frac{\partial H_z}{\partial y} - \frac{\partial H_y}{\partial z} - J_x$$

(2.5)

$$\varepsilon \frac{\partial E_y}{\partial t} = \frac{\partial H_x}{\partial z} - \frac{\partial H_z}{\partial x} - J_y$$

(2.6)

$$\varepsilon \frac{\partial E_z}{\partial t} = \frac{\partial H_y}{\partial x} - \frac{\partial H_x}{\partial y} - J_z$$

(2.7)

$$-\mu \frac{\partial H_x}{\partial t} = \frac{\partial E_z}{\partial y} - \frac{\partial E_y}{\partial z}$$

(2.8)

$$-\mu \frac{\partial H_y}{\partial t} = \frac{\partial E_x}{\partial z} - \frac{\partial E_z}{\partial x}$$

(2.9)

$$-\mu \frac{\partial H_z}{\partial t} = \frac{\partial E_y}{\partial x} - \frac{\partial E_x}{\partial y}$$

(2.10)

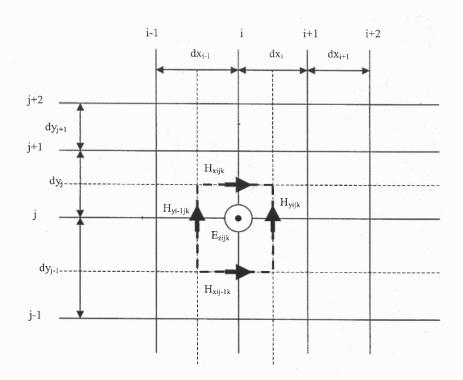

As illustrated in Figure 2.1, a special spatial discretization scheme named Yee cell, is used in The FDTD method to discretize the equations (2.5-2.10). The Yee algorithm centers its E and H components in 3-D space so that every E component is surrounded by four circulating H components, and every H component is surrounded by four circulating E components. The placements of the electromagnetic field components are off the grid nodes of one half cell size. The arrangement of the positions of E and H components is for the purpose to locate the electrical media more conveniently. In order to locate the magnetic media conveniently, the positions of E and H components can be exchanged.

Figure2.1 Non-uniform FDTD grid

12

This does not change the FDTD equations at all. In time domain, the E and H components are also defined at different time instants. Specifically, the E field is defined at the ndt and the H field is defined at (n+1/2)dt, n is a non-negative integer and dt is the temporal increment.

E and H field component expressions can be obtained with uniform cell size and only conduction current from equations (2.5-2.10)

.

$$E_{xijk}^{n+1} = \frac{\frac{\Delta t}{\varepsilon} - \frac{\sigma}{2}}{\frac{\Delta t}{\varepsilon} + \frac{\sigma}{2}} E_{xijk}^{n} + \frac{1}{\frac{\Delta t}{\varepsilon} + \frac{\sigma}{2}} \left( \frac{H_{zijk}^{n+1/2} - H_{zij-1k}^{n+1/2}}{\Delta y} - \frac{H_{yijk}^{n+1/2} - H_{yijk-1}^{n+1/2}}{\Delta z} \right)$$

(2.11)

$$E_{yijk}^{n+1} = \frac{\frac{\Delta I}{\varepsilon} - \frac{\sigma}{2}}{\frac{\Delta t}{\varepsilon} + \frac{\sigma}{2}} E_{yijk}^{n} + \frac{1}{\frac{\Delta t}{\varepsilon} + \frac{\sigma}{2}} \left( \frac{H_{xijk}^{n+1/2} - H_{xijk-1}^{n+1/2}}{\Delta z} - \frac{H_{zijk}^{n+1/2} - H_{zi-1jk}^{n+1/2}}{\Delta x} \right)$$

(2.12)

$$E_{zijk}^{n+1} = \frac{\frac{\Delta t}{\varepsilon} - \frac{\sigma}{2}}{\frac{\Delta t}{\varepsilon} + \frac{\sigma}{2}} E_{zijk}^{n} + \frac{1}{\frac{\Delta t}{\varepsilon} + \frac{\sigma}{2}} \left( \frac{H_{yijk}^{n+1/2} - H_{yi-1jk}^{n+1/2}}{\Delta x} - \frac{H_{xijk}^{n+1/2} - H_{xij-1k}^{n+1/2}}{\Delta y} \right)$$

(2.13)

$$H_{xijk}^{n+1/2} = H_{xijk}^{n-1/2} - \frac{\Delta t}{\mu} \left( \frac{E_{zij+1k}^{n} - E_{zijk}^{n}}{\Delta y} - \frac{E_{yijk+1}^{n} - E_{yijk}^{n}}{\Delta z} \right)$$

(2.14)

$$H_{yijk}^{n+1/2} = H_{yijk}^{n-1/2} - \frac{\Delta t}{\mu} \left( \frac{E_{xijk+1}^n - E_{xijk}^n}{\Delta z} - \frac{E_{zi+1jk}^n - E_{zijk}^n}{\Delta x} \right)$$

(2.15)

$$H_{zijk}^{n+1/2} = H_{zijk}^{n-1/2} - \frac{\Delta t}{\mu} \left( \frac{E_{yi+1jk}^{n} - E_{yijk}^{n}}{\Delta x} - \frac{E_{xij+1k}^{n} - E_{xijk}^{n}}{\Delta y} \right)$$

(2.16)

where the conduction current is evaluated as forward time average  $J^n = \sigma(E^n + E^{n+1})/2$ .

The new value of a field vector component at any space lattice point depends on its previous value and the previous values of the components of the other field at adjacent points [50, 51]. In another word, every E components can be calculated based on its

value at its previous time step and H field values around it at a half time step before. Every H field component can also be computed according to its value in previous time step and the E field values around it at a half time step before. Thus, this scheme is also called leap frog scheme.

The FDTD method is necessary to avoid numerical instability. The stability criteria of the FDTD method are [51]

$$c\Delta t \le \Delta x$$

(2.17)

$$c\Delta t \le \frac{1}{\left(\frac{1}{\Delta x^2} + \frac{1}{\Delta y^2}\right)^{1/2}}$$

(2.18)

$$c\Delta t \le \frac{1}{\left(\frac{1}{\Delta x^2} + \frac{1}{\Delta y^2} + \frac{1}{\Delta z^2}\right)^{1/2}}$$

(2.19)

Equations (2.16-2.18) are for 1-D, 2-D and 3-D methods respectively. They are also known as Courant-Eriedrichs-Lewy(CFL) stability criterion.

### **2.3 Boundary Condition Techniques**

The field computation domain must be limited in size because the computer can not store an unlimited amount of data. The computation domain must be large enough to enclose the structure of interest, and a suitable boundary condition on the outer perimeter of the domain must be used to simulate its extension to infinity. The outer boundary condition must suppress spurious reflections of the outgoing numerical wave analogs to an acceptable level, permitting the FDTD solution to remain valid for all time steps, especially after the reflected wave analogs return to the vicinity of the modeled structure. These conditions are called absorbing boundary conditions (ABCs). Two ABCs are used in this thesis, one is Mur's ABC, the other is Berenger's PML.

### 2.3.1 Mur's ABCs

Mur's ABCs are based on defactoring the second order wave equation into two first order wave equations, each of which represents the wave in opposite directions. Each component of the electric field independently satisfies the three-dimensional wave equation:

$$\left(\frac{\partial^2}{\partial x^2} + \frac{\partial^2}{\partial y^2} + \frac{\partial^2}{\partial z^2} - c^{-2}\frac{\partial^2}{\partial t^2}\right)W = 0$$

(2.20)

where W is any E or H component.

Define three inverse velocity components Sx, Sy and Sz

$$Sx = \frac{\partial t}{\partial x} \tag{2.21}$$

$$Sy = \frac{\partial t}{\partial y} \tag{2.22}$$

$$Sz = \frac{\partial t}{\partial z} \tag{2.23}$$

which satisfy

$$Sx^2 + Sy^2 + Sz^2 = c^{-2}$$

(2.24)

It is assumed that the mesh is located in the region  $0 \le x$ , and give boundary conditions for the plane x=0. The differential equation that describes the outgoing wave is

$$\frac{\partial W}{\partial x} \pm c^{-1} (1 - (cSy)^2 - (cSz)^2)^{1/2} \frac{\partial W}{\partial t} = 0$$

(2.25)

The first order Mur ABCs can be obtained by first order Taylor's series from Equation (2.25):

$$\frac{\partial W}{\partial x} = \frac{\partial W}{c\partial t}$$

(2.26)

From the second order Taylor's series:

$$(1 - (cSy)^{2} - (cSz)^{2})^{1/2} = 1 - \frac{1}{2}((cSy)^{2} + (cSz)^{2})$$

(2.27)

Second order Mur ABCs can be obtained:

$$\left(\frac{\partial^2}{c\partial x\partial t} + \frac{\partial^2}{2\partial y^2} + \frac{\partial^2}{2\partial z^2} - c^{-2}\frac{\partial^2}{\partial t^2}\right)W = 0$$

(2.28)

Mur's ABCs can keep the reflection coefficient as low as 20dB. But Mur's ABC is not faultless. A wave is absorbed without reflection only when it is a plane wave propagating perpendicularly to the boundary. Although the Mur's boundary condition can be extended to higher order if higher Taylor's series is used, it does not help much on the reflection and can cause a stability problem.

### 2.3.2 Perfect Matched Layer (PML)

Berenger [5] published a novel ABC for FDTD meshes in two dimensions with orders of magnitude of improved performance relative to any earlier technique. For a 2-D problem,

with only  $E_x$ ,  $E_y$  and  $H_z$  field components. If there is a medium, with property  $\frac{\sigma}{\varepsilon_0} = \frac{\sigma^*}{\mu_0}$ ,

where  $\varepsilon_0$  and  $\mu_0$  are the free space permittivity and permeability, and  $\sigma$  and  $\sigma^*$  denote electric conductivity and magnetic loss respectively. Then the impedance of the media equals that of vacuum and no reflection occurs. A plane wave is perfectly matched (zero reflection) when normally incident on a half space of this media.

But the absorbing medium described above fails perfect match for the EM waves that are not normally incident on the absorbing layer. The PML approach based upon a splitting of electric or magnetic field components in the absorbing boundary region with the possibility of assigning losses to the individual split field components, can absorb EM waves when oblique incident. The net effect of this is to create a non-physical absorbing medium adjacent to the outer FDTD mesh boundary that has a wave impedance independent of the angle of incidence and frequency of outgoing scattered waves. PML effective reflection coefficient is 1/3000<sup>th</sup> of standard second and third order analytical Mur's ABCs [5,49].

Using PML to terminate 2-D electrical structure having  $E_x$ ,  $E_y$  and  $H_z$  components [5]. Hz is split into two subcomponents: Hzx and Hzy.

$$\varepsilon \frac{\partial E_x}{\partial t} + \sigma_y E_x = \frac{\partial (H_{zx} + H_{zy})}{\partial y}$$

(2.29)

$$\varepsilon \frac{\partial E_y}{\partial t} + \sigma_x E_y = -\frac{\partial (H_{zx} + H_{zy})}{\partial x}$$

(2.30)

$$\mu \frac{\partial H_{zx}}{\partial t} + \sigma^*{}_x H_{zx} = -\frac{\partial E_y}{\partial x}$$

(2.31)

$$\mu \frac{\partial H_{zy}}{\partial t} + \sigma_y H_{zy} = \frac{\partial E_x}{\partial y}$$

(2.32)

If PML region is set according to following rules:

$$\frac{\sigma_x}{\varepsilon} = \frac{\sigma^* x}{\mu} \tag{2.33}$$

$$\frac{\sigma_{y}}{\varepsilon} = \frac{\sigma^{*}_{y}}{\mu}$$

(2.34)

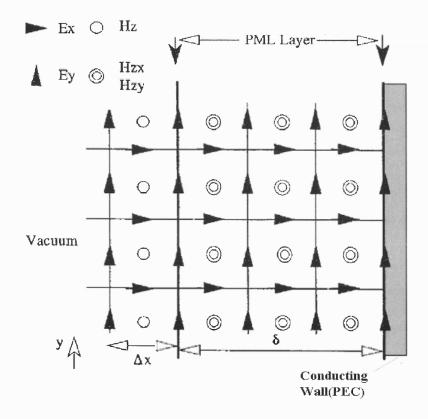

when electrical wave propagates in the +x direction, at maximum x, the electrical wave meet with PML that has  $\sigma_x$  and  $\sigma^*_x$  matched with  $\sigma_y = \sigma^*_y = 0$ . The PML permits transmission across the vacuum-PML interface without reflection, as shown in Figure 2.2. It is assumed that the loss in PML region increases quadratically with depth d. The loss  $\sigma$  will reach to its maximum value when d= $\delta$ . The loss in PML can be chosen to bound the reflection coefficient [47]

$$R = e^{\frac{2\sigma_{\max}\delta}{3\omega}}$$

(2.35)

So reflection coefficient can be kept to some desired level.

In three dimensional cases, all six Cartesian field vector components are split. The resulting PML modification of Maxwell's equations yields 12 equations [25], as follows:

$$\varepsilon \frac{\partial E_{xy}}{\partial t} + \sigma_y E_{xy} = \frac{\partial H_z}{\partial y}$$

(2.36)

$$\varepsilon \frac{\partial E_{xz}}{\partial t} + \sigma_y E_{xz} = -\frac{\partial H_y}{\partial z}$$

(2.37)

$$\mu \frac{\partial H_{xy}}{\partial t} + \sigma^*_{y} H_{xy} = -\frac{\partial E_z}{\partial y}$$

(2.38)

$$\mu \frac{\partial H_{xz}}{\partial t} + \sigma_y^{*} H_{xz} = -\frac{\partial E_y}{\partial z}$$

(2.39)

$$\varepsilon \frac{\partial E_{yx}}{\partial t} + \sigma_x E_{yx} = -\frac{\partial H_z}{\partial x}$$

(2.40)

$$\varepsilon \frac{\partial E_{yz}}{\partial t} + \sigma_z E_{yz} = \frac{\partial H_x}{\partial z}$$

(2.41)

$$\mu \frac{\partial H_{yx}}{\partial t} + \sigma^*_{x} H_{yx} = -\frac{\partial E_z}{\partial x}$$

(2.42)

$$\mu \frac{\partial H_{yz}}{\partial t} + \sigma^*{}_z H_{yz} = -\frac{\partial E_x}{\partial z}$$

(2.43)

Figure 2.2 Three layers: vacuum, PML, conducting wall.

$$\varepsilon \frac{\partial E_{zx}}{\partial t} + \sigma_x E_{zx} = \frac{\partial H_y}{\partial x}$$

(2.44)

$$\varepsilon \frac{\partial E_{zy}}{\partial t} + \sigma_y E_{zy} = -\frac{\partial H_x}{\partial y}$$

(2.45)

$$\mu \frac{\partial H_{zx}}{\partial t} + \sigma^* {}_x H_{zx} = -\frac{\partial E_y}{\partial x}$$

(2.46)

$$\mu \frac{\partial H_{zy}}{\partial t} + \sigma^*_{y} H_{zy} = \frac{\partial E_x}{\partial y}$$

(2.47)

Since the electromagnetic field changes rapidly in a PML medium in space but not in time, the exponential scheme in time does not improve stability. Thus, the central discretization scheme to discretize the time derivative is also used.

The electric and magnetic conductivity profile in a PML layer is also an important factor to influence the performance of the PML. Constant, linear, parabolic, and geometric profiles are all used to define the conductivity profile from the interface between PML and Yee cell to the outer boundary, normally perfect electrical conductor (PEC) wall. The parabolic profile is much better than the linear and constant profile, but for the simulation with a large number of iterations, the parabolic profile causes a significant error. The geometric profile can avoid this problem, but a more careful design must be made to define the PML boundary laryers.

Generally, the performance of PML is much better than Mur's ABCs. According to Berenger's work [5], the reflection coefficient of PML is 20 dB less than that of Mur's ABCs. The shortcoming of PML is its higher computational cost because of the splitting of the electromagnetic field components and additional layers in the FDTD grid. In the microwave and high frequency circuit analysis, involving complicated electromagnetic phenomena, such as near field phenomena and high order modes, PML is generally accepted as the main approach to handle boundary conditions in FDTD simulation.

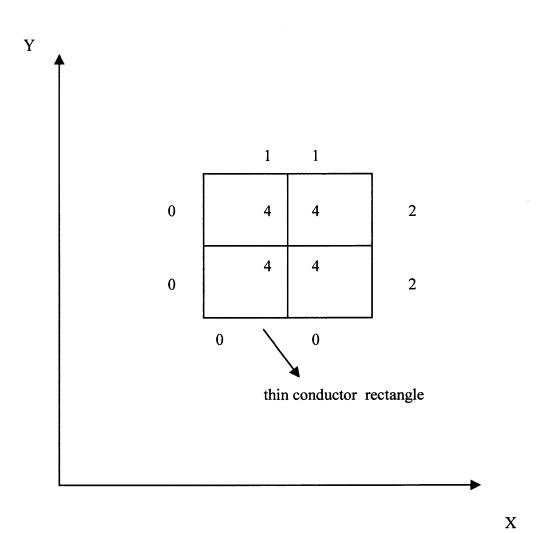

# 2.4 PEC cell type

FDTD simulation sometimes needs to treat very thin conductor layer with zero thickness. So an artificial property, which is called PEC type is created to stand for zero thickness conductor. The PEC property fixes some of the E components in a Yee cell to zero during all the computational time. There are 7 PEC types [29],

| PEC Type | Description                  |

|----------|------------------------------|

| 0        | No Components are fixed to 0 |

| 1        | Ex=0                         |

| 2        | Ey=0                         |

| 3        | Ez=0                         |

| 4        | Ex=Ey=0                      |

| 5        | Ex=Ez=0                      |

| 6        | Ey=Ez=0                      |

| 7        | Ey=Ez=Ez=0                   |

# Table 2.1 PEC type

Figure 2.3 is thin conductor rectangle that is expressed by PEC cell types. The four thin conductor cells are PEC type 4, which keep Ex and Ey to zero. Its boundary PEC cells are type 1 and 2; type 1 keeps Ex to zero, and type 2 keep Ey to zero. PEC is a very

Figure 2.3 Thin conductor rectangle's PEC type

useful property for FDTD. With its help, lumped elements can be added in between one or two cells. PEC is used default in this thesis. Non-PEC type is stated when it is used.

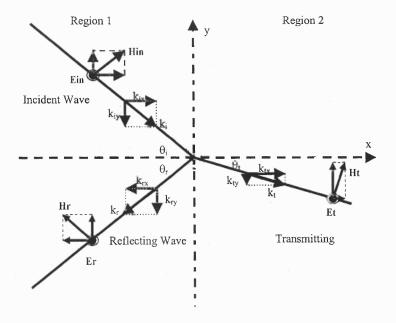

# 2.5 Numerical Error for Non-uniform Grid of Electromagnetic System

The non-uniform FDTD grid provides us flexibility to improve accuracy of simulation. It is often desirable to have a refined lattice in localized regions such as near sharp edges or corners to accurately model the local field phenomena. This section analyzes the characteristics of a plane wave on the boundary of two adjacent media with non-uniform FDTD rectangular grids. The reflection and refraction equations of the wave propagation at the boundary or two adjacent media due to the numerical dispersion of The FDTD method are derived. In the FDTD simulation, these equations are different from the theoretical solution due to numerical errors. The magnitude of numerical errors depends on the FDTD simulation parameters.

There are two regions for non-uniform grid reflection, as it is shown in Figure 2.4: Region One: incident wave and reflected wave

$$E_{z1} = \xi_1 A(e^{j(andt - (k_{xi}id_{x1} + k_{yi}jd_{yi})} + R \cdot e^{j(andt + (k_{xr}id_{x1} + k_{yr}jd_{yi})})$$

(2.48)

$$H_{x1} = A(\sin\theta_i e^{j(\omega n dt - (k_{xi} i d_{x1} + k_{yi} j d_{yi})} + R \cdot \sin\theta_r e^{j(\omega n dt + (k_{xr} i d_{x1} + k_{yr} j d_{yi})})$$

(2.49)

$$H_{y1} = A(\cos\theta_i e^{j(\omega ndt - (k_{xi}id_{x1} + k_{yi}jd_{yi})} - R \cdot \cos\theta_r e^{j(\omega ndt + (k_{xr}id_{x1} + k_{yr}jd_{yi})})$$

(2.50)

Region Two: transmitted wave

$$E_{z2} = \xi_2 B e^{j(\omega n dt - (k_x i d_{x2} + k_y j d_{y2})}$$

(2.51)