## **Copyright Warning & Restrictions**

The copyright law of the United States (Title 17, United States Code) governs the making of photocopies or other reproductions of copyrighted material.

Under certain conditions specified in the law, libraries and archives are authorized to furnish a photocopy or other reproduction. One of these specified conditions is that the photocopy or reproduction is not to be "used for any purpose other than private study, scholarship, or research." If a, user makes a request for, or later uses, a photocopy or reproduction for purposes in excess of "fair use" that user may be liable for copyright infringement,

This institution reserves the right to refuse to accept a copying order if, in its judgment, fulfillment of the order would involve violation of copyright law.

Please Note: The author retains the copyright while the New Jersey Institute of Technology reserves the right to distribute this thesis or dissertation

Printing note: If you do not wish to print this page, then select "Pages from: first page # to: last page #" on the print dialog screen

The Van Houten library has removed some of the personal information and all signatures from the approval page and biographical sketches of theses and dissertations in order to protect the identity of NJIT graduates and faculty.

#### **ABSTRACT**

## EMULATION OF THE DATAFLOW COMPUTING PARADIGM USING FIELD PROGRAMMABLE GATE ARRAYS (FPGAs)

#### by Segreen Ingersoll

Building a perfect dataflow computer has been an endeavor of many computer engineers. Ideally, it is a perfect parallel machine with zero overheads, but implementing one has been anything but perfect. While the sequential nature of control flow machines makes them relatively easy to implement, dataflow machines have to address a number of issues that are easily solved in the realm of control flow paradigm. Past implementations of dataflow computers have addressed these issues, such as *conditional* and *reentrant* program structures, along with the *flow of data*, at the processor level, i.e. each processor in the design would handle these issues. The design presented in this thesis solves these issues at the memory level (by using intelligent-memory), separating the processor from dataflow tasks. Specifically, a two-level memory design, along with a pool of processors was prototyped on a group of Altera FPGAs.

The first level of memory is an intelligent-memory called Dataflow Memory (DFM), carrying out dataflow tasks. The second level of memory called the Instruction Queue (IQ) is a buffer that queues instructions ready for execution, sent by the DFM. The second level memory has a multiple bank architecture that allows multiple processors from the processor pool to simultaneously execute instructions retrieved from the banks. After executing an instruction, each processor sends the result back to the dataflow memory, where they fire new instructions and send them to the IQ.

This thesis shows that implementing dataflow computers at the intelligentmemory level is a viable alternative to implementing them at the processor level.

## EMULATION OF THE DATAFLOW COMPUTING PARADIGM USING FIELD PROGRAMMABLE GATE ARRAYS (FPGAs)

by Segreen Ingersoll

A Thesis

Submitted to the Faculty of

New Jersey Institute of Technology

in Partial Fulfillment of the Requirements for the Degree of

Master of Science in Computer Engineering

Department of Electrical and Computer Engineering

January 2001

### **APPROVAL PAGE**

## EMULATION OF THE DATAFLOW COMPUTING PARADIGM USING FIELD PROGRAMMABLE GATE ARRAYS (FPGAs)

## Segreen Ingersoll

| Dr. Edwin Hou, Committee Member<br>Associate Professor of Electrical and Computer Engineering, NJIT | Date |

|-----------------------------------------------------------------------------------------------------|------|

| Dr. Durga Misra, Committee Member                                                                   | Date |

#### **BIOGRAPHICAL SKETCH**

**Author:** Segreen Ingersoll

**Degree:** Masters in Computer Engineering

Date: January 2001

### **Undergraduate and Graduate Education:**

- Master of Science in Computer Engineering,

New Jersey Institute of Technology, Newark, NJ, 2001

- Bachelor of Science in Computer Engineering, New Jersey Institute of Technology, Newark, NJ, 1998

- Bachelor of Science in Computer Science,

New Jersey Institute of Technology, Newark, NJ, 1998

- Bachelor of Science in Physics, Bombay University, Bombay, India, 1992

Major: Computer Engineering

#### **Presentations and Publications:**

Segreen Ingersoll and Sotirios Ziavras,

"Dataflow Computation With Intelligent Memories Emulated on Field-Programmable Gate Arrays (FPGAs)." VLSI Design Journal, submitted for publication, December 2000.

To my beloved parents

#### **ACKNOWLEDGEMENT**

I would like to express my deepest appreciation to Dr. Sotirios Ziavras, who not only served as my thesis advisor, providing valuable resources and insight, but also for supporting and encouraging my ideas. Special thanks are given to Dr. Edwin Hou and Dr. Durga Misra for actively participating in the committee.

I would like to take this opportunity to also express my gratitude to Dr. Edip Niver, who supported my work as a graduate student, providing me with an assistantship, and Dr. Raashid Malik who first introduced me to dataflow computing.

Finally I would like to mention a note of thanks to all the staff at ECE department for their assistance over the years.

## **TABLE OF CONTENTS**

| Cl | hapte | r       |                                                         | Page |

|----|-------|---------|---------------------------------------------------------|------|

| 1  | INT   | RODU    | CTION                                                   | 1    |

|    | 1.1   | Objec   | ctive                                                   | 1    |

|    | 1.2   | Funda   | amentals of Computing Paradigms                         | 1    |

|    |       | 1.2.1   | Control Flow                                            | 2    |

|    |       | 1.2.2   | Data Flow                                               |      |

| 2  | ISSI  | UES AI  | ND PRIOR RESEARCH                                       | 10   |

|    | 2.1   | Issues  | s (Data Flow in Depth)                                  | 10   |

|    | 2.2   | Prior   | Research                                                | 18   |

|    |       | 2.2.1   | Direct Communication Machines                           | 18   |

|    |       | 2.2.2   | Static Packet Communication Machines                    | 19   |

|    |       | 2.2.3   | Machines with Code-Copying Facilities                   | 20   |

|    |       | 2.2.4   | Tagged-Token Machines                                   | 21   |

|    |       | 2.2.5   | Other Architectures                                     | 22   |

|    | 2.3   | Motiv   | vation and Objectives                                   | 24   |

| 3  |       |         | ICAL APPROACH AND IMPLEMENTING A DATAFLOW               | 26   |

|    | 3.1   | Overv   | view of the Design                                      | 26   |

|    |       | 3.1.1   | Data Flow Memory                                        | 27   |

|    |       | 3.1.2   | Instruction Queue                                       | 29   |

|    |       | 3.1.3   | Processor Pool                                          | 30   |

|    |       | 3.1.4   | Flow of Data and Instructions in the Data Flow Computer | 30   |

|    |       | 3.1.5   | Remarks                                                 | 31   |

|    | 3.2   | Field 1 | Programmable Gate Arrays (FPGAs)                        |      |

|    | 3.3   | Detail  | ed Layout and Implementation of the Design              | 35   |

|    |       | 3.3.1   | DFM Architecture                                        | 35   |

|    |       | 3.3.2   | Dataflow Memory Implementation                          | 43   |

|    |       | 3.3.3   | Instruction Queue (IQ)                                  | 50   |

|    |       | 3.3.4   | Processor Pool                                          | 55   |

|    |       | 3.3.5   | Programming on the Dataflow Computer                    | 56   |

# TABLE OF CONTENTS (Continued)

| Cl | hapte | er                                                                      | Page  |

|----|-------|-------------------------------------------------------------------------|-------|

|    |       | 3.3.6 Altera Implementation                                             | 67    |

|    | 3.4   | Remarks                                                                 | 81    |

| 4  | TIM   | MINGS, SIMULATIONS, AND PERFORMANCE                                     | 84    |

|    | 4.1   | Timings                                                                 | 84    |

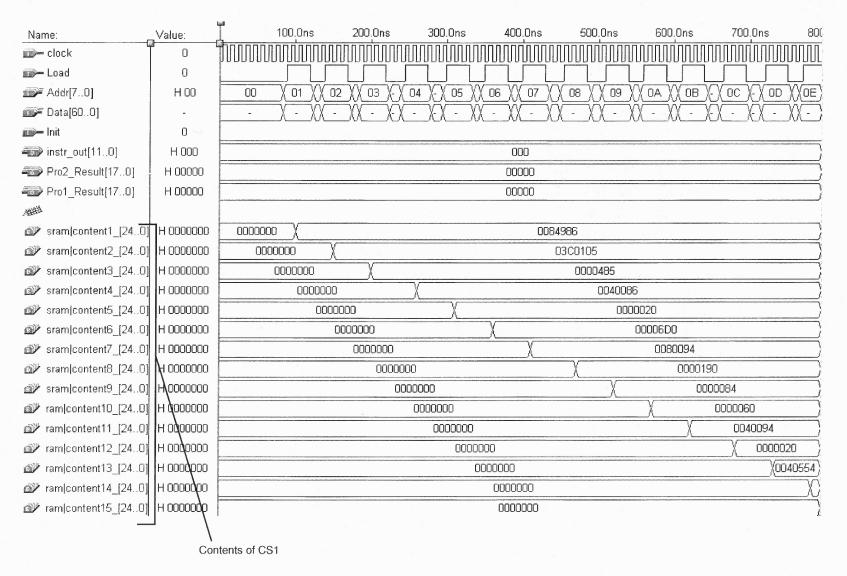

|    | 4.2   | Simulations                                                             | 88    |

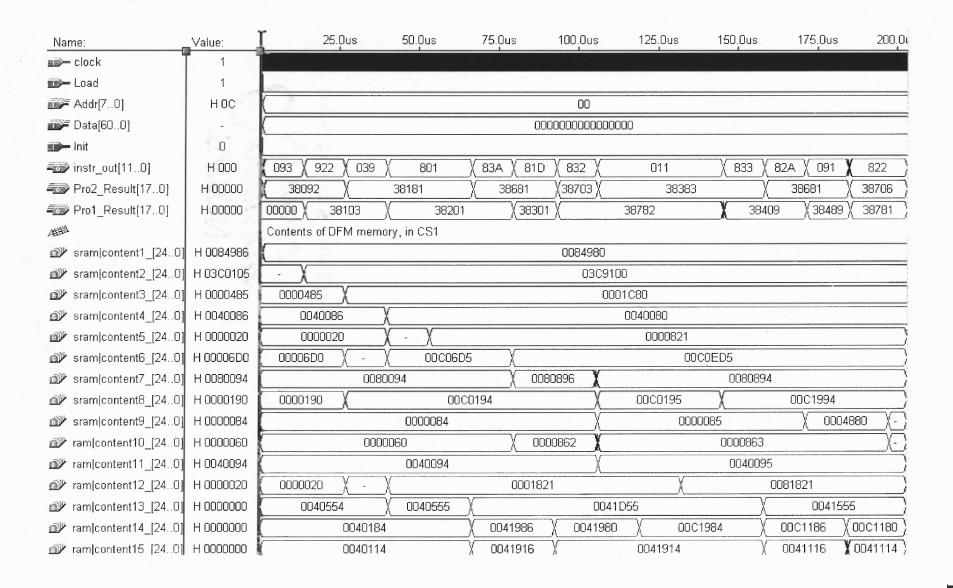

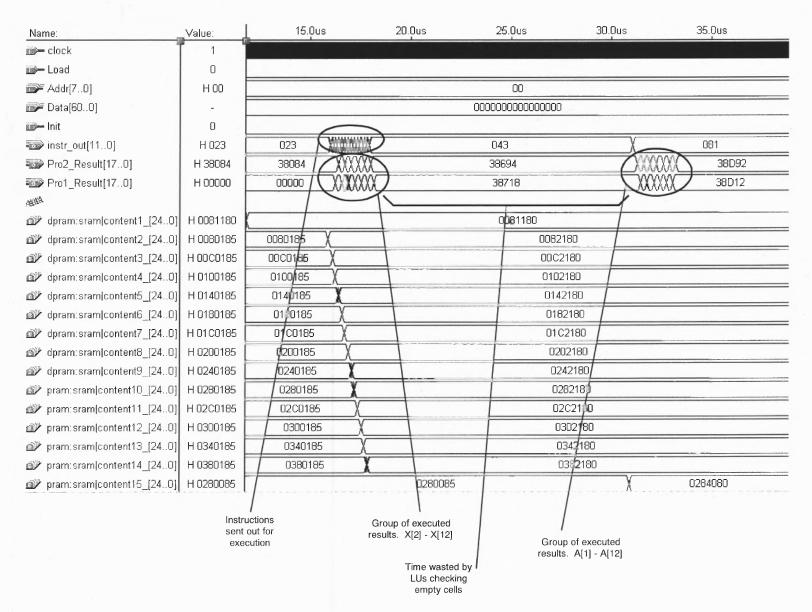

|    |       | 4.2.1 Program 1                                                         | 89    |

|    |       | 4.2.2 Program 2                                                         | 91    |

|    |       | 4.2.3 Program 3                                                         | 94    |

|    | 4.3   | Simulation Results                                                      | 97    |

|    |       | 4.3.1 Program 1                                                         | 97    |

|    |       | 4.3.2 Program 2                                                         | 99    |

|    |       | 4.3.3 Program 3                                                         | 100   |

| 5  | ANA   | ALYSIS AND ENHANCEMENTS                                                 | 102   |

|    | 5.1   | Enhancement I                                                           | 102   |

|    | 5.2   | Enhancement II                                                          | 103   |

|    | 5.3   | Enhancement III                                                         | 103   |

| 6  | CON   | NCLUSIONS                                                               | 107   |

| AF | PPEN  | DIX                                                                     | 108   |

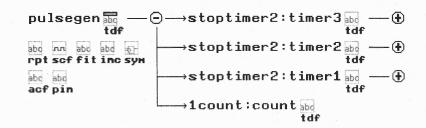

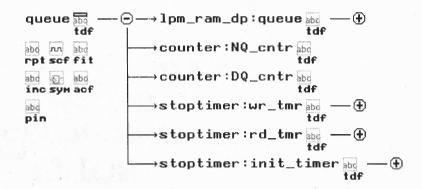

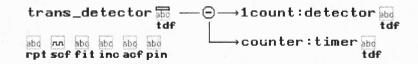

|    | App   | endix A – Hierarchies and Programs                                      | 109   |

|    |       | A.1 Hierarchy of the whole Dataflow Computer                            | 110   |

|    |       | A.2 Hierarchy of module – BLOCKB3_B                                     | 111   |

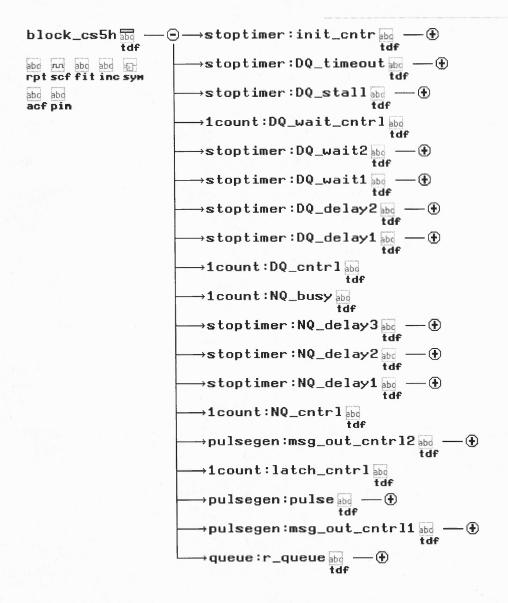

|    |       | A.3 Hierarchy and TDF Implementation of module – BLOCK_CS51             | H 112 |

|    |       | A.4 Hierarchy and TDF Implementation of module –  RESULT_BUS_CONTROLLER | 117   |

|    |       | A.5 TDF Implementation of module – INITIALIZE                           | 119   |

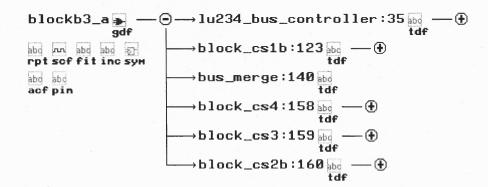

|    |       | A.6 Hierarchy of module – BLOCKB3_A                                     |       |

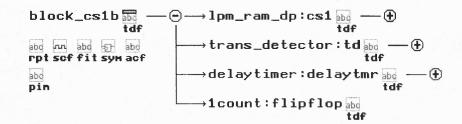

|    |       | A.7 Hierarchy and TDF Implementation of module – BLOCK_CS11             |       |

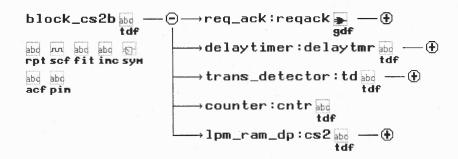

|    |       | A.8 Hierarchy and TDF Implementation of module – BLOCK_CS2I             |       |

|    |       | A.9 Hierarchy and TDF Implementation of module – BLOCK CS3.             |       |

# TABLE OF CONTENTS (Continued)

| age |

|-----|

| 131 |

|     |

| 134 |

| 136 |

| 137 |

| 139 |

| 144 |

| 145 |

| 148 |

| 149 |

| 150 |

| 151 |

| 152 |

| 154 |

| 155 |

| 156 |

| 157 |

| 159 |

| 160 |

| 161 |

| 162 |

| 164 |

| 165 |

| 166 |

| 171 |

| 172 |

|     |

## LIST OF TABLES

| Tabl | Table I                                                                                           |    |  |

|------|---------------------------------------------------------------------------------------------------|----|--|

| 1.1  | Execution of a set of instructions under the two execution paradigms;  Control Flow and Data Flow | 7  |  |

| 3.1  | Full Instruction Set                                                                              | 57 |  |

| 3.2  | Classification of Arrows associated with Dataflow Graph Nodes                                     | 61 |  |

| 3.3  | Sample Code                                                                                       | 63 |  |

| 3.4  | Equivalent Dataflow Program of the Sample Code                                                    | 64 |  |

| 4.1  | Timing of the result_bus_controller                                                               | 85 |  |

| 4.2  | Timing of the lu234_bus_controller                                                                | 85 |  |

| 4.3  | Timing of CS2 – CS4                                                                               | 86 |  |

| 4.4  | Timing of CS1                                                                                     | 87 |  |

| 4.5  | Timing of CS5                                                                                     | 87 |  |

| 4.6  | Timing of IQ                                                                                      | 88 |  |

| 4.7  | Timing of Processor Pool                                                                          | 88 |  |

| 4.8  | First Program Run on the Dataflow Machine in High Level Language                                  | 89 |  |

| 4.9  | First Program Run on the Dataflow Machine in Dataflow Language                                    | 90 |  |

| 4.10 | Second Program Run on the Dataflow Machine in High Level Language                                 | 92 |  |

| 4.11 | Second Program Run on the Dataflow Machine in Dataflow Language                                   | 93 |  |

| 4.12 | Third Program Run on the Dataflow Machine                                                         | 94 |  |

| 4.13 | Third Program Run on the Dataflow Machine in Dataflow Language                                    | 95 |  |

## LIST OF FIGURES

| Figu | Page Page                                                                                                                                      |

|------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.1  | Sample Program6                                                                                                                                |

| 1.2  | (a) Sample Program (b) Memory layout of instructions in Control Flow and Data Flow Computers                                                   |

| 2.1  | Dataflow graph of the program presented on the right                                                                                           |

| 2.2  | Functional diagram of a processing element in of a tagged-token machine [1] 11                                                                 |

| 2.3  | (a) A BRANCH node. (b) A non-deterministic MERGE node                                                                                          |

| 2.4  | Conditional Expression Graph13                                                                                                                 |

| 2.5  | Loop Construct Graph14                                                                                                                         |

| 2.6  | Interface for a Procedure Call. 16                                                                                                             |

| 2.7  | A survey of dataflow machines, categorized according to their architecture and implementation. The keys in the boxes refer to the machines [1] |

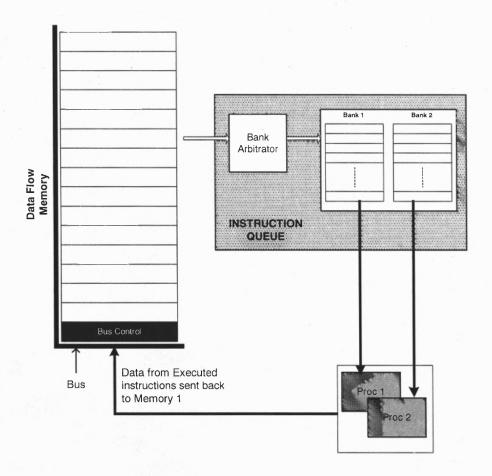

| 3.1  | Overall Structure of Data Flow Computer                                                                                                        |

| 3.2  | Internal Structure of Intelligent Cell in DFM                                                                                                  |

| 3.3  | Dataflow Memory Structure                                                                                                                      |

| 3.4  | DFM Cell Structure                                                                                                                             |

| 3.5  | DFM Cell Structure                                                                                                                             |

| 3.6  | Internal Structure of the DFM                                                                                                                  |

| 3.7  | Internal structure of the Block                                                                                                                |

| 3.8  | Messages on the Operand Bus / Result Arrival Format                                                                                            |

| 3.9  | Instruction Dispatch Format                                                                                                                    |

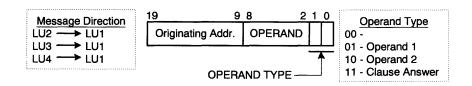

| 3.10 | Message Communication format between LU2/LU3/LU4 and LU1                                                                                       |

| 3.11 | Structure of Dataflow Computer Implemented in this Thesis                                                                                      |

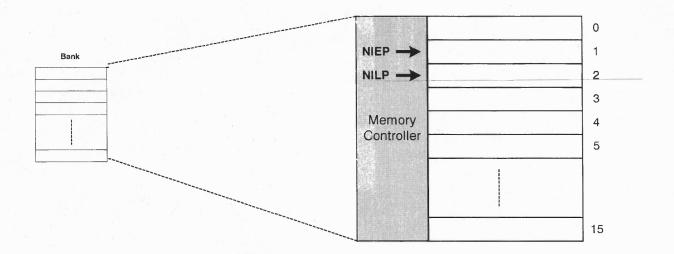

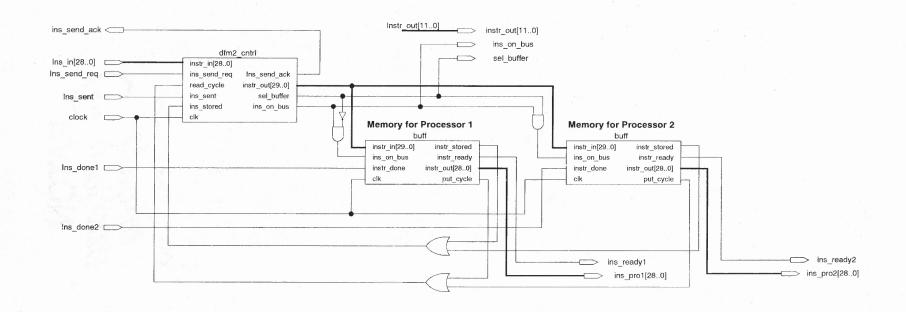

| 3.12 | Layout of Memory Bank in IQ                                                                                                                    |

| 3.13 | Structure of an IQ Memory Cell                                                                                                                 |

| 3.14 | Format of Instructions received by MC                                                                                                          |

| 3.15 | Result Dispatch format by a processor                                                                                                          |

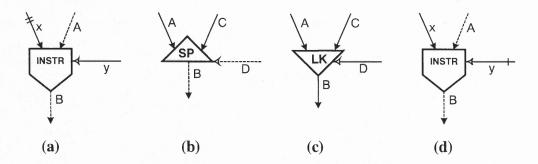

| 3.16 | Primitives to implement a Program Flow Graph                                                                                                   |

| 3.17 | Flow graph of the code presented in Table 3-4                                                                                                  |

| 3.18 | Flow graph of the sequential code in Table 3-3                                                                                                 |

# LIST OF FIGURES (Continued)

| Figu | re Pag                                                                         |

|------|--------------------------------------------------------------------------------|

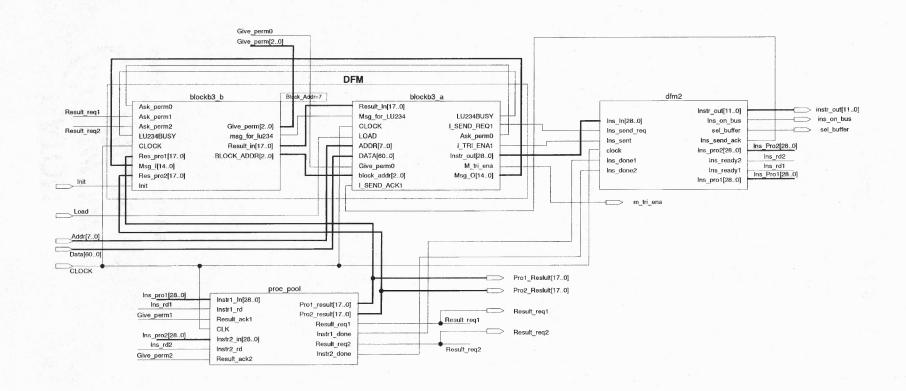

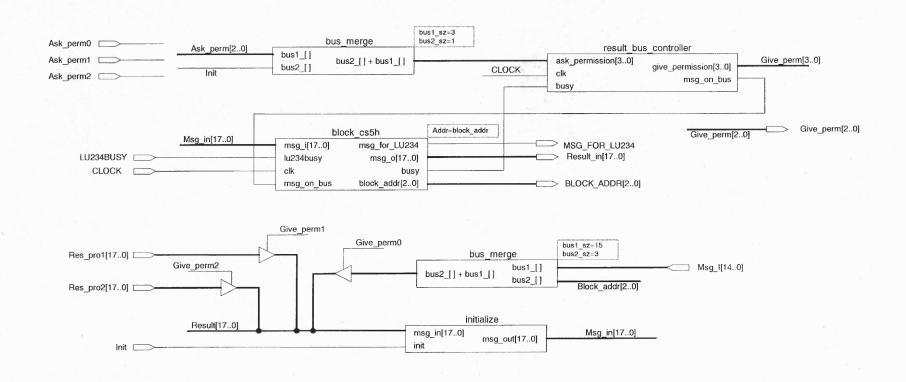

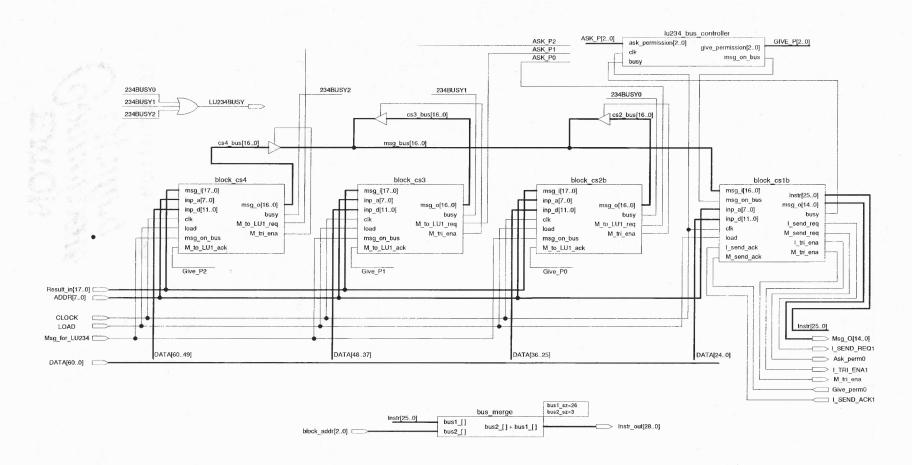

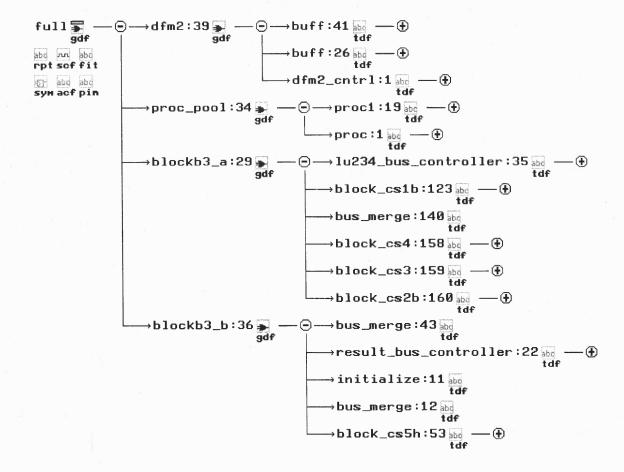

| 3.19 | Altera produced Graphic Design File of the Full Dataflow Computer (redrawn) 72 |

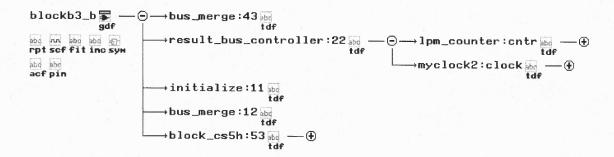

| 3.20 | Altera produced Graphic Design File of Blockb3_b (redrawn)                     |

| 3.21 | Altera produced Graphic Design File of Blockb3_a (redrawn)                     |

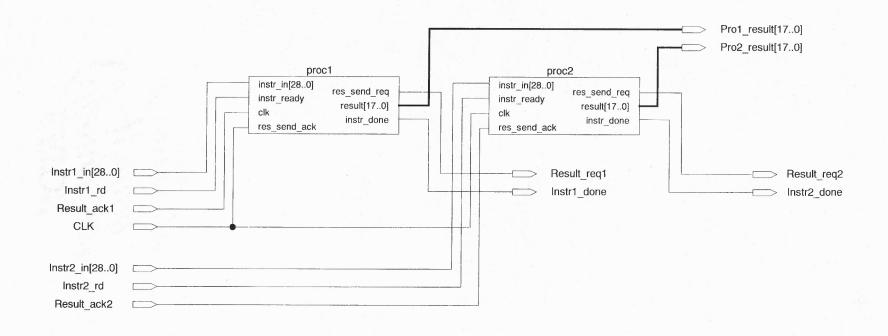

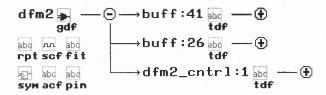

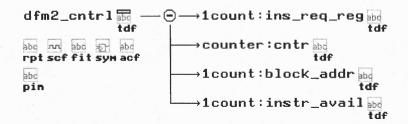

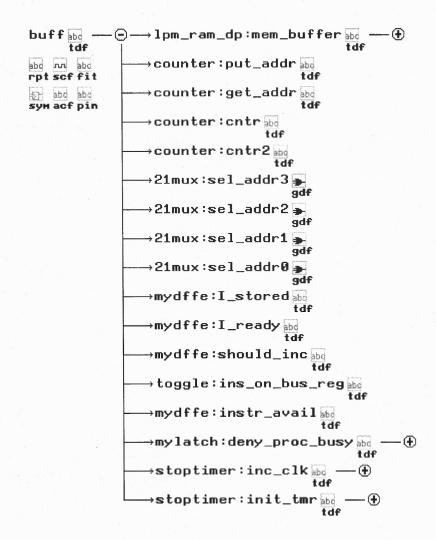

| 3.22 | Altera produced Graphic Design File of dfm2 (redrawn)                          |

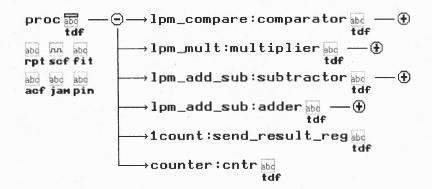

| 3.23 | Altera produced Graphic Design File of Proc_Pool (redrawn)                     |

| 5.1  | Possible Schematic of an Intelligent Cell                                      |

| 5.2  | Logic used to configure Flag Bits                                              |

| 5.3  | (a) High-Level implementation of DFM (b) Block Implementation                  |

|      |                                                                                |

#### 1 INTRODUCTION

#### 1.1 Objective

Computing or information systems today are the most complex human artifacts, in many respects, from their material composition. The invention of the transistor revolutionized the computing industry and has had a tremendous impact on the society in a manner that no one could have foreseen or predicted. Current estimates of transistor production stands at about 5 ~ 6 billion transistors every second [21]. As manufacturing processes get smaller and cheaper, add to that ever-faster computers, and simulation tools that can replicate an engineer's design to the smallest detail, allows innovators to stretch their imagination and ingenuity without any bounds. Every few years, what seemed improbable is accomplished and exceeded. The dataflow computer is one such entity, every new generation of design engineers has been coming closer to realizing a pure dataflow machine. Dataflow computing was first proposed in the 1950s, followed by dataflow schemas proposed by Karp and Miller in 1966 [1] and Rodriquez in1969 [1]. This document presents yet a new way of implementing a dataflow computer using FPGAs (Field Programmable Gate Arrays).

## 1.2 Fundamentals of Computing Paradigms

Computing architectures can be broadly classified into two major groups based on their execution model, namely *Control Flow* and *Data Flow*. This section briefly presents the properties of the two paradigms.

#### 1.2.1 Control Flow

By far, the Control Flow (CF) paradigm is the oldest surviving computing paradigm, which also happens to be the most popular architecture being implemented today. The CF model at its core is a sequential machine proposed by Von Neumann. It is surprising to observe that the basic Von Neumann sequential computation model has remained essentially the same through more than four decades. It is worth noting here that sequential machines have been shown to be universal computing machines by Alan Turing, and that the Von Neumann model can be considered as a pragmatic embodiment of the Turing machine [7].

The heart of a CF machine is the Program Counter (PC), which *steps* sequentially through a program (machine instructions) in memory, until it is explicitly changed by a instruction in memory such as a conditional instruction, or a jump instruction. Each *step* is divided into *sub-steps*; during the first *sub-step*, the memory address in the PC is used to fetch an instruction from memory while simultaneously incrementing the PC (PC = PC + 1). This is followed by a *sub-step* where the fetched instruction is decoded. In the subsequent *sub-step*, the operands specified by the instructions are fetched. This is followed by a *sub-step* where the instruction is sent to the Arithmetic Logic Unit (ALU) or execution unit, in general, to be executed. In the final *sub-step*, the result obtained earlier from the ALU is written back to memory or CPU registers. The whole process is then repeated and continues till a conditional instruction or a jump sends the PC in a new direction of execution. Other reasons the PC would change direction of execution, is when a procedure is called or when returning from a procedure, and when an exception occurs.

Within the framework of the von Neumann model, relatively few architectural innovations characterize today's sequential computers. These can be summarized as follows:

- The *indexed modification of addresses* and the *memory hierarchy* ideas was conceived by a group at Manchester University in 1949. The index registers permitted the execution of loops without modifying the instruction addresses and the automatic reallocation of programs in memory. The memory hierarchy idea led later to the *caches* and *virtual machine* concepts [7].

- In 1951, Wilkes proposed the *micro-programmed control* technique, as a new and systematic way of controlling the operation of computers [7].

- Another important innovation incorporated into the von Neumann model is the stack architecture proposed by Barton in 1958, as a tool for compiling and executing expressions, in order to have the machine architecture reflect the organization of a specific programming language. The same concept has been subsequently recognized as particularly advantageous for operating systems in managing subroutine invocation and in general program context [7].

- Other major innovations thrown into the cauldron of von Neumann model to particularly "improve performance" are the introduction of the pipeline architecture, vector arithmetic units, super-scalar structures and, separation of I/O from major processor tasks [7].

One reason for the whole hearted adoption of the Von Neumann architecture can be traced to its conceptual simplicity, which was necessary at the time it was conceived due to the high cost (and unreliability) of the original electronic components (vacuum tubes). A more poignant reason for its success is the fact that it has operated as an efficient bridge between software and hardware, permitting the hardware to be developed almost independently from the software and vice-versa.

#### 1.2.2 Data Flow

The concept of data-driven computation is as old as electronic computing. It is ironic that the same Von Neumann, who is some-times blamed for having created a bottleneck that dataflow architecture tries to remove, made an extensive study of neural nets, which have a data-driven nature [1]. Asynchronously operating in/out channels, introduced in the 1950s, which communicate according to a ready/acknowledge protocol, are among the first implementations of data-driven execution. The development in the 1960s of multiprogrammed operating systems provided the first experience with the complexities of large-scale asynchronous parallelism. After exposure to these problems in the MULTICS project, in 1969 Dennis developed the model of dataflow schemas, building on work by Karp and Miller (1966) and Rodriquez (1969) [1]. These dataflow graphs, as they were later called, evolved rapidly from a method for designing and verifying operating systems to a base language for a new architecture. The first designs for such machines (Dennis and Misunas 1974; Rumbaugh 1975 [1]) were made at Massachusetts Institute of Technology. The first dataflow machine became operational in July 1976 [1].

Dataflow and Control flow are two extremes of execution model spectrum. While control flow is inherently sequential, dataflow is inherently parallel. That is to say, to extract the parallelism out of a control flow machine, additional work has to be done to find instructions that can be executed concurrently. On the other hand, a dataflow machine's inherent parallelism eliminates this overhead.

In a dataflow computer, the execution of an instruction is driven by data availability instead of being guided by a program counter (described in the previous section). In theory, any instruction should be ready for execution whenever all operands needed for it's execution become available. Unlike sequential computers, where the instructions resident in memory need to be stored in an ordered manner (since the program counter steps through an ordered set of instructions), instructions in a data-driven program can be ordered randomly in memory. Though data and instructions reside in the same memory in a sequential von Neumann machine, they are stored in separate memory locations, i.e. an instruction and the data it operates on, does not reside in the same memory location. On the other hand, in a dataflow machine data are held inside the instructions [20].

Due to the inherent parallelism of dataflow machines, it is not possible to describe their operation in neat discrete steps as was possible in the operation of the Von Neumann computer. Instead, an overview of what happens inside a dataflow machine is presented. Results obtained from the execution of an instruction are called *data tokens*, and are passed directly between instructions [20], i.e. when a instruction is executed the produced result is duplicated into many copies, and forwarded directly to all instructions that need that value. Each of these instructions that receive the value check to see if they possess all the operands they need to execute. If any such instructions exist, they *fire* (they are dispatched to be executed), producing more data tokens upon execution, which in turn may fire other instructions. This process continues till no more data tokens are produced, and no more instructions are readied for execution. A data token once consumed by an instruction, is no longer available for reuse by other instructions [20].

This data-driven scheme requires no shared memory (since results are passed directly to needy instructions), no program counter, and no control sequencer (since no order of execution needs to be specified at run time) [20]. However, it requires special mechanisms to detect data availability, to match tokens with needy instructions, and to enable the chain reaction of asynchronous instruction executions. No memory sharing results in no *side effects*, which is a problem in von Neumann computers.

Asynchrony implies the need for handshaking or token-matching operations [20]. These two operations produce considerable overhead on a dataflow computer; a reason why dataflow machines have not made it into mainstream computing. A pure dataflow computer exploits fine-grain parallelism at the instruction level. Massive parallelism would be possible if data-driven mechanism could be cost-effectively implemented with low instruction execution overhead [20].

To get a better overview of the two paradigms covered, an example is presented of how a program is executed within the realm of either paradigms. Consider the execution of the following program:

#### Addr Instruction

- $1. \quad C = A + B$

- 2. D = C \* A;

- 3. E = C B;

- 4. F = C + D;

#### **Figure 1.1 Sample Program**

It can be easily seen from Table 1.1, that the dataflow model needs one less step to execute this program and that it extracts the maximum parallelism out of this set of instructions. Control flow on the other hand does not extract any parallelism and would require special software (compiler or OS) or hardware added on to the sequential model (look-ahead or branch prediction) to accomplish the same speedup.

Table 1.1 Execution of a set of instructions under the two execution paradigms; Control Flow and Data Flow

| STEPS | CONTROL FLOW                                                                               | DATA FLOW                                                                                                                                                                                                                                                             |

|-------|--------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I     | When PC is 1, operands A and B are added and the result is stored in C. PC is incremented. | When operands A and B become available, instruction 1 is sent for execution. The resulting sum C is sent to instructions 2, 3, and 4.                                                                                                                                 |

| II    | Operands C and A are multiplied and the result is stored in D. PC is incremented.          | Both instructions 2 and 3 have all their operands available (C from instruction 1, A & B from before instruction 1 was executed). Both instructions 2 & 3 are sent for execution and result D is sent to instruction 4, and E to any other instructions that need it. |

| III   | Operand B is subtracted from operand C and the result is stored in E. PC is incremented.   | Instruction 4 has all its operands available (C from 1 and D from 2), so it is dispatched for execution and the result F is forwarded to any needy instructions.                                                                                                      |

| IV    | Operands C and D are added and the result is stored in F. PC is incremented.               |                                                                                                                                                                                                                                                                       |

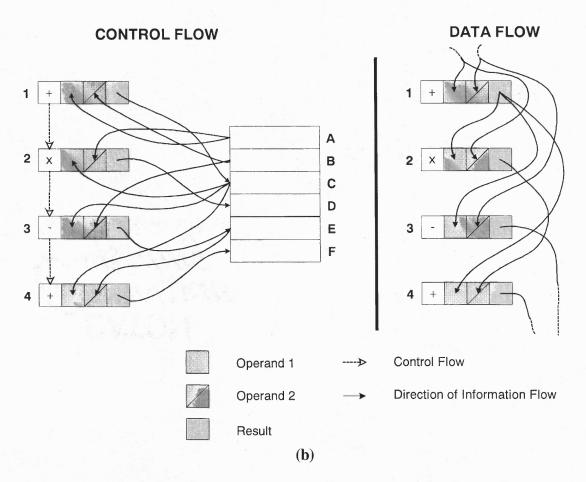

A program memory layout is presented below to show how the above set of instructions is laid out in memory of a control flow and data flow computer.

- 1. C = A + B;

- 2. D = C \* A;

- 3. E = C B;

- 4. F = C + D;

Figure 1-2 (a)

Figure 1.2 (a) Sample Program (b) Memory layout of instructions in Control Flow and Data Flow Computers.

The left side of the figure represents the program in memory of a control flow computer and the right side represents the program in memory of a data flow computer. Though the memory locations in the control flow computer, labeled 1,2,3,4 and A,B,C,D,E,F are shown separately, they belong to the same memory space. They are drawn side-by-side to accommodate the representation of the flow of operands and results. Note that there are no control flow arrows in the dataflow computer, since there aren't any. Also note that, while results are stored in designated locations in the memory of the control flow computer, in a dataflow computer the results are stored in the same location as the instructions receiving the results.

Now that the two paradigms have been adequately understood, it is only appropriate that issues that are to be dealt with when designing and implementing dataflow computers are discussed.

#### 2 ISSUES AND PRIOR RESEARCH

### 2.1 Issues (Data Flow in Depth)

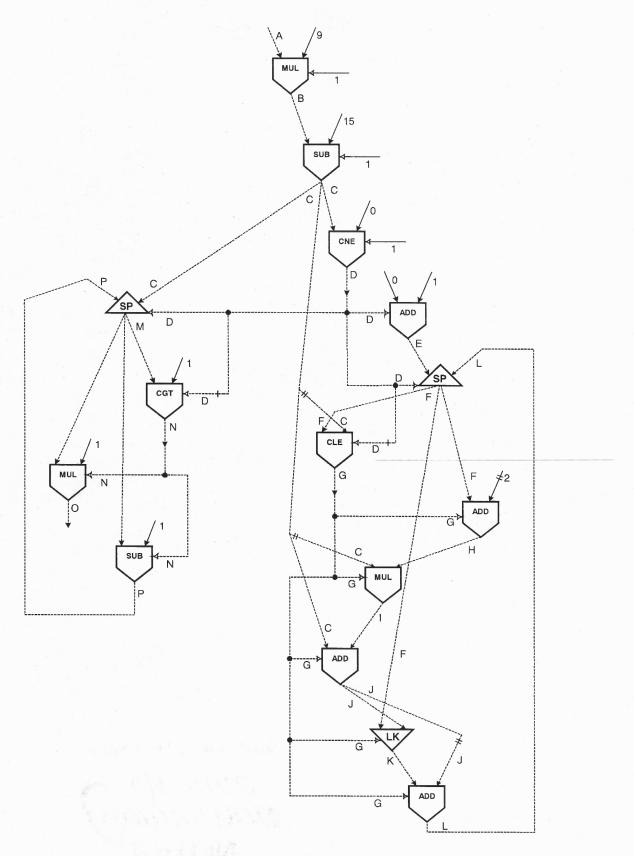

The dataflow-computing paradigm is a direct result of dataflow graphs, which are a characteristic component of graph theory. Shown in the figure below is the dataflow graph of the program that was presented earlier.

Figure 2.1 Dataflow graph of the program presented on the right

Each dataflow graph is represented using directed arcs and nodes; arcs are arrows entering or leaving the nodes, which are points that hold the instruction to be executed. The number of arcs entering a node equals the number of operands the node (instruction) needs to fire (execute), and the number of arcs leaving a node equals the number of nodes (instructions) that need the result of the firing node (instruction execution).

This simplistic execution model of dataflow computers is also its biggest drawback. The lack of an inherent control mechanism as in the von Neumann architecture requires other mechanisms to keep a dataflow computer in check.

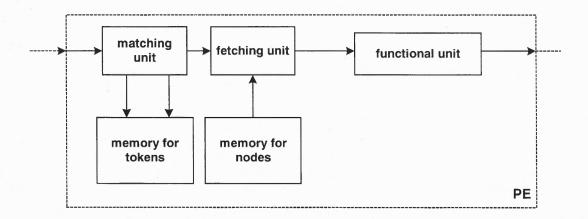

The first problem to be addressed is that of "How does an instruction know that its operands have arrived?" Since instructions are static objects without intelligence, some mechanism has to be provided to accomplish this task. This is normally done by a device called the *token matching unit*, as shown in the Figure 2.2. The figure below shows a typical construct of a dataflow computer called the *Processing Element (PE)*, which handles a number of nodes stored in the box labeled *memory for nodes* [1].

Figure 2.2 Functional diagram of a processing element in of a tagged-token machine [1].

Input arcs (data tokens) enter the PE from the left and output arcs (result) exit from the right of the PE. Each token entering the PE has two fields, 'a list of destination nodes' and 'a value' that has to be forwarded to the list of destination nodes. In most dataflow machines, the number of input arcs is limited to two, and associated with each item in the 'list of destination nodes' in the token is an extra bit that indicates whether the addressed node is monadic or dyadic. Only for a dyadic node does the matching unit check whether its local memory already contains a matching token, i.e. it looks for a token with the same destination. When the matching unit finds a node ready to fire, the fetching unit extracts the addressed node (instruction) from the 'memory for nodes' and

forwards the entire set (instruction, operand/s, and destination addresses) to the functional unit, which in turn executes the instruction and sends out the result (a token containing the result and destination addresses) [1].

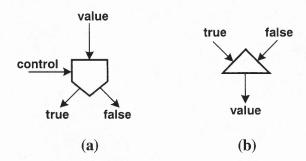

Other issues that plague dataflow machines are related to the implementation of simple programming constructs that are taken for granted in Von Neumann architecture, such as conditional statements, loops (count and conditional) and modularization (procedures and functions). Accommodating loops and conditionals requires nodes that implement controlled branching.

Figure 2.3 (a) A BRANCH node. (b) A non-deterministic MERGE node.

The conditional jump of a dataflow program is represented in a dataflow graph by BRANCH nodes. The most common form is the one depicted in Figure 2.3(a). A copy of the token absorbed from the value port is placed on the true or on the false output arc, depending on the value of the control token. Variations of this node with more than two alternative output arcs or with more than one value port (compound BRANCH) can also be used. A MERGE node does not have a strict enabling rule; that is, not all input ports have to contain a token before the node can fire. In the deterministic variety, the value of a control token determines from which of the two input ports a token is absorbed. A copy of the absorbed token is sent to the output arc. The nondeterministic MERGE node

shown in Figure 2.3 (b) (i.e., a MERGE node without control input) is enabled as soon as one of its input ports contains a token; when it fires, it simply copies the token that it receives to its successors.

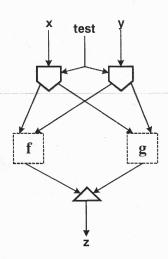

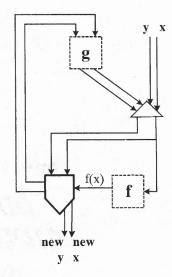

Figure 2.4 Conditional Expression Graph.

Figure 2.4 shows an implementation of a conditional construct graph corresponding to the expression z := if test then f(x, y) else g(x, y) fi. If one token enters at each of the three arcs at the top of the graph, the two BRANCH nodes will each send a token to subgraph f or to subgraph g depending on the value of test. Only the activated subgraph will eventually send a token to the MERGE node [1].

An iterative loop can also be implemented using the same two specialized nodes, BRANCH and MERGE. Figure 2.5 shows an implementation of a loop construct graph corresponding to the expression while f(x) do (x, y) := g(x, y) od.

Figure 2.5 Loop Construct Graph

Initially the values (x, y) are presented at the input arcs of the nondeterministic MERGE node which simply copies the values to its output arcs, which puts the value x at the input arc of the subgraph f activating it. The output of the subgraph f determines the output of the compound BRANCH. If the value at the control port of the BRANCH node is true, then f and f at the value ports of the BRANCH node are forwarded to the subgraph f if the value at the control port of the BRANCH node is false, then f and f at the value ports of the BRANCH node are sent the other way. Reception of f is f by the subgraph f fires it and produces two new values of f and f which are forwarded to the MERGE node. This process continues till the subgraph f evaluates a false output.

It may be noticed here that there is no exploitation of concurrency in executing this loop. This method is called the lock method [1][12]. It is safe and simple, but not very attractive for parallel machines. The level of concurrency is low since the BRANCH node acts as a lock that prevents the initiation of a new iteration before the previous one has been concluded. An alternative approach is the acknowledge method. This can be

implemented by adding extra acknowledge arcs from the consuming node to the producing node. These acknowledge arcs ensure that no arc will ever contain more than one token and the graph is therefore safe. One arc provides space for one token. In a manner too complicated to show here, the proper addition of dummy nodes and arcs can transform a reentrant graph into an equivalent one that allows overlap of consecutive iterations in a pipelined fashion. The acknowledge method therefore allows more concurrency than the lock method, but at the cost of at least doubling the number of arcs and tokens [1].

A higher level of concurrency can be obtained when each iteration is executed as a separate instance (or copy) of the reentrant subgraph. This code-copying method requires a machine with facilities to create a new instance of a subgraph and to direct tokens to the appropriate instance. A potentially more efficient way to implement code copying is to share the node descriptions between the different instances of a graph without confusing tokens that belong to separate instances. This is accomplished by attaching a tag to each token that identifies the instance of the node that it is directed to. These so-called tagged-token architectures have an enabling rule that states that a node is enabled if each input arc contains a token with identical tags. Though this method increases concurrency, implementation of such a technique is not easy and involves considerable overhead [1].

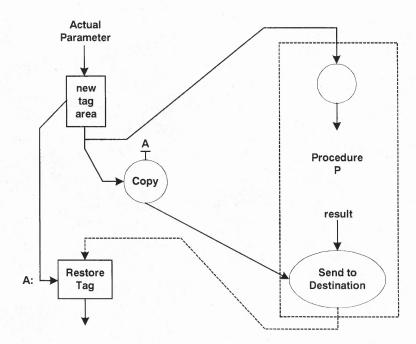

The last problem that needs to be mentioned is the issue of procedure invocation. Calling a procedure introduces similar problems as with reentrancy, to which the methods described above can be applied. In code-copying architectures, a copy of the called procedure is made. In tagged-token architectures, a new tag area is allocated for each

procedure call so that each invocation executes in its own context. Nested procedure calls, recursion, and co-routines can therefore be implemented without any additional problems. An extra facility is however required to direct the output tokens of the procedure activation back to the proper calling site. This is usually implemented as shown in Figure 2.6.

Figure 2.6 Interface for a Procedure Call.

On the left, a call is made to procedure P whose graph is on the right. P has one parameter and one return value. The actual parameter receives a new tag and is sent to the input node of P, and concurrently a token containing address A is sent to the output node SEND-TO-DESTINATION. This SEND-TO-DESTINATION node transmits the other input token to a node whose address is contained in the first token. The effect is that, when the return value of the procedure becomes available, the output node sends the result to node A, which then restores the tag belonging to the calling expression. These

output nodes are special nodes capable of sending tokens to nodes, to which they have no static arc [1].

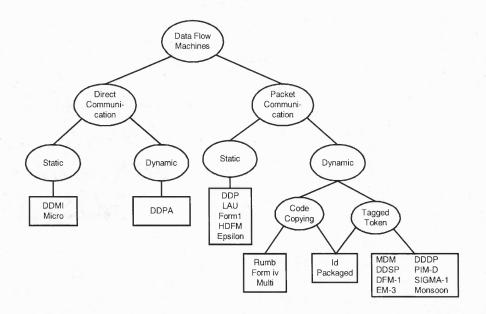

Machines that handle reentrancy by the lock or acknowledge method are called static; those employing code copying or tagged tokens are called dynamic. Static machines are much simpler than dynamic machines, but for most algorithms their effective concurrency is lower. Algorithms with a predominantly pipelining type of parallelism, however, execute efficiently on static machines with acknowledging [1].

#### **COMMUNICATION IN A DATA FLOW PARALLEL COMPUTER:**

Communication in a dataflow machine is accomplished either by *direct* communication or via a *packet communication network* [1].

In *direct communication* machines, adjacent nodes in the graph are allocated to the same processing element or to processing elements that have a direct connection with each other. An important property of direct communication architectures is that the communication medium delivers tokens in the same order as they were received [1].

Packet communication offers the greatest opportunity for load distribution and parallelism in the communication unit, since it can be constructed from asynchronously operating packet-switching modules. Such a module can accept a token and forward it to another module, depending on its destination address [1].

This section covered the issues affecting dataflow computers, and the solutions that researchers have come up with to overcome these issues. The apparently simple concept of data driven execution has many complex implementation issues, yet researchers have come up with brilliant ideas of implementing such machines, which is the topic of the next section.

#### 2.2 Prior Research

Figure 2.7 illustrates dataflow machines categorized according to the nature of the communication unit and the architecture of the processing elements.

Figure 2.7 A survey of dataflow machines, categorized according to their architecture and implementation. The keys in the boxes refer to the machines [1]

This categorization is not strict, but does broadly cover most dataflow machines implemented or hypothesized till date. At the end of this section, dataflow machines that do not strictly fall under the categories shown in Figure 2.7 will be presented.

#### 2.2.1 Direct Communication Machines

The main drawback of direct communication machines is that for many graphs it is difficult to find a good mapping onto the network (processor allocation problem). It may be a fruitful approach, however, for applications that have predictable and regular communication patterns matching the machine's topology. The most important member of this class is the oldest working dataflow machine, the DDMI [1]. The processing elements of this machine are arranged as a tree. Allocation is simplified by preserving the

hierarchical tree structure of the program. Any internal node of the processing tree can allocate a part of its program (a subtree) to any of its descendants. Allocation is simple and distributed, but far from optimal with respect to load distribution over the processing elements. The root of the tree forms a bottleneck in the communication between processing elements.

In Japan, an interesting dynamic direct communication machine has been developed for large-scale scientific calculations, such as solving partial differential equations [1]. The processing elements are arranged on a two-dimensional grid and use tags to distinguish tokens belonging to different activations. To avoid the necessity to allocate unique tag areas dynamically, the input language is somewhat restricted (no general recursion) so that static allocation is possible. A hardware simulator for 4 x 4 processing elements, each connected to eight neighbors has been used to study small applications. It confirmed analytical predictions that communication delay does not seriously degrade performance, provided that programs have enough parallelism.

#### 2.2.2 Static Packet Communication Machines

The first packet communication dataflow machine that became operational is the Distributed Data Processor [1], built at Texas Instruments. The references suggest that the DDP uses a locking method to protect reentrant graphs. Although the compiler may create additional copies of a procedure to increase parallelism, this copying occurs statically. It is a one-level machine with a ring-structured communication unit, augmented with a direct feedback link for tokens that stay within the same processing element. A prototype comprising four processing elements has been built.

Dennis and his colleagues at the Massachusetts Institute of Technology produced the first designs for dataflow machines [1]. The earliest design had a two-stage structure, an enabling unit (called an instruction cell) dedicated to one node and heterogeneous functional units. This design was later extended into a series of machines differing in the way they handled reentrancy and data structures. They ranged from the elementary Form I processor, which was static and could only handle elementary data, to the full-fledged Form IV processor, which had extensive structure facilities and could copy subgraphs on demand. The prototype that is now operational consists of eight processing elements and an equidistant packet routing network built from 2 x 2 routing elements.

Around 1990, Sandia National Laboratories in Albuquerque, NM, designed and implemented a static dataflow computer called the epsilon dataflow computer, based on the epsilon processor [9][11]. The overall epsilon system was designed as a scalable multi-processor architecture consisting of epsilon processors and structure memory units connected with a packet switched network. The whole design was implemented on a single board using off-the-shelf components. At the time the group demonstrated a sustained performance of the epsilon machine comparable to commercial minisupercomputers.

## 2.2.3 Machines with Code-Copying Facilities

The dataflow machines with potentially the highest level of parallelism are the dynamic dataflow machines; they employ either code copying or tags to protect reentrant graphs. It is a characteristic of a code-copying machine, that the physical address of a node cannot

always be determined statically. The first detailed design of a dataflow machine was of this type was presented by Rumbaugh in 1975 [1]. Allocation in this machine is per procedure; all the nodes and intermediate results of each procedure are stored in the memory of one processing element. There is a fast connection from the output to the input port of a processing element, such that a circular pipeline is created. Tokens stay within this pipeline unless they are directed to another procedure, in which case they are routed to a special processing element called the scheduler. This scheduler sends a copy of the called procedure and its input values to an idle processing element. If there is no idle processing element, it waits until a processing element becomes dormant and then saves its state (i.e., all the unprocessed tokens) and declares itself as idle. The Massachusetts Institute of Technology Form IV dataflow processor refers to a whole family of designs, some of which have implemented the code-copying scheme.

### 2.2.4 Tagged-Token Machines

The first tagged-token dataflow machine built was the Manchester Dataflow Machine [1]. The group developed the tagged-token concept to increase parallelism for reentrant graphs independently from similar work done by Arvind and Gostelow in 1977 [1]. The processing element of the Manchester Dataflow Machine had a pipeline of four units: token queue, matching unit, fetching unit, and functional unit. Each unit works internally in a synchronous manner, but they communicate via asynchronous protocols. More than 30 packets can be processed simultaneously in the various stages of the pipeline. To maximize the communication speed, the data paths are all parallel (up to 166 bits wide), transmitting a complete packet at a time. Consequently the sizes of packets, and thus of tokens, are fixed. The token queue is implemented as a simple FIFO buffer.

One of the newest dynamic dataflow machines following the tagged-token communication model is the Monsoon Computer built at the Massachusetts Institute of Technology in collaboration with Motorola Inc. [10]. The Monsoon is an experimental multi-threaded, multi-processor targeted to large-scale, general-purpose scientific and symbolic computations. The Monsoon machine includes a collection of 64-bit pipelined PEs that can execute up to 8 threads simultaneously. The PEs are connected via a multistage packet switch network to each other, and to a set of interleaved I-structure memory modules. An I-Structure memory module is a two stage pipelined structure consisting of a memory stage and an output stage. In the memory stage, an incoming request is decoded into an operation code, memory address, and a value or return continuation [10]. A memory operation is performed on the memory address, and for some operations, a response is generated to be sent to the requesting PE. If a response is generated, it is injected into the interprocessor network in the output stage, which forwards the response to the appropriate PE. The PE nodes implement hardware primitives for direct support of efficient multi-threading, including zero-cycle context switching, single cycle fork and join, and split-phase memory references with arbitrary reordering. The basic run-time execution state of a Monsoon program comprises a tree of activation records, which correspond to the invocation state of many simultaneous procedures that can be executing at the same time.

#### 2.2.5 Other Architectures

The EM-4 dataflow machine was based on the EMC-R dataflow processor, and was a system proposed by the Electrotechnical Laboratory in Japan around 1989 [4]. This architecture denounced the traditional architectural model in dataflow computing of

simple packet-switching, circular pipeline, and colored token style. It introduced the concept of a *strongly connected arc* and that of a *strongly connected block*. In the strongly arc model of representing a dataflow graph, arcs are categorized into two types: normal arcs and strongly connected arcs. A strongly connected arc is a normal arc that the user defines as strongly connected. A dataflow subgraph whose nodes are connected by strongly connected arcs is called a strongly connected block (SCB). Two firing rules were used. One, a node on a dataflow graph is firable when all the input arcs have their own tokens (a normal data-driven rule). The other is that after each SCB fires, all the processing elements which will execute a node in the block should execute nodes in the block exclusively. The architectural detours made in the evolution of this computer were based on these new concepts.

The Cydra 5 Directed Dataflow Architecture that was proposed in 1988 by Cydrome Inc, California, added a new twist to the dataflow paradigm [2]. According to the author Dr. B. Ramakrishna Rau, each executing operation on a data flow computer needs to address five issues:

- Will the operation be executed at all?

- If so, when will it execute?

- On which processing element will it execute?

- Where are the input operands located?

- Where will the result be placed?

Although a directed dataflow computer retains the important benefits of the dataflow architecture, it also makes the concept commercially viable by moving as much

decision-making as possible from runtime to compile time. While in a regular dataflow computer the listed five issues must be addressed at run-time for each operation executed, in directed dataflow architecture these issues are settled at the compile time to the extent possible.

The MADAME computer (MAcro-DAtaflow MachinE) was proposed at the Jozef Stefan Institute, Slovenia in 1991. The idea presented adopting dataflow scheduling in larger chunks of instructions, instead of the traditional instruction level scheduling (fine-grain dataflow) [8].

# 2.3 Motivation and Objectives

The concept of dataflow computers was first introduced to me as an undergraduate student of computer engineering. Its conceptual simplicity struck a chord within me immediately, but at the same time, the lack of methods to efficiently implement the dataflow concept challenged and motivated me to study it further. After investigating the work that other researchers in the field of computer engineering had done on dataflow computers, I realized that engineers were trying to tackle the problem of implementing a data flow computer at the processor level. Dataflow computers in the past have been implemented by using a modified processor, often called the *Processing Element* (PE), which composed of a processing unit along with memory to store partially active instructions and tags. The PE would also contain a matching unit to match the incoming tags, and in addition was assigned the task of sending and receiving tags, from and to other PEs (described earlier in Section 2.1). Most of the inactive instructions would reside in some memory outside the PE.

This thesis presents a way of implementing dataflow computer at the memory level, i.e. intelligent memory is used to perform dataflow tasks. Processors in this system perform the role of execution units; executing whatever instructions the dataflow memory sends it. The motivation behind this idea was that, such a method would incur lesser overhead than the previous methods used to implement data flow computers. In addition, this idea follows the dataflow paradigm very closely, as opposed to the pseudo-dataflow architectures that past researchers have proposed.

The objective of this thesis was to design and implement a proof-of-concept dataflow computer in which the memory is dataflow. Since building this machine on silicon was not a possibility, it was decided that FPGAs would be used instead to build the machine. Speed, efficiency and performance were not primary goals of this design, rather feasibility of the "dataflow memory" (active or intelligent memory) architecture was given priority.

The architecture that is presented in this thesis is a breakaway from the traditional methods of implementing data flow computers, and I believe that this architecture could possibly offer a promising solution in designing an efficient dataflow computer.

# 3 THEORETICAL APPROACH AND IMPLEMENTING A DATAFLOW COMPUTER

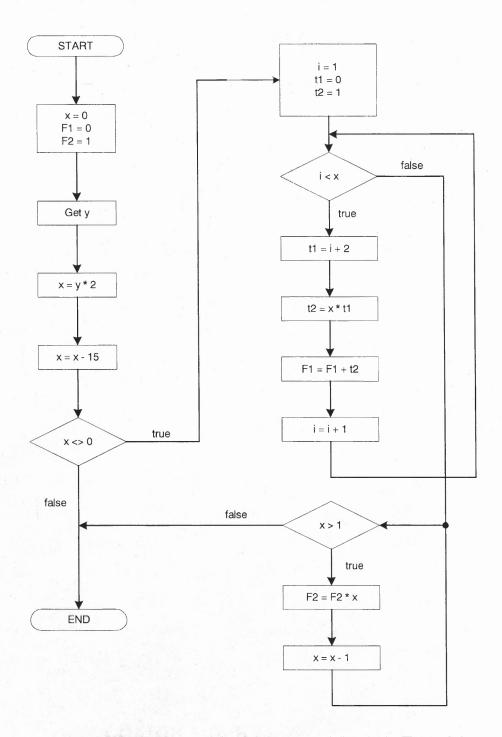

# 3.1 Overview of the Design

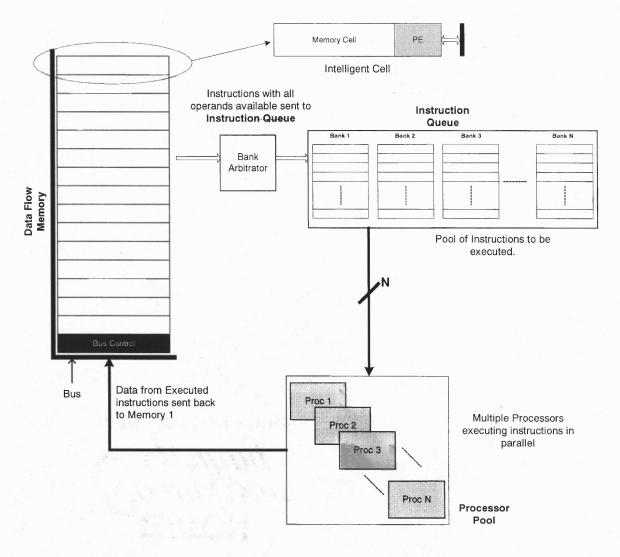

The basic structure of the Data Flow Computer (DFC) is shown in Figure 3.1. It consists of three major parts: the instruction memory *Data Flow Memory* (DFM), the intermediate buffer *Instruction Queue* (IQ) and the execution units *Processor Pool*. In addition there are minor components, such as the *Bank Arbitrator*, the *Bus* and the *Bus Control*.

Figure 3.1 Overall Structure of Data Flow Computer

# 3.1.1 Data Flow Memory

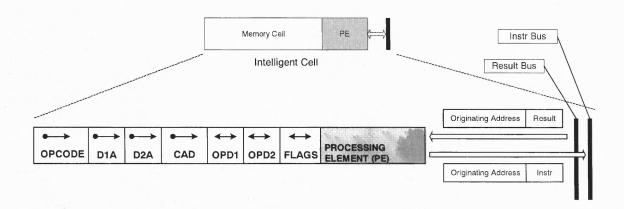

Data Flow Memory (DFM) is the heart of the Data Flow Machine in this design. It is a special kind of intelligent-memory, where **each** memory location is an *intelligent cell* (cell) consisting of two parts, the *instruction part*, and the *processing element* part.

The instruction part is in turn divided into 6 components:

- The instruction opcode (OPCODE).

- Source of the first operand (D1A).

- Source of the second operand (D2A).

- Source of the clause operand (CAD).

- Operand to be obtained from the first source (OPD1).

- Operand to be obtained from the second source (OPD2).

- Flags used to control the behavior of the instruction (FLAGS).

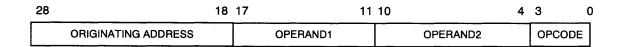

The result of an instruction that has finished executing is immediately broadcasted to all the cells in the DFM. Each broadcasted packet contains the result along with the address of the instruction in DFM that sent it for execution, and is called a result packet. The processing element (PE, different from previous dataflow discussions) in each cell is responsible for picking up broadcasted result packets sent by the processor pool via the result bus. If the address in the broadcasted result packet is either equal to D1A or D2A, then the data is written to either OPD1 or OPD2 respectively, and appropriate flags are set. When both OPD1 and OPD2 become available (determined by examining appropriate flags), the PE sends an executable packet (composed of the instruction opcode, the operands and the cell address of the sending PE) to the bank

arbitrator. An *executable* is an instruction ready for execution and contains four fields; the instruction opcode, operands 1 and 2, and the cell address of the sending PE. It is important to point out here that the bus on which the result packets are broadcasted is independent (separate) of the bus on which executable packets are relayed to the bank arbitrator. This is done to avoid congestion that would occur if one bus were used.

The CAD field is used to store the address of an instruction that sends the clause. A *clause* is a boolean value stored as a flag in the flags field which acts like a permission for the instruction that needs it, i.e. an instruction will execute only if it's clause field is '1'. The clause is useful in the construction and execution of "conditional" or "looping" program constructs. For an instruction to fire, three flags have to be set, the two operand flags (indicating at both operands are available) and the clause flag.

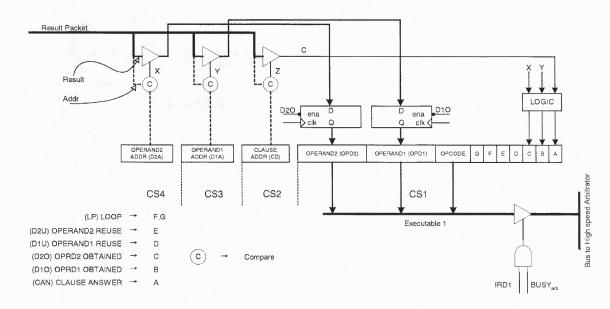

The internal structure of an intelligent cell in DFM is shown in Figure 3.2. Each section within an intelligent cell is labeled as described earlier. The little arrows within each cell denote the direction of information flow from the cell to the PE. The instruction bus and the result bus are also shown along with the format in which the PE communicates with them.

Figure 3.2 Internal Structure of Intelligent Cell in DFM

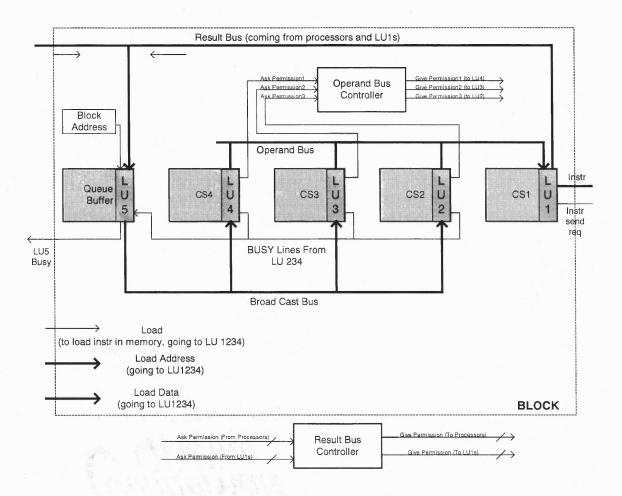

The Bus Controller (BC) in the DFM controls the arbitration of the result packets sent by the processor pool to the DFM. The bus controller assures that the result packets are broadcasted in orderly manner on the Result Bus.

## 3.1.2 Instruction Queue

The *Instruction Queue* (IQ) is an intermediate buffer between DFM and the Processor Pool, and is made up of the *Bank Arbitrator* (BA) and multiple banks of memory. The number of banks in IQ is equal to the number of processors in the processor pool. Each processor is assigned one bank exclusively. This assures that all processors can access memory at the same time. Ideally, a cross bar switch should be implemented so that a processor can access another bank if no instructions are available for execution in its own bank, but this method was avoided to keep the initial design simple. No processor is busy all the time or idles all the time; this is because the bank arbitrator makes sure that the number of executables allotted to each memory bank, hence to each processor, is the same. It uses a round robin scheme to allocate executables to the memory banks.

The IQ acts as a buffer from where the processor pool can access the executables. This leaves the DFM to do its tasks without worrying about distributing executables to the processor pool. When instructions are ready for execution, the DFM simply dispatches the corresponding executables to the IQ, where they await execution. This concept of a two level memory structure, one where all instructions are held, and another where only instructions ready for execution are held is similar to an idea presented by Dr. Dennis of the Massachusetts Institute of Technology [13].

#### 3.1.3 Processor Pool

The processor pool is simply a pool of execution units. Each processor sequentially executes ready instructions (executables) from the bank that it is assigned. The instructions are executed in no particular order because all the instructions in the memory bank are waiting to be executed.

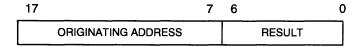

When any processor obtains an instruction, it also gets the originating address of the instruction. After execution, the obtained result along with the originating address (result packet) is sent to the *Bus Controller* of the DFM, which then broadcasts the packet to all the cells via the result bus.

# **3.1.4** Flow of Data and Instructions in the Data Flow Computer

## In Data Flow Memory.

The memory cell in DFM that has all its data (OP1 and OP2) and appropriate flags set, sends an executable out for execution (to the bank arbitrator). A seed can be used to initiate this.

#### In Intermediate Buffer.

Once the bank arbitrator receives the executable packet, it places that information in the appropriate memory location. It chooses the appropriate location by first choosing the correct memory bank, which it selects using a round robin scheme (it keeps track of the next bank it must use), and then selecting the next available location in that memory bank.

#### In Processor Pool.

3 Each processor in the processor pool executes the available ready instructions (executables) sequentially, stepping through them as in a Von Neumann machine.

After the processors associated with their respective banks retrieve the executables, the bank is notified and those locations from where the executables were retrieved are made available to store new executables.

4 Each processor in the pool executes the ready instruction that it retrieved from the IQ and then sends a result packet to the bus controller in the DFM.

#### In Data Flow Memory.

- 5 The bus controller broadcasts this packet to all the cells in memory.

- All the cells in DFM, pick up the broadcast packet. A cell absorbs the packet only if the originating address of the broadcast is equal to either one of its operand source addresses. (The PE of each cell does this comparison.)

- 7 Once a cell gets both its operands, the PE of that cell then sends a packet containing the executable (opcode + operands + cell address) to the bank arbitrator.

It may feel that broadcasting messages could cause considerable congestion on the bus, but the number of messages on the bus is never greater than the number of processors in the processor pool, since, besides the broadcast of the initial data (the seed used to initialize), all the broadcasting is done only by the processors.

#### **3.1.5** Remarks

This design presented here is suitable for small-scale data flow computers, i.e. a machine having about 16-32 processors in the processor pool. This restriction is foreseen due to two reasons. First, the number of memory banks in IQ will increase linearly with the number of processors, which for a large number of processors such as 1024 will be unrealistic. Secondly, having a large number of processors increases the number of broadcasted messages causing congestion on the broadcasting bus.

This thesis shows a new way of implementing a data flow computer, at the memory level (using intelligent-memory). Taking advantage of current advances in Field Programmable Gate Array (FPGA) technology, an FPGA-based prototype will be developed with emphasis on feasibility of the design. Performance currently is a secondary issue and is left for future research.

# 3.2 Field Programmable Gate Arrays (FPGAs)

Fastest performance is achieved when a design is implemented directly on silicon, with dedicated logic for all the different units. Since this project was a prototype, it was more important to check the feasibility of the design than performance. Hence a device was needed that could be easily reconfigured, if design flaws were detected. In addition to this, the device was required to have sufficient logic to be able to accommodate the different components of the design. The ideal solution for prototyping the dataflow computer was to use a FPGA.

FPGAs are user-programmable devices, which are widely accepted as an excellent technology for implementing moderately large digital circuits. They offer a cost-effective solution for prototyping, and have a much faster turn around time. Since FPGAs can be reprogrammed in the field, they can be used in innovative designs where hardware needs to change dynamically to adapt to different user applications. Though dynamically changeable hardware is not a consideration for this project, the ability to reprogram an FPGA unlimited number of times is particularly useful when prototyping, where the design is constantly being changed and updated. They also provide other advantages, such as shortening design and development cycles. In terms of speed-

performance, most FPGAs are slower than Complex Programmable Logic Devices. However, the rapid advance in FPGA technology is quickly closing the gap on speed and device density. One prominent disadvantage using FPGA technology is that circuit propagation delays are dependent on the performance of the design implementation tools used. This however is not a handicap for this project.

The internal architecture of an FPGA consists of several uncommitted logic blocks in which the design is to be encoded. The internal logic blocks consist of several universal gates that can be programmed to operate like multiplexers, decoders, logic gates, registers, transistors, random access memory and a slew of other digital logic primitives. The internal logic blocks are connected through a maze of programmable interconnects which can used to implement buses and logic interconnection. They have elaborate clocking schemes and optimization methods (based on design tools) that could produce faster hardware or use lesser logic blocks. Since all the logic blocks are independent, multiple units can be built in a single FPGA, all of which work independently and in parallel (key in the design of a parallel computer, such as a dataflow computer).

The FPGAs used in this design are those made by Altera Corp. Three models were chosen to implement the three major pieces of the dataflow computer; the DFM was implemented on a FLEX10KE, the IQ along with the bank arbitrator was implemented on the ACEK1K and the processor pool was implemented on a MAX9000.

The FLEX10KE was an ideal candidate for implementing the DFM because each device could provide up to 98,304 RAM bits that could be configured as dual-port memory for the DFM [17]. In addition each device contained sufficient logic, up to

200,000 gates depending on the device chosen, to implement the PEs in the DFM. All this is connected together by a fast interconnect network that has predictable interconnect delays [17].

The ACEX1K is a less powerful relative of the FLEX10KE. It has the same features as the FLEX10KE, except there is less of everything. The largest ACEX1K has 49,152 RAM bits and about 100,000 gates [17]. Since the logic and memory requirements for the IQ are less than that of the DFM, this device was an ideal device to implement the IQ in.

The MAX9000 is the smallest of the three devices used. This device contains no memory bits, but has sufficient logic gates and flipflops, up to 12,000 and 772 respectively, which was sufficient to implement the processor pool [19].

A major factor in deciding to use Altera's FPGAs to develop the prototype was the availability of a free development kit from Altera called MAX+II BASELINE version 10. In addition, Altera also supports university programs, through which it is possible to get free manuals on how to use the software, programming language reference (AHDL, Altera Hardware Definition Language), sample boards for hardware development, and most important of all, a technical help line to resolve problems faced during development.

In short, Altera FPGAs provided a low cost, highly configurable solution, along with a simple environment to develop the dataflow prototype. The FPGAs used for this project were appropriate for testing and verification, and have proven to be a very important tool for successful project completion.

# 3.3 Detailed Layout and Implementation of the Design

The detailed design of the proposed dataflow computer is presented in this section. Each component (DFM, IQ and Processor Pool) is covered in depth. This section also discusses the decisions made while implementing the proposed dataflow computer.

## 3.3.1 **DFM Architecture**

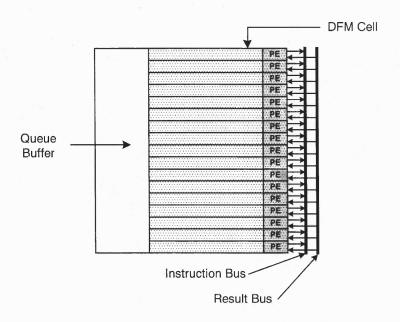

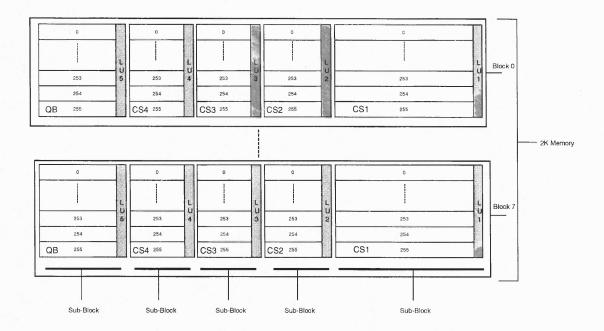

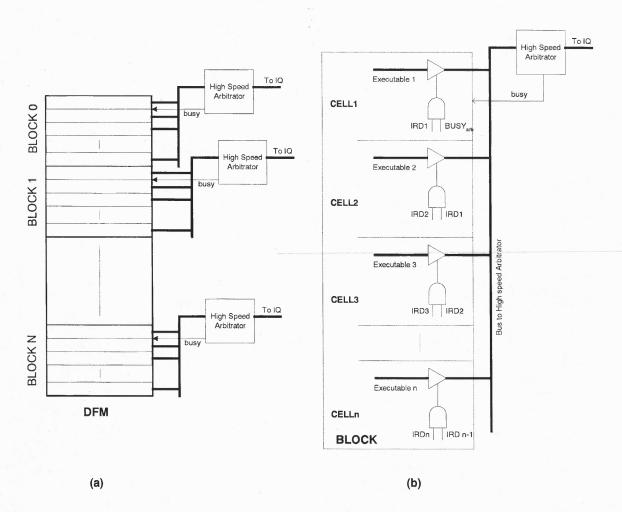

Figure 3.3 Dataflow Memory Structure

Besides the two buses shown in Figure 3.3, the DFM is divided into two sections, the *Queue Buffer* (QB) and the *DFM Cells*. The internal structure of a DFM cell is shown in Figure 3.4.

Figure 3.4 DFM Cell Structure

Each DFM memory cell is broken up into four sections, called *Cell Sections* (CS), CS1 through CS4. Each cell section, CS1 – CS4 holds a piece of the instruction to be executed. Controlling each CS, CS1 through CS4, is a 'Logic Unit' or LU. The LUs, LU1 through LU4, managing CS1 through CS4, respectively, constitute a PE. The bits in the CS's are grouped such that minimum communication is needed between the different LU's controlling the different CS's. By having an LU controlling only one CS, work on each CS is done independently and in parallel, avoiding potential waits that would arise if an LU controlled more than one CS across the cell.

#### **CELL SECTIONS:**

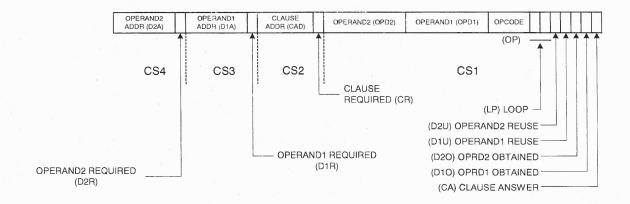

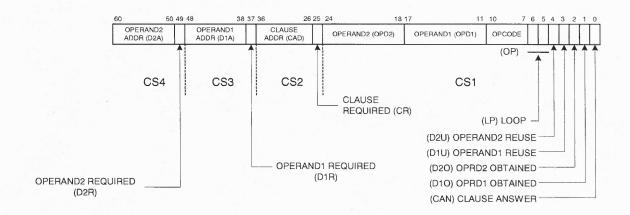

Cell Section 1(CS1): CS1 is made up of nine fields. Each field is described below.

Operand1 (OPD1): OPD1 is a field that holds operand1, which is received from the instruction whose address matches the value in D1A (source of operand1). OPD1 is sent to CS1 after LU3 picks up a result packet and makes a match between the originating address (OA) in the packet and D1A.

Operand2 (OPD2): OPD2 is a field that holds operand2, which is received from the instruction whose address matches the value in D2A (source of operand2). OPD2 is sent to CS1 after LU4 picks up a result packet and makes a match between the originating address (OA) in the packet and D2A.

Opcode (OP): OP is the opcode field, which holds the instruction to be executed.

Operand1 Obtained (D10): D10 is a one-bit flag that is set by LU1. The flag is set when LU1 receives OPD1 from LU3. This bit may be set at compile time or at run time. If it is set at compile time then the operand is already available (immediate value).

OPRD2 Obtained (D2O): D2O is a one-bit flag that is set by LU1. The flag is set when LU1 receives OPD2 from LU4. This bit may be set at compile time or at run time. If it is set at compile time then the operand is already available (immediate value).

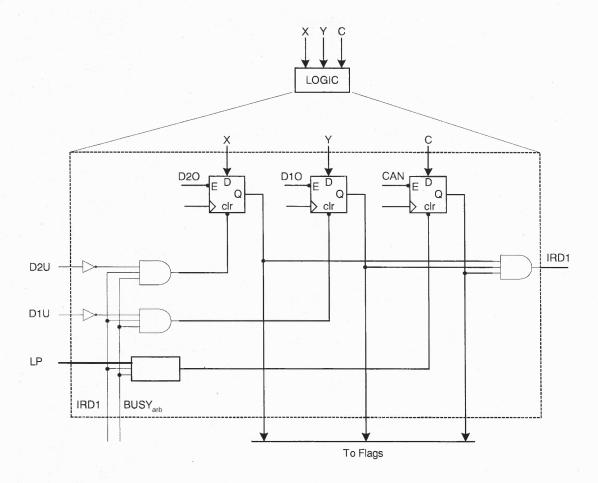

Clause Answer (CAN): This is a one-bit flag value which holds the boolean value that LU2 picked up from a message it received. This boolean value is sent by LU2 to LU1 when LU2 picks a message whose address matches the value in CAD. It is a bit used during execution of conditional and loop constructs. The CAN bit can be set at compile-time or at run-time. When a clause is not required to execute an instruction, this bit is set to '1' at compile time.

Operand1 Reuse (DIU) and Operand2 Reuse (D2U): Fields D1U, D2U and LP (described below) are used in implementing a loop, e.g. a FOR or WHILE loop. Often instructions from inside a loop require values from outside the loop, but instructions

from outside the loop execute and transmit their values only once (i.e. an instruction is fired only once). Hence the instruction inside the loop will receive that value only once, and it will fire only once. To overcome this problem the reuse bit is used. Setting this bit at compile time allows LU1 to realize that the received value has to be reused, and will not change the D1O/D2O bit of the firing instruction whose D1U/D2U bit/s is/are set. Thus that instruction can fire again when all its other operands/clauses are available.

D1U and D2U are one-bit flags, which are used to determine if operand1 and operand2 need to be reused. These bits are set only at compile time.

Loop (LP): Loops are a terrible construct to manage in Data Flow Machines, but they also are the most commonly used constructs in programming (the 90/10 rule). Loops usually start by checking some value before the start of the loop (e.g. while x < 5, where the value of x is set before the loop begins). This is particularly true for "while" and "for" loops. The next time around, the value of x is obtained from within the loop, which in the case of the example presented, would be an instruction such as "x = x + 1". Thus, the first time, the value of 'x' is obtained from outside the loop and every subsequent time, it obtained from inside the loop. Hence we need a primitive that is capable of obtaining the same variable from two different sources.

The second problem is that data flow machines are runaway machines; firing one instruction subsequently fires many instructions in different parts of the code. In particular when dataflow computers execute loop constructs, due to their inherent runaway nature it is highly probable that the machine may be executing different iterations of the same loop; i.e. part of the instructions in the loop are executing

iteration n, while other parts may be in iterations n+1, n+2, ..., n+m. This would not be a problem if there were no dependencies between consecutive iterations, but would be a disaster if there were any. Some way to control the execution of the loop is needed under these circumstances.

To accomplish these controls, a special 2-bit flag, called LOOP(LP) is used to implement 'loop constructs'. The 2-bit flag can only be set at compile time. The values that the LOOP (LP) flag can take are 0-3. The value 0 is used for instructions that are not used to implement a loop, i.e. only instructions that enclose the loop have their LP values greater than zero. All other instructions inside and outside the loop are set to zero. The other three values are used for constructing loops. Note that LP values 1-3 are not used to distinguish between different types of loop constructs, but are used to control how a loop executes.

#### When LP = 1.

A value of LP equal to 1 is used to initiate a loop (beginning of a loop). The instruction which has its LP flag set to 1, is a special instruction called SP (SPecial), which is not actually an instruction at all (it is never sent for execution). In the example above involving 'x', there would be a SP instruction whose LP value would be 1, its D1A field would contain the address from where the value of 'x' is obtained the first time (outside the loop) and D2A would contain the address from where the value of 'x' is obtained other times (inside the loop). The instruction fires whenever it receives the value of 'x', from either the address D1A or D2A.

#### When LP=2.

The SP instruction is always followed by a conditional instruction. This instruction

40

checks the loop conditional. In the example presented above, the conditional

instruction would check for x < 5. The result of this conditional statement is sent out

as a clause to all the instructions inside the loop. This instruction has its LP flag set to

2, because if it is treated as a regular instruction (LP = 0), upon execution its CAN bit

will be reset instantly along with its D10 and D20 flags, and this instruction will not

execute again when it receives its operands for the next iteration (since CAN is reset).

For the loop to iterate, all the instructions inside the loop need the clause coming from

this loop conditional instruction. To avoid such a situation, the LP flag of the loop

conditional instruction is set to 2, which instructs LU1 to leave the CAN bit intact

after it has sent the conditional instruction for execution.

When LP=3.

An instruction with a value of LP equal to 3 is used along with the loop instruction SP

to avoid situations where the runaway effect will cause a problem; i.e. a control of

iterations has to be maintained due to data dependencies between consecutive