# **Copyright Warning & Restrictions**

The copyright law of the United States (Title 17, United States Code) governs the making of photocopies or other reproductions of copyrighted material.

Under certain conditions specified in the law, libraries and archives are authorized to furnish a photocopy or other reproduction. One of these specified conditions is that the photocopy or reproduction is not to be "used for any purpose other than private study, scholarship, or research." If a, user makes a request for, or later uses, a photocopy or reproduction for purposes in excess of "fair use" that user may be liable for copyright infringement,

This institution reserves the right to refuse to accept a copying order if, in its judgment, fulfillment of the order would involve violation of copyright law.

Please Note: The author retains the copyright while the New Jersey Institute of Technology reserves the right to distribute this thesis or dissertation

Printing note: If you do not wish to print this page, then select "Pages from: first page # to: last page #" on the print dialog screen

The Van Houten library has removed some of the personal information and all signatures from the approval page and biographical sketches of theses and dissertations in order to protect the identity of NJIT graduates and faculty.

#### ABSTRACT

# INTEGRATED PRODUCT AND PROCESS DEVELOPMENT METHODOLOGIES FOR ENVIRONMENTALLY CONSCIOUS ELECTRONIC PRODUCTS

# by Pingtao Yan

This research focuses on integrated product and process development (IPPD) methodologies for environmentally conscious electronic products. After a review of current research issues in the field of product and process development, a generic framework for IPPD is proposed which describes most of the concerned issues formally as constrained optimization problems. These problems may include such optimization objectives as cost, benefit, and environmental impact. Based on this framework, an IPPD methodology is proposed as a systems approach to competitive and environmentally conscious product and process development. A case study on personal computer development is performed illustrating how to apply the methodology meaningfully and efficiently. Eco-compass concept is then integrated into the methodology to evaluate environmental impact, and a case study on business telephone development is performed. To automate the design of products and processes, a solution methodology for IPPD based on logical representation of process relations is proposed with two illustrating product development examples. Finally, a timed IPPD methodology is introduced with increased modeling capability and decision accuracy. It considers the execution duration of processes and their time-varying characteristics. The timed methodology is applied to the life cycle development of flexible manufacturing systems (FMSs) and provides a new way to develop cost-effective, high-quality, and environmentally conscious FMSs.

# INTEGRATED PRODUCT AND PROCESS DEVELOPMENT METHODOLOGIES FOR ENVIRONMENTALLY CONSCIOUS ELECTRONIC PRODUCTS

by Pingtao Yan

A Dissertation Submitted to the Faculty of New Jersey Institute of Technology in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy in Electrical Engineering

Department of Electrical and Computer Engineering

January 2000

Copyright © 2000 by Pingtao Yan

ALL RIGHTS RESERVED

and a start of the second start of the second

# **APPROVAL PAGE**

# INTEGRATED PRODUCT AND PROCESS DEVELOPMENT METHODOLOGIES FOR ENVIRONMENTALLY CONSCIOUS ELECTRONIC PRODUCTS

# Pingtao Yan

| Dr. MengChu Zhou, Dissertation Advisor                           | Date |

|------------------------------------------------------------------|------|

| Associate Professor of Electrical and Computer Engineering, NJIT |      |

| issociate Professor of Electrical and Computer Engineering, 1911 |      |

|                                                                  |      |

|                                                                  |      |

|                                                                  |      |

|                                                                  |      |

|                                                                  |      |

| Dr. Donald H. Sebastian, Dissertation Co-Advisor                 | Date |

| Professor of Industrial and Manufacturing Engineering, NJIT      |      |

|                                                                  |      |

|                                                                  |      |

|                                                                  |      |

|                                                                  |      |

|                                                                  |      |

|                                                                  |      |

| Dr. John D. Carpinelli, Committee Member                         | Date |

| Associate Professor of Electrical and Computer Engineering, and  |      |

| Computer and Information Science, NJIT                           |      |

| compater and micrimation berefied, 1,511                         |      |

|                                                                  |      |

|                                                                  |      |

|                                                                  |      |

|                                                                  |      |

|                                                                  |      |

| Dr. Reggie J. Caudill, Committee Member                          | Date |

| Professor of Industrial and Manufacturing Engineering, NJIT      |      |

|                                                                  |      |

|                                                                  |      |

|                                                                  |      |

|                                                                  |      |

|                                                                  |      |

| Dr. Edwin Hou, Committee Member                                  | Data |

|                                                                  | Date |

| Associate Professor of Electrical and Computer Engineering, NJIT |      |

|                                                                  |      |

|                                                                  |      |

|                                                                  |      |

|                                                                  |      |

|                                                                  |      |

Dr. Venkatesh Kurapati, Committee Member Senior Technical Staff Member, AT&T, Middletown, NJ

Date

# **BIOGRAPHICAL SKETCH**

Author: Pingtao Yan

**Degree:** Doctor of Philosophy in Electrical Engineering

Date: January 2000

# **Undergraduate and Graduate Education:**

- Doctor of Philosophy in Electrical Engineering, New Jersey Institute of Technology, Newark, NJ, 2000

- Master of Engineering in Electrical Engineering, Xi'an Jiaotong University, Xi'an, P. R. China, 1994

- Bachelor of Engineering in Electrical Engineering, Xi'an Jiaotong University, Xi'an, P. R. China, 1992

Major: Electrical Engineering

## **Presentations and Publications:**

- P. Yan, M. Zhou, and D. Sebastian, "A generic framework for integrated product and process development," Int. J. of Environmentally Conscious Design and Manufacturing, vol. 7, no. 3, pp. 47-57, 1998.

- P. Yan, M. Zhou, and D. Sebastian, "An integrated product and process development methodology: Concept formulation," *Robotics and Computer-Integrated Manufacturing*, vol. 15, pp. 201-210, 1999.

- P. Yan, M. Zhou, B. Hu, and Z. Feng, "Modeling and control of workstation level information flow in FMS using modified Petri nets," J. of Intelligent Manufacturing, vol. 10, no. 6, 1999.

- P. Yan, M. Zhou, D. Sebastian, and R. Caudill, "Integrating eco-compass concept into integrated product and process development," submitted to *Int. J. of Environmentally Conscious Design and Manufacturing* for review, 1999.

# BIOGRAPHICAL SKETCH (Continued)

## **Presentations and Publications:**

- P. Yan and M. Zhou, "A solution methodology for integrated product and process development based on logical representation of process relations," submitted to *IEEE Trans. on Sys., Man, and Cyber.* for review, 1999.

- P. T. Yan, Q. Z. Ye, S. H. Ong, and S. C. Tan, "A flexible snake model," in Proc. Int. Conf. on Control, Automation, Robotics and Vision, Singapore, Dec. 1996, pp. 2321-2325.

- P. T. Yan, Q. Z. Ye, S. H. Ong, and S. C. Tan, "Initializing snakes: A stepwise expanding flexible balloon," in *Proc. Scandinavian Conf. on Image Analysis*, Lappeenranta, Finland, June 1997, pp. 667-674.

- P. Yan, M. Zhou, B. Hu, and Z. Feng, "Modeling and control of the FMS workstation level information flow by a modified Petri net," in *Proc. IEEE Int. Conf. on Emerging Technologies and Factory Automation*, Los Angeles, CA, Sept. 1997, pp. 321-326.

- P. Yan, M. Zhou, and D. Sebastian, "Formulation of a generic framework for integrated product and process development," in *Proc. IEEE Int. Conf. on Sys., Man, and Cyber.*, San Diego, CA, Oct. 1998, pp. 2609-2614.

- P. Yan, M. Zhou, and D. Sebastian, "An integrated product and process development methodology: A case study," in CD-ROM Rensselaer's Int. Conf. on Agile, Intelligent, and Computer-Integrated Manufacturing, Troy, NY, Oct. 1998, Paper No. 46.

- P. Yan, M. Zhou, and D. Sebastian, "Multi-lifecycle product and process development: Selection of optimal production, usage, and recovery processes," in *Proc. IEEE Int. Symp. on Electronics and the Environment*, Danvers, MA, May 1999, pp. 274-279.

- P. Yan, M. Zhou, and R. Caudill, "A life cycle engineering approach to FMS development," submitted to *IEEE Int. Conf. on Robotics and Automation*, Sept. 1999.

- P. Yan and M. Zhou, "A solution methodology for IPPD based on logical representation of process relations," submitted to *IEEE Int. Symp. on Electronics and the Environment*, Oct. 1999.

To my beloved family

#### ACKNOWLEDGMENT

I would like to express my sincere gratitude to my advisor, Professor MengChu Zhou, and co-advisor, Professor Donald H. Sebastian, for their guidance, friendship, and moral support throughout this research.

Special thanks to Professors John D. Carpinelli, Reggie J. Caudill, Edwin Hou, and Dr. Venkatesh Kurapati for serving as members of the committee.

I am grateful to the support of the New Jersey Commission on Science and Technology and such industrial firms as Lucent Technologies, AT&T, Panasonic, and All Technics Products Inc. through the Multi-lifecycle Engineering Research Center (MERC) at NJIT.

Many of my fellow graduate students in the Discrete Event Systems Laboratory and the Multi-lifecycle Engineering Research Center are deserving of recognition for their support. I also wish to thank Lisa Fitton and Elizabeth McDonnell for their assistance over the past three years.

# **TABLE OF CONTENTS**

| C | hapt | er                                          | Page |

|---|------|---------------------------------------------|------|

| 1 | IN   | TRODUCTION                                  | 1    |

|   | 1.1  | Background                                  | 1    |

|   | 1.2  | Motivation                                  | 5    |

|   | 1.3  | Objective                                   | 8    |

|   | 1.4  | Organization                                | 9    |

| 2 | LIJ  | TERATURE REVIEW                             | 10   |

|   | 2.1  | Product Profitability Issues                | 10   |

|   | 2.2  | Environmental Consciousness Issues          | 21   |

|   | 2.3  | Summary                                     | 26   |

| 3 | A (  | GENERIC FRAMEWORK FOR IPPD                  | 27   |

|   | 3.1  | Ideas                                       | 28   |

|   | 3.2  | A Generic Framework for IPPD                | 29   |

|   | 3.3  | An Example                                  | 31   |

|   | 3.4  | Summary                                     | 35   |

| 4 | AN   | IPPD METHODOLOGY: CONCEPT FORMULATION       | 36   |

|   | 4.1  | Basic Concepts                              | 36   |

|   | 4.2  | An Application Procedure                    | 46   |

|   | 4.3  | Summary                                     | 47   |

| 5 | A (  | CASE STUDY ON PERSONAL COMPUTER DEVELOPMENT | 49   |

|   | 5.1  | Personal Computer Development               | 49   |

|   | 5.2  | Search Results and Discussions              | 61   |

|   | 5.3  | Summary                                     | 64   |

# TABLE OF CONTENTS (Continued)

| Chapter Pa |      | Page                                                                             |     |

|------------|------|----------------------------------------------------------------------------------|-----|

| 6          | INT  | FEGRATING ECO-COMPASS CONCEPT INTO IPPD                                          | 66  |

|            | 6.1  | Eco-compass                                                                      | 66  |

|            | 6.2  | Integration of Eco-compass Concept into IPPD                                     | 68  |

|            | 6.3  | A Case Study on Business Telephone Development                                   | 71  |

|            | 6.4  | Search Results and Discussions                                                   | 77  |

|            | 6.5  | Summary                                                                          | 79  |

| 7          |      | SOLUTION METHODOLOGY FOR IPPD BASED ON LOGICAL PRESENTATION OF PROCESS RELATIONS | 80  |

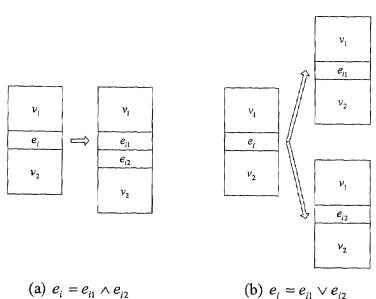

|            | 7.1  | Logical Representation of Process Relations                                      | 81  |

|            | 7.2  | Automatic Life Locus Setup                                                       | 84  |

|            | 7.3  | Algorithm Implementation                                                         | 89  |

|            | 7.4  | Application Examples                                                             | 91  |

|            | 7.5  | Summary                                                                          | 99  |

| 8          | ΑI   | LIFE CYCLE ENGINEERING APPROACH TO FMS DEVELOPMENT                               | 101 |

|            | 8.1  | A Timed IPPD Methodology                                                         | 102 |

|            | 8.2  | A Case Study on FMS Development                                                  | 108 |

|            | 8.3  | Summary                                                                          | 116 |

| 9          | CO   | NCLUSIONS AND FUTURE RESEARCH DIRECTIONS                                         | 118 |

|            | 9.1  | Conclusions                                                                      | 118 |

|            | 9.2  | Future Research Directions                                                       | 122 |

| R          | EFEF | RENCES                                                                           | 126 |

# LIST OF TABLES

| Tał | ble F                                                                                   | Page |

|-----|-----------------------------------------------------------------------------------------|------|

| 3.1 | Possible processes in a cup's life cycle.                                               | 33   |

| 5.1 | Possible processes in a PC's ELCS.                                                      | 52   |

| 5.2 | Meaning of process indices in a PC's different life phases                              | 56   |

| 5.3 | Indices of key processes in a PC's life cycle.                                          | 58   |

| 5.4 | Optimal life loci for a PC.                                                             | 62   |

| 5.5 | Average search time corresponding to increasing life locus tree size                    | 64   |

| 6.1 | Indices for processes in a telephone's life cycle.                                      | 75   |

| 6.2 | Optimal life loci for a telephone.                                                      | 78   |

| 7.1 | Possible processes in a cup's life cycle.                                               | 92   |

| 7.2 | Knowledge base <i>KB</i> for a cup.                                                     | 92   |

| 7.3 | Standard knowledge base <i>KB</i> for a cup                                             | 93   |

| 7.4 | Feasible life loci for a cup.                                                           | 93   |

| 7.5 | Key processes in a PC's life cycle.                                                     | 94   |

| 7.6 | Knowledge base <i>KB</i> for a PC.                                                      | 95   |

| 7.7 | Standard knowledge base KB for a PC.                                                    | 97   |

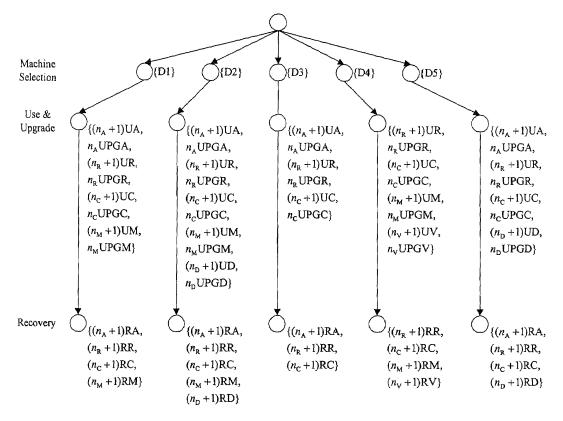

| 8.1 | Five FMS designs.                                                                       | 111  |

| 8.2 | Possible processes in an FMS's life cycle and their types and index (function) vectors. | 112  |

| 8.3 | Relations among $n_x$ , $t_x$ , $\rho_{x1}$ , $\rho_{x2}$ , and $\rho_{x3}$             | 115  |

| 8.4 | Optimal life loci for an FMS.                                                           | 115  |

# LIST OF FIGURES

| Fig | ure I                                                                 | Page |

|-----|-----------------------------------------------------------------------|------|

| 3.1 | Representation of product A's life cycle.                             | 29   |

| 3.2 | Product status representation of a life phase.                        | 29   |

| 3.3 | Process set representation of a life phase.                           | 30   |

| 3.4 | A simple example: A cup's life cycle.                                 | 32   |

| 3.5 | A directed graph showing all the possible cases of a cup's life cycle | 34   |

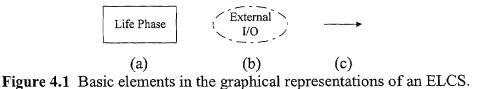

| 4.1 | Basic elements in the graphical representations of an ELCS            | 37   |

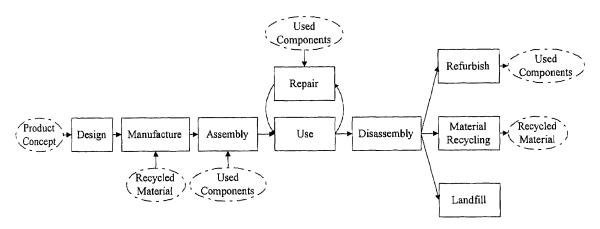

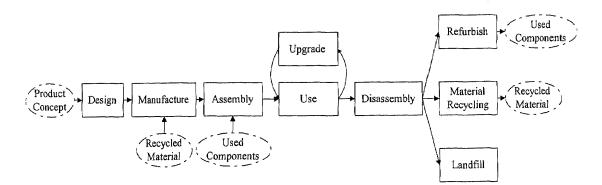

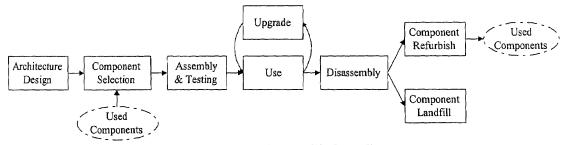

| 4.2 | A typical ELCS example.                                               | 37   |

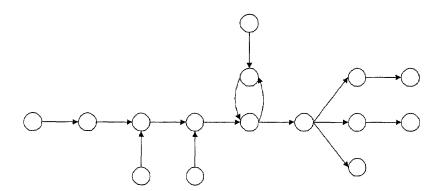

| 4.3 | The ELCS graph corresponding to the ELCS in Figure 4.2.               | 38   |

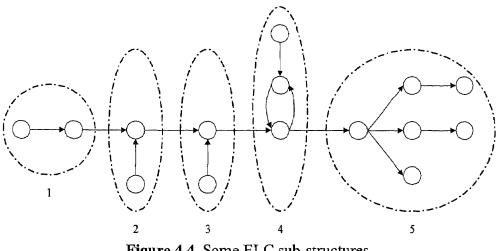

| 4.4 | Some ELC sub-structures.                                              | 39   |

| 4.5 | A simplified ELCS of the complex ELCS in Figure 4.2.                  | 41   |

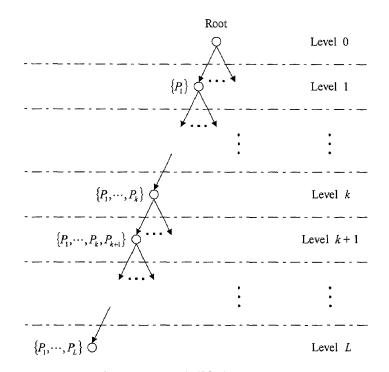

| 4.6 | Product A's ELCS.                                                     | 44   |

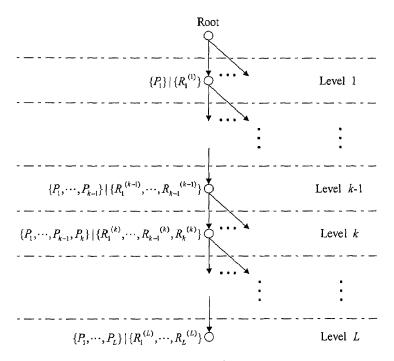

| 4.7 | A life locus tree.                                                    | 45   |

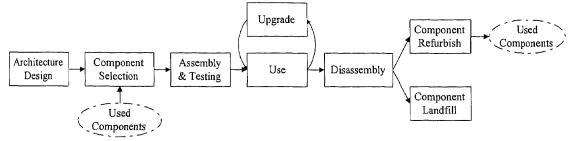

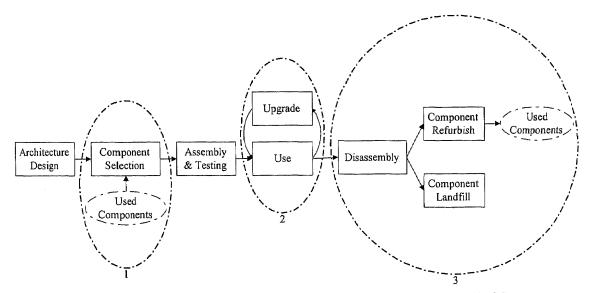

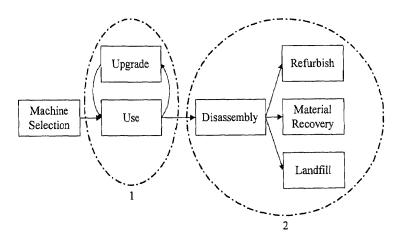

| 5.1 | An ELCS for PC.                                                       | 50   |

| 5.2 | Three complex ELC sub-structures in the PC's ELCS.                    | 50   |

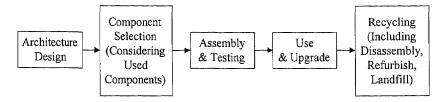

| 5.3 | A simplified ELCS for PC.                                             | 51   |

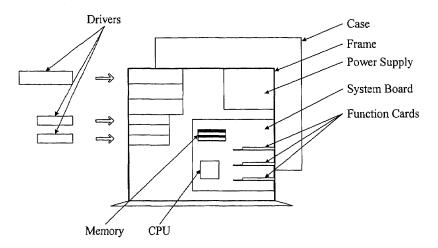

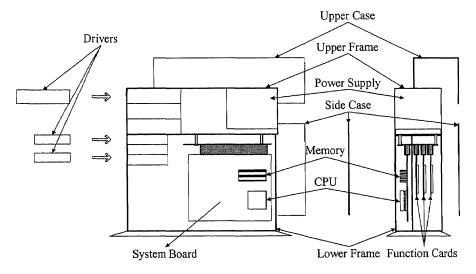

| 5.4 | Two PC architecture designs.                                          | 54   |

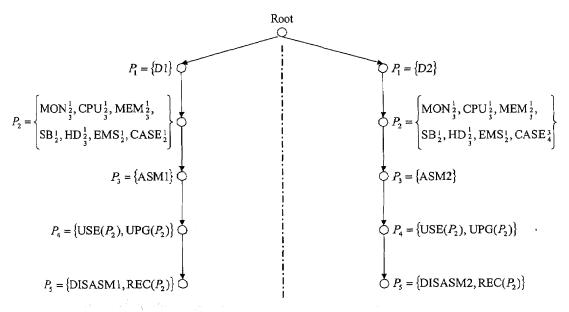

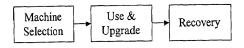

| 5.5 | Main structure of PC's life locus tree.                               | 60   |

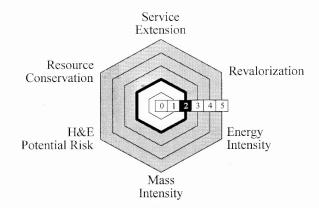

| 6.1 | Diagram of eco-compass.                                               | 68   |

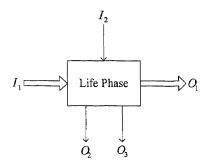

| 6.2 | Generic model of a life phase.                                        | 69   |

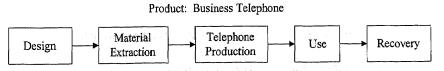

| 6.3 | An ELCS for business telephone.                                       | 71   |

| 6.4 | Four designs of business telephones.                                  | 72   |

# LIST OF FIGURES (Continued)

| Fig | ure                                                    | Page |

|-----|--------------------------------------------------------|------|

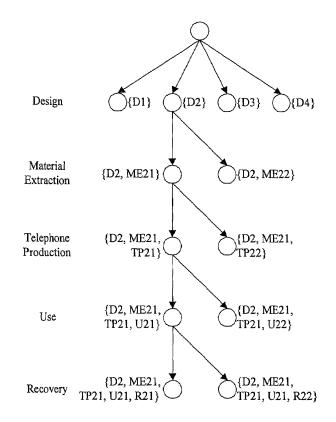

| 6.5 | A life locus tree for telephone.                       | 76   |

| 7.1 | An ELCS example.                                       | 81   |

| 7.2 | Knowledge base KB                                      | 83   |

| 7.3 | Application of associative and distributive laws.      | 86   |

| 7.4 | An ELCS for PC.                                        | 93   |

| 8.1 | Product A's expected life cycle structure.             | 105  |

| 8.2 | A timed life locus tree.                               | 107  |

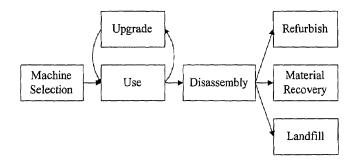

| 8.3 | An ELCS for FMS.                                       | 108  |

| 8.4 | Two complex ELC sub-structures in the FMS's ELCS.      | 109  |

| 8.5 | A simple ELCS for FMS.                                 | 109  |

| 8.6 | A timed life locus tree for FMS.                       | 114  |

| 9.1 | Input a knowledge base <i>KB</i>                       | 123  |

| 9.2 | Standardize KB and perform automatic life locus setup. | 124  |

| 9.3 | Depth-first optimal search.                            | 124  |

#### **CHAPTER 1**

#### INTRODUCTION

## 1.1 Background

A product is something sold by an enterprise to its customers. The economic success of manufacturing firms largely depends on their ability to identify the needs of customers and to create quickly products that meet these needs and can be produced at low cost. Product development is the set of activities beginning with the perception of a market opportunity and ending in the production, sale, and delivery of a product [Ulrich and Eppinger, 1995].

New product development has always been exciting, challenging, and most of all, very complex [Hainer, Kingsbury, and Gleicher, 1967; Buggie, 1981]. Throughout the history of industrial and social development, the introduction of new products has always been a close reflection of the developments in science and technology of the time. New scientific and technological developments and discoveries are transformed into new product features and better product performances to increase customer satisfaction and ultimately to bring more profit to an enterprise.

During the last two decades, science and technology are developing at an accelerating speed and widening broadness. New techniques, new materials, and new processing methods are coming up even more widely and frequently than ever. This is good and also bad news for product developers. On the one hand, these new techniques and new materials bring about many new selections and opportunities that product developers could use in their new product development processes to produce better

1

products. On the other hand, more options inevitably mean more complexity in the related decision making processes. Consequently, product development is becoming more complex and therefore more difficult along with scientific and technological development.

In addition to scientific and technological development, social and economic evolution also brings about more complexity and difficulty to a product development process. Customers are becoming much more demanding. Market competition is more intense than ever. New requirements for products arise from many new aspects: the society, government, environment, and so on. Companies under great pressure are making every effort to produce better products faster than their competitors, otherwise, their profit would not be attainable.

Among the social and economic issues concerning a product, environmental concerns are receiving more and more attention in the recent years. The demands to create eco-efficient products without compromising their cost, quality, and schedule constraints are increasing. An eco-efficient product may be defined as a product that both minimizes adverse environmental impact and maximizes conservation of valuable resources throughout its life cycle. Environmental impact includes energy consumption, waste emissions, health and safety impact, and so on.

Several factors have contributed to the growing interest of manufacturing firms in eco-efficiency [Fiksel, 1996]:

(1) Market awareness: Government, industrial, and retail customers are all increasingly conscious of the environmental performance of suppliers and products;

- (2) Differentiation: Eco-efficient designs are generally superior in terms of elegance, energy conservation, and cost of ownership, and may sway a purchase decision if price and performance are comparable;

- (3) Cost savings: Eco-efficient products and processes can make a significant contribution to product line profitability through savings in production, distribution, and other life cycle costs;

- (4) Eco-labeling programs: A number of product eco-labeling initiatives have arisen both in the U.S. and abroad, and the European Union is moving towards an ecolabeling standard;

- (5) Regulatory pressures: Regulations governing the environmental impact of products and production processes are becoming more stringent worldwide, especially with regards to waste disposal and recycling. Japan and several countries in Europe are enforcing product take-back laws governing automobile and electronic products; and

- (6) International standards: The International Organization for Standardization (ISO) has established Technical Committee TC207 to develop a global consensus on environmental management standards.

Perhaps the most important factor in changing industry attitudes is the realization that paying attention to environmental responsibility can actually increase profitability. Reducing pollution at the source and designing products and processes in ways that enhance environmental quality generally result in higher productivity and reduced operating costs, and may also increase market share. In response to growing levels of environmental concern, many companies saw the social and economic value of shifting their attention from cleaning up waste, to cleaning production processes, and finally to eco-design of products.

In Europe and the U.S., where environmental degradation has been so marked and community awareness so advanced, companies have recognized that their future viability depends on their competitive response to these changing circumstances. In global terms, it is the extent of the redesign of manufactured products to improve their environmental performance that best illustrates the impact of global concern for sustainable development.

There has been enough activity in the redesign of manufactured goods around the world to discern some clear stages of development. Initial eco-re-designed products simply reflected market pressures and concentrated on those elements that were the easiest to change. Concern with materials and solid waste, energy consumption, and the elimination of obvious toxic chemicals combined with significant attention to packaging defined the "first wave" of such products. Their environmental contribution was minimal, but they served to heighten and sharpen market demand.

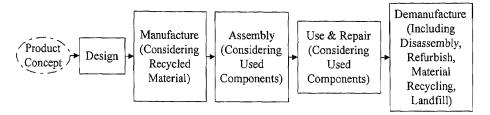

Later eco-designed products began to reflect increased attention to some full life cycle appreciation of environmental impact, with greater focus on recycled materials, design for disassembly, recyclability, and other strategies addressing problems resulting from production, use, and disposal.

Among industrial products, consumer electronics deserve substantial attention because of their tremendous environmental impact. A typical desktop computer contains many reusable and/or hazardous materials including lead, silver, gold, cadmium, plastic, and glass. When a personal computer is disposed in a landfill or incinerator, not only is the value of those materials lost, but the environmental costs of disposing of this equipment can be high as well. It has been estimated that 70% of the toxins in landfills are accounted for by 1% of the landfills' contents, principally consumer electronics.

The scope of this problem is enormous. More than 17 million computer displays were sold in 1994. It has been estimated that by the end of 1995, over 300 million televisions or computer monitors were in use. The Electronics Industry Association estimates that between 1991 and 1993, sales of televisions increased by more than 18%, sales of telephones increased by 20%, and sales of personal computers rose by almost 22%. Over 2 million pounds of plastic is used each year to manufacture these consumer electronics. However, less than 3% of that plastic is recycled.

New product development has never been easy, and it is becoming more difficult than ever before. A great amount of research effort is being pursued worldwide, trying from different perspectives to solve this problem.

## 1.2 Motivation

As shown in Section 1.1, product developers have a whole host of goals to optimize as they design their products: high performance, high reliability, low cost, attractive appearance, safety, and carefully chosen environmental impact.

The following environmental interactions are among those that the developers need to consider as they develop their products and processes [Socolow *et al.*, 1994; Graedel and Allenby, 1995]:

- Choosing raw materials: In the long term, society cannot be sustainable if it uses up important resources that are in short supply, e.g., copper and petroleum. Industrial product and process designs using any of the potentially limited materials should, if possible, be avoided;

- (2) Minimizing and specifying air emissions: Most industrial processes involve the emission of materials to the air. The most common emittants are solvents or cleaning agents, which are usually organic materials, often halogenated. Product developers should attempt to avoid processes that involve the emission of CFCs, halons,  $CH_4$ ,  $N_2O$ ,  $NO_x$ , or volatile organic carbon (VOC). Alternatively, these materials may be captured prior to their emission;

- (3) Minimizing and specifying liquid waste: Industrial operations use water for transport, cooling, and processing. In addition, organic solvents and other spent liquids constitute a portion of the liquid waste that industry must process or discard. The minimization of liquid waste, and the design of it to make it less costly to recycle than to discard, should be a central element in process design;

- (4) Minimizing and specifying solid waste: The disposal of solid waste has become one of the major problems of developed societies. In Europe, landfill capacity is so exhausted that only several years' dumping at the present rate is possible. In the U.S., about two-thirds of all landfills have closed within the past decade. Solid waste disposal has thus become increasingly expensive. Industry, which generates a substantial fraction of all solid waste, is increasingly under pressure to minimize its rate of solid waste production and disposal;

- (5) Designing for energy efficiency: Manufacturing activities consume 25-30% of all energy use in the U.S. and similar fractions elsewhere. Much of this consumption can be minimized by attention to process design and by the reuse of energy expended by manufacturing processes. Another aspect of design for energy efficiency is the minimization of energy consumption by products once they are in service; and

- (6) Recycling after use: The materials cycle in industrial ecology is effective only if materials are efficiently returned to the system for reuse. This process is greatly aided by product designs that aid disassembly, avoid the use of a multiplicity of materials or of irreversible materials bonding techniques, identify the materials used in the product, and avoid or minimize the inclusion of materials difficult or dangerous to recycle.

As an example, let us consider the development of a cup. Traditionally, requirements for a cup come from the user. The user requires that a cup be aesthetically pleasant, microwavable, able to endure temperature variations without breaking, etc. Recently, however, more and more requirements arise from people other than the user. For example, the manufacturer requires that a cup be easy to produce, production cost be as low as possible, etc. After a cup is used and disposed of, the recycling industry requires that recycling be easy, recycling cost be low, and hazardous emissions be minimum, etc. These different requirements from different life phases of a product merge into the need for an overall consideration of a product's entire life cycle and ultimately an integrated product and process development environment.

A great amount of research effort has been pursued worldwide to achieve these goals, among which are two critically important areas, namely, integrated product and process development and design for environment. Integrated product and process development (IPPD), also called life cycle engineering or concurrent engineering, is a systematic approach to the integrated, concurrent design of products and their related processes. It is intended to cause the developers, from the outset, to consider all the elements of a product's life cycle from conception through disposal, including quality, cost, schedule, and user requirements. Design for environment (DFE) is a systematic consideration of design performance with respect to environmental, health, and safety objectives over the full product and process life cycle. It takes place early in a product's design phase to ensure that the environmental consequences of a product's life cycle are understood before manufacturing decisions are committed.

Integrated product and process development methodologies for environmentally conscious electronic products are the focus of this research.

#### 1.3 Objective

The goal of this research is to develop systematic and formal approaches to competitive and environmentally conscious product and process development. Specific objectives include:

- Provide formal and mathematical models for generally considered product and process development problems;

- (2) Provide systematic, formal, and efficient methods to solve these problems;

8

- (3) Integrate fully environmental considerations into product and process development; and

- (4) Perform case studies on electronic product development using the proposed concepts and methods.

#### 1.4 Organization

This dissertation is organized as follows. Chapter 2 reviews the current research issues in the field of product and process development. Chapter 3 proposes a generic framework for IPPD, by which most of the concerned issues are formally described as constrained optimization problems. Based on this generic framework, an IPPD methodology is introduced in Chapter 4. Important concepts of the methodology are defined and an application procedure is provided illustrating how to apply the methodology systematically and efficiently to real product and process development. Chapter 5 provides a case study on personal computer development using the proposed methodology.

In order to enrich the methodology with respect to concrete evaluation of environmental impact, Chapter 6 integrates eco-compass concept into the methodology and provides a case study on business telephone development. Chapter 7 proposes a solution methodology for IPPD based on logical representation of process relations to automate the design of products and processes. Chapter 8 introduces time variable into the IPPD methodology to increase its modeling capability and decision accuracy, and applies it to the life cycle development of flexible manufacturing systems. Finally, Chapter 9 gives the conclusions and some future research directions.

#### CHAPTER 2

#### LITERATURE REVIEW

As mentioned in Chapter 1, new product development is becoming more complex and challenging along with scientific/technological development and social/economic evolution. Significant research effort is being carried out in industries and academia addressing various problems in this area. The current research issues generally fall into two categories: product profitability issues and environmental consciousness issues. This chapter reviews the major issues in these two categories.

#### 2.1 **Product Profitability Issues**

From the perspective of the investors in a for-profit enterprise, successful product development results in products that can be produced and sold profitably. Product profitability has always been the most important goal driving product development. Since profitability is usually difficult to assess directly, four more specific dimensions, all of which ultimately relate to profit, are commonly used to assess the performance of a product development effort. These four dimensions are: product quality, product cost, development time, and development cost [Ulrich and Eppinger, 1995]. High performance along these four dimensions should ultimately lead to economic success.

Research issues in this category focus on improving the profitability of a product through better development processes. These issues are typically represented by the concept of concurrent engineering, or similarly known as simultaneous engineering, life cycle engineering, or integrated product and process development (IPPD) [Ishii, 1990; Allen, 1990; Syan and Menon, 1994]. Concurrent engineering evolved as an alternative to the conventional sequential engineering method of product development. In a sequential engineering approach, each development stage starts only when the previous one is completed, which brings about major shortcomings that reduce the desired profitability [Hunt, 1993; Syan and Menon, 1994].

In its original definition, concurrent engineering is a systematic approach to the integrated, concurrent design of products and their related processes, including manufacture and support [Syan and Menon, 1994]. This approach is intended to cause the developers, from the outset, to consider all the elements of the product life cycle from conception through disposal, including quality, cost, schedule, and user requirements [Syan and Menon, 1994].

[Kalyan-Seshu and Bras, 1998] focuses on enabling the quantification and enhancement of product assemblability, serviceability, remanufacturability, recyclability, demanufacturability, and life cycle impact during product design. [Stuart, 1998] discusses materials selection for life cycle design. Research presented in [Chen and Liu, 1999] aims to provide on-line cost evaluation and advisory to help product designers avoid costineffective design. [Hatch and Badinelli, 1999] describes a methodology for making the decisions associated with the concurrent engineering of a product and its downstream field support. [Huang and Mak, 1998] proposes a dynamic transformation approach from a sequential engineering environment to a concurrent engineering environment by combining the focused application of "design for X" with the extensive use of business process re-engineering. [Pham and Dimov, 1998] presents a new approach to concurrent engineering that focuses on simultaneous product design and process planning. The proposed approach provides a natural way for conveying manufacturing information to the designers and applies a wide range of artificial intelligence techniques for knowledge acquisition and deductive reasoning. [Culbreth, Miller, and O'Grady, 1996] presents an approach to concurrent engineering systems for flexible automation that uses constraint networks to represent the constraining influences of the automation process. [Soyucayli and Otto, 1998] describes a means of exploring design and manufactured quality as a systems level concurrent engineering support tool.

[Yassine, Chelst, and Falkenburg, 1999] uses risk and decision analysis methodologies to determine the best use of sequential, partial overlapping, and concurrent engineering execution strategies. [Eldin, 1997] assesses the use of concurrent engineering as a schedule reduction tool using four case studies to evaluate the potential for concurrent engineering to reduce project delivery times without increasing project overall cost. The study carried out in [Poolton and Barclay, 1996] shows that there are many benefits to introducing concurrent engineering and that firms differ with respect to their needs for the concurrent engineering approach.

Factors of successful concurrent engineering implementations are also discussed. A theoretical and interdisciplinary model that considers the critical human and organizational variables for success in concurrent engineering is presented in [Duffy and Salvendy, 1999]. This model aims to determine the impact of organizational ergonomics on work effectiveness in concurrent engineering. [Litsikas, 1997] discusses the importance of management support and communication in concurrent engineering. [Tom, 1997] points out that true concurrent engineering cannot happen until the entire supply chain is fully, electronically integrated. Logistics involvement in the early phases of product design and development in a concurrent engineering environment is also found to be important [Dowlatshahi, 1996].

Concurrent engineering has wide applications in many fields [Shina, 1993]. Major U.S. manufacturers such as Ford Motor Co. and Xerox Co. have successfully implemented concurrent engineering to improve time-to-market and product quality [Blau, 1994]. Dutch company Philips Electronics credits concurrent engineering with helping it to develop a color LCD in record time while at the same time dramatically reducing production costs. The concurrent engineering approach has also helped to cut development time at German machine tool builder Hermie [Blau, 1994]. A number of electronic design automation vendors have introduced design tools that cater for more concurrent engineering by either focusing on the package itself or by offering a complete suite of tools that allows each stage of the design to communicate easily using the same language [Mannion, 1998]. Caterpillar Inc.'s Track-Type Tractor division carried out a company-wide concurrent engineering initiative and yielded increased flexibility and shortened delivery times for the production of bogies [Bates, 1997]. [Meller and Gau, 1996] reports a trend toward concurrent engineering approaches to layout and production system design. [de Graaf and Kornelius, 1996] describes an attempt to introduce interorganizational concurrent practices in a major printed circuit board manufacturing plant.

Providing concurrent engineering tools is another focus of research and development. A total of 17 European companies, including Daimler-Benz, have initiated a 6-year program to develop standard computer-aided tools and databases needed for concurrent engineering teams [Blau, 1994]. COMPASS (Computer Oriented Materials, Processes, and Apparatus Selection System) is a tool that helps design engineers identify potential manufacturing problems in the early stages of product development [Chan, King, and Wright, 1998]. It has a basic framework to provide essential information regarding production cost, cycle time, and product quality for all of the candidate processes. SPAW [Yetukuri, Yetukuri, and Fischer, 1996] is a design tool for planning a manufacturing process in a concurrent engineering environment, which is also designed to be integrated directly into a design-oriented concurrent engineering environment.

# 2.1.1 Special Issues in Concurrent Engineering

Special issues in concurrent engineering include quality function deployment, design for manufacture, design for assembly, and rapid prototyping [Syan and Menon, 1994].

# (a) Quality Function Deployment (QFD)

QFD is a structured planning method of concurrent engineering that is used to influence the incorporation of product attributes that are in accord with customer expectations. This is done by mapping the customer requirements into specific design features and eventually into manufacturing processes. QFD is used as a systematic method to both identify and prioritize customer requirements, and to translate these requirements into product and process specifications [Syan and Menon, 1994].

A review of QFD and related deployment techniques is provided in [Prasad, 1998]. QFD is used by some firms to convert customer requirements into appropriate technical requirements. It provides a framework for determining tradeoffs among different combinations of design features. The output of the QFD gives direct input into

and the standard and a second

product definition documents, customer requirements, and product specifications [Gautschi, 1993].

QFD is a very powerful tool when used by a cross-functional team in a concurrent product/manufacturing process development environment [Hales, 1994]. It uses lists and matrices to identify key information about the product or development process. Decision information is collected and weighed against customer requirements to ensure that the new product or service maintains its customer focus. Although QFD does not deal with the management aspects of developing a product, it generally improves the team's ability to define and design a product's attributes. [Goldense, 1993] gives advice on the benefits and cost of applying QFD within a company.

[Havener, 1993] discusses the way in which QFD can be effectively used to improve customer satisfaction and indicates eight steps in the QFD process:

- (1) Identify customer needs;

- (2) Identify product requirements;

- (3) Relate customer needs to product requirements;

- (4) Conduct a competitive performance assessment;

- (5) Conduct a technical feasibility assessment;

- (6) Perform a competitive technical assessment;

- (7) Reconcile the differences between technological limitations and customers' needsby product requirement tradeoffs; and

- (8) Develop important controls.

QFD has been successfully applied to a variety of industries such as automobiles, aerospace, electronics, textiles, and computer software. [Natarajan, Martz, and Kurosaka,

1999] applies QFD techniques to the design of an internal development system. The use of QFD technique as a tool for requirement acquisition and design analysis of a ground software intensive project is studied in [Elboushi and Sherif, 1997]. The results obtained indicate that the QFD process enables requirements to be captured and specifications and designs to be produced that are efficient, robust, and consistent. Telrad Telecommunication and Electronic Industries has developed a rigorous questionnaire methodology using QFD [Glushkovsky, Florescu, and Hershkovits, 1995]. Florida Power and Light (FPL), through one of its groups, launched a major customer research effort to determine what customers expect when they telephone FPL for a transaction. The group used QFD to systematically translate customer requirements into operational requirements [Graessel and Zeidler, 1993]. The use of QFD as a tool to improve software quality is examined in [Erikkson and McFadden, 1993].

QFD tools are also developed. International TechneGroup provides tools and technologies to support QFD. Its software tool, QFD/Capture, automates the compilation and prioritization of QFD data, performing all calculations and assisting in data analysis [Farrell, 1994]. In addition, the software generates the matrices fundamental to the QFD approach and ensures that customer requirements are not only built into the product, but also into the product's manufacturing process.

## (b) Design for Manufacture (DFM)

Many industrial manufacturing problems and inefficiencies can be traced back to the design stage. Substantial reductions in manufacturing costs could result from revisions at the design stage and such measures would crucially affect the success of a product. DFM

represents new awareness of the importance of design as the first manufacturing step. It recognizes that a company cannot meet quality and cost objectives with isolated design and manufacturing engineering operations. The objectives of the DFM approach are to identify product concepts that are inherently easy to manufacture, to focus on component designs for ease of manufacture and assembly, and to integrate both product design and manufacturing process design to make sure that the best match for needs and requirements is obtained [Syan and Menon, 1994].

[Ong and Nee, 1998] proposes a fuzzy set based fixturability evaluation procedure for establishing fixturing relations between the features on a part and assessing the suitability of these features for use as fixturing features during the machining of other features on the part. The optimization of device design for manufacture without sacrificing performance and reliability goals is discussed in [Lu, Holton, and Fenner, 1998]. The authors describe an optimized DFM procedure that uses new design of experiments, weighted least squares modeling, and multiple-objective mean-variance optimization methods. [Philpott, Warrington, and Branstad, 1996] presents a parametric contract modeler for providing manufacturing cost information to engineering designers during the early conceptual design phase of new product development. A computationally efficient method is presented in [Gadh and Prinz, 1995] to convert the basic topological elements used in CAD systems into more abstract geometrical features necessary for DFM analysis. [Bavishi, 1997] discusses the benefits of using cost-estimating software as a DFM tool.

The DFM philosophy is widely accepted in industry. [Dominach, 1993; Langan, 1998] discusses the DFM concept and application in the production of printed circuit

boards and printed wiring boards. General Motors reported that it can reduce component parts and assembly time almost by half by integrating DFM schemes in its product development process [Murray, 1995; King, 1996; Bonenberger, 1994]. Ranor Inc. used a PC-based CAD/CAM system to handle the design for assembly, the design for manufacture, and the machining processes of large manufacturing tasks [Raymond, 1995]. DFM techniques were also used in the design of a new front corner chassis assembly in the fourth generation 1993 Camaro/Firebird cars [Green and Reder, 1993].

Many companies are also developing design software that utilizes the principles of DFM. These companies include Boothroyd Dewhurst, Hewlett-Packard, Matra Datavision, and Lucas [Dvorak, 1994].

## (c) Design for Assembly (DFA)

It is acknowledged that assembly represents one of the major factors affecting product cost and quality. DFA is a key element in creating competitive products and reducing time-to-market. The objectives of the DFA approach are to identify product concepts that are inherently easy to assemble and to favor product and component designs that are easy to grip, feed, join and assemble by manual or automatic means [Syan and Menon, 1994].

[Tatikonda, 1994] describes a DFA methodology for product reengineering and new product development. Five factors to help companies optimize and successfully implement DFA strategies are proposed in [Munro, 1995]:

- (1) Leadership has acquired knowledge of tools and experience of project teams;

- (2) Leadership has developed and implemented a strategy;

- (3) The plan is understood and accepted by all involved;

- (4) External organizations are used for profound knowledge; and

- (5) Strategic managers utilize the correct approach.

A variety of DFA tools have been developed. Boothroyd Dewhurst has released a series of versions of its programs for designing easy-to-assemble, environmentally friendly products [Deitz, 1998]. These include the Design for Assembly (DFA) software package, which guides design engineers through an analysis of a proposed design's ease of assembly and reduces part count and assembly time, the Design for Manufacture (DFM) software package, which estimates tool costs through informed material trade-off judgments, and the Design for Environment software package, which works in tandem with DFA analyses to help designers evaluate and optimize the disassembly sequences of products for end-of-life recovery. These software tools are used by automotive industry suppliers to improve product cost and quality and to gain a competitive edge over other suppliers. Lucas Engineering and Systems has also developed design-support software tools [Kobe, 1994]. The Design for Assembly part of the Lucas system identifies poor designs, difficulty of assembly, unnecessary parts, and more.

#### (d) Rapid Prototyping (RP)

Prototype may be defined as an approximation of the product along one or more dimensions of interest [Ulrich and Eppinger, 1995]. Prototyping is the process of developing such an approximation of the product. The main purpose of building a prototype is to help people understand the system when they define the requirements, so that they can write the requirements down in product specifications. Prototyping is aimed at reducing design time by giving an accurate specification of the problem at the beginning, which therefore removes the need for later changes [Syan and Menon, 1994].

Rapid prototyping (RP) is also referred to as solid freeform fabrication (SFF), desktop manufacturing, and layered manufacturing. These techniques have the potential to produce accurate, structurally sound, 3-D models of objects designed using computers and manufactured directly using a CAD database, from a range of materials such as photocurable resin, ceramic and metallic powders, paper, and nanophase [Manthiram, Bourell, and Marcus, 1993; Onuh and Hon, 1998]. No part-specific tooling or human intervention is required, and the models are available to the user in minutes or hours [Crawford and Beaman, 1999; Ormond, 1993].

SFF methods include stereolithography, selective laser sintering, solid ground curing, 3-D printing, laminated object manufacturing, fused deposition modeling, and recursive mask and deposit processing [Marcus and Bourell, 1993; Amon, Beuth, and Weiss, 1998; Bandyopadhyay, Panda, and Janas, 1997; Agarwala, Bandyopadhyay, and van Weeren, 1996].

The general application areas of SFF are short-run manufacturing, mold and die making, and accurate tooling [Marcus and Bourell, 1993; Sriraman, Winek, and Habingreither, 1999]. [Langdon, 1999; Chalmers, 1998] reviews recent developments in rapid prototyping and considers their likely impact on the automotive industry.

The benefits attributed to RP include cost savings, time savings, and improved product quality. However, the real value of using RP technology in product development is to reduce risk. To date, at least 99% of RP use has fitted into one of the following six applications: concept models, presentation models, functional parts, tooling patterns, investment casting patterns, and alternative tooling [Mueller, 1999]. Companies that most effectively use RP in their product development effort use a combination of these applications and utilize them at appropriate points in the development process.

#### 2.2 Environmental Consciousness Issues

As mentioned in Chapter 1, with the rapid development of the industrial society, environmental issues are receiving more and more attention in the recent years. Demands for environmentally conscious products are a natural result of this trend. A great amount of research effort is being carried out concerning this problem [Brinkley, Kirby, and Charron, 1997; Sage, 1997; Srinivasan, Sheng and Wu, 1995a, 1995b; Ishii, Eubanks, and Di Marco, 1994; Jovane *et al.*, 1993; Navin-Chandra, 1993; Zhang and Yu, 1997; Zussman and Zhou, 1999]. In the literature, two major research areas are emphasized: life cycle analysis/assessment and design for environment.

## 2.2.1 Life Cycle Analysis/Assessment (LCA)

Life cycle analysis/assessment (LCA) is a family of methods for systematically assessing material and energy use, waste emissions, services, processes, and technologies associated with a product over its entire life. Three types of LCA methods are in use: life cycle inventory analysis, impact analysis, and cost analysis [Mizuki *et al.*, 1997]. Life cycle inventory analysis uses quantitative data to establish the levels and types of energy and material inputs to a system and the resulting release. Impact analysis generally involves normalization and weighting of the inventory results to formulate an overall

metric for comparing dissimilar environmental results. Cost analysis derives cost properties associated with unit operations.

A comprehensive overview of life cycle assessment methodologies is presented in [De Langhe, Criel, and Ceuterick, 1998].

[Munoz and Sheng, 1995] presents an analytical approach for determining the environmental impact of machining processes. [Luo et al., 1999] presents a method for analyzing the environmental performance of solid freeform fabrication processes. A technique for producing a rapid life cycle assessment is described in [Graedel, Allenby, and Comrie, 1995]. [Hendrickson, Horvath, and Joshi, 1998] shows that process and product models used for performing LCAs can be represented as process flow diagrams or as matrices of process interactions. [Saur, Hesselbach, and Eyerer, 1997] discusses enhancements to LCA that are designed to improve the quality of conclusions used as design parameters. A framework for environmental LCA based on physical measures is presented in [Knoepfel, 1996] and applied to the comparison of long-distance energy transport systems. A mixed LCA approach is used in [Schuckert, Saur, and Florin, 1996] to evaluate the environmental behavior of products or systems through an investigation of energy uses in all life stages of an industrial product from the extraction of raw materials to the disposal of wastes. An LCA approach to manufacturing process and materials selection is described in [Harsch, Schuckert, and Eyerer, 1996]. [Zhou et al., 1996; Caudill et al., 1997; Al-Okush, Caudill, and Thomas, 1999] introduces a multi-lifecycle concept and proposes a multi-lifecycle assessment (MLCA) methodology to evaluate the energy consumption and environmental emissions of a product. The methodology is

1. 《新聞》:《語語答》:[1985]

implemented into a software package [Jin, 1999] that provides a useful decision support tool to develop products and processes that are suitable for multiple life cycles.

[Alting, Hauschild, and Wenzel, 1998] uses three industrial cases to show how a newly developed LCA methodology can assist product developers in the development of more environmentally friendly products. A study was commissioned by the U.K. Department of the Environment to assess how LCA methodology could be developed and applied to assist decision makers in waste management [Barton, Dalley, and Patel, 1996]. [Curran, 1995] describes how an LCA approach can be a beneficial support tool in assessing pollution prevention opportunities. The benefits of using economy input-output life-cycle analysis to estimate economy-wide discharges are discussed in [Lave, Cobas Flores, and Hendrickson, 1995]. The use of LCA to identify the environmental impact of products and to evaluate opportunities to reduce this impact is discussed in [Curran, 1993].

LCA has a wide range of applications. Electronic equipment manufacturer Nortel has applied LCA extensively in its overall environmental management strategy [Azapagic and Solberg Johansen, 1998]. A modified life cycle analysis (MLCA) was developed by Ford Motor Co. for the automotive industry [Sullivan, Costic, and Han, 1998]. The steel industry is gaining valuable experience in the use of LCA [Chubbs and Steiner, 1998]. [Steele and Allen, 1998] uses an abridged life cycle assessment, which produces easily comprehended information about each life stage of a product, to analyze environmental impact associated with recycling and waste management of four battery technologies. [Hazel, 1996] discusses the use of life cycle assessment as a method for evaluating the impact of coating formulation strategies on environmental and cost performance.

# 2.2.2 Design for Environment (DFE)

Design for environment (DFE) is a newly formed academic and technological area as people have realized that it is the product design stage that plays the most important role in the product's entire life cycle, and improvements in design bring about the greatest benefits and provide the most efficient solutions to the difficult environmental problems that may be faced later. It takes place early in a product's design phase to ensure that the environmental consequences of a product's life cycle are understood before manufacturing decisions are committed. The scope of DFE encompasses many disciplines, including environmental risk management, product safety, occupational health and safety, pollution prevention, ecology and resource conservation, accident prevention, and waste management. It is actually a combination of several design topics including disassembly, recovery, recyclability, regulatory compliance, disposition, health and safety impact, and hazardous material minimization [Mizuki *et al.*, 1997].

[Glantschnig, 1994] explores issues and challenges faced by product designers and environmental design specialists developing green products and investigates external factors and forces that impact green design. [Hersh, 1998] presents an excellent survey of systems approaches to green design and discusses their applications to the computer industry. A comprehensive overview of design for environment methodologies is presented in [De Langhe, Criel, and Ceuterick, 1998]. [Zhang, Kuo, and Lu, 1997] updates information about environmentally conscious design and manufacturing and provides some general information, guidelines, and references for research and implementation. A review of DFE approaches to sustainable development is presented in [Keoleian and Menerey, 1994]. [Sheng and Hertwich, 1998] presents an overview of the hierarchical levels of comparative waste assessment which links process-level emissions to immediate, site-wide, and eco-system impact.

DFE has many successful industrial applications. Some of the best-known environmentally progressive companies include AT&T, IBM, Hewlett-Packard, MCC, Dow Chemical, and so on [Fiksel, 1996]. In the semiconductor industry, addressing environmental issues has resulted in a cultural change in which environmental impact must be considered during product and process design [Beu and Mendicino, 1997]. The U.S. government has launched a nationwide program that aims to encourage engineers to develop more environmentally conscious designs. The National Environmental Technology Strategy calls for the promotion of innovation, the reduction of red tape, the reinvention of regulations, and improved availability of information [Wingo, 1995]. Several examples of green design are described in [Considine, 1995].

With the development of DFE theory, sophisticated design support tools are necessary for the early stage of design. These tools are able to provide guidance on design regarding to environmental impact, thus assisting designers in integrating environmental consciousness into functional considerations [Zhang and Yu, 1997]. [Thomson, Koshland, and Lucas, 1997] proposes a comprehensive environmental decision-making tool, called the index ITOX, for evaluating the effectiveness of hazardous waste destruction technologies, especially thermal-processing methods such as incineration. The Boeing Company is currently campaigning to persuade other major manufacturers to join it in creating a general purpose pollution prevention design software package. The purpose of the software, which is called the Expert Process Advisory System (EPAS), is to instantaneously present designers with information about the environmental ramifications of their design options. EPAS allows all the relevant facts to be ranked and weighted, thus improving product designs and reducing environmental life cycle costs [Betts, 1998].

# 2.3 Summary

The economic success of manufacturing firms largely depends on their ability to identify the needs of customers and to create quickly products that meet these needs and can be produced at low cost. New product development is becoming easier but at the same time more complex and challenging along with scientific/technological developments and social/economic evolutions.

This chapter provides an overview of the major research issues/effort being carried out in academia and industries about future products and processes. These issues can generally be classified into two categories: the category of product profitability issues and the category of environmental consciousness issues. Product profitability issues address how to develop a profitable product in more efficient ways, and environmental consciousness issues address how to minimize the environmental impact of industrial products throughout their life cycles.

This research addresses issues in both categories and provides an integrated solution methodology to competitive and environmentally conscious product and process development.

### CHAPTER 3

## A GENERIC FRAMEWORK FOR IPPD

Chapter 2 illustrates the diversity of research issues that are being addressed by industries and academia in the area of product and process development. Some methods and techniques are proposed and some tools are developed that are efficient and successful in solving some specific problems. However, there are no *general* methods existing that can systematically and efficiently solve the *general* problems in this area. Consequently, the overall status of new product development is still more or less ad hoc and disappointing. Successful solution of one problem does not mean much for others. When new problems arise, people do not know how to solve them as rapidly and efficiently as having been done on former ones.

However, if we look into the nature of current research issues of concern, we could notice that there exists great similarity under their seeming diversity. That is, most of these research issues have the same basic nature: they are concerned with some kind of requirements exerted on some specific phases (or the entire) of a product's expected life cycle. By this nature, most of the major research effort is trying to find some good or optimal solutions to fulfil the corresponding requirements.

Based on this observation, we then have the idea to re-address these seemingly different research issues/problems in a unified way such that we can find some *general* solutions to the *general* problems (both existing and forthcoming). As a result, a generic framework for integrated product and process development is developed in this chapter as the first major achievement of our research effort.

27

This chapter is organized as follows. Section 3.1 states the ideas underlying the generic framework. Section 3.2 gives the mathematical description of the generic framework. Section 3.3 explains the physical meaning of the generic framework through a simple product example.

## 3.1 Ideas

In the beginning of this chapter, we investigate the nature of current research issues in the area of product and process development. It is noticed that most of these research issues are dealing with some kind of requirements exerted on some specific phases (or the entire) of a product's life cycle. People are trying to find better and more systematic ways to fulfil these requirements, e.g., to reduce product development time and cost, to reduce manufacturing cost, to minimize environmental impact, and ultimately to obtain a successful product.

Based on this observation, our research is focused on looking for a methodology by which most of these seemingly different issues/problems are described uniformly and then solved similarly and formally.

To do this, a product's entire life cycle should be considered. This is because requirements for a product may arise from every step of its life cycle. In addition, a product's life cycle should be further divided into life phases. This is because requirements for a product are usually more precisely specified for each life phase than for the entire life cycle. Each life phase has its component activities and the corresponding quality of performance. Moreover, there exists close interrelationship among the product's life phases. The activities in each life phase may influence the activities in its posterior life phases. Therefore, in order to improve the performance of a life phase, not only should some requirements be exerted on this specific life phase, some other related requirements should also be exerted on its prior life phases that have influence on this one. Following this manner, most of the research issues of concern could be combined into a large constrained optimization problem and then be solved formally.

The generic framework for integrated product and process development, which will be described next, represents the ideas hereinabove.

# 3.2 A Generic Framework for IPPD

The mathematical description of the generic framework is as follows:

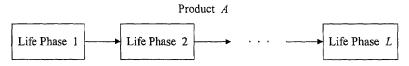

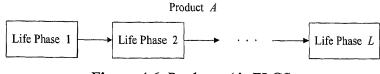

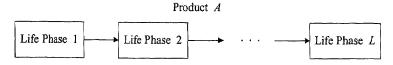

Represent the target product as A. Consider A's entire life cycle. A's life cycle is divided into a sequence of L life phases (or *life stages* as used by some researchers) as shown in Figure 3.1. Division is based on the extent of interest and the necessary granularity.

Figure 3.1 Representation of product A's life cycle.

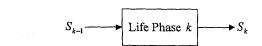

For life phase k, its input product status is  $S_{k-1}$ , and its output product status is  $S_k$  (Figure 3.2).

Figure 3.2 Product status representation of a life phase.

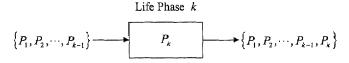

There are  $n_k$  major processes/activities in life phase k, i.e.,  $n_k$  major processes/activities constitute the transformation of product status from  $S_{k-1}$  to  $S_k$ . These  $n_k$ processes/activities are represented by a process set  $P_k$ :

$$P_k = \left\{p_1^k, p_2^k, \cdots, p_{n_k}^k\right\},\,$$

which is constrained by process sets  $P_1, P_2, \dots$ , and  $P_{k-1}$ :

$$P_k\Big|_{P_1,P_2,\cdots,P_{k-1}}.$$

Therefore, life phase k has an alternative process set representation as shown in Figure 3.3.

Figure 3.3 Process set representation of a life phase.

Based on the preceding representation of a product's life cycle, a general index vector  $\mathbf{c}$ ,

$$\mathbf{c} = \begin{pmatrix} c_1 & \cdots & c_i & \cdots & c_\alpha \end{pmatrix}^T,$$

is proposed and applied to each life phase to evaluate its corresponding performance. Index vector **c** may consist of such components as cost, benefit, and environmental impact. For life phase k, we have an index vector  $\mathbf{c}_k$ :

$$\mathbf{c}_{k} = \mathbf{c}(P_{k}) = \begin{pmatrix} c_{1k} & \cdots & c_{ik} & \cdots & c_{\alpha k} \end{pmatrix}^{T},$$

where  $c_{ik} = c_i(P_k)$  is the *i*th index of life phase k.

Altogether, there are L index vectors (one for each life phase):

$\mathbf{c}_{k} = \mathbf{c}_{k} \cdots \mathbf{c}_{k} \cdots \mathbf{c}_{k}$

They are gathered into an index matrix C to evaluate the overall performance of the product's entire life cycle:

$$\mathbf{C} = \begin{pmatrix} \mathbf{c}_1 & \cdots & \mathbf{c}_k & \cdots & \mathbf{c}_L \end{pmatrix} = \begin{pmatrix} c_{11} & \cdots & c_{1k} & \cdots & c_{1L} \\ \vdots & & \vdots & & \vdots \\ c_{\alpha 1} & \cdots & c_{\alpha k} & \cdots & c_{\alpha L} \end{pmatrix}_{\alpha \times L}$$

Various transforms of C can also be defined to evaluate product A's different performances:

# transform(C).

Finally, the generally concerned research issues can be expressed as:

Given C or transform(C), find process sets  $P_1, P_2, \dots$ , and  $P_L$ ,

such that C or transform(C) is optimized.

### 3.3 An Example

This section provides some additional explanations about the physical meaning of the generic framework. A simple cup development example is used throughout this section to clarify the statement.

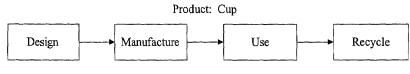

As mentioned in Chapter 1, the increasing number and variety of requirements from different life phases of a product merge into the need for an overall consideration of a product's entire life cycle and ultimately an integrated product and process development environment. For an integrated cup development environment, for example, a cup's entire life cycle should be considered. Also, with the requirements for the different life phases of a cup, we should divide a cup's life cycle into interesting life phases, with each life phase corresponding to its specific performance requirements. For a simple illustration, assume that a cup has a life cycle as shown in Figure 3.4.

Figure 3.4 A simple example: A cup's life cycle.

In Figure 3.4, a cup's life cycle consists of four consecutive life phases, i.e., design, manufacture, use, and recycle. Each life phase has its corresponding activities and performance criteria. Moreover, there exists close relationship among these life phases. Theoretically, the activities in one life phase influence the activities in all its posterior life phases. In this example, the design phase influences the other three phases; the manufacture phase influences the use and recycle phases; and the use phase influences the recycle phase. In other words, the activities in one life phase are influenced by the activities in each of its prior life phases. As a result, if we want to *really* optimize the performance of a life phase, not only should the activities in this life phase be adjusted, the activities in each of its prior life phases should be adjusted as well. For example, in order to optimize the performance of a cup's recycle phase, we definitely need to select the best recycling method to obtain low cost, minimum environmental impact, and maximum benefit, etc. Moreover, many other more important adjustment decisions should be made in the design, manufacture, and use phases as well, which all influence the recycle phase. For example, a better design, which may mean selection of a better material with less hazardous component, can make recycling much easier and with less environmental impact.

To further quantify the preceding explanations, assume that for each life phase k in Figure 3.4, process set  $P_k$  consists of only one process  $p^k$ , i.e.,

$$P_k = \left\{ p^k \right\}$$

Each process  $p^k$  may be one of several possible selections. The possible processes for each  $p^k$  are summarized in Table 3.1.

| Life Phase  | Process | Meaning                                              |  |

|-------------|---------|------------------------------------------------------|--|

| Design      | D1      | Foam cup design                                      |  |

|             | D2      | Plastic cup design                                   |  |

|             | D3      | Glass cup design                                     |  |

| Manufacture | M1      | Manufacture foam cup                                 |  |

|             | M2      | Manufacture plastic cup                              |  |

|             | M3      | Manufacture glass cup                                |  |

| Use         | U       | Use the cup                                          |  |

| Recycle     | R1      | Foam cup recycled for secondary use (e.g. packaging) |  |

|             | R2      | Plastic cup material recycling process A             |  |

|             | R3      | Plastic cup material recycling process B             |  |

|             | R4      | Glass cup material recycling process C               |  |

|             | R5      | Glass cup material recycling process D               |  |

Table 3.1 Possible processes in a cup's life cycle.

Assume that the general index vector **c** has two component  $c_1$  and  $c_2$ .  $c_1$  means cost and  $c_2$  means environmental impact. For life phase k, we have an index vector  $\mathbf{c}_k = \mathbf{c}(P_k) = \mathbf{c}(p^k)$ . For a cup's entire life cycle, we have an index matrix:

$$\mathbf{C} = \begin{pmatrix} \mathbf{c}_1 & \mathbf{c}_2 & \mathbf{c}_3 & \mathbf{c}_4 \end{pmatrix}.$$

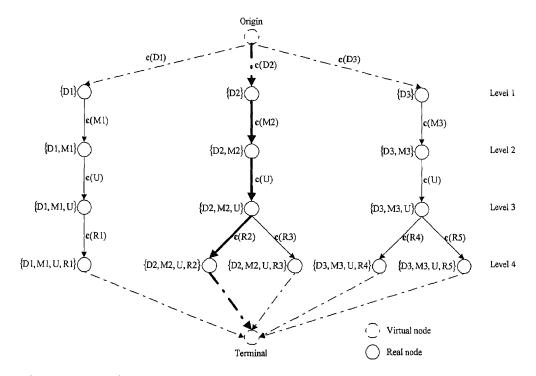

Based on the former information, we can enumerate all the possible cases of a cup's life cycle as shown in the directed graph of Figure 3.5. In Figure 3.5, there are two virtual nodes (origin and terminal) and four levels of real nodes. Level k corresponds to life phase k in a cup's life cycle. A directed path from the origin to the terminal represents a possible case of a cup's life cycle. A real node on level k has marking  $\{p^1, \dots, p^k\}$  (referring to the representation method of Figure 3.3). The input arc to a real node on level k has weight  $\mathbf{c}(p^k)$ .

Figure 3.5 A directed graph showing all the possible cases of a cup's life cycle.

Now assume that we want to optimize the index vector  $\mathbf{c}_4 = \mathbf{c}(p^4)$ , which means that we want to minimize cost  $c_1(p^4)$  and environmental impact  $c_2(p^4)$ . In order to do this, we simply check the values of  $\mathbf{c}_4 = \mathbf{c}(p^4)$  at all the possible processes of  $p^4$  and find out that recycling process R2, for example, is the optimal one. This recycling process in turn requires design D2 in the design phase, and manufacture process M2 in the manufacture phase. Thus, in order to optimize  $\mathbf{c}_4 = \mathbf{c}(p^4)$ , we make the following selections:

$$p^{1} = D2$$

,  $p^{2} = M2$ ,  $p^{3} = U$ , and  $p^{4} = R2$ .

This is shown by the bold path in Figure 3.5.

This simple product example shows the practical meaning of the proposed generic framework.

### 3.4 Summary