### **Copyright Warning & Restrictions**

The copyright law of the United States (Title 17, United States Code) governs the making of photocopies or other reproductions of copyrighted material.

Under certain conditions specified in the law, libraries and archives are authorized to furnish a photocopy or other reproduction. One of these specified conditions is that the photocopy or reproduction is not to be "used for any purpose other than private study, scholarship, or research." If a, user makes a request for, or later uses, a photocopy or reproduction for purposes in excess of "fair use" that user may be liable for copyright infringement,

This institution reserves the right to refuse to accept a copying order if, in its judgment, fulfillment of the order would involve violation of copyright law.

Please Note: The author retains the copyright while the New Jersey Institute of Technology reserves the right to distribute this thesis or dissertation

Printing note: If you do not wish to print this page, then select "Pages from: first page # to: last page #" on the print dialog screen

The Van Houten library has removed some of the personal information and all signatures from the approval page and biographical sketches of theses and dissertations in order to protect the identity of NJIT graduates and faculty.

### ABSTRACT

# DESIGN AND ANALYSIS OF A SCALABLE TERABIT MULTICAST PACKET SWITCH: ARCHITECTURES AND SCHEDULING ALGORITHMS

### by Feihong Chen

Internet growth and success not only open a primary route of information exchange for millions of people around the world, but also create unprecedented demand for core network capacity. Existing switches/routers, due to the bottleneck from either switch architecture or arbitration complexity, can reach a capacity on the order of gigabits per second, but few of them are scalable to large capacity of terabits per second.

In this dissertation, we propose three novel switch architectures with cooperated scheduling algorithms to design a terabit backbone switch/router which is able to deliver large capacity, multicasting, and high performance along with Quality of Service (QoS). Our switch designs benefit from unique features of modular switch architecture and distributed resource allocation scheme.

Switch I is a unique and modular design characterized by input and output link sharing. Link sharing resolves output contention and eliminates speedup requirement for central switch fabric. Hence, the switch architecture is scalable to any large size. We propose a distributed round robin (RR) scheduling algorithm which provides fairness and has very low arbitration complexity. Switch I can achieve good performance under uniform traffic. However, Switch I does not perform well for non-uniform traffic.

Switch II, as a modified switch design, employs link sharing as well as a token ring to pursue a solution to overcome the drawback of Switch I. We propose a round robin prioritized link reservation (RR+POLR) algorithm which results in an improved performance especially under non-uniform traffic. However, RR+POLR

algorithm is not flexible enough to adapt to the input traffic. In Switch II, the link reservation rate has a great impact on switch performance.

Finally, Switch III is proposed as an enhanced switch design using link sharing and dual round robin rings. Packet forwarding is based on link reservation. We propose a queue occupancy based dynamic link reservation (QOBDLR) algorithm which can adapt to the input traffic to provide a fast and fair link resource allocation. QOBDLR algorithm is a distributed resource allocation scheme in the sense that dynamic link reservation is carried out according to local available information. Arbitration complexity is very low. Compared to the output queued (OQ) switch which is known to offer the best performance under any traffic pattern, Switch III not only achieves performance as good as the OQ switch, but also overcomes speedup problem which seriously limits the OQ switch to be a scalable switch design. Hence, Switch III would be a good choice for high performance, scalable, large-capacity core switches.

# DESIGN AND ANALYSIS OF A SCALABLE TERABIT MULTICAST PACKET SWITCH: ARCHITECTURES AND SCHEDULING ALGORITHMS

by Feihong Chen

A Dissertation

Submitted to the Faculty of

New Jersey Institute of Technology

in Partial Fulfillment of the Requirements for the Degree of

Doctor of Philosophy

Department of Electrical and Computer Engineering

May 2000

Copyright © 2000 by Feihong Chen ALL RIGHTS RESERVED

### APPROVAL PAGE

# DESIGN AND ANALYSIS OF A SCALABLE TERABIT MULTICAST PACKET SWITCH: ARCHITECTURES AND SCHEDULING ALGORITHMS

### Feihong Chen

| Dr. Alı N. Akansu, Dissertation Co-Advisor                                                                     | Date  |

|----------------------------------------------------------------------------------------------------------------|-------|

| Professor of Electrical and Computer Engineering, NJIT                                                         | Date  |

| 2 20102002 01 <b>2</b> 10001000 0000 00001                                                                     |       |

|                                                                                                                |       |

|                                                                                                                |       |

| Dr. Needet Haun Diggestation Co. Advisor                                                                       | Date  |

| Dr. Necdet Uzun, Dissertation Co-Advisor<br>Assistant Professor of Electrical and Computer Engineering, NJIT   | Date  |

| Assistant Professor of Electrical and Computer Engineering, 1911                                               |       |

|                                                                                                                |       |

|                                                                                                                |       |

|                                                                                                                |       |

| Dr. Nirwan Ansari, Committee Member                                                                            | Date  |

| Professor of Electrical and Computer Engineering, NJIT                                                         |       |

|                                                                                                                |       |

|                                                                                                                |       |

|                                                                                                                |       |

| D. C. D. D. D. Committee Momber                                                                                | Date  |

| Dr. Symeon Papavassiliou, Committee Member<br>Assistant Professor of Electrical and Computer Engineering, NJIT | Date  |

| Assistant 1 folessor of Electrical and Computer Engineering, 17011                                             |       |

|                                                                                                                |       |

|                                                                                                                |       |

|                                                                                                                |       |

| Dr. H. Jonathan Chao, Committee Member                                                                         | Date  |

| Professor of Electrical Engineering, Polytechnic University, Brookly                                           | n, NY |

### **BIOGRAPHICAL SKETCH**

Author:

Feihong Chen

Degree:

Doctor of Philosophy in Electrical Engineering

Date:

May 2000

### Undergraduate and Graduate Education:

- Doctor of Philosophy in Electrical Engineering New Jersey Institute of Technology, Newark, NJ, 2000

- Master of Science in Electrical Engineering Beijing University of Posts and Telecommunications, Beijing, P.R.China, 1996

- Bachelor of Science in Electrical Engineering Xi'An University of Electronic Science and Technology (XIDIAN University), Xi'An, ShannXi, P.R.China, 1993

Major:

Electrical Engineering

### Presentations and Publications:

F. Chen, B. Yener, A.N. Akansu and S. Tekinay,

"A Novel Performance Analysis for the Copy Network in a Multicast ATM Switch,"

Proc. of IEEE ICCCN'98, Lafayette, LA, October 12-25, 1998, pp. 99-106.

F. Chen, N. Uzun and A. N. Akansu,

"A High Performance Output-Oriented Cell Scheduling Algorithm for Multicast ATM Switches,"

Proc. of CISS'99, Baltimore, MD, March 17-19, 1999, pp. 803-808.

F. Chen, N. Uzun and A. N. Akansu,

"A Large Scale Multicast ATM Switch With Input and Output Link Sharing," Proc. of IEEE GLOBECOM'99, Rio de Janeiro, Brazil, Dec. 1999, pp. 1251-1255.

### F. Chen, N. Uzun and A. N. Akansu,

"A Scalable Multicast ATM Switch using Link Sharing and Prioritized Link Reservation,"

Proc. of IEEE ICCCN'99, Boston, MA, October 1999, pp.218-222.

### F. Chen, N. Uzun and A. N. Akansu,

"Design of a Large Scale Multicast Packet Switch with a Distributed Resource Allocation Algorithm,"

Proc. of CISS'2000, Princeton, NJ, March 15-17, 2000, pp. FP 6.5 - FP6.10.

### F. Chen, N. Uzun and A. N. Akansu,

"A Distributed Dynamic Scheduling Algorithm for a Terabit Multicast Packet Switch,"

to be presented at IFIP NETWORKING'2000, Paris, France, May 2000.

### F. Chen, N. Uzun and A. N. Akansu,

"Design and Analysis of a Scalable Terabit Multicast Packet Switch with Dual Round Robin Dynamic Link Reservation,"

to be presented at IEEE ATM Workshop, Germany, June 2000.

### F. Chen, N. Uzun and A. N. Akansu,

"A Scalable Terabit Multicast Packet Switch with Link Sharing and Dual Round Robin Dynamic Link Reservation," submitted to the IEEE/ACM Transaction on Networking, January 2000.

### F. Chen, N. Uzun and A. N. Akansu,

"A Scalable Terabit Core Switch for Broadband Internet," submitted to IEEE MILCOM'2000, Los Angeles, LA, October 2000.

This work is dedicated to my husband and our parents.

### ACKNOWLEDGMENT

First and foremost, I would like to express my sincere gratitude to my advisors and mentors, Dr. Ali N. Akansu and Dr. Necdet Uzun. I appreciate Dr. Akansu for his constant support, guidance, and encouragement in every step of my way. I would like to thank Dr. Uzun, an excellent advisor and a good friend, for his inspiration and valuable discussion; for the time he has put into helping me to make this dissertation the comprehensive work it is today; and for his belief in my abilities and encouraging me to aim high.

I would like to thank my dissertation committee, Dr. Nirwan Ansari, Dr. Symeon Papavassiliou, and Dr. H. Jonathan Chao, for their being interested in this work and stimulating many valuable discussions and insightful comments. I would also like to extend my appreciation to Dr. Bulent Yener and Dr. Sirin Tekinay for their help at the beginning of this research work.

Likewise, I would like to thank Ms. Anne McMahon, who is always there for us and helps a lot in many ways. I would also like to extend my appreciation to the staff of the ECE department for their constant assistance in just about everything.

Many thanks are also due to my colleagues at NJCMR and CCSPR, especially my good friends Mahalingam Ramkumar, Xiaodong Cai, Minyi Zhao, Pingping Zong, Bin He and Anil Bircan, for all the help they have offered towards completion of this dissertation, and for a lot of fun we shared together. I would also like to thank Xueming Lin, Ziqiang Xu, and Jianguo Chen for their continues help and advise from the first day I joined NJIT.

Finally, words can never express the gratitude I feel toward my husband and our parents, whose support provides the foundation upon which this work and other achievements were built.

### TABLE OF CONTENTS

| $\mathbf{C}$ | hapt | er                                                                            | Page |

|--------------|------|-------------------------------------------------------------------------------|------|

| 1            | INT  | RODUCTION                                                                     | . 1  |

|              | 1.1  | Motivation                                                                    | . 1  |

|              | 1.2  | Review                                                                        | . 1  |

|              | 1.3  | Design Issues                                                                 | . 6  |

|              |      | 1.3.1 Multicasting                                                            | . 6  |

|              |      | 1.3.2 Scalability                                                             | . 8  |

|              |      | 1.3.3 Low Complexity                                                          | . 9  |

|              |      | 1.3.4 High Performance                                                        | . 9  |

|              | 1.4  | Outline                                                                       | . 11 |

| 2            |      | OVEL PERFORMANCE ANALYSIS FOR THE COPY NETWORK A MULTICAST ATM SWITCH         |      |

|              | 2.1  | Introduction                                                                  | . 14 |

|              | 2.2  | Notation and Assumptions                                                      | . 16 |

|              | 2.3  | Performance Analysis of NBNS Copy Network                                     | . 18 |

|              | 2.4  | Performance Analysis for both SIBNS and SIBS Copy Networks                    | . 19 |

|              |      | 2.4.1 Notation and Assumption                                                 | . 21 |

|              |      | 2.4.2 The Proposed Markov Model                                               | . 21 |

|              |      | 2.4.3 Performance Analysis                                                    | . 25 |

|              |      | 2.4.4 Validation of the Markov Model for SIBNS and SIBS                       | . 28 |

|              | 2.5  | Conclusion                                                                    | . 31 |

| 3            |      | TTCH I: A LARGE SCALE MULTICAST ATM SWITCH USING NPUT AND OUTPUT LINK SHARING | . 32 |

|              | 3.1  | Introduction                                                                  | . 32 |

## TABLE OF CONTENTS (Continued)

| $\mathbf{C}$ | hapt | er                                                                                               | ıge |

|--------------|------|--------------------------------------------------------------------------------------------------|-----|

|              | 3.2  | Switch Architecture                                                                              | 32  |

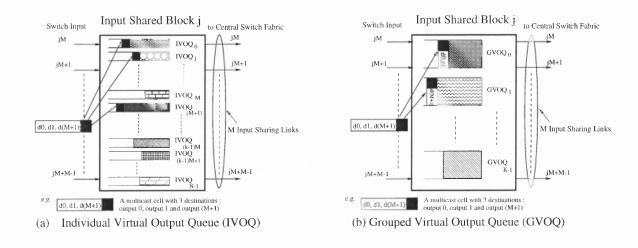

|              |      | 3.2.1 Input Shared Block                                                                         | 34  |

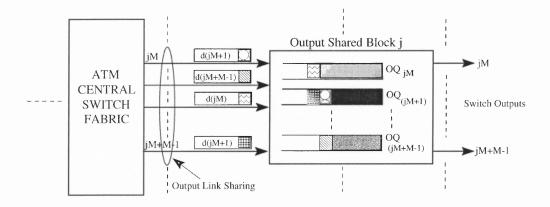

|              |      | 3.2.2 Output Shared Block                                                                        | 35  |

|              |      | 3.2.3 Central Switch Fabric                                                                      | 36  |

|              | 3.3  | Cell Scheduling                                                                                  | 36  |

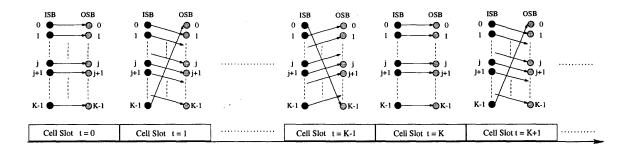

|              |      | 3.3.1 IVOQ Round Robin                                                                           | 37  |

|              |      | 3.3.2 GVOQ Round Robin                                                                           | 38  |

|              | 3.4  | Performance Evaluation                                                                           | 40  |

|              |      | 3.4.1 Traffic Model                                                                              | 40  |

|              |      | 3.4.2 Switch Performance                                                                         | 41  |

|              | 3.5  | Conclusion                                                                                       | 51  |

| 4            |      | TCH II: A MODIFIED SWITCH DESIGN USING LINK SHARING ND PRIORITIZED LINK RESERVATION              | 54  |

|              | 4.1  | Introduction                                                                                     | 54  |

|              | 4.2  | Switch Architecture                                                                              | 54  |

|              | 4.3  | Cell Scheduling                                                                                  | 56  |

|              |      | 4.3.1 Cell Delivery                                                                              | 56  |

|              |      | 4.3.2 Link Reservation: RR+POLR Algorithm                                                        | 56  |

|              |      | 4.3.3 Remarks                                                                                    | 60  |

|              | 4.4  | Switch Performance                                                                               | 61  |

|              | 4.5  | Conclusion                                                                                       | 70  |

|              |      | 4.5.1 Advantages of Switch II                                                                    | 70  |

|              |      | 4.5.2 Disadvantages of Switch II                                                                 | 72  |

| 5            |      | TCH III: A SCALABLE TERABIT MULTICAST PACKET SWITCH TH DUAL ROUND ROBIN DYNAMIC LINK RESERVATION | 74  |

|              | 5 1  | Switch Architecture                                                                              | 74  |

## TABLE OF CONTENTS (Continued)

| Cı | hapte | er     |                                         | Pa | age |

|----|-------|--------|-----------------------------------------|----|-----|

|    | 5.2   | Cell S | cheduling                               |    | 76  |

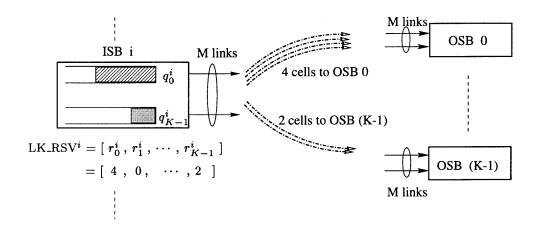

|    |       | 5.2.1  | Cell Delivery                           |    | 76  |

|    |       | 5.2.2  | Link Reservation                        |    | 77  |

|    | 5.3   | REQ-   | QOBDLR Algorithm                        |    | 79  |

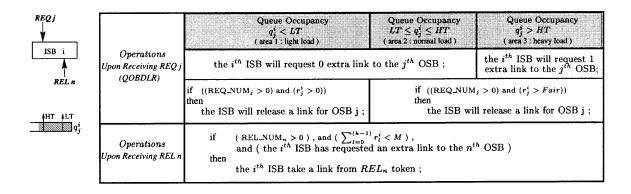

|    |       | 5.3.1  | Operations upon receiving $REQ_j$ Token |    | 80  |

|    |       | 5.3.2  | Operations upon receiving $REL_n$ Token |    | 81  |

|    |       | 5.3.3  | Remarks on REQ-QOBDLR Algorithm         |    | 81  |

|    |       | 5.3.4  | Conclusion on REQ-QOBDLR Algorithm      |    | 82  |

|    | 5.4   | REQF   | REL-QOBDLR Algorithm                    |    | 82  |

|    |       | 5.4.1  | Operations upon receiving $REL_n$ Token |    | 83  |

|    |       | 5.4.2  | Operations upon receiving $REQ_j$ Token |    | 85  |

|    |       | 5.4.3  | Remarks on REQREL-QOBDLR Algorithm      |    | 85  |

|    | 5.5   | Analy  | sis of QOBDLR Algorithms                |    | 86  |

|    |       | 5.5.1  | Algorithm Complexity                    |    | 86  |

|    |       | 5.5.2  | The choice of HT and LT                 |    | 86  |

|    |       | 5.5.3  | Scalability of QOBDLR Algorithms        |    | 89  |

|    | 5.6   | Perfor | mance Evaluation                        |    | 95  |

|    |       | 5.6.1  | Traffic Model                           |    | 95  |

|    |       | 5.6.2  | Switch Performance                      |    | 97  |

|    | 5.7   | Concl  | usion                                   |    | 108 |

| 6  | CON   | CLUS   | ION AND FUTURE WORK                     |    | 109 |

| AI | PPEN  | IDIX A | REQ-QOBDLR ALGORITHM                    |    | 111 |

| AI | PPEN  | IDIX B | REQREL-QOBDLR ALGORITHM                 |    | 115 |

| RI | EFER  | ENCE   | S                                       |    | 119 |

### LIST OF TABLES

| Tab! | le<br>·                                                                                                                                                                                                                                                                                                                                                                                                             | Page |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 1.1  | Performance requirements and objectives for BSS [42]. *: includes non-queueing related delays but excludes propagation, and does not include delays due to processing above ATM layer. N/S: not specified                                                                                                                                                                                                           | . 10 |

| 3.1  | Switch I: switch performance under uniform unicast traffic with different input load $\rho$ . The observed performance statistics are: (1) throughput; (2) average end-to-end cell delay and delay jitter $(D_{E-to-E}, (\text{Min}, \text{Max}))$ ; (3) average cell delay in ISB and delay jitter $(D_{ISB}, (\text{Min}, \text{Max}))$ ; (4) average occupancy of OSB $(S_{OSB})$ and $(\text{Min}, \text{Max})$ | . 42 |

| 3.2  | Switch I: switch performance under uniform multicast traffic with different input load $\rho$ . The observed performance statistics are: (1) throughput; (2) average end-to-end cell delay and delay jitter $(D_{E-to-E}, (\text{Min, Max}))$ ; (3) average cell delay in ISB and delay jitter $(D_{ISB}, (\text{Min, Max}))$ ; (4) average occupancy of OSB $(S_{OSB})$ and $(\text{Min, Max})$ )                  | . 48 |

| 4.1  | RR+POLR Algorithm                                                                                                                                                                                                                                                                                                                                                                                                   | . 58 |

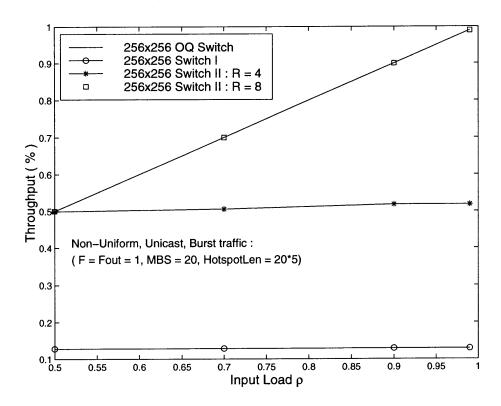

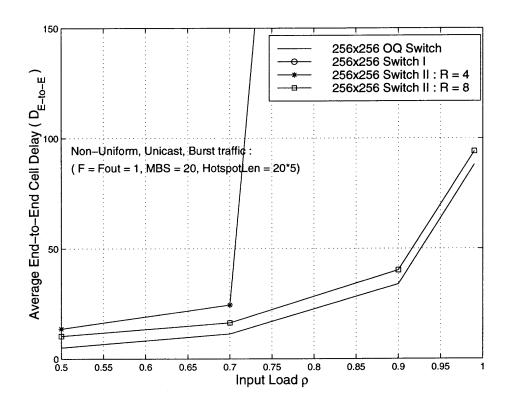

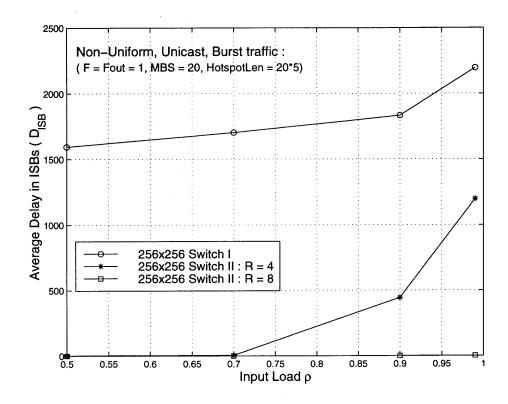

| 4.2  | Switch II: performance comparison under non-uniform unicast traffic with different input load $\rho$ . The observed performance statistics are: (1) throughput; (2) average end-to-end cell delay and delay jitter $(D_{E-to-E}, (\text{Min, Max}))$ ; (3) average cell delay in ISB and delay jitter $(D_{ISB}, (\text{Min, Max}))$ ; (4) average occupancy of OSB $(S_{OSB})$ and $(\text{Min, Max})$             | . 63 |

| 4.3  | Switch II: performance comparison under non-uniform multicast traffic with different input load $\rho$ . The observed performance statistics are: (1) throughput; (2) average end-to-end cell delay and delay jitter $(D_{E-to-E}, (\text{Min, Max}))$ ; (3) average cell delay in ISB and delay jitter $(D_{ISB}, (\text{Min, Max}))$ ; (4) average occupancy of OSB $(S_{OSB})$ and $(\text{Min, Max})$ )         | . 68 |

| 5.1  | The possible choices of HT and LT for an 256x256 switch consisting of 8 ISBs and 8 OSBs, i.e. $N=256, K=8, m=M=32$ . We select HT = 4, and LT = 2                                                                                                                                                                                                                                                                   | . 89 |

# LIST OF TABLES (Continued)

| Tabl | le                                                                                                                                                                                                                                                                                                                                                                                                     | Page  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 5.2  | Switch III: performance comparison under uniform multicast traffic with different input load $\rho$ . The observed performance statistics are: (1) throughput; (2) average end-to-end cell delay and delay jitter $(D_{E-to-E}, (\text{Min, Max}))$ ; (3) average cell delay in ISB and delay jitter $(D_{ISB}, (\text{Min, Max}))$ ; (4) average occupancy of OSB $(S_{OSB})$ and $(\text{Min, Max})$ | . 99  |

| 5.3  | Switch III: performance comparison under unicast "1 ISB $\rightarrow$ 1 OSB HotSpot" traffic. The observed performance statistics are: (1) throughput; (2) average end-to-end cell delay and delay jitter ( $D_{E-to-E}$ , (Min, Max)); (3) average cell delay in ISB and delay jitter ( $D_{ISB}$ , (Min, Max)); (4) average occupancy of OSB ( $S_{OSB}$ and (Min, Max))                             | . 102 |

### LIST OF FIGURES

| Figu | ıre                                                                                                                                                                                                                                                             | age |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 1.1  | Review on multicast ATM switches                                                                                                                                                                                                                                | 3   |

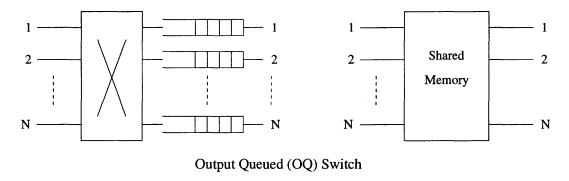

| 1.2  | A general architecture of an output queued (OQ) switch                                                                                                                                                                                                          | 4   |

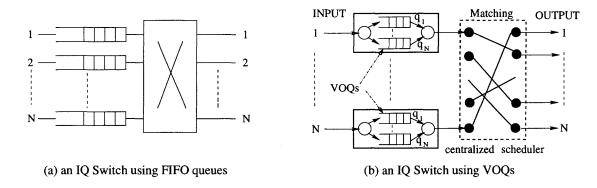

| 1.3  | A general architecture of input queued (IQ) switch: (a) an IQ switch using FIFO queues; (b) an IQ switch using VOQs                                                                                                                                             | 4   |

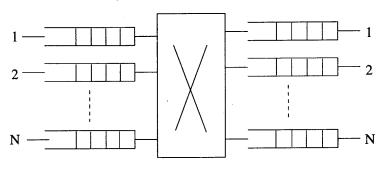

| 1.4  | A general architecture of input-output queued (IOQ) switch                                                                                                                                                                                                      | 6   |

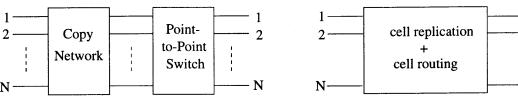

| 1.5  | Multicast switches                                                                                                                                                                                                                                              | 7   |

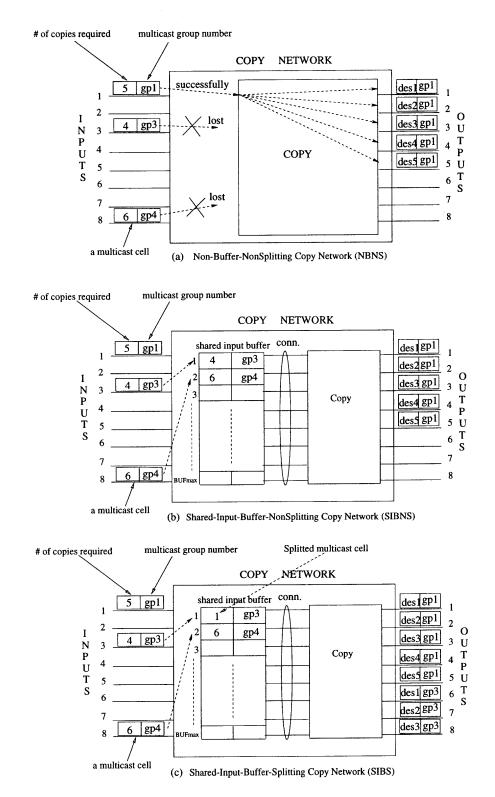

| 2.1  | Three scenarios of copy network in a multicast ATM switch                                                                                                                                                                                                       | 15  |

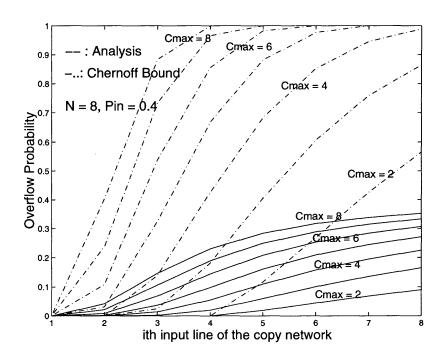

| 2.2  | Overflow probability in NBNS                                                                                                                                                                                                                                    | 19  |

| 2.3  | Cell loss and throughput in NBNS                                                                                                                                                                                                                                | 20  |

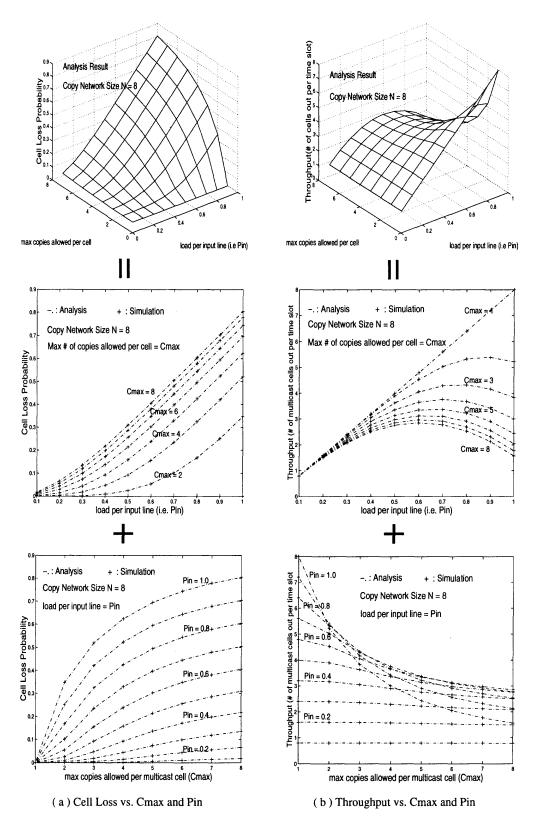

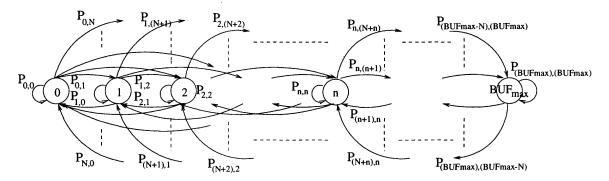

| 2.4  | The general Markov Model for both SIBNS and SIBS                                                                                                                                                                                                                | 22  |

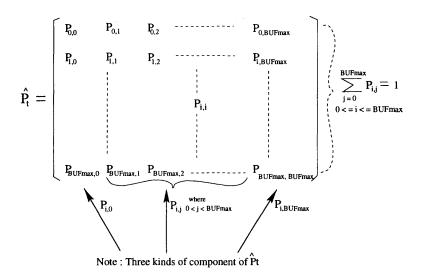

| 2.5  | State transition probability matrix of Markov chain : $\hat{P}_t \dots \dots$                                                                                                                                                                                   | 23  |

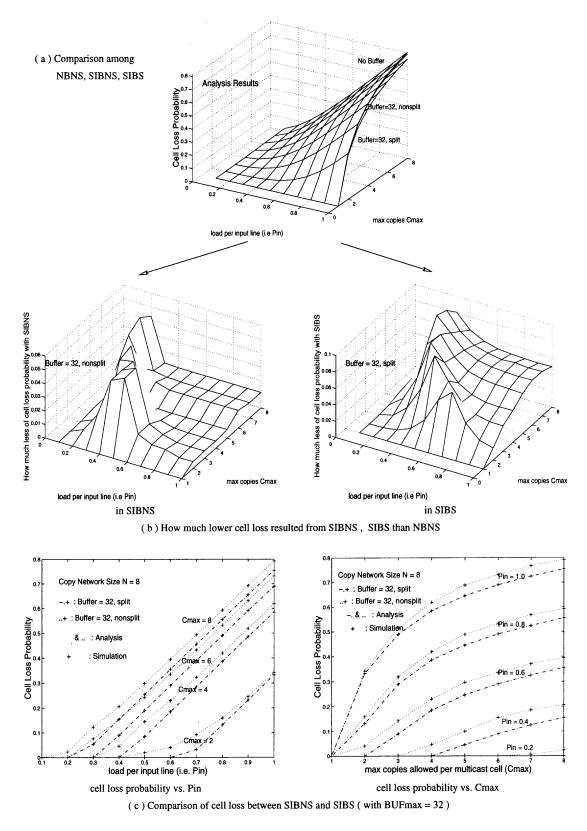

| 2.6  | Cell loss in three scenarios : NBNS, SIBNS and SIBS                                                                                                                                                                                                             | 26  |

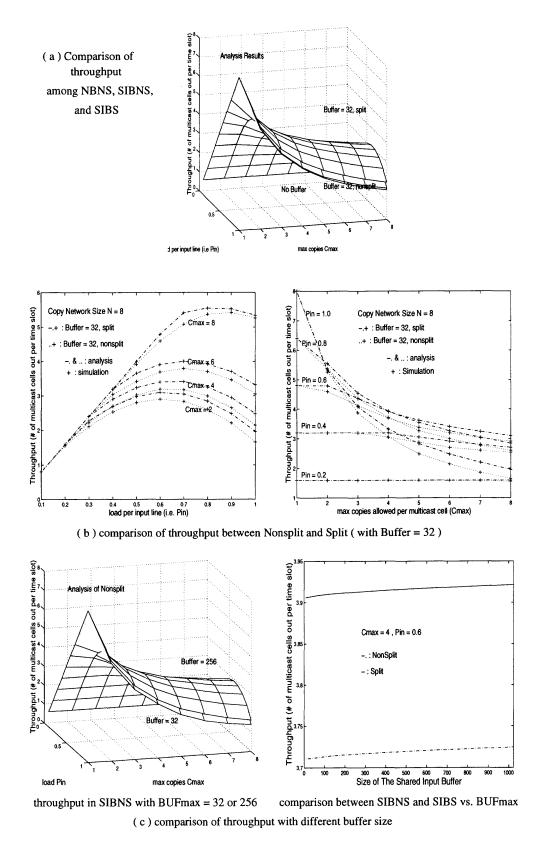

| 2.7  | throughput in three scenarios: NBNS, SIBNS and SIBS                                                                                                                                                                                                             | 27  |

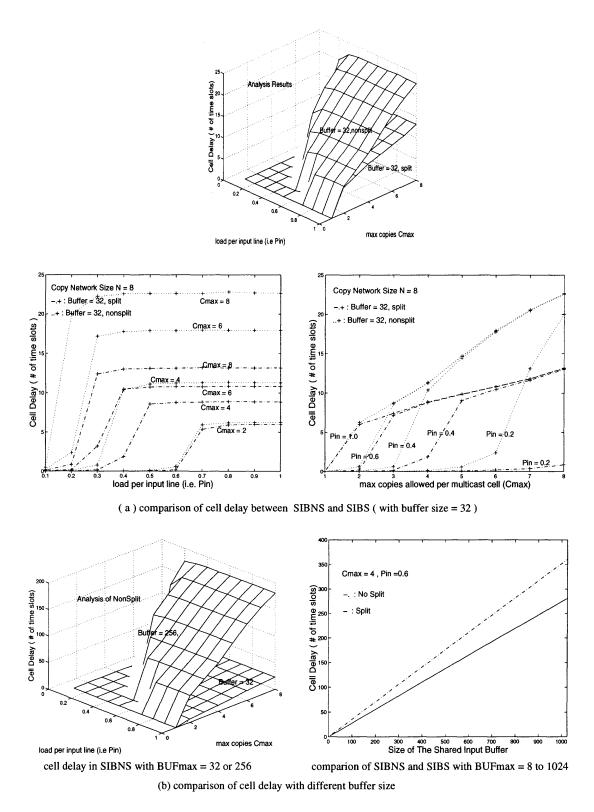

| 2.8  | Cell delay in shared-input-buffer copy networks : SIBNS and SIBS $\ \ldots \ .$                                                                                                                                                                                 | 29  |

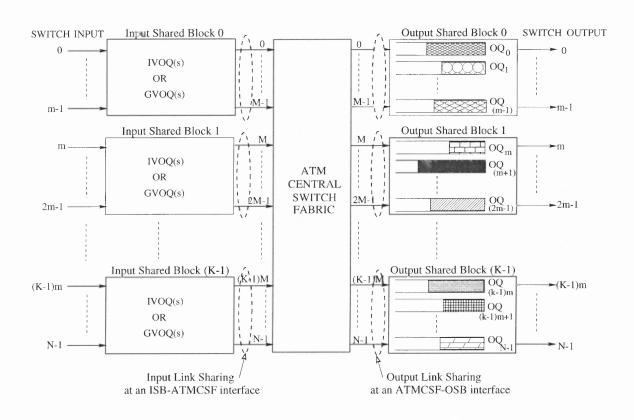

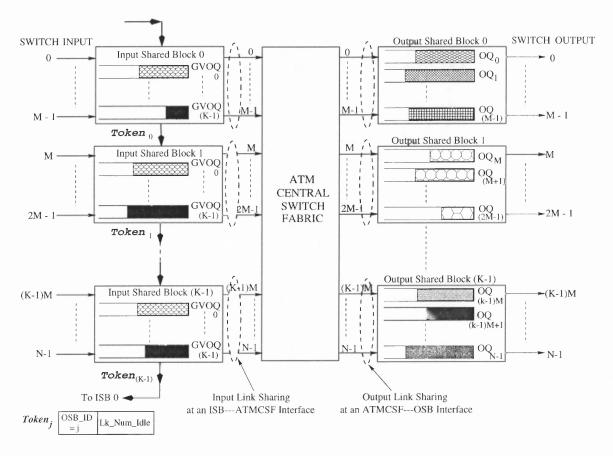

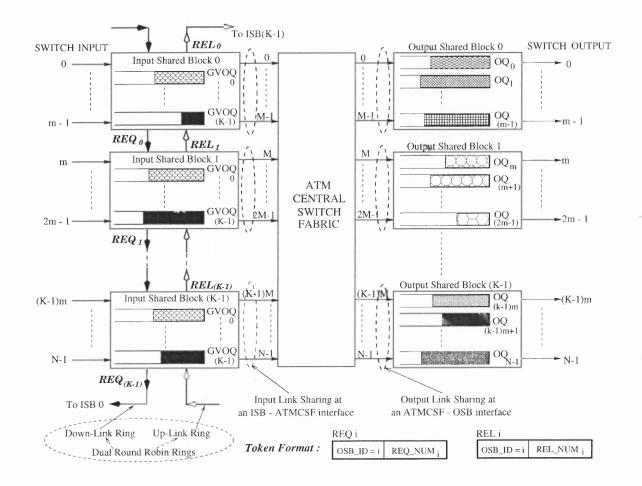

| 3.1  | Switch I: an $N \times N$ switch consists of $K$ ISBs, $K$ OSBs and ATMCSF; $K = \frac{N}{m}$ and $m = M$ in this dissertation. Input link sharing is achieved at every ISB-ATMCSF interface, and output link sharing is achieved at every ATMCSF-OSB interface | 33  |

| 3.2  | Input Shared Block (ISB) : (a) the $j^{th}$ ISB using IVOQs ; (b) the $j^{th}$ ISB using GVOQs                                                                                                                                                                  | 34  |

| 3.3  | Output Shared Block (OSB) with output link sharing (here, $m=M$ )                                                                                                                                                                                               | 36  |

| 3.4  | Switch I applies round robin (RR) cell scheduling which is based on an one-to-one group mapping from $K$ ISBs to $K$ OSBs                                                                                                                                       | 37  |

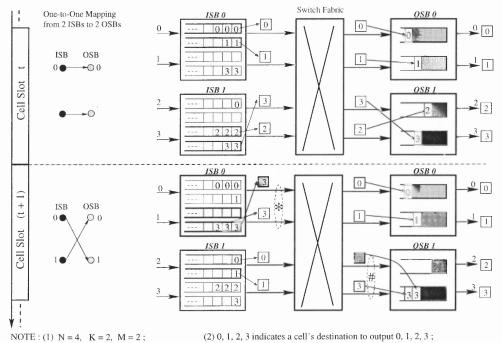

| 3.5  | IVOQ Round Robin in an 4x4 switch $(N = 4, m = M = 2, K = 2) \dots$                                                                                                                                                                                             | 38  |

| 3.6  | GVOQ Round Robin in an 4x4 switch $(N=4, m=M=2, K=2)$                                                                                                                                                                                                           | 39  |

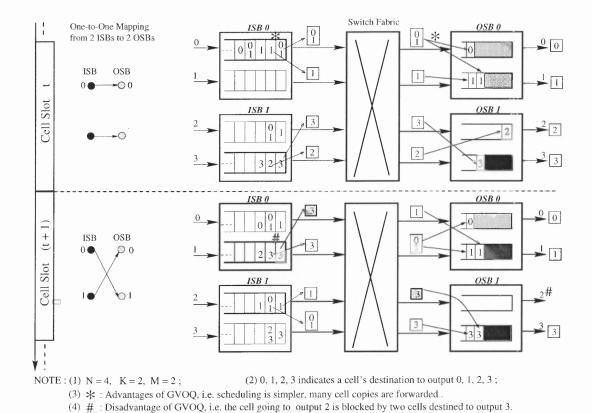

| 3.7  | Traffic Model: Multicast Bursty Traffic                                                                                                                                                                                                                         | 40  |

### LIST OF FIGURES (Continued)

| Figu | P                                                                                                                                                                                                                                                    | age |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

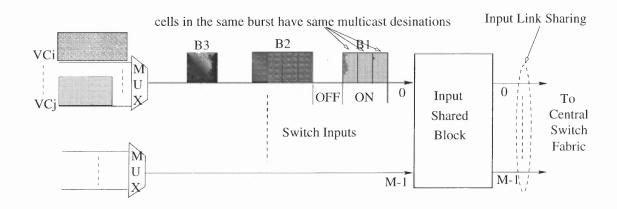

| 3.8  | Switch I: throughput under uniform unicast traffic                                                                                                                                                                                                   | 44  |

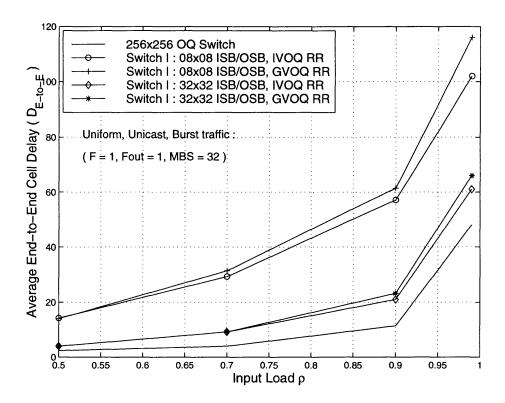

| 3.9  | Switch I : average end-to-end cell delay $(D_{E-to-E})$ under uniform unicast traffic                                                                                                                                                                | 45  |

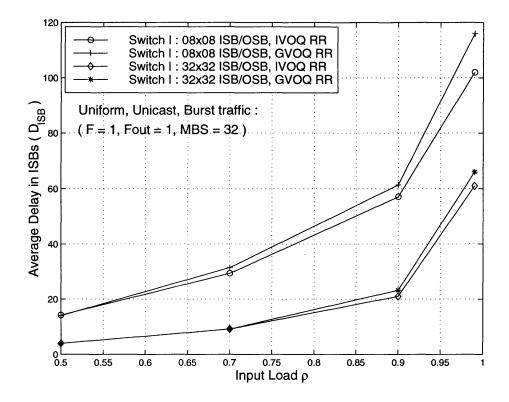

| 3.10 | Switch I : average cell delay in ISB $(D_{ISB})$ under uniform unicast traffic.                                                                                                                                                                      | 46  |

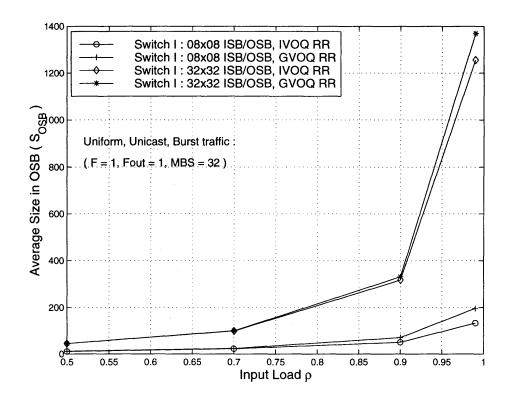

| 3.11 | Switch I : average size of OSB $(S_{OSB})$ under uniform unicast traffic                                                                                                                                                                             | 47  |

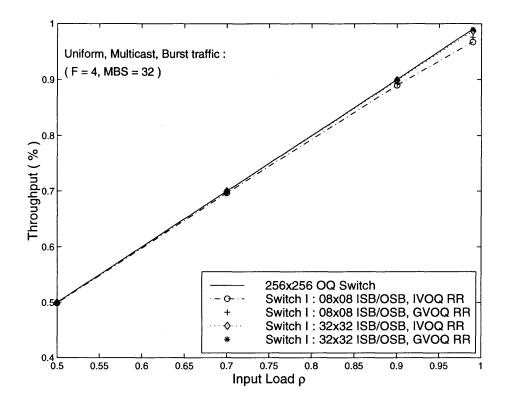

| 3.12 | Switch I: throughput under uniform multicast traffic                                                                                                                                                                                                 | 49  |

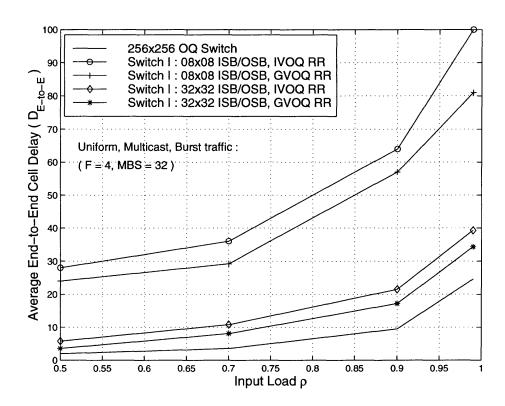

| 3.13 | Switch I : average end-to-end cell delay $(D_{E-to-E})$ under uniform multicast traffic                                                                                                                                                              | 50  |

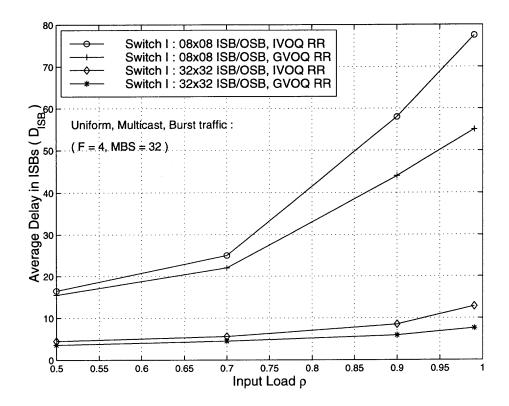

| 3.14 | Switch I : average cell delay in ISB $(D_{ISB})$ under uniform multicast traffic.                                                                                                                                                                    | 51  |

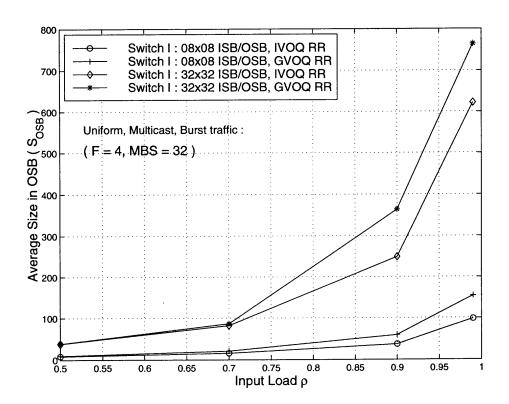

| 3.15 | Switch I : average size of OSB ( $S_{OSB}$ ) under uniform multicast traffic                                                                                                                                                                         | 52  |

| 3.16 | Performance of Switch I under '1 ISB $\rightarrow$ 1 OSB hotspot non-uniform traffic'                                                                                                                                                                | 53  |

| 4.1  | Switch II: an $NxN$ switch consists of $K$ ISBs, $K$ OSBs, ATMCSF, and a token ring; $K = \frac{N}{M}$ . Cell delivery in a cell slot is based on link reservation. We propose a round robin prioritized output link reservation (RR+POLR) algorithm | 55  |

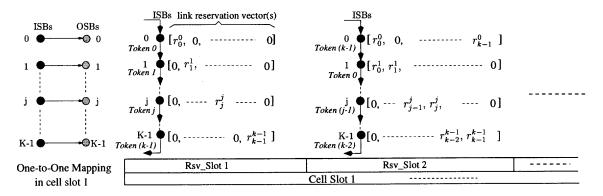

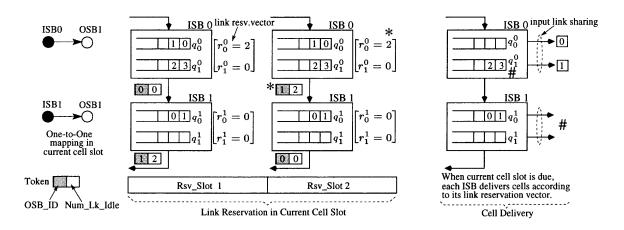

| 4.2  | Round Robin Prioritized Output Link Reservation (RR+POLR) algorithm performed in the $1^{st}$ Cell_Slot                                                                                                                                              | 59  |

| 4.3  | Switch II : throughput under "1 ISB $\rightarrow$ 1 OSB hotspot unicast traffic"                                                                                                                                                                     | 64  |

| 4.4  | Switch II : average end-to-end cell delay $(D_{E-to-E})$ under "1 ISB $\rightarrow$ 1 OSB hotspot unicast traffic"                                                                                                                                   | 65  |

| 4.5  | Switch II : average cell delay in ISB $(D_{ISB})$ under "1 ISB $\rightarrow$ 1 OSB hotspot unicast traffic"                                                                                                                                          | 66  |

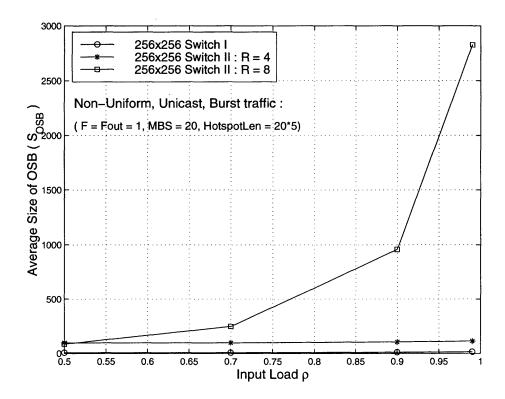

| 4.6  | Switch II : average size of OSB $(S_{OSB})$ under "1 ISB $\rightarrow$ 1 OSB hotspot unicast traffic"                                                                                                                                                | 67  |

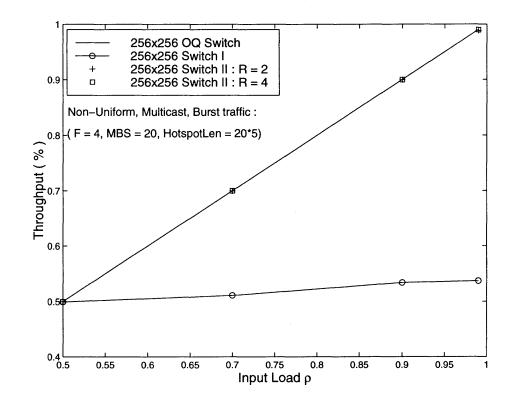

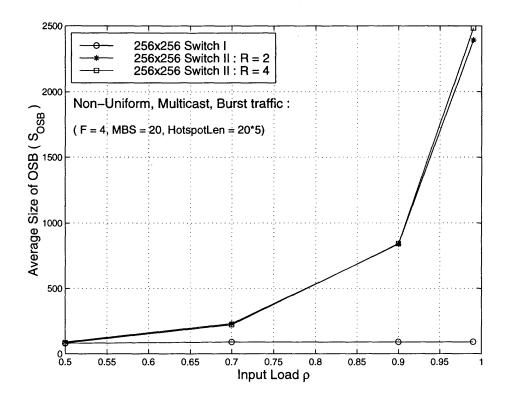

| 4.7  | Switch II : throughput under "1 ISB $\rightarrow$ 1 OSB hopspot multicast traffic".                                                                                                                                                                  | 69  |

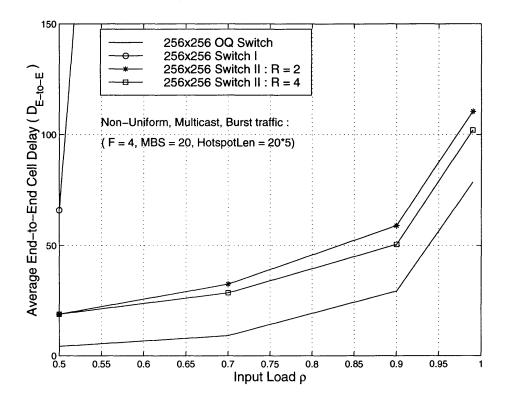

| 4.8  | Switch II: average end-to-end cell delay $(D_{E-to-E})$ under "1 ISB $\rightarrow$ 1 OSB hopspot multicast traffic"                                                                                                                                  | 70  |

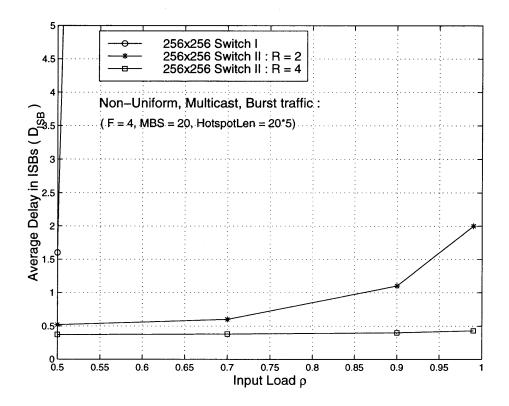

| 4.9  | Switch II : average cell delay in ISB $(D_{ISB})$ under "1 ISB $\rightarrow$ 1 OSB hopspot multicast traffic"                                                                                                                                        | 71  |

### LIST OF FIGURES

(Continued)

| Figu | ire                                                                                                                                                                                                                                                                                              | age |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.10 | Switch II : average size of OSB $(S_{OSB})$ under "1 ISB $\rightarrow$ 1 OSB hopspot multicast traffic"                                                                                                                                                                                          | 72  |

| 4.11 | RR+POLR causes starvation of OSBs (refer to $\sharp$ ) in an example 4x4 switch, 2x2 ISBs/OSBs (N=4,M=2,K=2)                                                                                                                                                                                     | 73  |

| 5.1  | Switch III: an $N \times N$ switch consists of $K$ ISBs, $K$ OSBs, ATMCSF, and dual round robin rings; $K = \frac{N}{m}$ , $m = M$ . Cell delivery is based on link reservation. Dual round robin rings provide a mechanism for ISBs to dynamically "borrow" and/or "lend" links from each other | 75  |

| 5.2  | Cell delivery is based on link reservation                                                                                                                                                                                                                                                       | 77  |

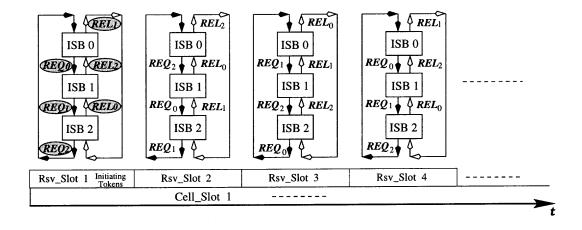

| 5.3  | Rsv_Slot (link reservation slot) vs. Cell_Slot (cell delivery slot) in an example switch consisting of 3 ISBs and 3 OSBs                                                                                                                                                                         | 78  |

| 5.4  | REQ-QOBDLR algorithm which is performed in every Rsv_Slot                                                                                                                                                                                                                                        | 79  |

| 5.5  | REQREL-QOBDLR algorithm which is performed in every Rsv_Slot. Assume that the $i^{th}$ ISB is receiving $REQ_j$ and $REL_n$ token in current Rsv_Slot                                                                                                                                            | 83  |

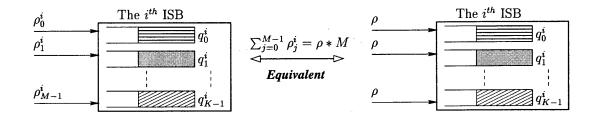

| 5.6  | An ideal traffic scenario : the aggregated input load to the $i^{th}$ ISB ( $0 \le i < K$ ) uniformly targets $K$ OSBs. Every ISB has the same traffic pattern                                                                                                                                   | 87  |

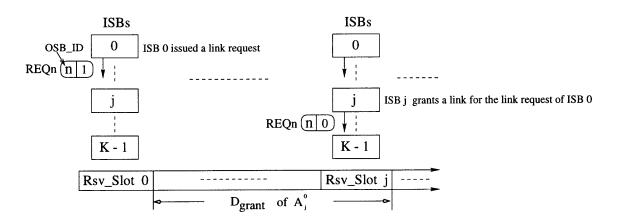

| 5.7  | $D_{grant}$ in REQ-QOBDLR Algorithm                                                                                                                                                                                                                                                              | 90  |

| 5.8  | How to get $P_r(q_n^i > c)$ , where c is a constant value                                                                                                                                                                                                                                        | 93  |

| 5.9  | Traffic Model : Multicast Burst Traffic                                                                                                                                                                                                                                                          | 96  |

| 5.10 | Switch III : throughput performance under unicast "1 ISB $\rightarrow$ 1 OSB HotSpot" traffic                                                                                                                                                                                                    | 103 |

| 5.11 | Switch III: average end-to-end cell delay $(D_{E-to-E})$ under unicast "1 ISB $\rightarrow$ 1 OSB HotSpot" traffic                                                                                                                                                                               | 103 |

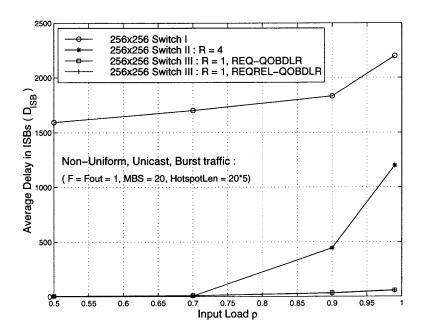

| 5.12 | Switch III : average delay in ISBs $(D_{ISB})$ under unicast "1 ISB $\rightarrow$ 1 OSB HotSpot" traffic                                                                                                                                                                                         | 104 |

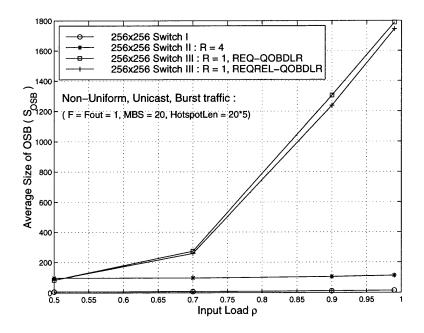

| 5.13 | Switch III : average size of OSBs $(S_{OSB})$ under unicast "1 ISB $\rightarrow$ 1 OSB HotSpot" traffic                                                                                                                                                                                          | 104 |

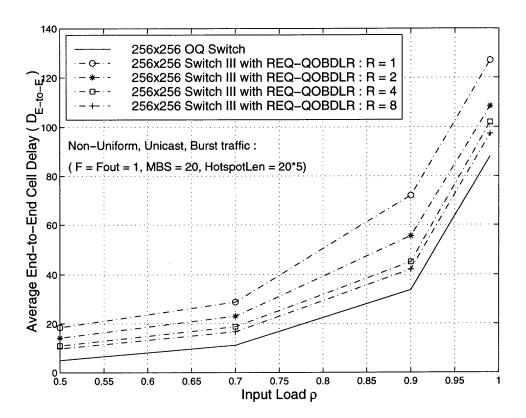

| 5.14 | $D_{E-to-E}$ in Switch III using REQ-QOBDLR algorithm with different link reservation rate (i.e. $R = \frac{Cell\_Slot}{Rsv\_Slot}$ ) under unicast "1 ISB $\rightarrow$ 1 OSB HotSpot" traffic                                                                                                  | 106 |

# LIST OF FIGURES (Continued)

| Figu | re l                                                                                                                                                                                                    | Page |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

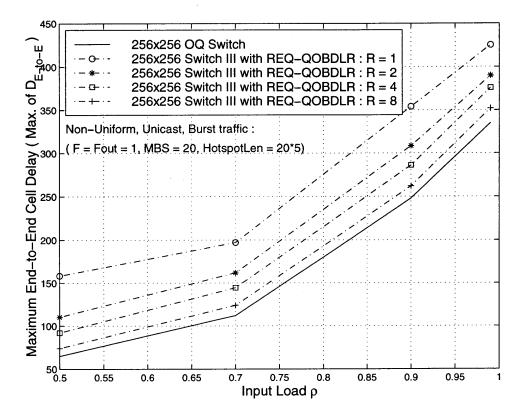

| 5.15 | Max. of $D_{E-to-E}$ in Switch III using REQ-QOBDLR algorithm with different link reservation rate (i.e. $R = \frac{Cell\_Slot}{Rsv\_Slot}$ ) under unicast "1 ISB $\rightarrow$ 1 OSB HotSpot" traffic | 107  |

| A.1  | When receiving $REQ_j$ token, the $i^{th}$ ISB decides whether to request an extra link for the $j^{th}$ OSB. The $i^{th}$ ISB uses $s_j^i$ to record a link request for the $j^{th}$ OSB               | 112  |

### CHAPTER 1

#### INTRODUCTION

### 1.1 Motivation

Internet today is under tremendous growth and enjoys its world wide success. The scalable and distributed nature of the Internet attracts more and more users and service providers. Meantime, many emerging applications demand increased bandwidth and generate a huge volume of traffic. It creates an unprecedented demand for core network capacity. Also, the exponential growth of traffic may cause several problems in the network such as congestion, unpredictable delay, insufficient reliability and low availability. Facing those challenges, the core switch/router is therefore required to be able to deliver higher performance in terms of large capacity, high speed, multicasting as well as the Quality of Service (QoS).

In a word, scalable multi-terabit multicast switches/routers are in demand. However, existing switches/routers, due to the bottleneck from either switch architecture or arbitration complexity, can reach a capacity on the order of gigabits per second but few of them is scalable to terabit capacity.

In this dissertation, we propose several switch architectures and scheduling algorithms to approach the desired scalable terabit multicast packet<sup>1</sup> switch.

### 1.2 Review

In the history of switch design [1] [2], various multicast ATM switches have been proposed in literature. As shown in Fig 1.1, switch fabric on which a switch architecture is built can be classified into three types: Banyan network, Crossbar network, and Clos network. Starlite switch [3], Turner's broadcast switch [4] and Lee's

1 In this dissertation, a packet has fixed length of 53 bytes.

multicast switch [5] were the typical multicast switches based on Banyan network. Later on, a practical version of Lee's switch is proposed in [6]. And another advanced switch with fault-tolerant multistage interconnection network (MIN) switch is presented in [7]. Those switches have an advantage of a reduced hardware complexity. But, internal path conflict and head of line (HOL) blocking are the challenges for those switches to achieve high performance and scalability. One of the switches built on Crossbar network is Knockout Multicast switch [8], which utilizes a concentrator in every output port to resolve output contention. Following Knockout Multicast switch, Crossbar switch [9], Shared Concentration and Output Queueing Multicast (SCOQ) [10], Multicast Output Buffered ATM Switch (MOBAS) [11], Abacus [12], and a growable multicast switch [13] were proposed. Crossbar switches can achieve high performance because of output queueing and output contention resolution. The tradeoff is the cost of hardware complexity and speedup required. Growable packet switch [14] and ring sandwich network [15] were the multicast ATM switches based on Clos network. [20] presents a performance study for a buffered Clos switch. In fact, Clos network belongs to MIN but it only has 3 stages. Since Clos network can provide multiple paths from an input port to an output port, internal path conflicts are relaxed. Clos network has better performance than Banyan network but it has higher hardware complexity.

Existing packet switches including above multicast switches are able to achieve Gigabit/sec capacity. But, few of them provides further scalability to Terabit/sec. Besides the restraint from switch fabric, queueing strategy and cooperated scheduling scheme have a great impact on switch scalability as well. From switch buffering point of view, switches can be classified into output-queued (OQ) switches<sup>2</sup>, input-queued (IQ) switches, and input-output-queued (IOQ) switches.

<sup>&</sup>lt;sup>2</sup>OQ switches include centralized shared memory switches.

| Switch<br>Proposed<br>Year | Based on<br>Crossbar network/<br>Knockout switch | Based on Bo                             | Based on Clos Network                             |                                            |

|----------------------------|--------------------------------------------------|-----------------------------------------|---------------------------------------------------|--------------------------------------------|

| 1984                       |                                                  | Starlit sw                              | itch (Huang et al.)                               |                                            |

| 1988                       | Multicast Knockout<br>switch (K.Y.Eng et al.)    | Turner's broadcast switch               | Lee's multicast switch                            |                                            |

| 1990                       | Gauss ASE<br>(R.J.F. Vries)                      |                                         | 1                                                 |                                            |

| 1991                       |                                                  | Sunshine switch (J.N.Giacopelli et al.) | Recursive multistage structure (R. Cusani et al.) | Growable packet switch (D.J.Marchok et al. |

| 1994                       | SCOQ switch<br>(D.X.Chen et al.)                 | LGMIN<br>(W.D. Zhong et al.)            | Multinet switch<br>(H.S. Kim)                     |                                            |

| 1995                       | MOE<br>(H.J. Ch                                  | BAS<br>nao et al.)                      |                                                   | Ring sandwich network<br>(Y.Yang et al.)   |

| 1997                       | 997 Abacus switch Gu (H.J. Chao et al.)          |                                         | Guo & Chang's<br>switch                           |                                            |

Figure 1.1 Review on multicast ATM switches

Fig 1.2 depicts a general model of an OQ switch. OQ switches, such as [8, 11, 12, 13, 16, 17, 18, 19, 21], proved to maximize throughput and optimize latency. Hence, OQ switches are able to provide Quality of Service (QoS) guarantees [22, 23, 24, 28]. But, switch fabric and output buffers have to operate N (N is the switch size in terms of the number of switch inputs/outputs) times as fast as the line rate, because cells arriving at switch inputs have to be delivered to and stored in output queues in a same cell slot. It may be practical to implement an output queued switch or router with an aggregated bandwidth of several 10Gb/s. But, it is not feasible to design a large OQ switch with fast line rate, because memory access speed achieved in commercial is not fast enough to support N times speedup.

On the other hand, IQ switches (see Fig 1.3) become more attractive because switch fabric and input memory only need to run as fast as the line rate. An IQ switch with FIFO queues is known to suffer head of line (HOL) blocking which limits the throughput to  $(2 - \sqrt{2}) = 58.6\%$ . To overcome HOL blocking, virtual

Figure 1.2 A general architecture of an output queued (OQ) switch

output queues (VOQs) are applied in every switch input together with scheduling algorithms like Longest Queue First (LQF)[30], Oldest Cell First (OCF)[31], Longest Port First (LPF) [32] to achieve 100% maximized throughput. To support multicast traffic, TATRA and WBA were proposed for IQ switches [33] [34]. A combined input output queued (CIOQ) switch has been proposed[35] and demonstrated that the CIOQ switch can precisely emulate the OQ switch when speedup  $S \geq 2 - \frac{1}{N}$ . In addition, [36] [37] [38] propose some priority queueing algorithms for integrated traffic.

**Figure 1.3** A general architecture of input queued (IQ) switch : (a) an IQ switch using FIFO queues ; (b) an IQ switch using VOQs .

Though IQ switches are capable of supporting high speed line rate without any speedup in hardware, scheduling arbitration complexity of at least  $O(N^{2.5})$  is a big obstacle if IQ switches grow to a large size. The reason is that, most scheduling algorithms proposed for IQ switches employ a centralized scheduler, which needs to collect traffic information from N switch inputs in every cell slot and consumes multiple iteration to determine the final input-output matching. Situation may become more complex under multicast traffic. As scheduling complexity increases with switch size N, an IQ switch using a centralized scheduler has difficulties in growing to a large switch size and terabit/sec capacity.

IOQ Switches are combinations of IQ switches and OQ switches (refer Fig 1.4). As comparison study in [39], OQ switches deserve the best throughput/delay performance for arbitrary traffic distributions. However, since the current memory access time is limited to a few nsec by state-of-the-art integrated circuit technology, output-buffered switch architecture is not scalable for large-capacity systems. On the other hand, IQ switches endures poor throughput/delay performance because of HOL blocking, but input-queued architecture is feasible to extend. The IOQ switch is a solution by trading off the high performance of the OQ switch and the low hardware complexity of the IQ switch.

One of few existing IOQ switch designs is CIOQ switch [35]. But, the reason for CIOQ switch in [35] to adopt both input queueing and output queueing is to provide QoS in IQ switches. As speedup is required in IQ switches for QoS purpose, output queueing is needed to avoid cell loss. CIOQ switch, in fact, can be classified as an IQ switch. The centralized scheduler sustains an arbitration complexity of  $O(N^{2.5})$  so that CIOQ switch [35] is not scalable. In addition, the modular batcher-binary-banyan switch [40] proposed by T.T.Lee and Sunshine switch [41] proposed

Input-Output (IOQ) Queued Switch

Figure 1.4 A general architecture of input-output queued (IOQ) switch

by Bellcore are also IOQ switches. But, because of irregular interconnection pattern in hardware, those switches are limited to up to 20Gb/s.

### 1.3 Design Issues

Several issues should be considered when we design a large-capacity switch. In this section, we mainly address following aspects which are targeted in our design of a scalable terabit multicast packet switch.

### 1.3.1 Multicasting

In today's B-ISDN and Internet, many services, such as teleconferencing, entertainment video, distributed data processing, are characterized by point(multipoint)to-multipoint communication. Switches need to support not only point-to-point connections, but also multipoint connections. Multicast switch is a solution for sending information from one sender to a group of receivers.

Multicast functions in ATM switches can be implemented either with a separate nonblocking copy network followed by a point-to-point routing network, or with an

·N

(a) a multicast switch consists of a copy network and a point-to-point switch

(b) a multicast switch with an integrated function of cell replication and cell routing.

Figure 1.5 Multicast switches

integrated switching fabric performing both replication and routing functions. Fig 1.5 illustrate the two alternatives.

The architecture of a nonblocking copy network followed by a traditional point-to-point ATM switching network is adopted by many commercially available switches [3, 4, 5, 6], because the traditional switch doesn't need to change completely but only adding a copy network ahead. Copy network replicates an input multicast cell <sup>3</sup> to the number of cell copies. Then the cell copy is routed to an output line through a point-to-point routing network. But, the copy network faces the problem of overflow which may cause performance degradation. In addition, there is an implementation redundancy by separating copy network and routing network. It increases hardware complexity.

Another architecture of multicast switch is shown in Fig 1.5(b). Cell duplication and cell routing are integrated together in implementations. For example, [7, 11, 12, 16, 17, 18, 19, 20, 43, 44] are the switches using either output buffer or shared-memory to handle the cell copy and to schedule cells at the same time. And the multicast IQ switches belong to this type of switch architecture. [28] is a typical shared-memory architecture combining cell duplication and cell delivery. Most

<sup>&</sup>lt;sup>3</sup>In this paper, the multicast cell is defined as a cell with one destination or multiple destinations.

recent switch designs adopt this integrated switch architecture to reduce hardware complexity and achieve an efficient buffer management as well.

### 1.3.2 Scalability

Scalability can be evaluated from two aspects — capacity and expandability. Internet applications continue to grow and create an ever-increasing demand for bandwidth. Switches have to be scalable to avoid being frequently re-architectured in order to support massive increase of traffic. Thus, core switches face an emerging challenge to provide more than 100Gb/s even Terabit/s capacity. Existing switches using current state-of-the-art technology can obtain a capacity up to several 10Gb/s, but are not easy to pursue Terabits/sec due to some constrains such as memory access rate or arbitration complexity. For example, shared-memory switches are optimal in performance and also cost effective. But, switch size and capacity of shared-memory is ruled by the fact that:

$$\frac{R*N*2}{\text{cell slot}} \leq \frac{1}{\text{RAM read/write cycle}}$$

(1.1)

where R is the input line rate, and N is the number of switch inputs (outputs). Bounded by the RAM read/write rate, it is observed that shared-memory switch is not able to gear to the high capacity expectation.

In addition to capacity, another necessary requirement for scalability is expandability. It considers whether switch architecture supports increased speeds or additional switch ports, and how flexible the switch can be to pursue an expanding configuration. The best solution would be a modular switch architecture.

### 1.3.3 Low Complexity

Both hardware complexity and scheduling arbitration complexity must be minimized. Hardware complexity is often measured in terms of logic gate counts, chip pinout, memory speed, implementation costs. From prototype design to real implementation, above concerns should be carefully evaluated. For example, the multicast switch using copy network usually has implementation redundancy and incurs high hardware costs. In addition, some switches such as the OQ switch are limited by the memory access speed because of the up to N times speedup required. The switch fabric with shuffle connection from N switch inputs to N switch outputs gains reliability but pays for high connection cost. In short, an efficient switch design should minimize the hardware complexity but without sacrificing reliability and performance.

Apart from hardware complexity, arbitration complexity should be low to gear up the hardware design. The IQ switch, for example, is better than the OQ switch in the aspect of hardware complexity. But, the IQ switch uses a centralized scheduler to resolve HOL blocking so that the IQ switch tolerant a high arbitration complexity of at least  $O(N^{2.5})$ . The arbitration complexity hinders the IQ switch to build a large scale switch.

In summary, we may need to trade off between the hardware complexity and arbitration complexity in order to pursue a good solution based on some specific design requirements.

### 1.3.4 High Performance

Switches should provide satisfactory performance. Bellcore has recommended performance requirements and objectives for a Broadband Switching Systems (BSS) [42]. Table 1.1 defines three classes of Quality of Service (QoS) and explains the associated performance objectives.

Table 1.1 Performance requirements and objectives for BSS [42]. \*: includes non-queueing related delays but excludes propagation, and does not include delays due to processing above ATM layer. N/S: not specified.

| Performance Parameters                            | CLP | QoS 1                | QoS 3                | QoS 4                |

|---------------------------------------------------|-----|----------------------|----------------------|----------------------|

| Cell Loss Ratio                                   | 0   | $< 10^{-10}$         | $ <10^{-7}$          | $< 10^{-7}$          |

| Cell Loss Ratio                                   | 1   | N/S                  | N/S                  | N/S                  |

| Cell Transfer Delay (99 percentile) *             | 1/0 | $150~\mu \mathrm{s}$ | $150~\mu\mathrm{s}$  | $150~\mu \mathrm{s}$ |

| Cell Delay Variation ( $10^{-10}$ quantile)       | 1/0 | $250~\mu \mathrm{s}$ | N/S                  | N/S                  |

| Cell Delay Variation (10 <sup>-7</sup> quantile ) | 1/0 | N/S                  | $250~\mu \mathrm{s}$ | $250~\mu \mathrm{s}$ |

QoS class 1 is dedicated to cell loss sensitive applications. It corresponds to AAL layer class A service which is defined by ITU-T XIII Group and ATM Forum. QoS class 3 is applied for low latency, connection-oriented data transfer applications which is intended for AAL class C service. In addition, QoS class 4 is related to low latency, connectionless data transfer applications which is for AAL class D service.

The performance parameters include *cell loss ratio*, *cell transfer delay*, and *cell delay variation*. The performance objectives associated to a QoS class are determined by the status of the cell loss priority (CLP) bit in the ATM cell header. End users can initialize the CLP bit but switches along the connection path can change it according to network conditions.

For all three QoS classes, the probability of cell transfer delay greater than  $150\mu s$  is guaranteed to be less than 1 percent, i.e. :

Pr. [ cell transfer delay

$$> 150 \ \mu s$$

]  $< 0.01$

The probability of cell delay variation (CDV) greater than  $250\mu$ s is required to be less than  $10^{-10}$  for QoS class 1, and to be less than  $10^{-7}$  for QoS class 3/4.

In addition to above performance objectives, switches need to be flexible to cooperate other technologies such as connection admission control, buffer management, traffic engineering in order to provide Quality of Service (QoS) guarantees.

### 1.4 Outline

Our goal is to design a scalable terabit multicast packet switch which is capable of multicasting, large capacity, low complexity, modular configuration, and high performance. In this dissertation, we propose three switch architectures with cooperated scheduling algorithms — namely Switch I, Switch II, and Switch III, to achieve the desired switch. Our designs benefit from unique features of modular switch architecture and distributed scheduling arbitration.

In chapter 2, we first present a theoretical work on the performance of copy network under three scenarios: (1) Non-Buffer-NonSplitting copy network (NBNS). (2) Shared-Input-Buffer-NonSplitting copy network (SIBNS). (3) Shared-Input-Buffer-Splitting copy network (SIBS). For NBNS, we derived the exact overflow and cell loss probabilities instead of the Chernoff Bound [5]. Furthermore, we propose a general Markov Model, a novel theoretical approach, for the performance analysis of the Shared-Input-Buffer copy networks. This analysis method can be applied for both SIBNS and SIBS. Theoretical and simulation results are compared for every scenario.

In chapter 3, we propose a novel switch design, namely Switch I, using input and output link sharing. Switch inputs and outputs are grouped into small modules called Input Shared Blocks (ISBs) and Output Shared blocks (OSBs). Link sharing resolves output contention and eliminates the speedup requirement for central switch fabric.

Two Round Robin (RR) scheduling algorithms are proposed. Both schemes provide a group mapping from an ISB to an OSB. Scheduling complexity is dramatically reduced. The switch can easily extend to high capacity and large scale. Performance evaluation demonstrates that the switch can achieve good performance under uniform multicast<sup>4</sup> traffic. However, isolated Input Shared Blocks (ISBs) prevent switch from achieving high performance under non-uniform traffic.

To overcome the weakness of Switch I, in chapter 4, we present Switch II, a modified switch design using link sharing and prioritized link reservation. ISBs are connected by a token ring. We propose a Round Robin Prioritized Output Link Reservation (RR+POLR) algorithm to allocate link resource and alleviate starvation of OSBs. Switch II obtains an improved performance under non-uniform traffic. But, RR+POLR algorithm is not flexible enough to adapt the dynamic traffic timely. Switch performance is highly determined by how fast link reservation rate the switch can pursue.

Switch III, as an enhanced switch design using link sharing and dual round robin dynamic link reservation, is finally proposed in chapter 5. Unlike the previous two switches, ISBs are connected by dual rings on which K link request tokens (REQs) and K link release tokens (RELs) circulate in a round robin manner. Cell delivery is based on link reservation in every ISB. We propose two Queue Occupancy Based Dynamic Link Reservation (QOBDLR) algorithms to achieve a fast and fair link resource allocation among ISBs. QOBDLR is a distributed link reservation scheme in a way that every ISB, according to its local information, can dynamically increase/decrease its link reservation by "borrowing" or "lending" links from/to each other. Arbitration complexity is O(1). Switch III is competitive to OQ switches in

<sup>&</sup>lt;sup>4</sup>In this work, multicast traffic includes unicast traffic, i.e., a multicast cell may have one or multiple destinations.

the sense that Switch III not only can achieve a comparable performance to OQ switches under any traffic pattern but also can eliminate N times speedup required in OQ switches.

At last, conclusion is drawn and future work is addressed in chapter 6.

### CHAPTER 2

### A NOVEL PERFORMANCE ANALYSIS FOR THE COPY NETWORK IN A MULTICAST ATM SWITCH

### 2.1 Introduction

To accommodate the growing demands for a wide class of services, such as voice, data, teleconferencing and entertainment video, a broadband packet network needs to support not only point-to-point connections, but also multipoint connections. Multicast switching is a solution for delivering information from a given source to a group of destination.

A conventional architecture of multicast ATM switches consists of a nonblocking copy network followed by a traditional point-to-point ATM switching network [4][5][26][47][49]. It provides point-to-multipoint connections by performing two operations: packet replication and packet switching. The function of copy network replicates an incoming cell to the number of required copies.

By applying a self-routing non-blocking fabric, the copy network does not have any internal conflict. But, the copy network faces the problem of overflow if the total copies required exceed the number of output lines of the network. Various scheduling algorithms [47][50][52] to maximize throughput of the copy network were proposed. They introduce additional buffers (input/output/central buffer) and/or scheduling algorithms (one-shot, splitting, etc.), in order to maximize the number of cell copies injected to the point-to-point switching network.

In this chapter, we present a theoretical work on the performance of the copy network in three typical scenarios (shown in Fig 2.1). In Non-Buffer Non-Splitting (NBNS) copy network (Fig 2.1(a)), all the copies required by a multicast cell are replicated in the same time slot. The copy network has no inside buffer to save blocked cells. NBNS causes high cell loss. To prevent the blocked cells from being

Figure 2.1 Three scenarios of copy network in a multicast ATM switch

lost, we introduce a shared input buffer in the copy network. Two scheduling algorithms are considered for the Shared-Input-Buffer copy network: Non-Splitting algorithm (SIBNS) (Fig 2.1(b)), all the copies required by a multicast cell are replicated in a same time slot; Splitting algorithm (SIBS) (Fig 2.1(c)), a multicast cell can be partially copied in a time slot, and the remains can be delayed to the next time slot.

For NBNS, we derived the exact overflow and cell loss probabilities instead of the Chernoff Bound [5]. Furthermore, we propose a novel theoretical approach based on a general Markov model, for the performance analysis of the Shared-Input-Buffer copy networks. This analysis method can be applied for both SIBNS and SIBS. Both theoretical analysis and simulation results are presented for every scenario. The comparison shows that shared-input-buffer (SIBNS and SIBS) can obtain an improved performance with lower cell loss and higher throughput. However, the tradeoff is long cell delay. With the splitting algorithm, SIBS can provide better performance than NBNS and SIBNS.

This chapter is organized as follows. In Section 2.2, we provide several notations and assumptions that we use throughout this chapter. Section 2.3 presents performance analysis for NBNS copy network. In Section 2.4, we propose a general Markov Model for the performance analysis of both SIBNS and SIBS copy networks. The analysis model is examined by the numerical and simulation results. Conclusions are finally drawn in Section 2.5.

### 2.2 Notation and Assumptions

We assume that: (1) input lines are independent and identically distributed; (2) cells' arrival is Poisson process. If an input line has cells arriving, this input line is an active line, otherwise, it's an idle line.

N: size of the copy network. (for 8 inputs/8 outputs copy network, N=8);

$C_{max}$ : the maximum number of copies allowed for every multicast cell,  $0 < C_{max} \le N$ ;

C: random variable, represents the number of copies required. Assumed to be uniformly distributed;

$C_k$ : Probability that the number of copies is k, i.e. pdf of random variable C;

$$C_k = P(C = k) = \frac{1}{C_{max}}, \quad k = 1, 2, \dots C_{max}$$

(2.1)

$P_{in}$ : Probability that an input line is active,

$$P_{in} = P(\text{the number of arriving cells} > 0) = 1 - e^{-\lambda t}$$

(2.2)

$CP_i$ : random variable, i.e. the number of copies required by the  $i^{th}$  multicast cell in the processing queue;

$CP_i(k)$ : Probability that the  $i^{th}$  multicast cell in the processing queue (or the multicast cell on the  $i^{th}$  input line) needs k copies,  $k = 0, 1, 2, ..., C_{max}$ ,

$$CP_i(k) = \begin{cases} 1 - P_{in} & \text{if } k = 0\\ P_{in}C_k & \text{if } k = 1, 2, \dots, C_{max} \end{cases}$$

(2.3)

$\mathbf{E}[\lambda]$ : average input load from N input lines;

$$E[\lambda] = \sum_{i=0}^{N} i P(IN = i)$$

$$= \sum_{i=0}^{N} i * {N \choose i} P_{in}^{i} (1 - P_{in})^{N-i}$$

(2.4)

P(IN = i) is the probability that there are i multicast cells arriving from N input lines in a time slot.

# 2.3 Performance Analysis of NBNS Copy Network

Assume that, in every cell slot, the copy network serves incoming multicast cells from the  $1^{st}$  input line to the  $N^{th}$  input line (i.e., top-down order). If the total number of desired cell copies exceeds the size of the copy network, some multicast cell(s) arrived at the later input lines will be discarded.

$P_{ovfl}(i)$ : Overflow probability of the  $i^{th}$  input line. When total copies required by the multicast cells of the first i active input lines exceeds the size of the copy network, overflow occurs in the  $i^{th}$  input line. The multicast cell on the  $i^{th}$  input line cannot be copied in this time slot.

$$P_{ovfl}(i) = P(CP_1 + CP_2 + \dots + CP_i > N)$$

$$= \sum_{j=N+1}^{i*C_{max}} P(CP_1 + CP_2 + \dots + CP_i = j)$$

(2.5)

$P(CP_1 + CP_2 + \cdots + CP_i = j)$  can be obtained by the convolution of  $CP_i(k)$ .

$P_{lost}$ : The average cell loss probability. Overflow results in cell loss. The first input line which may overflow starts is the  $(\lfloor \frac{N}{C_{max}} \rfloor + 1)^{th}$  input.

$$P_{lost} = \sum_{i=\lfloor \frac{N}{C_{max}} \rfloor + 1}^{N} P(\text{the } i^{th} \text{ input line is active}) * P(i^{th} \text{ input line is overflow})$$

$$= \frac{1}{N} \sum_{i=\lfloor \frac{N}{C_{max}} \rfloor + 1}^{N} P_{ovfl}(i)$$

(2.6)

Throughput: The average number of multicast cells successfully passing through the copy network per time slot;

$$Throughput = E[\lambda] * (1 - P_{lost}) = \left[\sum_{i=0}^{N} iP(IN = i)\right] (1 - P_{lost})$$

(2.7)

The performance of NBNS copy network is examined in Fig 2.2, Fig 2.3 by simulation (+) and numerical (-.) results. Fig 2.2 shows the overflow probability of

each input line. There is an unfairness: the later input line will have higher overflow probability. Our analysis provides an exact overflow probability, while the Chernoff Bound [5] is much looser. Fig 2.3 illustrates cell loss and throughput. Large copy load  $(C_{max})$  and heavy input load  $(P_{in})$  incur more cell loss and less throughput. NBNS does not introduce any cell delay in copy network.

Figure 2.2 Overflow probability in NBNS

# 2.4 Performance Analysis for both SIBNS and SIBS Copy Networks

To improve the performance of copy network, a solution is to apply additional buffers [47][48][50][51]. In this paper, we focus on the shared input buffer with two scheduling methods (NonSplitting and Splitting algorithms).

SIBNS: In Shared-Input-Buffer Non-Splitting scenario, cell copies belonged to a same multicast cell should be delivered in a same cell slot. Otherwise, the multicast

Figure 2.3 Cell loss and throughput in NBNS

cell is blocked in the shared buffer with whole copy requirements. Buffered cells have higher priority to be served than a new arriving cell.

SIBS: In Shared-Input-Buffer Splitting scenario, the copy network can make partial copies for a multicast cell. The splitted cell is saved into shared buffer with remained copy requests.

## 2.4.1 Notation and Assumption

$BUF_{max}$ : the maximum size of the shared input buffer.

$BUF_m$ : the length of the shared input buffer at the end of the  $m^{th}$  time slot.

$IN_m$ : the number of new arriving cells from N inputs in the  $m^{th}$  time slot. In every time slot, at most 1 cell comes into the copy network from each input line.

$$P(IN_m = n) = \binom{N}{n} P_{in}^n (1 - P_{in})^{N-n}$$

(2.8)

$OUT_m$ : the number of multicast cells successfully delivered out of the copy network in the  $m^{th}$  time slot. In a time slot, at most N multicast cells can go through the copy network (when each cell just needs 1 copy). The probability distribution of  $OUT_m$  is:

$$P(OUT_m = n) \stackrel{\text{def}}{=} P(CP_1 + CP_2 + \dots + CP_n \le N)$$

(2.9)

$LOST_m$ : the number of cells lost in the  $m^{th}$  time slot.

$$LOST_m = BUF_{m-1} + IN_m - OUT_m - BUF_{max}; \text{ where } LOST_m \ge 0$$

(2.10)

# 2.4.2 The Proposed Markov Model

In Fig 2.4, we propose a general Markov Model for SIBNS and SIBS. Each state indicates current queue length in the shared buffer, i.e., how many multicast cells are waiting in the shared memory.

NOTE: Pij is the state transition probability. Pij = 0 if |i-j| > N

Figure 2.4 The general Markov Model for both SIBNS and SIBS

The model we propose is unique in the sense that each multicast cell occupies only one unit in the buffer, no matter how many copies it requires. It can be applied to many different scheduling algorithms, buffer and copy network sizes.

**2.4.2.1** State Transition Probabilities  $P_{i,j}$ : Let  $P_{i,j}$  be the state transition probability from state i to state j. We have a State Transition Probability Matrix  $\hat{P}_t$  shown in Fig 2.5. Note, the maximum number of states jumped in a cell slot is constrained by the size of the copy network, i.e.  $P_{ij} = P(BUF_m = j|BUF_{m-1} = i)$ , where  $|i - j| \leq N$ .

To figure out the state transition probability matrix  $\hat{P}_t$ , we separately look for three main parts as :

•  $P_{i,0}$ , where  $0 \le i \le BUF_{max}$ ;

$$P_{i,0} = P(BUF_m = 0 | BUF_{m-1} = i) = \sum_{n=0}^{N-i} P(IN = n)P(OUT = i + n)$$

where  $0 \le i \le BUF_{max}$ , and  $i + n \le N$  (2.11)

$$P(OUT = i + n) = P(CP_1 + \dots + CP_{i+n} \le N)$$

Figure 2.5 State transition probability matrix of Markov chain :  $\hat{P}_t$

$$= 1 - P(CP_1 + \dots + CP_{i+n} > N)$$

(2.12)

•  $P_{i,j}$ , where  $0 < j < BUF_{max}$ ,  $|i - j| \le N$ ;

$$P_{i,j} = P(BUF_m = j | BUF_{m-1} = i)$$

$$= \sum_{n=max\{0,(j-i)\}}^{min\{N,(N+j-i)\}} P(IN = n)P(OUT = i + n - j)$$

(2.13)

where  $\max\{0,\,(j-N)\} \leq i \leq \min\{N+j,BUF_{max}\},$  and  $i+n-j \leq N$  .

$$P(OUT = i + n - j) = P(CP_1 + CP_2 + \dots + CP_{i+n-j} \le N)$$

$$*P(CP_1 + \dots + CP_{i+n-j} + CP_{i+n-j+1} > N)$$

$$\vdots$$

$$*P(CP_1 + \dots + CP_{i+n-j} + \dots + CP_{min\{N,(i+n)\}} > N)$$

$$= P(CP_1 + \dots + CP_{i+n-j} \le N) *$$

$$\min_{k=i+n-j+1} P(CP_1 + CP_2 + \dots + CP_k > N)$$

(2.14)

The derivation of P(OUT = i+n-j), here, has additional concerns. First of all, it should not be overflow for the first (i+n-j) multicast cells, i.e.  $P(CP_1+CP_2+\cdots+CP_{i+n-j} \leq N)$ . However, it must be overflow for any first k  $(k \geq i+n-j)$  multicast cells in the buffer, i.e.  $\prod_{k=i+n-j+1}^{\min\{N,(i+n)\}} P(CP_1+CP_2+\cdots+CP_k > N)$ .

•  $P_{i,BUF_{max}}$ , where  $0 \le i \le BUF_{max}$ ,  $LOST \ge 0$ ;

$$P_{i,BUF_{max}} = P(BUF_m = BUF_{max}|BUF_{m-1} = i)$$

$$= \sum_{n=(BUF_{max}-i)}^{N} P(IN = n)P_{out}$$

$$= \sum_{n=(BUF_{max}-i)}^{N} P(IN = n) \left[ \sum_{l=\lfloor \frac{N}{C_{max}} \rfloor}^{n+i-BUF_{max}} P(OUT = l) \right] (2.15)$$

$$P(OUT = l) = P(CP_1 + \dots + CP_l \le N) * \prod_{k=l+1}^{N} P(CP_1 + \dots + CP_k > N);$$

$$Note, P(OUT < \lfloor \frac{N}{C_{max}} \rfloor) = 0.$$

From  $P_{i,0}$ ,  $P_{i,j}$  and  $P_{i,BUF_{max}}$ , we finally obtain the state transition probability matrix  $\hat{P}_t$ .

**2.4.2.2** State Probabilities  $P_i$ :  $P_i$  is the steady state probability of the Markov Chain, i.e, the probability that the buffer length is i. Let  $\Pi$  be a vector of the stationary state probability,  $\Pi = [P_0, P_1, \dots, P_{BUF_{max}}]$ . We have,

$$\Pi = \Pi * \hat{P}_t \ and \ \sum_{i=0}^{BUF_{max}} P_i = 1$$

(2.16)

From Eq. 2.16, we get the stationary state probability  $P_i$ , where  $0 \le i \le BUF_{max}$ .

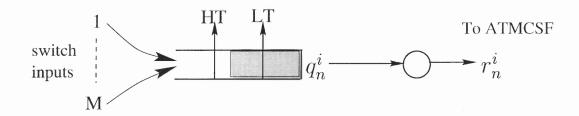

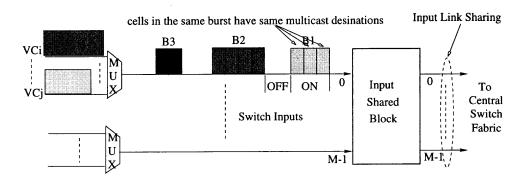

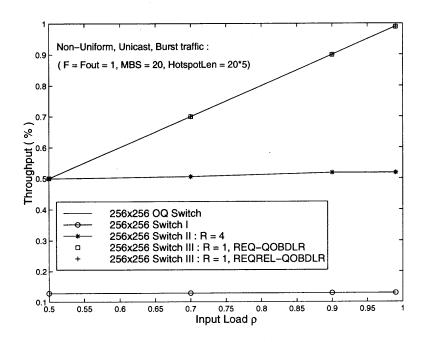

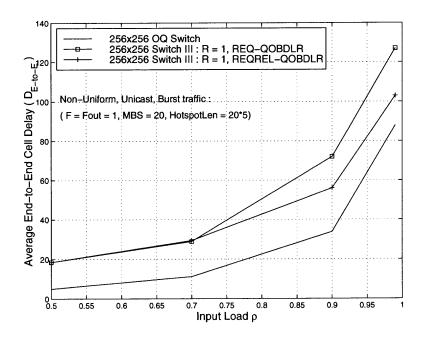

## 2.4.3 Performance Analysis