# **Copyright Warning & Restrictions**

The copyright law of the United States (Title 17, United States Code) governs the making of photocopies or other reproductions of copyrighted material.

Under certain conditions specified in the law, libraries and archives are authorized to furnish a photocopy or other reproduction. One of these specified conditions is that the photocopy or reproduction is not to be "used for any purpose other than private study, scholarship, or research." If a, user makes a request for, or later uses, a photocopy or reproduction for purposes in excess of "fair use" that user may be liable for copyright infringement,

This institution reserves the right to refuse to accept a copying order if, in its judgment, fulfillment of the order would involve violation of copyright law.

Please Note: The author retains the copyright while the New Jersey Institute of Technology reserves the right to distribute this thesis or dissertation

Printing note: If you do not wish to print this page, then select "Pages from: first page # to: last page #" on the print dialog screen

The Van Houten library has removed some of the personal information and all signatures from the approval page and biographical sketches of theses and dissertations in order to protect the identity of NJIT graduates and faculty.

### ABSTRACT

#### ON SCHEDULING INPUT QUEUED CELL SWITCHES

### by Shizhao Li

Output-queued switching, though is able to offer high throughput, guaranteed delay and fairness, lacks scalability owing to the speed up problem. Input-queued switching, on the other hand, is scalable, and is thus becoming an attractive alternative. This dissertation presents three approaches toward resolving the major problem encountered in input-queued switching that has prohibited the provision of quality of service guarantees.

First, we proposed a maximum size matching based algorithm, referred to as min-max fair input queueing (MFIQ), which minimizes the additional delay caused by back pressure, and at the same time provides fair service among competing sessions. Like any maximum size matching algorithm, MFIQ performs well for uniform traffic, in which the destinations of the incoming cells are uniformly distributed over all the outputs, but is not stable for non-uniform traffic. Subsequently, we proposed two maximum weight matching based algorithms, longest normalized queue first (LNQF) and earliest due date first matching (EDDFM), which are stable for both uniform and non-uniform traffic. LNQF provides fairer service than longest queue first (LQF) and better traffic shaping than oldest cell first (OCF), and EDDFM has lower probability of delay overdue than LQF, LNQF, and OCF. Our third approach, referred to as store-sort-and-forward (SSF), is a frame based scheduling algorithm. SSF is proved to be able to achieve strict sense 100% throughput, and provide bounded delay and delay jitter for input-queued switches if the traffic conforms to the (r, T) model.

## ON SCHEDULING INPUT QUEUED CELL SWITCHES

by Shizhao Li

A Dissertation Submitted to the Faculty of New Jersey Institute of Technology in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy

Department of Electrical and Computer Engineering

May 1999

## Copyright © 1999 by Shizhao Li ALL RIGHTS RESERVED

.....

S.F

## APPROVAL PAGE

## ON SCHEDULING INPUT QUEUED CELL SWITCHES

## Shizhao Li

| Dr. Nirwan Ansari, Dissertation Advisor                           | Date  |

|-------------------------------------------------------------------|-------|

| Professor of Electrical and Computer Engineering, NJIT            |       |

|                                                                   |       |

|                                                                   |       |

|                                                                   |       |

|                                                                   |       |

|                                                                   |       |

| Dr. John Carpinelli, Committee Member                             | Date  |

| Associate Professor of Electrical and Computer Engineering, NJIT  |       |

| 1 3 3 3 3 3 3 3                                                   |       |

|                                                                   |       |

|                                                                   |       |

|                                                                   |       |

|                                                                   |       |

| Dr. Xiaoqiang Chen, Committee Member                              | Date  |

| Member of Technical Staff, Bell Labs, Lucent Technologies, Holmde | l, NJ |

|                                                                   |       |

|                                                                   |       |

|                                                                   |       |

|                                                                   |       |

| Dr. Sirin Tekinay, Committee Member                               | Date  |

| Assistant Professor of Electrical and Computer Engineering, NJIT  | Duit  |

| Assistant Professor of Electrical and Computer Engineering, 14311 |       |

|                                                                   |       |

|                                                                   |       |

|                                                                   |       |

|                                                                   |       |

| Dr. Bulent Yener, Committee Member                                | Date  |

| Assistant Professor of Computer and Information Science, NJIT     |       |

| <b>.</b>                                                          |       |

## **BIOGRAPHICAL SKETCH**

Author: Shizhao Li

**Degree:** Doctor of Philosophy

Date: May 1999

## Undergraduate and Graduate Education:

- Doctor of Philosophy in Electrical Engineering, New Jersey Institute of Technology, Newark, NJ, 1999

- Master of Science in Electrical Engineering, Beijing University of Posts and Telecommunications, Beijing, P. R. China, 1994

- Bachelor of Science in Electrical Engineering, Shandong University, Jinan, Shandong, P. R. China, 1991

## Major: Electrical Engineering

## **Presentations and Publications:**

- S. Li, J. G. Chen, and N. Ansari, "Fair queueing for input-buffered ATM switches," ICATM'98, France, pp. 252-259, Jun., 1998.

- R. Venkateswaran, S. Li, X. Chen, C.S. Raghavendra, and N. Ansari, "Enhanced VC merging mechanisms for multipoint to multipoint communications," ICCCN'98, Lafayette, Louisiana, pp. 4-11, Oct. 1998.

- S. Li, and N. Ansari, "Scheduling input-queued switches with QoS features," ICCCN'98, Lafayette, Louisiana, pp. 107-112, Oct. 1998.

- S. Li, and N. Ansari, "Provisioning QoS features for input-queued switches," IEE Electronics Letters, vol. 34, no. 19, pp. 1826-1827, Sept. 17.

- S. Li, and N. Ansari, "Input queued switching with QoS guarantees," INFOCOM'99, New York, New York, pp. 1152-1159, Mar., 1999.

- S. Li, J. Li, and N. Ansari, "Earliest Due Date First Matching for Input-Quered Cell Switches," CISS'99, Baltimore, MD, Mar. 1999.

This work is dedicated to my family

#### ACKNOWLEDGMENT

I would like to thank my advisor Dr. Nirwan Ansari for his continuous guidance, support and encouragement throughout my graduate study at NJIT. I greatly appreciate the knowledge and insightful comments he has been providing to me. I feel fortunate that I had a chance to conduct research under such an excellent advisor. Dr. Xiaoqiang Chen gave me so much help when I worked at Lucent Technologies as a summer intern, and he continues to give me advice. I am honored to express my gratitude to him. I would also like to thank Dr. John Carpinelli, Dr. Sirin Tekinay, and Dr. Bulent Yener for serving on my dissertation committee.

I would also like to thank Dr. Jianguo Chen for all the helpful discussions. Dr. R. Venkateswaran helped me understand many problems when I worked with him at Lucent Technologies. I thank Dr. Xueming Lin and Dr. Huaping Liu for helping me familiarize with the working environment when I first came to the Center for Communications and Signal Processing.

## TABLE OF CONTENTS

| $\mathbf{C}$ | Pag |                                                                          |      |

|--------------|-----|--------------------------------------------------------------------------|------|

| 1            | INT | RODUCTION                                                                | . 1  |

|              | 1.1 | Buffering Schemes and its Effects on the Design<br>of Traffic Scheduling | . 1  |

|              | 1.2 | Design Criteria for a Traffic Scheduler                                  | . 4  |

|              | 1.3 | Traffic Scheduling in Input-Queued Switches                              | . 5  |

|              |     | 1.3.1 Maximum Size Matching Based Algorithms                             | . 6  |

|              |     | 1.3.2 Maximum Weight Matching Based Algorithms                           | . 9  |

|              | 1.4 | Traffic Scheduling in Output-Queued Switches                             | . 11 |

|              |     | 1.4.1 Representative Work-conserving Schedulers                          | . 11 |

|              |     | 1.4.2 Representative Non-work-conserving Schedulers:                     | . 16 |

|              | 1.5 | Traffic Scheduling in Combined Input Output Queued Switches              | . 17 |

|              |     | 1.5.1 Algorithm Description                                              | . 18 |

|              | 1.6 | Contributions of the Dissertation                                        | . 20 |

| 2            | MIN | -MAX FAIR INPUT QUEUEING (MFIQ)                                          | . 23 |

|              | 2.1 | Queueing Analysis                                                        | . 24 |

|              | 2.2 | Min-max Fair Input Queueing Algorithm                                    | . 28 |

|              | 2.3 | Simulation Results and Performance Comparison                            | . 31 |

| 3            | MA  | XIMUM WEIGHT MATCHING                                                    | . 35 |

|              | 3.1 | Switch and Traffic Models                                                | . 36 |

|              | 3.2 | Longest Normalized Queue First (LNQF) Algorithm                          | . 38 |

|              |     | 3.2.1 Algorithm Description                                              | . 38 |

|              |     | 3.2.2 Analysis of Stability                                              | . 40 |

|              | 3.3 | Earliest Due Date First Matching (EDDFM) Algorithm                       | . 46 |

|              | 3.4 | Performance Comparison of Proposed Algorithms                            | . 47 |

| 4            | STC | DRE-SORT-AND-FORWARD (SSF)                                               | . 50 |

## Chapter

## Page

|   | 4.1 | The S              | tore-Sort-and-Forward Algorithm               | 52 |

|---|-----|--------------------|-----------------------------------------------|----|

|   |     | 4.1.1              | Framing Strategy and Cell Admission Policy    | 52 |

|   |     | 4.1.2              | The Sorting Algorithm                         | 54 |

|   | 4.2 | Algori             | thm Analysis                                  | 59 |

|   |     | 4.2.1              | Guaranteed QoS                                | 59 |

|   |     | 4.2.2              | Complexity Issues                             | 63 |

| 5 | CON | NTRIB <sup>.</sup> | UTIONS ON ATM MULTICASTING                    | 70 |

|   | 5.1 | Soluti             | ons to the Sender Identification Problem      | 72 |

|   |     | 5.1.1              | Mechanisms that Prevent Cell Interleaving     | 73 |

|   |     | 5.1.2              | Mechanisms that Support ATM Cell Interleaving | 74 |

|   | 5.2 | Comp               | arison between VC-Merge and VP-Merge          | 76 |

|   |     | 5.2.1              | Simulation Study                              | 77 |

|   |     | 5.2.2              | Summary of the Results                        | 80 |

|   | 5.3 | Impro              | wed VC-Merge Mechanisms                       | 80 |

|   |     | 5.3.1              | Multiple VC-merge Mechanisms                  | 81 |

|   |     | 5.3.2              | Simulation Results                            | 85 |

|   | 5.4 | Concl              | usions                                        | 88 |

| 6 | SUN | IMAR               | Y AND FUTURE RESEARCH                         | 89 |

## LIST OF TABLES

## Table

| 1.1 | Comparison of representative work-conserving schedulers for output-<br>queued switches. $L_i$ is the maximum packet size of session <i>i</i> , $L_{max}$ is<br>the maximum packet size among all the sessions, <i>R</i> is the transmission<br>rate of the switch, and $\sigma_i$ is the bucket depth of session <i>i</i> | 15 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2 | Performance of representative non-work-conserving schedulers for output-<br>queued switches. $T$ is the frame size and $\theta$ is the constant delay between<br>an arriving frame and its corresponding departing frame                                                                                                  | 18 |

| 2.1 | Statistics of the simulation results: $d_i$ is the delay of session $i$ and $r_i$ is the rate of session $i$ . $F_S$ is the instantaneous fairness of the algorithm. $D_{max}$ is the maximum additional delay caused by contentions while $Lag_{max}$ is the maximum normalized service lag of the algorithm             | 33 |

| 3.1 | Statistics of the simulation results: $d_{i,j}$ is the average delay of the <i>j</i> th session in VOQ $(1, i)$                                                                                                                                                                                                           | 48 |

## LIST OF FIGURES

| Figu | Ire P                                                                                                              | age |

|------|--------------------------------------------------------------------------------------------------------------------|-----|

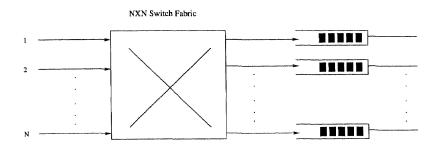

| 1.1  | Output buffering architecture                                                                                      | 2   |

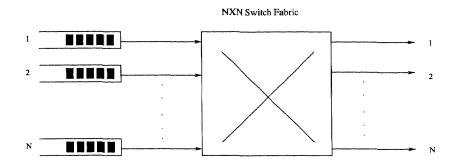

| 1.2  | Input buffering architecture                                                                                       | 3   |

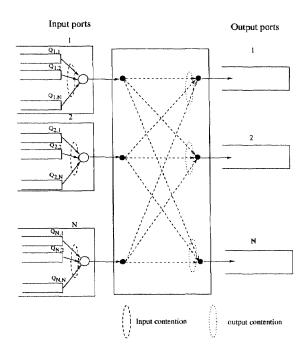

| 1.3  | Virtual output queueing and input/output contentions                                                               | 6   |

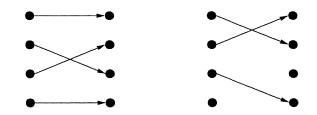

| 1.4  | An example of a bipartite graph                                                                                    | 7   |

| 1.5  | Two possible matches of a bipartite graph                                                                          | 8   |

| 1.6  | One iteration of the Iterative Round Robin Scheduling algorithm                                                    | 9   |

| 1.7  | A bipartite graph matching example:(a) the request graph, (b) a maximum weight match, and (c) a maximum size match | 10  |

| 2.1  | Virtual output queueing                                                                                            | 25  |

| 2.2  | The discrete time Markov chain for the total queue length of one queue group                                       | 26  |

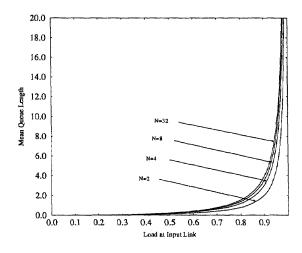

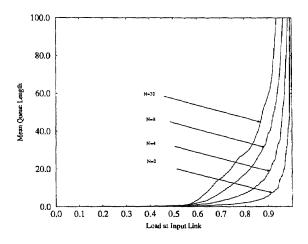

| 2.3  | Mean queue length of a queue group with ideal throughput                                                           | 27  |

| 2.4  | Mean queue length of a queue group simulation results                                                              | 28  |

| 2.5  | The pseudo-code of the min-max fair input queueing algorithm                                                       | 30  |

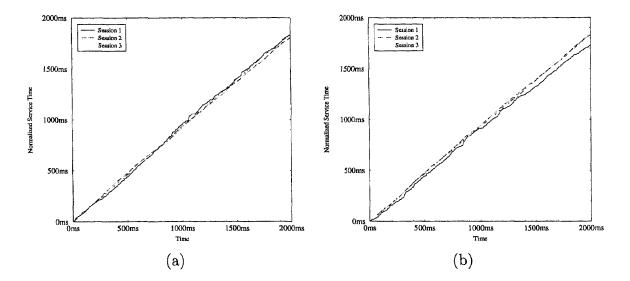

| 2.6  | Comparison of normalized service time received by the three sessions: (a) MFIQ, and (b) reference scheduler        | 31  |

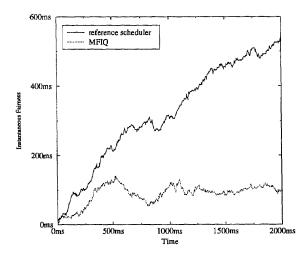

| 2.7  | Instantaneous fairness: MFIQ versus reference scheduler                                                            | 32  |

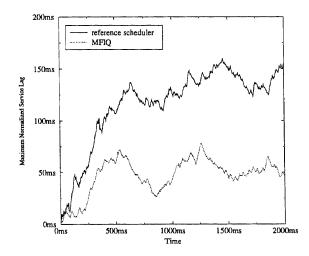

| 2.8  | Maximum normalized service lag: MFIQ versus reference scheduler                                                    | 34  |

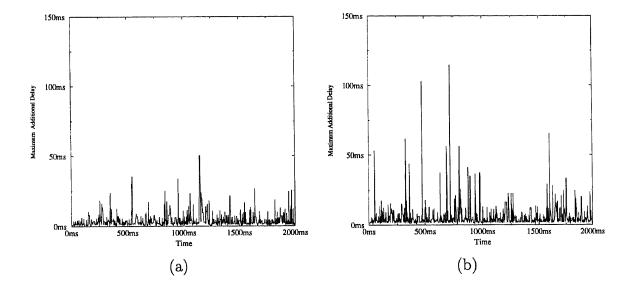

| 2.9  | Comparison of maximum additional delay: (a) MFIQ, (b) reference<br>scheduler                                       | 34  |

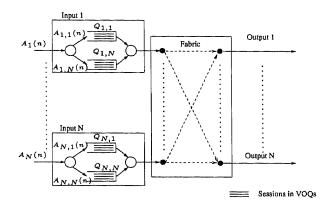

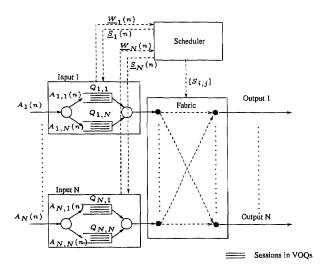

| 3.1  | Input-queue switch model                                                                                           | 37  |

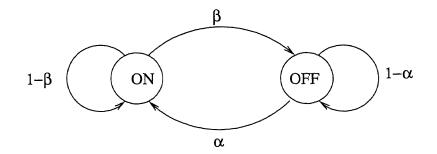

| 3.2  | Simple ON-OFF traffic model                                                                                        | 38  |

| 3.3  | LNQF scheduler                                                                                                     | 40  |

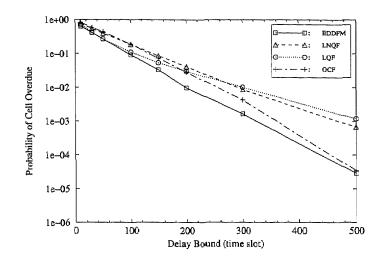

| 3.4  | Comparison of probability of cell overdue                                                                          | 47  |

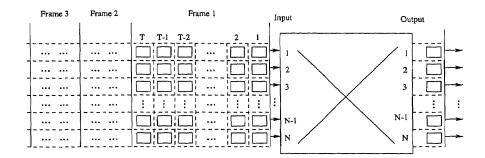

| 4.1  | An $N \times N$ input-queued switch with time axis divided into frames                                             | 52  |

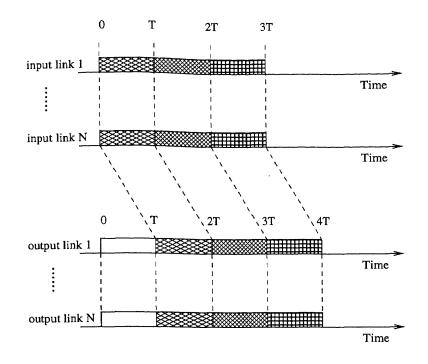

| 4.2  | Time relation between cell arrivals and departures                                                                 | 53  |

## Figure

## Page

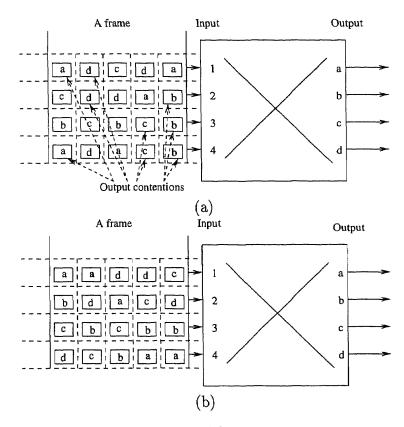

| 4.3 | Cells arrived in one frame: (a) original arrival orders. (b) scheduled transmission orders                                                                                                                                                                                                                                                                                                                | 55 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

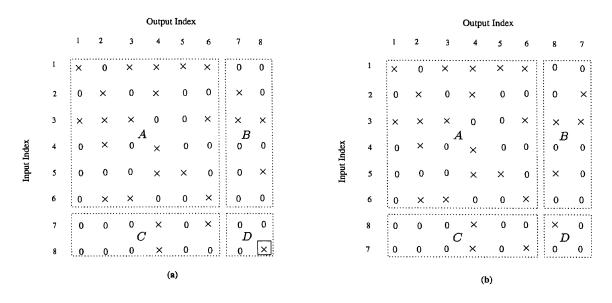

| 4.4 | A single effective move: (a) There is a nonzero element in block $D$ . (b) The nonzero element is moved to the upper-left corner of block $D$ by swapping rows 7 and 8, and then columns 7 and 8                                                                                                                                                                                                          | 58 |

| 4.5 | A double effective move: (a) Block $D$ has only zeros and there is a nonzero element in block $B$ corresponding to a nonzero element in block $C$ . (b) The nonzero element in block $C$ is moved to block $D$ by swapping columns 5 and 8                                                                                                                                                                | 59 |

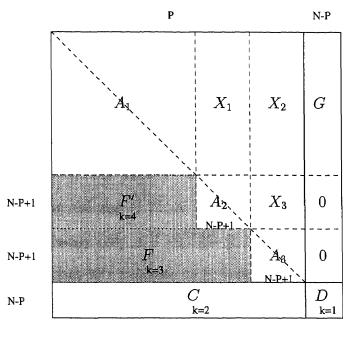

| 4.6 | A multiple effective move: (a) There are only zero elements in block $B$ corresponding to the nonzero elements in block $C$ . (b) Residue matrix $F$ is constructed by swapping columns 2 and 6, and then rows 2 and 6. There is a nonzero element in $G$ corresponding to a nonzero element in $F$ . (c) The nonzero element in $F$ can be moved to the zero block below $G$ by swapping columns 1 and 8 | 60 |

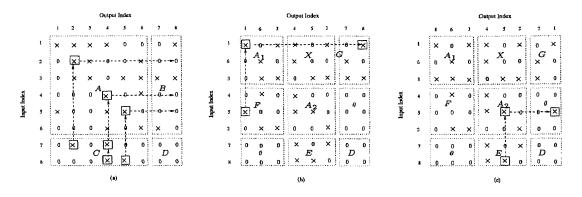

| 4.7 | Two extreme cases of cell transmission: (a) the cell experiences an end-<br>to-end delay of $(n-1)T + \tau$ . (b) the cell experiences an end-to-end<br>delay of $(n+1)T - \tau$                                                                                                                                                                                                                          | 63 |

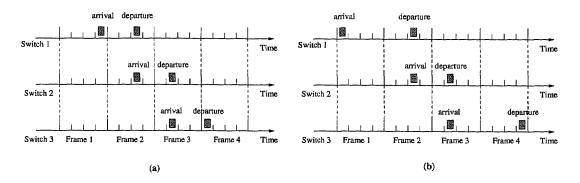

| 4.8 | Decomposition of a traffic matrix                                                                                                                                                                                                                                                                                                                                                                         | 67 |

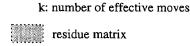

| 5.1 | Star configuration                                                                                                                                                                                                                                                                                                                                                                                        | 77 |

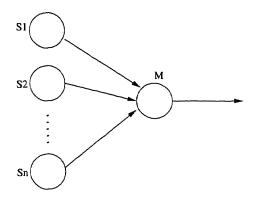

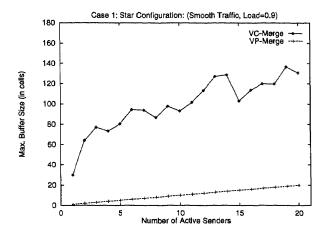

| 5.2 | Star Configuration: Case 1: VC-Merge vs VP-Merge                                                                                                                                                                                                                                                                                                                                                          | 78 |

| 5.3 | Star Configuration: Case 1: VC-Merge vs VP-Merge: Smooth                                                                                                                                                                                                                                                                                                                                                  | 79 |

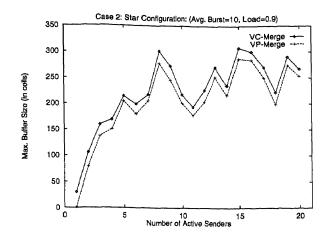

| 5.4 | Star Configuration: Case 2: VC-Merge vs VP-Merge                                                                                                                                                                                                                                                                                                                                                          | 81 |

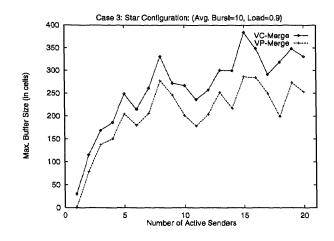

| 5.5 | Star Configuration: Case 3: VC-Merge vs VP-Merge                                                                                                                                                                                                                                                                                                                                                          | 82 |

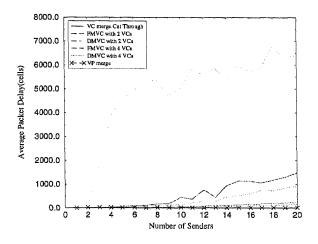

| 5.6 | Comparison of DMVC and FMVC with virtual cut-through VC-Merge $% \mathcal{A}$ .                                                                                                                                                                                                                                                                                                                           | 85 |

| 5.7 | Comparison of DMVC and FMVC with increasing number of identifiers .                                                                                                                                                                                                                                                                                                                                       | 86 |

| 5.8 | Comparison of SMVC with store and forward VC-Merge                                                                                                                                                                                                                                                                                                                                                        | 87 |

### CHAPTER 1

### INTRODUCTION

Telecommunication networks have been evolving from pure circuit switching based telephone networks to packet switching based broadband integrated service networks providing services for transport of voice, audio, images, real-time video, graphics, data, and other multimedia applications. Different applications have strikingly different requirements of the quality of service (QoS), and thus the design of traffic scheduling for switches to satisfy these various requirements is very crucial and challenging.

## 1.1 Buffering Schemes and its Effects on the Design of Traffic Scheduling

The objective of traffic scheduling is to satisfy the requirements of guaranteed performance such as delay, delay jitter for real-time traffics, and a fair distribution of the network resources for best effort applications. Scheduling algorithms fulfill this task by selecting a cell for transmission in the next transmission period for each output link of the switch among the cells destining for the same output link. Switch fabric architectures and buffering mechanisms affect the scheduling algorithm design. An ATM switch typically consists of three parts: input ports, output ports and a switch fabric. Input ports buffer cells coming from input links while output ports buffer cells going out to output links. The fabric routes cells from arbitrary input links to arbitrary output links. Many architectures for switch fabrics have been proposed in the literature. Shared memory, bus, crossbar, and multistage networks [1] are among the commonly used architectures.

Figure 1.1 Output buffering architecture

In general, switch architectures can be categorized into three main types based on the adopted buffering mechanisms: the input-queued switch in which buffers are placed at the input side, the output-queued switch in which buffers are placed at the output side, and the combined input output queued switch in which buffers are placed at both the input and output sides.

Most of the early studies [2, 3, 4, 5, 6, 7, 8] focused on scheduling output queued switches (OQ) owing to its conceptual simplicity. By assuming that cells are readily available to be transmitted to the output links upon entering a switch, as shown in Figure 1.1, many proposed algorithms are able to provide QoS guarantees (see [9] for an overview). However, the output queueing architecture suffers from the scalability problem. Since more than one cell can arrive at the switch in a given time slot heading for the same output, the fabric and output buffers should have the capability to accommodate all of the cells to avoid cell loss and to meet certain delay bounds. In the worst case, an  $N \times N$  switch has to run N times faster than a single link when all N inputs receive cells directed to the same output in a time slot. The buffers, switch fabric, and control system have to be sped up proportionally to the number of input or output links, and thus severely limiting the switch capacity.

The input queueing (IQ) architecture, on the other hand, has good scalability. Since buffers are placed at the input of the switch, as shown in Figure 1.2, the fabric

Figure 1.2 Input buffering architecture

and buffers can run at the same speed as a single link without causing cell loss. Owing to its scalability, input queueing is receiving attention in both the research and commercial communities [10, 11, 12, 13, 14, 15]. Low throughput and no QoS guarantees are two major problems with the input queueing architecture. Extensive studies [12, 13, 14, 15, 16, 17] on improving the throughput of an input-queued switch have been conducted in the literature, and studies on providing QoS guarantees are still undergoing [18, 19].

There has been a trade off between QoS guarantees and scalability: the input queueing architecture is scalable but cannot provide guaranteed QoS, while the output queueing architecture can provide guaranteed QoS but is not scalable. Lately, there is a trend to adopt combined input output queueing (CIOQ), in which buffers are placed at both the input and output sides of a switch [20, 21]. It has been proven in [20] that a speedup of 2 is sufficient for a CIOQ switch to behave identically to an output-queued switch which employs work-conserving and monotonic scheduling discipline.

#### 1.2 Design Criteria for a Traffic Scheduler

Below is a high-level description of design criteria that switch designers must consider for the design and implementation of an appropriate traffic scheduler.

- Isolation among flows: A connection sending data at or below its negotiated rate should not be affected by misbehaving connections which send data at a rate higher than their negotiated rates.

- End-to-end delay: Real time applications have stringent requirements on the end-to-end delay. Cells arrived too late may have no use to the applications. Thus, scheduling algorithms should be able to provide guaranteed end-to-end delay bound for individual sessions.

- End-to-end delay jitter: The end-to-end delay jitter of a session is defined as the maximum difference of the delay experienced by any two cells belonging to the session. Continuous media playback applications usually have stringent requirements on the delay jitter. Ideally, a network should not introduce any delay jitter for these applications (i.e., constant delay or zero delay jitter).

- Throughput: Throughput is defined as the highest load under which a switch can forward without dropping any cell.

- Fairness: If the bandwidth usage of a connection is below its negotiated rate, the excess bandwidth should be distributed fairly among all connections. The commonly used fairness is defined as follows [4]: the fairness of a scheduling algorithm is the maximum difference of the normalized service received by any two sessions over the interval in which both sessions are continuously backlogged, i.e.,

$$F_S = \max_{\forall i,j, \ j \neq i} \left| \frac{W_i(t_1, t_2)}{r_i} - \frac{W_j(t_1, t_2)}{r_j} \right|.$$

(1.1)

where  $W_i(t_1, t_2)$  is the service session *i* received during time interval  $[t_1, t_2]$ , and  $r_i$  is the rate of session *i*. The smaller the amount, the fairer the algorithm is.

- Scalability: Since there could be thousands of connections sharing the same link, the algorithm must be scalable.

- Implementation complexity: The high switching speed imposes the scheduling algorithms to make decisions in a very short time. For example, at the rate of 622 Mbps, the switch has to make decision within less than  $0.7\mu s$ . Thus, scheduling algorithms must have a simple implementation.

#### 1.3 Traffic Scheduling in Input-Queued Switches

One of the major problems with input-queued switches is the head-of-line (HOL) blocking, which limits the throughput of such a switch to only 58.6% under uniform Bernoulli traffic when a single FIFO queue is maintained in each input buffer [22]. The throughput can be improved by making more than one cell in the buffer accessible to the scheduler. A windowed buffer with a size of W, in which any of the first W cells in the buffer are accessible, can improve the throughput noticeably, even with a small W. Virtual output queueing, in which an individual FIFO queue corresponding to each output is maintained in each input buffer as shown in Figure 1.3, is another method to improve throughput. All the cells at the head of the FIFO queues are accessible to the scheduler, and thus HOL blocking is avoided. However, contentions still occur when multiple cells try to get through the fabric. Output contentions occur when more than one virtual output queues (VOQs) in the same input buffer are non-empty. The contentions limit the throughput of an

Figure 1.3 Virtual output queueing and input/output contentions

input-queued switch, and thus constrain the switch from providing QoS guarantees to the applications.

Note that when more than one cell can be accessed by the scheduler in one input buffer, selecting different cells for transmission could lead to different throughput, owing to the inter-dependence of the inputs.

Maximizing the throughput of a switch can be mapped to the maximum matching problem in a bipartite graph. Algorithms proposed in the literature can be classified into two categories: maximum size and maximum weight matching based algorithms.

## 1.3.1 Maximum Size Matching Based Algorithms

Maximum size matching based algorithms maximize the number of connections between the input and output ports with the constraint of unique pairing. Representative scheduling algorithms include PIM (Parallel Iterative Matching) [12],

Figure 1.4 An example of a bipartite graph

*i*SLIP (Iterative Round Robin with slip) [14], and MFIQ (Min-max Fair Input Queueing) [17]. Figure 1.4 shows a bipartite graph, in which each input port is represented by a vertex in one group, and each output port is represented by a vertex in the other group. Each accessible cell is represented by an edge from an input port vertex in which it is stored to an output port vertex to which it is directed. Two possible matches of the configuration in Figure 1.4 are shown in Figure 1.5, in which one achieves the maximum throughput while the other does not.

**1.3.1.1 Representative Schedulers:** Finding the maximum match may take a long time [23]. Thus, most proposed mechanisms for matching resort to a maximal match, which has less complexity but in the worst case contains only 50% of the possible pairings of the maximum match [12].

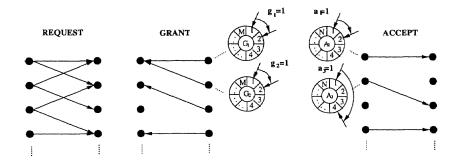

Parallel Iterative Matching (PIM) is a three-phase algorithm in finding a maximal match, consisting of requests, grants, and acknowledgments between the input and output ports. The complexity of PIM is proven to converge on average in O(logN) [12]. Many crossbar matching algorithms proposed in the literature [12, 24] are based on PIM.

McKeown and Anderson [14] later proposed IRRM for an ATM switch, which was found to have the same performance as PIM, but with a much lower hardware

Figure 1.5 Two possible matches of a bipartite graph

complexity. Similar to PIM, the following three steps are iterated for an M input, N output switch as described in [14]:

- 1. Each unmatched input sends a request to every output for which it has a queued cell.

- 2. If an unmatched output receives any requests, it chooses the one that appears next in a round-robin scheduler starting from the highest priority element. The output notifies each input whether or not its request was granted. The pointer  $g_i$  to the highest priority element of the round-robin scheduler is incremented (modulo M) to one location beyond the granted input.

- 3. If an input receives a grant, it accepts the one that appears next in a roundrobin scheduler starting from the highest priority element. The pointer  $a_i$  to the highest priority element of the round-robin scheduler is incremented (modulo N) to one location beyond the accepted output.

An example of one iteration of the three phases is illustrated in Figure 1.6. In the example, input port 1 has one or more cells for output ports 1 and 2, input port 2 has one or more cells for output ports 1 and 3, and so on. The grant schedules are shown for output ports 1 and 2. The accept schedules are shown for input ports 1 and 2. At the end of the first iteration,  $g_1$ ,  $g_2$  and  $a_1$  are incremented to 2, and  $a_2$

Figure 1.6 One iteration of the Iterative Round Robin Scheduling algorithm

is incremented to 4. The basic IRRM algorithm will not perform well for a single iteration because it does not allow the schedulers to be misaligned. IRRM with slip (iSLIP) was proposed later to achieve 100% utilization in one iteration. The iSLIP algorithm is identical to IRRM except that the pointer  $g_i$  in phase 2 is incremented if and only if the grant was accepted.

A 320 Gbps crossbar system is currently in development [25] adopting iSLIP and algorithms of similar nature.

#### 1.3.2 Maximum Weight Matching Based Algorithms

Maximum size matching based algorithms work well for uniformly distributed traffic. However, it was pointed out that a switch using maximum size matching based algorithms is not stable for non-uniform traffic [13, 15], i.e., the expected queue length in the switch could increase without bound. Maximum weight matching based algorithms were proposed later to achieve 100% throughput for both uniform and non-uniform traffic.

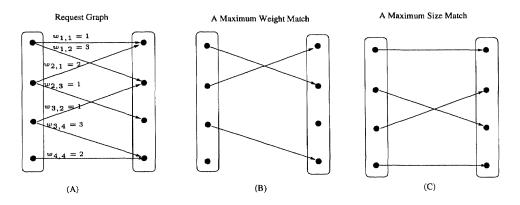

Consider the bipartite graph shown in Figure 1.7(a). Associated with each edge is a weight, which is defined differently for different algorithms. For example, setting weight as the queue length of the VOQ leads to LQF (Longest Queue First) [13], and setting weight as the delay time of the head cell in the VOQ leads to OCF

Figure 1.7 A bipartite graph matching example:(a) the request graph, (b) a maximum weight match, and (c) a maximum size match.

(Oldest Cell First) [15]. A maximum weight matching algorithm computes a match which can maximize the aggregate weight. The computational complexity of LQF and OCF is  $O(N^3 log N)$ . LPF [16] was proposed later to reduce the complexity to  $O(N^{2.5})$ , in which the weight of a VOQ  $Q_{i,j}$  is set as follows:

$$w_{i,j}(n) = \begin{cases} R_i(n) + C_j(n) & L_{i,j}(n) > 0\\ 0 & otherwise \end{cases}$$

where  $L_{i,j}(n)$  is the queue length of  $Q_{i,j}$  at time slot n,  $R_i(n) = \sum_j^N L_{i,j}(n)$  is the total number of cells that are currently stored in input i, and  $C_j(n) = \sum_i^N L_{i,j}(n)$  is the total number of cells stored at the input side destining for output j.

Note that maximum size match in which the maximum number of connections between inputs and outputs is obtained is a special case of maximum weight matching in which the weights of the non-empty VOQs are set to 1 and the weights of empty VOQs are set to 0. A maximum weight match and a maximum size match based on the same request graph are shown in Figure 1.7(b) and (c), respectively.

#### 1.4 Traffic Scheduling in Output-Queued Switches

Since cells arrive in an output-queued switch are immediately available for transmission, the scheduler only needs to resolve the contention among the cells sharing the same output link. In general, schedulers can be classified into two types: work-conserving and non-work-conserving. A work-conserving scheduler is never idle when there are cells buffered in the system, while a non-workconserving scheduler could be idle even if there are cells waiting in the buffer. Generalized Processor Sharing (GPS) [2], Weighted Fair Queueing (WFQ) [2], Self-Clocked Fair Queueing (SCFQ) [4], Virtual Clock [5], and Weighted Round Robin (WRR) [26] are examples of work-conserving schedulers, and Hierarchical-Round-Robin (HRR) [27], Stop-and-Go queueing [28] and Jitter-Earliest-Due-Date [29] are non-work-conserving schedulers.

### 1.4.1 Representative Work-conserving Schedulers

In this section, we briefly describe several representative work-conserving scheduling algorithms. We first present an idealized service discipline GPS and its packet version WFQ, also called Packetized Generalized Processor Sharing (PGPS), followed by SCFQ and Virtual Clock.

1.4.1.1 Generalized Processor Sharing: Generalized Processor Sharing (GPS) is an idealized scheduling discipline, which is defined based on a fluid-model. Associated with each session is a real number  $r_i$ , which represents its service share of the server. It is assumed that in GPS all the flows are serviced simultaneously with rates proportional to  $r_i$ , implying that the data unit is infinitely divisible. Let  $B(t_1, t_2)$  be the set of sessions that are backlogged in the time interval  $(t_1, t_2)$  and R be the total rate of the server. The service  $W_i(t_1, t_2)$  that a backlogged session i can

receive is proportional to its rate  $r_i$ . If session *i* is continuously backlogged during the interval  $(t_1, t_2]$ , the service it receives is

$$W_i(t_1, t_2) \geq \frac{r_i}{\sum_{j \in B} r_j} R(t_2 - t_1).$$

(1.2)

The minimum service rate offered to session i during that time interval is

$$\frac{r_i}{\sum_{j=1}^M r_j} R(t_2 - t_1), \tag{1.3}$$

where M is the maximum number of sessions which are backlogged in the server during that time interval. The GPS server serves each backlogged session simultaneously; each session is granted a rate equal to the minimum service rate of the session plus a fair share of the excess bandwidth which is available from sessions which are temporarily not backlogged. The normalized service time of a session, i, is defined as the amount of service  $W_i(t_1, t_2)$  the session receives during that interval divided by its rate  $r_i$ . GPS, with the assumptions that data unit can be infinitely divisible (infinitesimally small) and all sessions can be served simultaneously, is a perfect scheduler with ideal fairness (F = 0), and low end-to-end delays.

Many Packet Fair Queueing (PFQ) algorithms [2, 3, 4] were proposed to emulate the GPS model for scheduling output-queued switches. Each PFQ algorithm maintains a system potential v(t), which is initialized to be zero whenever the server becomes idle, and is updated accordingly. In addition, associated with the kth packet of a session, *i*, that arrives at time  $a_i^k$ , are a virtual starting time  $S_i^k$  and a virtual finishing time  $F_i^k$ . The virtual times are updated according to the following rule [2]:

$$\begin{cases} S_i^k = max\{F_i^{k-1}, v(a_i^k)\} \\ F_i^k = S_i^k + \frac{l_i^k}{r_i} \end{cases}$$

(1.4)

where  $l_i^k$  represents the length of the kth packet of session *i*. PFQ algorithms approximate GPS performance by selecting cells with the minimum virtual finishing or starting time for transmission. Different policies for updating the system potential lead to different PFQ algorithms. For example, choosing real time as the system potential leads to Virtual Clock [5], and choosing the virtual finishing time of the current session in progress as the system potential leads to Self-Clocked Fair Queueing [4].

**1.4.1.2** Weighted Fair Queueing: GPS cannot be implemented since servers transmit packets in their entirety, i.e., packets are not infinitesimally small, and a server cannot serve more than one packet at any time. A packet-by-packet transmission scheme called Weighted Fair Queueing (WFQ) or Packet Generalized Processor Sharing (PGPS) was proposed [2] as an approximation to GPS. The system potential used in WFQ is updated according to

$$v(t_2) = v(t_1) + \frac{t_2 - t_1}{\sum_{i \in B} r_i},$$

(1.5)

where B represents the set of backlogged sessions during time interval  $(t_1, t_2]$ , during which the set of backlogged sessions are fixed. Thus, the system potential v(t) is a piecewise linear functions of real time whose slopes depend on the total rate of the currently backlogged sessions.

WFQ algorithm can be summarized as follows:

- 1. The system potential is updated when backlogged sessions change.

- 2. At the arrival of a new packet, the system potential v(t) is computed first. Suppose that the new arrived packet is the *k*th packet in session *i*, its virtual finishing time is updated as follows:

$$F_i^k \leftarrow max\{F_i^{k-1}, v(a_i^k)\} + \frac{l_i^k}{r_i}.$$

(1.6)

3. The scheduler selects the packet with the smallest virtual finishing time for transmission.

Let V be the maximum number of sessions a server can serve simultaneously. Maintaining a sorted list of virtual finishing time requires a computation of O(logV). However, at most V events could occur during the transmission of one packet [30], and therefore, the complexity of computing virtual finishing time in WFQ algorithm is O(V), making the algorithm prohibitive for implementation.

**1.4.1.3 Virtual Clock:** Virtual Clock (VC), proposed by Zhang [5], tries to emulate a static TDM system. In VC, the system potential is selected to be the real time and the virtual finishing time is updated according to the following rule:

$$F_i^k \leftarrow max\{F_i^{k-1}, a_i^k\} + \frac{l_i^k}{r_i},\tag{1.7}$$

where  $a_i^k$  is the real time when the kth packet of session *i* arrives at the switch. The cell with the minimum virtual finishing time is selected for transmission.

The complexity of computing the virtual finishing time is reduced to O(1). However, maintaining a sorted list of the virtual finishing time has a complexity of O(logV), and thus, the complexity of Virtual Clock is O(logV). It has been proven that VC has the same delay bound as WFQ and poor fairness, as shown in Table 1.1.

1.4.1.4 Self-Clocked Fair Queueing: Self-Clocked Fair Queueing (SCFQ) was proposed and analyzed in [4]. In SCFQ, the packet with the minimum virtual finishing time is scheduled for transmission. SCFQ chooses the virtual finishing time of the current being served packet as the system potential. Let  $v_{cur}$  be the virtual finishing time of the packet in service. The virtual finishing time of the new packet

Table 1.1 Comparison of representative work-conserving schedulers for outputqueued switches.  $L_i$  is the maximum packet size of session *i*,  $L_{max}$  is the maximum packet size among all the sessions, *R* is the transmission rate of the switch, and  $\sigma_i$ is the bucket depth of session *i*.

| servers | delay                                                 | fairness                                                                                                                                                             | complexity |

|---------|-------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| WFQ     | $rac{\sigma_i + L_{max}}{r_i} + rac{L_{max}}{R}$    | $\frac{\max(C_j + \frac{L_{max}}{r_i} + \frac{L_j}{r_j}, C_i + \frac{L_{max}}{r_j} + \frac{L_i}{r_i})}{C_i = \min((V-1)\frac{L_{max}}{r_i}, \max(\frac{L_n}{r_n}))}$ | O(V)       |

| VC      | $\frac{\sigma_i + L_{max}}{r_i} + \frac{L_{max}}{R}$  | $\frac{c_i}{\infty} \xrightarrow{r_i, r_i} \frac{c_i}{r_i} \frac{c_i}{r_i}$                                                                                          | O(logV)    |

| SCFQ    | $\frac{\sigma_i + L_{max}}{r_i} + \frac{VL_{max}}{R}$ | $rac{L_i}{r_i} + rac{L_j}{r_j}$                                                                                                                                    | O(logV)    |

is updated as follows:

$$F_i^k \leftarrow max\{F_i^{k-1}, v_{cur}\} + \frac{l_i^k}{r_i}.$$

(1.8)

By simplifying the calculation of the system potential, the complexity of SCFQ is reduced to O(logV). The trade off is that the end-to-end delay bounds grow linearly with the number of sessions that share the outgoing link, as shown in Table 1.1. Thus, the end-to-end delay bounds cannot be guaranteed by controlling sessions' negotiated rates.

Table 1.1 summarizes the performance of representative work-conserving output schedulers. All the three algorithms adopt leaky buckets to regulate bursty traffic, i.e.,  $A_i(t_1, t_2) \leq \sigma_i + \rho_i(t_2 - t_1)$ , where  $A_i(t_1, t_2)$  is the amount of traffic that enters the switch during any time interval  $(t_1, t_2]$ ,  $\rho_i$  is the average sustainable rate, and  $\sigma_i$  is the bucket depth of session *i*. The fairness shown in the table is based on the assumption [31] that only two sessions *i* and *j* are compared, each of which has infinite supply of packets. As shown in Table 1.1, WFQ has the best performance but the highest complexity. Virtual Clock can provide the same delay bound as WFQ but with poor fairness. On the contrary, SCFQ has good fairness but the delay is not bounded.

#### 1.4.2 Representative Non-work-conserving Schedulers:

With a non-work-conserving scheduler, the server could be idle even when there are cells waiting for service. This results in a higher average packet delay and lower server throughput. However, the delay bound is a more important performance index for the guaranteed performance service [9]. Moreover, non-work-conserving schemes maintain traffic smoothness inside the network, and thus simplify the analysis of end-to-end delay in a networking environment. Therefore, non-working conserving schedulers have also been studied extensively. In this section, we briefly describe two representative non-work-conserving schedulers: Stop-and-Go and Hierarchical Round Robin.

1.4.2.1 Stop-and-Go Queueing: Stop-and-Go queueing was first introduced by Golestine [7]. A framing strategy is adopted in the algorithm to segment the time axis into fixed length periods called frames. Arriving and departing frames are defined, and a constant delay  $\theta$ , where  $0 \leq \theta < T$ , between an arriving frame and its corresponding departing frame is introduced. Cells arrived during one arriving frame are only eligible for transmission in the corresponding departing frame. Stop-and-Go ensures that cells arrived during the same frame in the source stay in the same frame throughout the network. (r, T) traffic model is adopted in Stop-and-Go, in which a connection with a rate of  $r_{i,j}$  can transmit no more than  $r_{i,j} \cdot T$  bits during a frame with a length of T. If each server along the connection path guarantees that cells arrived during one frame can always be transmitted in the next frame, end-to-end delay bounds can be guaranteed. The framing strategy introduces a coupling problem between delay bound and bandwidth granularity. Consider a framing with a length of T. The minimum bandwidth allocated to a connection is  $\frac{L}{T}$ , where L is the length of one cell. Therefore, a large T is preferable for a fine bandwidth allocation. However, a small T is desired to reduce delay. The coupling problem was resolved by adopting hierarchical framing strategy as described in [32].

**1.4.2.2 Hierarchical Round Robin Scheduler:** Hierarchical Round Robin (HRR) adopts a hierarchical framing strategy [27]. The time axis in HRR is also segmented into frames, each of which consists of a number of slots. A slot at a higher level frame can either be assigned to a connection or to a lower level frame. The server scans through the frame in a round robin fashion. If the current slot is assigned to a connection, a packet from this connection is transmitted when there are packets waiting; otherwise, the server stays idle. Therefore, HRR is a non-work-conserving scheduler. If the current slot is assigned to a lower level frame, a slot of the lower frame is served in the same fashion.

Table 1.2 summarizes the performance of Stop-and-Go and HRR. Both Stopand-Go and HRR can maintain smoothness in a networking environment owing to their non-work-conserving nature. In Stop-and-Go, cells arrived in the same frame at the network entrance will be transmitted in the same frame throughout the network, while in HRR cells arrived in the same frame can be transmitted in different frames.

1.5 Traffic Scheduling in Combined Input Output Queued Switches Combined input and output queueing (CIOQ) approach was proposed to resolve the trade off between the QoS guarantees and scalability [20, 21], in which buffers are

٩,

**Table 1.2** Performance of representative non-work-conserving schedulers for outputqueued switches. T is the frame size and  $\theta$  is the constant delay between an arriving frame and its corresponding departing frame

| schedulers  | traffic constrain | delay        | delay jitter | buffer space   |

|-------------|-------------------|--------------|--------------|----------------|

| Stop-and-Go | (r,T)             | $T + \theta$ | T            | $r(2T+\theta)$ |

| HRR         | (r,T)             | 2T           | 2T           | 2rT            |

placed at both sides of a switch. CIOQ emulates an output scheduling algorithm in such a way that the cell transmission order in CIOQ is the same as that in the emulated output scheduling algorithm in every time slot. Since it is only necessary to forward the cell to be transmitted in the next time slot in the emulated OQ scheduler to the output side of the switch, CIOQ does not require speedup of N to guarantee the same performance. It has been proven [20] that a switch using CIOQ with speedup of 2 can provide the same QoS guarantees as a switch using an OQ scheduling algorithm.

#### 1.5.1 Algorithm Description

Push-in queue concept was used in [20], i.e., arriving cells can be placed at any position in the queue and once the cells are placed in the queue, the relative order cannot be changed. In a CIOQ switch, each input maintains an input queue, where the cells are stored in a specific order. Different algorithms are characterized by the orders the cells are stored in each input queue. Likewise, each output maintains an output queue which consists of cells waiting for departure. Moreover, an output priority list, which is an ordered list of cells stored in inputs and directed to that particular output, is maintained in each output. The cells on the output priority list are always ordered according to the emulated output scheduling algorithm. A variety of CIOQ algorithms have also been proposed to emulate OQ scheduling with a speedup of 2. The algorithms differ from each other only in the insertion policy. For example, placing an arriving cell as far from the head of its input queue as possible leads to Critical Cells First (CCF) [20], and placing an arriving cell at the front of the input queue leads to Last In Highest Priority (LIHP) [20]. Each time slot is divided into four phases [20]:

- 1. The arrival phase: New cells arrive only in this phase.

- 2. The first scheduling phase: Cells are scheduled for transmissions from inputs to outputs.

- 3. The second scheduling phase: Again, cells are scheduled for transmissions from inputs to outputs.

- 4. The departure phase: Cells are transmitted out from the outputs only in this phase.

Since CIOQ requires speedup of 2, two scheduling phases are needed. During each scheduling phase, a stable matching algorithm is used to calculate a stable matching between inputs and outputs. A matching is said to be stable if for a cell cin an input, one of the following holds:

- Cell c is part of the matching, i.e., c is going to be transmitted from the input side to the output side during this phase.

- 2. A cell which is ahead of c in its input queue is part of the matching.

- 3. A cell which is ahead of c in its output queue is part of the matching.

Note that conditions 2 and 3 could be satisfied at the same time. A stable matching algorithm given by Gale and Shapely [33] can find a stable matching within

at most M iterations, where M is the total length of all the input queues. It is proven that in CIOQ, cells to be transmitted in the next time slot in the emulated output scheduler can always be forwarded to the output side, and thus the same QoS guarantees as the emulated output scheduler can be provided.

#### 1.6 Contributions of the Dissertation

In chapter 2, we consider the scheduling problem under uniform traffic. We model and analyze the back pressure problem with independent Bernoulli traffic load, and show that back pressure occurs with high probability under loaded traffic. The average queue length at the input buffer is also derived. To address the above issues in input-queued switches, we propose a maximum size matching based algorithm, referred to as min-max fair input queueing (MFIQ), which minimizes the additional delay caused by back pressure and at the same time provides fair service among competing sessions.

As pointed out in [13, 15], maximum size matching based algorithms do not perform well for non-uniform traffic. There are several maximum weight matching based algorithms proposed in the literature [13, 16, 15] to achieve high throughput under non-uniform traffic. However, only aiming at maximizing throughput could generate adverse effects on traffic shape and quality of service (QoS) features such as delay and fairness. In chapter 3, two algorithms are proposed to provide some QoS features while achieving high throughput for input-queued switches. By setting the weight of an edge in the bipartite graph to the normalized queue length of the corresponding VOQ, the longest normalized queue first (LNQF) [18, 34] provides fairer service than LQF and better traffic shape than OCF. The stability of LNQF is also proven. In earliest due date first matching (EDDFM), the weight is a function of delay bound and thus forces the cells with earliest delay due date to have highest priority to receive service. Simulation results show that EDDFM has lower probability of delay over due than LQF, LNQF, and OCF.

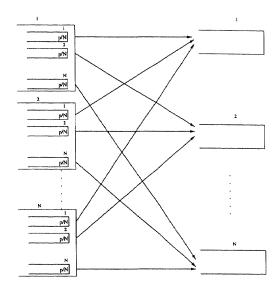

The maximum matching based algorithms can only achieve asymptotical 100% throughput, and thus, cannot provide deterministic QoS guarantees. In Chapter 4, a frame based scheduling algorithm, referred to as Store-Sort-and-Forward (SSF) [19], is proposed to provide QoS guarantees for input-queued switches without requiring speedup. SSF uses a framing strategy in which the time axis is divided into constant-length frames, each made up of an integer multiple of time slots. Cells arrived during a frame are first held in the input buffers, and are then "sorted-and-transmitted" within the next frame. A bandwidth allocation strategy and a cell admission policy are adopted to regulate the traffic to conform to the (r, T) traffic model. A strict sense 100% throughput is proved to be achievable by rearranging the cell transmission orders in each input buffer, and a sorting algorithm is proposed to order the cell transmission. The delay and delay jitter are bounded by the transmission time of one frame. It is proved that a perfect matching can be achieved within  $N(\ln N+O(1))$  effective moves.

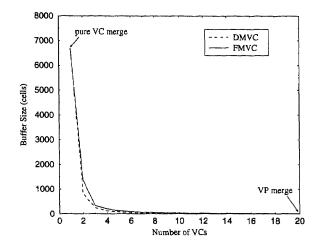

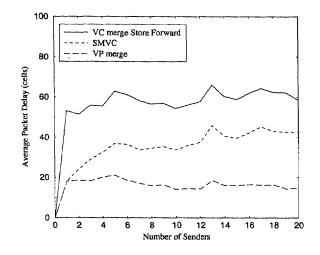

Chapter 5 presents our contributions on ATM multicasting. The routing and signaling protocols for supporting multipoint-to-multipoint connections in ATM networks have been presented in recent publications. VP-Merge and VC-Merge techniques have been proposed as the likely candidates for resolving the sender identification problem associated with these connections. The additional buffer requirements in the VC-Merge mechanism and the limitations of VPI space in the VP-Merge mechanism have been the main reasons for concern about their effective utility. In this chapter, we propose improvements to these traditional merging techniques. Our proposal describes a scalable VP-Merge scheme and analyzes different mechanisms to implement the scheme in ATM networks. To facilitate an elegant implementation, we introduce VP-VC Switching, a new switching mode different from traditional VP Switching and VC Switching modes. We also propose an improved VC-Merge technique [35] to control the additional buffers at intermediate merge points. Aptly named Dynamic Multiple VC-Merge (DMVC), Fixed Multiple VC-Merge (FMVC) and Selective Multiple VC-Merge (SMVC), these mechanisms define a generic scheme for merging the data from multiple senders onto one or more outgoing links. By appropriately choosing the number of connection identifiers per connection, these schemes lead to a large reduction in the buffer requirements and an effective utilization of the VPI/VCI space. Based on extensive simulations, we show that by using two connection identifiers per connection, there is an 80% reduction in buffer requirements for DMVC and FMVC when compared to the buffer required for traditional VC-Merge.

#### CHAPTER 2

#### MIN-MAX FAIR INPUT QUEUEING (MFIQ)

It was shown [22] that the throughput of an input-queued switch is limited to 0.586 when a single first-in-first-out (FIFO) queue is used in each input port under uniform Bernoulli traffic. This is mainly owing to the head of line (HOL) blocking, i.e., if cells in the front of the input queue are blocked, the cells stored behind them cannot be transmitted even if their destination output ports are open. Since the publication of the seminal paper by Karol *et al.* [22], many works [36, 14] have indicated that the throughput of the input-buffered switch can be improved by using well designed scheduling algorithms. Parallel Iterative Matching (PIM) will reach 100% throughput if a sufficiently large number of iterations are used. Iterative round-robin matching with slip (*i*SLIP) [14] was proposed later that has similar performance as PIM at much lower hardware complexity.

While scheduling algorithms designed for output-buffered switches, like Packet Fair Queueing (PFQ), can provide end-to-end delay bound and fairness among sessions, they are not directly applicable to input-buffered switches without causing performance degradation. When the scheduler at an input port schedules one cell for transmission, schedulers at other input ports could also schedule cells for transmission to the same output port. Only one cell can get through the fabric, and the other cells are back pressured and stored in the input ports. Instead of wasting bandwidth, the scheduler in a back pressured port should schedule another cell for transmission. As a result, the back pressured sessions suffer extra delay and lose their fair share of the bandwidth while other sessions get more services than they should. The key issue is what type of actions should a scheduler executes when the output port is open for the back pressured sessions after a certain time lapse. Instead of only aiming at maximizing the throughput, we propose an algorithm, called minmax fair input queueing (MFIQ), to minimize the additional delay and to arbitrate fair service among all competing sessions in an input port.

The rest of the chapter is organized as follows. The model of the back pressure problem under independent Bernoulli traffic is presented in Section 1, and it is shown that the effect of back pressure is significant. Section 2 presents our proposed scheduler, and simulation results are shown in Section 3. Remarks are concluded in Section 4.

## 2.1 Queueing Analysis

Consider a system with N input ports, N output ports, and an  $N \times N$  fabric. The cell arrival processes at the input ports are assumed independent and identical Bernoulli. Let p be the traffic load, i.e., in any given time slot, the probability that a cell arrives at a particular input port is p. The cell has equal probability of 1/N to go to any given output port, and successive cells are independent. To eliminate HOL blocking, virtual output queueing is adopted, i.e., N separated queues, each of which is associated with a corresponding output port, are maintained in an input port. The probability of a cell appearing at a virtual output queue (VOQ) is p/N. There are  $N^2$  VOQs in the system as shown in Figure 2.1. Associated with an output port is a queue group with N VOQs, each of which is located in one of the N input ports. The cell arrival processes in these queues are also independent. Let A be the total number of cells appeared at the head of each VOQ in a queue group in one time slot. Thus, A is a Binomial random variable and has the following distribution:

$$P(A=i) = \binom{N}{i} (p/N)^{i} (1-p/N)^{N-i}.$$

(2.1)

Figure 2.1 Virtual output queueing

Contention occurs when more than one of the VOQs have cells in the same time slot. Only one out of the competing cells can get through the fabric, and the others are back pressured for later transmission. Thus, back pressure occurs with probability

$$P_B = \sum_{i=2}^{N} {N \choose i} (p/N)^i (1-p/N)^{N-i}$$

=  $1 - (1 - \frac{p}{N})^{N-1} (1 - \frac{p}{N} + p).$  (2.2)

When the number of input ports increases, the probability of back pressure becomes

$$\lim_{N \to \infty} P_B = 1 - e^{-p} (1+p).$$

(2.3)

Note that Equation (2.3) is monotonically increasing with the load p. The probability of back pressure reaches its maximum value of 1 - 2/e when the load reaches one.

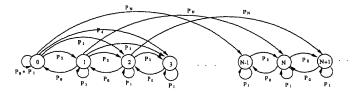

Consider the total queue size of one queue group. With the assumption that one cell can always be transmitted during the time slot if there are cells at the head of the N VOQs, the Markov chain for the total queue length of the queue group can be obtained as shown in Figure 2.2, where

Figure 2.2 The discrete time Markov chain for the total queue length of one queue group

$$p_i = \binom{N}{i} (P/N)^i (1 - P/N)^{N-i},$$

and the state value of the chain indicates the queue size of the queue group. The transition probability matrix of the Markov chain is

$$\mathbf{p} = \begin{bmatrix} p_0 + p_1 & p_2 & p_3 & \dots & p_N & 0 & \dots \\ p_0 & p_1 & p_2 & \dots & p_{N-1} & p_N & \dots \\ 0 & p_0 & p_1 & p_2 & \dots & \dots & \dots \\ 0 & 0 & \dots & \dots & \dots & \dots & \dots \\ \vdots & \vdots \end{bmatrix}$$

It is difficult to derive the close form distribution of the queue length, but the generating function of the queue length distribution can be readily derived:

$$Q(z) = \frac{(1-p)(z-1)}{z-A(z)},$$

(2.4)

where

$$A(z) = (1 - \frac{p}{N} + z\frac{p}{N})^{N}$$

(2.5)

is the generating function of random variable A. Thus, the mean steady-state queue length can be obtained as follows:

$$\overline{Q} = \lim_{z \to 1} Q'(z) = \frac{N-1}{N} \frac{p^2}{2(1-p)},$$

(2.6)

where  $Q'(\cdot)$  is the derivative of  $Q(\cdot)$ . Figure 2.3 shows the average total queue length in a queue group associated with one output port.

Figure 2.3 Mean queue length of a queue group with ideal throughput

Note that Equation (2.6) is applicable to every queue group. If queue groups corresponding to different output ports are independent, the average queue length at the input buffer of the switch is  $N\overline{Q}$ . Since the traffic in the N input ports are independent, the average queue length in one input port is also  $\overline{Q}$ . The Markov chain is derived based on the assumption that there is always a cell to be transmitted to a given output port whenever there are cells in the queue group. In fact, if more than one output port schedule the same input port to transmit cells, only one cell can be transmitted. As a result, the bandwidths of the other output ports are not utilized. Thus, the actual throughput can only be lower than what is assumed here. Hence, the average queue length at the input buffer in a realistic situation (Figure 2.4) is longer than the ideal case (Figure 2.3). Thus, back pressure can potentially cause adverse effect on the delay and fairness of the competing sessions.

Figure 2.4 Mean queue length of a queue group simulation results

# 2.2 Min-max Fair Input Queueing Algorithm

Before we proceed to describe our algorithm which will overcome the shortcomings of applying PFQ directly to input-buffered switches, we first define the following.

**Definition 1** A reference scheduler(RS) of a system is an ideal scheduler which operates without back pressure but has the same configuration as the real scheduler in the system.

The reference scheduler maintains its own virtual time. The virtual time of a session scheduled by the reference scheduler is updated no matter whether the session is back pressured in the real system. Thus, virtual time of sessions in the reference system keeps track of the service that the sessions should receive in the real system.

**Definition 2** The additional delay of a cell is the time interval between the time when the cell is transmitted in the real system and the time when the cell is scheduled in the reference scheduler.

Note that the additional delay is negative when the cell is transmitted before it is scheduled in the reference scheduler. **Definition 3** The normalized service lag of a session is the difference between the normalized service time the session should receive in the reference scheduler and the normalized service time it has received in the real system.

For input-buffered switches, the schedulers of input ports are not independent from each other. When more than one input port schedules cells to the same output port, contention occurs. Only one of the competing cells can get through the fabric, and the others are back pressured in the input ports. To increase throughput, the scheduler of the back pressured input port needs to schedule another cell that is free of contention. Thus, the back pressured cell experiences additional delay and loses its fair share of service. On the contrary, the being served session receives earlier and more service than its fair share. There could be more than one session back pressured at the same time. When the output ports for the back pressured cells are open for transmission, which cell should be transmitted? Within the context of GPS which is the perfectly fair scheduler, the back pressured session with the largest normalized service lag is the one that has been back pressured longest, thus experiencing the largest additional delay. It is therefore intuitively fair to transmit the cell of the session that has been back pressured the longest. This is the essence our algorithm as shown in Figure 2.5.

In the algorithm, a reference virtual time system and a real virtual time system are maintained. The virtual time of each session is updated in the reference system, independent of the status of the real system, to keep track of the normalized service the session should receive. Normalized service lags are maintained in the real system. The system potential V(t) can be updated by using any PFQ algorithms like WFQ [2], SCFQ [4],  $WF^2Q$  [6], and  $WF^2Q$ + [37]. For example, if WFQ is Cell\_reaches\_head\_of\_queue(session i, packet \*cell) if  $i \in B$ if  $queue\_length(i) == 0$  $S_i \leftarrow max(V, S_i)$  $F_i \leftarrow S_i + l/r_i$ else $S_i \leftarrow V$  $lag_i \leftarrow 0$  $B \leftarrow B \cup i$ enqueue(session i, packet \*cell)Transmit\_cell  $q_to_update \leftarrow min_i F_i$  $q\_to\_send \leftarrow max_i \ lag_i \ \{i \mid i \in not \ BP \ \}$ if  $q_{to_send} \neq -1$ dequeue(q\_to\_send) Update\_system\_potential()  $S_{q\_to\_update} \leftarrow S_{q\_to\_update} + l/r_{q\_to\_update}$  $F_{q\_to\_update} \leftarrow S_{q\_to\_update} + l/r_{q\_to\_update}$ if  $q_to_update \neq q_to_send$ normalized\_lag[q\_to\_update]  $\leftarrow$  normalized\_lag[q\_to\_update] +  $l/r_{q_to_update}$  $normalized_lag[q_to_send]$  $\leftarrow normalized\_lag[q\_to\_send] - l/r_{q\_to\_send}$

```

\begin{array}{c} Session\_leave(session \ i) \\ B \leftarrow B \setminus i \end{array}

```

Figure 2.5 The pseudo-code of the min-max fair input queueing algorithm

selected to update the system potential, the rule is

$$V(t+\tau) = V(t) + \frac{\tau}{\sum_{i \in B} r_i},$$

(2.7)

where B represents all backlogged sessions and  $\tau$  is the time increment. The session with the smallest virtual finishing time  $F_i$  in the reference scheduler is updated regardless of the status of the real system, i.e., the virtual finishing time of the selected session *i* in the reference system is updated no matter whether it is back pressured or not. The session with the largest normalized lag is scheduled for transmission in the real system. If the transmitted session *j* is not the session selected

Figure 2.6 Comparison of normalized service time received by the three sessions: (a) MFIQ, and (b) reference scheduler

in the reference system, the selected session is deferred for transmission. Thus, the normalized service lag of the selected session is increased by  $l/r_i$ , and that of the transmitted session is decreased by  $l/r_j$ .

# 2.3 Simulation Results and Performance Comparison

Consider a system with eight input ports and eight output ports. To eliminate HOL blocking, virtual output queueing is used. Each VOQ has three sessions with transmission rates of 1, 5 and 10 Mbps. WFQ was selected to update the system potential. Simulations were conducted for a load of 0.8, 0.9 and 0.95. Each simulation lasted through 2 seconds.

Two schedulers were simulated: our proposed MFIQ algorithm, and the reference scheduler defined earlier, in which sessions were scheduled only based on their virtual times in the reference scheduler. When the scheduled session was back pressured, its virtual time was updated and another session which was free of

Figure 2.7 Instantaneous fairness: MFIQ versus reference scheduler

contention was selected for transmission. The scheduler did not keep track of the service time lost by the back pressured sessions. Thus, the lost service time could not be compensated.

The normalized service times received by three sessions belonging to different VOQs are shown in Figure 2.6. Since our proposed algorithm always selected the session with the largest normalized service lag for transmission, the differences of the received normalized service times among sessions were smaller than that of the reference scheduler. The instantaneous fairness, which is the difference between the largest normalized service lag and the smallest normalized service lag experienced by all sessions, is compared in Figure 2.7. The instantaneous fairness of MFIQ is much smaller than that of the reference scheduler, even though they both experience randomness owing to the back pressure. The proposed MFIQ has better performance in terms of maximum normalized service lag and maximum additional delay, as shown in Figures 2.8 and 2.9.

Table 2.1 illustrates the statistics of the simulations for different loads. Four results can be derived from the table.

**Table 2.1** Statistics of the simulation results:  $d_i$  is the delay of session i and  $r_i$  is the rate of session i.  $F_S$  is the instantaneous fairness of the algorithm.  $D_{max}$  is the maximum additional delay caused by contentions while  $Lag_{max}$  is the maximum normalized service lag of the algorithm.

| load                                | 0.8    |       | 0.9    |       | 0.95   |       |

|-------------------------------------|--------|-------|--------|-------|--------|-------|

| schedulers                          | RS     | MFIQ  | RS     | MFIQ  | RS     | MFIQ  |

| $d_1(\text{ms}): r_1=1 \text{Mbps}$ | 0.98   | 1.17  | 2.07   | 2.54  | 5.24   | 4.24  |

| $d_2(ms): r_2=5Mbps$                | 0.50   | 0.41  | 0.88   | 0.82  | 1.85   | 1.49  |

| $d_3$ (ms): $r_3$ =10Mbps           | 0.28   | 0.28  | 0.43   | 0.61  | 1.35   | 1.01  |

| queue length (cell)                 | 19.97  | 19.33 | 39.56  | 39.26 | 71.89  | 75.77 |

| $F^{S}(ms)$                         | 327.45 | 51.87 | 314.75 | 88.45 | 378.96 | 88.83 |

| $D_{max}(ms)$                       | 3.47   | 3.20  | 5.78   | 4.22  | 11.09  | 5.19  |

| $Lag_{max}(ms)$                     | 66.66  | 15.87 | 110.73 | 47.13 | 116.35 | 41.65 |

- 1. The two algorithms have similar performance in terms of average delay and average queue length.

- 2. The proposed MFIQ has better performance in terms of fairness and additional delay.

- 3. The average delay of a session is inversely proportional to its rate.

- 4. Average instantaneous fairness, average maximum additional delay, and average queue length increase as the load increases.

Figure 2.8 Maximum normalized service lag: MFIQ versus reference scheduler

Figure 2.9 Comparison of maximum additional delay: (a) MFIQ, (b) reference scheduler

#### CHAPTER 3

## MAXIMUM WEIGHT MATCHING

Maximum size matching based algorithms work well for uniformly distributed traffic. However, it was pointed out that a switch using maximum size matching based algorithms is not stable for non-uniform traffic [13, 15], i.e., the expected queue length in the switch could increase without bound. Round robin scheduler, which has low implementation complexity, is adopted in *i*SLIP to resolve the contention among cells stored in the same input port. However, the priority of a round robin scheduler is not a function of the queue length. Thus, *i*SLIP performs poorly for non-uniform traffic, in which the average queue length of the FIFO queues could differ strikingly under loaded traffic. Maximum weight matching can achieve high throughput under both uniform and non-uniform traffic in which each session is assigned a weight and a match with the maximum aggregate weight is obtained. Longest queue first (LQF) [13] and oldest cell first (OCF) [15] are among the maximum weight matching approach, in which the queue length and the delay time of head of line cell are set as the weights, respectively.

Algorithms which only aim at maximizing throughput could generate adverse effects on traffic shape and quality of service (QoS) features such as delay and fairness. In LQF, the priority is set according to the queue length, i.e., the queue with the largest length has the highest priority to receive service. Since the queues of the VOQs with different arrival rates are built up at different speeds, using the queue length as the weight forces the scheduler to serve the VOQs with high arrival rates and starve the VOQs with low arrival rates. This is the main reason why LQF leads to unfair service and uncontrollable delay time for the VOQs with low arrival rates. On the other hand, OCF avoids starvation by setting delay time as the weight, in which the unserved cells get growing "older" until they eventually become "old" enough to be served. Using delay time as the weight forces the scheduler to serve the VOQs burst by burst, thus sacrificing the QoS requirements. By observing that session rates and delay requirements should be incorporated in the scheduler design in order to satisfy the QoS requirements, we propose two new algorithms, referred to as longest normalized queue first (LNQF) and earliest due date first matching (EDDFM).

The rest of the chapter is organized as follows. In Section 1, we describe our switch and traffic models. Section 2 presents one of our proposed algorithms, referred to as longest normalized queue first (LNQF) and proves that a switch using LNQF is stable under both uniform and non-uniform traffic. Section 3 proposes another algorithm: earliest delay due date first matching (EDDMF). Section 4 shows the performance of the proposed algorithm. Concluding remarks are given in Section 5.

#### 3.1 Switch and Traffic Models