## **Copyright Warning & Restrictions**

The copyright law of the United States (Title 17, United States Code) governs the making of photocopies or other reproductions of copyrighted material.

Under certain conditions specified in the law, libraries and archives are authorized to furnish a photocopy or other reproduction. One of these specified conditions is that the photocopy or reproduction is not to be "used for any purpose other than private study, scholarship, or research." If a, user makes a request for, or later uses, a photocopy or reproduction for purposes in excess of "fair use" that user may be liable for copyright infringement,

This institution reserves the right to refuse to accept a copying order if, in its judgment, fulfillment of the order would involve violation of copyright law.

Please Note: The author retains the copyright while the New Jersey Institute of Technology reserves the right to distribute this thesis or dissertation

Printing note: If you do not wish to print this page, then select "Pages from: first page # to: last page #" on the print dialog screen

The Van Houten library has removed some of the personal information and all signatures from the approval page and biographical sketches of theses and dissertations in order to protect the identity of NJIT graduates and faculty.

#### **ABSTRACT**

### **DUAL MATERIAL GATE FIELD EFFECT TRANSISTOR (DMG-FET)**

### by Wei Long

Improving performance and suppressing short channel effects are two of the most important issues in present field effect transistors development. Hence, high performance and long channel like behaviors are essential requirements for short channel FETs. This dissertation focuses on new ways to achieve these significant goals. A new field effect transistor — dual material gate FET (DMG-FET) — is presented for the first time. The unique feature of the DMG-FET is its gate which consists of two laterally contacting gate materials with different work functions. This novel gate structure takes advantage of material work function difference in such a way that charge carriers are accelerated more rapidly in the channel and the channel potential near the source is screened from the drain bias after saturation. Using HFET as a vehicle, it is shown that the drive current and transconductance in DMG-FET are therefore substantially enhanced as compared to conventional FET. Moreover, it is observed that the short channel effects such as channel length modulation, DIBL and hot-carrier effect are significantly suppressed. Numerical simulations are employed to investigate the new device structure and related phenomenon. A simple and practical DMG-HFET fabrication process has been developed. The proposed DMG-HFET is thus realized for the first time. Experimental results exhibit improved characteristics as the simulation results predicted.

# DUAL MATERIAL GATE FIELD EFFECT TRANSISTOR (DMG-FET)

by Wei Long

A Dissertation

Submitted to the Faculty of

New Jersey Institute of Technology

In Partial Fulfillment of the Requirements for the Degree of

Doctor of Philosophy

Department of Electrical and Computer Engineering

January 1998

Copyright © 1998 by Wei Long

ALL RIGHTS RESERVED

### APPROVAL PAGE

### DUAL MATERIAL GATE FIELD EFFECT TRANSISTOR (DMG-FET)

### Wei Long

|                                                                                                                                                   | Oct. 14,189,                |

|---------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| Dr. Ken K. Chin, Dissertation Advisor<br>Professor of Physics, NJIT                                                                               | Date                        |

| Director of NJIT-Rutgers(Newark) Joint Applied Physics MS/Ph.D. P.                                                                                | rogram                      |

|                                                                                                                                                   | 8 Oct 1997<br>Date          |

| Dr. William N. Carr, Committee Member Professor of Electrical and Computer Engineering, NJIT Professor of Physics, NJIT                           | Date                        |

|                                                                                                                                                   | Uct 2997                    |

| Dr. Haim Grebel, Committee Member Professor of Electrical and Computer Engineering, NJIT                                                          | Dáte                        |

| Dr. Edip Niver, Committee Member Associate Professor of Electrical and Computer Engineering, NJIT                                                 | Oct. 29, 1997  Date         |

| Dr. Marek/Sosnowski, Committee Member                                                                                                             | 0425 197<br>Date            |

| Associate Professor of Electrical and Computer Engineering, NJIT                                                                                  | 0.± 16 1997                 |

| Dr. Jenn-Ming Kuo, Committee Member<br>Member of Technical Staff, Bell Laboratories, Lucent Technologies                                          | <u>Oct. 16,1997</u><br>Date |

|                                                                                                                                                   | 30 tept 97                  |

| Dr. Erhard Kohn, Committee Member<br>Professor of Electronic Device and Circuit, University of Ulm, Germany<br>Adjunct Professor of Physics, NJIT | Date                        |

#### **BIOGRAPHICAL SKETCH**

Author: Wei Long

Degree: Doctor of Philosophy

Date: January 1998

Date of Birth:

Place of Birth:

### Undergraduate and Graduate Education:

- Doctor of Philosophy in Electrical Engineering,

New Jersey Institute of Technology, Newark, NJ, 1997

- Master of Science in Applied Physics,

New Jersey Institute of Technology, Newark, NJ, 1994

- Master of Science in Electrical Engineering,

Chinese Academy of Sciences, Shanghai, P.R.China, 1987

- Bachelor of Science in Electrical Engineering, Tsinghua University, Beijing, P.R.China, 1983

Major: Electrical Engineering

#### Presentation and Publications:

- W. Long and K.K.Chin, "Dual Material Gate Field Effect Transistor (DMG-FET)," to be published in *IEDM Proc. Dig.*, DC. Dec., 1997.

- W. Long, L. Lee. E. Kohn and K.K. Chin, "Analytical Modeling of Dual Gate HFETs," to be published in *IEEE Transactions on CAD of IC and Systems*.

- L. Lee, W. Long, S. Strahle, E. Kohn, et al., "Dual Gate HFET with Closed Spaced Electrodes on InP," 15<sup>th</sup> Biennial IEEE Cornell Conference on Advanced Concepts High Speed The Semiconductor Devices and Circuits, NY, 1995.

- W. Long and K. K. Chin, "Dual/Multi Material Gate Field Effect Transistor (DMG-FET)," US Patent (Pending).

To the Memory of My Parents

#### **ACKNOWLEDGMENT**

A great number of wonderful people have made my NJIT career a rewarding and memorable experience.

First, I would like to express my sincerest gratitude to my advisor, Professor Ken K. Chin, for his guidance and support throughout my years at NJIT. In way more than one, he has made me realize my fullest potential. I would especially like to thank him for giving me the freedom to pursue my research interest.

Special thanks are given to Prof. W. N. Carr, Prof. H. Grebel, Prof. E. Niver, Prof. M. Sosnowski, Prof. E. Kohn and Dr. J. M. Kuo for actively participating in my committee.

My rewarding experience was the summer I spend at the Electron Devices & Circuits Department, University of Ulm, Germany. I would especially like to thank Professor E. Kohn for giving me the opportunity to work with his group on interesting and stimulating dual gate topics. I would like also to thank Prof. Kohn for his fruitful and insightful discussions and many comments on final thesis. I would thank Mr. L. H. Lee at Univ. of Ulm for his great support and encouragement during and after my stay in Germany. I would like to thank Ms. U. Spitzberg for introducing me to so many wonderful German places when I was at Germany. I also wish to thank Dr. S. Strahle for her help during my German visit.

I want to give my sincerest gratitude to Dr. Kuo of the high speed electronics department of Bell Labs, Lucent Technologies, for supplying us with the pesudomophic MBE heterostructure material.

## ACKNOWLEDGMENT (Continued)

I have greatly benefited from the access to the III-V material fabrication laboratory/clean room at Columbia University, NYC. I would like to thank my old friends and former colleagues Mr. Haijiang Ou and Dr. Yuefei Yang for their kind help in the device processing and characterization.

I would thank Professor Zhiping Yu of Stanford University for providing the most recent version of PISCES codes and for his stimulating discussion on various issues relating to my thesis.

I am further indebted to Prof. Sosnowski for many suggestions and corrections.

I would give my gratitude to Dr. Jun Li for his consistent help in setting up the PISCES in our system. I would like to thank Prof. Wang for the help in device measurements.

The time I have spend at NJIT has been even more enjoyable due to all the friendship that I have made. In particular, I would like to thank Y. W. Zhang, Jack Zhang, C. Q. Sun, H. Opyrchal, J. Opyrchal, H. S. Luo, X. Q. Zhang, Y. X. Zhang, Y. Shi, C. Sun, C. Q. Qiu, etc. I would like to thank many of my fellow graduate students in the dept. and group for their help.

Finally, special thanks go to my wife, my daughter, my sister, my brothers and their families for their endless support, love and understanding through all my career. This dissertation is specially dedicated to the memory of my parents who loved and supported me the best.

### TABLE OF CONTENTS

| Chap | ter  |           | Pa                                                        | age |

|------|------|-----------|-----------------------------------------------------------|-----|

| 1    | INTR | ODUCTI    | ON                                                        | 1   |

|      | 1.1  | Motivat   | ions                                                      | 1   |

|      | 1.2  | Scope an  | nd Organizations                                          | 4   |

| 2    | BACK | GROUN     | D IMFORMATION                                             | 6   |

|      | 2.1  | Introduc  | etion                                                     | 6   |

|      | 2.2  | Develop   | oment of HFETs                                            | 7   |

|      | 2.3  | Principle | es of Operation                                           | 7   |

|      | 2.4  | Dynamic   | e Performance of Short Channel HFET                       | .10 |

|      |      | 2.4.1 F   | Parasitic Effects                                         | .10 |

|      |      | 2.42      | The Effects of Feedback Capacitance and Drain Conductance | .13 |

|      |      | 2.4.3 F   | Fmax, an Important Figure of Merit of RF HFETs            | .14 |

|      |      | 2.4.4     | Other Short Channel Effect Related Issues                 | .15 |

|      | 2.5  | The Stat  | e-of-the-art Approaches of Short Channel HFETs            | .15 |

|      |      | 2.5.1 S   | Self-aligned Gate and Ohmic Contact                       | .16 |

|      |      | 2.5.2 П   | Double-recessed Technique                                 | 17  |

|      |      | 2.5.2 \   | V-shaped Spike Gate HFETs                                 | 18  |

|      |      | 2.5.4 E   | Dual Gate HFETs                                           | .19 |

|      | 2.6  | Primary   | Goals of This Research                                    | .20 |

|      | 2.7  | Scope ar  | nd Methodology Used in This Research                      | 21  |

|      | 2.8  | Summar    | y                                                         | 22  |

| Chap | ter  | Pa                                                        | age |

|------|------|-----------------------------------------------------------|-----|

| 3    |      | LYTICAL MODELING FOR DUAL GATE HFET I-V<br>HARACTERISTICS | .23 |

|      | 3.1  | Introduction                                              | .23 |

|      | 3.2  | Analytic Single Gate Model                                | .25 |

|      | 3.3  | The Common Node Voltage Model of Dual Gate HFETs          | 31  |

|      |      | 3.3.1 The Analytic Model                                  | .32 |

|      |      | 3.3.2 Discussions                                         | 37  |

|      | 3.4  | Dual Gate I-V Characteristics                             | 38  |

|      | 3.5  | Summary                                                   | 40  |

| 4    | DUAL | GATE HFET SMALL SIGNAL CHARACTERISTICS                    | 42  |

|      | 4.1  | Introduction                                              | 42  |

|      | 4.2  | Single Gate Small Signal Parameters                       | 43  |

|      |      | 4.2.1 The Transconductance and Drain Conductance          | 44  |

|      |      | 4.2.2 The Gate Capacitance and Feedback Capacitance       | 45  |

|      | 4.3  | Dual Gate HFET Small Signal Equivalent Circuit            | 46  |

|      | 4.4  | Dual Gate Small Signal Parameters                         | 51  |

|      |      | 4.4.1 The Transconductance                                | 51  |

|      |      | 4.4.2. The Gate Capacitance                               | 53  |

|      |      | 4.4.3. The Output Conductance                             | 53  |

|      |      | 4.4.4 The Feed Back Capacitance                           | 56  |

| Chapt | ter  | l de la companya de | Page |

|-------|------|---------------------------------------------------------------------------------------------------------------|------|

|       | 4.5  | Results and Discussions                                                                                       | 56   |

|       | 4.6  | Summary                                                                                                       | 59   |

| 5     | A NE | W DEVICE STRUCTURE: DUAL MATERIAL GATE FET                                                                    | 61   |

|       | 5.1  | Introduction                                                                                                  | 61   |

|       | 5.2  | Screening Effect in Dual Gate FET                                                                             | 64   |

|       | 5.3  | Velocity Enhancement in Split Gate FET                                                                        | 69   |

|       | 5.4  | The Introduction of Dual Material Gate FET                                                                    | 74   |

|       | 5.5  | Comparison of DMG-FET with Other Device Structures                                                            | 80   |

|       | 5.6  | Summary                                                                                                       | 86   |

| 6     | DMG- | FET DESIGN AND ITS SIMULATED CHARACTERISTICS                                                                  | 87   |

|       | 6.1  | Introduction                                                                                                  | 87   |

|       | 6.2  | Design Consideration 1: The Threshold Voltage of DMG-FET                                                      | 89   |

|       | 6.3  | Design Consideration 2: The Role of Work Function Difference in DMG-FET                                       | 91   |

|       | 6.4  | Design Consideration 3: The Role of Lengths of the Two Gate Materials in DMG-FET                              | 95   |

|       | 6.5  | High Performance of DMG-FET                                                                                   | .101 |

|       | 6.6  | Suppressed Short Channel Effect in DMG-FET                                                                    | .104 |

|       |      | 6.6.1 Channel Length Modulation                                                                               | .104 |

|       |      | 6.6.2 Drain Induced Barrier Lowering                                                                          | .107 |

| Chapt | ter |         |                                                                   | Page |

|-------|-----|---------|-------------------------------------------------------------------|------|

|       |     | 6.6.3   | Hot Carrier Effects                                               | 112  |

|       | 6.7 | •       | rison Between a 1μm (0.5μm + 0.5μm) Gate DMG-HFE<br>Gate SMG-HFET |      |

|       | 6.7 | Summa   | ıry                                                               | 117  |

| 7     | DMG | -HFET F | FABRICATION AND EXPERIMENTAL RESULTS                              | 119  |

|       | 7.1 | Introdu | action                                                            | 119  |

|       | 7.2 | HFET    | Fabrication Process                                               | 120  |

|       | 7.3 | DMG S   | Structure Fabrication                                             | 123  |

|       | 7.4 | Device  | performance                                                       | 126  |

|       |     | 7.4.1   | I-V Characteristics                                               | 127  |

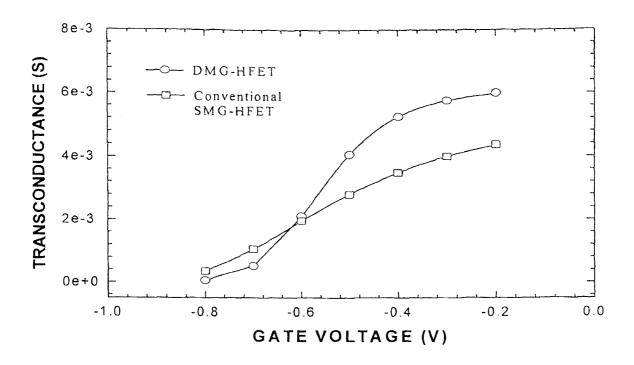

|       |     | 7.4.2   | The Tansconductance                                               | 127  |

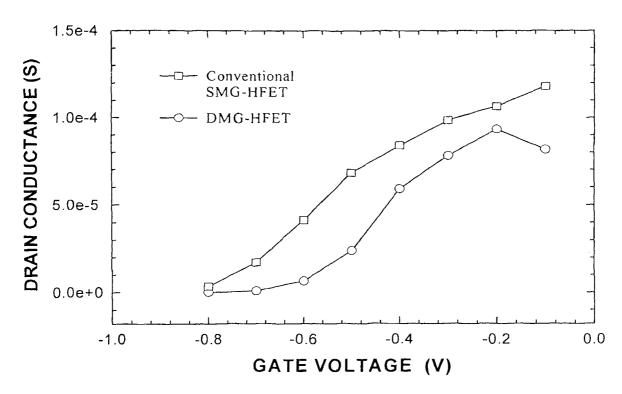

|       |     | 7.4.3   | The Drain Conductance                                             | 130  |

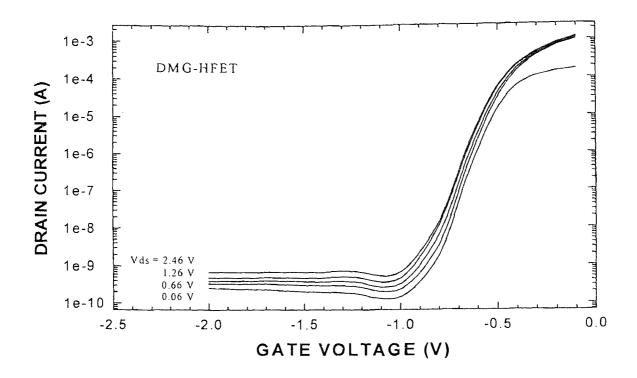

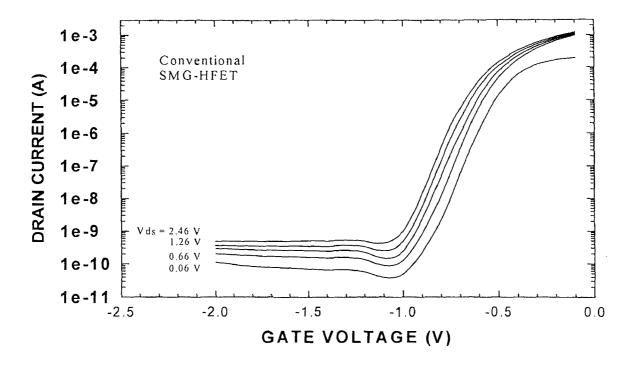

|       |     | 7.4.4   | Subthreshold Behaviors                                            | 130  |

|       | 7.5 | Summ    | ary                                                               | 132  |

| 8     | CON | CLUSIO  | N                                                                 | 134  |

|       | 8.1 | Summ    | ary                                                               | 134  |

|       |     | 8.1.1   | Analytical Study of Dual Gate FETs                                | 134  |

|       |     | 8.1.2   | Numerical Simulation of DMG-FETs                                  | 135  |

|       |     | 8.1.3   | Experimental Realization of DMG-HFET and Its Results              | ·136 |

| Chapter                                               |

|-------------------------------------------------------|

| APPENDIX A PISCES AND THE SIMULATION DETAILS          |

| A.1 Carrier Transport Model                           |

| A.2 Material Properties for Heterostructures          |

| A.2.1 Material Parameters for Device Simulation       |

| A.2.2 Interpolation Scheme for Composition Dependence |

| A.2.3 Parameter for Base Materials                    |

| A.3 Mobility Models                                   |

| A. 3.1 Low Field Mobility models                      |

| A. 3.2 Mobility Dependence on Longitudinal Field143   |

| A.4 Simulation Example                                |

| REFERENCES                                            |

### LIST OF TABLES

| Table |                                   | Page |

|-------|-----------------------------------|------|

| 3.1   | Assumed and Calculated parameters | 36   |

| A.1   | Material Parameters               | 140  |

| A.2   | Constant Mobility Used in PISCES  | 142  |

| A.3   | GaAs Parameters                   | 142  |

### LIST OF FIGURES

| Figur | e Pa                                                                                                                                                                                 | ge         |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

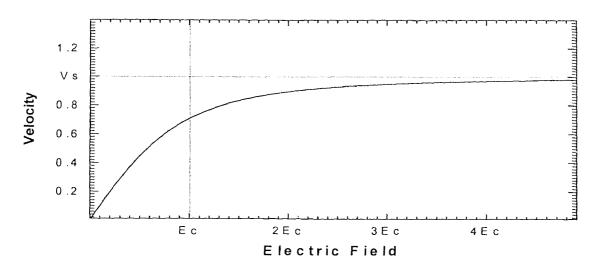

| 3.1   | The relationships of $(v_d - E)$ dependence defined by equation (2.1)                                                                                                                | 26         |

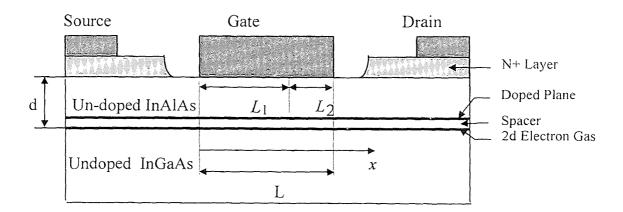

| 3.2   | A Cross-sectional Schematic Diagram of the Single Gate HFET Structure                                                                                                                | 27         |

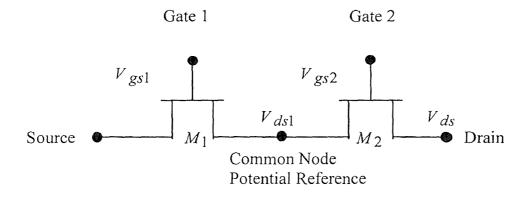

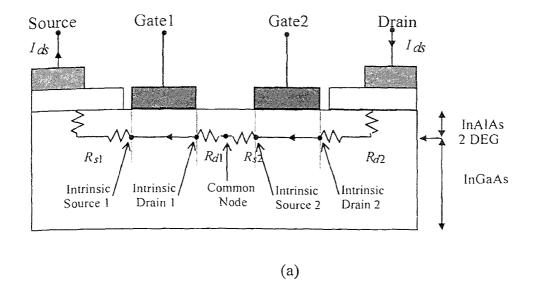

| 3.3   | Configuration of dual gate HFET                                                                                                                                                      | 30         |

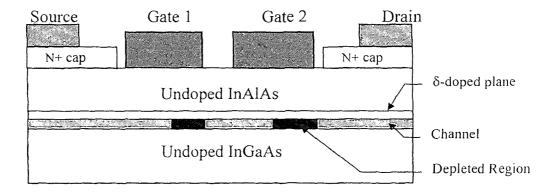

| 3.4   | Dual-Gate Structure with a single Recess                                                                                                                                             | 31         |

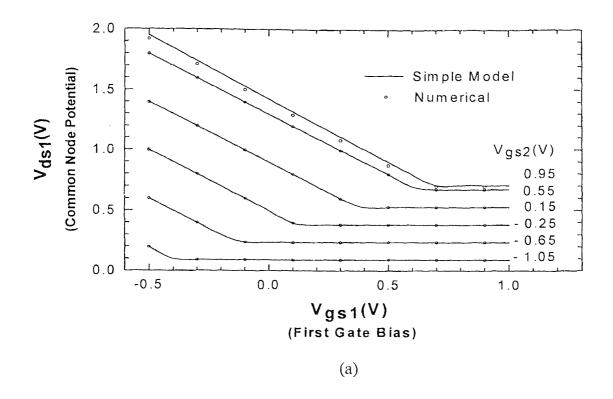

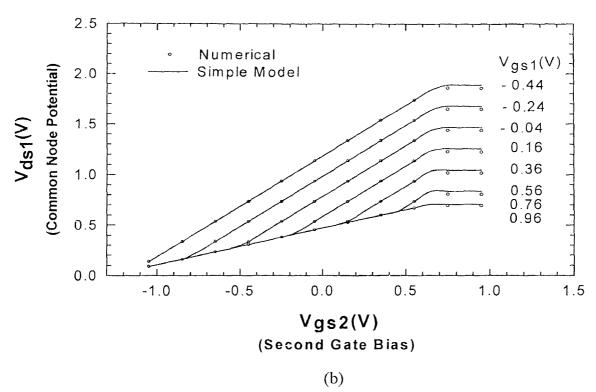

| 3.5   | Comparison of the dependences of DGFET common node $V_{ds1}$ upon $V_{gs1}$ and $V_{gs2}$ at $V_{ds}$ =2V                                                                            | 3 <i>5</i> |

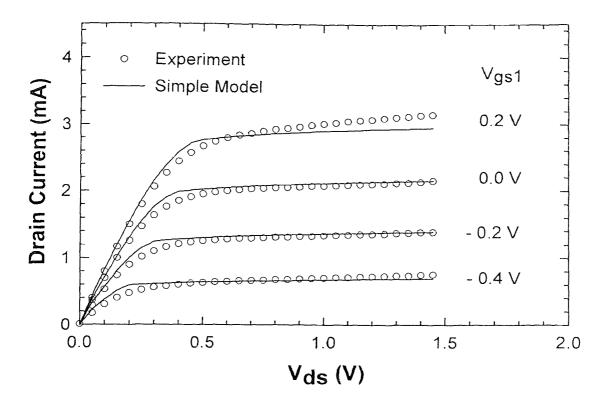

| 3.6   | DGHFET I-V characteristics of the first gate at $V_{gs2}$ = 0V for a 0.2 $\mu$ m dual gate HFET. The solid lines are caculated results and circled markers are our experimental data | 40         |

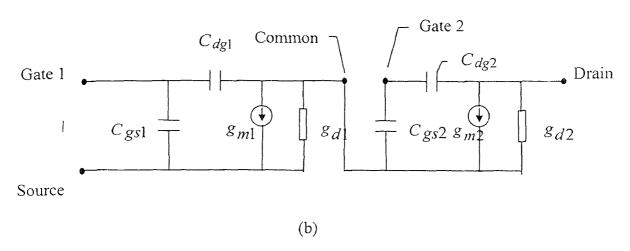

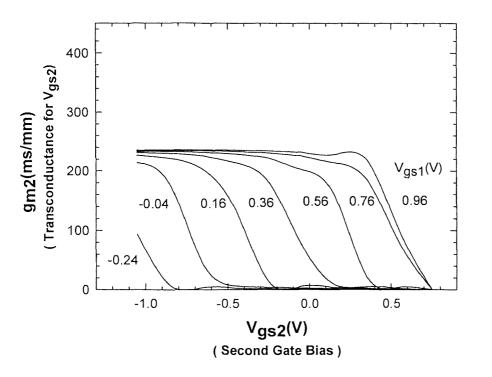

| 4.1   | Intrinsic small signal Equivalent circuit of Dual Gate HFET                                                                                                                          | 47         |

| 4.2   | Dual Gate HFET Eqivalent Circuit with $V_{gs2}$ Biased at Certain Value                                                                                                              | 47         |

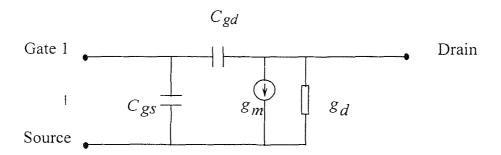

| 4.3   | Gate voltage dependence of the transconductance for the first equivalent gate with several $V_{gs2}$ bias. The dotted line represents single gate results                            | 50         |

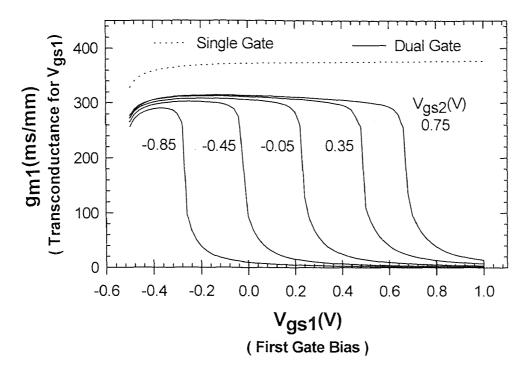

| 4.4   | Gate voltage dependence of the transconductance for the second equivalent gate with several $V_{gs1}$ bias                                                                           | 50         |

| 4.5   | Gate voltage dependence of the $C_{gs}$ for several values of $V_{gs2}$ and SGFET5                                                                                                   | 52         |

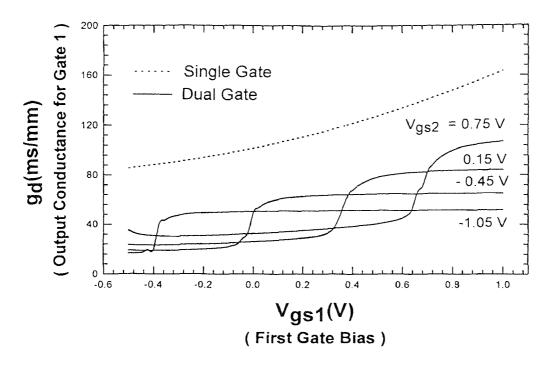

| 4.6.  | Variations with $V_{gs1}$ of the output conductance for the first gate of DGFE5                                                                                                      | 55         |

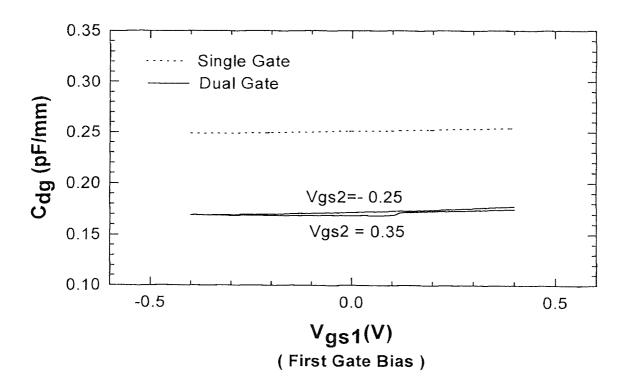

| 4.7   | Varitions with $V_{gs1}$ of the feedback capacitance with $V_{gs2}$ biased at -0.25V and -0.35V. The dotted line represents single gate                                              | 55         |

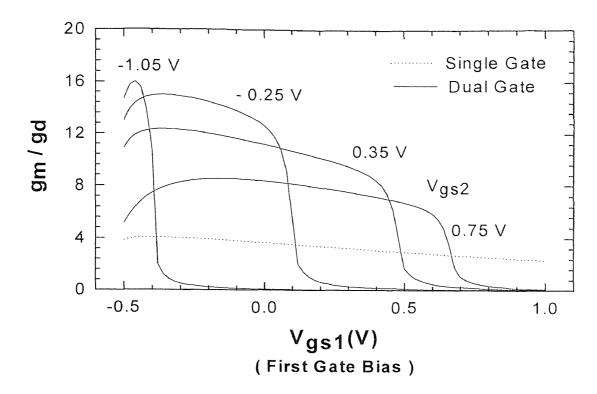

| 4.8   | $g_m/g_d$ ratio as a function of control gate voltage $V_{gs1}$ at $V_{ds} = 2V$ in DGFET(solid curves) and SGFET(dotted curve)                                                      | 57         |

| Figure | Pa <sub>i</sub>                                                                                                                                                                                                    | ge         |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

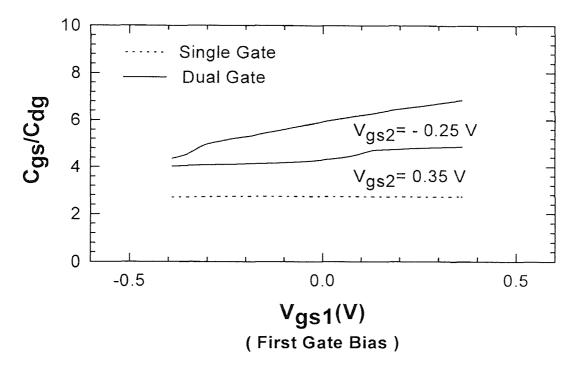

| 4.9    | $C_{gs}/C_{dg}$ ratio as a unction of control gate voltage $V_{gs1}$ at $V_{ds}$ =2V in DGFET(solid curves) and SGFET(dotted curve)                                                                                | 57         |

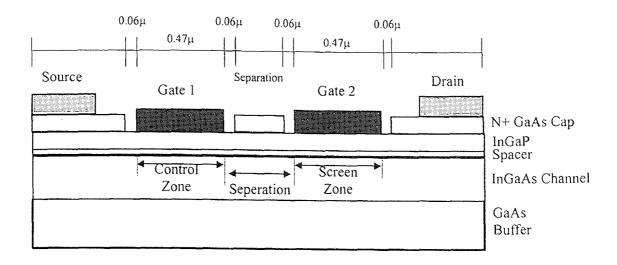

| 5.1    | Typical Schematic Cross Section of Dual Gate HFET                                                                                                                                                                  | 5 <i>5</i> |

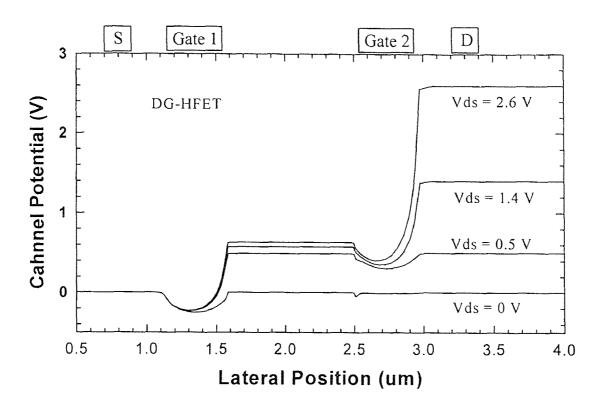

| 5.2    | Profile of potential variation along the channel for dual gate HFET with gate to gate separation of 1 $\mu$ m ( Gate length of both gates are 0.47 $\mu$ m )                                                       | 65         |

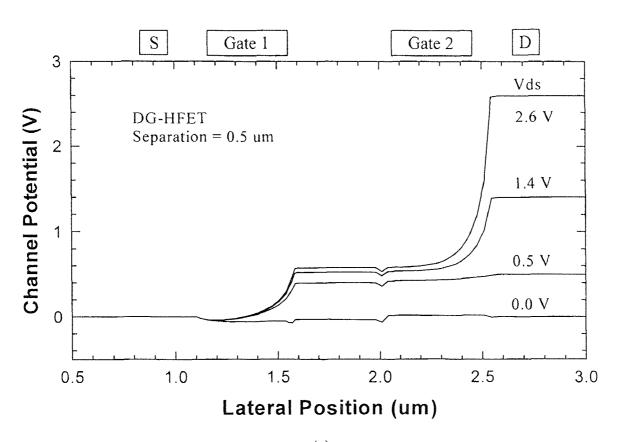

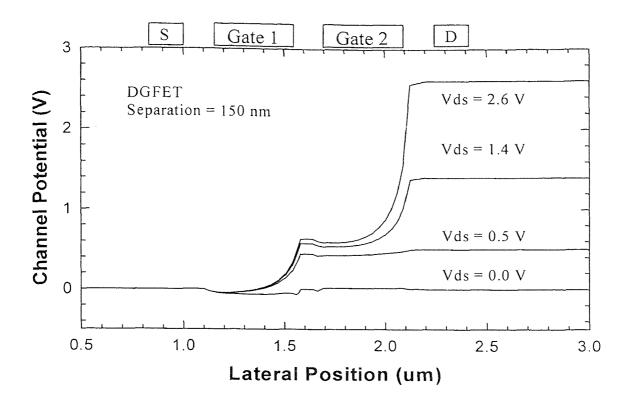

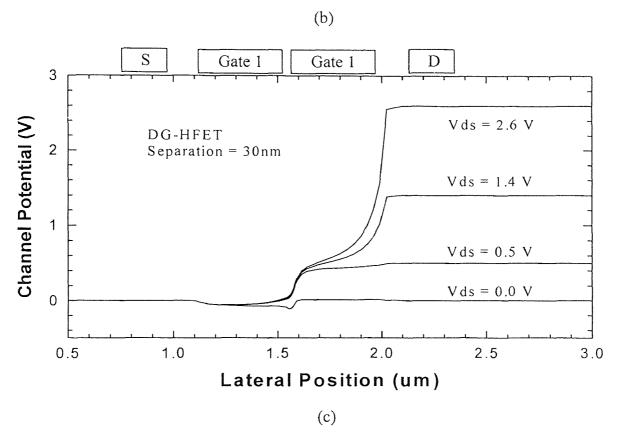

| 5.3    | Spatial variation of channel potential for various values of gate separations.  Screening effect is retained true for all the gate separations studied                                                             | 58         |

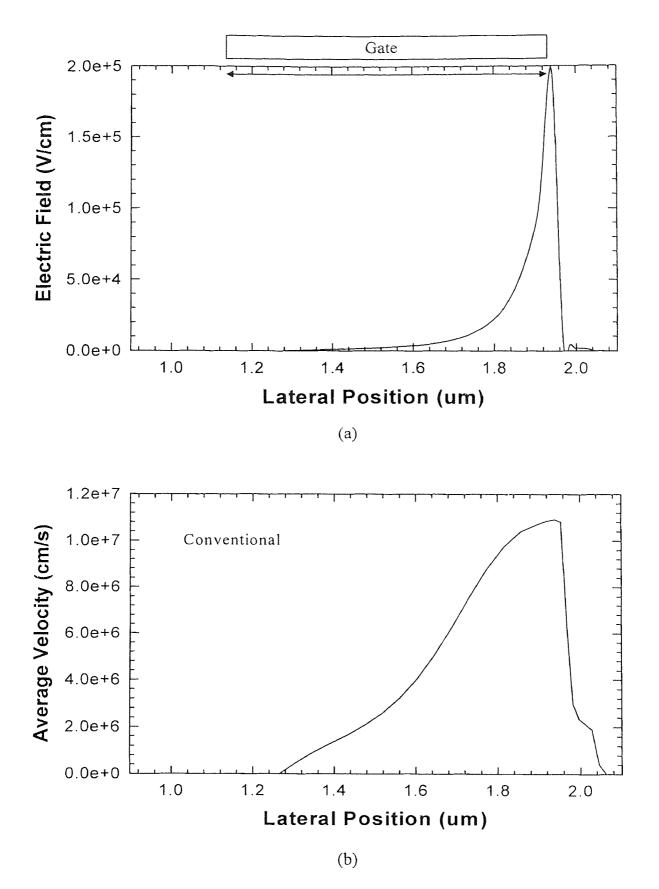

| 5.4    | Profile of electric field and electron velocity along the channel for conventional HFET with a gate length of 0.8 µm                                                                                               | 70         |

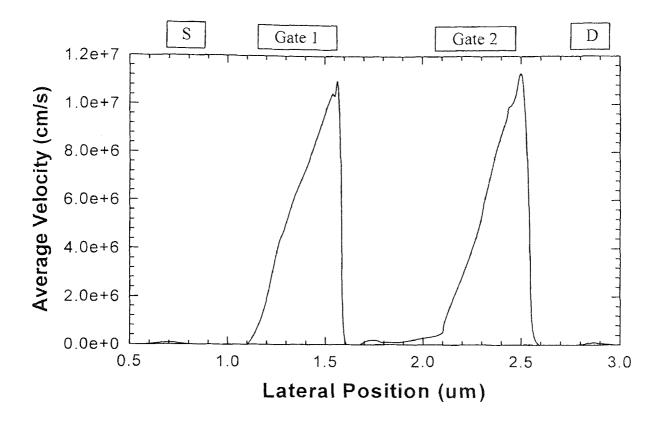

| 5.5    | The electron average velocity profile of a conventional DG-HFET with a large gate separation of 0.5 µm.                                                                                                            | 7 1        |

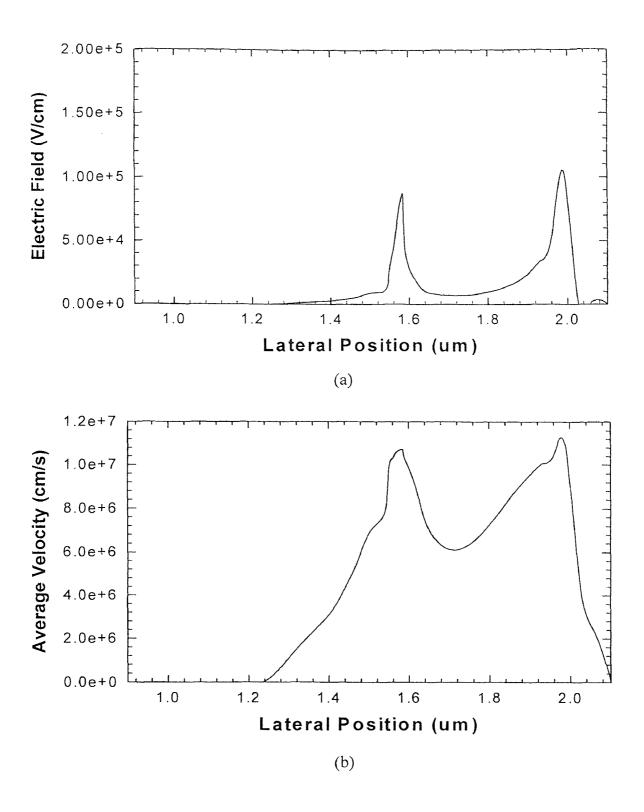

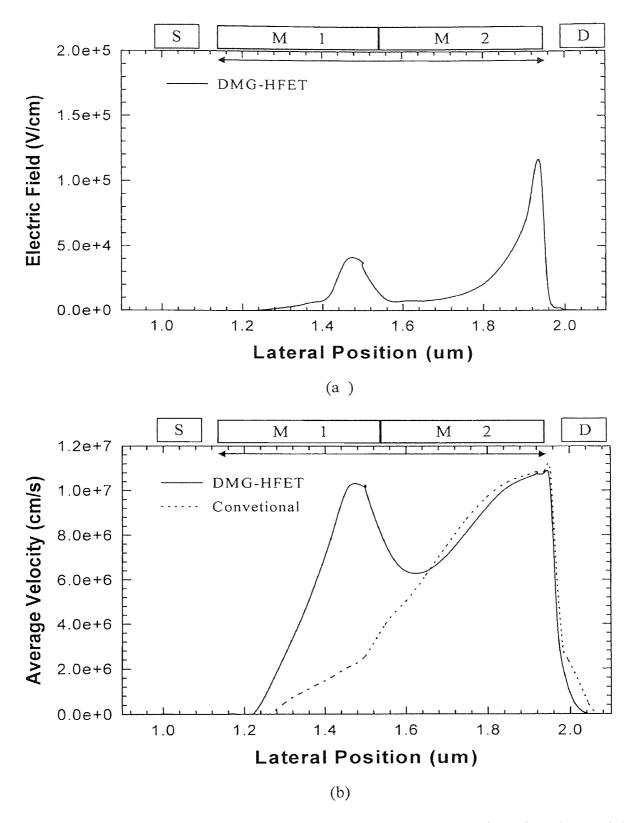

| 5.6    | The electric field (a) and average velocity (b) profiles along the channel of DG-HFET with extremely small gate separation (30 nm). Electric fields in the two gate regions overlap resulting velocity enhancement | 73         |

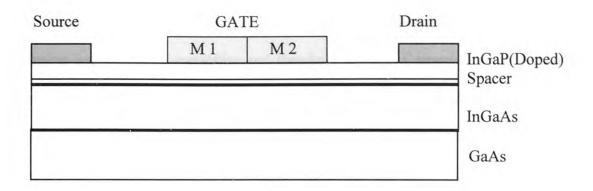

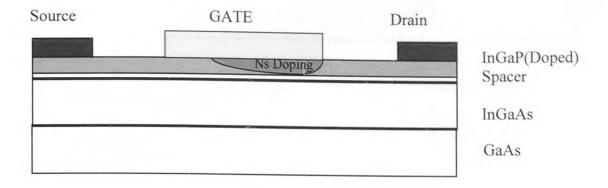

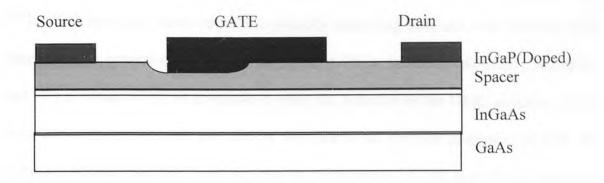

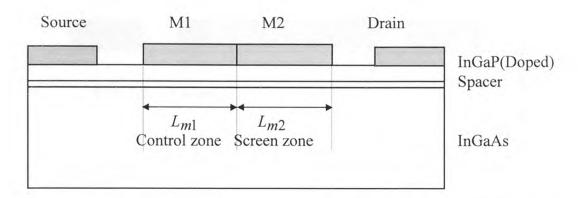

| 5.7    | Dual Material Gate HFET (DMHFET) structure consisting of gate using two lateral contacting materials with different work function                                                                                  | 75         |

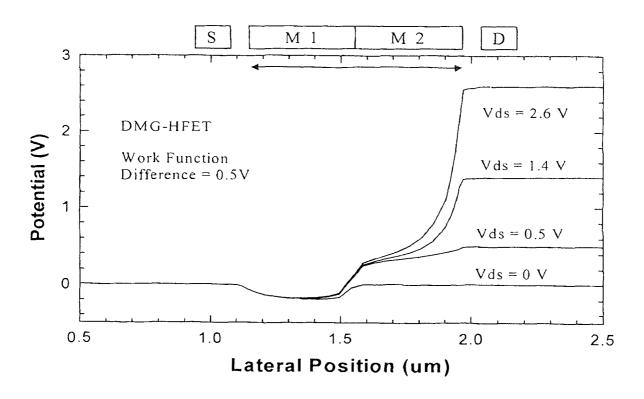

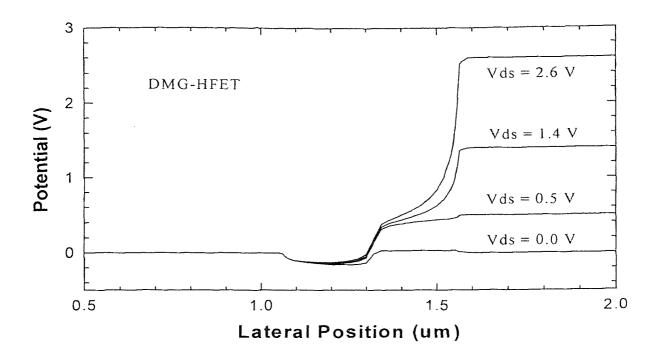

| 5.8    | The channel potential profile for dual material gate HFET with gate length of 0.8 µm. The applied gate voltage is -0.6 V. Strong screening effect is demonstrated                                                  | 76         |

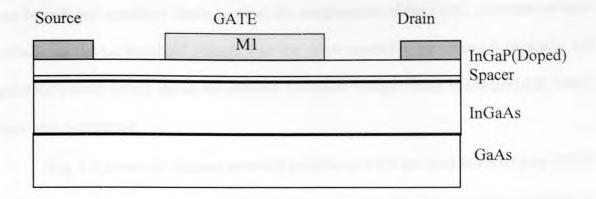

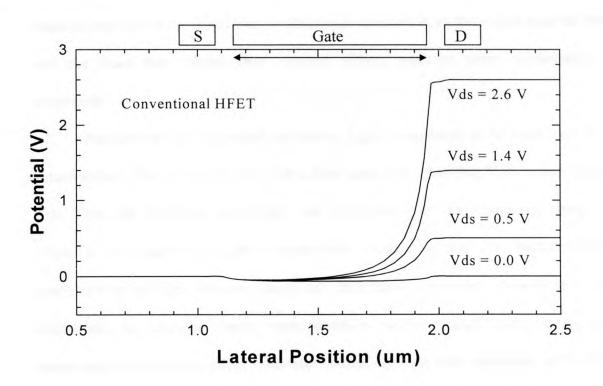

| 5.9    | Schematic cross section of conventional single material gate HFET                                                                                                                                                  | 77         |

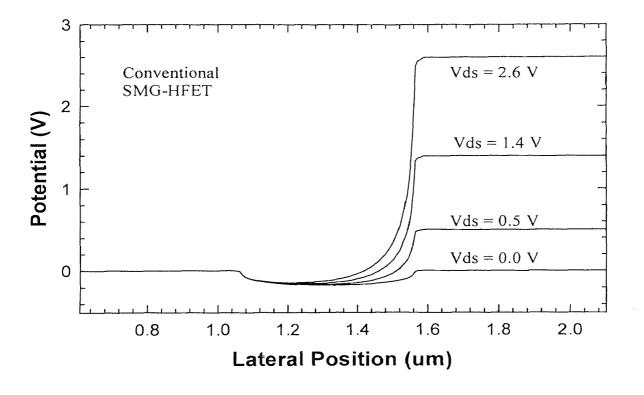

| 5.10   | The channel potential profiles of conventional HFET with different drain biases. The gate length is 0.8 µm; gate bias is -0.6 V. There is no screening effect in this situation                                    | 77         |

| 5.11   | Electric field (a) and average electron velocity (b) profile of dual material gate HFET. In (b), the velocity profile of conventional single material gate HFET is also show for comparison                        | 79         |

| Figure | ${f P}_{f a}$                                                                                                                                                                                                                                          | age            |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 5.12   | Schematic cross section of asymmetric channel HFET. More n-type doping is introduced in the region near drain making drain side threshold voltage less positive                                                                                        | .82            |

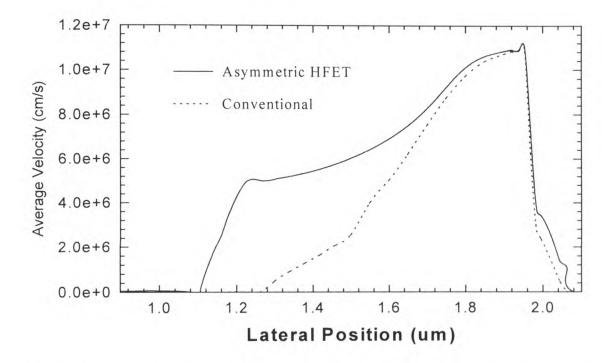

| 5.13   | Channel electron average velocity profile of asymmetric HEFT. Velocity enhancement is achieved by asymmetric threshold voltage distribution                                                                                                            | .82            |

| 5.14   | Channel potential profiles of normal asymmetric HEFT. There is no evidence of screening effect                                                                                                                                                         | 83             |

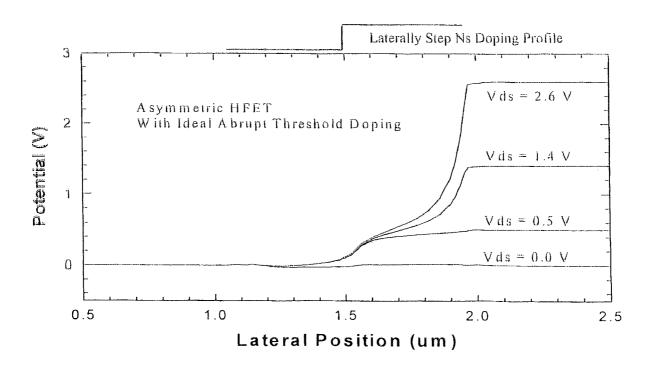

| 5.15   | The channel potential profiles of Asymmetric HEFT with ideal step threshold doping profile. Excellent screening effect shows up only at this t heoretic situation                                                                                      | 83             |

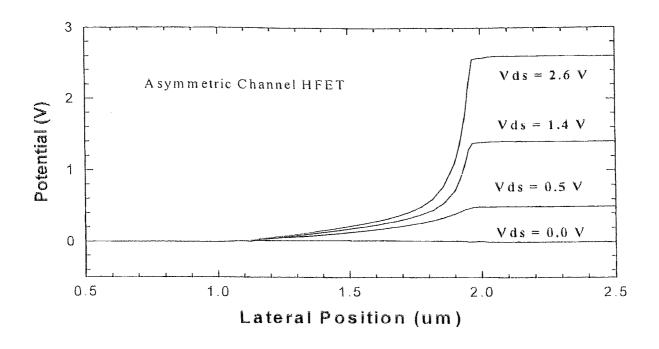

| 5.16   | Another DMHFET related asymmetric HFET structure using dual recess wet etching technology. Different threshold is realized via different channel depths                                                                                                | 85             |

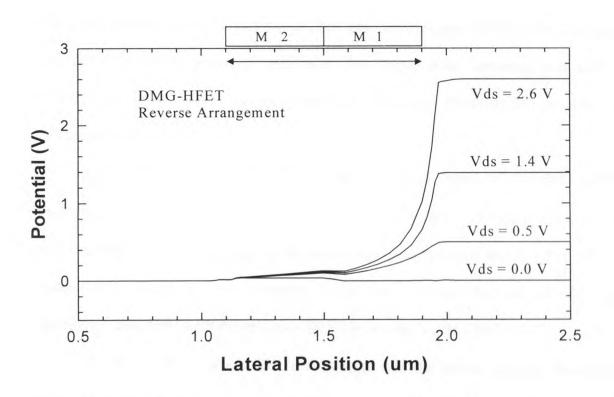

| 5.17   | Channel potential distribution of dual material gate HFET when inverse the gate structure to make threshold voltage near source smaller than that near the drain ( $V_{t1} < V_{t2}$ ). There are not screening effect and velocity enhancement effect | 85             |

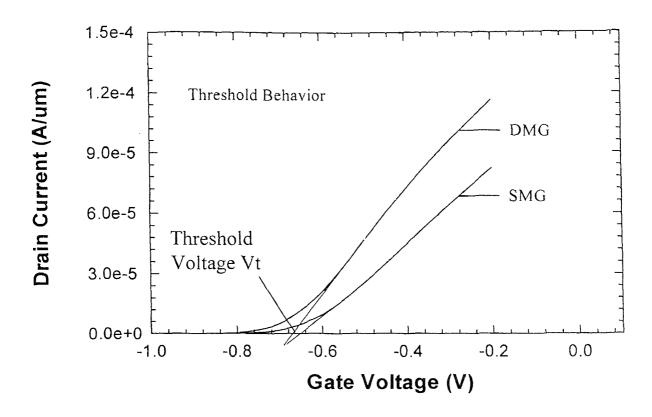

| 6.1    | The threshold behaviors of dual material gate HFET (DMG-HFET) and conventional SMG-HFET. Very close values (-0.67V for DMG and -0.65V for SMG )of threshold voltages have been extrapolated                                                            | 90             |

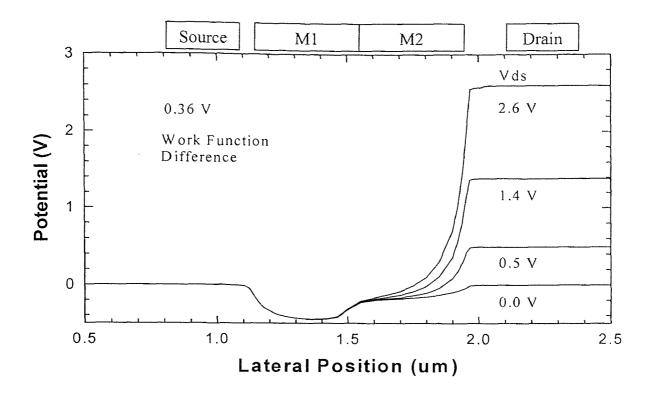

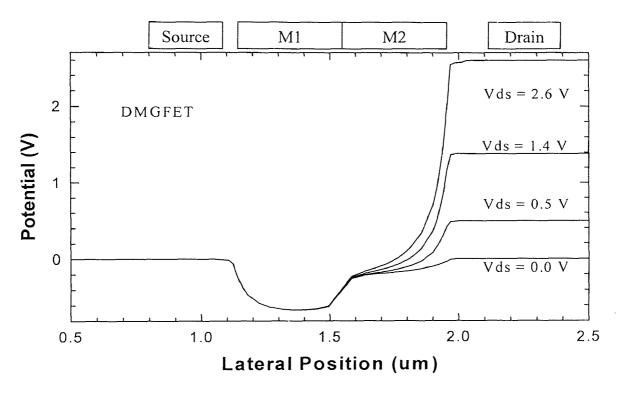

| 6.2    | Channel potential profiles of DMG-HFET with work function difference of 0.36 V                                                                                                                                                                         | 93             |

| 6.3    | Channel potential profiles of DMG-HFET with work function difference of 0.63 V                                                                                                                                                                         | <del>)</del> 3 |

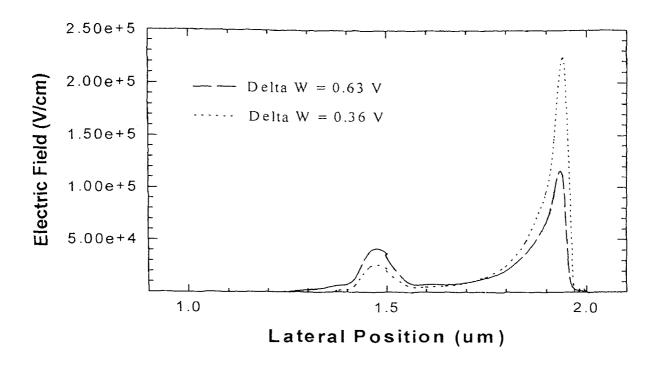

| 6.4    | Channel electric field distributions for two typical work function differences $\Delta W$ of 0.36V and 0.63V, respectively. The external biases are                                                                                                    | 14             |

| Figur | e Page                                                                                                                                                                                                                   |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

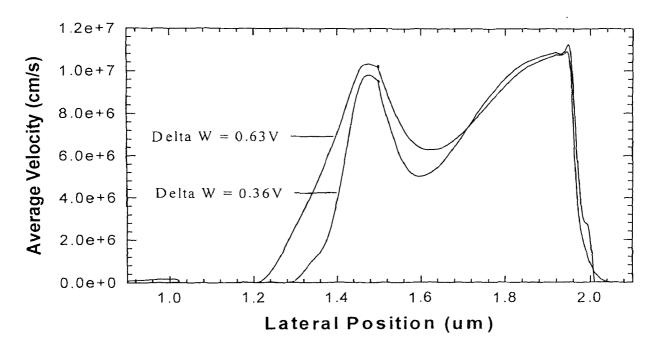

| 6.5   | Channel electron velocity profiles of DMGFET for different work function differences under same biases                                                                                                                   |

| 6.6   | Schematic cross-section of a dual material gate HFET. The two components of the gate region are shown95                                                                                                                  |

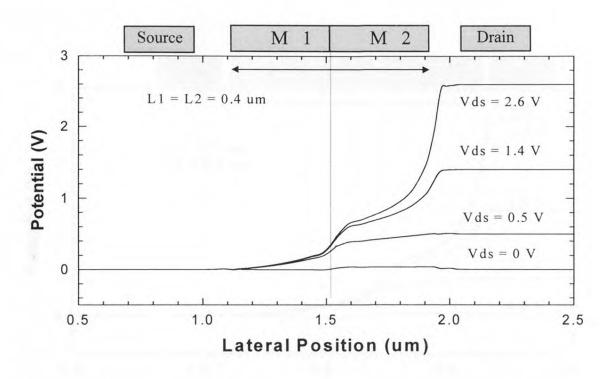

| 6.7   | Channel potential profile of DMG-HFET with equal lengths of $L_{m1}$ and $L_{m2}$ .  The gate bias is 0V96                                                                                                               |

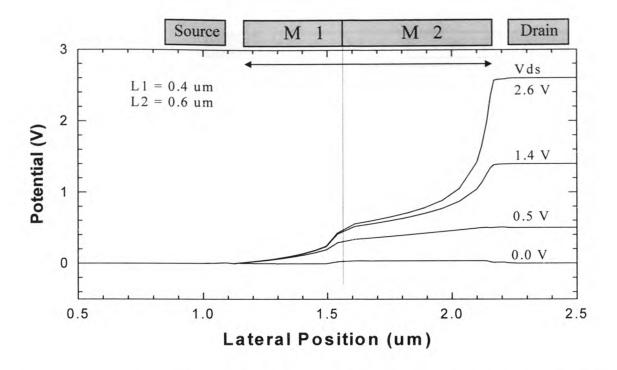

| 6.8   | The channel potential profiles of DMG-HFET with longer $L_{m2}$ . The gate bias is $0.0V$                                                                                                                                |

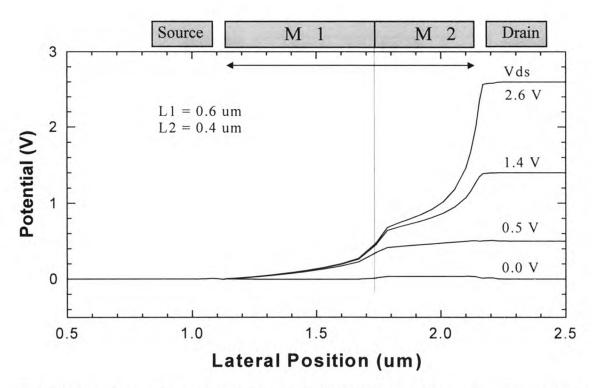

| 6.9   | The channel potential profiles of DMG-HFET with longer $L_{m1}$ . The gate bias is $0.0 \text{V}$                                                                                                                        |

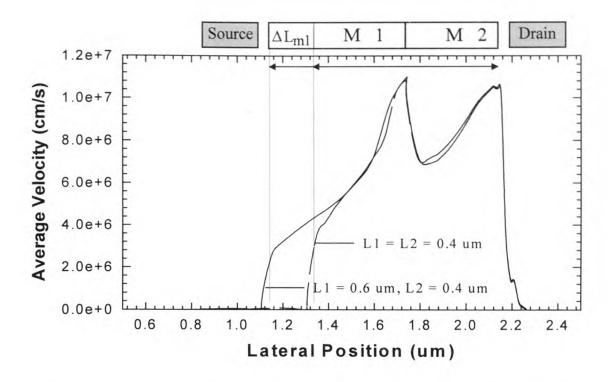

| 6.10  | The channel velocity profile changes with the $L_{m1}$ variation for DMG-HFET                                                                                                                                            |

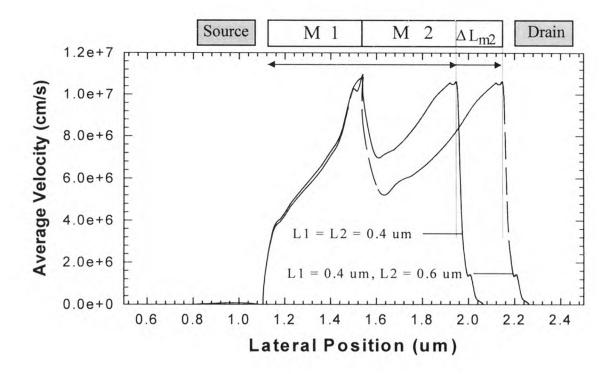

| 6.11  | The channel velocity profile changes with the $L_{m2}$ variation in DMG-HFET98                                                                                                                                           |

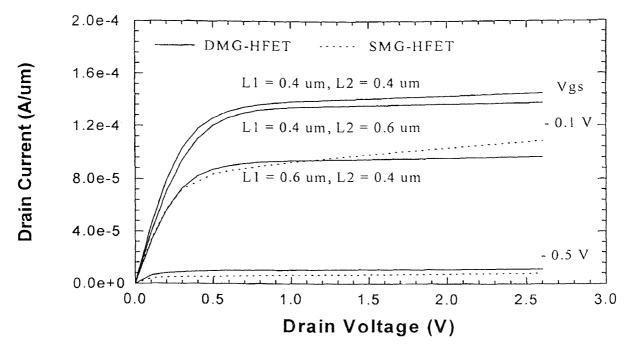

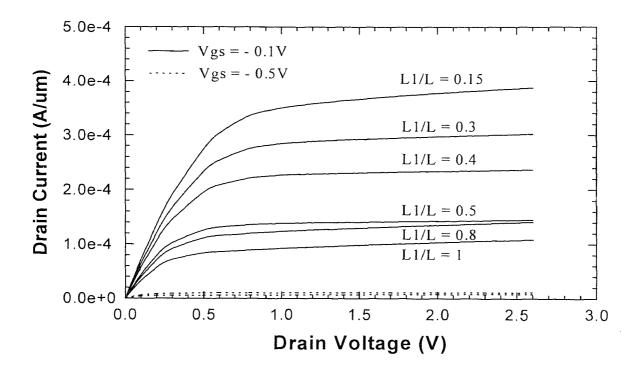

| 6.12  | The I-V characteristics of various $L_{m1}$ and $L_{m2}$ values of DMGFET. Conventional SMGFET's curves are also included for comparison99                                                                               |

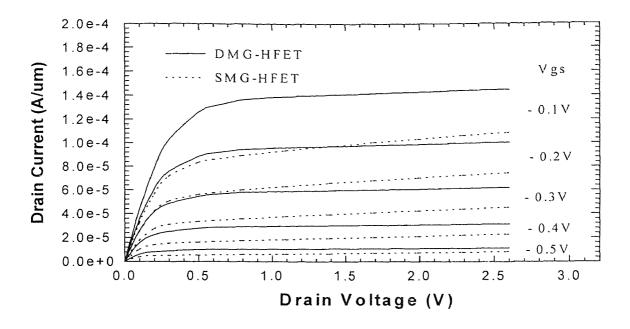

| 6.13  | The I-V characteristics of DMG-HFET with $L_{m1} = L_{m2} = 0.4 \mu\text{m}$ and SMG-HFET with gate length of 0.8 $\mu\text{m}$                                                                                          |

| 6.13  | The drain current variation with the change of gate sizes $L_{m1}$ or $L_{m2}$ , where $L_{m1} + L_{m2} = L$ fixed at 0.8 µm. Two gate voltage are used and the threshold voltages are almost same in all the situations |

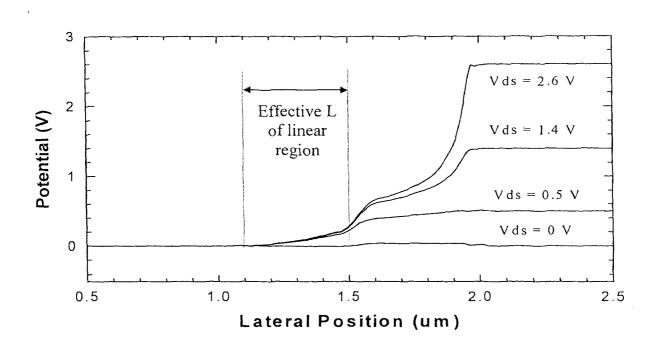

| 6.15  | Channel potential distribution of SMG-HFET. The effective linear region length $L$ is seen continuously decreases with the drain bias increase105                                                                        |

| 6.16  | Channel potential distribution of DMG-HFET. The effective linear region length L is seen nearly remain unchanged with the drain bias over                                                                                |

| Figur | e Page                                                                                                                                                                                                                                                 |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

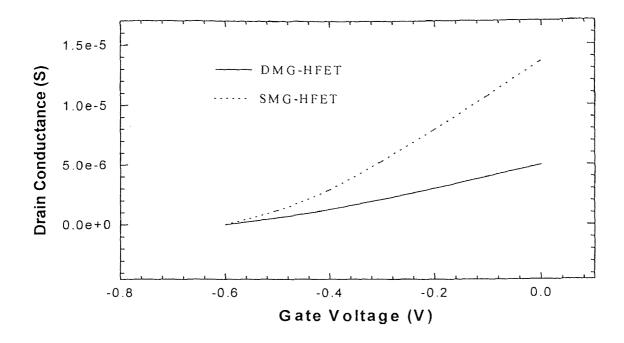

| 6.17  | The drain conductance behaviors of both DMG-HFET and SMG-HFET106                                                                                                                                                                                       |

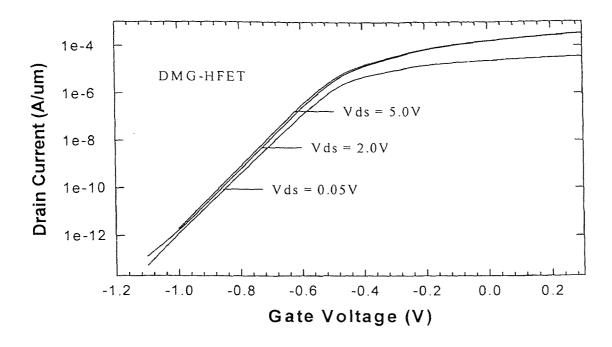

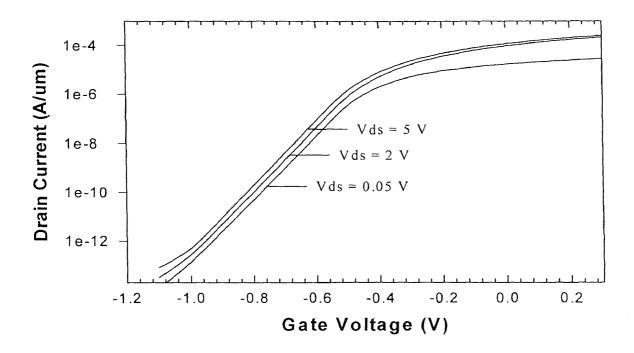

| 6.18  | Plot of log $I_{ds}$ versus $V_{gs}$ for DMG-HFET operated below threshold, with $V_{ds}$ as the parameter. The value of $\Delta V_{gs}/\Delta V_{ds}$ for a fixed value of $I_{ds}$ (e.g., $1\times10^{-7}$ A/µm) is used to characterize the DIBL109 |

| 6.19  | Plot of log $I_{ds}$ versus $V_{gs}$ for conventional SMG-HFET operated below threshold, with $V_{ds}$ as the parameter. $\Delta V_{gs}/\Delta V_{ds}$ value is also used                                                                              |

| 6.20  | The calculated channel potential of DMG-HFET for different drain biases110                                                                                                                                                                             |

| 6.21  | The calculated channel potential of SMG-HFET for different drain biases                                                                                                                                                                                |

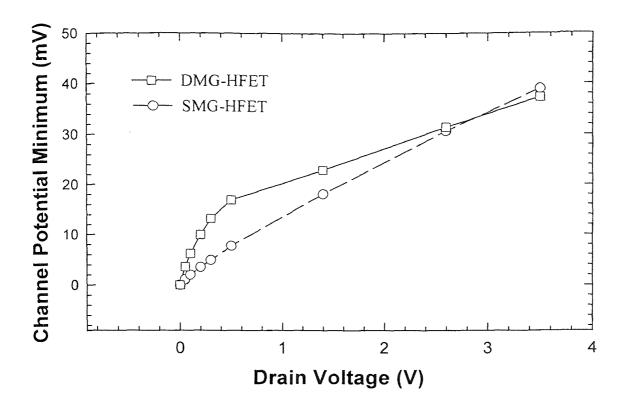

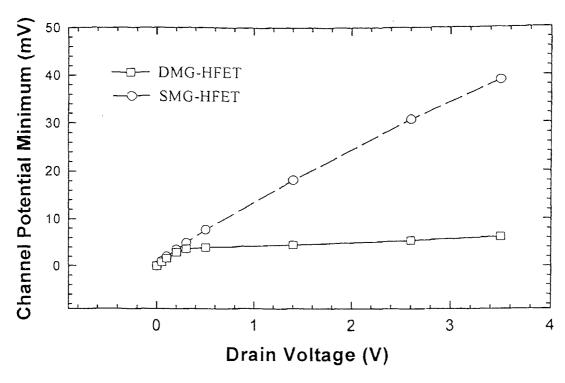

| 6.22  | Variation of channel potential minimum $\varphi_{\min}$ or potential energy barrier height versus $V_{ds}$ for DMG-FET and SMG-FET with same channel length                                                                                            |

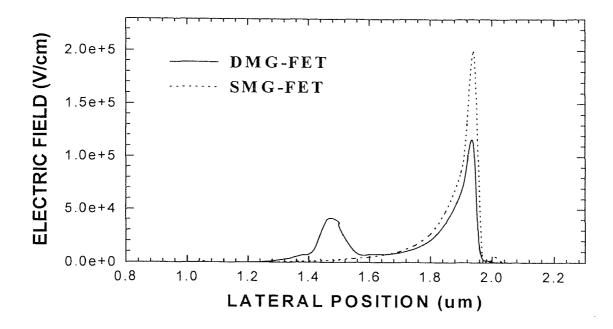

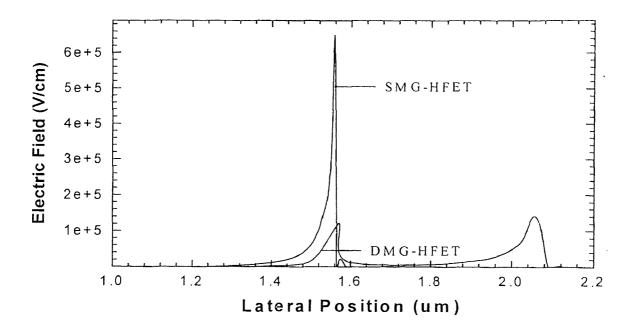

| 6.23  | The longitudinal channel electric field behavior of DMG-HFET and SMG-HFET in saturation. ( $V_{gs}$ = -0.4 V and $V_{ds}$ = 1.4 V)                                                                                                                     |

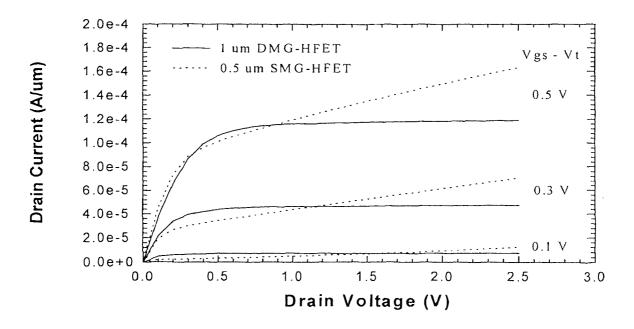

| 6.24  | I-V characteristics of a 0.5 $\mu$ m gate SMG-HFET and a 1 $\mu$ m (0.5 $\mu$ m + 0.5 $\mu$ m) gate DMG-HFET                                                                                                                                           |

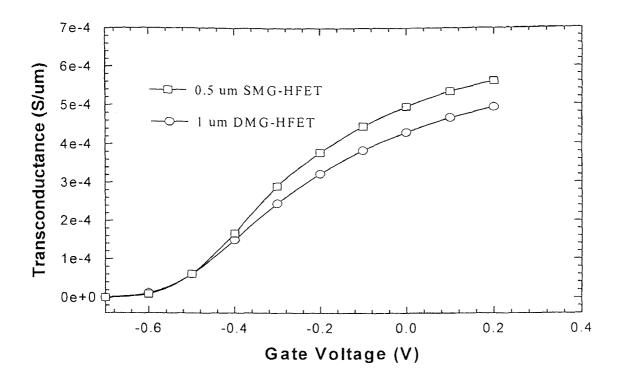

| 6.25  | The transconductance behaviors of the 0.5 $\mu m$ gate SMG-HFET and 1 $\mu m$ (0.5 $\mu m$ + 0.5 $\mu m$ ) gate DMG-HFET                                                                                                                               |

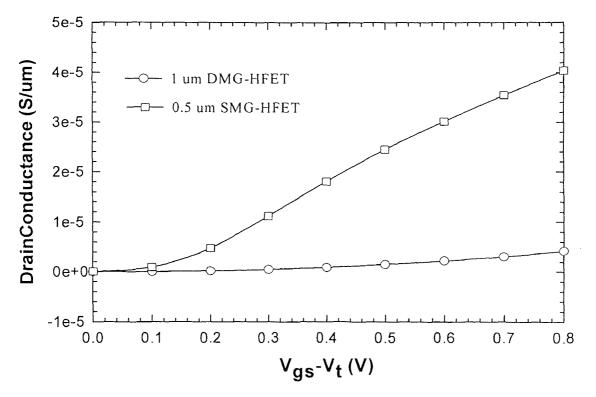

| 6.26  | Drain conductance behaviors of the two HFETs115                                                                                                                                                                                                        |

| 6.27  | Comparison of the channel potential minimum versus drain bias between a 0.5 $\mu m$ gate SMG-HFET and a 1 $\mu m$ ( 0.5 $\mu m$ + 0.5 $\mu m$ ) gate DMG-HFET                                                                                          |

| 6.28  | Longitudinal channel electric field distributions for a 0.5 µm gate SMG-HFET                                                                                                                                                                           |

| Figur | e Page                                                                                                                                     |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------|

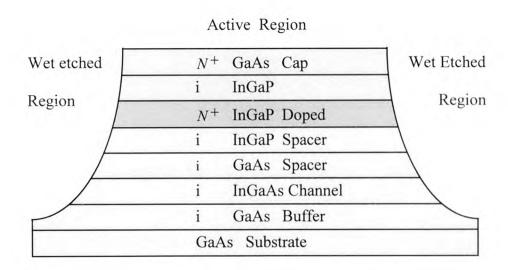

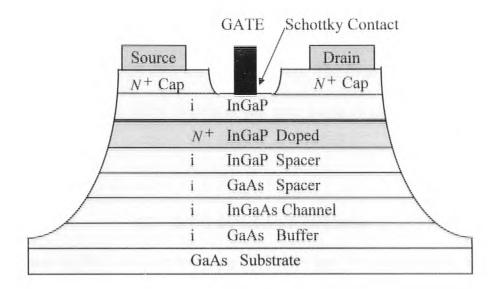

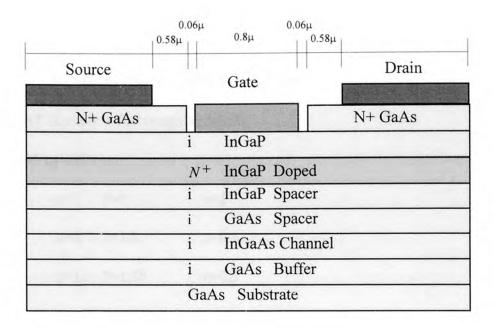

| 7.1   | Schematic structure of the starting MBE grown psudomophic heterojunction materials                                                         |

| 7.2   | Process cross section of the active region after the mesa etching to form the isolation between active regions                             |

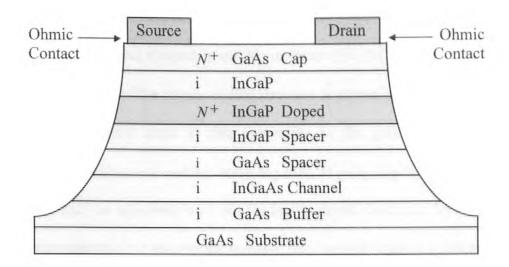

| 7.3   | Process cross section after the formation Source/Drain ohmic contact                                                                       |

| 7.4   | Process cross section after the gate metallization. A typical HFET is fabricated                                                           |

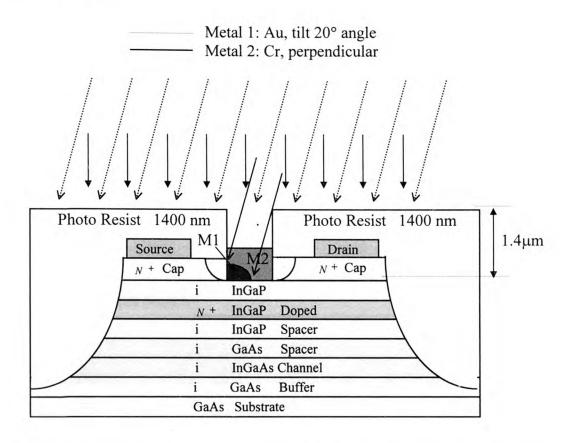

| 7.5   | Schematic diagram of the DMG structure fabrication process. The large work function metal is Au and the small work function metal is Cr124 |

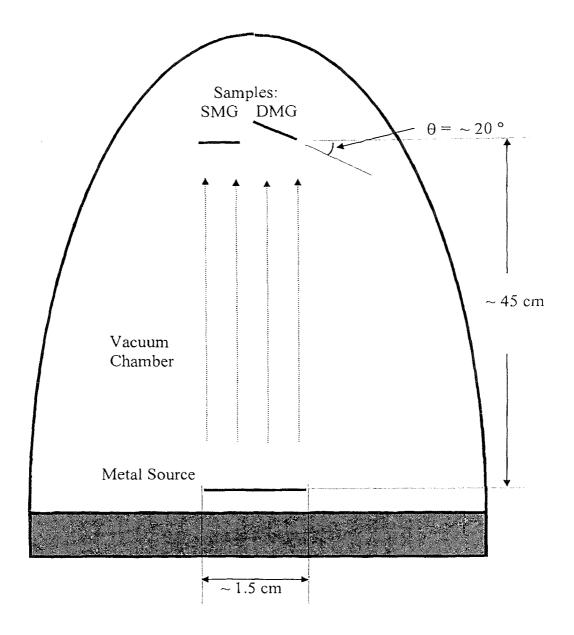

| 7.6   | Simplified schematic diagram of the evaporation method used to fabricate both SMG and DMG in the same vacuum system                        |

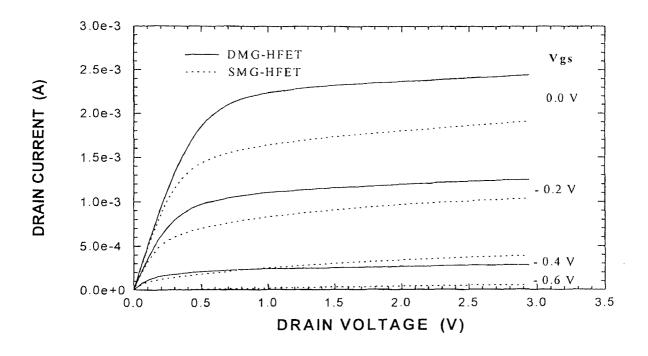

| 7.7   | Measured output characteristics of DMG-HFET (solid line) and SMG-HFET (dashed line)                                                        |

| 7.8   | Measured transconductance as a function of gate voltage for DMG-HFET and SMG-HFET                                                          |

| 7.9   | Measured drain conductance versus gate voltage for DMG-HFET and conventional SMG-HFET                                                      |

| 7.10  | Measured subthreshold characteristics of DMG-HFET at various $V_{ds}$ 110                                                                  |

| 7.11  | Measured subthreshold characteristics of SMG-HFET at various $V_{ds}$ 120                                                                  |

#### CHAPTER 1

#### INTRODUCTION

#### 1.1 Motivation

High performance high speed field effect transistors (FET), including MOSFET (metal-oxide-semiconductor FET), MESFET (metal-semiconductor FET), and HFET (heterostructure FET), have been playing increasingly important roles in high performance, high speed and high density IC applications, both analog and digital. High figure of merit values, such as high transconductance and drain impedance, are required. During the past decade, excellent high speed and performance have been achieved (see for example [1]) through improved design, the use of higher quality material, and the shink of the device structure. However, two major problems persist, namely, short channel effects and gate transport inefficiency.

The predominant feature of the detrimental short channel effects is high drain conductance, which also prevents the pinch off and leads to a shift in threshold voltage, and therefore  $V_T$  dependence on drain voltage [2], [3]. The phenomenon has been previously described in several cases of FETs (see for example [4]).

It has been demonstrated that the dual gate (DG) FET structure is an effective means to overcome the short channel effects [5], [6]. The DG-FET can be treated as a cascade connection of two FETs as long as the separation between the two gates is large compared to the channel thickness. But the evaluation of the dependence of its performance on DC bias and on its technological parameters is still extremely complicated due to an additional freedom of variables. Hence, it has become important that the dual gate analytical model be available for fully utilizing the benefits of the DG

structure, since the devices would have to be designed based on the analytic understanding of the device.

Gate transport efficiency is related to the average electron transport velocity traveling through the channel, which is related to the electric field distribution along the channel. In a field effect transistor, electrons enter into the channel with a low initial velocity, gradually accelerating towards the drain. As numerous numerical simulations of FETs indicate, the maximum electron drift velocity is reached near the drain [7]. The electrons move very fast in the region near the drain but relatively slow in the region near the source. Hence, the speed of the device is affected by a relatively slow electron drift velocity in the channel near the source region.

In 1989, M. Shur [8] theoretically suggested a split gate (SG) FET structure to enhance the gate transport efficiency. This device consists two closely separated gates with the gate closer to the drain having a positive voltage offset with respect to the gate near the source. Therefore, the electric field along the channel becomes more uniform and the electrons near the source are accelerated more rapidly. As a consequence, the average electron velocity in the channel is increased. However, the attempt to realize the SG-FET [9] has not been satisfactory up till now. The challenge is not only related to technological difficulties, but, above all, also to the inherent fringing capacitance between the two gates which rises significantly as separation of the two gates become close to or smaller than the channel depth as the device requires. This is detrimental to the device high speed performance. Thus, other ways have been looked for to take full advantage of the high efficiency electron transport without the inherent capacitance effect.

This thesis focuses on issues related to the reduction of short channel effects and the improvement of gate transport efficiency via dual gate or dual gate related approach.

Suppressing short channel effects hinges on an in-depth understanding of dual gate effects involved. Hence, the first part of this thesis attempts to present a new and simple analytic dual gate model by considering one of the most important parameters in calculating dual gate characteristics — the common node potential at the mid point between the two channels, fundamental treatment of which has been lacking in dual gate modeling.

Enhancing dual gate transport efficiency mandates a scaling in gate separation to less than channel thickness. As a consequence, parasitic gate to gate fringing capacitance [10] becomes dominant or comparable to intrinsic capacitance. This is extremely harmful to device's high frequency performance. Thus, a new approach to device structure design is needed. To this end, the split gate effect and the concept developed in the first part of this thesis for dual gate HFET are extended to a new device structure — a dual material gate (DMG) HFET. We select the HFET as a vehicle to explore the concept of DMG, which is presented in the main part of this thesis as a generic device structure, valid for all kinds of FETs, including MOSFET, MESFET, and HFET.

If we use two different materials with different work functions for the two gates in a DG-HFET, and merge them into one single gate by connecting them laterally, we obtain a DMG-HFET. The advantage of DMG is that both short channel effects and gate transport efficiency can be improved considerably. In the main part of this thesis, the simulation, structure design, processing realization, and measured characteristics of the DMG-HFET are presented in detail.

### 1.2 Scope and Organization

Introduction of a new device requires four steps: present approach overview, now approach analytic analysis, numerical simulations and practical realization. The existing approaches provide basis for new device. The physics based analytic models can give an overall knowledge and insight of device behavior and predict its dynamic characteristics dependence on its technological parameters and bias conditions. Numerical simulations serve the purpose of providing detailed data to illustrate complex device phenomena. Thus, with the help of these two approaches, one can predict the characteristics, and therefore selectively target technology optimizations. This leads to much improved effectiveness of experimental approaches with a large number of technological parameters.

The scope of this thesis is based on the following systematic methodology for our new device construction. The first step involves analytical modeling and calculation of dual gate HFETs. Secondly, in order to develop our new device structure, dual gate and split gate effects are investigated using numerical simulations. Then, the dual material gate structure is presented and compared with other related device structures. Afterwards, the proposed DMG structure is simulated and studied extensively. Finally, the optimized device structure supported by simulations is fabricated and tested.

In chapter 2, an overview of the state-of-the-art HFET is presented together with the design and optimization of the single gate HFET structures. The approaches employed in this thesis to develop new device structure are also discussed.

As we mentioned, the objective of this thesis is to develop a novel high performance DMG-HFET, which is virtually an extension the dual gate structure. Since analytic analysis has been lacking for DG-HFETs, it is carried out in first few chapters of

the thesis. In this part, Chapter 3 provides the background of a DC model and the calculation of DC I-V characteristics. The mechanism developed in Chapter 3 is then employed in Chapter 4 to calculate the key small signal characteristics. A systematic analysis needed for understanding of the origin of dual gate effect and for further device design and optimizations is also made.

Chapter 5 is concerned with the more detailed numerical simulation and study. Based on the theoretic approach, the novel device structure--dual material gate (DMG) FET--is proposed and its new features are outlined using HFET as the vehicle. Chapter 6 deals with the design, optimization and characteristic simulation of the resulting new DMG-HFET.

Finally, in Chapter 7, the DMG-HFET processing procedure is presented. Our goal is to realize the device which improves both short channel effects and gate transport efficiency. The fabricated DMG-HFETs are characterized under a wide range of bias conditions. As expected, the new device does exhibit greatly improved transport efficiency and significantly suppresses short channel effects, as our simulation results predicted.

Chapter 8 summarizes the conclusions of our research.

#### CHAPTER 2

#### **BACKGROUND INFORMATIONS**

#### 2.1 Introduction

We have used HFET as a vehicle for the presentation of a new device structure as mentioned in preceding chapter. The HFET is a nature extension of the modulation-doping concept. By applying an external voltage across the heterojunction interface, one can modulate the 2DEG density, and thus its conductivity. Due to the high electron mobility, this novel device is the fastest three-terminal semiconductor device in the world and is very promising in ultra-high-speed/high-frequency applications. Today, there are tens of millions of HFETs in operation around world.

In this chapter, an overview of the state-of-the-art HFET is presented together with the design and optimization of the single gate HFET structures. The approaches employed in this thesis to develop new device structure are also discussed.

### 2.2 Development of HFETs

A breakthrough in HFET technology occurred when it was demonstrated that high quality, dislocation-free gallium indium arsenide (GaInAs) can be grown "pseudomorphically" on a GaAs substrate without misfit dislocations as long as its thickness is less than a certain critical thickness[11],[12],[13]. This approach results in HFET structures with higher conduction band discontinuity and, consequently, higher 2DEG sheet density and modulation efficiency. As a result, the fT of state-of-the-art HFET's improved substantially, from 110 Ghz in 1987[14] to over 150 Ghz[15].

During this period, a significant amount of research and development also took place in the AlInAs/GaInAs material system, grown on an InP substrate[16],[17]. The conduction band discontinuity between AlInAs and GaInAs is considerably higher than other material systems, which results in a significantly higher 2DEG sheet density and modulation efficiency. This improvement yielded an approximately 33% increase in fT for state-of-the-art HFETs, from 150 to over 200GHz in 1988[18].

These dramatic improvements are also a result of significant advances in the fabrication of HFETs. The gate length of state-of-the-art HFETs has been steadily reduced, from 0.33um in 1984[19] to .05um in 1992[14]. At these short gate lengths, the effects of parasitic resistances become more pronounced and often mask the intrinsic device performance. As a result, a number of "mushroom-" or T-gate, and self-aligned gate process have been developed to reduce gate and parasitic source resistances, while still maintaining a small gate "footprint" [14],[20].

In addition, a great deal of work has been devoted to suppress the short channel effects of the HFETs. Several effective approaches, such as double-recessed structure[21], undoped surface cap structure[22], lightly doped drain structure[23], and low conductance drain[24], have been demonstrated. Significant improvements in short channel effect behaviors have been achieved.

### 2.3 Principles of Operation

The basic principles of operation of HFET can be described by a one dimensional(1-D) charge control model in the direction perpendicular to the heterojunction interface, which was developed by Delagebeaudeuf *et al* [25]. It was assumed that, for 0 < Ns < Nso.

$$qNs = Cs(Vg-Vth)$$

(2.1)

where Ns is the 2DEG sheet density, q the electrostatic charge, Cs the 2DG capacitance per unit area, Vg the applied gate voltage, and Vth the threshold voltage.

Despite its simplified assumptions, the charge control approximation correctly predicts the linear dependence of Ns on Vg. The real behavior, however, rapidly deviates from a simple linear relationship when Ns versus Vg curve approaches its upper bounds (Nso). This nonlinear charge control characteristic is associated with the onset of parasitic charge modulation in the wide-band gap material. The gate potential modulates the 2EDG electrons and their parent donors simultaneously, resulting in a nonconstant capacitance. This mechanism is responsible for the premature saturation of Ns in a modulation-doped structure and leads to degradation in device performance.

The modulation efficiency is a useful concept in the design and analysis of FET structures[26],[27]. Loosely speaking, it indicates how efficiently an FET modulates the total channel charge (Qtot) in order to produce an incremental change in drain current (Ids):

efficiency =

$$\eta \propto \text{delta(Ids)/delta(Qtot)}$$

(2.2)

Since Qtot is made up of various charge components, each with an unequal contribution to Ids, one must examine the rate of change of each of these components separately.

In a HFET structure, the only charge component that contributes to Ids is that of the 2DEG(Ns); the other "parasitic" components, such as donor bound electrons and low velocity electrons that reside in the wide-gap material, contribute essentially nothing to Ids. We now examine the simplest case in which the modulation of charge is assumed to be uniform over the entire length of the gate. We assume that all electrons in the 2DEG

travel at their saturated velocity (Vsat) over the entire length of the gate while those residing in the wide-gap material --- bound and free --- are stationary. Thus, the rate of charge of Ids with respect to Qtot is given by

$$\Delta Ids/\Delta Qtot = \Delta (q Vsat Ns)/\Delta (Qtot)$$

= Vsat  $\Delta (q Ns)/\Delta (Qtot)$  (2.3)

Comparing (2.2) and (2.3), one can define the modulation efficiency,  $\eta$ , as the ratio of the rate of change of the "useful" charge over that of the total charge, i.e.,

$$\eta = \frac{q\Delta Ns / \Delta Vg}{\Delta Q tot / \Delta Vg} = \frac{q\Delta Ns / \Delta Vg}{C_{tot}}$$

(2.4)

Since  $\Delta Q$ tot >  $q\Delta Ns$ , 0<  $\eta$  <1. An  $\eta$  of 1.0 represents the most efficient state of operation in which only the 2DEG sheet charge is being modulated by the gate voltage.

The current gain cutoff frequency  $(f_T)$  of a HFET, which is the most useful figure of merit for assessing device speed, is thus given by

$$f_T = \frac{g_m}{2\pi C_{gs}} = \frac{q v_{sat} (\Delta N_s / \Delta V_g)}{2\pi L_g Ctot}$$

(2.5)

where  $g_m$  is the device transconductance, Cgs is the total gate capacitance, and  $L_g$  is gate length.

Substitute (2.4) into (2.5), one obtains

$$f_T = \frac{v_{\text{sat}}}{2\pi L_g} \eta \tag{2.6}$$

Thus the excess charge modulation reduces the  $f_T$  by a factor equal to  $\eta$ .  $\eta$  assumes the gate bias dependence of  $f_T$  as well as the differences among various types of FET's of similar gate length and saturation velocity.

Since the distribution of 2DEG electrons(Ns) and electron velocity are nonuniform along the gate, the modulation of charge is not as efficient as the ideal case that all electrons in the 2DEG travel at their saturation velocity (Vsat) over the entire length of the gate. Thus in order to support the same amount of current, the gate has to modulate more charges, particularly near the source end of the gate where the electron velocity is lowest. As a result, the modulation efficiency along the gate is always less than unity; and its magnitude depends on Ns, as well as the difference in Ns at the source and drain ends of the gate or the velocity distribution along the gate.

It is clear from the above discussion that one can establish the following relationship:

$$gm = Cs Vsat \eta$$

(2.7)

The maximum transconductance is achieved by improve  $\eta$  to reach the value of unity. Thus for a given gate length, and gate to channel thickness, the intrinsic transconductance of a HFET depends solely on the modulation efficiency.

This formulation has offered new insights on HFET's principles of operation. It was therefore found that smaller conduction band discontinuity( $\Delta$ Ec) material system modulates more parasitic charge components, causing more severe reduction in HFET overall modulation efficiency.

### 2.4. Dynamic Performance of Short Channel HFET

#### 2.4.1 Parasitic Effects

Since the speed of an FET is traditionally limited by the electron transit time, the most obvious approach to improve this speed has always been a reduction in gate length.

Unfortunately, as the gate length approach the 0.1µm regime, this strategy is no longer effective. At such a short gate length, the electron transit time is comparable to, or even smaller than, other parasitic delays in the device. Consequently, as the gate length is reduced, a simultaneous effort must be made to proportionally reduce the various parasitic delays as well. Among those, the parasitic capacitance charging time (gate pad, gate fringe, etc.), the source resistance, and drain delay (due to the extension of the drain depletion region), are the dominant delays and must be further reduced[29],[15].

Here, we describe the parasitic effects using a small signal model that takes into account the charging time associated with the gate pad ( $t_{pad}$ ) and gate fringe ( $t_{fringe}$ ) capacitances, as well as an additional parasitic delay due to the extension of the drain depletion region beyond the gate edge ( $t_{drain}$ )[30]:

$$t_T = t_{pad} + t_{fringe} + t_{drain} + t_i = \frac{1}{2\pi f_T}$$

(2.8)

where  $t_T$  and  $t_i$  are the total and intrinsic delays, respectively. For simplicity, we left various terms, such as the output conductance  $(g_{ds})$ , and feedback capacitance  $(C_{gd})$ , and drain resistances  $(R_d)$ , for later consideration.

For a field effect transistor with a pad capacitance  $C_{pad}$ , extrinsic transconductance  $g_m$ , and gate width,  $t_{pad}$  is approximately given by

$$t_{pad} = \frac{C_{pad}}{g_{m}} \tag{2.9}$$

where  $C_{pad}$  is typically 10 fF per 50×50- $\mu$ m bonding pad. Although often ignored, this parasitic charging time has been found to account for a significant portion of the total

delay in ultra-short gate length FET's. For instance, a  $t_{pad}$  of 0.33 ps is estimated for a 30  $\mu$ m wide device with  $g_m = 1000$  mS/mm and  $C_{pad} = 10$ fF, which is as much as 60% of the intrinsic delay of a 0.1 $\mu$ m gate length AlGaAs/GaInAs MODFET[15].

Similarly, the gate fringe capacitance charging time is given by

$$t_{fringe} = \frac{C_{fringe}}{g_{mo}}$$

(2.10)

where  $g_{mo}$  is the intrinsic  $g_{m}$  and is approximately related to the extrinsic  $g_{m}$  and source resistance Rs by the relationship:

$$g_{\mathbf{m}} = \frac{g_{mo}}{1 + g_{mo} \cdot R_S} \tag{2.11}$$

Thus the presence of  $R_s$  affects only the gate pad, but not gate fringe, capacitance charge time. This fringe capacitance is typically 0.18 pF/mm for HFETs.

The drain delay ( $t_{drain}$ ) due to the extension of the drain depletion region is a difficult parameter to be obtained with high accuracy. For state-of-the-art MODFET's,  $t_{drain}$  introduces an additional 0.1-0.2 ps delay at low drain bias voltages [14].

From (2.3), the intrinsic delay at a particular bias condition is given by

$$t_i = \frac{C_{gs}}{g_{mo}} = \frac{L_g}{v_{sat} \cdot \eta}$$

(2.12)

where  $\eta$  is the modulation efficiency. Typically,  $t_i$  is equal approximately 0.4-0.6 ps for 0.1  $\mu$ m gate length HFETs.

### 2.4.2 The Effects of Feedback Capacitance and Drain Conductance

In above discussions, we have taken into account the effects of the parasitic elements in addition to the major parameters, namely  $C_{gs}$  and  $g_{m}$ . Similarly, as the gate length continues to decrease, the effects of the feedback capacitance  $C_{gd}$  and drain conductance  $g_{ds}$  become more and more important. When these term are included, it can be shown that (2.4) must be modified as follows[31]:

$$t_T = \frac{C_{pad}}{g_{m}} + \frac{C_{gs} + C_{fringe} + C_{gd}}{g_{mo}} \cdot [1 + g_{ds}(R_s + R_d)] + C_{gd}(R_s + R_d)$$

(2.13)

Therefore, in order to avoid excessive delays associated with  $g_{ds}$  and  $C_{gd}$ , one must ensure the following:

$$g_{ds}(R_s + R_d) \ll 1 \tag{2.14}$$

and

$$\frac{g_{\text{mo}}}{1 + (C_{gs} + C_{fringe}) / C_{gd}} (R_s + R_d) \ll 1$$

(2.15)

Since  $g_{mo}$  must be increased with reduced gate length, one must proportionally reduce  $g_{ds}$  and  $C_{gd}$  in addition to the reduction of parasitic resistances, Rs and Rd, in order to minimize the effects associated with them.

It has been demonstrated that both  $g_{ds}$  and  $C_{gd}$  are strong functions of drain bias and drain recessed width[32]. This is due to the extension of drift region as a space charge layer by drain bias. Thus, the  $g_{ds}$  and  $C_{gd}$  could be reduced largely by increasing the recess width and drain bias. For high performance short channel HFETs a

highly doped cap layer is necessary to reduce the parasitic resistances. Therefore a recessed device configuration is employed. However, the performance of the device depends strongly on the shape of the recess configuration. A narrow recess leads to a low  $g_{ds}$  and high  $C_{gd}$ , whereas a wide recess introduces a current limiter, especially at the source. Therefore an asymmetric recess configuration is needed. A wider recess at the drain side can be used to reduce feedback and improve breakdown. A narrow recess at the source side leads to a low parasitic source resistance.

### 2.4.3 $f_{\text{max}}$ , an Important Figure of Merit of RF HFETs

In above discussions, we concentrated on  $f_T$ , which is certainly an important figure-of-merit, especially in terms of digital performance. But with regard to RF performance,  $f_{\rm max}$  is probably better indicator of high frequency performance. From reference [31],  $f_{\rm max}$  can be expressed below:

$$f_{\text{max}} = \frac{f_T}{\sqrt{4 \frac{g_{ds}}{g_{mo}} (g_{mo} R_g + \frac{R_s + R_d}{1/g_{mo} + R_s}) + \frac{4}{5} \frac{C_{gd}}{C_{gs}} (1 + \frac{2.5 C_{gd}}{C_{gs}}) (1 + g_m R_s)^2}}$$

(2.16)

Equation (2.11) demonstrates that  $f_{\max}$  takes more into account the losses associated with gate resistance,  $R_g$ , output conductance,  $g_{ds}$ , and gate drain feedback capacitance  $C_{gd}$ . Moreover, the ratios  $\frac{g_m}{g_{ds}}$  and  $\frac{C_{gs}}{C_{gd}}$  gain more influence. It should be noted that a device that is optimized for high  $f_{\max}$  is not usually operated at optimized  $f_T$ . Therefore, it is not practicable to have a single device working simultaneously at highest

$f_{\text{max}}$  and  $f_T$ . Instead many approaches are devoted to considerably improving  $\frac{g_m}{g_{ds}}$ ,

$\frac{C_{gs}}{C_{gd}}$ , and small signal gain of ultra-short gate-length HFETs while not significantly

degrade  $f_T$ .

#### 2.4.4 Other Short Channel Effect Related Issues

between the gate length and effect gate-to-channel separation). Many key parameters,

Performance of short channel FETs is a strong function of device aspect ratio (the ratio

such as  $g_m$ ,  $g_{ds}$ ,  $\frac{g_m}{g_{ds}}$  and  $\frac{C_{gs}}{C_{gd}}$ , degrades due to the reduction in aspect ratio. Thus, as

the gate length of an FET is reduced, one must also proportionally reduce its vertical dimensions in order to maintain a reasonably high aspect ratio and thereby acceptable short channel effects. This geometrical parameter is a very important factor in controlling the field effect action of a transistor, and should be maintained above five[30].

For a given gate length, one can often increase the device transconductance and suppress short channel effects by reducing the gate-to-channel separation or increase the aspect ratio. This will also result in high speed or lower parasitic delays, which is proportional to the parasitic capacitance divided by transconductance.

#### 2.5 The State-of-the-art Approaches of Short Channel HFETs

Significant improvement has been achieved in the area of short channel HFETs. Numerous device structures and excellent performance (e.g.  $f_{\rm max}$ ,  $f_T$ , breakdown and

gain) have been reported in the literatures. However, due to complicity and often controversy behaviors, it is difficulty to merit all the parameters in a single device. Thus different approaches are often aimed to optimize one or some of the key parameters for specific applications. In this section, we discuss approaches of the state-of-the-art HFETs and the physics behind these approaches.

#### 2.5.1 Self-aligned Gate and Ohmic Contact

In the presence of parasitic effects, the extrinsic  $f_T$  of a short gate length HFET is no longer inversely proportional to its gate length. In order to improve the speed of ultrashort gate length HFETs, self-aligned gate scheme was used to allow the source and drain contacts to be "self-aligned" to the gate[33]. In this technology, additional ohmic contacts are evaporated in a self-aligned process using the T-gate structure as mask. The corresponding self-aligned gate HFETs exhibited a factor-of-2 reduction in delays associated with  $g_{ds}$  and  $C_{gd}$ , due to their extremely low Rs and Rd. This is expected by (2.13) and (2.14). Moreover, for a 0.1 $\mu$ m gate length devices reported in [34], ~70% reduction in the Rs and Rd resulted in an increase in extrinsic transconductance approximately 22%, from 900 to 1100 mS/mm, and that in extrinsic  $f_T$  approximately 15%, from 200 to 230 GHz. With further optimization, the state-of-the-art self-aligned HFET with extrinsic transconductance of 1580 mS/mm and extrinsic  $f_T$  of 340 Ghz have been achieved for a 0.05  $\mu$ m pseudomorphic HFET[35].

Another very attractive self-aligned gate structure is the lightly doped drain (LDD) structure[23]. The fundamental concept of this approach is the decrease of

maximum electric field along the channel. It shows low parasitic resistance, low drain conductance and high breakdown voltage. In addition, since the breakdown voltage is related to the strong electric field at the drain side of the gate, asymmetric LDD structures, such as lightly doped deep drain structure and long lightly doped drain[23], have therefore been proposed to further increase the drain breakdown voltage while the small source resistance.

## 2.5.2 Double-recessed Technique

HFETs with short gate length suffer from a high drain conductance,  $g_{ds}$ , low voltage gain  $\frac{g_m}{g_{ds}}$  and low breakdown voltage, which consequently degrade the  $f_{max}$  and other performance. For many applications especially RF power, it is desired to have high breakdown voltage. Three advantages of high breakdown voltage are known: (1) higher breakdown has been attributed to longer life times[36]; (2) higher breakdown allows higher drain operating voltage which translates to a higher output power density as long as the power gain is sustained. (3) Higher drain operating voltage usually leads to lower  $g_{ds}$  and  $G_{gd}$ , and consequently higher voltage gain and  $\frac{G_{gs}}{G_{gd}}$  ratio. Thus it is desirable to develop a HFET that has a breakdown voltage appropriate for the intended drain operation voltage.

An effective method for suppressing short channel effects and increasing the breakdown voltage is to use a double-recessed gate process. We know a wide recess width allows the spreading of the space charge while a narrow recess leads to small

source resistance. Therefore, the double stepped recess with gate close to the source combines the advantages of narrow recess (high transconductance and drain current) and wide recess (high breakdown voltage, low output conductance and low feedback capacitance). These leads to high RF performances.

An important issue is associated with distance,  $L_{gd}$ , between the gate metal edge and the N+ cap layer on the drain side of the device. In short gate-length HFETs,  $L_{gd}$  can have a profound effect on both the DC current-voltage characteristics and RF gain of device due to the extension of drift region. Increase  $L_{gd}$  benefit FET performance by reducing the output conductance and the gate to drain feedback capacitance[21]. It was shown that longer  $L_{gd}$  HFETs have simultaneously improved  $\frac{C_{gs}}{C_{gd}}$ ,  $\frac{g_m}{g_{ds}}$  and  $g_m$  in extremely short gate-length HFETs. Excellent  $f_{max}$  and gain have been achieved while not seriously degrading the  $f_T$  using double recess and longer  $L_{gd}$  [21].

# 2.5.3 V-shaped Spike Gate FETs

Both low-voltage and high efficiency operations are major concerns for the power applications. The narrowed voltage swings is due to the presence of the knee voltage of FETs which is originated from the on-resistance. This ends up with decreasing the available output power as well as the drain efficiency. In order to reduce the on-resistance, shrinking the channel length is most effective, however, as mentioned earlier, shortening the channel causes higher drain conductance that reduces the power gain and thereby the power added efficiency(PAE).

Recently, Tsuyoshi *et al* [22] reported very short channel HFETs using a V-shaped spike gate structure, which was first proposed by Kohn[37], in order to reduce the on-resistance. It was shown that this V-shaped structure can suppress the increase of drain conductance, because the depletion widening from the fringe of the V-shaped gate alleviates the electric field between the gate and drain. A lowest on-resistance ever reported by using the unique gate structure has been achieved. The attained on-resistance was less than a half of that without V-shaped spike. The implemented device achieved the PAE of 70% with 31.5 dBm output power at drain bias of 1.5V for the first time[22].

#### 2.5.4 Dual Gate FETs

The advantage of dual gate structure comes from the added functionalities obtained by integrating two independent FET's in a compact manner. Compared to the single gate FET, a dual gate FET of the same gate length provides the same input impedance with higher output impedance, higher breakdown voltage, higher power gain, and much reduced feedback capacitance. This is mainly due to the second gate which increases the effective gate length and the distance between first gate edge and the drain end, therefore, also increases the aspect ratio, which suppresses short channel effects. However, the penalty of the improvements is also due to the increasing of the total effective gate length. This produces higher gate capacitance and lower transconductance, and consequently, lower  $f_T$ . Thus, a trade-off is required to optimize dual gate FETs.

### 2.6 Primary Goals of This Research

In the view of the trend of improving FET performance, device structure based on asymmetric design have become very attractive. Several new approaches, such as double-recessed structure[21], asymmetrical lightly asymmetrical doped drain low conductance drain[24], and asymmetrical channel doping structure[23]. FETs[38],[39], have been demonstrated to be very effective in suppressing short channel effect, increasing the breakdown voltage and/or enhancing transconductance. In this work, we propose a new type of FET structure, the dual material gate field effect transistor (DMGFET), which is presented to suppress short channel effects and enhance transconductance simultaneously. The special feature of this new structure approach is that the improvements are due to the modification of electric field along the channel. We will show that this structure can considerably reduce drain conductance and improve transconductance. Like other device structures, this device has its inherited demerits besides the merits. Although the DMGFET exhibits lower  $g_{ds}$ , Cdg and higher  $g_m$ , its Cgs tends to be higher. Thus, a proper treatment of these parameters will require a tradeoff. Another related issues is the manufacturing. Here we have limited ourselves to the ideal structural effect. Therefore more issues related to manufacturing are not addressed. Hence further works are still needed to obtain more stable/repeatable processing methods and, especially, to control the two gate contacts which are functions of many experimental parameters.

# 2.7 Scope and Methodology Used in This New Structure Development

In this work, we employ analytical modeling, device simulation and experimental data for the new structure study. Analytical model provides good physical insight. Device numerical simulation is a good tool for different structure comparison or trend prediction. The experimental approach is thus guided by simulation and analytical models.

Although the proposed DMGFET is a single gate FET, it has a structure like dual gate FET. We therefore expect that it has the benefits of both single and dual gate structures. In order to take full advantage of the dual gate effects, we first study the principles of operation of the dual gate HFET: Chapter 3 will outline the dual gate intrinsic I-V characteristics for the simplest case using simple analytical approach. To understand dual gate small signal behavior, Chapter 4 will discuss its key small signal parameters. In Chapter 3 and 4, we will simulated and studied dual gate InAlAs/InGaAs HFET, since this device is an ideal test vehicle for dual gate effects discussed in the chapters and we previously studied experimental dual gate HFET behaviors using this material system[40].

The rest chapters will be devoted to the new device structure, DMGFET. We will emphasize the pseudomorphic InGaP/InGaAs HFET since this device is most suitable for stable and simple device fabrications. The device structure and parameters employed in this study are primary come from the real material structure we used for experimental processing, which was provided by Bell Labs, Lucent Technologies.

A 2-D device simulator, PISCES, is used as a numerical tool to investigate the presented new device structure and other related device structures. It should be noted that PISCES is not a well developed tool for HFETs simulations, since some of the models it

to serve as a tool to predict the trend of device behavior under different structures. In order to make the best comparisons, we will usually fix the channel doping Nso, gate-to-channel thickness and other vertical device parameters unchanged for devices simulated. The detail of this parameters used are presented in the Appendix A.

## 2.8 Summary

We have presented an overview on the state-of-the-art single gate HFET and the trends in improve single gate HFET performances. It was demonstrated that increase modulation efficiency and reduce parasitic and short channel effects are extremely important in achieving ultra-high-performance short channel HFETs.

We anticipate that the DMGFET will demonstrate enhanced overall electron velocity along the channel and therefore increased modulation efficiency. In addition, the short channel effects could be suppressed by this novel structure. Therefore, this new device can be a promising candidate for the applications such as low noise FET( needs high gm and low gds, Rs, etc), power amplifiers (high gm/gd ratio, low gds, Rs, Cdg, etc.), and digital integrated circuits (high modulation efficiency, low parasitic, etc.).

#### CHAPTER 3

#### ANALYTIC MODEL FOR DG-HFET DC CHARACTERISTICS

#### 3.1 Introduction

Our development of analytical dual gate (DG) model starts with a closed form analytic single gate model proposed by Khondker et al [41], which has been successfully used for the prediction of single gate HFET behavior, and then proceeds through a set of simplifying assumptions to arrive at a novel expressions for the common node potential between the two gates that determines the operating status under each gate. For single gate, the DC I-V behavior, which is described in term of the two possible operating regions, is simply determined by given external biases. Whereas for dual gate, it is determined by specifying the common node potential in addition to the external bias conditions. Hence, to characterize the operation of dual gate analytically, we can not simply plug in the given external bias values into single gate equations, rather we have to solve for the common node potential under the given biases before the single gate analytic equations can be used. This points out that the major work needed for the dual gate model is to figure out external bias dependence of the common node potential.

Consider the DG-HFET to be composed of two single gates in cascade, its common gate potential can be obtained by determination of the intersection of two HFET I-V curves. Due to the complicated expression of HFET I-V behavior, we have to resort to non-analytic method which involves a numerical procedure. However, if we assume that the non-linearity in the whole linear operating region is weak, and that after both gates are in saturation, most of the excessive drain-source biasing voltage  $V_{dS}$  is dropped under the second gate near the drain, then the common node potential or the

intersection point can be calculated simply through analytic equations. Hence, we postulate that under those simplifying assumptions, the common node potential is governed by the analytic expressions thus derived, which forms the cornerstone of our dual gate analytic model.

In this chapter, we present the above-mentioned analytic methodology for calculating the DG-HFET I-V characteristics from the simplified analytic equations. A detailed derivation and discussion are presented in this chapter, which is organized into three main sections.

The first part, Section 3.2, is devoted to the derivation and simplification of the single gate HFET analytic model, which was originally presented by Khondker et al [41]. The Sub-Section 3.2.1 deals with the setting up of the I-V expressions based on charge control principles, while 3.2.2 presents an important simplification to the I-V expressions which permits us to calculate simple closed form expressions for DC characteristics.

In the beginning of Section 3.3, we discuss the approximations and outline the derivation of dual gate common node potential equations from single gate equations. The section concludes with a closed form expression for common node potential, which has external bias conditions as parameters. It is important to understand the dependence of common node potential on external biasing, since it determines how external biasing influences the operating status of the two HFETs, and therefore, the performance of the DG-HFET. This forms the subject of discussion in Sub-Section 3.3.2.

Finally Section 3.4 discusses the analytic methodology that allows one to calculate the DG-HFET I-V characteristics from a knowledge of device physical structure and bias parameters. Calculation and discussion of the key small signal parameters of DG-HFET forms the subject of the next chapter in which we first derive the closed form

expressions for those parameters, and then employ the machinery developed in this chapter to calculate DG-FET's behavior and discuss the dual gate effects.

## 3.2 Analytic Single Gate Modeling