### **Copyright Warning & Restrictions**

The copyright law of the United States (Title 17, United States Code) governs the making of photocopies or other reproductions of copyrighted material.

Under certain conditions specified in the law, libraries and archives are authorized to furnish a photocopy or other reproduction. One of these specified conditions is that the photocopy or reproduction is not to be "used for any purpose other than private study, scholarship, or research." If a, user makes a request for, or later uses, a photocopy or reproduction for purposes in excess of "fair use" that user may be liable for copyright infringement,

This institution reserves the right to refuse to accept a copying order if, in its judgment, fulfillment of the order would involve violation of copyright law.

Please Note: The author retains the copyright while the New Jersey Institute of Technology reserves the right to distribute this thesis or dissertation

Printing note: If you do not wish to print this page, then select "Pages from: first page # to: last page #" on the print dialog screen

The Van Houten library has removed some of the personal information and all signatures from the approval page and biographical sketches of theses and dissertations in order to protect the identity of NJIT graduates and faculty.

#### **ABSTRACT**

## DESIGN, SIMULATION AND FABRICATION OF A MEMS IN-SITU, CONTACTLESS SENSOR TO DETECT PLASMA INDUCED DAMAGE DURING REACTIVE ION ETCHING

#### by Subramanian Ganesh

The present trend in the semiconductor industry is towards submicron devices. An inevitable process technique in achieving this is by reactive ion etching of the polysilicon gate. During RIE, the gate oxide may get damaged due to several causes. One of the main causes of the damage is the non-uniformity of the plasma. It is reported that these plasma inconsistencies are mainly due to electrode design and that they create spatial plasma potential fluctuation. These fluctuations are reported to be in the range of 10-20 Volts. By providing an in-situ monitoring of the wafers, the reliability of the device could be established. The purpose of this sensor is to detect the spatial fluctuations. It works on the principle of electrostatic forces. It is made of polysilicon (gate material) and consists of two cantilevers separated by 2µm constituting a parallel plate capacitor configuration. The design, simulation and fabrication of the sensor was carried out. The test results demonstrated that sensors with beam lengths 150µm, 200µm and 250µm deflect by 2µm at externally applied voltages of 65, 56, and 50 volts respectively. Optimized beam dimensions that would deflect by 1.2µm at an applied voltage of 20 Volts is estimated from the experimental results and has the following dimensions: length of the cantilever =  $200\mu m$ , width =  $2\mu m$ , the thickness =  $1.6\mu m$ , and the space between the cantilevers  $is = 1.2 \mu m$ .

## DESIGN, SIMULATION AND FABRICATION OF A MEMS IN-SITU CONTACTLESS SENSOR TO DETECT PLASMA INDUCED DAMAGE DURING REACTIVE ION ETCHING

by Subramanian Ganesh

A Thesis

Submitted to the Faculty of

New Jersey Institute of Technology

in Partial Fulfillment of the Requirements for the Degree of

Master of Science in Engineering Management

Department of Industrial and Manufacturing Engineering

January 1997

#### APROVAL PAGE

# DESIGN, SIMULATION AND FABRICATION OF A MEMS IN-SITU, CONTACTLESS SENSOR TO DETECT PLASMA INDUCED DAMAGE DURING REACTIVE ION ETCHING

#### Subramanian Ganesh

| Dr. Durgamadhab Misra, Thesis Advisor<br>Associate Professor of Electrical Engineering, NJIT                          | Date |

|-----------------------------------------------------------------------------------------------------------------------|------|

|                                                                                                                       |      |

| Dr. George Abdou, Co-Advisor, Committee Member. Associate Professor of Industrial and Manufacturing Engineering, NJIT | Date |

|                                                                                                                       |      |

| Dr. Robert Marcus, Committee Member, Research Professor, Electrical and Computer Engineering, NJIT                    | Date |

#### **BIOGRAPHICAL SKETCH**

Author: Subramanian Ganesh

Degree: Master of Science

Date: January 1997

#### Undergraduate and Graduate Education:

Master of Science in Engineering Management

New Jersey Institute of Technology, Newark, New Jersey, 1997

Bachelor of Science in Mechanical Engineering,

R.V. College of Engineering, Bangalore University,

Bangalore, India, 1994

Major: Engineering Management

#### **ACKNOWLEDGMENT**

I would like to express my deepest appreciation to Dr. Durgamadhab Misra for his guidance, support and encouragement throughout this research.

Special thanks to Dr. George Abdou for participating in my thesis committee and for making this interdisciplinary thesis possible. I would also like to thank Dr. Robert Marcus for participating in my thesis committee and for offering valuable suggestions and guidance, especially in testing of the device.

Thanks to Dr. Swain for his guidance through the thesis and for his support during my entire study period. Thanks also to Murat, Ravi, and Rai for everything.

#### TABLE OF CONTENTS

| Cha | apter |                                                          | Page |

|-----|-------|----------------------------------------------------------|------|

| 1   | INTR  | RODUCTION                                                | 1    |

|     | 1.1   | Overview                                                 | 1    |

|     |       | 1.1.1 Device Damage from Plasma                          | 1    |

|     |       | 1.1.1.1 Reversible Effects                               | 2    |

|     |       | 1.1.1.2 Irreversible Effects                             | 3    |

|     | 1.2   | Objective                                                | 8    |

|     | 1.3   | Principle of Operation                                   | 9    |

|     | 1.4   | Material Selection                                       | 10   |

|     | 1.5   | Design Considerations                                    | 11   |

| 2   | SIMU  | JLATION                                                  | 13   |

|     | 2.1   | Introduction                                             | 13   |

|     | 2.2   | Basic Electrostatics                                     | 13   |

|     | 2.3   | Device Simulation                                        | 18   |

|     |       | 2.3.1 Electrostatic Attraction of Nearly Parallel Plates | 18   |

|     | 2.4   | Calculations                                             | 21   |

| 3   | FAB   | RICATION                                                 | 27   |

|     | 3.1   | Introduction                                             | 27   |

## TABLE OF CONTENTS (Continued)

| Chapter |                                                  | Page |

|---------|--------------------------------------------------|------|

| 3.2     | NJIT Clean Room                                  | 27   |

| 3.3     | Outline of the Process Steps for Fabrication     | 28   |

|         | 3.3.1 Flow Sheet for Fabrication of the Device   | 28   |

|         | 3.3.2 Schematic of the Fabrication of the Device | 30   |

| 3.4     | Deposition of SiO2 by LPCVD                      | 33   |

|         | 3.4.1 Introduction                               | 33   |

|         | 3.4.2 Experimental Values                        | 38   |

| 3.5     | Deposition of Polysilicon.                       | 39   |

|         | 3.5.1 Introduction                               | 39   |

| 3.6     | Polysilicon Doping                               | 39   |

| 3.7     | Photolithography                                 | 41   |

|         | 3.7.1 Introduction                               | 41   |

| 3.8     | Etching                                          | 42   |

|         | 3.8.1 Introduction                               | 42   |

|         | 3.8.2 Description of the RIE Process             | 42   |

| 3.9     | Metal Sputtering                                 | 45   |

|         | 3.9.1 Introduction                               | 45   |

|         | 3.9.2 Photolithography and Patterning of Metal   | 45   |

| 3.10    | Sacrificial Oxide Etch                           | 46   |

### TABLE OF CONTENTS (Continued)

| Ch | apter                                                        | Page |

|----|--------------------------------------------------------------|------|

| 4  | TESTING PROCEDURE AND RESULTS                                | 49   |

|    | 4.1 Introduction                                             | 49   |

|    | 4.2 Steps Involved in Testing                                | 50   |

|    | 4.3 Experimental Results                                     | 54   |

|    | 4.4 Discussion                                               | 55   |

| 5  | CONCLUSION                                                   | 61   |

|    | 5.1 Future Scope                                             | 61   |

|    | APPENDIX A Oxide Deposition and Reactor Description          | 63   |

|    | APPENDIX B Mechanical Properties of Polysilicon              | 67   |

|    | APPENDIX C Polysilicon Deposition Methods and Conditions     | 68   |

|    | APPENDIX D Polysilicon Doping Conditions                     | 71   |

|    | APPENDIX E Evaporation and Sputtering Process and Conditions | 72   |

|    | APPENDIX F Sacrificial Oxide Etch.                           | 78   |

|    | APPENDIX G Photoresist Terminology and Lithography           | 79   |

|    | APPENDIX H Etching                                           | 82   |

#### LIST OF TABLES

| Table |                                                                                                 | Page |

|-------|-------------------------------------------------------------------------------------------------|------|

| 1.1   | Mechanical properties of polysilicon                                                            | 11   |

| 2.1   | Computed values of capacitance and force using equations 2.4 & 2.8                              | . 22 |

| 2.2   | Computed values of capacitance and force using equations 2.4 & 2.9                              | . 22 |

| 2.3   | Computed values of capacitance and force using equations 2.5 & 2.8                              | . 23 |

| 2.4   | Computed values of capacitance and force using equations 2.5 & 2.9                              | . 23 |

| 2.5   | Computed deflection obtained for various beam lengths using combination of equations (Computed) | 24   |

| 2.6   | Varying voltage and deflection obtained for varying beam lengths                                | . 25 |

| 3.1   | Conditions to etch polysilicon (Standard)                                                       | . 42 |

| 3.2   | Conditions used for etching polysilicon                                                         | . 43 |

| 4.1   | Comparison of experimental and simulated values                                                 | 56   |

| 4.2   | Simulated values including correction factors                                                   | 59   |

| A.1   | Oxide deposition parameters                                                                     | 63   |

| A.2   | Oxide thickness measured at various points on the wafer                                         | 64   |

| C.1   | Polysilicon deposition conditions                                                               | 68   |

| D.1   | Polysilicon diffusion conditions                                                                | 69   |

| E.1   | Sputter deposition of Metal                                                                     | 75   |

#### LIST OF FIGURES

| Figure | 2                                                                              | Page |

|--------|--------------------------------------------------------------------------------|------|

| 1.1    | Electrostatic breakdown of gate oxide                                          | 4    |

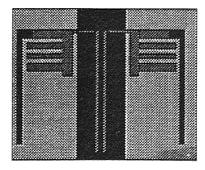

| 1.2    | Top view of the sensor                                                         | 12   |

| 1.3    | Gate oxide damage during etching of the conductive gate electrode              | 12   |

| 2.1    | Simple schematic showing the application of voltage and capacitance build up   | 14   |

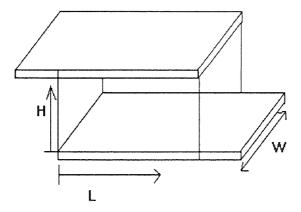

| 2.2    | Parallel plates with width W, length L, and H the distance between the plates. | 15   |

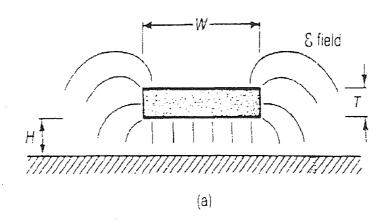

| 2.3    | Fringing capacitance of narrow wires                                           | 17   |

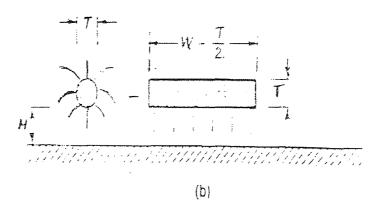

| 2.4    | Cross section of a typical MEMS type structure                                 | 19   |

| 2.5    | Graph showing the deflection calculated for the combination of equations.      | 26   |

| 2.6    | Graph showing deflection versus applied voltage for different beam lengths     | 26   |

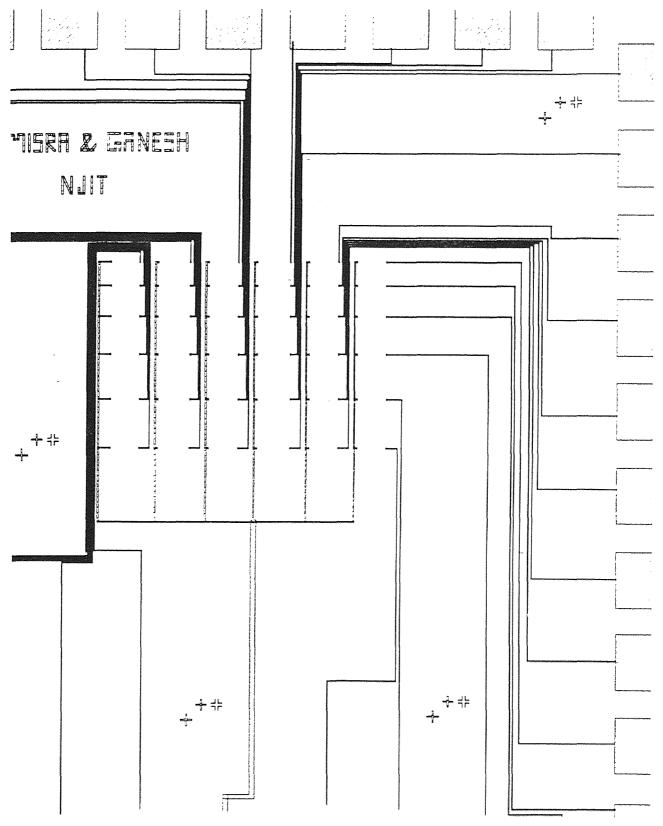

| 3.1    | Schematic of the Fabrication of the Device                                     | 30   |

| 3.1    | Schematic of the Fabrication of the Device (Continued)                         | 31   |

| 3.1    | Schematic of the Fabrication of the Device (Continued)                         | 32   |

| 3.1    | Schematic of the Fabrication of the Device (Continued)                         | 33   |

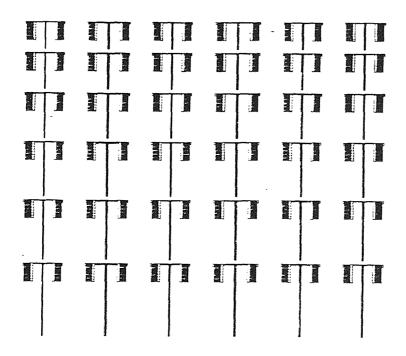

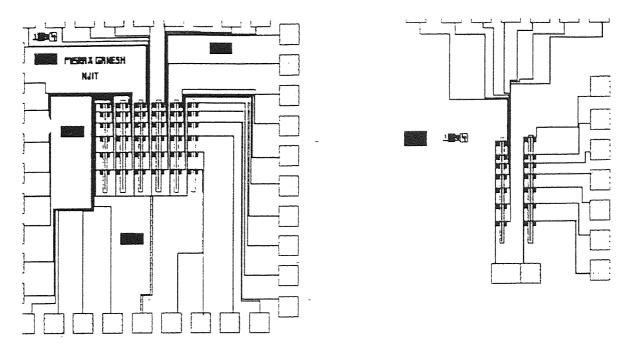

| 3.2a   | Polysilicon pattern mask design                                                | 34   |

| 3.2b   | Metal pattern design                                                           | 35   |

| 3.2c   | Sacrificial oxide pattern design                                               | 36   |

| 3.2d   | All the masks superimposed on one another                                      | 37   |

## LIST OF FIGURES (Continued)

| Figure |                                                                            | Page |

|--------|----------------------------------------------------------------------------|------|

| 3.4    | Micrograph of the etched polysilicon beams                                 | 44   |

| 3.5    | Over etch on part 'A' of the cantilever structure                          | 44   |

| 3.6    | SEM micrograph showing the released cantilevers                            | 48   |

| 4.1    | Schematic showing the connections made to test electrical isolation        | 52   |

| 4.2    | SEM micrograph showing the beams collapsed on the substrate                | 53   |

| 4.3    | Schematic showing the connections made to test continuity                  | 53   |

| 4.4    | Comparison of simulated and experimental values                            | 56   |

| 4.5    | Graph of correction factor 1 & 2 considered to the simulated results       | 59   |

| A.1    | Schematic representation of the LPCVD reactor                              | 61   |

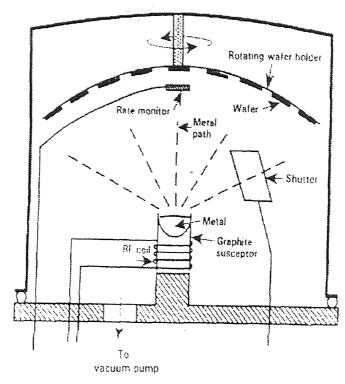

| E.1    | Schematic of a typical spherical radio-frequency evaporation system        | 72   |

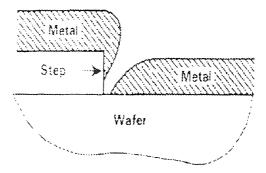

| E.2    | Metal discontinuity over step caused by shadowing in an evaporation system | 72   |

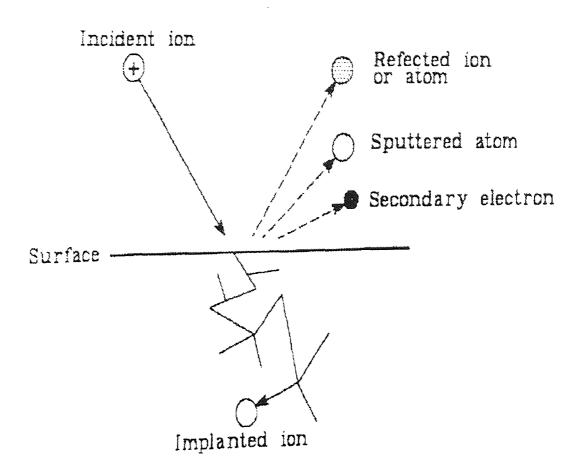

| E.3    | The sputtering process.                                                    | 73   |

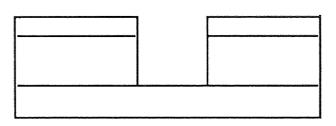

| H.1    | Anisotropic etch profile                                                   | 81   |

#### CHAPTER 1

#### **INTRODUCTION**

#### 1.1 Overview

The need for large throughput, high resolution and low cost turn the attention of semiconductor manufacturers to the reactive plasma processes. Although there has been a lot of work done in plasma processing, full monitoring of the process, especially in the area of device damage is still lacking. The present trend in the industry is towards submicron devices. As the devices get reduced in size the thickness of gate oxide is also reduced. RIE plays an important role in the definition of small dimensions. This furthers the need for a more accurate and controllable system to be installed, especially in the area of reactive ion etching.

#### 1.1.1 Device Damage from the Plasma

Wafers in a plasma are exposed to energetic particles and photon bombardment. This radiation consists of ions, electrons, ultraviolet photons and soft x-rays. While most ions bombard the surface with energies below a few tens of volts, ion energy on the 'tail' of the distribution can be more than 1000 Volts [1], depending on the sheath potential. Average electron energy in the plasma ranges from a few volts to 10V or more[1], but electrons reaching the walls are thought to have lower energy owing to the plasma potential. When

high energy radiation strikes the wafer surface, it can cause both shallow and deep surface disruption (damage), which alters electrical characteristics and degrades device performance. Both reversible and irreversible device damage can occur. In general the significance of these effects increase with particle energy, and hence with peak RF potential and power. Damage occurs in various forms, atomic displacements caused by ion impact, which have been observed upto 150 A<sup>o</sup> deep [1], electron hole pairs produced by primary ionization from the UV and X-ray photons, and secondary ionization where electrons formed by primary processes create defect centers. The damage can usually be detected by a change in the capacitance-voltage (CV) signature of the MOS capacitors, or in the operating parameters of simple transistor structure, which give threshold voltage, flatband voltage, Q<sub>SS</sub>, lifetime and other parameters.

1.1.1.1 Reversible Effects: Every plasma process causes surface alteration because of the energetic radiation present in the plasma, and almost any plasma causes some change in measured device parameters. If these changes were always irreversible, it would be hard to make useful semiconductor devices with plasma processing. Miniaturization would have been limited, since plasma processing is essential for fabricating devices with small critical dimensions. Fortunately, much of this radiation can be removed by thermal annealing.

Device damage from UV photons can be removed by a thermal anneal at 350°C [1] (to the point that the original electrical parameters determined by CV measurements are restored). High energy ion bombardment damage, on the other hand is generally

removed by annealing at 650°C [1], while severe x-ray damage is rare, because the sheath and bias potentials in most plasma processes are too low to produce an appreciable x-ray flux. In those cases where x-rays are a problem, changing some metallic parts of the reactor to insulating materials can eliminate x-ray production. Since most device fabrication schedules include thermal cycling to at least 700-900°C after the critical gate levels, much damage from plasma processing is removed naturally, without any special processing.

However, new device designs include shallow junctions, which cannot tolerate high temperature at all. Hence, high energy ion damage is becoming more of a problem. Difficulties also arise with thin gate insulators (<150 A<sup>O</sup>) that must have extremely good material characteristics for reliable performance. Here the x-ray flux must be reduced to an absolute minimum, so the use of metallic reactor surfaces is minimized and low potentials are used. Remote plasma systems (plasma transport reactors) and magnetron reactors offer a less energetic ion flux and have found increasing use in these applications.

1.1.1.2 Irreversible Effects: Unfortunately, two "killer" effects that can occur in plasma are not reversible. The first of the these is contamination during critical operations such as window and/or via-step etching. If polymer formed by the plasma itself, or foreign materials such as dirt or sputtered reactor material, enters an open contact, it will be covered later by metallization. The result is unexpected doping or an unwanted resistance,

which cannot be corrected. Hence control of reaction products from the plasma chemistry, particularly polymeric products, is essential.

A second, more subtle, source of irreversible damage is electrostatic breakdown of the thin insulating films caused by charge that is deposited during the plasma process cycle. The gate insulator film in many state-of-the-art device structures are becoming extremely thin. (150-250A°). While a high quality silicon dioxide film can withstand about 12-15MV/cm [1] for short periods, this amounts to only 10-15 volts across a 100A thick SiO<sub>2</sub> gate dielectric. Beyond this point there is a catastrophic breakdown, and no way to repair the film.

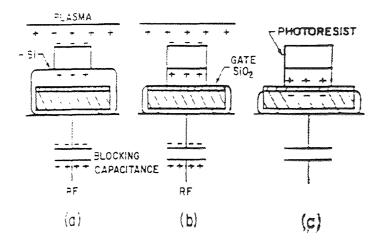

The mechanism of plasma induced breakdown is illustrated in figure 1.1

Figure 1.1 Electrostatic breakdown of gate oxide

Fig 1.1a shows a patterned polysilicon-coated wafer placed on the "cathode". When the plasma is turned on, the conductive poly which wraps around the wafer edge shields the gate dielectric and transfers the charge to the electrode and blocking capacitor.

Fig 1.1 b. The poly is patterned and the front to back conductive path is broken.

Fig 1.1c. Charge deposited during the plasma turn-off transient is trapped on the front oxide surface with mirror change below.

If the electric field generated by this charge exceeds breakdown, the thin oxide dielectric will be mechanically disrupted.

A film of conductive polysilicon was deposited over thin gate oxide (SiO<sub>2</sub>) and covered with a photoresist mask pattern. The wafer is then placed in a plasma to transfer the mask pattern into the polysilicon film. At the point depicted in Fig 1.1a the plasma has just been struck. As the sheath is established, the smaller electrode (cathode) is negatively charged by electrons until, at a steady state, there are equal fluxes of electrons and ions. Initially, the conductive polysilicon film extends around the wafer and forms a continuous electrical circuit from the front to the electrode underneath. Hence the negative electrode potential appears across the "blocking" capacitance, which is a part of the power supply or matching network. If the plasma were turned off at this point, there would be a transient flow of charge to the wafer and surrounding surface, but this charge would induce no potential across the gate because it is still surrounded by the conducting polysilicon layer. As the mask pattern is etched into the polysilicon, the conductive path at the edge of the wafer is finally broken (Fig 1.1b), and the gate electrode is isolated. Still, at this point, there is little or no potential difference between the gate electrode and substrate below because there was electrostatic equilibrium when the path was broken.

When etching is finished and the plasma is turned off, however, positive ions from the decaying plasma will deposit small amounts of charge on the resist and gate electrode. Meanwhile, the wafer substrate is maintained at the reactor electrode potential. Since the gate oxide dielectric is thin, the charge that collects can induce high transient fields across the gate and cause breakdown. Free charge reaching the reactor electrode

during this transient has little effect on its potential because of the large capacitance to ground through the blocking capacitor and stray coupling.

By contrast, if the wafer is placed on an insulating surface, substrate potential is not held at that of the large electrode and there is less danger of breakdown. In this case, voltage from the turnoff transient will be divided between the gate capacitance and the wafer/insulator/electrode capacitor. Clearly, plasma operation should be characterized with test devices to insure that transient potentials are kept well below the level that produces the electrostatic breakdown.

During photoresist stripping a similar condition can occur. Wafers are put into barrel etchers where the resist collects charge as it approaches the floating point potential of the plasma. For a typical oxygen plasma used for stripping photresist, the floating potential is about -5V. If electrical transients in the system during the resist strip cycle suddenly increase the floating point potential, electrically isolated areas can charge at different rates (because of the geometrical arrangement of wafers with respect to the plasma in the reactor) so that breakdown potential of thin insulators (12-15Vdc) is exceeded.

Another experiment further illustrates these phenomena. Capacitors with 100A [1] dielectrics fabricated on wafers were tested to determine the Fowler-Nordheim tunneling current through the capacitors as a function of impressed voltage. These wafers were divided into two groups with one group loaded into metal support "boats" and the other into quartz boats. Both boats were placed in the commercial resist strip system in which wafer boats are held on a grounded metal support system within a metal reactor chamber.

After resist stripping, the capacitors were tested a second time. Wafers in the quartz were unaffected by the stripping cycle. Tunneling current through almost half the capacitors in the metal boat group, on the other hand, increased from 5-50nA with about a 10V potential difference, to 1-50mA after the strip cycle, a level indicating a device failure (end-of-life is a tunneling current above  $1\mu\text{A}$ ).

The results are simply explained. In order for breakdown to occur, a potential difference must exist across the film. Since both sides of the wafers reached the same floating potential in the quartz boat, there was no potential difference. By contrast, the capacitor electrodes connected to the substrate in the metal boat were maintained at a ground potential so that transients in the floating potential during stripping were imposed across the SiO<sub>2</sub> film [1].

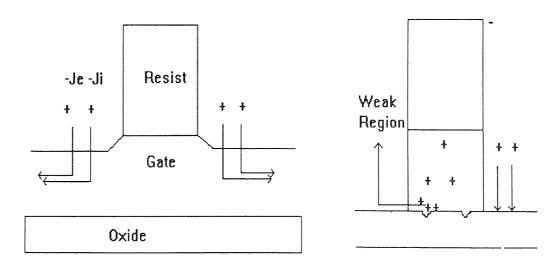

One aspect of the plasma process is the uniformity of plasma which requires precise monitoring. It is believed that during polysilicon gate etching the damage to oxide occurs mainly due to plasma non-uniformity [2]. Plasma nonuniformity produces electron and ion current that do not balance locally and can generate oxide damage. There are three main current components at the surface of a wafer placed in an rf plasma. While at 13.56 Mhz the largest is the rf displacement current, this is usually of secondary importance in surface charging because of the low impedence presented by the oxide. Next there is positive ion flux that is responsible for anisotropic etching. The flux average is nearly constant with time and depends linearly on the local plasma density. The final component, electron flux, flows briefly in every rf cycle to balance the ions lost from the central plasma region. In a uniform plasma, the ion and electron conduction currents

locally balance each other over the rf cycle. Charging is not a problem and the surface potential stays close to that of the substrate.

The situation for a nonuniform plasma differs significantly. Ion and electron currents do not have to balance locally through the rf cycle, although there must be a net balance over the electrode as a whole (refer figure 1.3). Where excess ion current occurs, the imbalance (e.g., net current flux to the wafer) causes wafer surface charging and results in increased voltage across the sheath. The charge build up continues until the currents balance or the oxide begins to conduct. The plasma inconsistencies are mainly due to electrode design which create spatial plasma potential fluctuation. The spatial plasma potential fluctuations are observed in the range of 10-20 Volts [2]. This voltage fluctuation charges the wafer surface. The capacitive coupling of contact pads and the conductors on the wafer surface can develop plasma nonuniformity and thereby create high charging effects in the oxide. The intensity of oxide charging is determined by the net local current imbalance (voltage fluctuation ) and area of the gate polysilicon after the end point is reached. Before endpoint the imbalanced current normally flows through the conducting polysilicon film [12]. Because of this current imbalance the oxide goes through nonuniform current stresses that can lead to the oxide failure or initiate degradation (charging) that may cause oxide failure at a later time.

#### 1.2 Objective

A sensor could be fabricated using existing surface micromachining techniques so as to provide manufacturers of VLSI circuits with an in-situ, non-destructive contactless

evaluation, which enables accurate monitoring of the semiconductor wafers undergoing reactive ion etching (RIE). This thesis deals with the operating principle, design, simulation, fabrication and characterization of such a sensor that could detect charging damage caused during reactive ion etching of polysilicon and other films.

In this chapter a general idea of the device principle, material selection, and design considerations is detailed. The second chapter deals with the device modeling and simulation [5,6]. Electrostatic equations and structural bending of beam equations are used to simulate the device [14-20]. The third chapter gives the detailed fabrication and process flow used [13]. The fourth chapter details the testing procedures and methodology followed. The fifth chapter deals with the results obtained from the characterization of the beams and a comparison drawn between the simulation and the actual results obtained. It also deals with the practical limitations of the device and any potential problems that might be expected to encounter during actual application.

#### 1.3 Principle of Operation

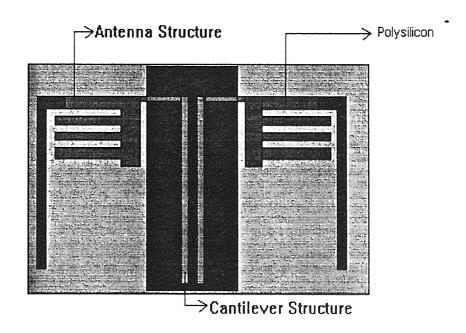

It is well known that plasma induced damage causes a spatial voltage to develop in the chamber which leads to a charge build up. The proposed design consists of a set of parallel cantilevers made of Polysilicon. These cantilevers are individually integrated with an antenna structure. These antenna structures support a large surface area so as to sense this charge. The charge thus accumulated by the antenna structure are transferred over the entire length of the polysilicon cantilever. Once there exsists a potential a

potential difference between the pair of cantilevers and as the cantilevers are in close proximity they deflect in accordance with the type of charge accumulated (like charges or unlike charges) during the plasma etching process (Refer figure 1.2).

The cantilevers can be modeled using the analogy of a parallel plate configuration. The capacitance developed in the cantilevers, the induced force and the deflection can be calculated using this analogy. Therefore, the force that drives these set of cantilevers is the electrostatic force, generated as and when the cantilevers are charged.

#### 1.4 Material Selection

This sensor is to be integrated on the wafer on which transistors are fabricated. The standard CMOS process flow includes an oxide deposition and polysilicon deposition to form the gate. A small area on the mask plate that is used to define the polysilicon gate is reserved for the sensor. At all other process steps like well formation, implantation etc. the sensor area is covered with photoresist. This will protect the sensor.

The sensors are constructed during the RIE of polysilicon. Consequently the material of the cantilever was chosen as Polysilicon. Polysilicon is a strong material with a modulus of elasticity of  $1.9 \times 10^{11}$  N/m<sup>2</sup>

Highly doped polysilicon acts as a good conductor. To calculate capacitance and electrostatic force, it is assumed that the plates are good conductors and this is necessary as good conductors aid in charge transfer over the plate area in a uniform manner. Hence polysilicon was chosen.

Some of the mechanical properties of Polysilicon are given in the table below.

**Table 1.1** Mechanical properties of Polysilicon [3]

| Mechanical Property | Value                                   |

|---------------------|-----------------------------------------|

| Yield Strength      | 7*10 <sup>10</sup> dyne/cm <sup>2</sup> |

| Knoop Hardness      | 850 Kg/mm <sup>2</sup>                  |

| Young's Modulus     | 1.9×10 <sup>11</sup> N/m <sup>2</sup>   |

| Density             | 2.3 g/cm <sup>3</sup>                   |

#### 1.5 Design Considerations

In standard CMOS process the standard dimension for the thickness of polysilicon is 0.3 - 0.5 $\mu$ . The cantilevers are to deflect in a horizontal plane where the width to thickness ratio (aspect ratio) needs to be minimized in order to achieve a larger deflection for a particular voltage. A minimum of  $2\mu$  width was chosen due to fabrication constraints. With the width and the thickness dimensions fixed the only available parameter is the length. There are eight sets of cantilevers fabricated, with the width of each ranging from  $2\mu$  to  $3\mu$  and the thickness  $1.5\mu m$ . The length of the cantilever vary from  $50\mu m$  to  $250\mu m$  in steps of  $50\mu m$ . Some of the design considerations are based on Tabrications limitations and others are based on the simulated values. Cantilevers with varying dimensions of length, width and distance between them are selected in order to get a range of working values. A length of  $250\mu$  was selected as the upper limit because a cantilevers with greater length would add significantly to sag. This would cause the

parallality to be lost in the horizontal plane. On the other hand a cantilevers with length less than  $50\mu$  would significantly reduce appreciable deflection.

The top view of the proposed structure is shown in figure 1.2

Figure 1.2 Top view of the sensor

Figure 1.3 Gate oxide damage during etching of the conductive gate electrode

#### **CHAPTER 2**

#### **SIMULATION**

#### 2.1 Introduction

As explained earlier the sensor works on the electrostatic principle. The basic force that is needed to deflect the cantilevers is obtained from the charges that get accumulated in each individual polysilicon cantilever beam that is isolated from the environment by the gate oxide.

The principle of operation, the dimensional parameters of the beams and the charge build up, force and deflection achievable is detailed. We know that the voltage that is generated in the plasma chamber will be in the range of 10-20 Volts [1,2]. Keeping this in mind simulation is done so as to arrive at a value of beam dimensions that will be able to function in the specified voltage range.

#### 2.2 Basic Electrostatics

The simulation methodology is outlined.

- i. The capacitance that is developed when a particular voltage is applied is calculated.

- ii. The electrostatic force generated owing to this capacitance is calculated. This is explained in the sub-section Device Simulation.

- iii. Deflection achieved is calculated considering parallel plates of cantilever nature (that is free at one end and fixed at the other) This is also outlined in the sub-section Device Simulation.

There are many methods to calculate the capacitance. A few of the approaches are detailed below.

A) By definition of capacitance

$$Q = CV (2.1)$$

where: 'Q' is the charge accumulated,

'C' is the capacitance,

'V' is the impressed voltage.

B) Assuming that the plates are semi-infinite, then

$$C = \varepsilon A/H = \varepsilon WL/H$$

(2.2)

where: 'ɛ' is the dielectric constant of air,

'A' is the effective area of the plates,

'H' the distance between the plates (Refer figure 2.2).

C)

$$I = dQ/dT = C dV/dT + V dC/dT [4]$$

(2.3)

where I= Transient current. (Refer figure 2.1)

Figure 2.1 Simple schematic showing application of voltage and capacitance build up

Figure 2.2 Parallel plates with width W, length L and H the distance between the plates

D) The simulation of parallel plate contributions to the capacitance is done. Also the capacitance due to fringing electric fields also constitutes a major contribution to the capacitance of narrow plates. For a  $2\mu$  process the fringing capacitance of a poly wire can be as high as the parallel capacitance [5].

The capacitance between a conducting wire and a ground plane or another wire is determined by solving the Laplace's equation. Rather than solve this electric field problem, we will examine two special cases that have well known solutions. The first special case is that of a parallel plate capacitor. The capacitance is

$$C_{plate} = \varepsilon WL/H$$

(2.4)

The capacitance depends linearly on the area WL and the dielectric constant  $\epsilon$ , and inversely on the distance H between the two plates.  $C_{plate}$  closely approximates the true capacitance when W, L >> H.

The second special case occurs for narrow wires; that is, for L>>H and  $W \le H$ . A simple expression for the capacitance can be obtained if we approximate the wire as a long cylinder [5]. In this case, we have

$$C = \frac{2\pi \varepsilon L}{\ln(1 + \frac{2H}{W}(1 + \sqrt{1 + \frac{W}{H}})}$$

(2.5)

Note that the capacitance of the cylinder depends only logarithmically on W and H. We have interpreted W as the diameter of the cylinder. An examination of these two special cases illustrates an important implication. For a given insulator of height H, narrowing the wires through better lithographic and etching techniques will linearly decrease the capacitance only until the width of the wire becomes of the same order as its height. After that, further improvements are achieved at only a logarithmic rate. Typically total capacitance is some combination of parallel plate capacitance one calculates using the parallel plate formulae and the fringing or edge capacitance. We can use Equations (2.4) and (2.5) to approximate [5] the total capacitance of the plate. We define

$$C_{\text{wire}} = C_{\text{plate}} + 2C_{\text{edge}}$$

(2.6)

where  $C_{plate}$  is given by Equation (2.4).  $C_{edge}$  can be approximated as is shown in figure 2.3.

We replace the sides of the wire with half cylinders. The edge capacitance is then approximated by half the cylinder capacitance minus a small portion of the parallel plate solution we have replaced [5].

We have

$$Cedge \approx \varepsilon L \left\{ \frac{\pi}{\ln\left(1 + \frac{2H}{T}\left(1 + \sqrt{1 + \frac{T}{H}}\right)\right)} - \frac{T}{4H} \right\}$$

(2.7)

For H = T and  $\epsilon$  = 3.9 $\epsilon$ 0, we have C edge  $\cong$  0.044fF/ $\mu$ m. This number is independent of

Т.

**Figure 2.3** Fringing capacitance of narrow wires: (a) fringing electric field lines of a wire; (b) model of a wire as a parallel plate capacitor plus a cylindrical conductor over a ground plane

Equation (2.7) is valid for polysilicon and metal lines.

This approach is used to determine the capacitance that develops between the plates.

Once this capacitance is established then the force developed due to this capacitance is calculated and the same force made use of to determine the deflection that could be generated. This is detailed in the next sub-section.

#### 2.3 Device Simulation

Again for the calculation of force there are two approaches considered.

The force developed due to this capacitance could be calculated from the equation

$$F = \frac{C^2 V^2}{2\varepsilon A} \tag{2.8}$$

where C is the capacitance developed between the plates

V is the voltage applied

A is the effective area between the plates

The value of capacitance is obtained from the latter method explained in sub-section Basic Electrostatics.

The other approach to calculate the electrostatic force is given below.

$$F = (1/2)e_0V^2 (W/H) (L/H)$$

(2.9)

(Refer figure 2.2)

#### 2.3.1 Electrostatic Attraction for Nearly Parallel Plates

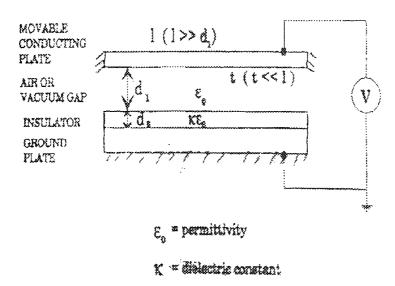

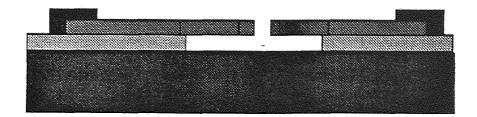

In many cases, the structural displacements can be modeled as displacements between nearly parallel plates. Figure 2.4 shows an example this case where two conducting plates are separated by an air (or vacuum) gap and one plate is covered by a thin insulator. In this case, when the voltage between the plates is held constant, the force between the plates is given by the equation 2.10 [6].

$$P = \frac{F}{A} = \frac{\varepsilon V^2}{2} \left( d_1 + d_2 / \kappa \right) - 2 \tag{2.10}$$

**Figure 2.4** Cross-section of a typical MEMS type structure showing a movable conducting plate, air gap, insulator, and immovable ground plate. A voltage, V, is applied between the upper conducting plate and the ground plate

P = Pressure  $\epsilon = Permittivity$  E = Force  $\epsilon = Permittivity$  E = Force  $\epsilon = Permittivity$   $\epsilon = Permit$

Often, one of the conducting plates will be fixed and the other allowed to move but be restrained by mechanical forces. If a voltage is applied between the plates, the plates will be attracted. At some voltage, the electrostatic attraction between the plates will be sufficient to overcome the mechanical restoring forces and some or all of the upper plate will collapse into contact with the ground plate. This voltage is called pull-in voltage  $(V_p)$ . If the voltage is now reduced, the upper plate will remain in contact until a second, lower voltage, called release voltage  $V_r$ , is reached.

Nathanson [21], first described the pull-in phenomenon for an application called the resonant gate transistor which was modeled using a pair of parallel plates with one plate fixed and the other supported by a simple spring constant K. He showed that for this system the pull-in voltage is given by Equation (2.11)

$$Vp = \sqrt{\frac{8Kd3}{27\varepsilon A}} \tag{2.11}$$

Once the force is calculated using equation 2.8, the deflection is then calculated.

Applying simple beam theory, for a cantilever structure simply supported at one end and free at the other and considering a uniformly distributed load, the deflection is given by

$$=\frac{FL^3}{8EI} \tag{2.12}$$

Here I is the moment of inertia of the beam taken about the horizontal plane and is given

by

$$I = \frac{WT^3}{12}$$

(2.13)

where: 'E' is the Youngs modulus of polysilicon

'F' the force applied on the beams as calculated by equation 2.8

'L' the length of the beam

#### 2.4 Calculations

There are two equations that are used to determine the capacitance namely, 2.4 and 2.5, and two equations available for calculation of force which are 2.8 and 2.9. All four equations are made use of in all combinations and the values obtained are compared.

A) Using equation 2.4 and 2.8 we have

$$C_{\text{plate}} = \varepsilon WL/H \text{ and } F = \frac{C^2V^2}{2\varepsilon A}$$

$\varepsilon = 8.854 \times 10^{-12} \text{ F/m}$

$W = 1.6 \mu m$ . This is the thickness obtained on deposition of polysilicon. Although W is the width of the parallel plates, in our case the effective width is nothing but the thickness of the beams as the parallel plates are in a vertical direction.

$L = 75 \mu m$ ,  $100 \mu m$ ,  $150 \mu m$ ,  $200 \mu m$ . These are the beam lengths considered

$H = 2\mu m$  is the distance between the beams

V = 10volts. This value is an arbitrary value chosen so as to determine the range in which the deflection would be expected to lie and also because we want the device to operate at this voltage.

| Lengths (μm) | Capacitance (F/m) ×10 <sup>-16</sup> | Force (N) × 10 <sup>-8</sup> |

|--------------|--------------------------------------|------------------------------|

| 75           | 5.312                                | 1.32                         |

| 100          | 7.083                                | 1.763                        |

| 150          | 10.62                                | 2.64                         |

| 200          | 14.166                               | 3.53                         |

Table 2.1 Computed values of capacitance and force using equations 2.4 and 2.8

B) Using equations 2.4 and 2.9 which are

$C_{plate} = \varepsilon W L / H$  and  $F = (1/2)e_0 V^2 (W/H) (L/H)$  we compute the capacitance and force.

Table 2.2 Computed values of capacitance and force using equations 2.4 and 2.9

| Lengths (μm) | Capacitance (F/m) ×10 <sup>-16</sup> | Force (N) × 10 <sup>-8</sup> |

|--------------|--------------------------------------|------------------------------|

| 75           | 5.362                                | 1.32                         |

| 100          | 7.083                                | 1.77                         |

| 150          | 10.62                                | 2.65                         |

| 200          | 14.166                               | 3.54                         |

C) Using equations 2.5 and 2.8 which are

$$C_{\text{plate}} = C = \frac{2\pi\varepsilon L}{\ln(1 + \frac{2H}{W}(1 + \sqrt{1 + \frac{W}{H}}))}$$

and  $F = \frac{C^2V^2}{2\varepsilon A}$  we compute the

capacitance and force.

| Lengths (μm) | Capacitance (F/m) ×10 <sup>-15</sup> | Force (N) $\times$ 10 <sup>-7</sup> |

|--------------|--------------------------------------|-------------------------------------|

| 75           | 2.16                                 | 2.19                                |

| 100          | 2.89                                 | 2.94                                |

| 150          | 4.33                                 | 4.411                               |

| 200          | 5.782                                | 5.89                                |

Table 2.3 Computed values of capacitance and force using equations 2.5 and 2.8

D) Using equations 2.5 and 2.9 which are

$$C_{\text{plate}} = C = \frac{2\pi \varepsilon L}{\ln(1 + \frac{2H}{W}(1 + \sqrt{1 + \frac{W}{H}}))}$$

and  $F = (1/2)e_0V^2$  (W/H) (L/H) we compute

the capacitance and force.

Table 2.4 Computed values of capacitance and force using equations 2.5 and 2.9

| Lengths (μm) | Capacitance (F/m) ×10 <sup>-15</sup> | Force (N) × 10 <sup>-8</sup> |

|--------------|--------------------------------------|------------------------------|

| 75           | 2.16                                 | 1.328                        |

| 100          | 2.89                                 | 1.77                         |

| 150          | 4.33                                 | 2.65                         |

| 200          | 5.78                                 | 3.54                         |

The deflection is calculated applying the simple beam equation  $\delta = FL^3/8EI$

This equation is considering a uniformly applied load for a cantilever.

$E = 1.9 \times 10^{11} \text{ N/m}^2$ , the Youngs Modulus of polysilicon

$I = WT^3/12$ , the moment of inertia of the beam considered in the vertical axis, T is the width of the cantilever which is  $2\mu m$ .

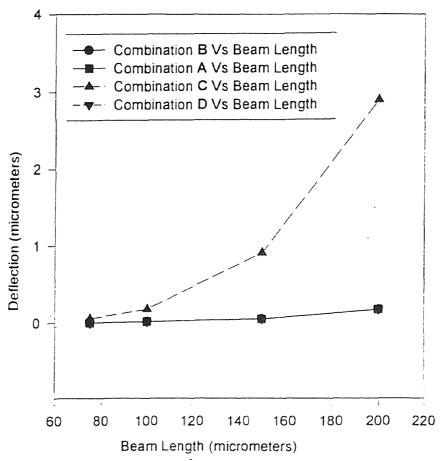

The deflection is obtained using all the four combinations

Combination 1 = A, Combination 2 = B, Combination 3 = C, Combination 4 = D

Similarly computation is done for a varying voltage for each beam length. Also the thickness of the beams is changed from 1.6 $\mu$ m to 2 $\mu$ m. The results are tabulated below.

The table 2.6 shows the voltage being increased from 2 volts to 20 volts. The beam length is varied from 100 µm to 250 µm in steps of 50 µm.

**Table 2.5** Deflection obtained for various beam lengths using the combination of equations (Computed)

| · · ·       | δ obtained for Combination of Equations (μm) |        |       |        |  |

|-------------|----------------------------------------------|--------|-------|--------|--|

| Beam Length | A                                            | В      | С     | D      |  |

| 75          | 0.0034                                       | 0.0034 | 0.056 | 0.0034 |  |

| 100         | 0.0108                                       | 0.0108 | 0.181 | 0.0108 |  |

| 150         | 0.0549                                       | 0.0549 | 0.91  | 0.0549 |  |

| 200         | 0.174                                        | 0.174  | 2.9   | 0.174  |  |

The deflections are calculated using combination D so as to include the capacitance caused due to the fringing fields. This set of deflections is the theoretical simulation results. Based on this results the dimensions of the beam have been set up.

The dimensions of the beam are as follows:

Length of the beam = Increase from  $50\mu m$  to  $200\mu m$  in steps of  $50\mu m$ .

Width of the beam = Increase from  $1.5\mu m$  to  $3\mu m$  in steps of  $0.5\mu m$ .

Thickness of the beam =  $2\mu m$

Space between the beams =  $2\mu$ m and  $2.5\mu$ m

The graph (figure 2.5) of beam length versus deflection for a constant impressed voltage of 10 Volts is shown. The graph plots the deflection calculated using the four combination of equations. It is clear that combination A, combination B and combination D match. Using Combination C we get a different set of values. Hence the simulation is done considering equation combination D.

**Table 2.6** Varying voltage and deflection simulated for varying beam lengths

| Applied | Beam Length                 |                     |                             |        |                             |       |                             |        |

|---------|-----------------------------|---------------------|-----------------------------|--------|-----------------------------|-------|-----------------------------|--------|

| Voltage |                             |                     |                             |        |                             |       |                             |        |

| Volts   | 250                         | 250μ 200μ 150μ 100μ |                             |        |                             |       |                             | 1      |

|         | Force x10 <sup>-8</sup> (N) | δ (μ)               | Force x10 <sup>-8</sup> (N) | δ (μ)  | Force x10 <sup>-8</sup> (N) | δ (μ) | Force x10 <sup>-8</sup> (N) | δ (μ)  |

| 2       | 0.221                       | 0.017               | 0.177                       | 0.0069 | 0.132                       | 0.002 | 0.088                       | 0.0004 |

| 5       | 1.38                        | 0.106               | 1.106                       | 0.043  | 0.83                        | 0.013 | 0.55                        | 0.0027 |

| 10      | 5.53                        | 0.426               | 4.427                       | 0.1743 | 3.32                        | 0.055 | 2.21                        | 0.0099 |

| 15      | 12.4                        | 0.956               | 9.96                        | 0.393  | 7.4                         | 0.123 | 4.98                        | 0.024  |

| 20      | 22.13                       | 1.706               | 17.76                       | 0.69   | 13.2                        | 0.219 | 8.85                        | 0.043  |

The graph (figure 2.6) shows the simulation of deflection versus applied voltage with the voltage increased from 2 Volts to 20 Volts. The graph is plotted over the lengths  $100\mu m$  to  $200\mu m$  in steps of  $50\mu m$ . It is seen that the deflection achieved for a cantilever of length  $200\mu m$ , width  $2\mu m$  and for a applied voltage of 20 Volts is  $0.69\mu m$ .

Figure 2.5 Graph showing the deflection calculated for the combination of equations

Figure 2.6 Graph showing deflection versus applied voltage for different beam lengths

## **CHAPTER 3**

## **FABRICATION**

## 3.1 Introduction

In this chapter the detailed fabrication sequence is described. A brief introduction to the particular process step is detailed in the beginning of each process and the actual values during the fabrication given following this. All the defects and problems encountered during each of the processing step is discussed at the end of that particular process and the ways in which to overcome these problems are also detailed.

## 3.2 NJIT Clean Room

All the process work was done in the NJIT clean-room. NJIT clean room is a 1200-sq.-ft and class 10 fabrication line. It was equipped with all the necessary tools for processing wafers up to 150mm in diameter. These equipment include:

- 1) Wafer Inspection microscope, Dektak profilemeter

- 2) Nanometrics optical line width

- 3) Wet chemical station Ultratek mask/wafer scrub

- 4) Semitool spin/rinse dryers

- 5) Karl Suss exposure system

- 6) Nanometrics FTM

- 7) Inspection microscope

- 8) MTI Coat and develop system

- 9) Drytek reactive ion etching system

- 10) Leitz MPV FTM

- 11) Varian sputtering system

- 12) BTU diffusion furnace

- 13) BTU LPCVD furnace

- 14) MDA toxic gas monitors

- 15) Tubewash station

- 16) MG Industries gas cabinets

## 3.3 Outline of the Process Steps for Fabrication

An outline of the processing steps that need to be followed is outlined. First the flow charts for the fabrication of the device is detailed and following this a schematic of the process is detailed.

## 3.3.1 Flow Sheet for Fabrication of the Device

Silicon Wafer

Deposition of LPCVD oxide

J

| Deposition of Polysilicon)                                  |

|-------------------------------------------------------------|

| <b>\</b>                                                    |

| Photolithography to pattern polysilicon                     |

| (Mask I)                                                    |

| (Mask 1)  ↓                                                 |

| Reactive Ion Etching(RIE) of Polysilicon                    |

| <b>\</b>                                                    |

| Sputtering of Metal                                         |

| $\downarrow$                                                |

| Photolithography to pattern the Metal                       |

| (Mask 2)                                                    |

| $\downarrow$                                                |

| Wet Etch of the Metal                                       |

| <b>\</b>                                                    |

| Photolithography to define the sacrificial oxide etch areas |

| (Mask 3)                                                    |

Wet etch of the sacrificial oxide to release the beam structures

## 3.3.2 Schematic of the Fabrication of the Device

The figure shows the step by step processes the wafer undergoes. A small description is given as the caption to each figure

Figure 3.1 a A plain silicon wafer is taken and the preliminary steps like denuding and cleaning it in DI water is done

Figure 3.1 b A 1.5 µm thick LPCVD LTO is deposited on the wafer

Figure 3.1 c A 1.5 µm thick polysilicon is deposited on the LTO

Figure 3.1 d This polysilicon is patterned using Mask 1. Top and side view are seen

Figure 3.1 e A  $0.5\mu m$  metal is sputtered on the patterned polysilicon.

Figure 3.1 f The metal is wet patterned using Mask2 and wet etched as shown in the top and side view

Figure 3.1 g Sacrificial mask # 3 is used to pattern the wafer so as to define the oxide etch regions.

Figure 3.1h The wafer is etched in a wet etch bath so as to release the beams

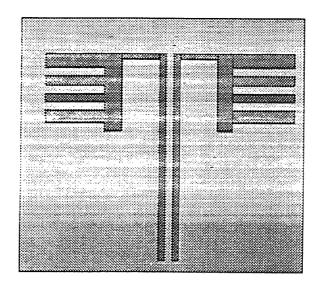

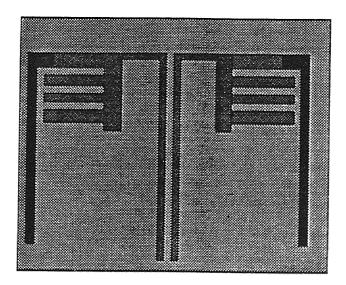

The mask plates #1,#2 and #3 that are used were fabricated by Photronics Inc. The design of these masks are shown below. Figure 3.2 a shows the mask 1 which is the polysilicon pattern mask. This pattern defines the beam and antennae design. Figure 3.2 b shows the metal routing design. This mask is used to route the metal lines to provide for probing. Figure 3.2 c shows the mask used to define the sacrificial etch oxide in order to release the beams.

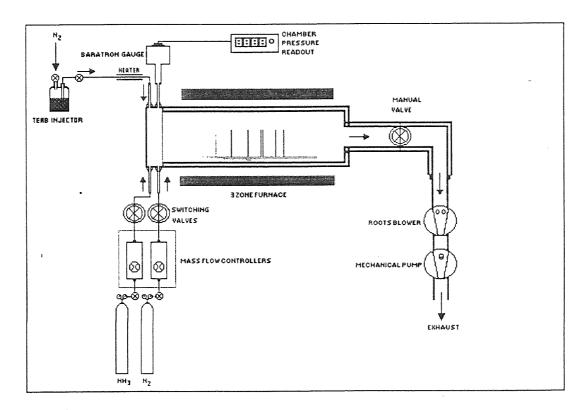

## 3.4 Deposition of SiO<sub>2</sub> by LPCVD

#### 3.4.1 Introduction

Low pressure chemical vapor deposition (LPCVD) of silicon di oxide is generally based on the reaction of SiH<sub>4</sub> and oxygen. The feasibility of using organic liquid sources like tetra ethyl ortho silicate(TEOS), ethyl tri ethoxy silane(ETOS), diacetoxydi-tert-butoxysilane(DADBS), to form silicon di oxide for microelectronics applications has

Figure 3.2 a Polysilicon pattern mask design

Figure 3.2 b Metal pattern design

Figure 3.2 c Sacrificial oxide pattern design

Figure 3.2d All the mask patterns superimposed on one another

demonstrated by several researchers. Such liquid precursors offer numerous advantages over the use of silane including superior step coverage and increased safety.

DES is a precursor capable of producing oxide films at temperatures as low as  $350^{\circ}$ C, thus allowing its use as a dielectric between aluminum metallization levels or as a top layer passivation coating. DES has several advantages over silane including superior conformity, low particulate formation, low stress, and high crack resistance. DES is a colorless liquid with a boiling point of  $56^{\circ}$ C and freezing point less than  $-76^{\circ}$ C at atmospheric pressure. It exhibits a vapor pressure of 207 Torr at  $20^{\circ}$ C.

The description of the LPCVD reactor is detailed in Appendix A

## 3.4.2 Experimental Values

The requirement was an oxide of thickness  $1.5\mu m$ . The wafer underwent the following process steps before loading them into the furnace. A total of 12 wafers of p-type was chosen as the batch. The wafers were purchased from WaferNet Inc. The sheet resistivity of these wafers was  $10~\Omega/square$ .

The detailed flow chart of the process and the oxide deposition conditions is detailed in Appendix A2.

The deposition rate of the LPCVD reactor was  $600A^{\circ}$  /minute. One of the wafers was removed from the furnace after the first 8 hours of deposition and its thickness measured. It was found that the deposition rate had considerably lowered . The new deposition rate was found to be  $540~A^{\circ}$  /minute. Based on this deposition rate the time to completion was fixed. The entire deposition took 24 hours and 45 minutes resulting in an average oxide thickness of  $1.43\mu$ .

An important note here is that the wafers were not removed from the reactor at any point of time. Therefore there was no need for any kind of denuding to be done in between depositions.

The oxide thickness was measured using a Leitz MPV FTM. The oxide thickness were measured at 13 points on the wafer. The points at which the oxide thickness was measured and the thickness is detailed in Appendix A3. The oxide thickness measured was 1.6µm.

## 3.5 Deposition of Polysilicon

## 3.5.1 Introduction

Applications of polysilicon to IC construction include its use for leads and MOS gate electrodes, as a fuse material in making ROMs, as load resistors in some MOS circuits, and as a diffusion source for emitter or source/drains. In addition, active devices will occasionally be made in thin-film polysilicon.

All of these applications require layers of polysilicon less than 1µm thick. But polysilicon is an extremely strong material and is very popular as a structural material and is dominating most of the MEMS devices. The mechanical properties of polysilicon is given in Appendix B.

The methods of polysilicon deposition is detailed in Appendix C. The process flow chart and the deposition conditions are outlined in Appendix C1

The polysilicon deposited was measured to be 1.6µm thick.

## 3.6 Polysilicon Doping

The polysilicon film of thickness  $1.5\mu m$  had to be doped with Phosphorus so as to achieve a very low resistivity. The process flow of the doping and the process conditions is detailed in Appendix D.

Doping serves two purposes. Firstly as mentioned before we need a very low resistivity of Polysilicon as the polysilicon beams are going to carry charge. The

resistivity being low this will aid in easy charge transfer and will not result in any sort of temperature build up.

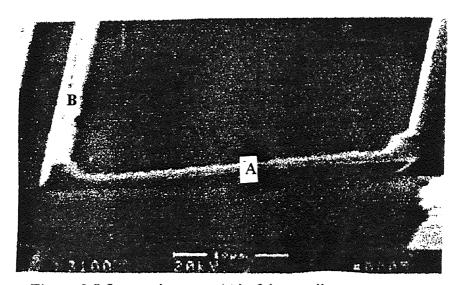

Also diffusion is carried out at 950°C. This acts as a thermal mechanism to reduce strain built in the polysilicon while undergoing deposition. It is clearly noticed that polysilicon films that have undergone annealing have considerable reduction in strain. This is well substantiated by the fact that there was no bending or warping of the beams during release. The longest beam is 250µm and as the SEM micrograph 3.5 shows, there is no bending along the entire length. Therefore there was no need to add another anneal step as the diffusion itself took care of this.

Also important to note that after diffusion there is about 1500A° of oxide deposited on the wafer. We used a 1 minute BOE etch to get rid of this oxide layer. This should be done carefully as any remains of oxide will hinder the device working by acting as an insulator.

Figure 3.3 SEM micrograph showing horizontal beams with no bending

The Polysilicon resistivity was again measured and found to be  $10 \Omega$ /square. This is well within the expected value.

## 3.7 Photolithography

## 3.7.1 Introduction

Fabrication of micro electro mechanical devices or optic devices on a silicon substrate requires working on a tiny region of the substrate. The patterns that define such regions are created by lithographic processes. That is layers of photoresist materials are first spin coated onto the wafer substrate. Next the resist layer is selectively exposed to a form of radiation, such as ultra violet light, electrons, or x rays. An exposure tool and mask, or a data tape in electron beam lithography are used to effect the desired selective exposure. The patterns in the resist are formed when the wafer undergoes the subsequent "development" step. The areas of the resist remaining after development protect the substrate regions they cover. Locations from resist has been removed can be subjected to a variety of additive or subtractive processes that transfer the pattern onto the substrate surface.

The basic photoresist terminology and description of the lithographic process is described in Appendix G.

## 3.8 Etching

## 3.8.1 Introduction

Etching in microelectronics fabrication is a process by which material is removed from the silicon substrate or from thin films on the substrate surface. When the mask layer is used to protect specific regions of the wafer surface, the goal of etching is to precisely remove the material which is not covered by the mask.

The theory of wet and dry etching is detailed at length in Appendix H.

## 3.8.2 Description of the RIE Process

The polysilicon was etched using slightly different conditions than the standard conditions followed by the clean room. The clean room standards as well as the conditions that were used are given in the table below.

**Table 3.1** Conditions to etch Poly (Standard)

| Power                        | 400 W     |

|------------------------------|-----------|

| Pressure                     | 150 mTorr |

| Flow rate of SF <sub>6</sub> | 50 sccm   |

| Flow Rate of Freon-112       | 50sccm    |

| Temperature                  | 25°C      |

The etch rate for Polysilicon is 388 Å/min under these conditions. Thus the etch time is decided depending on the thickness of the Polysilicon.

The conditions above resulted in polysilicon cantilevers having poor vertical walls. The edges of the cantilever were sloped by at least 150. This is not acceptable as the effective electrostatic force will reduce in case the walls are not perfectly vertical. To reduce this effect the power of the reactor was maximized and the pressure in the chamber minimized so as to achieve a concentrated etch on the polysilicon resulting in good vertical walls. The table shows the process conditions to etch polysilicon.

**Table 3.2** Conditions used for etching of Polysilicon

| Power                        | 650 W    |

|------------------------------|----------|

| Pressure                     | 70 mTorr |

| Flow rate of SF <sub>6</sub> | 37 sccm  |

| Flow Rate of Freon-112       | 37sccm   |

| Temperature                  | 25°C     |

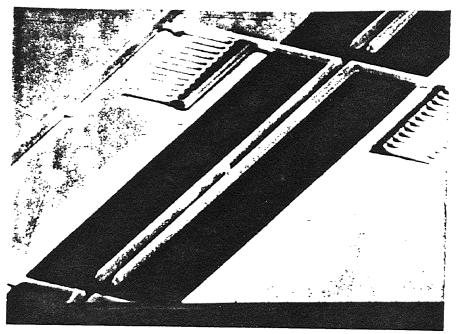

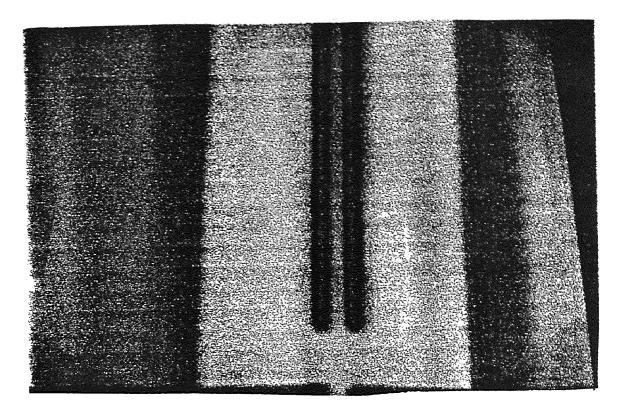

The etching of polysilicon was done and observed under the microscope. The SEM micrograph shows the polysilicon after the etching is completed. We can clearly see that the etching is uniform and there is a clear gap between the beams.

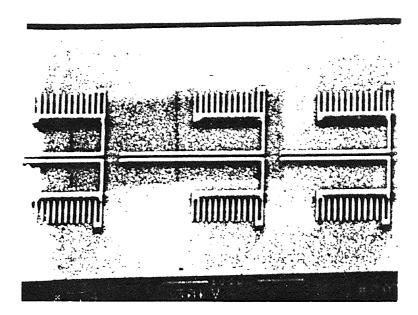

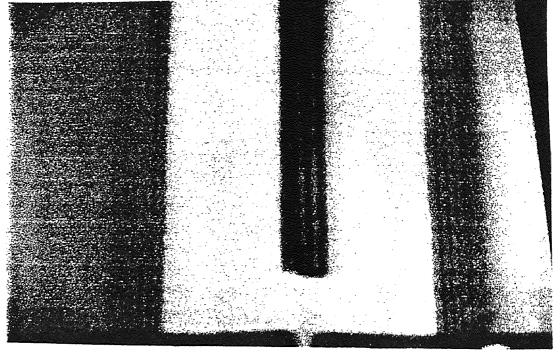

Another problem that arose due to the increased power was that the part 'A' of the cantilever structure was consistently getting over etched compared to part 'B' (refer figure 3.5). This may be due to localized loading effect and the formation of a retarding potential being developed in the part 'B' of the cantilever. The retarding potential may

develop due to continuous exposure to the plasma and reduces the anisotropic etching effect of the ions. On the other hand part 'B' has another cantilever just 2µm from it. In order to minimize the overetch on 'A' the process was carried out in four etch stages, the time of each etch being 8 minutes. This helped in reducing the effect of the retarding potential. This effective and a uniform etch was obtained.

Figure 3.4 Micrograph of the etched polysilicon beams

Figure 3.5 Over etch on part 'A' of the cantilever structure

## 3.9 Metal Sputtering

## 3.9.1 Introduction

The next step in the fabrication of the device is the metal deposition. Metal is used as the connections of the device. The metal used here was an alloy of Al-Si-Cu.

The most widely used techniques to deposit metals are, evaporation, sputtering, and CVD (chemical vapor deposition). Variations to these techniques are collimated sputtering and selective CVD. Some of the deposition methods are detailed in Appendix E. The flow chart as well as the deposition conditions are also detailed in Appendix E.

## 3.9.2 Photolithography and Patterning of Metal

After the metal deposition, the sheet resistivity of the wafer is checked. It should be in the range of 1-2 $\Omega$ /. The wafer is then taken and photoresist pun on it. This is then patterned using mask #2. The wafer is ready for metal etching. Metal etching was done by a wet etch process.

The wet etch process involves that the wafer be dipped in a solution of etchant which is a combination of sulfuric and nitric acid.

The etch rate at 45°C is 1000 A°/minute. This is a critical step as the aluminum etching solution eats away the metal deposited in 30 seconds as we have a thickness of only 5000 A°

As soon as the 30 seconds is up the wafer is immediately dipped in water so as to stop the reaction. The wafer is then dipped in a photoresist strip bath of M-pyrol. This isn't done

in a conventional p-strip bath as there is metal deposited and the p-strip bath attacks metal. Therefore if there is metal deposited on the wafer then the M-pyrol bath is used. The time of stripping is usually 5 minutes in bath A and 5 minutes in the bath B.

#### 3.10 Sacrificial Oxide Etch

The device is now ready for release of the cantilever structures. Photolithography is done so as to pattern the areas that need to be protected and the areas around the beams exposed. Mask #3 is used for this. Once the patterning is done the wafers are ready for release.

The method of etching followed here is wet etching. We need an isotropic etch so that oxide underneath the beams also is etched. The etching solution for oxide selected was Hydrofluoric Acid (HF). Buffered HF in the ratio 7:1 was selected.

A experiment was set up so as to take care of the following potential problems:

a) In case the time chosen for the etch results in an over etch then there is a problem of the beams collapsing on the substrate.

- b) In case of an under etch time, then the beams will not be released from the substrate.

- c) One of the major problems facing the release of cantilever or doubly supported beams is the effect of Van der Waals forces that come into play during the phase change from liquid to gas. This occurs when the wafer is washed with water and the water dries in air. The water molecules under the beams pull the beams onto the substrate when they evaporate. Care should be taken to avoid this problem.

The method of avoiding the first two problems is by arriving at a process time that optimally etches the sacrificial oxide layer. This time was experimentally determined to be 8 minutes and 30 seconds. The process steps followed for the sacrificial etch is detailed in Appendix F.

The points to be born in mind while carrying out this process step are:

- I) At no point of time should the wafer be allowed to dry. There should always be a film of liquid on the wafer. While transferring from the BHF bath to the DI water bath, a film of BHF must be allowed to remain on the wafer.

- ii) A film of M-Pyrol is allowed to remain on the wafer and this is placed as is on the hot plate. The hot plate is kept at 120°C and there is a step increase from room temperature to 120°C. This results in the liquid molecules quickly drying up.

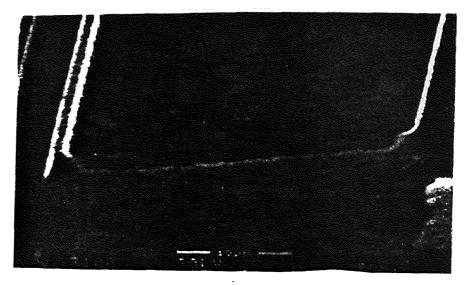

It is observed that there is no collapse of the beams on the wafer on the substrate if the above mentioned points are followed. The SEM micrograph shows the released cantilever beams.

Figure 3.6 SEM micrograph showing the released cantilever beams

## **CHAPTER 4**

## TESTING PROCEDURE AND RESULTS

#### 4.1 Introduction

The method adopted in calibrating the sensor is detailed in this chapter. Following this the experimental results are outlined.

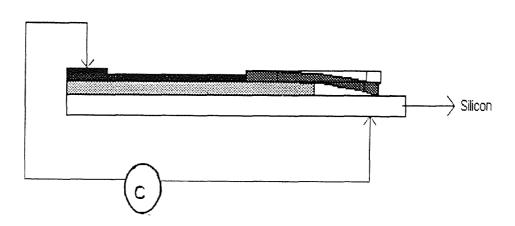

As we know the device is based on the electrostatic principle, several methods have been used to test the device. In our case a voltage is applied between the cantilevers. This is done by probing the metal bonding pads. The bonding pads are made of Al-Cu-Si alloy and are routed in such a fashion such that they directly connect to the antennae structures of each individual cantilevers. The routing is designed in such a way that the cantilever pairs i.e. the right cantilever and the left cantilever of each device are electrically isolated. As there are eight columns and six rows of devices on each module the total number of devices on each die is forty eight. Each of the device has two connecting points or probing points so as to power it. That brings the total number of probing pads to ninety six. The size of each module has to be minimized so as to achieve greater packing density on each wafer. The overall size of each module is about ten thousand micron by ten thousand micron. It is possible to fit in ninety six bonding pads in this limited area considering the fact that the

bonding pads have to be of a minimum of 500µm by 500µm each with a gap of at least 500µm between them.

This problem was solved by connecting all the right cantilevers of each device to one single bonding pad. In this case the voltage will have to be impressed between the left cantilever of the device under consideration and the common bonding pad for that particular module. This has proved to work effectively as we save space on the chip as well as the time of testing is considerably shortened. For testing many devices on each module only the left bonding pad of each device will have to be probed. The right cantilever's bonding pad will remain probed all the time as long as the same module is being tested.

A probe station made by the Micromanupulator company was used. The wafer was split into 6 parts due to space limitations on the microscope. An optical microscope was used to test the device. The wafers are vacuum held on the probe station and are also clamped lightly onto the microscope. A d.c voltage source is applied. The left probe is connected to the +ve of the supply and the right probe connected to the -ve of the supply. The current cut off is kept at a minimum as we are interested in applying a constant voltage with minimum current flow.

## 4.2 Steps Involved in Testing

A detailed account is given of the steps involved in testing.

The wafer is placed on the microscope base. A thorough survey of the wafer is done. Checks for presence of dirt or any other foreign body is essential as this may lead to

some unforeseen problems. The wafer is scanned and a good module is then selected for experimentation. Selection of a module involves:

- i) The polysilicon cantilevers look uniform and are straight, there should not be any curvature along the length of the cantilevers whatsoever. Also the cantilevers must appear released from the oxide underneath. This means that all of the sacrificial oxide should have been etched away. This is difficult to see in an optical microscope as the only view achievable in this case is a top view. Therefore a Scanning Electron Microscope is used. The SEM micrograph gave a very clear indication whether or not the cantilevers are released.

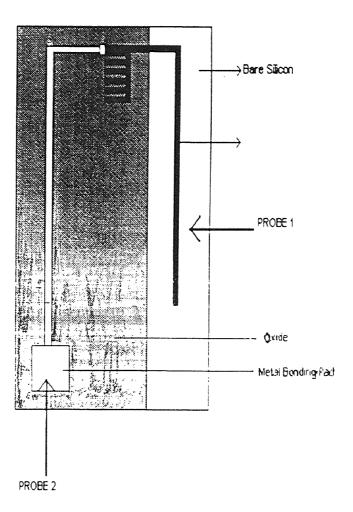

- ii) The next step is to check if the cantilevers have collapsed onto the substrate. The problem of cantilevers collapsing onto the substrate can take place due to adhesion of the water molecules present in between the cantilevers and the substrate. The Van der Waals forces present can be very high and even bond the cantilevers onto the substrate. Also the cantilevers may collapse on to the substrate due to self weight. To make sure the cantilevers are released is checked with the help of the SEM. Another method of testing this problem is by checking the connectivity between the cantilevers and the substrate. As shown in figure 4.1 one of the bonding pads is probed and the other probe is connected to the substrate. If the cantilevers have collapsed on the substrate then this acts as a electrical short.. If there is no continuity then this could mean one of two things. Either the cantilevers are upright or there is a electrical break in the metal routing. The SEM micrograph 4.2 shows the cantilever collapsed onto the substrate. This particular device shows a continuity when the test is done.

iii) The metal routing needs to be checked to make sure that the applied voltage on the bonding pad is reaching the cantilevers. As shown in figure 4.3 the bonding pad is probed and the antennae structure is probed. We got a continuity signal.. This proves that there is good contact between the poly and the metal and also that the route is good. One of the problems faced during fabrication is the step coverage occurring between the metal and the poly. The polysilicon is  $1.6\mu m$ . The metal thickness is  $0.5\mu m$  and there may be a break in the metal covering the polysilicon. This test ensures that there is good contact between the poly and metal.

Figure 4.1 Schematic showing the connections made to test the electrical isolation

Figure 4.2 SEM micrograph showing the cantilevers collapsed on the substrate.

Figure 4.3 Schematic showing the connection made to test continuity

iv) The next step is to apply voltage. The probes are placed on the bonding pads so as to power individual devices. The d.c source is in the 'off' position. After the connections are

made the current is kept at a minimum and the voltage is increased in steps of 2 volts. The microscope is connected to the video monitor and the experiment is recorded.

Some of the points to be noted during testing are:

- A) Care should be taken to see that the corresponding device is being tested for the bonding pads that are being probed. Although this seems to be a simple problem it seems to be the most prevalent one.

- B) The increase in voltage should be done extremely slowly, about 2 volts every 30 seconds.

- C) On the event of any of the probe wires touching ground, it will not be possible to increase the voltage on the source. If such a problem should arise then isolation of the wires are to be checked. This problem may occur also if there has been a localized oxide breakdown. The oxide is about 1.6µm thick. In case we increase the voltage to about 100 volts then there is a possibility of oxide breakdown. This causes a electrical short to the ground and it will not be possible to achieve increase in voltage.

## 4.3 Experimental Results

The test results obtained are as follows. The cantilever of length  $150\mu m$  deflected by  $2\mu m$  for an applied voltage of 65 Volts. As the space between the beams was  $2\mu m$ , the maximum achievable deflection is also  $2\mu m$ . It was not possible to record the deflection at incremental steps of applied voltage as the cantilevers were pulled towards each other instantly.

55

incremental steps of applied voltage as the cantilevers were pulled towards each other instantly.

Similarly beams of length  $200\mu m$  and  $250\mu m$  deflected by  $2\mu m$  for applied voltages of 56 volts and 50 Volts.

## 4.4 Discussion

The Table 4.1 shows the comparison of the experimental results and the simulated results for the following parameters:

- I) The length of the cantilevers :  $150\mu m$ ,  $200\mu m$  and  $250\mu m$

- ii) The width of the cantilevers: 2µm

- iii) The thickness of the cantilevers: 1.6µm

- iv) The space between the cantilevers : 2μm

- v) The deflection is set at 2μm

- vi) The permitivity of air  $\varepsilon = 8.854 * 10^{-12}$

- vi) The young's modulus of Polysilicon =  $1.9 * 10^{-11} \text{ N/m}^2$

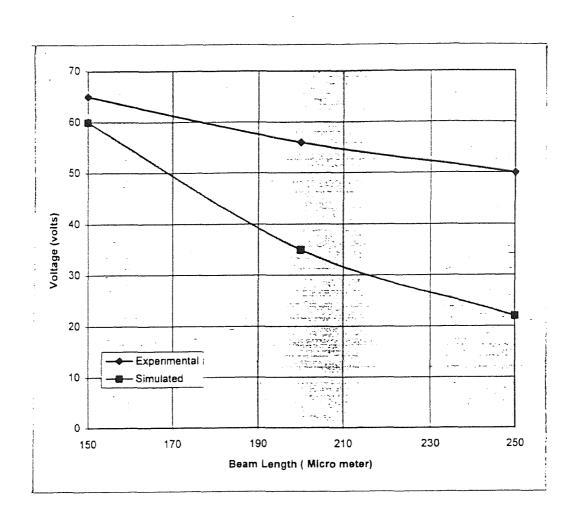

This is also summarized in figure 4.4

Table 4.1 Comparison of experimental and simulated values

|                        | Voltage (Volts) |           | Deflection (μm) |  |  |

|------------------------|-----------------|-----------|-----------------|--|--|

| Cantilever Length (µm) | Experimental    | Simulated | Constant        |  |  |

| 150                    | 65              | 60.1      | 2               |  |  |

| 200                    | 56              | 35        | 2               |  |  |

| 250                    | 50              | 22        | 2               |  |  |

Figure 4.4 Comparison of simulated and experimental values

## Estimation of beam length