## **Copyright Warning & Restrictions**

The copyright law of the United States (Title 17, United States Code) governs the making of photocopies or other reproductions of copyrighted material.

Under certain conditions specified in the law, libraries and archives are authorized to furnish a photocopy or other reproduction. One of these specified conditions is that the photocopy or reproduction is not to be "used for any purpose other than private study, scholarship, or research." If a, user makes a request for, or later uses, a photocopy or reproduction for purposes in excess of "fair use" that user may be liable for copyright infringement,

This institution reserves the right to refuse to accept a copying order if, in its judgment, fulfillment of the order would involve violation of copyright law.

Please Note: The author retains the copyright while the New Jersey Institute of Technology reserves the right to distribute this thesis or dissertation

Printing note: If you do not wish to print this page, then select "Pages from: first page # to: last page #" on the print dialog screen

The Van Houten library has removed some of the personal information and all signatures from the approval page and biographical sketches of theses and dissertations in order to protect the identity of NJIT graduates and faculty.

INFORMATION TO USERS

This manuscript has been reproduced from the microfilm master. UMI

films the text directly from the original or copy submitted. Thus, some

thesis and dissertation copies are in typewriter face, while others may be

from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the

copy submitted. Broken or indistinct print, colored or poor quality

illustrations and photographs, print bleedthrough, substandard margins,

and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete

manuscript and there are missing pages, these will be noted. Also, if

unauthorized copyright material had to be removed, a note will indicate

the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by

sectioning the original, beginning at the upper left-hand corner and

continuing from left to right in equal sections with small overlaps. Each

original is also photographed in one exposure and is included in reduced

form at the back of the book.

Photographs included in the original manuscript have been reproduced

xerographically in this copy. Higher quality 6" x 9" black and white

photographic prints are available for any photographs or illustrations

appearing in this copy for an additional charge. Contact UMI directly to

order.

UMI

A Bell & Howell Information Company 300 North Zeeb Road, Ann Arbor MI 48106-1346 USA 313/761-4700 800/521-0600 UMI Number: 9635200

Copyright 1996 by Wu, Ying-Chieh

All rights reserved.

UMI Microform 9635200 Copyright 1996, by UMI Company. All rights reserved.

This microform edition is protected against unauthorized copying under Title 17, United States Code.

300 North Zeeb Road Ann Arbor, MI 48103

| ÷ |   |  |

|---|---|--|

|   |   |  |

|   |   |  |

|   |   |  |

|   | * |  |

#### ABSTRACT

## THEORY AND DESIGN OF PORTABLE PARALLEL PROGRAMS FOR HETEROGENEOUS COMPUTING SYSTEMS AND NETWORKS

## by Ying-Chieh Wu

A recurring problem with high-performance computing is that advanced architectures generally achieve only a small fraction of their peak performance on many portions of real applications sets. The Amdahl's law corollary of this is that such architectures often spend most of their time on tasks (codes/algorithms and the data sets upon which they operate) for which they are unsuited. Heterogeneous Computing (HC) is needed in the mid 90's and beyond due to ever increasing superspeed requirements and the number of projects with these requirements. HC is defined as a special form of parallel and distributed computing that performs computations using a single autonomous computer operating in both SIMD and MIMD modes, or using a number of connected autonomous computers. Physical implementation of a heterogeneous network or system is currently possible due to the existing technological advances in networking and supercomputing. Unfortunately, software solutions for heterogeneous computing are still in their infancy. Theoretical models, software tools, and intelligent resource-management schemes need to be developed to support heterogeneous computing efficiently. In this thesis, we present a heterogeneous model of computation which encapsulates all the essential parameters for designing efficient software and hardware for HC. We also study a portable parallel programming tool, called Cluster-M, which implements this model. Furthermore, we study and analyze the hardware and software requirements of HC and show that Cluster-M satisfies the requirements of HC environments.

## THEORY AND DESIGN OF PORTABLE PARALLEL PROGRAMS FOR HETEROGENEOUS COMPUTING SYSTEMS AND NETWORKS

by Ying-Chieh Wu

A Dissertation

Submitted to the Faculty of

New Jersey Institute of Technology

in Partial Fulfillment of the Requirements for the Degree of

Doctor of Philosophy

Department of Computer and Information Science

May 1996

Copyright © 1996 by Ying-Chieh Wu ALL RIGHTS RESERVED

#### APPROVAL PAGE

# THEORY AND DESIGN OF PORTABLE PARALLEL PROGRAMS FOR HETEROGENEOUS COMPUTING SYSTEMS AND NETWORKS

## Ying-Chieh Wu

| Dr. Mary M. Eshaghian, Dissertation Advisor                                                              | Date   |

|----------------------------------------------------------------------------------------------------------|--------|

| Director of Advanced Computer Architecture and Parallel Processing Labo                                  | ratory |

| Assistant Professor of Computer and Information Science and                                              |        |

| Electrical and Computer Engineering, NJIT                                                                |        |

|                                                                                                          |        |

|                                                                                                          |        |

|                                                                                                          |        |

| Dr. John D. Carpinelli, Jommittee Member                                                                 | Date   |

| Director of Computer Engineering                                                                         |        |

| Acting Associate Chair of Electrical and Computer Engineering                                            |        |

| Associate Professor of Electrical and Computer Engineering and                                           |        |

| Computer and Information Science, NJIT                                                                   |        |

|                                                                                                          |        |

|                                                                                                          |        |

| Dr. Peter A. Ng, Committee Member                                                                        | D (    |

|                                                                                                          | Date   |

| Professor and Chairperson of Computer and Information Science, NJIT                                      |        |

|                                                                                                          |        |

|                                                                                                          |        |

| Dr. Alice C. Parker, Committee Member                                                                    | Date   |

| The Vice Provost for Research and Dean of Graduate Studies                                               | - 400  |

| Professor of Electrical Engineering-Systems,                                                             |        |

| University of Southern California, Los Angeles, CA                                                       |        |

| omversity of bouthern camorna, bos ringeles, or                                                          |        |

|                                                                                                          |        |

|                                                                                                          |        |

| Dr. Richard B. Scherl, Committee Member                                                                  | Date   |

| Assistant Professor of Computer and Information Science, NJIT                                            | Date   |

| Tibbliotant I Totobot of Compator and Information Science, 11011                                         |        |

|                                                                                                          |        |

|                                                                                                          |        |

|                                                                                                          |        |

| Dr. Sotirios G. Ziavras, Committee Member                                                                | Date   |

| Dr. Sotires G. Ziavras, Committee Member  Associate Professor of Electrical and Computer Engineering and | Date   |

#### BIOGRAPHICAL SKETCH

Author: Ying-Chieh Wu

**Degree:** Doctor of Philosophy

**Date:** May 1996

#### Undergraduate and Graduate Education:

- Doctor of Philosophy in Computer Science, New Jersey Institute of Technology, Newark, NJ, 1996

- Master of Science in Computer Science,

University of Missouri, Columbia, MO, 1992

- Bachelor of Science in Computer Science,

Tunghai University, Taichung, Taiwan, 1989

Major: Computer Science

#### Journal Publications:

- 1. A Suboptimal Heterogeneous Mapping, with M. M. Eshaghian and A. C. Parker, accepted for publication in *Journal of High Performance Computing*, 1996.

- 2. Evaluation of Two Programming Paradigms for Heterogeneous Supercomputing, with S. Chen, M. M. Eshaghian, R. Freund and J. L. Potter, *Journal of Parallel and Distributed Computing*, 31(1), pp. 41-55, Nov., 1995.

- 3. Mapping Arbitrary Nonuniform Task Graphs onto Arbitrary Nonuniform System Graphs, with S. Chen and M. M. Eshaghian, in revision for publication in *IEEE Transactions on Parallel and Distributed Systems*.

- 4. The Heterogeneous Optimal Selection Theory, with S. Chen, M. M. Eshaghian, A. Khokhar and M. E. Shaaban, in revision for publication in *Parallel Processing Letters*.

- On Estimating The Resource Requirements of Heterogeneous Tasks, with M. M. Eshaghian and A. C. Parker, submitted to Future Generations Computer Systems.

#### **Book Chapters and Magazines**

- A Portable Programming Model for Network Heterogeneous Computing, in M. Eshaghian (ed.) Heterogeneous Computing, Artech House, Norwood, MA, 1996.

- 2. Mapping and Resource Estimation in Network Heterogeneous Computing, in M. Eshaghian (ed.) *Heterogeneous Computing*, Artech House, Norwood, MA, 1996.

- 3. A Portable Parallel Programming Tool, with M. Eshaghian, submitted to *IEEE Computer*, Oct., 1995.

#### Conference Publications:

- 1. A Suboptimal Algorithm for Mapping Parallel Tasks onto Heterogeneous Systems, with M. M. Eshaghian and A. C. Parker, submitted to Fifth IEEE International Symposium on High Performance Distributed Computing, January 1996.

- 2. Mapping Arbitrary Non-Uniform Task Graphs onto Arbitrary Non-Uniform System Graphs, with S. Chen and M. M. Eshaghian, *Proc. of the International Conference on Parallel Processing*, Vol. II, pp. 191-195, Oconomowoc, WI, August, 1995.

- 3. On Estimating The Resource Requirements of Heterogeneous Tasks, with M. M. Eshaghian and A. C. Parker, *Proc. of the IPPS Workshop on Heterogeneous Computing*, pp. 47-52, Santa Barbara, CA, April, 1995.

- A Sub-Optimal Assignment of Application Tasks onto Heterogeneous Systems, with J. Desouza-Batista, M. M. Eshaghian, A. C. Parker, and S. Prakash, Proc. of the IPPS Workshop on Heterogeneous Computing, pp. 9-16, Cancun, Mexico, April, 1994.

- 5. Scalable Heterogeneous Programming Tools, with S. Chen, M. M. Eshaghian, R. F. Freund, and J. L. Potter, *Proc. of the IPPS Workshop on Heterogeneous Computing*, pp. 89-96, Cancun, Mexico, April, 1994.

To my lovely wife and my parents

#### ACKNOWLEDGMENT

The author wishes to express his sincere gratitude to his advisor, Professor Mary M. Eshaghian, for her guidance, friendship, and moral support throughout this research.

Special thanks to Professor John D. Carpinelli, Professor Peter A. Ng, Professor Alice C. Parker, Professor Richard B. Scherl, and Professor Sotirios G. Ziavras for serving as members of the committee and offering invaluable suggestions to this dissertation.

The author appreciates the consistent help from the Cluster-M project team members: Geetha Chitti, Ajitha Gadangi, Javier G. Vasquez, and especially Dr. Song Chen.

Lastly, the author wants to thank his dear wife, Shiu-Ling Chen, for her love, understanding and help without which he simply can not complete this dissertation.

## TABLE OF CONTENTS

| C | hapt | er     |                                                       | Page |

|---|------|--------|-------------------------------------------------------|------|

| 1 | INT  | RODU   | UCTION TO HETEROGENEOUS COMPUTING                     | . 1  |

|   | 1.1  | Intro  | duction                                               | . 1  |

|   | 1.2  | Netwo  | ork Layer                                             | . 2  |

|   | 1.3  | Comr   | nunication Layer                                      | . 4  |

|   | 1.4  | Intell | igent Layer                                           | . 5  |

|   |      | 1.4.1  | Code Profiling and Analytical Benchmarking            | . 5  |

|   |      | 1.4.2  | Heterogeneous Optimal Selection Theory                | . 6  |

|   | 1.5  | Organ  | nization of the Dissertation                          | . 8  |

|   |      | 1.5.1  | Portable Programming Model                            | . 9  |

|   |      | 1.5.2  | Partitioning, Mapping and Scheduling                  | . 10 |

|   |      | 1.5.3  | Hardware Estimation                                   | . 12 |

|   |      | 1.5.4  | Software Environments                                 | . 12 |

| 2 |      |        | BLE PARALLEL PROGRAMMING MODEL FOR HETEROUS COMPUTING |      |

|   | 2.1  | Introd | duction                                               | . 14 |

|   | 2.2  | Cluste | er-M Portable Parallel Programming Tool               | . 17 |

|   |      | 2.2.1  | Cluster-M                                             | . 17 |

|   |      | 2.2.2  | Basic Concepts                                        | . 18 |

|   | 2.3  | A Por  | table Parallel Programming Model                      | . 20 |

|   |      | 2.3.1  | Machine-Independent Program Parameters                | . 22 |

|   |      | 2.3.2  | Program-Independent Machine Parameters                | . 23 |

|   |      | 2.3.3  | Evaluation Function                                   | . 23 |

|   | 2.4  | Non-U  | Jniform Clustering                                    | . 24 |

|   |      | 2.4.1  | Clustering Directed Task Graphs                       | . 24 |

|   |      | 2.4.2  | Clustering Undirected System Graphs                   | . 29 |

| $\mathbf{C}$ | hapt | er     | 1                                          | Page |

|--------------|------|--------|--------------------------------------------|------|

|              | 2.5  | Cluste | er-M Mapping Algorithm                     | 32   |

|              |      | 2.5.1  | Preliminaries                              | 34   |

|              |      | 2.5.2  | The Algorithm                              | 35   |

|              |      | 2.5.3  | Mapping Examples                           | 37   |

|              | 2.6  | Comp   | arison Results                             | 44   |

|              |      | 2.6.1  | Scheduling                                 | 44   |

|              |      | 2.6.2  | Task Allocation                            | 55   |

|              | 2.7  | Concl  | usion                                      | 61   |

| 3            | MA   | PPING  | AND SCHEDULING FOR HETEROGENEOUS COMPUTING | G 62 |

|              | 3.1  | Introd | luction                                    | 62   |

|              | 3.2  | A Sur  | vey of Heterogeneous Mappings              | 64   |

|              |      | 3.2.1  | Nondeterministic Algorithms                | 65   |

|              |      | 3.2.2  | Graph-Based Algorithms                     | 68   |

|              |      | 3.2.3  | Semi-Dynamic Algorithms                    | 72   |

|              | 3.3  | An Au  | gmented Cluster-M Mapping                  | 73   |

|              |      | 3.3.1  | Task Clustering                            | 74   |

|              |      | 3.3.2  | System Clustering                          | 76   |

|              |      | 3.3.3  | Augmented Cluster-M Mapping                | 78   |

|              |      | 3.3.4  | Comparison Study                           | 82   |

|              | 3.4  | Conclu | usion                                      | 84   |

| 4            | HAF  | RDWAF  | RE ESTIMATION OF HETEROGENEOUS COMPUTING   | 86   |

|              | 4.1  | Task ( | Compatibility and Task Conflict Graphs     | 87   |

|              | 4.2  | The G  | reedy Algorithm                            | 90   |

|              | 4.3  | Specia | l Task Conflict and Compatibility Graphs   | 91   |

|              |      | 4.3.1  | Interval Graphs                            | 92   |

|              |      | 4.3.2  | Chordal Graphs                             | 93   |

|              |      | 433    | Comparability Graphs                       | 93   |

| C  | hapt | er     |                                            | Page  |

|----|------|--------|--------------------------------------------|-------|

|    | 4.4  | Estim  | nating Using Clustering Technique          | . 95  |

|    | 4.5  | Comp   | parison Results                            | . 96  |

|    | 4.6  | Concl  | uding Remarks                              | . 102 |

| 5  | SOF  | TWAF   | RE REQUIREMENTS OF HETEROGENEOUS COMPUTING | 104   |

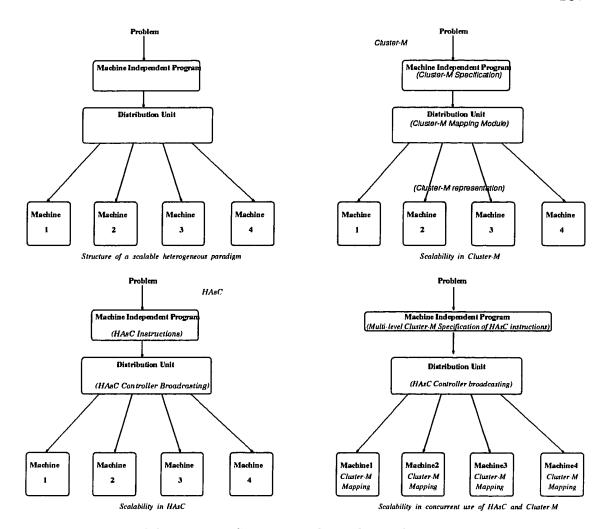

|    | 5.1  | Scalal | bility                                     | . 105 |

|    |      | 5.1.1  | Homogeneous Scalability                    | . 105 |

|    |      | 5.1.2  | Heterogeneous Scalability                  | . 107 |

|    | 5.2  | Cluste | er-M Constructs                            | . 110 |

|    |      | 5.2.1  | Implementation of the Cluster-M Constructs | . 111 |

|    |      | 5.2.2  | Cluster-M Problem Specification Macros     | . 117 |

|    | 5.3  | Heter  | ogeneous Associative Computing(HAsC)       | . 122 |

|    |      | 5.3.1  | Instruction Execution                      | . 125 |

|    |      | 5.3.2  | HAsC Administration                        | . 126 |

|    |      | 5.3.3  | HAsC Instruction Set                       | . 127 |

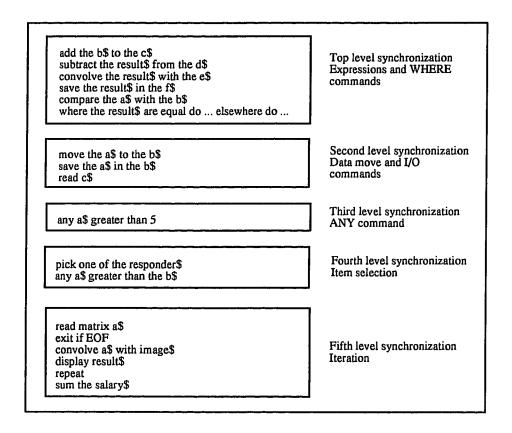

|    |      | 5.3.4  | Associative Instruction Levels             | . 128 |

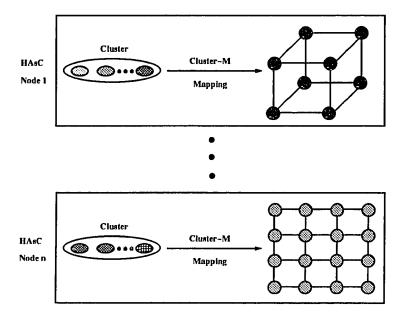

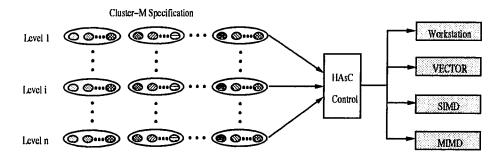

|    | 5.4  | Cluste | er-M and HAsC                              | . 131 |

|    |      | 5.4.1  | Concurrent use of Cluster-M and HAsC       | . 132 |

|    |      | 5.4.2  | Scalability of Cluster-M and HAsC          | . 132 |

| 6  | CON  | CLUD   | OING REMARKS                               | . 135 |

| RI | CEER | ENCE   | S                                          | 138   |

·---

## LIST OF TABLES

| Tab! | le P                                                                             | age |

|------|----------------------------------------------------------------------------------|-----|

| 1.1  | Notations used in HOST formulation                                               | 9   |

| 2.1  | Gaussian elimination mapping results using two processors with speed 2 and 1.6   | 43  |

| 2.2  | Gaussian elimination mapping results using two processors with speed 1 and 1     | 43  |

| 2.3  | Gaussian elimination mapping results using two processors with speed 0.8 and 0.7 | 43  |

| 2.4  | Comparison of Cluster-M and MH on system (1)                                     | 46  |

| 2.5  | Comparison of Cluster-M and MH on system (2)                                     | 47  |

| 2.6  | Comparison of Cluster-M and MH on system (3)                                     | 47  |

| 2.7  | Comparison of Cluster-M and MH on system (4)                                     | 48  |

| 2.8  | Comparison of Cluster-M, MFMC, and MH on system (2)                              | 48  |

| 2.9  | Comparison of Cluster-M, MFMC, and MH on system (3)                              | 49  |

| 2.10 | Comparison of Cluster-M, MFMC, and MH on system (4)                              | 49  |

| 2.11 | Mapping of Bokhari's algorithm and Cluster-M                                     | 60  |

| 2.12 | Comparisons of mappings of Bokhari's algorithm and Cluster-M                     | 61  |

| 4.1  | Comparison of different resource estimating techniques                           | 102 |

## LIST OF FIGURES

| Figu | ıre P                                                                                              | age |

|------|----------------------------------------------------------------------------------------------------|-----|

| 1.1  | A heterogeneous network-based parallel computing system                                            | 3   |

| 1.2  | Intelligent layer services                                                                         | 6   |

| 1.3  | Input format of HOST                                                                               | 7   |

| 2.1  | Cluster-M mapping process                                                                          | 18  |

| 2.2  | Horizontal and vertical partitioning of a task graph                                               | 20  |

| 2.3  | Clustering Nonuniform Directed Graphs (CNDG) algorithm                                             | 26  |

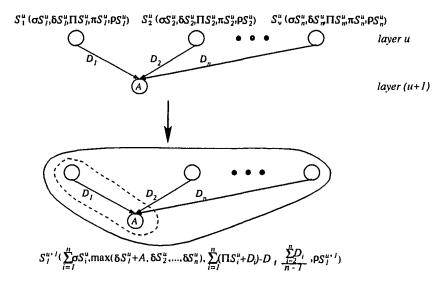

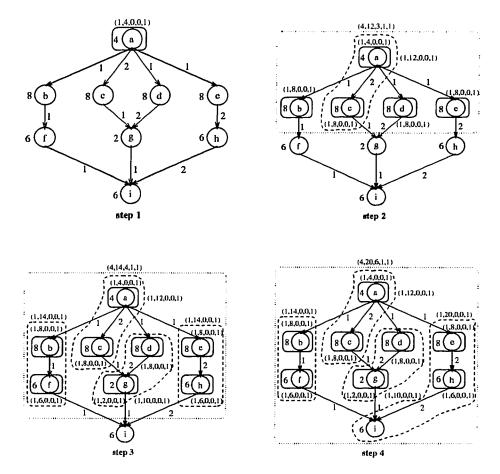

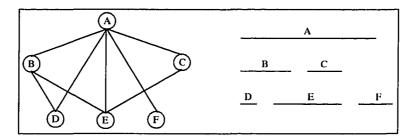

| 2.4  | Clustering on a join-node: a general case                                                          | 28  |

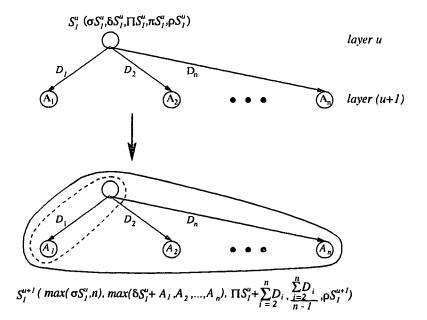

| 2.5  | Clustering on a fork-node: a general case                                                          | 29  |

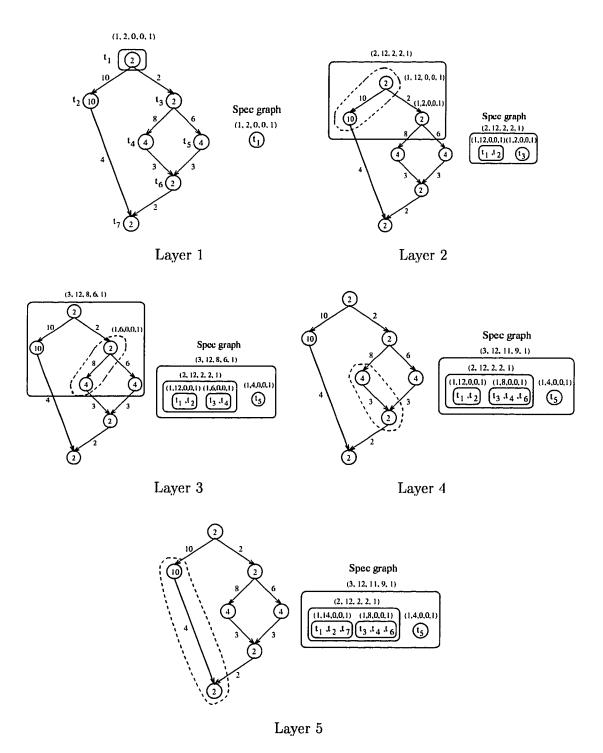

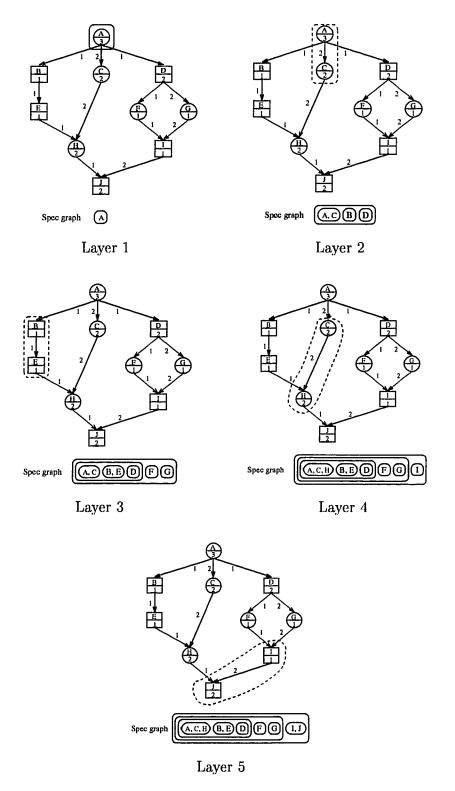

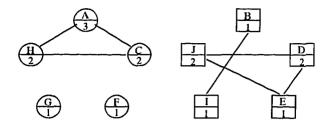

| 2.6  | A task graph and steps for obtaining the Spec graph                                                | 30  |

| 2.7  | Clustering Nonuniform Undirected Graphs (CNUG) algorithm                                           | 33  |

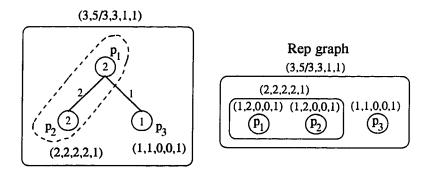

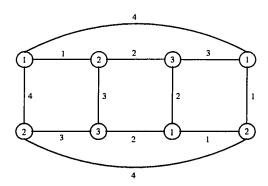

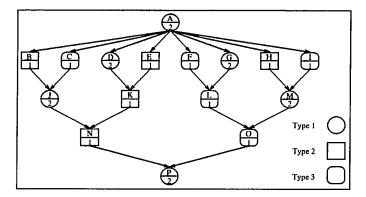

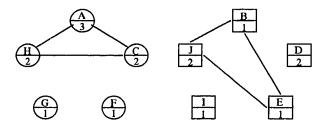

| 2.8  | A nonuniform system graph and its Rep graph                                                        | 34  |

| 2.9  | Mapping algorithm.                                                                                 | 38  |

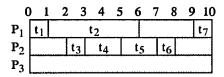

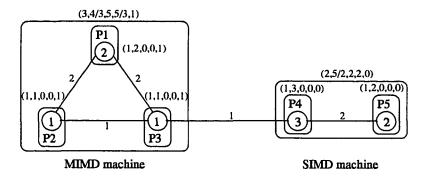

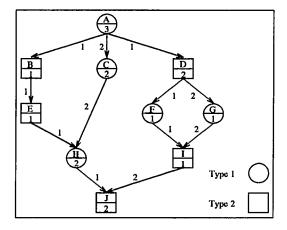

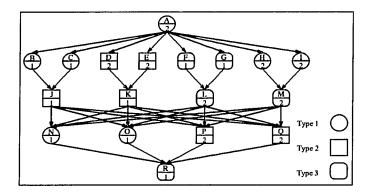

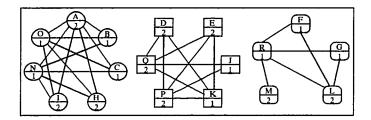

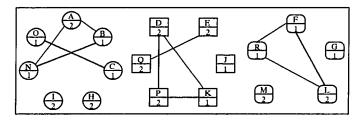

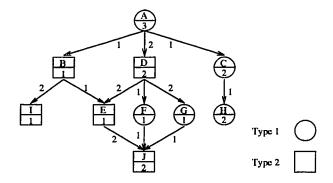

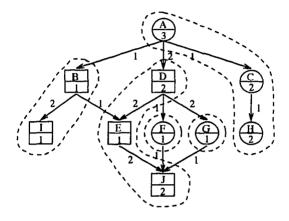

| 2.10 | A mapping example                                                                                  | 39  |

| 2.11 | Gantt chart of the obtained schedule                                                               | 39  |

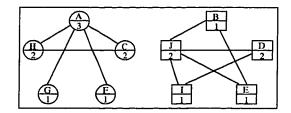

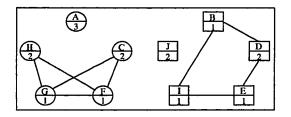

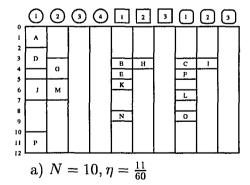

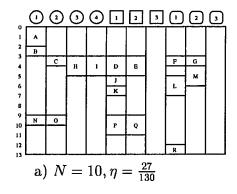

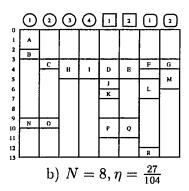

| 2.12 | Mappings on different system graphs                                                                | 40  |

| 2.13 | The Fortran code of the Gaussian elimination on a $N \times N$ matrix                              | 41  |

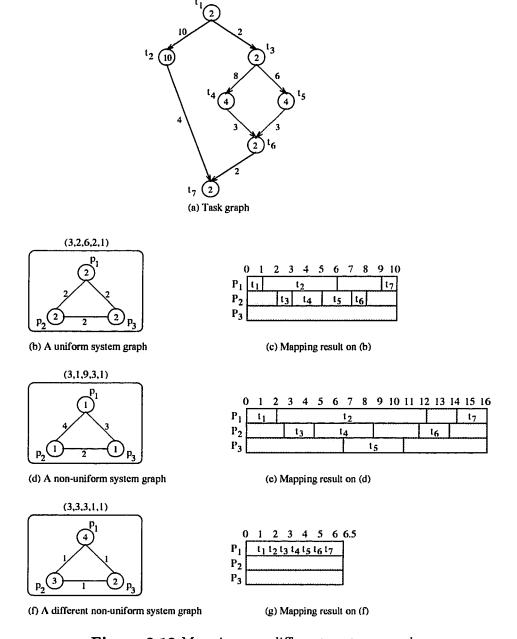

| 2.14 | (a) The task graph and (b) the mapping result of the Gaussian elimination on a $5 \times 5$ matrix | 42  |

| 2.15 | More Gaussian elimination mapping results                                                          | 43  |

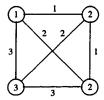

| 2.16 | System (2): A completedly connected system                                                         | 45  |

| 2.17 | System (3): A hypercube system                                                                     | 45  |

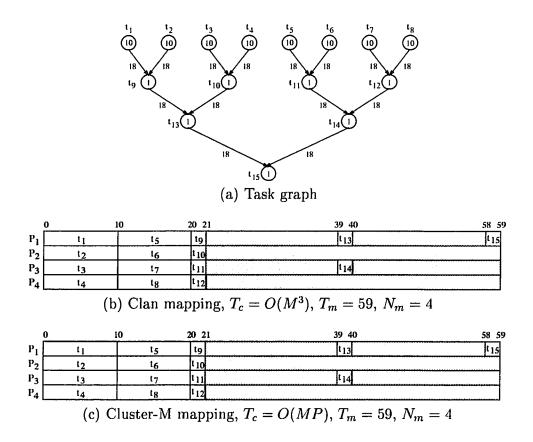

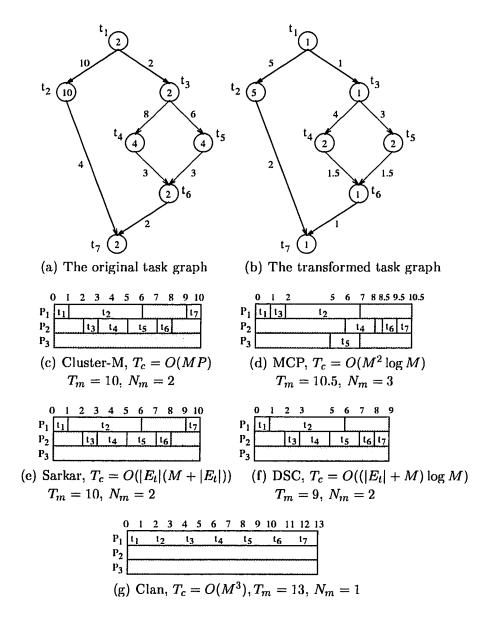

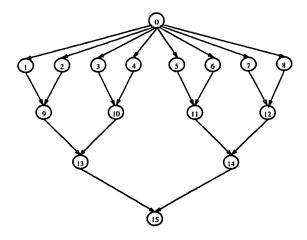

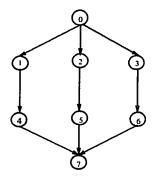

| 2.18 | Comparison example with Clan                                                                       | 51  |

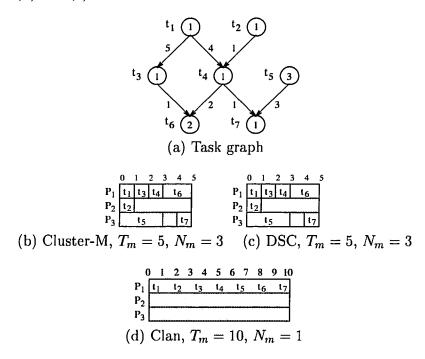

| 2.19 | Comparison example with MCP, Sarkar, DSC and Clan                                                  | 52  |

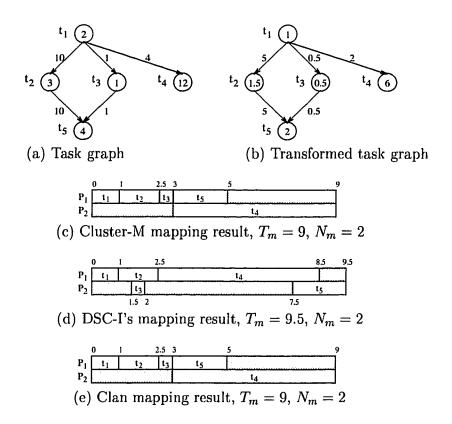

| 2.20 | Comparison example 2 with DSC and Clan                                                             | 54  |

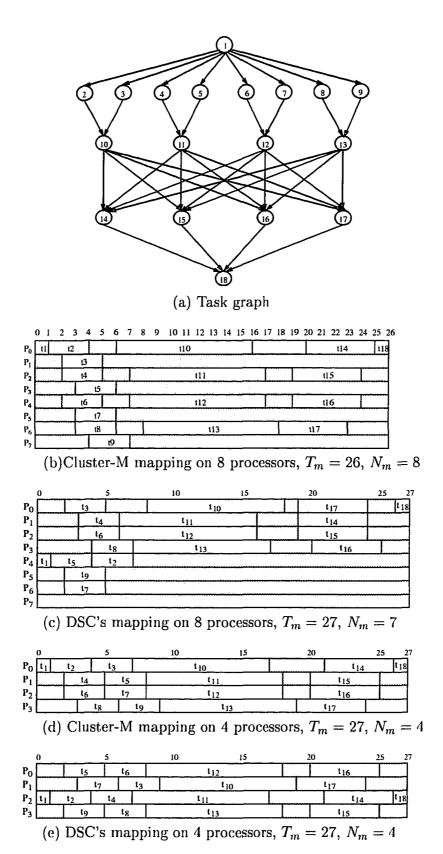

| 2.21 | Comparison example 3 with DSC and Clan                                                             | 55  |

| Figu | ıre                                                                        | Page |

|------|----------------------------------------------------------------------------|------|

| 2.22 | Comparison example 4 with DSC                                              | . 56 |

| 2.23 | Comparison example 1 with Chaudhary and Aggarwal: task graph               | . 57 |

| 2.24 | Comparison example 1 with Chaudhary and Aggarwal: mapping results          | . 57 |

| 2.25 | Comparison example 2 with Chaudhary and Aggarwal: task graph               | . 58 |

| 2.26 | Comparison example 2 with Chaudhary and Aggarwal: mapping results          | . 58 |

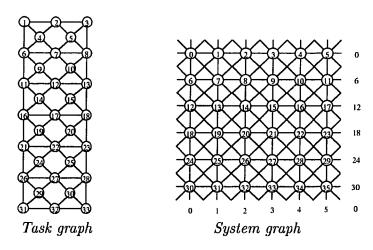

| 2.27 | Comparison example with Bokhari: task and system graph                     | 59   |

| 3.1  | The Augmented Task Clustering (ATC) algorithm                              | 74   |

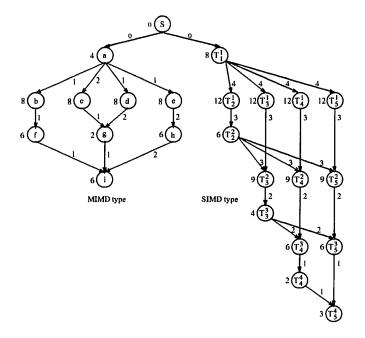

| 3.2  | A heterogeneous subtask consists of MIMD and SIMD code segments            | 76   |

| 3.3  | Clustering the MIMD code segment                                           | 77   |

| 3.4  | The Augmented System Clustering (ASC) algorithm                            | 77   |

| 3.5  | The system graph and its clustering of a heterogeneous suite               | 78   |

| 3.6  | Augmented Cluster-M mapping algorithm                                      | 81   |

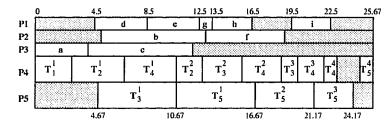

| 3.7  | The Gantt chart of obtained schedule                                       | 82   |

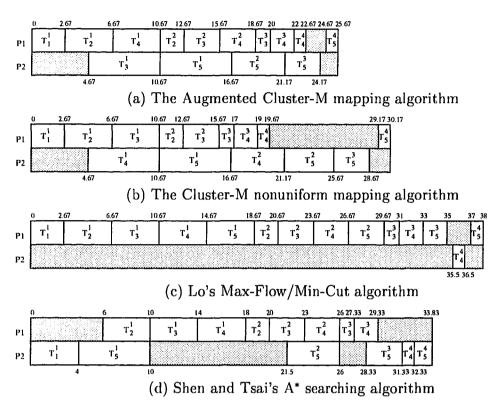

| 3.8  | The mapping results by using different algorithms                          | 83   |

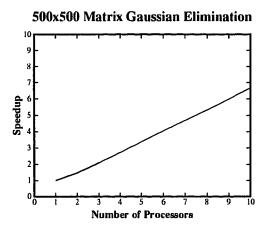

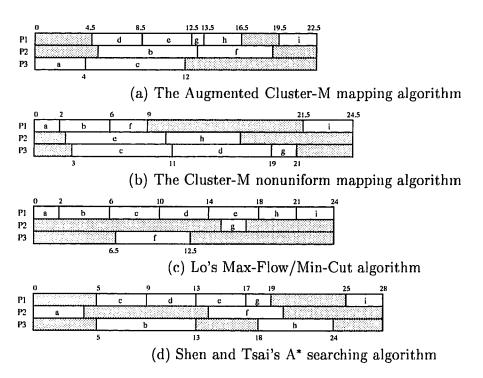

| 3.9  | The mapping results of Gaussian elimination by using different algorithms. | 84   |

| 4.1  | A task flow graph $G$                                                      | 88   |

| 4.2  | The task compatibility graph of $G$                                        | 89   |

| 4.3  | The task conflict graph of $G$                                             | 89   |

| 4.4  | Greedy-Clique-Cover-Algorithm                                              | 91   |

| 4.5  | An interval graph and its interval representation [62]                     | 92   |

| 4.6  | A chordal graph and its subtree representation [62]                        | 93   |

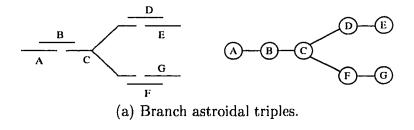

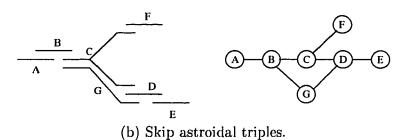

| 4.7  | Two kinds of astroidal triples [62]                                        | 95   |

| 4.8  | Clustering algorithm.                                                      | 97   |

| 4.9  | A task graph and steps for obtaining the Spec graph                        | 98   |

| 4.10 | Task flow graph of Example 1                                               | 99   |

| Figu | ıre                                                                                                                                                              | age |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

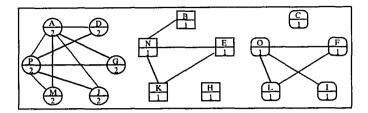

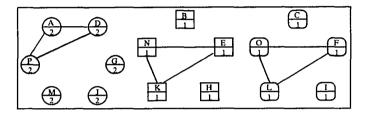

| 4.11 | Task compatibility graph of Example 1                                                                                                                            | 100 |

| 4.12 | Identified cliques of Figure 4.11                                                                                                                                | 100 |

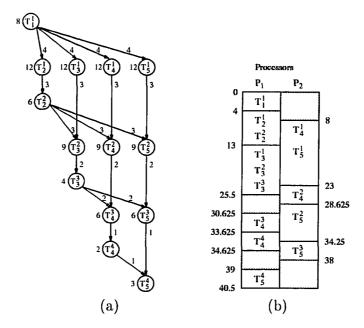

| 4.13 | Gantt charts of Example 1, using a) estimated number of processors obtained by the task compatibility graph approach and b) optimal minimum number of processors | 100 |

| 4.14 | Task flow graph of Example 2                                                                                                                                     | 101 |

| 4.15 | Task compatibility graph of Example 2                                                                                                                            | 101 |

| 4.16 | Identified cliques of Figure 10                                                                                                                                  | 101 |

| 4.17 | Gantt charts of Example 2, using a) estimated number of processors obtained by the task compatibility graph approach and b) optimal minimum number of processors | 101 |

| 4.18 | The task flow graph used for Table 4.1                                                                                                                           | 102 |

| 4.19 | The estimated result obtaining from method 1                                                                                                                     | 102 |

| 4.20 | The estimated result obtaining from method 2 and method 3                                                                                                        | 103 |

| 4.21 | The estimated result obtaining from method 4                                                                                                                     | 103 |

| 5.1  | Hierarchical breakdown of a task                                                                                                                                 | 108 |

| 5.2  | PCN System Structure                                                                                                                                             | 112 |

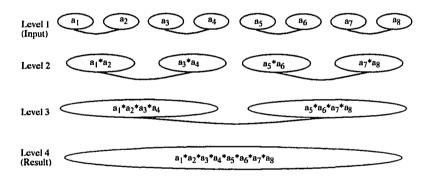

| 5.3  | Cluster-M Specification of associative binary macro                                                                                                              | 119 |

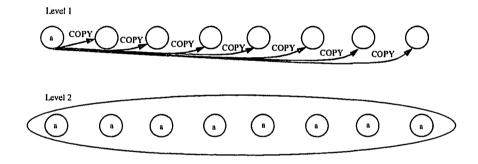

| 5.4  | Cluster-M Specification of broadcast macro                                                                                                                       | 122 |

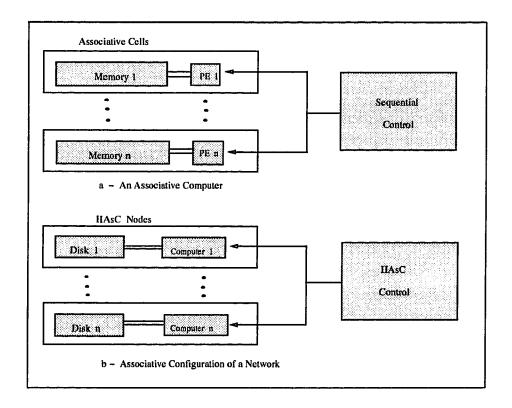

| 5.5  | Associative Configuration of a Network                                                                                                                           | 123 |

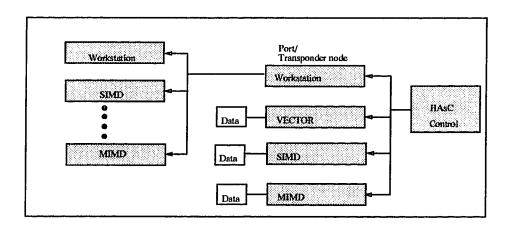

| 5.6  | A Layered Heterogeneous Network                                                                                                                                  | 124 |

| 5.7  | Instruction Synchronization                                                                                                                                      | 130 |

| 5.8  | Cluster-M aided HAsC computation within HAsC nodes                                                                                                               | 133 |

| 5.9  | Switching between Cluster-M and HAsC                                                                                                                             | 133 |

| 5.10 | Scalability of HAsC and Cluster-M                                                                                                                                | 134 |

#### CHAPTER 1

#### INTRODUCTION TO HETEROGENEOUS COMPUTING

In this chapter, we introduce heterogeneous computing in Section 1.1 and discuss the three layers of heterogeneous computing in Sections 1.2 to 1.4. The organization of this thesis is then presented in Section 1.5.

#### 1.1 Introduction

Today's supercomputing applications are characterized by a high level of diversity in terms of the type of embedded parallelism and by an ever-increasing demand for computational performance. Conventional parallel supercomputing systems utilize a number of homogeneous processors to cooperate on solving parallel tasks. These systems are usually classified according to the multiplicity of data and instruction streams [31].

Such homogeneous systems provide efficient solutions to tasks with embedded parallelism matching that offered by the system (i.e. SIMD, MIMD, vector). If more than one type of parallelism is present in a task, the system performance is greatly degraded. If greater computational power is needed, the whole system needs to be replaced by a more powerful homogeneous system, a costly solution.

Heterogeneous computing is a novel approach that overcomes several short-comings of conventional homogeneous parallel systems. Heterogeneous computing (HC) is defined as a special form of parallel and distributed computing that performs computations using a single autonomous computer operating in both SIMD and MIMD modes, or using a number of connected autonomous computers. This approach aims at providing high performance by executing portions of code on machines offering similar types of parallelism.

The HC environment is comprised of several hardware and software components that manage the suite of heterogeneous machines in the system, thus enabling applications to run efficiently. The hardware and software requirements for HC can be classified into three layers: network layer, communication layer, and intelligent layer. In this thesis, we concentrate on issues related to the intelligent layer. We next describe each of these layers.

#### 1.2 Network Layer

The network layer in HC includes the physical aspects of interconnecting the autonomous high performance machines in the system. This includes low level network protocols and machine interfaces. Current Local Area Networks (LANs) can be used to connect existing machines but this approach is not suitable for HC. In order to realize a HC environment, higher bandwidth and lower latency networks are essential. The bandwidth of commercially-available LANs is limited to about 10 Mbits/sec. However, in HC, assuming machines operating at 25 MHz clock with 40 MIPS instruction rate and 16 bits word length, a bandwidth in the order of 1 Gbits/sec is required to match computation and communication.

Recent advances in network technology have made it feasible to build gigabit LANs. Links in these networks are capable of operating on the order of 1 Gbits/sec or higher rates. Thus having at least 100 more bandwidth than today's 10 Mbits/sec Ethernets. Gigabit LAN standards are emerging. The High Performance Parallel Interface (HIPPI), whose physical layer has been approved as an ANSI standard, will likely become the backbone for interconnecting machines in HC. HIPPI-based LANS support data rates of 800 Mbits/sec and 1.6 Gbit/sec. Such networks have been used to interconnect CRAY-2 and CM-2 at the Minnesota Supercomputer Center [70]. A similar project using A CRAY Y-MP and CM-2 was undertaken at the Pittsburgh Supercomputing Center [47].

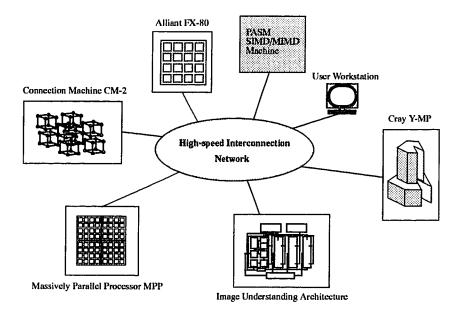

Figure 1.1 A heterogeneous network-based parallel computing system.

Even with high bandwidth networks, there are three main sources of inefficiency in current network implementations. First, existing application interfaces incur excessive overhead due to context switching and data copying between the user process and the machine's operating system. Secondly, each machine must incur overhead of executing high-level protocols that ensure reliable communication between tasks. Also, the network interface burdens the machine with interrupt handling and header processing for each packet.

Nectar [5] is an example of a network backplane for heterogeneous multicomputers. It consists of a high-speed fiber-optic network, large crossbar switches and powerful network interface processors. Protocol processing is off-loaded to these interface processors.

In HC, modules from various vendors share physical interconnections. Since different manufacturers usually use different communication protocols, the network management problem becomes more complex [52]. The following three general approaches in dealing with network heterogeneity are given in [72]:

- 1. To treat the heterogeneous network as a partitioned network, each partition employs a uniform set of protocols,

- 2. to have only a single "visible" network management console, and

- 3. to integrate the heterogeneous management functions at a single management console.

#### 1.3 Communication Layer

The HC environment achieves efficient execution of parallel tasks by decomposing the task into several modules which are assigned to machines in the system with a similar mode of embedded parallelism. The task modules run on assigned machines as local processes. These processes need to exchange intermediate results and process synchronization information, either from processes residing in the same machine or from processes residing on other machines using the network. Since each machine on the system may utilize different process communication and synchronization primitives, a uniform system-wide communication mechanism operating above native operating systems is needed to facilitate this exchange of information. Due to the networked nature of HC and the lack of shared memory, such a communication mechanism must support message passing.

An example of a communication tool suitable for HC is the parallel virtual machine (PVM) [66]. The PVM system emulates a virtual concurrent computing machine on a suite of networked machines by executing system-level processes on each machine. A process that runs on a local machine can access the virtual machine via library routines embedded in imperative procedural languages, such as C. Communication support is provided for process management via stream-oriented message-passing, synchronization based on barriers or variants of rendezvous and/or auxiliary tasks. These library routines interact with the PVM system process on each machine,

which then provides the requested actions in cooperation with PVM system processes running on other machines in the system. Other examples of networking communication tools are Portable Programs for Parallel Processors (P4) and Message Passing Interface (MPI). MPI includes a number of utilities for supporting message passing while P4 can handle both message passing and shared memory. MPI is a message passing interface for MIMD distributed memory concurrent computers. MPI includes point-to-point and collective communication routines, as well as support for process groups, communication contexts, and application topologies.

#### 1.4 Intelligent Layer

The intelligent layer of the HC environment provides system-wide tools and techniques necessary to manage the suite of heterogeneous machines and to insure proper and efficient execution of tasks. Such tools operate over the native operating systems of the individual machines and use the process communication primitives provided by the communication layer. The services provided by this layer are the most challenging ones in HC and include programming environments, language support, application task decomposition, mapping and scheduling, and load balancing, as illustrated in Figure 1.4. We next briefly describe two functions which are essential for designing and supporting these various services. These functions are used in the Heterogeneous Optimal Selection Theory (HOST) presented in Section 1.4.2.

#### 1.4.1 Code Profiling and Analytical Benchmarking

Traditional program profiling involves testing a program assumed to be comprised of several modules, by running it on some test data. The profiler monitors the execution of the program and gathers statistics including the running time of each program module. This information is then utilized to modify different modules

Figure 1.2 Intelligent layer services.

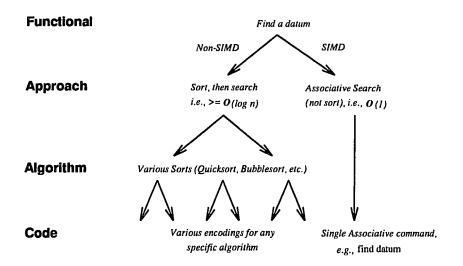

improving the overall execution time. In HC, profiling is not done only to estimate the execution time of code, but the type of the code according to the execution mode is also considered. This is achieved by *code-type profiling*. The code-type profiling introduced in [35] is a code-specific function to determine the code-type (e.g. SIMD, MIMD, vector, scalar, etc.).

Analytical benchmarking provides a mean to measure how well the available machines perform on a given code-type [35]. While code-type profiling identifies the type of code, analytical benchmarking ranks machines in terms of efficiency in executing a given code. Thus, analytical benchmarking techniques determine the relative effectiveness of a given parallel machine on various computation types.

#### 1.4.2 Heterogeneous Optimal Selection Theory

In Freund's Optimal Selection Theory (OST), it can be assumed that the number of machines available is unlimited and that an application task is comprised of several uniform and non-overlapping code segments. Code segments are considered to be

Figure 1.3 Input format of HOST.

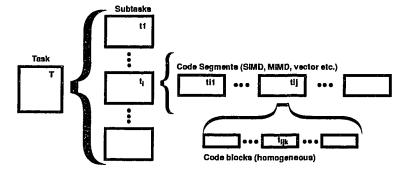

executed in a series. Each code segment has homogeneous parallelism embedded in its computations. A code segment is decomposed into code blocks. All code blocks within a code segment have the same type of parallelism and can be executed concurrently. This type is determined by the process of task profiling. The goal of OST is to assign the code blocks, within each code segment, to the available matching machine types so that it may be optimally executed. Information about how fast a given machine type can execute a code type is assumed to be known as a result of analytical benchmarking. Augmented Optimal Selection Theory (AOST) [71] extended OST to incorporate the performance of code segments on non-optimal machine choices, assuming that the number of available machines for each type is limited. Based on this assumption, a code segment most suitable for one type of machine may have to be assigned to another type.

The Heterogeneous Optimal Selection Theory (HOST) [16] is an extension of AOST in two ways: it incorporates the effects of various, fine-grain, mapping techniques available on individual machines and it assumes heterogeneous embedded parallelism. The input format of HOST, as shown in Figure 1.3, allows concurrent execution of mutually independent code segments. An application task is decomposed into several subtasks which are then executed in series. Each subtask may contain a collection of code segments which can be executed in parallel. A code segment consists of a set of code blocks and a code block consists of a number of instructions.

All the code blocks within a code segment are of the same type and are to be executed concurrently or sequentially on the machines of the same type, depending on their interdependencies. A machine type is identified according to the underlying architecture, such as SIMD, MIMD, vector or scalar. Each machine type may have more than one model, for example, the Ncube and Mesh are two models of an SIMD machine type. In HOST, heterogeneous code blocks of different code segments can be executed concurrently on different machine types, thus exploiting the heterogeneous parallel computations embedded in a given application. Narahari et al.[51] extended HOST to the *Generalized Optimal Selection Theory (GOST)*. GOST allows non-optimal selections of machines, as in AOST, and heterogeneous code blocks, as in HOST. It further incorporates data communication time, system reconfiguration time and data conversion time [51].

To express the formulation of HOST, some parameters must be defined. Table 1.1 contains a complete listing of this notation. For a more detailed description of these terms, see [16]. HOST is formulated as follows:

For any subtask, there exists a

$$\tau$$

with  $\min_{\tau} \chi[\tau]$  subject to  $\sum_{j=1}^{S} (\gamma[Y[j], j] \times c[Y[j]]) \leq C$

Based on HOST, an optimal machine selection leading to a minimum execution time exists. To find such an optimal solution, however, is not computationally feasible. Therefore, we present an overview of a set of sub-optimal solutions in the next section.

#### 1.5 Organization of the Dissertation

This thesis focuses on the design issues of the intelligent layer in HC. In this section, we briefly present an overview of these issues. They are presented in detail later in this thesis.

| S                 | the number of code segments of the given task                           |

|-------------------|-------------------------------------------------------------------------|

| $\overline{M}$    | the number of different machine types to be considered                  |

| $\eta[y]$         | the number of machine models of type y                                  |

| $\alpha[y]$       | the number of mappings available on machine type $y$                    |

| $oxed{eta[y,l]}$  | the number of available machines of model $l$ of type $y$               |

| v[y,j]            | the maximum number of code blocks code segment $j$ can be               |

|                   | decomposed                                                              |

| $\gamma[y,j]$     | the number of machines of type y actually used to execute code          |

|                   | segment j                                                               |

| m[y,k]            | mapping technique used for a code block $k$ on machine type $y$         |

| $\theta[y,m]$     | the optimal speedup for a particular mapping $m$ on machine type $y$    |

| $\pi[y,j]$        | how well a code segment $j$ can be matched with machine type $y$        |

| $\Lambda[y,k]$    | utilization factor when running code block $k$ on a machine of type $y$ |

| p[j]              | the percentage of execution time of code segment $j$ within a given     |

|                   | subtask                                                                 |

| p[j,k]            | the percentage of execution time of block $k$ within code segment $j$   |

| $\mu[y,j]$        | mapping vector for code segment $j$ on machine type $y$                 |

| $\delta[y,j,\mu]$ | execution time of segment $j$ with mapping $\mu$ on machine type $y$    |

| $\lambda[y,j]$    | minimum execution time of segment $j$ among all possible mappings       |

|                   | on type $y$                                                             |

| $\tau$            | machine type selection vector                                           |

| $\chi[	au]$       | execution time of the given subtask with machine type selection $	au$   |

| Y[j]              | the type of machine selected to execute code segment j                  |

| c[Y[j]]           | the cost of machine selected to execute code segment j                  |

| C                 | the total cost constraint                                               |

|                   | <del></del>                                                             |

Table 1.1 Notations used in HOST formulation

#### 1.5.1 Portable Programming Model

A programming paradigm suitable for the intelligent layer must allow portable software to be shared and/or distributed among various computers in the heterogeneous suite. Furthermore, it must support architecturally independent programming which does not include any architecturally specific details. Since homogeneous programming tools are not suitable to heterogeneous computing, we need to develop a new tool based on a heterogeneous programming model. We present a heterogeneous parallel programming model, called Cluster-M, in Chapter 2. This model is proposed to bridge between software and hardware for heterogeneous computing.

It acts as an intermediate medium based on which portable parallel programs are specified and can be mapped onto dynamically reconfigured heterogeneous organizations. The implementation of this model as a portable programming tool is also presented. Using Cluster-M, a single program can be ported among various heterogeneous architectures or suite of computers.

#### 1.5.2 Partitioning, Mapping and Scheduling

In HC, similar to homogeneous systems, the problems of partitioning a parallel task into several modules, mapping resulting modules into various machines and scheduling the execution of each module are pertinent. In the past, the partitioning and mapping problems for homogeneous parallel environments have been investigated extensively [9, 10, 18, 30, 43, 44, 61, 63, 64]. However, HC poses new constraints. In the following, we define partitioning and mapping as two different problems and also differentiate between the contexts of these terms in homogeneous and heterogeneous environments.

In a homogeneous environment, the partitioning problem addressed in [12, 36, 39] can be divided into two sub-problems. *Parallelism detection* determines the parallelism in a program. *Clustering* combines several operations into tasks and thus partitions the application into several tasks. Each cluster is then assigned to a processor. Both of these sub-problems can be performed by the user, the compiler or by the machine at run time.

The mapping/allocation of program modules to processors has been addressed by many researchers in the past [9, 18, 30, 43, 44, 61]. Informally, in homogeneous environments the mapping problem can be defined by assigning program modules to processors. Thus, the number of pairs of communicating modules that fall on pairs of directly connected processors is maximized [9]. In HC, machines are globally connected through a high-bandwidth network, and therefore the assignment of

communicating modules to directly-connected machines is not an issue. However, other objective functions for mapping, such as matching the code-type to the machine-type, add additional constraints. If such mapping has to be performed at run time, for load balancing purposes or due to failure of a machine, the mapping becomes more complicated.

In homogeneous environments, the scheduling process assigns each task to a processor in order to achieve better processor utilization and high throughput. Three levels of scheduling are generally employed. High-level scheduling selects a subset of all submitted jobs competing for the available resources. Intermediate-level scheduling responds to short-term fluctuations in the system load by temporarily suspending and activating processes to achieve smooth system operation. Low-level scheduling determines the next ready process to be assigned to a processor for a certain duration.

In HC, while all of the above three levels of scheduling may reside in each machine, a fourth level of scheduling is needed. This level deals with scheduling at the system level. The scheduler maintains a balanced system-wide workload by monitoring the progress of all the tasks in the system. The scheduler needs to know the different task-types and available machine-types (i.e., SIMD, MIMD, Mixed-mode, etc.) in the system, since tasks may be reassigned due to changes in the system configuration or due to overload problems. Communication bottlenecks and queueing delays incurred due to the heterogeneity of hardware add additional constraints on the scheduler. The scheduler also needs to use information from code-type profiling and analytical benchmarking.

In Chapter 3, we extend the algorithms of Chapter 2 to incorporate the "type heterogeneity" (i.e. SIMD and MIMD) of tasks and systems in HC. The augmented mapping algorithm presented maps tasks to processors of similar computation type and proceeds with an enhanced fine-grain mapping technique. Since the expected

number of clusters at every level of the fine-grain mapping is constant, we propose to use an optimal matching strategy to enhance the algorithm. Therefore, we formulate and solve each step of the fine-grain cluster mapping by using an Integer Linear Programming (ILP) model.

#### 1.5.3 Hardware Estimation

Once the information provided by code-type profiling is available, it is desirable to know how many processors are needed for each of the code types. In Chapter 4, we propose two methods for estimating the minimum number of processors required for each of these code types in HC. The first method involves making use of task compatibility graphs. We show that a task compatibility graph can be generated by analyzing certain compatible relations between task module pairs of a given task flow graph. We define the resource (processor) minimization problem therefore to be equivalent to finding the minimal number of cliques that cover the task compatibility graph, or to finding the minimal number of colors that color the vertices of its complement graph, called task conflict graph. We solve this problem using a greedy approach in  $O(|V| \log |V| + |E|)$  time, where |V| and |E| are the number of vertices and edges of the task compatibility graph. We further show that for special types of task compatibility graphs, the optimal solution can be obtained in polynomial time. The second method studied in Chapter 4 uses the Cluster-M methodology for estimating the minimum number of processors. Examples are shown to compare the estimated results obtained using different techniques.

#### 1.5.4 Software Environments

In HC, machine-independent and portable parallel programming languages and tools are required. Also, a HC software package should be portable among and executable on various architectures. Certain tools are needed to act as intermediate media based on which machine-independent algorithms can be designed using a single

programming language. These are then mapped onto the desired architecture. One such programming model, Linda [13, 11] defines a logically shared data structuring memory mechanism called tuple space. However, Linda is difficult to implement on architectures not supporting a shared memory structure. In contrast to Linda, the programming tool Express supports a distributed-memory system organization. However, algorithms coded using Express are machine dependent, and therefore are not fully portable. Other candidate parallel programming environments for HC are: the Actors Programming model [1, 2, 3] and Tool for Large-Grained Concurrency (TLC). TLC, developed by BBN, employs implicitly parallel constructs to specify the dependencies among a set of coarse-grained remote computations. The Actors model, on the other hand, allows massively parallel execution of algorithms. At extra cost of implementing such a system, Actors is machine independent: it can be executed on shared memory computers and over distributed networks.

Cluster-M, presented in Chapter 2, is a model which provides an environment for porting various tasks onto the machines in a heterogeneous suite, so that resource utilization is maximized and the overall execution time is minimized. In Chapter 5, we formally define the scalability of heterogeneous programming paradigms. Also, we present another portable and scalable programming paradigm, called Heterogeneous Associative Computing (HAsC)[54]. HAsC models a heterogeneous network as a coarse-grained associative computer and is designed to optimize the execution of problems where the size of the program is small compared to the amount of data processed. It uses broadcasting to avoid the mapping problem. Ease of programming and execution speed, not the utilization of idle resources are the primary goals of HAsC. We show that both Cluster-M and HAsC are scalable. We then illustrate how these two paradigms can be used together to provide an efficient medium for heterogeneous programming.

#### CHAPTER 2

# A PORTABLE PARALLEL PROGRAMMING MODEL FOR HETEROGENEOUS COMPUTING

We present a heterogeneous parallel programming model called Cluster-M. This model is proposed to bridge between software and hardware for heterogeneous computing. It acts as an intermediate medium based on which portable parallel programs are specified and then can be mapped onto dynamically reconfigured heterogeneous organizations. The implementation of this model as a portable programming tool is presented in this chapter. Using Cluster-M, a single software can be ported among various heterogeneous architectures or suite of computers.

#### 2.1 Introduction

A programming paradigm suitable for the intelligent layer should allow portable software to be shared and/or distributed among various computers in the heterogeneous suite. Furthermore, it should support architecturally independent programming that does not include any architecturally specific details. A number of homogeneous programming tools have been developed that take a high-level program as the input and map it onto the underlying systems. The question is whether or not these homogeneous programming tools can be directly used for heterogeneous computing. Examples of these tools include Linda, Prep-P, Oregami, Hypertool, PARSA, and PYRROS [13, 8, 45, 74, 75]. Linda [13] defines a logically shared memory mechanism called tuple space. Tuple space holds two kinds of tuples: process tuples, which are under active evaluation, and data tuples, which are passive. Ordinarily, building a Linda program involves dropping a process tuple into tuple space and then spawning other process tuples. This pool of process tuples, all executing simultaneously, exchange data by generating, reading, and consuming data tuples. Once a process tuple has finished executing, it turns into a data tuple that is indistinguishable from

other data tuples. Linda requires large volumes of data to be exchanged to and from the shared memory. For this reason, Linda has been mostly used for coarse-grain computations.

Prep-P, Oregami, Hypertool, and PYRROS, however, all include an architecturally independent mapping component that can map a fine-grain given parallel program onto either a special or an arbitrary system. However, the mapping components of Prep-P [8] and Oregami [45] are basically libraries of specialized mapping algorithms that only map regularly structured programs onto regularly structured systems. Their mappings for irregularly structured programs or systems that are not found in the libraries may be slow and ineffective. Hypertool [74] and PYRROS [75] generate fast and near-optimal mappings for arbitrary programs by using a clustering method. However, they can only be mapped onto fully connected systems. Therefore, they are not suitable for a heterogeneous network that may have arbitrary interconnections. This chapter will only focus on the tools that can efficiently map arbitrary program tasks onto arbitrary computer systems. Since homogeneous programming tools are not suitable to heterogeneous computing, we need to develop a new tool based on a heterogeneous programming model. An essential component of such a tool will be an efficient mapping algorithm, which maps an arbitrary task onto an arbitrary system.

A program task can be represented by a task graph, with each node representing a task module and each edge representing data communication between two modules. Each node is associated with a weight representing the time needed to execute the instructions contained in the node on a baseline computer, while the weight of an edge represents the communication amount. Similarly, a parallel computer system can be modeled as a weighted undirected system graph, whose weights represent processor speeds and transmission rates of communication links. If the task graphs and the system graphs are known before program execution, then mapping of the task

graphs onto the system graphs is called static mapping. Here, we consider only static mapping. In static mapping, the assignments of the nodes of the task graphs onto the system graphs are determined prior to the execution and are not changed until the end of the execution. Static mapping can be classified in two general ways. The first classification is based on the topology of task and/or system graphs [15]. Based on this, the mappings can be classified into four groups: (1) mapping specialized tasks onto specialized systems, (2) mapping specialized tasks onto arbitrary systems, (3) mapping arbitrary tasks onto specialized systems and (4) mapping arbitrary tasks onto arbitrary systems. The second classification can be based on the uniformity of the weights of the nodes and the edges of the task and/or the system graphs. Based on this, the mappings can be categorized into the following four groups: (1) mapping uniform tasks onto uniform systems [7, 9, 15, 24, 43], (2) mapping uniform tasks onto nonuniform systems, (3) mapping nonuniform tasks onto uniform systems [22, 48, 59, 74, 76] and (4) mapping nonuniform tasks onto nonuniform systems [44, 60].

Two of the earlier static mapping algorithms that can map arbitrary nonuniform task graphs onto arbitrary nonuniform system graphs are Lo's Max Flow/Min Cut algorithm [44], and El-Rewini and Lewis' mapping heuristic (MH) algorithm [22]. The time complexity of these two algorithms are  $O(M^4N\log M)$  and  $O(M^2N^3)$  respectively, where M is the number of task modules and N is the number of processors. In this chapter we present a mapping technique that is used in the mapping module of an implemented tool, which is based on a portable programming model for heterogeneous computing called Cluster-M. Using this paradigm, we can produce near-optimal mapping of arbitrary nonuniform architecture-independent task graphs onto arbitrary nonuniform system graphs in O(MP) time, where P = max(M, N). Similar to BSP and LogP, the Cluster-M model serves as an intermediate layer between software and hardware. Therefore, it supports portable

machine-independent programming. BSP and LogP support portable programming for a set of uniform (homogeneous) processing units, while the Cluster-M model allows the processing units to be nonuniform (heterogeneous).

The rest of this chapter is organized as follows. In Section 2 we present the Cluster-M heterogeneous model of computation. In Section 3, the components of the Cluster-M tool are presented. The efficiency of the Cluster-M mapping module is discussed in Section 4. Concluding remarks are in Section 5.

# 2.2 Cluster-M Portable Parallel Programming Tool

A tool implementing the Cluster-M model, presented in the last section, must support portable parallel algorithm design and programming. It must provide a mechanism so that both set of parameters can be extracted from any given problem and any underlying heterogeneous organization. Furthermore, this tool must provide an efficient mechanism for mapping these portable programs onto heterogeneous systems using these two sets of parameters. The Cluster-M tool, presented below, is an implementation of the model satisfying these conditions.

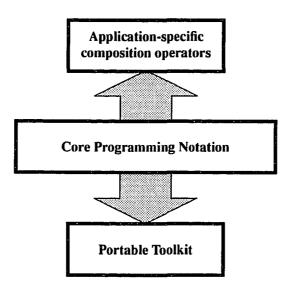

#### 2.2.1 Cluster-M

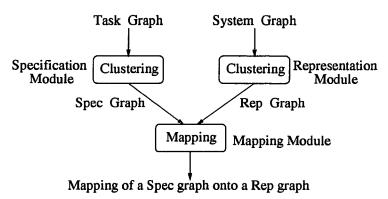

Cluster-M is a programming tool that facilitates the design and mapping of portable parallel programs [15]. Cluster-M has three main components: the specification module, the representation module and the mapping module. In the specification module, machine-independent algorithms are specified and coded using the program composition notation (PCN) [34] programming language [25]. Cluster-M specifications are represented in the form of a multilayer clustered task graph called a Spec graph. Each clustering layer in the Spec graph represents a set of concurrent computations, called Spec clusters. A Cluster-M representation represents a multilayer partitioning of a system graph called a Rep graph. At every partitioning layer

of the Rep graph, there are a number of clusters called Rep clusters. Each Rep cluster represents a set of processors with a certain degree of connectivity. Given a task (system) graph, a Spec (Rep) graph can be generated using one of the Cluster-M clustering algorithms. The clustering is done only once for a given task (system) graph, independent of any system (task) graphs. It is a machine-independent (application-independent) clustering, therefore it is not necessary to repeat it for different mappings. For this reason, the time complexities of the clustering algorithms are not included in the time complexity of the Cluster-M mapping algorithm. In the mapping module, a given Spec graph is mapped onto a given Rep graph. This process is shown in Figure 2.1. In an earlier publication [15], two Cluster-M clustering algorithms and a mapping algorithm were presented for uniform graphs. Next, the basic concepts used in Cluster-M clustering and mapping will be explained. In Section 3, we will show how uniform Cluster-M algorithms can be extended and applied to nonuniform task and system graphs.

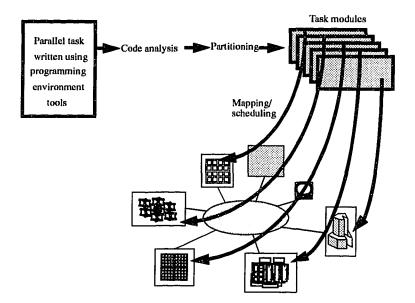

Figure 2.1 Cluster-M mapping process.

#### 2.2.2 Basic Concepts

There are a number of reasons and benefits in clustering task and system graphs in the Cluster-M fashion. Basically, Cluster-M clustering causes both task and system graphs be partitioned so that the complexity of the mapping problem is simplified

and good mapping results can be obtained. In clustering an undirected graph, completely connected nodes are grouped together forming a set of clusters [15, 25]. Clusters are then grouped together again if they are completely connected. This is continued until no more clustering is possible. When an undirected graph is a task graph, then doing this clustering essentially identifies and groups communicationintensive sets of task nodes into a number of clusters called Spec clusters. Similarly for a system graph, doing the clustering identifies well-connected sets of processors into a number of clusters called Rep clusters. In the mapping process, each of the communication intensive sets of task nodes (Spec clusters) is to be mapped onto a communication-efficient subsystem (Rep cluster) of suitable size. Note that the mapping of undirected task graphs onto undirected system graphs is referred to as the allocation problem. An earlier publication [15] showed that Cluster-M clustering and mapping algorithms can lead to good allocation results. It compared its results with Bokhari's  $O(N^3)$  algorithm and showed that its algorithm has a lower time complexity of O(MN), where M and N are the number of nodes in the task and system graphs, respectively.

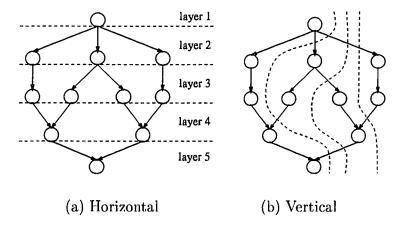

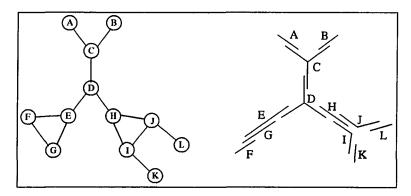

Clustering directed graphs (i.e., directed task graphs) produces two types of graph partitioning: horizontal and vertical. Horizontal partitioning is obtained because, as part of clustering, we divide a directed graph into a layered graph such that each layer consists of a number of computation nodes that can be executed in parallel and a number of communication edges incoming to these nodes. This is shown in Figure 2.2(a). The layers are to be executed one at a time. Therefore, the mapping is done one layer at a time. This significantly reduces the complexity of the mapping problem since the entire task graph need not be matched against the entire system graph.

Vertical graph partitioning is obtained because, as part of the clustering, the nodes from consecutive layers are merged or embedded. All the nodes in a layer are

Figure 2.2 Horizontal and vertical partitioning of a task graph.

merged to form a cluster if they have a common parent node in the layer above or a common child node in the layer below. Doing this traces the flow of data. This information will be used later as part of the mapping so that the tasks are placed onto the processors in a way that total communication overhead is minimized. For example, to avoid unnecessary communication overhead, the task nodes along a path may be embedded into one another so that they are assigned to the same processor. The effect of this type of partitioning is shown in Figure 2.2(b).

Both horizontal and vertical graph partitionings are accomplished by performing the clustering in a bottom-up fashion. The Cluster-M mapping will then be performed in a top-down fashion by mapping the Spec clusters one layer at a time onto the Rep clusters. The next two sections show how these clustering and mapping ideas work for nonuniformly weighted graphs. The nonuniform algorithms shown in this chapter are nontrivial extensions of the Cluster-M uniform algorithms presented in an earlier publication [15].

#### 2.3 A Portable Parallel Programming Model

A computational model is designed such that it can be an efficient bridge between software and hardware; high-level languages can be compiled efficiently on to the model; yet it can be efficiently implemented in hardware [69]. The von Neumann model is a computational model that successfully bridges the gap for sequential computations. For parallel computing, a number of models have been introduced. One of the earliest and most widely used parallel models is the parallel random access machine (PRAM) model [32]. This model is unrealistic because it assumes that all processors work synchronously and that interprocessor communication is free [19]. Several variations of the PRAM model have been proposed to identify restrictions that would make it more practical while preserving the unrealistic assumption that communication is free. Algorithms that are designed based on PRAM and its variations perform very poorly once mapped onto parallel machines with electrical interconnects. If the electrical interconnects are to be replaced with optical ones, however, the PRAM algorithms can be implemented efficiently [29, 26]. The optical model of computation (OMC) is a computational model for parallel architectures with unit-delay optical interconnects.

The bulk-synchronous parallel model (BSP) developed by Valiant [69] attempts to bridge theory and practice for all types of parallel computations. It assumes processors work synchronously, and it models latency and limited bandwidth. It requires few machine parameters as long as a certain programming methodology is followed. An improvement over the BSP model is the LogP model proposed by Culler et al. [19]. LogP allows algorithm designers to address key performance issues without specifying unnecessary details. It allows machine designers to give a concise performance summary of their machines, against which algorithms can be evaluated. Using LogP, portable parallel algorithms can be designed, if processors are all assumed to be identical (homogeneous).

Heterogeneous computing is defined as a special form of parallel and distributed computing that performs computations using a single autonomous computer operating in both SIMD and MIMD modes, or using a number of connected autonomous computers. Furthermore, the heterogeneous architectures may be changed at every step of computation as new resources become available or occupied. Because of the nonuniformity and the unpredictability in the availability of the processing units, the LogP model will not be suitable as a model for heterogeneous computing [58]. The following presents the portable programming model called Cluster-M, which can efficiently bridge the software and hardware in a heterogeneous environment. This model allows software portability without imposing any restrictions on the hardware. The Cluster-M model consists of two sets of parameters, one for representing a portable parallel program and the other for specifying the organization of the underlying heterogeneous architecture or suite. In addition, the Cluster-M model consists of an evaluation function for predicting the time performance of any two sets of parameters being considered.

# 2.3.1 Machine-Independent Program Parameters

A given parallel program consists of a sequence of steps such that in each step a number of computations can be done concurrently. Each step is called a layer. These concurrent computations for a given step (layer) can each be presented by a cluster called a Spec cluster. The mth Spec cluster at layer u is denoted by  $S_m^u$  and associated with the following parameters.

- $\sigma S_m^u$  The size of  $S_m^u$ , which is the maximum number of nodes in this cluster that can be computed in parallel.

- $\delta S_m^u$  The maximum sequential computation amounts (i.e., the maximum number of clock cycles required to execute all the instructions sequentially using a baseline computer) in  $S_m^u$ .

- $\Pi S_m^u$  The total amount of communication from layer 1 to layer u of  $S_m^u$ .

- $\pi S_m^u$  The average communication amount at the layer u in  $S_m^u$ .

$\rho S_m^u$  The computational type of  $S_m^u$ . Its value is set to 0 for a single instruction, multiple data (SIMD) type and 1 for a multiple instruction, multiple data (MIMD) type.

# 2.3.2 Program-Independent Machine Parameters

Any heterogeneous architecture can be similarly represented in a multilayered format such that each layer presents a set of processing units that are completely connected. Each processing unit is represented by a cluster called a Rep cluster. The nth Rep cluster at layer v is denoted by  $R_n^v$  and associated with the following parameters.

$\sigma R_n^v$  The number of processors contained in  $R_n^v$ .

$\delta R_n^v$  The average computation speed of the processors in  $R_n^v$ .

$\Pi R_n^v$  The total data transmission rate including the transmission rate over the links (communication bandwidth) and over the nodes (switching latency) from layer 1 to layer v in  $R_n^v$ .

$\pi R_n^v$  The average data transmission rate at layer v of  $R_n^v$ .

$\rho R_n^v$  The computational type of the Rep cluster. Its value is set to 0 for a SIMD type and 1 for an MIMD type.

#### 2.3.3 Evaluation Function

In heterogeneous computing, the structure of the underlying heterogeneous organization may be changed dynamically. Therefore, it is desirable to be able to compute an estimated total execution time for mapping a program onto the heterogeneous architecture at every step of the computation. We denote the estimated total execution time of mapping the Spec cluster  $S_i^u$  onto the Rep cluster  $R_j^v$  by  $\tau(S_i^u, R_j^v)$ , which includes computation time and communication time. The total computation amount of  $S_i^u$  is estimated to be  $\sigma S_i^u \times \delta S_i^u$ , and the total computation power of  $R_j^v$

can be calculated as  $\sigma R_j^v \times \delta R_j^v$ . Therefore, the computation time for executing  $S_i^u$  on  $R_j^v$  is estimated to be  $(\sigma S_i^u \times \delta S_i^u)/(\sigma R_j^v \times \delta R_j^v)$ . Similarly, the total communication requirement of  $S_i^u$  is  $\Pi S_i^u$  and the total communication capacity of  $R_j^v$  is  $\Pi R_j^v$ , hence the estimated communication time for mapping  $S_i^u$  on  $R_j^v$  will be  $\Pi S_i^u/\Pi R_j^v$ . A slow-down factor, d, is defined that indicates the factor of slow down due to mismatch of the computation type between  $S_i^u$  and  $R_j^v$ . This leads to an estimated execution time in (2.1). Note that the estimated execution time does not take into consideration the memory requirements of a given problem and the memory space available in the underlying organization. This is mainly due to the fact that the model does not contain any parameters for memory size requirements and availabilities.

$$\tau(S_i^u, R_j^v) = d \times \frac{\sigma S_i^u \times \delta S_i^u}{\sigma R_j^v \times \delta R_j^v} + \frac{\Pi S_i^u}{\Pi R_j^v}, \quad d = \begin{cases} \sigma S_i^u & \text{if } \rho S_i^u = 1 \text{ and } \rho R_j^v = 0\\ 1 & \text{otherwise} \end{cases}$$

(2.1)

The Cluster-M tool presented in the previous section is an implementation of this model. We will show that using the clustering algorithms presented in Section 2.4 as part of the tool, the above two set of parameters can be extracted from any given task or system graph.

# 2.4 Non-Uniform Clustering

In this section we first present a clustering algorithm to be used for directed task graphs independent of any system graphs and then present another one for undirected system graphs independent of any task graphs. Both algorithms are done only once for any given task or system graph and are not repeated as part of the mapping process.

## 2.4.1 Clustering Directed Task Graphs

A task can be represented by a directed graph  $G_t(V_t, E_t)$ , where  $V_t = \{t_1, ..., t_M\}$  is a set of task modules to be executed and  $E_t$  is a set of edges representing the partial

orders and communication directions between task modules. A directed edge  $(t_i, t_j)$  represents that a data communication exists from module  $t_i$  to  $t_j$  and that  $t_i$  must be completed before  $t_j$  can begin, where  $1 \leq i, j \leq M$ . Each edge  $(t_i, t_j)$  is associated with  $D_{ij}$ , the amount of data required to be transmitted from module  $t_i$  to module  $t_j$ , where  $D_{ij} \geq 1$ . Each task module  $t_i$  is associated with its amount of computation  $A_i$ , that is, the number of clock cycles required to execute all the instructions of  $t_i$  on a baseline machine. Note that  $A_i \geq 1$  and  $D_{ij} \geq 1$  if there exits an edge  $(t_i, t_j)$ , for  $1 \leq i, j \leq M$ . If a directed edge  $(t_i, t_j)$  exists,  $t_i$  is called a parent node (module) of  $t_j$  and  $t_j$  a child node (module) of  $t_i$ . If a node has more than one child, it is called a fork-node. If a node has more than one parent, it is called a join-node. A task graph is divided into a number of layers, so that all nodes in a layer can be executed concurrently.