# **Copyright Warning & Restrictions**

The copyright law of the United States (Title 17, United States Code) governs the making of photocopies or other reproductions of copyrighted material.

Under certain conditions specified in the law, libraries and archives are authorized to furnish a photocopy or other reproduction. One of these specified conditions is that the photocopy or reproduction is not to be "used for any purpose other than private study, scholarship, or research." If a, user makes a request for, or later uses, a photocopy or reproduction for purposes in excess of "fair use" that user may be liable for copyright infringement,

This institution reserves the right to refuse to accept a copying order if, in its judgment, fulfillment of the order would involve violation of copyright law.

Please Note: The author retains the copyright while the New Jersey Institute of Technology reserves the right to distribute this thesis or dissertation

Printing note: If you do not wish to print this page, then select "Pages from: first page # to: last page #" on the print dialog screen

The Van Houten library has removed some of the personal information and all signatures from the approval page and biographical sketches of theses and dissertations in order to protect the identity of NJIT graduates and faculty.

#### ABSTRACT

# DESIGN OF A LAPD INTERFACE USING THE T7130 MULTICHANNEL LAPD CONTROLLER AND THE T7115A SYNCHRONOUS PROTOCOL DATA FORMATTER

# by Hopeton Saint John Walker

As the ISDN telecommunications standard gains acceptance, there is an ever increasing need for intelligent interfaces to implement the L2 protocol known as LAPD. The T7130 MLC, the T7115A SPYDER-T and the MC68020 microprocessor were used to design a LAPD Interface that conforms to the LAPD protocol as specified by CCITT.

The LAPD Interface utilizes a Shared Memory Array which is attached to the Data Link Processors in a single bus configuration. The SMA Arbitration Control allows access to the SMA on a prioritized basis and was implemented as a state machine using PAL's. L2 drivers and L3 management software were written and used to test the operability of the interface via an emulator.

The LAPD Interface was able to terminate 32 HDLC channels configured for LAPD operation with an average throughput of 942.42 messages per second. The LAPD Interface was also able to operate efficiently in an environment in which random errors of the order of 1E-6 were injected.

# DESIGN OF A LAPD INTERFACE USING THE T7130 MULTICHANNEL LAPD CONTROLLER AND THE T7115A SYNCHRONOUS PROTOCOL DATA FORMATTER

by Hopeton Saint John Walker

> Robert W. Van Houten Library New Jersey Institute of Technology

A Thesis

Submitted to the Faculty of New Jersey Institute of Technology in Partial Fulfillment of the Requirements for the Degree of Master of Science in Electrical Engineering

Department of Electrical and Computer Engineering,

January 1995

# APPROVAL PAGE

# DESIGN OF A LAPD INTERFACE USING THE T7130 MULTICHANNEL LAPD CONTROLLER AND THE T7115A SYNCHRONOUS PROTOCOL DATA FORMATTER

# Hopeton Saint John Walker

Dr. Constantine N. Manikopoulos, Thesis Advisor Date Associate Professor of Electrical and Computer Engineering, NJIT

Dr. Sotirios Ziavras 'Date Assistant Professor of Electrical and Computer Engineering, NJIT

Dr. Anthony D. Robbi Date Associate Professor of Electrical and Computer Engineering, NJIT

# **BIOGRAPHICAL SKETCH**

Author: Hopeton Saint John Walker

Degree: Bachelor of Science in Electrical Engineering

Date: January 1995

# Undergraduate and Graduate Education:

- Master of Science in Electrical Engineering, New Jersey Institute of Technology, Newark, New Jersey, 1995

- Bachelor of Science in Electrical Engineering, New Jersey Institute of Technology, Newark, New Jersey, 1993

Major: Electrical Engineering

This thesis is dedicated to Herbert Edward Walker II.

#### ACKNOWLEDGMENT

The author wishes to thank Dr. Mannikopoulos for his sincere gratitude, guidance friendship and moral support. Throughout my latter years at NJIT, he has provided advice that has lead to my academic and professional growth.

Special thanks to my wife, Shelley Walters-Walker, for her constant and unwavering encouragement, faith, sympathy, good cheer and moral support during the trying periods marked by my determination to complete this thesis.

The author would also like to thank Sheridan Quarless, Juan Segura, William Wong, Jitendra Patel, Steve Christie, Carl Gauntlett, Florencio Martinez, Mariano Lalumia, Errol Drummond, Harold Shichman and Chu Le.

# TABLE OF CONTENTS

| Chapter                                              | Page |

|------------------------------------------------------|------|

| 1 LAPD INTERFACE HARDWARE SPECIFICATIONS             | 1    |

| 1.1 Data Link Processors - T7130 and T7115A          | 1    |

| 1.1.1 Function                                       | 1    |

| 1.1.2 Synchronous Protocol Data Formatter - SPYDER-T | 2    |

| 1.1.3 Multichannel LAPD Controller - T7130           |      |

| 1.1.4 T7130, T7115A and HOST Interface               | 5    |

| 1.1.5 Multichannel LAPD Controller Private I/O Port  | 6    |

| 1.1.6 Initialization of the Data Link Processor      | 6    |

| 1.2 HOST - MC68020                                   | 7    |

| 1.2.1 Function                                       | 7    |

| 1.2.2 HOST Initialization and Diagnostics            | 9    |

| 1.2.3 Level-2 Management of the LAPD Data Links      | 9    |

| 1.2.4 Level-3 Management                             | 9    |

| 1.3 Shared Memory Array                              | 10   |

| 1.3.1 Function                                       | 10   |

| 1.3.2 Shared Memory Array Initialization             | 11   |

| 1.3.3 Shared Memory Request - DMA level Assignment   | 11   |

| 1.4 Arbitration Control                              |      |

| 1.4.1 Function                                       |      |

| Chapter Pa                                            | ge |

|-------------------------------------------------------|----|

| 1.5 Interrupt Control                                 | 13 |

| 1.5.1 Function I                                      | 13 |

| 1.5.2 Interrupt Request for HOST Service              | 13 |

| 1.5.3 BIM Interrupts                                  | 14 |

| 1.5.4 MFP Interrupts                                  | 15 |

| 1.5.5 Exception Vectors                               | 15 |

| 1.5.6 Interrupt Request for External CPU Service      | 16 |

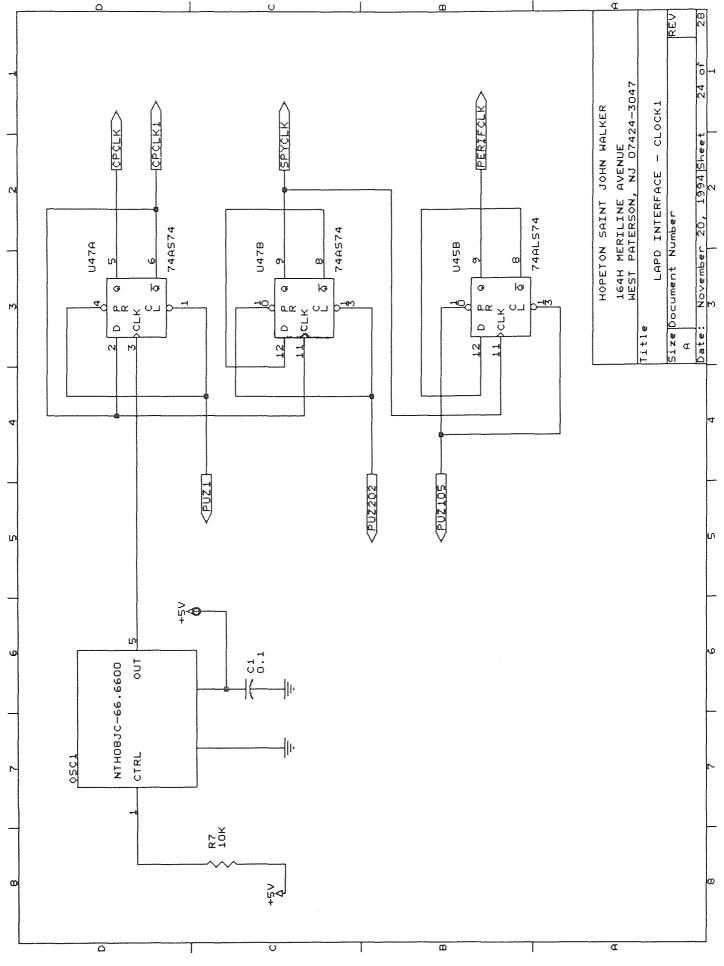

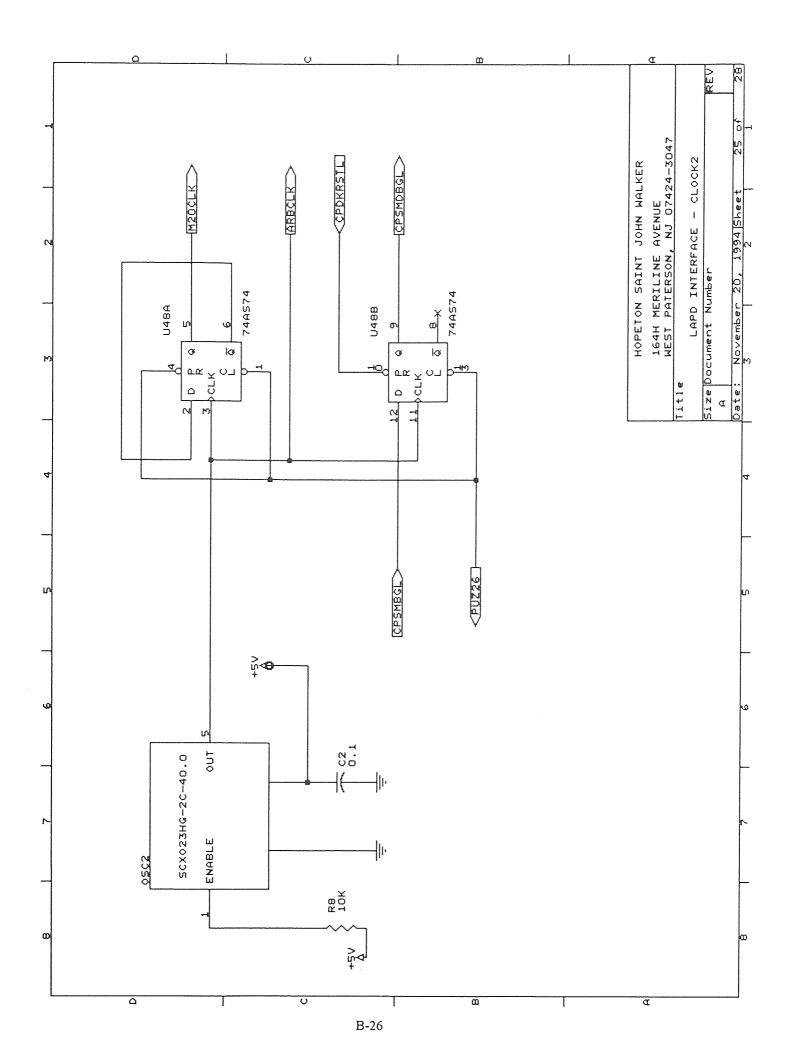

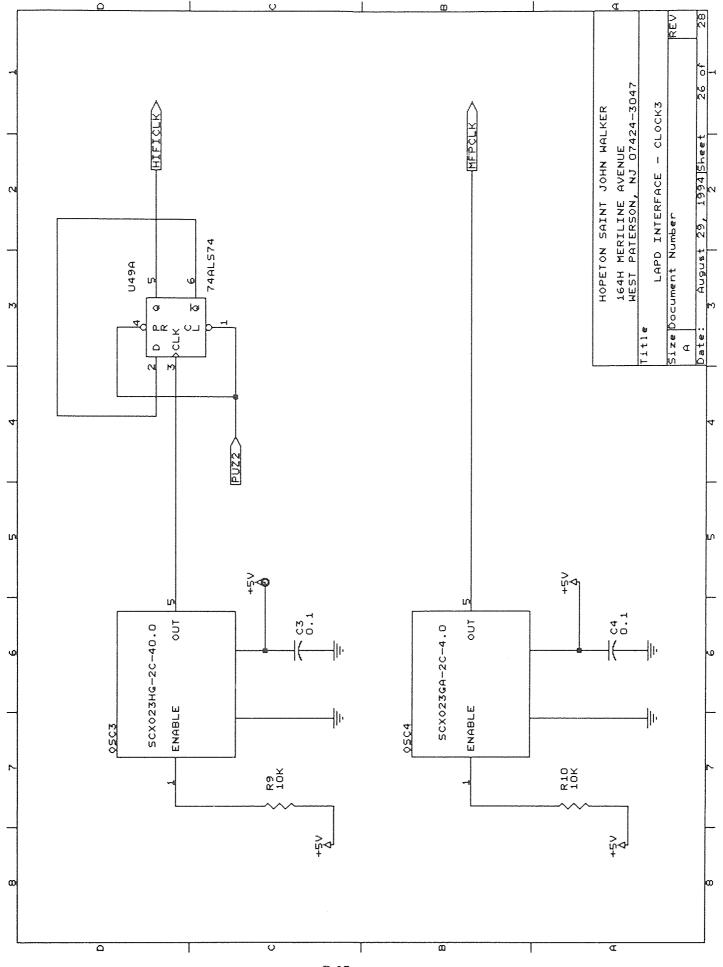

| 1.6 LAPD Interface Clocks                             | 16 |

| 1.6.1 Function                                        | 16 |

| 1.7 HOST to HDLC Private Communication Link           | 17 |

| 1.7.1 Function                                        | 17 |

| 1.8 Registers                                         | 18 |

| 1.8.1 HOST Device Interrupt Request Register          | 18 |

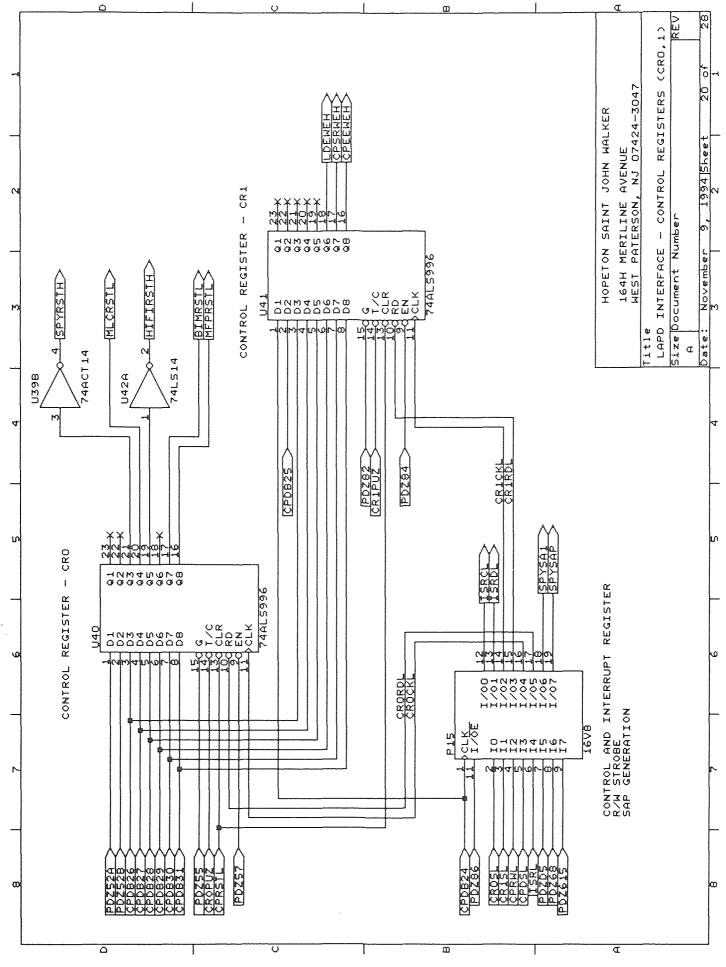

| 1.8.2 HOST Control Register - CR0                     | 19 |

| 1.8.3 HOST Control Register - CR1                     | 20 |

| 1.8.4 HOST Interrupt Status Register                  | 21 |

| 1.8.5 HOST Exception Vector                           | 22 |

| 1.8.6 System Control Register                         | 23 |

| 1.8.7 External CPU to HOST Interrupt Request Register | 25 |

| Chapter                                                                                                  | Page |

|----------------------------------------------------------------------------------------------------------|------|

| 1.9 Shared Memory Requirements for LAPD Interface                                                        | 26   |

| 1.9.1 Calculation of Memory Requirement                                                                  | . 26 |

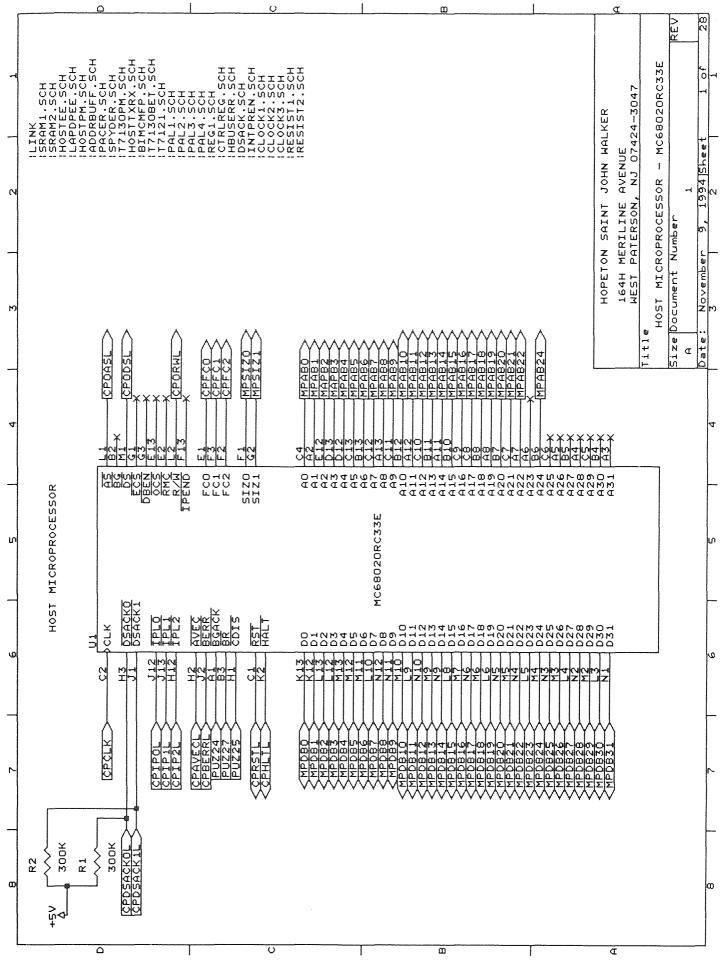

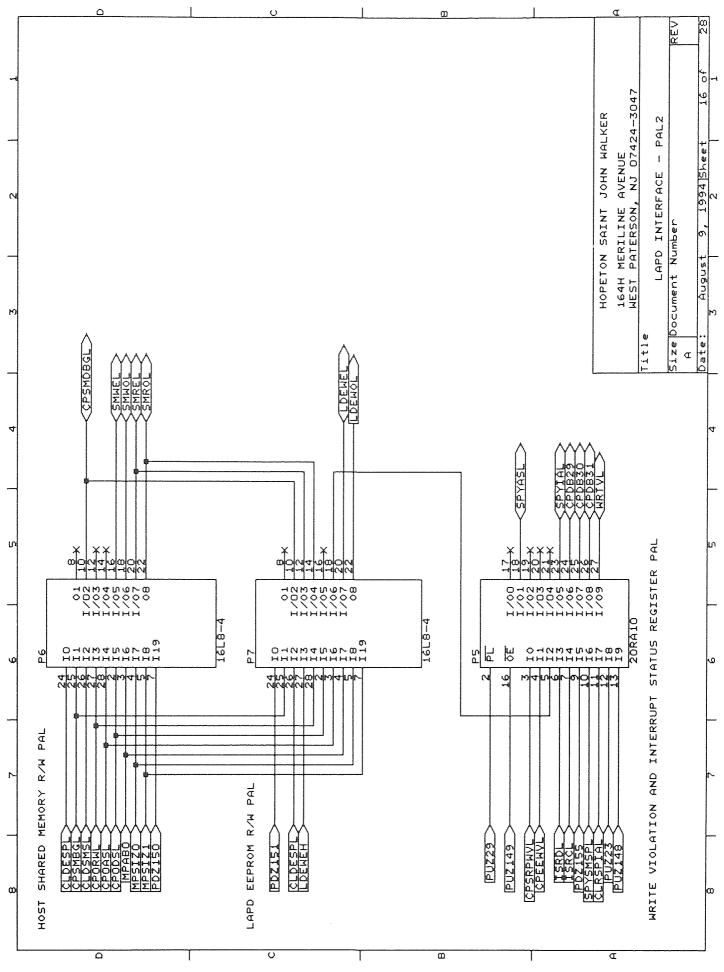

| 2 LAPD INTERFACE CIRCUIT DESCRIPTION                                                                     | . 28 |

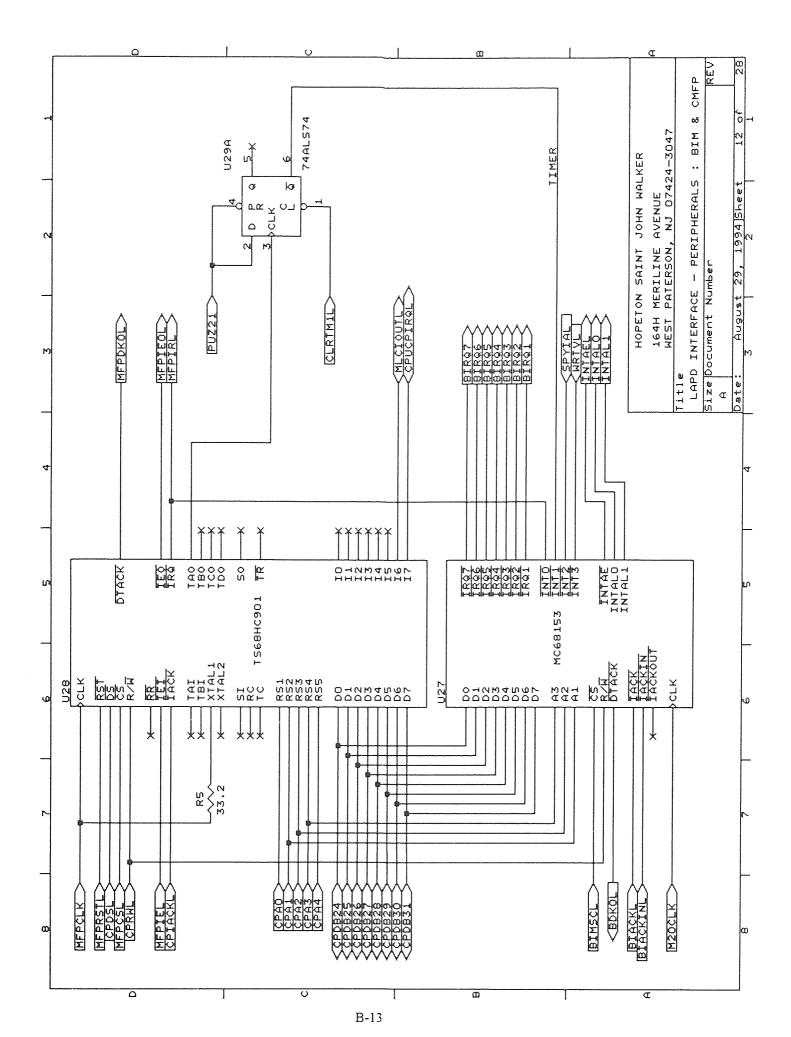

| 2.1 Circuit Description for the LAPD Interface                                                           | . 28 |

| 2.1.1 Interface Overview                                                                                 | . 28 |

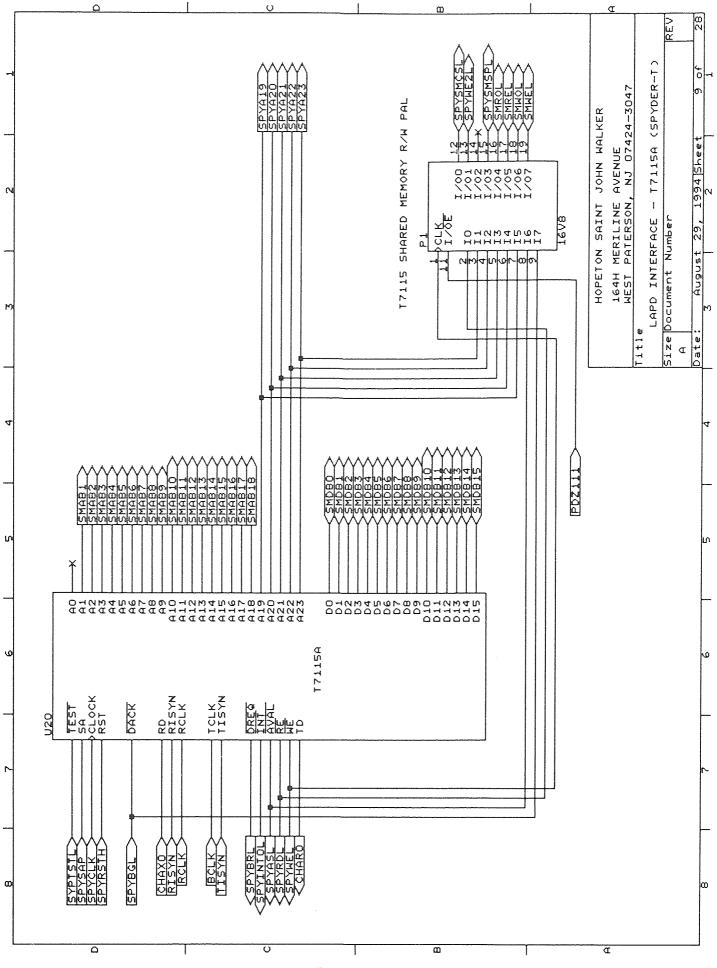

| 2.2 SPYDER-T Access to Shared Memory Array                                                               | 29   |

| 2.2.1 Shared Memory Access                                                                               | 29   |

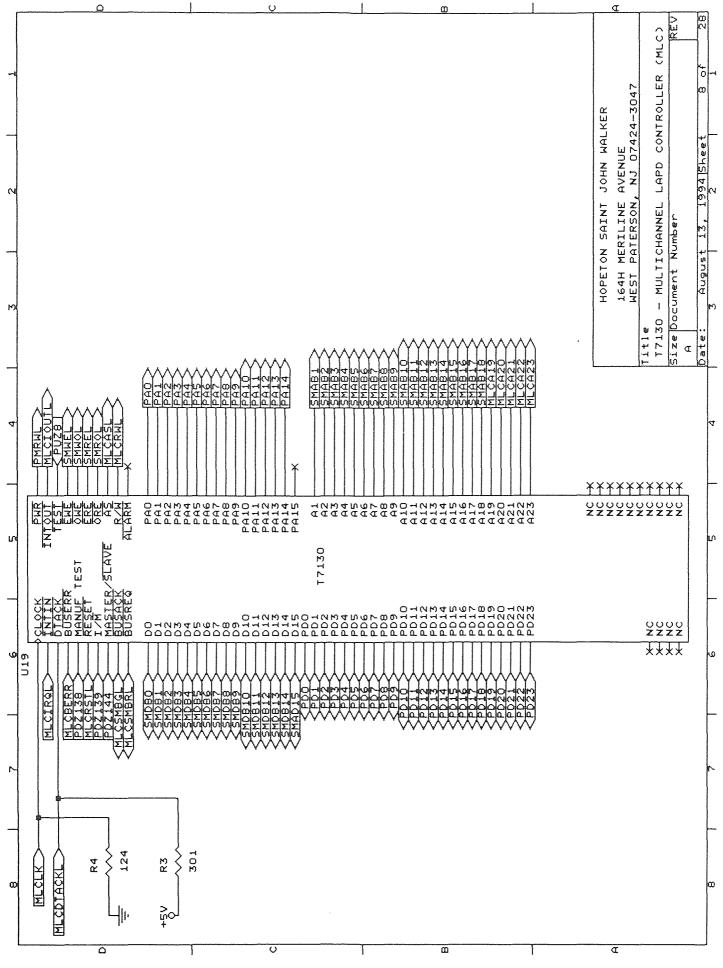

| 2.3 Multichannel LAPD Controller - T7130                                                                 | 30   |

| 2.3.1 Function                                                                                           | 30   |

| 2.3.2 Multichannel LAPD Controller External I/O Port - Access to Shared Memory Array                     | 31   |

| 2.3.3 Multichannel LAPD Controller External I/O Port - Access to SRAM Devices in the Shared Memory Array | 31   |

| 2.3.4 External I/O Port - Access to EEPROM Devices in the Shared Memory<br>Array                         | 32   |

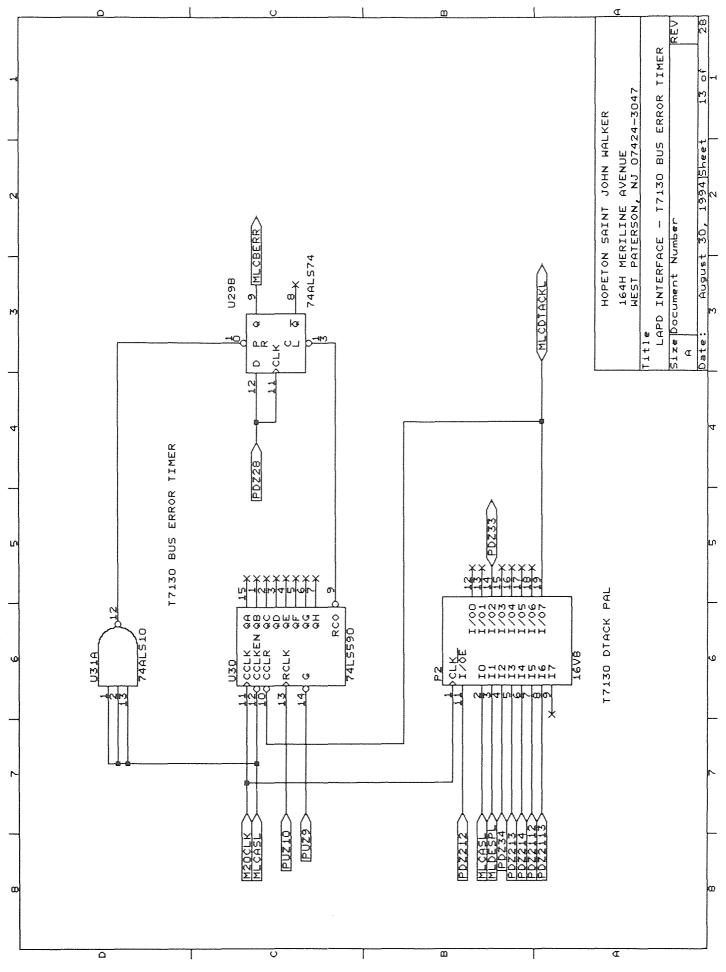

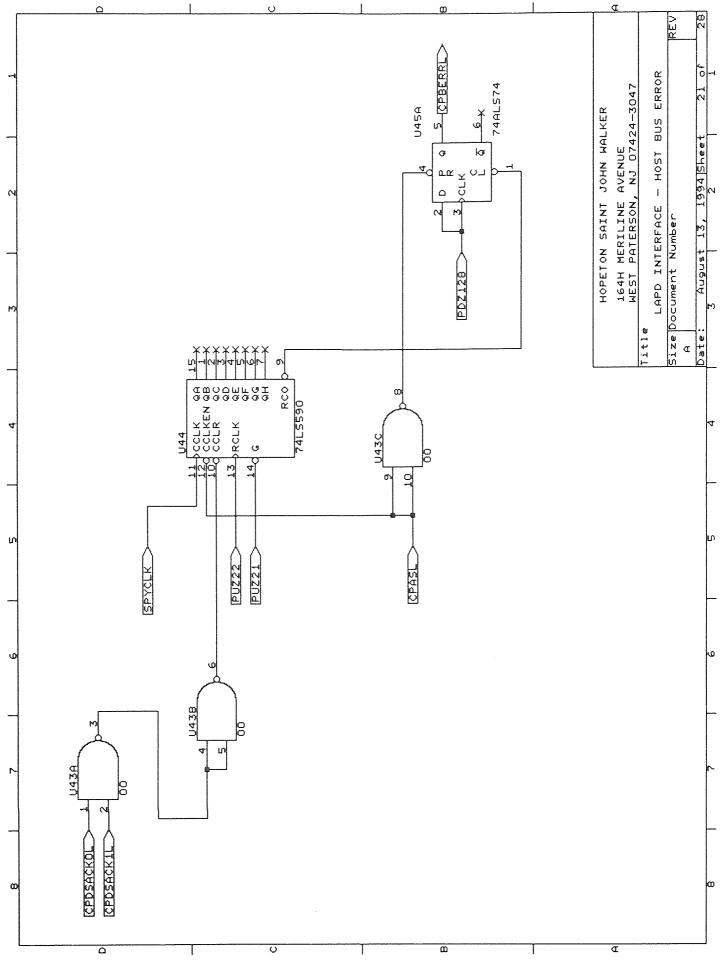

| 2.3.5 External I/O Port - Bus Error, SMA Chip Selects and T7130 DTACK                                    | 33   |

| 2.3.6 Multichannel LAPD Controller Private I/O Port                                                      | 34   |

| 2.3.7 Multichannel LAPD Controller Clock Source                                                          | 34   |

| 2.4 T7130, T7115A and MC68020 Interface                                                                  | 35   |

| 2.4.1 Overview                                                                                           | 35   |

| 2.4.2 HOST or SPYDER-T to Multichannel LAPD Controller                                                   | 35   |

| Chapter                                             | Page |

|-----------------------------------------------------|------|

| 2.4.3 Multichannel LAPD Controller to HOST          |      |

| 2.4.4 Initialization of the T7130 and T7115A        | 36   |

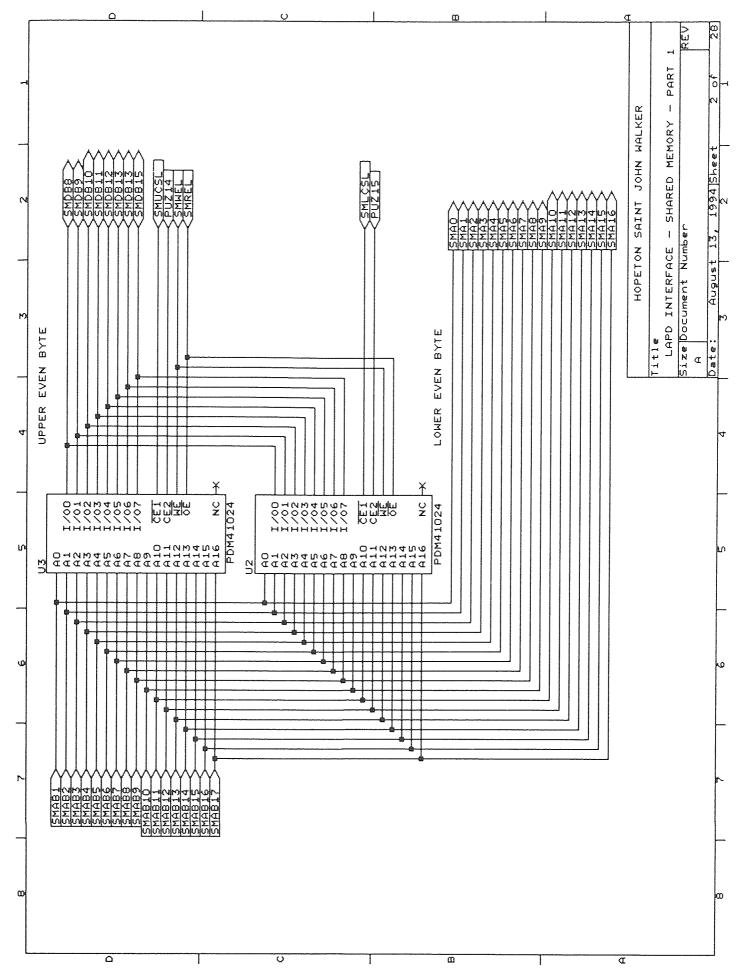

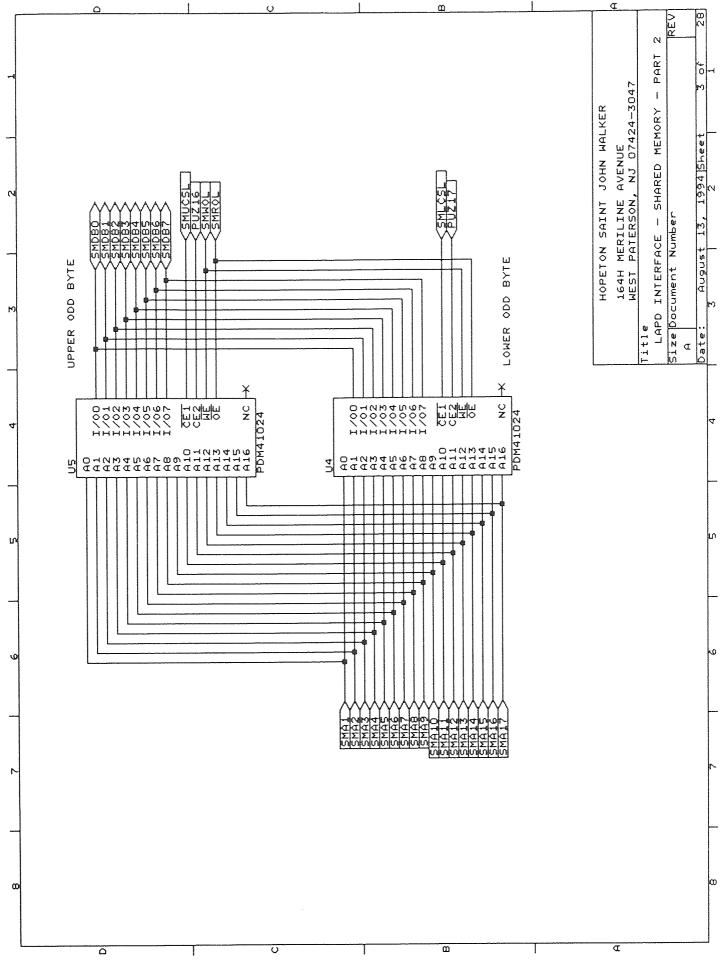

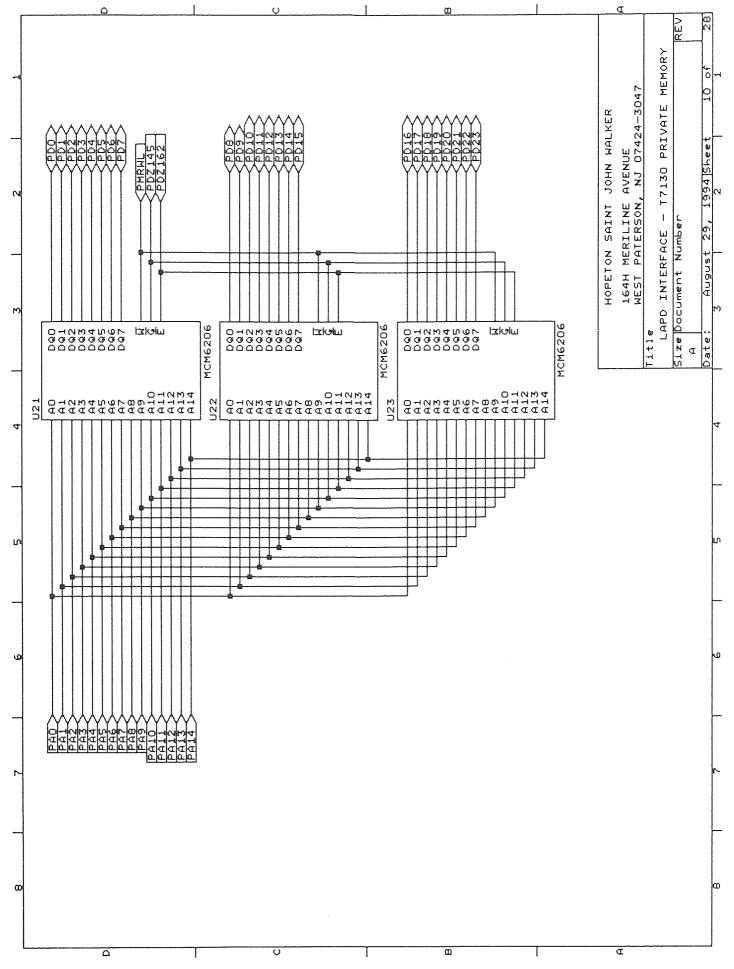

| 2.5 Shared Memory Array                             | 37   |

| 2.5.1 Structure and Function                        | 37   |

| 2.5.2 Common Shared Memory Array                    |      |

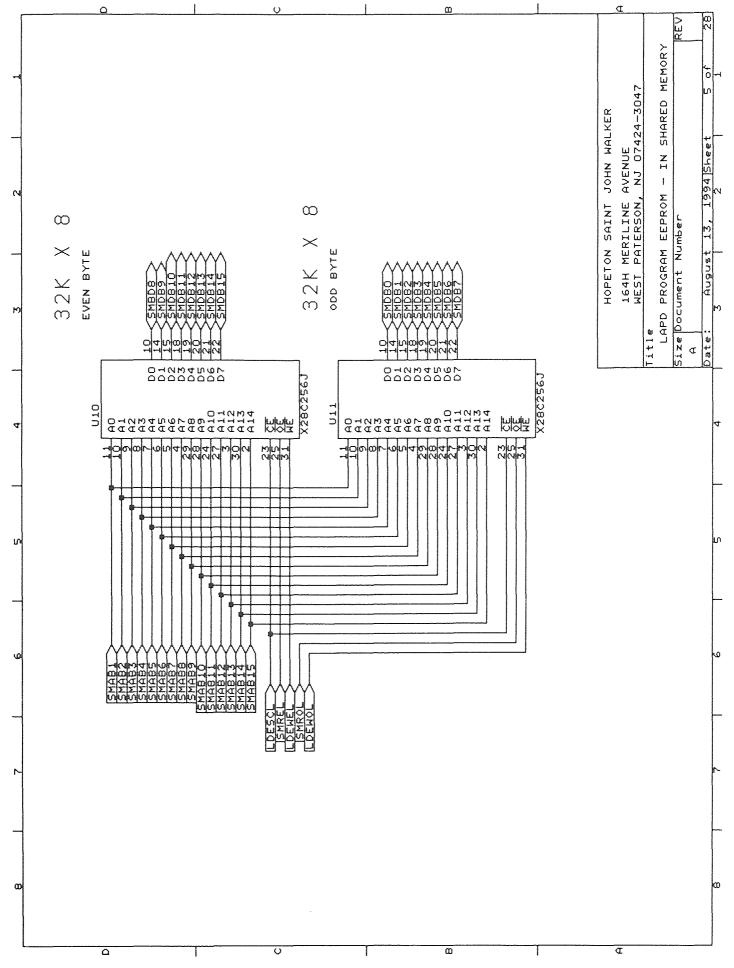

| 2.5.3 Shared Memory Array LAPD protocol Code EEPROM | 39   |

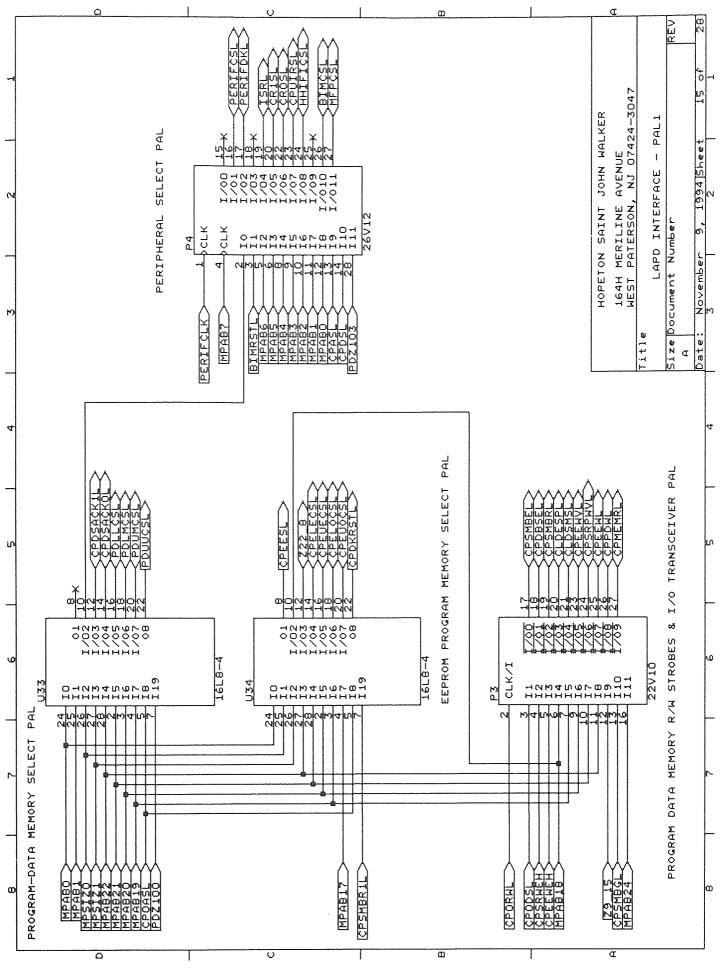

| 2.5.4 Shared Memory Array Chip Select               | 40   |

| 2.5.5 Shared Memory Array Address/Data Bus          | 40   |

| 2.5.6 Shared Memory Array R/W Bus                   | 40   |

| 2.5.7 Initialization                                |      |

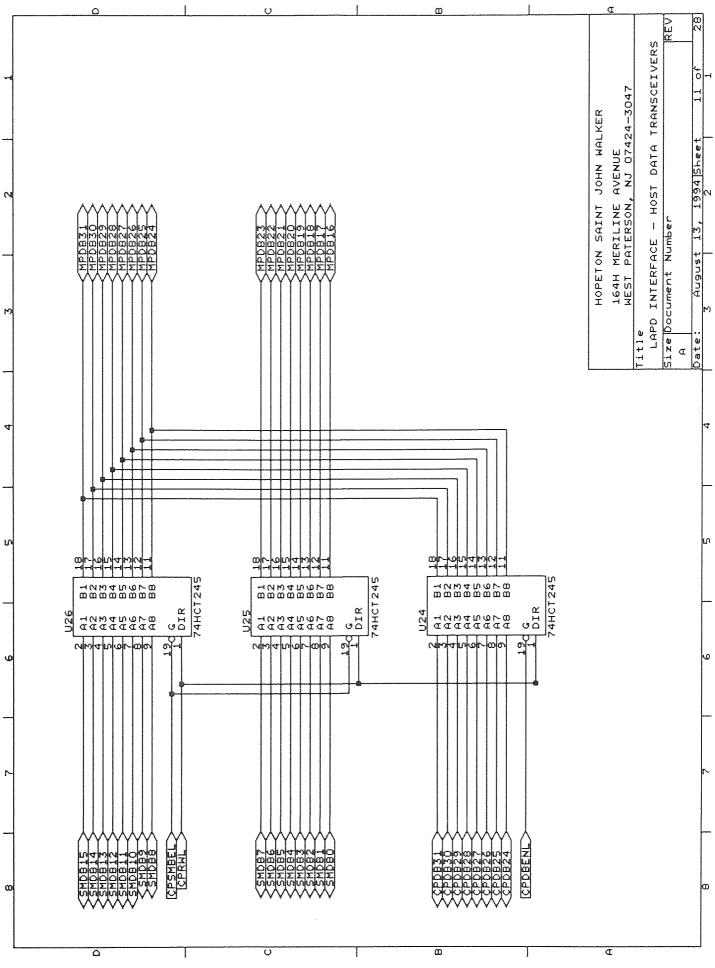

| 2.6 HOST - Main Processor and Support Logic         |      |

| 2.6.1 Elements and Function                         | 41   |

| 2.6.2 HOST Support Logic                            |      |

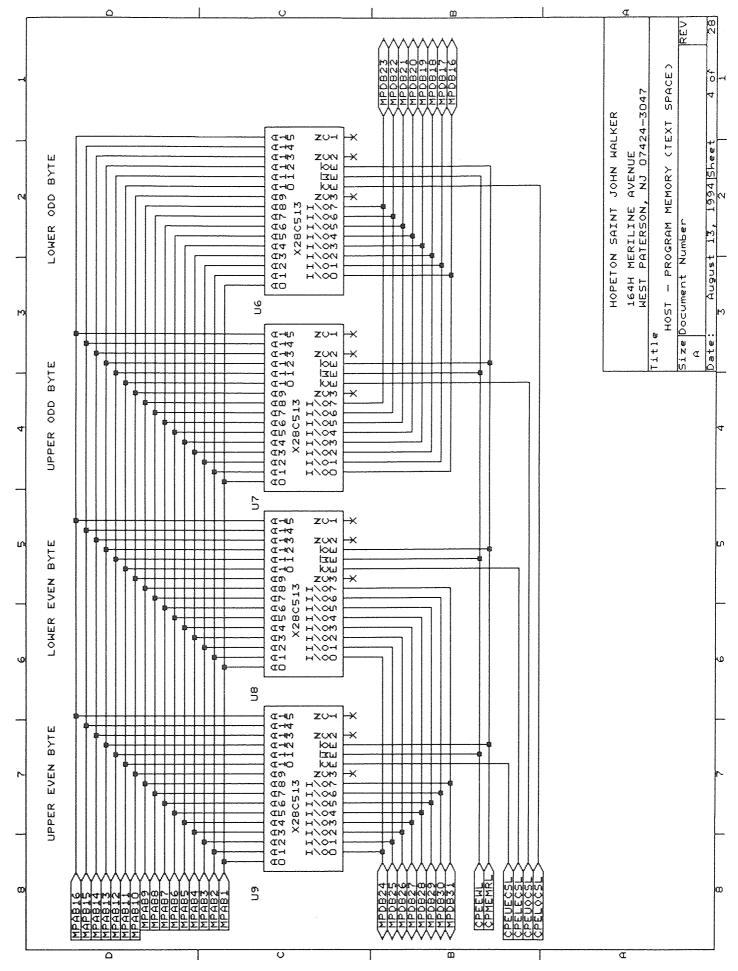

| 2.6.3 HOST EEPROM and SRAM                          | 45   |

| 2.6.4 Local Program Space                           | 45   |

| 2.6.5 Local EEPROM Program Space                    | 46   |

| 2.6.6 Access to Shared Memory Array SRAM and EEPROM | 46   |

| 2.7 HOST Peripherals                                | 47   |

| 2.7.1 Interrupt Control Devices                     |      |

| Chapter Page                                                             |

|--------------------------------------------------------------------------|

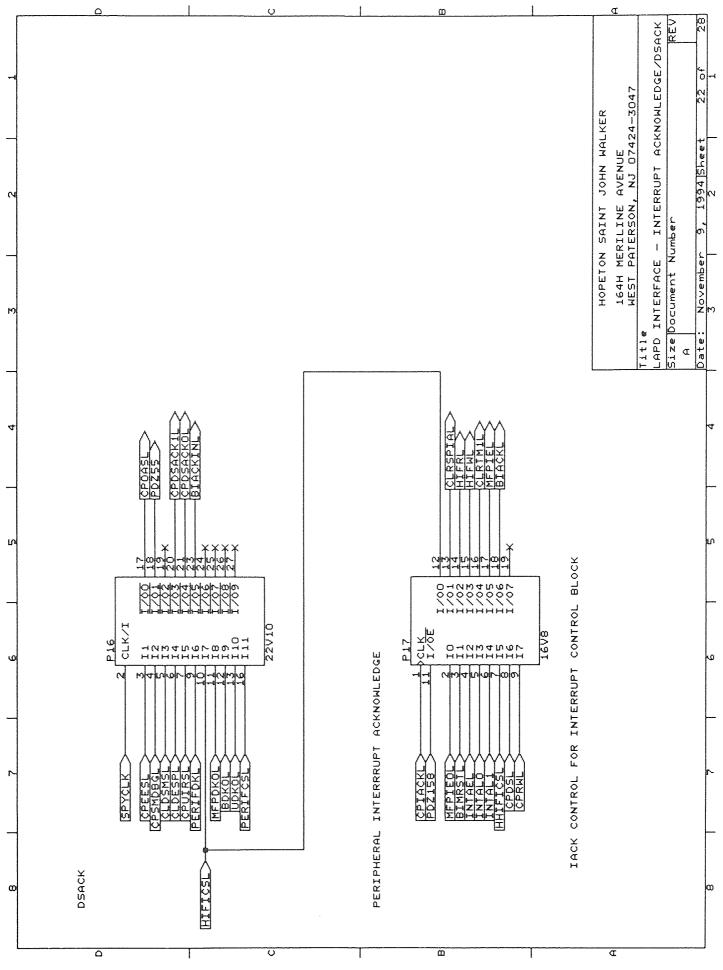

| 2.7.2 Interrupt Control Block                                            |

| 2.7.3 Interrupt Request for HOST Interface                               |

| 2.7.4 BIM Interrupts                                                     |

| 2.7.5 MFP Interrupts                                                     |

| 2.7.6 Exception Vectors                                                  |

| 2.7.7 Host Interrupt Acknowledge                                         |

| 2.8 HOST Functions                                                       |

| 2.8.1 Overview                                                           |

| 2.8.2 Initialization and Diagnostics                                     |

| 2.8.3 Level-2 Management of the LAPD Data Links                          |

| 2.8.4 Level-3 Management 51                                              |

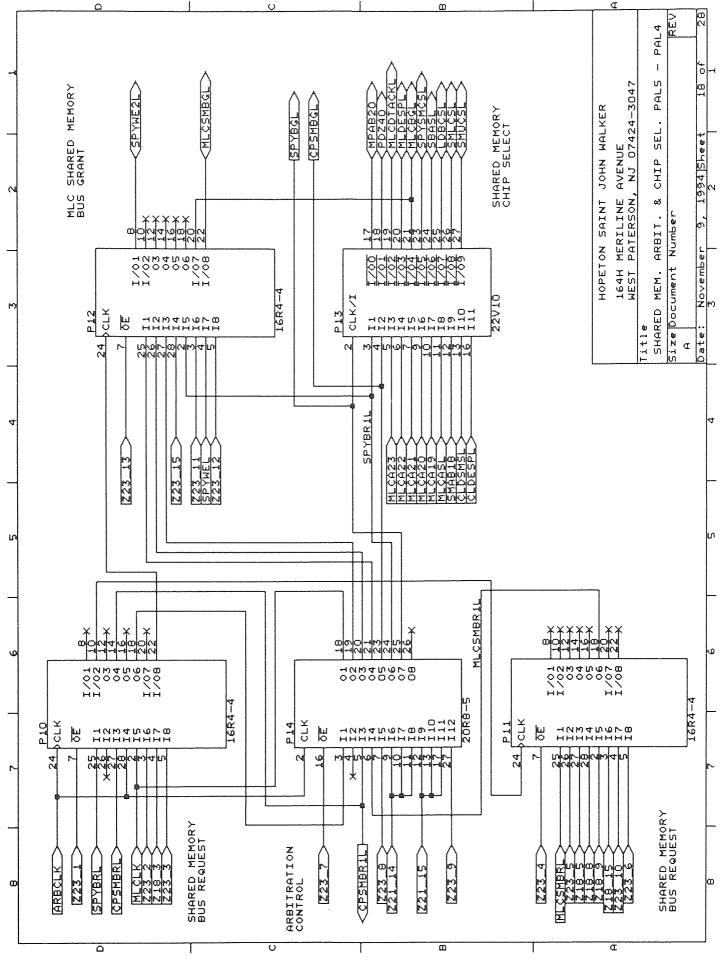

| 2.9 Arbitration Control Block                                            |

| 2.9.1 Function                                                           |

| 2.9.2 Shared Memory Array Request - DMA Level Assignment 52              |

| 2.9.3 Arbitration Control - Shared Memory Array Request/Grant Process 53 |

| 2.9.4 Initialization                                                     |

| 2.10 LAPD Interface Clocks                                               |

| 2.10.1 Function                                                          |

| Chapter Pa                               | ge          |

|------------------------------------------|-------------|

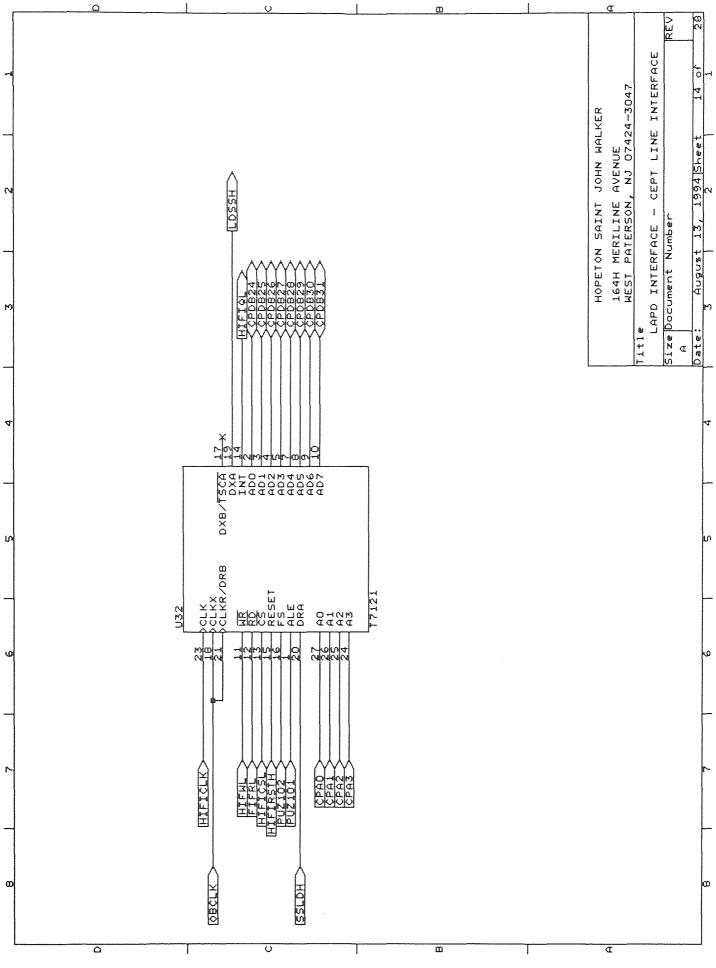

| 2.11 HDLC Private Communication Link     | 56          |

| 2.11.1 Function                          | 56          |

| 2.12 T7130 and T 7115A Memory Map        | 57          |

| 2.12.1 Memory Maps                       | 57          |

| 3 BACKGROUND, CONCLUSIONS AND SUGESTIONS | 58          |

| 3.1 LAPD Interface                       | 58          |

| 3.1.1 Importance                         | 58          |

| 3.1.2 LAPD Devices                       | 59          |

| 3.1.3 Testing and Test Results           | 61          |

| 3.1.4 Throughput                         | 61          |

| APPENDIX A PLD EQUATIONS A               | <b>L</b> -1 |

| APPENDIX B ORCAD SCHEMATICS B            | 3-1         |

| REFERENCES                               |             |

# LIST OF TABLES

| Table                                                    | Page |

|----------------------------------------------------------|------|

| 1 Examples of TEI and SAPI assignments                   | 4    |

| 2 Shared Memory Array DMA Level Assignment               | 12   |

| 3 Interrupt Requests to HOST                             |      |

| 4 LAPD Interface Clock Requirements                      | 17   |

| 5 Interrupt Request Register                             |      |

| 6 HOST Control Register CR0                              | 19   |

| 7 HOST Control Register CR1                              | 20   |

| 8 HOST Interrupt Status Register                         |      |

| 9 HOST Exception Vector                                  | 23   |

| 10 System Control Register                               | 24   |

| 11 External CPU to HOST Interrupt Request Register       | 25   |

| 12 TD and RD Memory Requirements                         |      |

| 13 Other Shared Memory Data Structure Requirements       | 27   |

| 14 HOST Programmable Logic Devices                       | 44   |

| 15 Arbitration Control Block, Programmable Logic Devices | 53   |

| 16 T7130 I/O Memory Map                                  | 57   |

| 17 T7115A I/O Memory Map                                 | 57   |

| 18 HOST Memory Map Memory Devices                        | 57   |

| 19 MC68020 Memory Map for Peripheral Devices             | 57   |

| 20 MC68020 Memory Map for Peripheral Devices             | 62   |

# ACRONYMS

| ACB    | Arbitration Control Block                           |

|--------|-----------------------------------------------------|

| BET    | Bus Error Timer                                     |

| BG     | Bus Grant                                           |

| BR     | Bus Request                                         |

| CB     | Control Blocks                                      |

| CQ     | Command Queue                                       |

| CMOS   | Complementary Metal Oxide Semiconductor             |

| CR     | Control Register                                    |

| CRC    | Cyclic Redundancy Check                             |

| CSA    | Common Shared Memory Array                          |

| DL     | Data Link                                           |

| DLP    | Data Link Processor                                 |

| DLCI   | Data Link Control Identifier                        |

| DMA    | Direct Memory Access                                |

| DSW    | Diagnostic Status Word                              |

| DTACK  | Data Transfer ACKnowledge                           |

| EEPROM | Electrically Erasable Programmable Read Only Memory |

| ETSI   | European Telecommunications Standards Institute     |

| EX CPU | External Central Processing Unit                    |

| FCS    | Frame Check Sequence                                |

| HDLC   | High Level Data Link Control                        |

| HOST   | MC68020 Microprocessor                              |

| HSB    | HDLC Statistics Block                               |

| IACK   | Interrupt ACKnowledge                               |

| ICB    | Interrupt Control Block                             |

| IQ     | Interrupt Queue                                     |

| IRR    | Interrupt Request Register                          |

| ISDN   | Integrated Services Didital Network                 |

| ISR    | Interrupt Status Register                           |

| L2     | Layer 3                                             |

| L3     | Layer 3                                             |

| LAP    | Link Access Procedure                               |

| LAPB   | Link Access Procedure on the B-Channel              |

| LAPD   | Link Access Procedure on the D-Channel              |

| MLC    | Multichannel LAPD Controller (T7130)                |

| NVM    | Non-Volatile Memory                                 |

| PLD    | Programmable Logic Device                           |

| RFA    | Remote Frame Alignment                              |

| RG     | Request Grant                                       |

# ACRONYMS (Continued)

| RD<br>SA<br>SAPI<br>SM<br>SMA<br>SMBR<br>SPYDER-T<br>SRAM | Receive Descriptor<br>SPYDER-T Attention<br>Service Access Point Identifier<br>Shared Memory<br>Shared Memory Array<br>Shared Memory Bus Request<br>Synchronous Protocol Data Formatter (T7115A)<br>Static Random Access Memory<br>Transmit Descriptor |

|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                           |                                                                                                                                                                                                                                                        |

|                                                           | 5 5                                                                                                                                                                                                                                                    |

| SMBR                                                      | Shared Memory Bus Request                                                                                                                                                                                                                              |

| SPYDER-T                                                  | Synchronous Protocol Data Formatter (T7115A)                                                                                                                                                                                                           |

| SRAM                                                      | Static Random Access Memory                                                                                                                                                                                                                            |

| TD                                                        | Transmit Descriptor                                                                                                                                                                                                                                    |

| TEI                                                       | Termination Endpoint Identifier                                                                                                                                                                                                                        |

| TQ                                                        | Transmit Queue                                                                                                                                                                                                                                         |

| VLSI                                                      | Very Large Scale Integrated                                                                                                                                                                                                                            |

|                                                           |                                                                                                                                                                                                                                                        |

## **CHAPTER 1**

## LAPD HARDWARE SPECIFICATIONS

#### 1.1 Data Link Processors - T7130 and T7115A

# 1.1.1 Function

The Data Link Processors (DLP), provides the termination point for the LAPD protocol and consists of two CMOS VLSI devices. Namely, the T7115 Synchronous Protocol Data Formatter (SPYDER-T) and the T7130 Multichannel LAPD Controller (MLC). These devices are intelligent peripherals to the Motorola MC68020 microprocessor (HOST) and provide the hardware necessary to perform the complete Level 2 (L2) link layer protocol, Link Access Procedure - D Channel (LAPD). The T7130, T7115A and MC68020 exchange all commands and status through common areas located in SRAM within the Shared Memory Array (SMA). These areas include the Control Blocks (CB), Command Queue (CQ) and the Interrupt Queue (CQ). The T7115 and T7130 both have DMA capability. Communication between the SPYDER-T and MLC also occurs through common data structures<sup>1</sup> contained in the LAPD Interface Shared Memory Array. The SPYDER-T and MLC are memory mapped inside the MC68020 I/O space through the Control Register (CR0) for the purpose of reset and initialization.

<sup>&</sup>lt;sup>1</sup> A more detail description of these data structures can be found in the T7115A and T7130 data sheets.

#### 1.1.2 Synchronous Protocol Data Formatter - SPYDER-T

The LAPD protocol uses two delimiters, called flags, to identify frame boundaries. A Frame Check Sequence (FCS) field is included for the error detection code and is calculated from all the bits in the LAPD frame exclusive of the flags. As each packet of a LAPD data channel is transferred to the T7115A and T7130 the SPYDER-T performs low level formatting functions. This low level formatting corresponds to,

- 1. insertion and detection of the LAPD header and tail flags, and

- 2. calculation of the Cyclic Redundancy Check (CRC) code that is used for either

- comparison with the received FCS (for error reporting), or

- to append to outgoing message frames as the FCS field on each activated LAPD data channel.

The SPYDER-T does not report that a complete LAPD message has been received until all bytes between the header and tail flags are received without any CRC errors and the address, control and information fields have been transferred to receive buffers in SRAM within the Shared Memory Array (SMA). The SPYDER-T has limited on-chip buffering capability and must periodically performs a two byte DMA transfer<sup>1</sup> on the received data.

In the transmit direction, the SPYDER-T begins transmission of a LAPD frame with the header flag, reads the address, control and information bytes from memory, then appends the CRC bytes and closing flag. Whenever a complete frame is received or transmitted by the SPYDER-T, it updates selected bits in the shared data structure between the SPYDER-T and MLC. This shared data structure is referred to as the T7115

<sup>&</sup>lt;sup>1</sup> The SPYDER-T must perform the DMA transfer to shared memory within six clock cycles (16.67MHZ clock) after a request has been initiated.

Interrupt Queue (T7115A-IQ) and contains information about the status of each LAPD channel. The Interrupt Queue is polled<sup>2</sup> by the MLC and indicates which incoming or outgoing LAPD channel is ready for further Level-2 (L2) processing by the MLC. Although the SPYDER-T has on-chip DMA capability, it does not have a transfer acknowledge mechanism to ensure that a I/O cycle has been completed, such as the DTACK input signal commonly found on the MC680XX family of microprocessors. Consequently, external logic has been included in the T7130 and T7115A block to detect for any illegal<sup>3</sup> SPYDER-T address outside valid SMA space.

# 1.1.3 Multichannel LAPD Controller - T7130

The T7130 Multichannel LAPD Controller manages all Level-2 Data Link (DL) functions and processes the LAPD frame header, address and control fields. In the receive direction, these fields are parsed by the MLC whereas in the transmit direction, these fields are built by the T7130 and appended to the outgoing LAPD frame.

The address field is two bytes wide and provides two levels of multiplexing specific for each LAPD frame. The first level of multiplexing discriminates between Terminal End Points when multiple users are sharing the same physical interface. For example, a single LAPD channel allocated between point A and point B, can serve as the Data Link for multiple transceivers. In order to identify a single transceiver at point B, a unique 7-bit number (modulo 128) referred to as a Termination Endpoint Identifier (TEI), is assigned to each transceiver and is part of the address field. The second level of multiplexing is concerned with identifying the type of traffic message that is contained in

<sup>&</sup>lt;sup>2</sup> The T7115-T7130 polling is interrupt driven.

<sup>&</sup>lt;sup>3</sup> A SPYDER-T Illegal address interrupt is generated and sent to the LAPD Interface Interrupt Control Block.

the information field for each TEI. Packet data, call control procedure, and message flow control are a few examples. The Service Access Point Identifier (SAPI), a 6-bit field contained in the address bytes, provides the second level of multiplexing. Examples of TEI and SAPI assignments are shown in table 1. The Data Link Control Identifier (DLCI) is used to uniquely identify a logical connection and consists of a TEI/SAPI pair.

| TEI VALUE  |                                    |  |

|------------|------------------------------------|--|

| 0-63       | TEI not automatically assigned     |  |

| 127        | Used during auto TEI assignment    |  |

|            |                                    |  |

| SAPI VALUE |                                    |  |

| 0          | Call Control Procedure - Signaling |  |

| 63         | L2 Management Procedure            |  |

Table 1Examples of TEI and SAPI assignments

The control field of the LAPD frame consists of either one or two bytes identifying the LAPD message as one of three types: S-frame, U-frame, or I-frame. The first two types provide supervisory and control functions for the Data Link, while Level-3 (L3) data is carried in I-frames. The T7130 administers all message flow and error control through the S and U frames without intervention from the HOST processor.

After processing the message frame headers, the MLC passes any Level-3 or management entity information to the HOST by way of the T7130 Interrupt Queue (IQ) in

the LAPD Common SRAM<sup>4</sup> Array (CSA). The IQ permits a handshaking mechanism between the HOST and MLC for the purpose of exchanging message pointers.

All commands necessary to activate selected LAPD channels and initialize a Data Link are provided by the HOST through the MLC Command Queue (CQ). The HOST writes commands to the CQ which subsequently controls all Data Link operations, including the actual establishment and management of a Data Link. All this is done autonomously by the MLC.

# 1.1.4 T7130, T7115A and HOST Interface

The T7115A, T7130 and HOST exchange all commands and status information through common shared data structures. This information exchange process is interrupt driven primarily to reduce the Shared Memory Array I/O bus occupancy of the T7130. In the polling mode, the T7130 and HOST must constantly request the LAPD Interface shared memory resource area where Command and Interrupt Queues are located. The T7130 is interrupted whenever,

- 1. the T7115 updates the T7115 Interrupt Queue (T7115-IQ), or

- 2. the HOST updates the T7130 Command Queue (T7130-CQ).

Upon receiving an interrupt from either of the above two sources, the T7130 reads the T7115-IQ first, performs the required actions, and then reads the T7130-CQ and executes the host commands. The HOST, on the other hand, is interrupted whenever the T7130 updates it's Interrupt Queue (T7130-IQ). This DLP HOST directed interrupt is processed through the Interrupt Control Block (ICB).

<sup>&</sup>lt;sup>4</sup> The SRAM devices in the SMA do not introduce any wait states for the T7130.

# 1.1.5 Multichannel LAPD Controller Private I/O Port

A 16-bit address, 24-bit data I/O port on the MLC provides access to the Level-2 LAPD protocol code that is contained in fast SRAM and executed by the T7130. This I/O port is accessible only by the T7130. A read or write to private memory is performed once per MLC clock cycle. The MLC operates with a 50 ns clock period (20MHZ). The MLC executes all the LAPD code from this private memory and this scheme provides for modifications to be made to the LAPD code without complications. The LAPD code resides in EEPROM, located in the SMA and must be downloaded to the T7130 private memory during initialization. As a result, changes to the LAPD code is possible through an update of this LAPD program memory.

## 1.1.6 Initialization of the Data Link Processor

The initialization of the T7130 and T7115A is performed by the HOST on power-up. At this point, both the SPYDER-T and MLC are held in a reset state until the MC68020 completes any applicable diagnostic routine. On successful completion, the HOST

- initializes (formats) the data structures in shared memory which are used by the DLP.

- 2. removes the reset to the SPYDER-T and MLC.

After removal of the reset, the SPYDER-T remains in an idle mode while the MLC begins the following initialization procedure,

1. downloads the LAPD code<sup>5</sup> from EEPROM to the private SRAM memory.

<sup>&</sup>lt;sup>5</sup> The EEPROM containing the LAPD code resides in the Shared Memory Array. Hardware write protection of the LAPD EEPROM is provided by the HOST

- verify the integrity of the LAPD code in SRAM by computing a 24-bit Cyclic Redundancy Checksum (CRC).

- 3. begin execution of the LAPD code in private memory.

Since the SPYDER-T is in the idle state and has not been activated, no status information is exchanged between the T7115 and T7130, through the T7115-IQ. To complete initialization of the T7130 and T7115A, the HOST must pulse the SPYDER-T Attention pin (SA) which causes the SPYDER-T to load internal DMA registers with a pointer<sup>6</sup>, to access instructions in shared memory and begin Data Link operations.

## 1.2 HOST - MC68020

## 1.2.1 Function

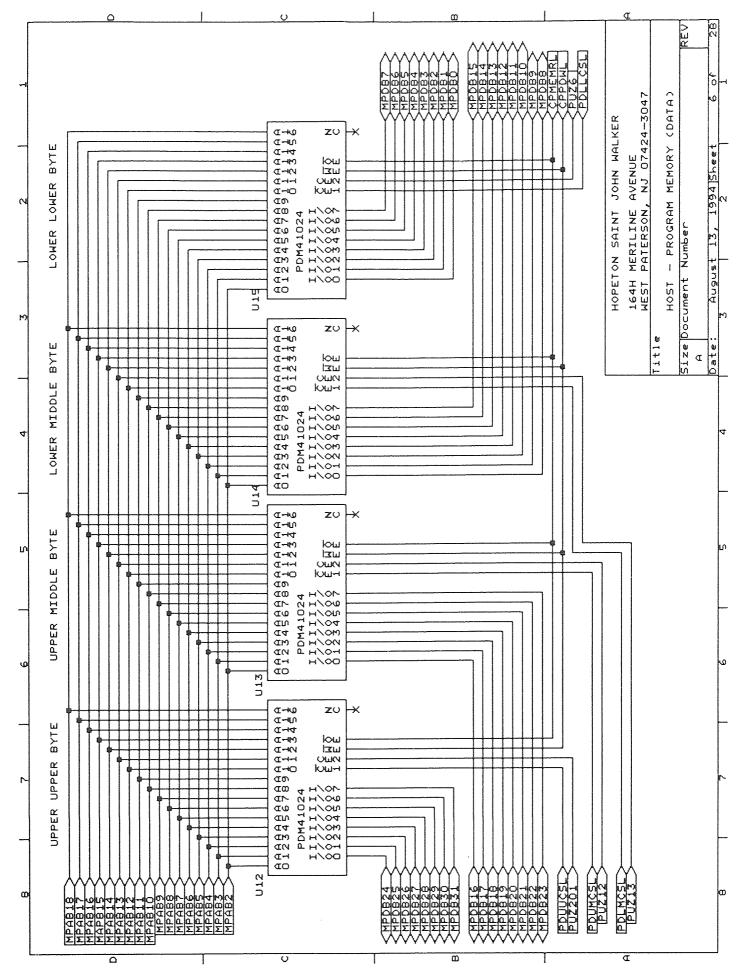

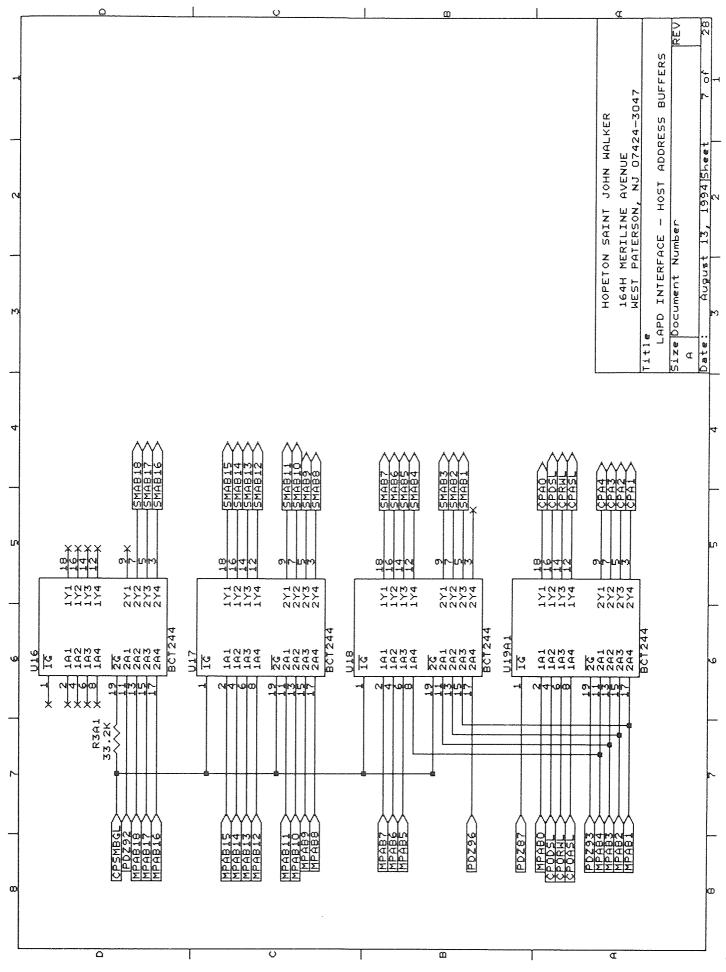

The Motorola MC68020 features a 32-bit address and 32-bit data bus and operates at 33.33MHZ<sup>7</sup>. The motivation for using the MC68020 is twofold. The first is the fast memory access<sup>8</sup> and the second is the ability for long word (32-bit) access. Instruction and data fetches can take advantage of long word access. The HOST is supported by EEPROM, SRAM and several peripheral devices summarized in the following list

- 256K bytes of EEPROM for program memory

- 256K bytes of "shadow" SRAM for program memory

- 256K bytes of SRAM for data memory

- 64K bytes of EEPROM<sup>9</sup> for the LAPD code

<sup>&</sup>lt;sup>6</sup> SPYDER-T Configuration Pointer

<sup>&</sup>lt;sup>7</sup>30 ns clock cycle

<sup>&</sup>lt;sup>8</sup> 4 clock cycles for an I/O access

<sup>&</sup>lt;sup>9</sup> This memory space is also I/O mapped into the T7130 I/O space for the purpose of down loading the LAPD code into the private memory of the T7130

• Interrupt Control Devices

MC68153 (BIM - Interrupt Control)

MC68901 (MFP - Interrupt Control and Timer).

Interrupt Status Register (ISR)

Interrupt Request Register (IRR)

• Control Registers

CR0

CR1

• HDLC Interface Device

## AT&T T7121 (HIFI-64)

All peripheral devices and memory, including the SMA, are mapped in the HOST I/O space. Control register, CR0, is used for reset and initialization of the DLP and peripheral devices. Write protection<sup>10</sup> of program memory space contained in both EEPROM and SRAM is set through the control register CR1. The status of any write violations<sup>11</sup> are contained in the ISR.

Interrupts from the HOST directed to either the T7130, T7115A or an External Processor (EX\_CPU) are possible through the IRR. All program and data memory (contained in fast SRAM) are configured as a 32-bit (*longword*) port which is designed for *zero* wait states. All EEPROM program memory is configured as a word port and the peripherals configured as a byte port.

<sup>&</sup>lt;sup>10</sup> The EEPROMS are also protected with a software key whereas SRAM is protected only through the write enable bit in control register CR1

<sup>&</sup>lt;sup>11</sup> The source of the violation

The HOST performs three major functions:

- 1. LAPD Interface Initialization and any applicable diagnostics

- 2. Level-2 Management

- 3. Level-3 Management

#### 1.2.2 HOST Initialization and Diagnostics

The HOST can perform a series of diagnostics and initialization tests that are executed immediately following a power-up or reset. A failure in anyone of the tests could indicate that the Interface requires service. Non-destructive diagnostics can also run during normal operation. These may include memory tests.

## 1.2.3 Level-2 Management of the LAPD Data Links

The Level-2 programs that manage Data Link operations<sup>12</sup> reside in EEPROM and are executed by the HOST in order to provide a stable link connection. The control and return status of the DLP is accomplished through shared data structures in memory and the HOST administers the format of these structures. The T7130 and T7115A are permitted to activate LAPD data channels after the HOST completes any relevant diagnostics.

# 1.2.4 Level-3 Management

To assist with Level-3 (L3) management routines, a T7121 device has been added to provide a HDLC communication path which can assist in the processing and/or dispatching of Operation and Link Maintenance.

<sup>9</sup>

<sup>&</sup>lt;sup>12</sup> TEI management, connection management, flow control, etc

# 1.3 Shared Memory Array

## 1.3.1 Function

The Shared Memory Array (SMA) serves as the common memory resource for the LAPD Interface. The SMA is a single port (16-bit) memory array consisting of both EEPROM and SRAM devices. Since the SMA bus is limited to only one I/O transfer at a time, access management is performed by the Arbitration Control Function Block. The SMA couples the LAPD protocol devices<sup>13</sup> and HOST along with any other external interface that may be added to complement a system. External devices may include an External CPU (EX\_CPU).

The SRAM functions as a shared memory resource for the T7115, T7130 and HOST, and is referred to as the Common Shared SRAM Array (CSA). The CSA provides a total of 512 Kbytes of storage. The CSA is mapped into the I/O space of the HOST, T7130 and T7115A. EEPROM devices included in the SMA are accessible only by the T7130 and HOST. All communication between the HOST and LAPD devices is through data structures contained in the CSA, within the SMA. The SRAM in the CSA does not introduce any wait states for either the T7130 or T7115.

This common SRAM resource functions as the central depository for all L3 messages, associated L2 message flow and error control, and LAPD protocol state variables. Other type data structures include, Receive Descriptors (RD) and Transmit Descriptors (TD). These provide buffers and message pointers for the status of all activated LAPD channels. The instruction primitives required for the DLP are contained

<sup>&</sup>lt;sup>13</sup> T7115 (SPYDER-T), T7130 (MLC)

in Command Queues (CQ) while the Interrupt Queues (IQ) serve as a handshake mechanism between the T7130, T7115A, HOST and any external processor.

In addition to SRAM, the SMA also contains 64K bytes of EEPROM which is programmed with the LAPD protocol code<sup>14</sup> executed by the T7130. Only the T7130 and HOST have access to the EEPROM devices contained in the SMA. The MLC can only read the EEPROM devices whereas the HOST can write new LAPD code by execution of an update routine.

## 1.3.2 Shared Memory Array Initialization

The format for all the data structures are defined in the data sheets of the LAPD protocol devices and is administered by the HOST during any initialization of the LAPD Interface. Initialization of the CSA follows immediately after the HOST completes any applicable diagnostics. The HOST then begins to configure (*format*) the data structures and upon completion of the formatting process, the HOST removes the reset from the MLC and issues a SPYDER Attention (SA) instruction which initiates the request for establishment of a LAPD data-link.

## 1.3.3 Shared Memory Request - DMA Level Assignment

The SPYDER-T (T7115) has limited on-chip buffers and has the most critical DMA requirement for memory access otherwise corruption of activated LAPD channels will occur. The next highest level has been assigned to any External CPU (EX\_CPU) which prevents the EX\_CPU from excessive waiting times when requesting access into the LAPD Interface Shared Memory Array. The HOST obtains the SMA resource

<sup>&</sup>lt;sup>14</sup> The LAPD code is transferred at initialization to private memory of the T7130

(*EEPROM or SRAM*) whenever the SPYDER-T or an EX\_CPU are not in the process of requesting access to the SMA. There is no critical DMA requirement for the T7130 which is assigned the lowest priority for access to the SMA.

#### **1.4 Arbitration Control**

# 1.4.1 Function

The Arbitration Control (AC) block of the HOST processes all requests for SMA access from the SPYDER-T, MLC, HOST and any EX\_CPU. Communication among these processors is through the SMA. Access to the SMA is through a single 16-bit I/O port and only one device can access the common memory resource at any given time. The AC block provides the mechanism that manage all accesses to either SRAM in the CSA or to the EEPROM devices containing the LAPD code. The selection process that determines which device is allowed access into the SMA is based upon critical DMA times and the order of priority is presented in table 2. The Arbitration Control block is initialized through the power-on reset which clears all Bus Grants (BG).

| PRIORITY | DEVICE   |  |

|----------|----------|--|

| 1        | SPYDER-T |  |

| 2        | EX_CPU   |  |

| 3        | HOST     |  |

| 4        | MLC      |  |

Table 2

Shared Memory Array DMA Level Assignment

1=Highest Priority

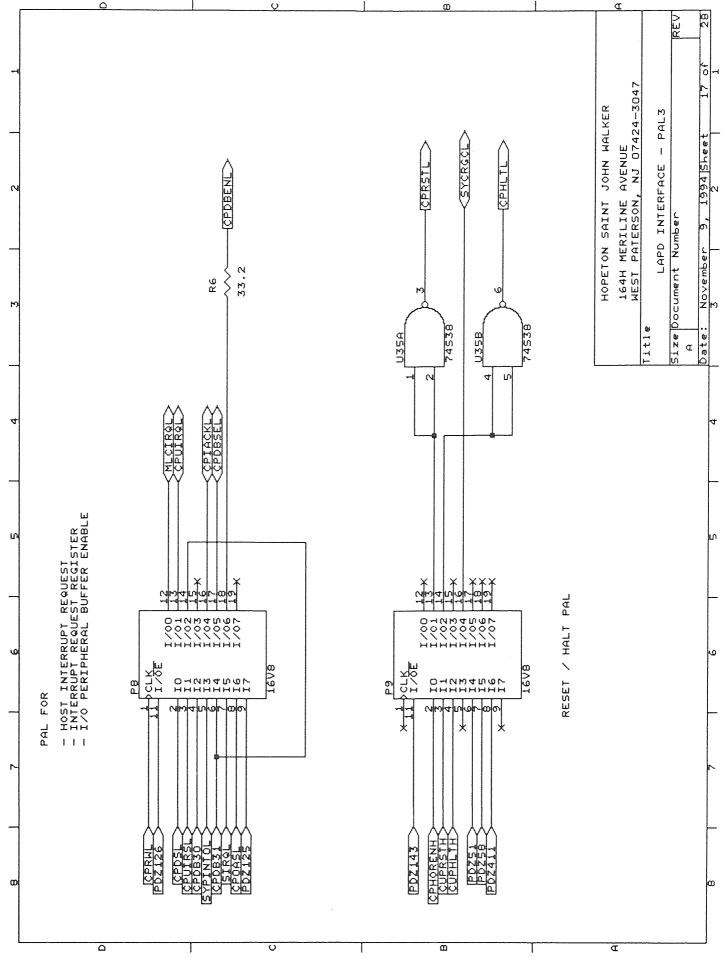

#### 1.5 Interrupt Control

#### 1.5.1 Function

There are two interrupt control paths that are designed for the Interface. These include:

- 1. the interrupt requests for HOST service from on-board peripheral devices, or from an EX\_CPU, and

- 2. the interrupt requests for an EX\_CPU service from the HOST.

# 1.5.2 Interrupt Requests for HOST Service

All interrupt requests to the HOST are handled by the MC68153 Bus Interrupt Module (BIM) and the MC68901 Multi-Function Peripheral (MFP). Interrupt Requests are terminated and prioritized by the BIM and MFP. The BIM provides interrupt request service for four external devices and the MFP provides interrupt request service for eight external and eight internal interrupts. One BIM interrupt channel input, CH0, is dedicated to the MFP. The interrupt request output of the MFP which represents the state of any MFP interrupt source is connected to BIM CH0 allowing all of the MFP interrupt requests to be grouped into a single level before being presented to the HOST. The interrupt requests for the HOST are shown in table 3.

Even though all of the MFP interrupts are grouped at the same level, they are assigned to individual levels within the MFP. Both devices also support programmable level assignment and mask enables for each interrupt request.

|           | Interrupts serviced by the BIM |             |

|-----------|--------------------------------|-------------|

|           | Interrupt                      | BIM Channel |

| Memor     | y Write Violations             | CH3         |

| SPYDE     | R-T Illegal Address            | CH2         |

| Task Sc   | ask Scheduler (Timer) CH1      |             |

| MFP       |                                | CH0         |

|           | Interrupts serviced by the MFP |             |

| Interrupt |                                | MFP Channel |

| EX_CP     | U                              | CH7         |

| MLC L     | ink Interrupt                  | CH6         |

| HDLC      | Interrupt                      | CH5         |

| SPARE     |                                | CH4         |

| SPARE     |                                | CH3         |

| SPARE     |                                | CH2         |

| SPARE     |                                | CH1         |

| SPARE     |                                | CH0         |

Table 3 Interrupt Requests to HOST

#### 1.5.3 BIM Interrupts

All HOST memory write violations are assigned to BIM input channel CH3. These interrupts result from the HOST attempting to write to either local program memory (*EEPROM or SRAM*) or to the T7130 LAPD protocol memory (*EEPROM contained in the SMA*) without the proper write enable bit set. These enables are contained in Control Register 1 (CR1). In order to determine which write violation caused the BIM channel CH3 to be activated, the HOST must read the Interrupt Status Register (ISR), which contains all the write violation status flags.

BIM channel CH2 indicates any illegal SPYDER-T DMA address outside valid SMA space and the 10msec Timer or Task Scheduler is assigned to CH1. The MFP is assigned BIM channel CH0.

#### 1.5.4 MFP Interrupts

All data link related interrupts from the T7130 MLC are assigned to channel CH6 of the MFP. Whenever the T7130 updates it's interrupt queue, an interrupt to the MFP is generated. The HDLC interface device (HIFI-64) is assigned to MFP channel CH5 and indicates a full or empty FIFO condition on the HIFI-64 device which provides the private HDLC data link between the LAPD Interface and other external entity<sup>15</sup>.

Channel 7 of the MFP can be memory mapped into the EX\_CPU I/O space and provides for an interrupt driven message interface between the HOST and an EX\_CPU. All EX\_CPU to HOST (out-going) messages are contained in an out-going message queue in shared memory and whenever the EX\_CPU writes any message for the HOST in this queue, the EX\_CPU has the option of interrupting the HOST through this MFP channel.

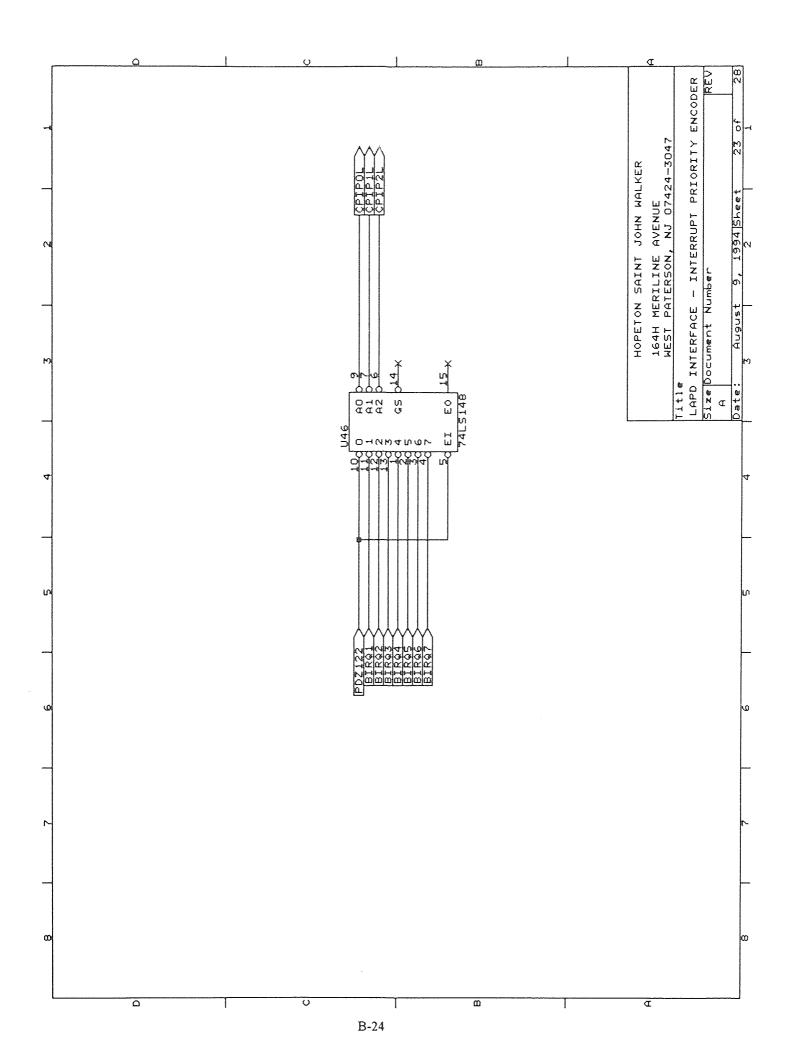

## 1.5.5 Exception Vectors

The vectors for BIM channels CH3, CH2 and CH1 are supplied by the BIM while the MFP provides all the interrupt vectors for BIM channel CH3. The Interrupt handlers are in a daisy chain configuration with the BIM first in the chain followed by the MFP. All interrupt vectors must be loaded into the interrupt handlers BIM and MFP by the HOST during initialization. The HOST obtains the exception vectors during executing an Interrupt ACKnowledge (IACK) cycle and individual interrupt requests that caused the exception is cleared during the IACK cycle<sup>16</sup>.

<sup>&</sup>lt;sup>15</sup> eg SS7

<sup>&</sup>lt;sup>16</sup> (With the exception of the Write Violations (BIM CH0); the HOST must clear these write violation sources with a write command to the Interrupt Status register, (ISR).

#### 1.5.6 Interrupt Requests for External CPU service

The LAPD Interface provides an interrupt path from the HOST to an EX\_CPU. The LAPD Interface can generate a level six interrupt request to the EX\_CPU. An EX\_CPU interrupt acknowledge cycle must clear the interrupt request and obtains the exception vector from the interrupt vector register. The HOST interrupt vector is loaded during initialization.

The LAPD Interface Interrupt Request is part of the interrupt driven message exchange protocol between the HOST and EX\_CPU. All HOST to EX\_CPU (incoming) messages are contained in an incoming message queue in the CSA and whenever the HOST writes any message for the EX\_CPU in this queue, the HOST has the option of interrupting the EX\_CPU through this interrupt path.

# 1.6 LAPD Interface Clocks

# 1.6.1 Function

The LAPD Interface requires various clock sources, eight are derived from three resident crystal oscillators. All crystal oscillators are enabled from a tri-state control.

| Device              | Frequency | Source               |  |  |

|---------------------|-----------|----------------------|--|--|

|                     |           |                      |  |  |

| HOST                | 33.33MHZ  | 66.66 MHZ Oscillator |  |  |

| T7115 SPYDER-T      | 16.67 MHZ |                      |  |  |

|                     |           |                      |  |  |

| Arbitration Circuit | 40.00 MHZ | 40.00 MHZ Oscillator |  |  |

| T7130MLC            | 20.00 MHZ |                      |  |  |

|                     |           |                      |  |  |

| MC68901             | 4.00 MHZ  | 4.00 MHZ Oscillator  |  |  |

| Т7115-СНІ           | 8.0 KHZ   |                      |  |  |

|                     |           |                      |  |  |

| T7121-CHI           | 2.048 MHZ |                      |  |  |

Table 4

LAPD Interface Clock Requirements

## 1.7 HOST to HDLC Private Communication Link

#### 1.7.1 Function

The Interface supports a private serial HDLC communication link between the LAPD Interface and any other subsystem that requires such service. The AT&T T7121 HDLC interface for ISDN (HIFI-64), provides this feature. The HIFI-64 is memory mapped inside the HOST I/O space and is controlled through various internal registers accessible by the HOST. The device contains a 64-byte FIFO which significantly reduces the number of interrupts that must be processed by the HOST.

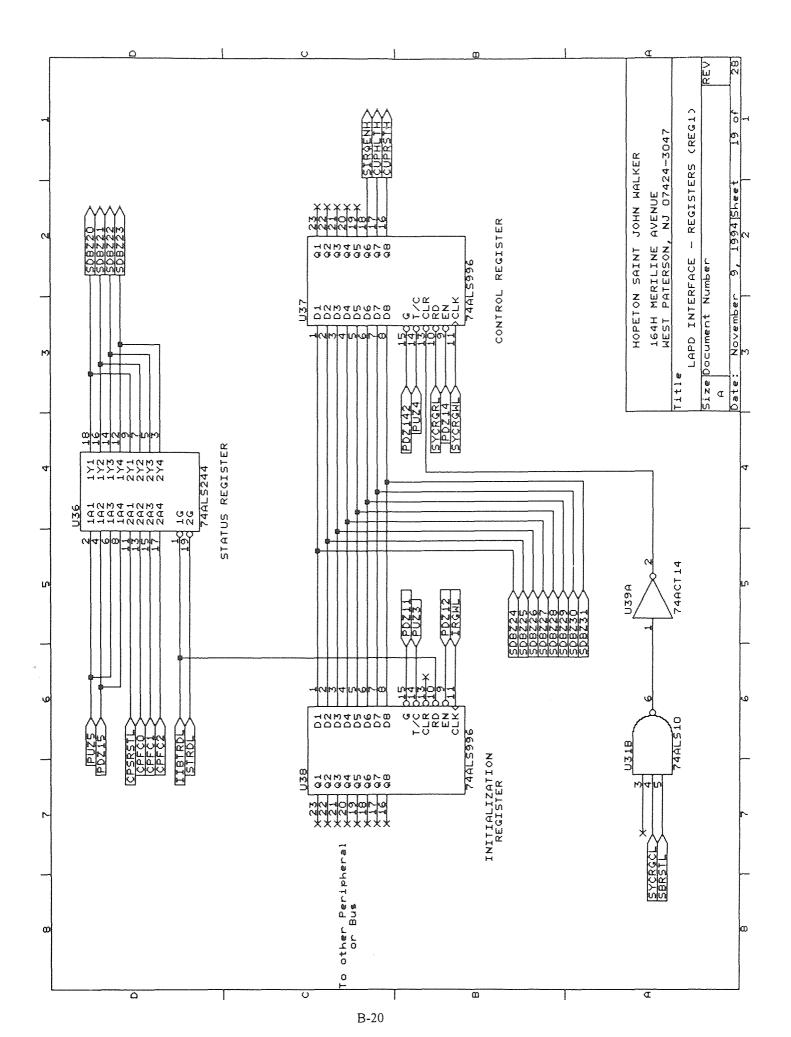

#### 1.8 Registers

### 1.8.1 HOST Device Interrupt Request Register

The Interrupt Request Register (IRR) is located at address xx3xxxf0. Table 5 shows the bit positions, names and read or write status of the relevant bits. All undefined bit positions are don't cares.

Table 5 Interrupt Request Register

| Summer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 31                           | 30                     | 29        | 28        | 27        | 26        | 25        | 24        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|------------------------|-----------|-----------|-----------|-----------|-----------|-----------|

| Contraction of the second se | HOST to<br>EX_CPU INT<br>REQ | HOST to MLC<br>INT REQ | undefined | undefined | undefined | undefined | undefined | undefined |

| Contraction of the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | R/W                          | W                      |           |           |           |           |           |           |

# HOST to EX\_CPU INT REQ

This is the INTerrupt REQuest (INT REQ) for an EX\_CPU service. Whenever the HOST sets this bit to a logic "0", an interrupt request to the EX\_CPU is generated. The interrupt request is enabled through the HOST System Control Register and it is disabled on a reset. Whenever the EX\_CPU executes an interrupt acknowledge cycle, the interrupt request bit is cleared.

#### HOST to MLC INT REQ

This is the INTerrupt REQuest for the T7130 Multi-channel LAPD Controller (MLC INT

REQ). Whenever the HOST sets this bit to a logic "0", an interrupt request to the MLC

is generated. This is an address and data triggered command ;this register bit position is

non-latching. The value read back is not guaranteed to be the same value that was written

to bit-30.

# 1.8.2 HOST Control Register - CR0

The HOST Control Register (CR0) is located at address xx3xxxf2. Table 6 shows the bit positions, names and read or write status of the relevant bits. Bit position 25 in CR0 is undefined.

# Table 6HOST Control Register 0 - CR0

| 31      | 30      | 29 | 28        | 27        | 26        | 25 | 24        |

|---------|---------|----|-----------|-----------|-----------|----|-----------|

| MFP RST | BIM RST |    | T7121 RST | T7130 RST | T7115 RST |    | T7115A SA |

| R/W     | R/W     |    | R/W       | R/W       | R/W       |    | W         |

# MFP RST

This is the ReSeT control for the MC68901 Multi-function Peripheral MFP.

#### **BIM RST**

This is the ReSeT control for the MC68153 Bus Interrupt Module (BIM).

#### T7121 RST

This is the ReSeT control for the T7121 HDLC (HIFI-64).

## T7130 RST

This is the ReSeT control for the T7130 Multi-channel LAPD Controller (MLC).

#### T7115 RST"

This is the ReSeT control for the T7115 SPYDER-T.

# T7115 SA

This is the start-up (initialization) control for the T7115 SPYDER-T. This is an address

and data triggered command. As a result, when this bit is set to a logic "0," a pulse is

issued to the T7115 SPYDER Attention (SA) pin. No provision for a read back of this bit

is provided. If a read of this bit is attempted, there is no guarantee that this bit is either a logic "0" or "1".

## Resets

All resets are a two step process. To reset a peripheral, the processor must first write a zero into the selected bit position (which is the active state for the peripheral device), followed by writing a one which negates the reset control to the peripheral.

## 1.8.3 HOST Control Register - CR1

The HOST Control Register (CR1) is located at address xx3xxxf4. Table 7 shows the bit positions, names and read or write status of the relevant bits. This register is cleared (all bits set to a logic "0") during a LAPD Interface reset. All spare bits are read and write but do not perform ANY FUNCTION.

Table 7HOST Control Register 1 - CR1

| 31       | 30       | 29       | 28     | 27     | 26     | 25     | 24     |

|----------|----------|----------|--------|--------|--------|--------|--------|

| EEWEL MP | SRWEL_MP | EEWEL LD | UNUSED | UNUSED | UNUSED | UNUSED | UNUSED |

| R/W      | R/W      | R/W      | R/W    | R/W    | R/W    | R/W    | R/W    |

#### EEWEN MP

This is the Write ENable for HOST EEPROM program memory. When the EEWEN\_MP bit is set to a logic "1", no write violation interrupt is generated when the HOST attempts to write to this memory space.

#### SRWEN\_MP

This is the Write enable for HOST SRAM for program memory. When the SRWEN\_MP bit is set to a logic "1," no interrupt is generated when the HOST attempts to write to this memory space.

## EEWEN\_LD

This is the Write ENnable for LAPD EEPROM protocol memory contained in the Shared Memory Array. When the EEWEN\_LD bit is set to a logic "1", no interrupt is generated when the HOST attempts to write to this memory space.

## 1.8.4 HOST Interrupt Status Register

The HOST Interrupt Status Register is located at address xx3xxxf6. Table 8 shows the bit positions, names and read or write status of the relevant bits. All undefined bit positions are don't cares. No provision is made to clear individual bits in this register. A clear (all write violations set to a logic "0") is performed by addressing this register while in the write mode.

# Table 8HOST Interrupt Status Register

| - | 31       | 30       | 29       | 28        | 27        | 26        | 25        | 24        |

|---|----------|----------|----------|-----------|-----------|-----------|-----------|-----------|

|   | EEWVL MP | SRWVL_MP | EEWVL_LD | undefined | undefined | undefined | undefined | undefined |

| - | R/W      | R/W      | R/W      |           |           |           |           |           |

## EEWV MP

This is the Write Violation status flag for the HOST EEPROM. When this bit is read as a logic "1", this indicates an attempted write to HOST EEPROM program memory has occurred without the corresponding write enable bit set. The EEWEN\_MP bit in CR1

controls the state of the write violation status flag. If EEWEN\_MP is set to a logic "1,"

the HOST can write to EEPROM space and no write violation interrupt is generated.

#### SRWV MP

This is the Write Violation status flag for the HOST SRAM. When this bit is read as a logic "1", this indicates an attempted write to HOST SRAM program memory has occurred without the corresponding write enable bit set. The SRWEN\_MP bit in CR1 controls the state of the write violation status flag. If SRWEN\_MP is set to a logic "1," the HOST can write to SRAM space and no write violation interrupt is generated.

#### EEWV LD

Write Violation status flag for the HOST LAPD EEPROM. When this bit is read as a logic "1", this indicates that an attempted write to LAPD protocol memory EEPROM in the SMA has occurred, without the corresponding write enable bit set. The LDWEN\_MP bit in CR1 controls the state of the write violation status flag. If LDWEN\_MP is set to a logic "1", the HOST can write to LAPD protocol memory and no write violation interrupt is generated.

## **1.8.5 HOST Exception Vector**

Table 9 shows the bit positions, names and read or write status of the relevant bits for the HOST Exception Vector Register. All undefined bit positions are don't cares.

|           |           |           | ferial and the second | CONTRACTOR OF THE OWNER OF | mig .     |           |           |

|-----------|-----------|-----------|------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----------|-----------|

|           |           |           | Upper                                                                                                            | r Byte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |           |           |           |

| 31        | 30        | 29        | 28                                                                                                               | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 26        | 25        | 24        |

| undefined | undefined | undefined | undefined                                                                                                        | undefined                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | undefined | undefined | undefined |

|           | L         |           | Upper Mi                                                                                                         | ddle Byte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |           |           | L         |

| 23        | 22        | 21        | 20                                                                                                               | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 18        | 17        | 16        |

| CPFC2     | CPFC1     | CPFC0     | HOST RST                                                                                                         | undefined                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | undefined | undefined | undefined |

| R         | R         | R         | R                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |           |           |           |

|           |           |           | Lower Mi                                                                                                         | ddle Byte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |           |           |           |

| 15        | 14        | 13        | 12                                                                                                               | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 10        | 9         | 8         |

| undefined | undefined | undefined | undefined                                                                                                        | undefined                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | undefined | undefined | undefined |

|           |           |           | Lowei                                                                                                            | r Byte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |           |           |           |

| 7         | 6         | 5         | 4                                                                                                                | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2         | 1         | 0         |

| undefined | undefined | undefined | undefined                                                                                                        | undefined                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | undefined | undefined | undefined |

| R/W       | R/W       | R/W       | R/W                                                                                                              | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | R/W       | R/W       | R/W       |

## Table 9HOST Exception Vector Register

## CPFC0-CPFC2

The three bits, CPFC0, CPFC1, and CPFC2 are the function code of the host and

identifies the address space of the current bus cycle.

## HOST RST

The HOST ReSeT bit indicates the state of the HOST (MC68020) reset pin.

## Interrupt Vector

This is the HOST Exception Vector. The exception vector is loaded by the EX\_CPU

during system initialization.

## 1.8.6 System Control Register

Table 10 shows the bit positions, names and read or write status of the relevant bits for the

System Control Register. All undefined bit positions are don't cares.

# Table 10System Control Register

|           |           |            | and the second |           |           |           |           |

|-----------|-----------|------------|------------------------------------------------------------------------------------------------------------------|-----------|-----------|-----------|-----------|

|           |           |            | Upper I                                                                                                          | Byte      |           |           |           |

| 31        | 30        | 29         | 28                                                                                                               | 27        | 26        | 25        | 24        |

| HOST INT  | HOST HLT  | HOST INTEN | UNUSED                                                                                                           | UNUSED    | UNUSED    | UNUSED    | UNUSED    |

| R/W       | R/W       | R/W        | R/W                                                                                                              | R/W       | R/W       | R/W       | R/W       |

|           |           | 1          | Upper Mide                                                                                                       | dle Byte  |           |           |           |

| 23        | 22        | 21         | 20                                                                                                               | 19        | 18        | 17        | 16        |

| undefined | undefined | undefined  | undefined                                                                                                        | undefined | undefined | undefined | undefined |

|           | 1         |            | Lower Mid                                                                                                        | dle Byte  | 1         | L         | l         |

| 15        | 14        | 13         | 12                                                                                                               | 11        | 10        | 9         | 8         |

| undefined | undefined | undefined  | undefined                                                                                                        | undefined | undefined | undefined | undefined |

|           | 1         | l          | Lower l                                                                                                          | Byte      | 1         | I         | I         |

| 7         | 6         | 5          | 4                                                                                                                | 3         | 2         | 1         | 0         |

| undefined | undefined | undefined  | undefined                                                                                                        | undefined | undefined | undefined | undefined |

|           |           |            |                                                                                                                  |           |           |           |           |

## HOST RST

The HOST ReSeT bit controls the reset function of the MC68020. To reset the HOST, this bit is set to a logic "1". The reset process is s single step process. To reset the HOST, bit 31 is set to a logic "1". Circuitry on the interface will clear all bits in the

Control Register (set to a logic "0") after the processor has cycled through reset.

## HOST HLT

The HaLT bit controls the halt function of the MC68020. To halt the HOST, this bit is

set to a logic "1". To disable the halt request, the bit must be set to a logic "0".

## HOST INTEN

The HOST INTerrupt ENable bit allows a HOST to EXT\_CPU interrupt request. The

HOST to EX CPU interrupt is described in the HOST Device Interrupt Request. If this

bit is set to a logic "1", the HOST interrupt requests are enabled.

## 1.8.7 External CPU to HOST Interrupt Request Register

Table 11 shows the bit positions, names and read or write status of the relevant bits for the

EX\_CPU to HOST Interrupt Request Register. All undefined bit positions are don't cares.

|           |           |           | Upper I    | Byte      |           |           |           |

|-----------|-----------|-----------|------------|-----------|-----------|-----------|-----------|

| 31        | 30        | 29        | 28         | 27        | 26        | 25        | 24        |

| HOST INT  | undefined | undefined | undefined  | undefined | undefined | undefined | undefined |

| W         |           |           |            |           |           |           |           |

|           |           |           | Upper Mide | ile Byte  |           |           |           |

| 23        | 22        | · 21      | 20         | 19        | 18        | 17        | 16        |

| undefined | undefined | undefined | undefined  | undefined | undefined | undefined | undefined |

|           |           |           |            |           |           |           |           |

|           |           |           | Lower Mide | dle Byte  |           |           |           |

| 15        | 14        | 13        | 12         | 11        | 10        | 9         | 8         |

| undefined | undefined | undefined | undefined  | undefined | undefined | undefined | undefined |

|           |           |           |            |           |           |           |           |

|           |           | 1         | Lower I    | Byte      |           |           |           |

| 7         | 6         | 5         | 4          | 3         | 2         | 1         | 0         |

| undefined | undefined | undefined | undefined  | undefined | undefined | undefined | undefined |

|           |           |           |            |           |           |           |           |

Table 11External CPU to HOST Interrupt Request Register

## HOST INT

The HOST INTerrupt triggers an EX\_CPU to HOST interrupt request. This is an address and data triggered command. If this bit is set to a logic "1", an interrupt request is sent to the HOST through the interrupt control block. (channel 7 of the MFP). If a read of this bit is attempted, there is no guarantee that this bit is either a logic "0" or logic "1".

## 1.9 Shared Memory Requirements for LAPD Interface

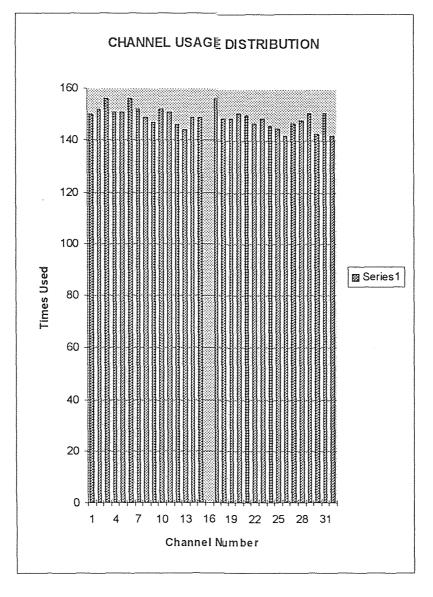

## 1.9.1 Calculation of Memory Requirement