# **Copyright Warning & Restrictions**

The copyright law of the United States (Title 17, United States Code) governs the making of photocopies or other reproductions of copyrighted material.

Under certain conditions specified in the law, libraries and archives are authorized to furnish a photocopy or other reproduction. One of these specified conditions is that the photocopy or reproduction is not to be "used for any purpose other than private study, scholarship, or research." If a, user makes a request for, or later uses, a photocopy or reproduction for purposes in excess of "fair use" that user may be liable for copyright infringement,

This institution reserves the right to refuse to accept a copying order if, in its judgment, fulfillment of the order would involve violation of copyright law.

Please Note: The author retains the copyright while the New Jersey Institute of Technology reserves the right to distribute this thesis or dissertation

Printing note: If you do not wish to print this page, then select "Pages from: first page # to: last page #" on the print dialog screen

The Van Houten library has removed some of the personal information and all signatures from the approval page and biographical sketches of theses and dissertations in order to protect the identity of NJIT graduates and faculty.

## **ABSTRACT**

# PERFORMANCE EVALUATION AND SEQUENCE CONTROL OF AN AUTOMATED MANUFACTURING SYSTEM

# by Vijaykumar D. Desai

In an automated sequential manufacturing system Programmable Logic Controllers (PLC) are widely used. As the control specification varies, the control software needs to be rewritten to accommodate the new specification. Since PLC has high flexibility, one can update the current system while it is running thereby making easier implementation. In order to design flexible, reusable and maintainable control software, a good modeling tool is required. Petri nets are such a tool. Which facilitates analysis of behavioral properties, performance evaluation, and systematic construction of discrete event simulators and controllers. In this thesis a system with one robot and five sequential work stations is used as an example of an automated system. To illustrate the Petri net method, performance and other properties of this system are evaluated. The PLC program is also developed for sequence control of the system.

# PERFORMANCE EVALUATION AND SEQUENCE CONTROL OF AN AUTOMATED MANUFACTURING SYSTEM

by Vijaykumar D. Desai

A Thesis

Submitted to the Faculty of

New Jersey Institute of Technology

in Partial Fulfillment of the Requirements for the Degree of

Master of Science in Electrical Engineering

Department of Electrical and Computer Engineering

January 1995

#### APPROVAL PAGE

# PERFORMANCE EVALUATION AND SEQUENCE CONTROL OF AN AUTOMATED MANUFACTURING SYSTEM

# Vijaykumar D. Desai

Dr. MengChu Zhou, Thesis Advisor

Assistant Professor

Department of Electrical and Computer Engineering, NJIT

Dr. Anthony Robbi, Committee Member

Associate Professor

Department of Electrical and Computer Engineering, NJIT

Dr. Marshall Kuo, Committee Member

Professor

Department of Electrical and Computer Engineering, NJIT

## BIOGRAPHICAL SKETCH

Author: Vijaykumar D. Desai

Degree: Master of Science in Electrical Engineering

Date: January 1995

# Undergraduate and Graduate Education:

- Master of Science in Electrical Engineering,

New Jersey Institute of Technology, Newark, NJ, 1995

- Bachelor of Science in Electrical Engineering, New Jersey Institute of Technology, Newark, NJ, 1984

Major: Electrical Engineering

This thesis is dedicated to my family

# **ACKNOWLEDGMENT**

I wish to express my sincere thanks to Dr. Zhou for his guidance and encouragement throughout the progress of this thesis. Special thanks to Dr. Robbi and Dr. Kuo for serving as members of the committee.

# TABLE OF CONTENTS

| Chapter                                  | Page |

|------------------------------------------|------|

| 1 INTRODUCTION                           | . 1  |

| 2 THEORY OF PETRI NETS                   | 3    |

| 2.1 Introduction to Petri Nets           | 3    |

| 2.2 Application of Petri Nets            | 3    |

| 2.3 Description of Petri Nets            | 4    |

| 2.4 Behavioral Properties of Petri Nets  | 9    |

| 2.4.1 Reachability                       | . 9  |

| 2.4.2 Boundedness                        | . 9  |

| 2.4.3 Liveness                           | . 9  |

| 2.4.4 Reversibility                      | 11   |

| 2.4.5 Consistency                        | 11   |

| 2.4.6 Persistence                        | 11   |

| 2.5 Analysis Methods                     | 11   |

| 3 DEVELOPMENT OF A MODEL                 | 18   |

| 3.1 System Description                   | 18   |

| 3.2 Building Graphical Model             | 23   |

| 4 PERFORMANCE EVALUATION OF THE SYSTEM   | 28   |

| 4.1 Software Packages                    | 28   |

| 4.2 Requirements and Terminology of SPNP | 29   |

# TABLE OF CONTENTS (Continued)

| Chapter                                                                                             | Page         |

|-----------------------------------------------------------------------------------------------------|--------------|

| 4.3 Performance Analysis of the System                                                              | . 37         |

| 5 CONTROL OF THE SYSTEM USING PLC                                                                   | . 43         |

| 5.1 History of PLC                                                                                  | . 43         |

| 5.2 Description of PLC                                                                              | . 44         |

| 5.3 Description of Basics of Ladder Diagram                                                         | . 46         |

| 5.4 Ladder Logic Program for the System                                                             | . 49         |

| 5.4.1 Ladder Logic Program for S1 Module                                                            | . 49         |

| 5.4.2 Ladder Logic Program for S1 Failure Module                                                    | . 51         |

| 5.5 Ladder Logic Program for the System                                                             | 52           |

| 6 CONCLUSION                                                                                        | . 55         |

| APPENDIX A SPNP Program of the Illustrative Example                                                 | . 56         |

| APPENDIX B SPNP Program of Five Sequence Work Station System                                        | . 59         |

| APPENDIX C Output files of S4 in a Five Sequence Work Station System as Shown in Figure 3.1 and 3.4 | . 69         |

| APPENDIX D PLC Ladder Logic Program of S1 in a Five Sequence work Station System                    | . <b>7</b> 9 |

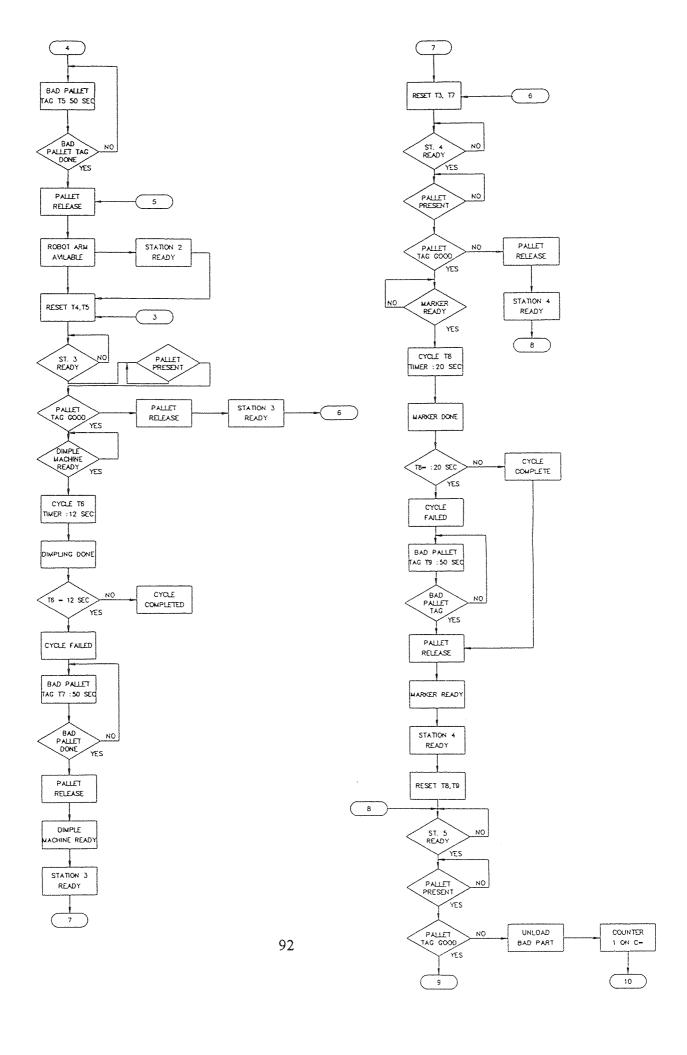

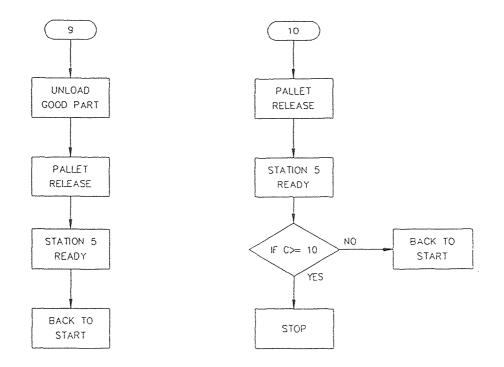

| APPENDIX E Flow Chart of Five Sequence Work Station System for Ladder Logic Program                 | . 91         |

| REFERENCES                                                                                          | . 94         |

# LIST OF TABLES

| 11 2 | able P                                                                 | age  |

|------|------------------------------------------------------------------------|------|

| 1    | Place Designations of Illustrative Example                             | 6    |

| 2    | Place Designations for SPNP Program                                    | 21   |

| 3    | Place Designations for S1 Module                                       | 24   |

| 4    | Place Designations for S1 Failure Module                               | 27   |

| 5    | Terminologies for SPNP Software                                        | 30   |

| 6    | ".rg" File of Illustrative Example                                     | 31   |

| 7    | ".mc" File of Illustrative Example                                     | 33   |

| 8    | ".prb" File of Illustrative Example                                    | 34   |

| 9    | ".log" File of Illustrative Example                                    | 34   |

| 10   | ".out" File of Illustrative Example                                    | 35   |

| 1]   | System Production rate and Utilization of S4 for failure rate at 1%    | 39   |

| 12   | 2 System Production rate and Utilization of S4 for failure rate at 10% | 40   |

| 13   | 3 System Production rate and Utilization of S4 for failure rate at 30% | 41   |

| 14   | 4 Main Menu                                                            | . 53 |

# LIST OF FIGURES

| Figure                                                                                          | age |

|-------------------------------------------------------------------------------------------------|-----|

| 2.1 Deadlock free Petri Net Model of Illustrative Example                                       | 7   |

| 2.2 Deadlock Occurs when in Initial Marking Number of Token in p1 > p7 in  Illustrative Example | 7   |

| 2.3 Reachability Tree for the Illustrative Example                                              | 14  |

| 3.1 Five Sequence Work Station System                                                           | 22  |

| 3.2 Station Module of Petri Net Model                                                           | 25  |

| 3.3 Station Failure Module of Petri Net Model                                                   | 25  |

| 3.4 Petri Net Model of Five Sequence Work Station                                               | 26  |

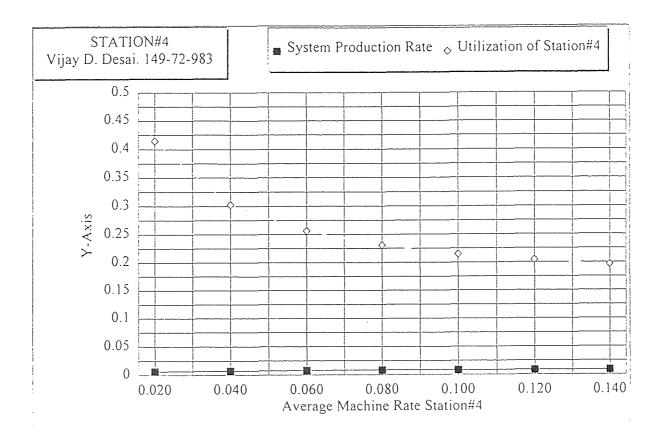

| 4.1 System Production rate and Utilization of S4 for failure rate at 1%                         | 39  |

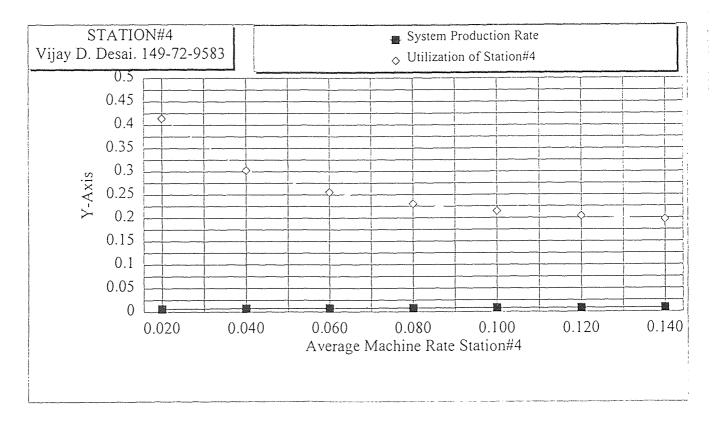

| 4.2 System Production rate and Utilization of S4 for failure rate at 10%                        | 40  |

| 4.3 System Production rate and Utilization of S4 for failure rate at 30%                        | 41  |

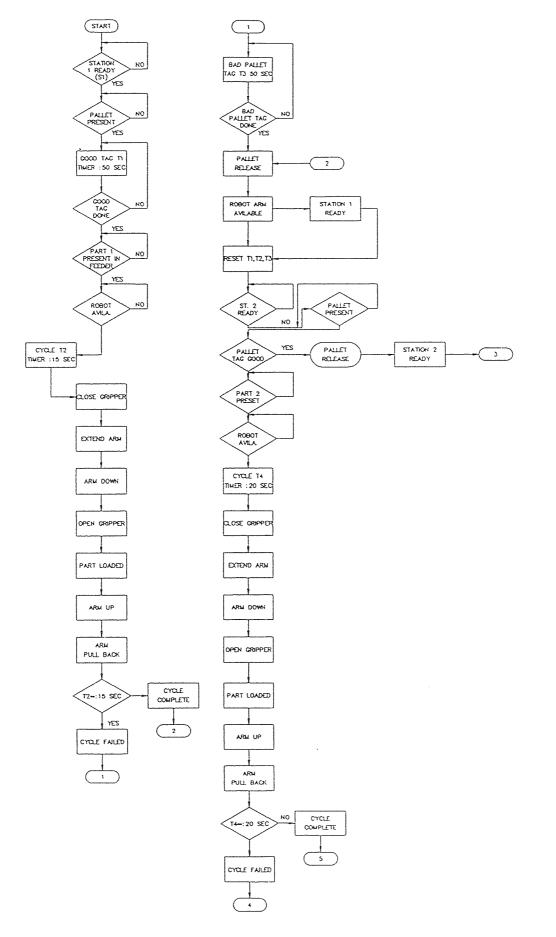

| 5.1 Flow Chart of Five Sequence Work Station System for Ladder Logic Program                    | 50  |

#### CHAPTER 1

#### INTRODUCTION

Development of a software is dependent on the model it is based on. Petri nets have been extensively used in software development [20]. One of the major advantage of using Petri nets is that the same model is used for the analysis of behavioral properties and performance evaluation.

Petri nets were successfully applied for sequence control. Petri net based sequence controllers are easy to design, implement, and maintain. In the early 80's, Hitachi Ltd. developed a Petri net based sequence controller [16] which was successfully used in real manufacturing applications to control parts assembly systems, and automatic warehouse load/unload system [17]. The use of Petri nets substantially reduced the development time compared with traditional approach. Numerous approaches to synthesis and implementation of Petri net based sequence controllers have been reported in the past few years [4].

Programmable Logic Controllers are commonly used for the sequence control in automated systems. They can be designed using ladder logic diagrams, which are known to be very difficult to debug. Since ladder diagrams are widely used in the industries for hardwired logic circuits, they became a standard way of providing control information from the designers to the users of equipment. When programmable controllers were introduced, this type of circuits was desirable because they were easy to use and interpret for practicing engineers.

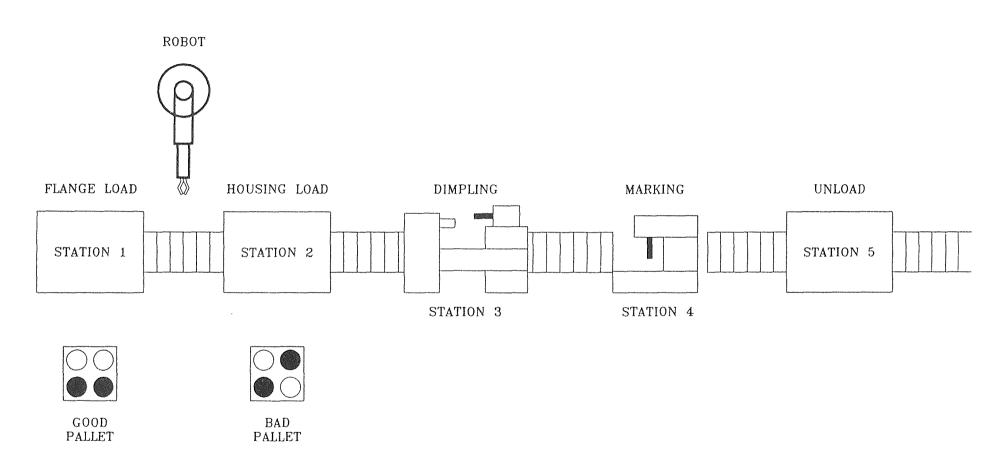

In this thesis, a system consisting of five work stations and a shared resource (robot) is used to show how a Petri net model can be developed for performance evaluation and a PLC Program is developed for sequence control. Stations 1 and 2 are loading machines for two different parts via a same robot, Station 3 is a dimpling machine, Station 4 is a marking machine and Station 5 is unloading machine which unloads and separates finished and unfinished goods. Unfinished goods may result due to failure of any work stations. This process can be extended to any number of work stations. Performance evaluation and behavior properties are also studied. Ladder Logic Programs are finally developed to implement a PLC for the system.

#### CHAPTER 2

#### THEORY of PETRI NETS

#### 2.1 Introduction to Petri Nets

In 1962 Carl A. Petri created a net like mathematical tool for the study of communication with automata. The resulting tool was named as Petri nets. Petri net methodology utilizes both mathematical and graphical representations.

Changing control specifications can be easily implemented using such a graphical tool. As mathematical models petri nets reflect behavior of the system. The performance evaluation can be conducted by using either analytical techniques, based on the underlying (semi)-markov processes or discrete event simulation. By incorporating time functions that follow probabilistic distributions to transitions, one can obtain production rates for manufacturing system models, throughput, critical resource utilization and reliability measures.

Some of the most fundamental properties of Petri nets are reachability, boundedness, liveness, reversibility, consistency and persistence as given later in Section 2.4.

#### 2.2 Application of Petri Nets

Petri nets (PN's) were successfully used in modeling and analysis of communication protocols [3]. PN's are also applied to the modeling of Just-in-Time manufacturing

systems [22]. They are also widely used in flexible manufacturing systems due to their ability to model asynchronous operations, concurrence, deadlock, conflicting events, and event-driven systems [11]. PN's can be used from design through evaluation to control. It is possible to compile the net into control code data for implementation and execution on the shop floor [24]. Petri nets also inspired GRAFCET for the application to finite state automation processes, which became standard for specifying sequence control in France in 1977 [22], and later became an international standard called Sequential Function Charts. Since then more research and developments are done using Petri nets in various applications for automated manufacturing systems. A bibliography of Petri nets [19], published in 1991, contains 4099 entries dealing with Petri net theory and applications.

# 2.3 Description of Petri Nets

A Petri net can be identified by its graph in which there are three types of objects. They are places, transitions, and tokens. Directed arcs connect transitions to places and places to transitions. A place (P) can be shown as a circle, a transition (T) as bar or box and a token as a dot inside the place. Input function (I) defines the directed arcs from places to transitions. Output function (O) defines the directed arcs from transitions to places. In a real system, a place represents status of a resource or an operation. A transition represents either start or completion of an event or process. A place with a token represents resource available or operation being executed.

A marked Petri net is defined as  $Z = (P, T, I, O, m_0)$ . P is a finite set of places  $\{p_1, p_2, ..., p_n\}$ . T is a finite set of transitions  $\{t_1, t_2, ..., t_s\}$  with the following condition,

$P \cup T \neq \emptyset$  and  $P \cap T = \emptyset$ . Input function (I) defines  $(P \times T) \mapsto N$  and Output function (O) define as  $(P \times T) \mapsto N$ , where N is a set of non-negative integers. If there exist k directed arcs connecting place p to transition t, I(p,t)=k or O(p,t)=k, which graphically represented by a single arc with multiplicity, or weight k.  $m_0$ :  $(P \mapsto N)$  is an initial marking of places. A marking defines current status of the model system. A transition is enabled when each input place p of t contains at least the number of tokens equal to weight k of the directed arc connecting p to t. When a transition, t, is enabled, it may be fired. If fired it removes from each input place p the number of tokens equal to the weight of directed arc connecting p to t. Also, it deposits in each output place p the number of tokens equal to the weight of the directed arc connecting t to p.

The mathematical representation of a PN consists of two matrices. The input matrix, I, is derived from the Petri net graphical representation. The input matrix is an (n × s) matrix where n is the number of places and s is the number of transitions. The entries in the input matrix correspond to the weights of the input arcs from places (row) to transitions (column). Similarly, the output matrix, O, is an (n × s) matrix. The entries in the output matrix correspond to the weights of the output arcs from transitions (column) to places (row). Incidence matrix, C, describes the dynamic characteristics of the system and is equal to the difference between the output and input matrices, O - I. This matrix represents the change in tokens of places when transitions fire. Negative (positive) numbers in the incidence matrix signify the consumption (creation) of tokens. The state or marking of a Petri net denotes the number of tokens occupying each place and is captured in one dimension matrix of size n.

To illustrate how Petri nets can be used to model, we consider the following example of Robot #1, Machine #1 and a buffer with limited capacity. Machine #1 acquires Robot #1 and loads parts using Robot #1, then processes it. Finished parts are unloaded into buffer automatically when it is available. The buffer is of limited capacity. When the robot is available, it unloads finished parts into storage from the buffer and the cycle continues.

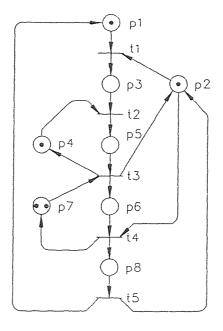

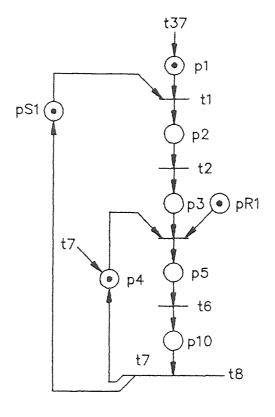

The net is shown in Figure 2.1 and its places are described in Table 1.

Table 1 Place Designations of Illustrative Example

| P <sub>1</sub> | Machine #1 (M1)    | p <sub>5</sub>        | M1 process using R1    |  |

|----------------|--------------------|-----------------------|------------------------|--|

| p <sub>2</sub> | Robot #1 (R1)      | p <sub>6</sub> Buffer |                        |  |

| p <sub>3</sub> | M1 acquire R1      | P <sub>7</sub>        | Buffer capacity        |  |

| p <sub>4</sub> | Raw Material /Part | p <sub>8</sub>        | Unload buffer using R1 |  |

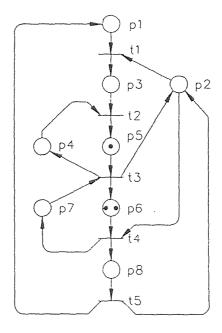

In this example the robot is shared by M1 for loading and by the buffer for unloading. Since the buffer has limited capacity, M1 does not continuously produce finished parts until the buffer is unloaded by R1. Assume that initial marking is  $m_0 = (3,1,0,1,0,0,2,0)$ , where  $p_1$  has more tokens than buffer capacity  $p_7$ . Then deadlock

FIGURE 2.1- DEADLOCK FREE PETRI NET MODEL OF ILLUSTRATIVE EXAMPLE

FIGURE 2.2-DEADLOCK OCCURS WHEN NUMBER OF TOKEN IN INITIAL MARKING IN p1 IS GREATER THAN p7 IN ILLUSTRATIVE EXAMPLE

will be reached if firing sequence  $t_1, t_2, t_3, t_1, t_2, t_3, t_1, t_2$  occurs. At this time  $(0,0,0,0,1,2,0,0)^T$  marking is reached, as shown in Figure 2.2. Since  $p_7$  does not have a token,  $t_3$  is unable to fire. And also, since  $p_2$  does not have a token, and  $t_4$  is unable to fire. To avoid this  $p_1$  should have less than buffer capacity tokens or a mechanism by which when the buffer is full the robot must unload the buffer before the M1 uses the robot to produce next part. This is a Sequential Mutual Exclusion in which there is a shared resource [22]. This shows that one should verify deadlock condition, especially when there are shared resources present in the system. One of the advantages of Petri net models is that one can analyze some of the properties related to a manufacturing process. They can be behavioral, structural, qualitative properties and logical correctness.

The input matrix I, output matrix O and incidence matrix C for the illustrative example considered are as follows:

$$I = \begin{bmatrix} 1 & 0 & 0 & 0 & 0 \\ 1 & 0 & 0 & 1 & 0 \\ 0 & 1 & 0 & 0 & 0 \\ 0 & 0 & 1 & 0 & 0 \\ 0 & 0 & 1 & 0 & 0 \\ 0 & 0 & 1 & 0 & 0 \\ 0 & 0 & 1 & 0 & 0 \\ 0 & 0 & 0 & 1 \end{bmatrix} \qquad O = \begin{bmatrix} 0 & 0 & 0 & 0 & 1 \\ 0 & 0 & 1 & 0 & 1 \\ 1 & 0 & 0 & 0 & 0 \\ 0 & 0 & 1 & 0 & 0 \\ 0 & 0 & 1 & 0 & 0 \\ 0 & 0 & 0 & 1 & 0 \\ 0 & 0 & 0 & 1 & 0 \end{bmatrix} \qquad C = \begin{bmatrix} -1 & 0 & 0 & 0 & 1 \\ -1 & 0 & 1 & -1 & 1 \\ 1 & -1 & 0 & 0 & 0 \\ 0 & 1 & -1 & 0 & 0 \\ 0 & 0 & 1 & -1 & 0 \\ 0 & 0 & 0 & 1 & -1 \end{bmatrix}$$

The behavioral properties depend on initial marking and its significance in manufacturing process is defined as below.

#### 2.4 Behavioral Properties of Petri Net

# 2.4.1 Reachability

The reachability set  $R(m_0)$  of a Petri net, is defined as the set of all markings which are obtainable from the initial marking  $m_0$ , through some firing sequence  $L(m_0)$  [18]. This means that a system can reach a specific state, or particular functional behavior. This can be verified by finding a sequence of transition firings which would result in transforming a marking  $m_0$  to  $m_i$ .  $m_i$  represents a specific state, and the sequence of firings represents the required functioned behavior. Thus the problem of identifying the existence of a specific state  $m_i$ , of the system can be redefined as the problem of finding if  $m_i \in R(m_0)$ .

#### 2.4.2 Boundedness

A PN is said to be k-bounded for any reachable marking, m, none of the places contains more than k (k is a nonnegative integer number) tokens. A 1-bounded Petri nets is called safe [18]. In manufacturing, boundedness implies to the absence of capacity overflows. Safeness of an operation place, guarantees that there is no attempt to request execution of an ongoing process. If a resource place is safe, it implies only one available resource.

#### 2.4.3 Liveness

There are five degrees of liveness, L0-L4. They are defined with respect to a single transition as follows [18]:

- L0 "dead" if t can never be fired in any sequence of  $L(m_0)$ .

- Ll "potentially firable" if t can be fired at least once in some

- firing sequence L(m<sub>0</sub>).

- L2 given any positive integer k, t can be fired at least k times in some firing sequence  $L(m_0)$ .

- L3 if t appears infinitely often in some firing sequence  $L(m_0)$ .

- L4 "live" if t is L1-live for every marking, m, in  $R(m_0)$ .

A PN is said to be "live" if all transitions in the net are L4-live. A live PN is one which cannot be deadlocked. This property guarantees that a system can successfully produce and all modeled processes can occur. Coffman at. al. [10] showed that four conditions must hold for a deadlock to occur. These four conditions are:

- 1. Mutual exclusion: a resource is either available or allocated to a process which has an exclusive access to this resource [21].

- Hold and Wait: a process is allowed to hold a resource(s) while requesting more resources.

- 3. No preemption: a resource(s) allocated to a process cannot be removed from the process, until it is released by the process itself.

- 4. Circular wait: two or more processes are arranged in a chain in which each process waits for resources held by the process next in the chain.

In the illustrative example shown in Figure 2.2, deadlock can be reached when  $m_0(p_1)$  is greater than  $m_0(p_7)$ . It can be shown that all four conditions of deadlock hold.

### 2.4.4 Reversibility

A reversible PN is one that can always return to a home state via some firing sequence in  $L(m_n)$ . The home state is usually, but not necessarily, the initial state [18]. This property in manufacturing means the system can be initialized from any reachable state.

### 2.4.5 Consistency

A Petri net is said to be (partially) consistent if there exists a marking  $m_0$  and a firing sequence  $L(m_0)$  returning to  $m_0$  such that every (some) transition appears at least once in  $L(m_0)$  [18]. Reversibility implies consistency, but consistency does not necessarily imply reversibility. In manufacturing, this means that cyclic activities exist.

#### 2.4.6 Persistence

A PN is considered to be persistent if firing of any enabled transition does not disable previously enabled transition [18]. In shared resource allocation a persistent net model implies that there is no conflict among processes.

#### 2.5 Analysis Methods

Once the Petri net model is formulated, it must be analyzed to show that it does meet customer requirements and all inputs and outputs are considered. The fundamental methods of analysis are based on the reachability tree and matrix equation representation of a net. Also, a systematic transformation of a Petri net can be done, by reducing the number of places and transitions in a net, and at the same time preserving the properties

such as boundedness, conservativeness, liveness, etc. Some of these techniques were discussed in [18].

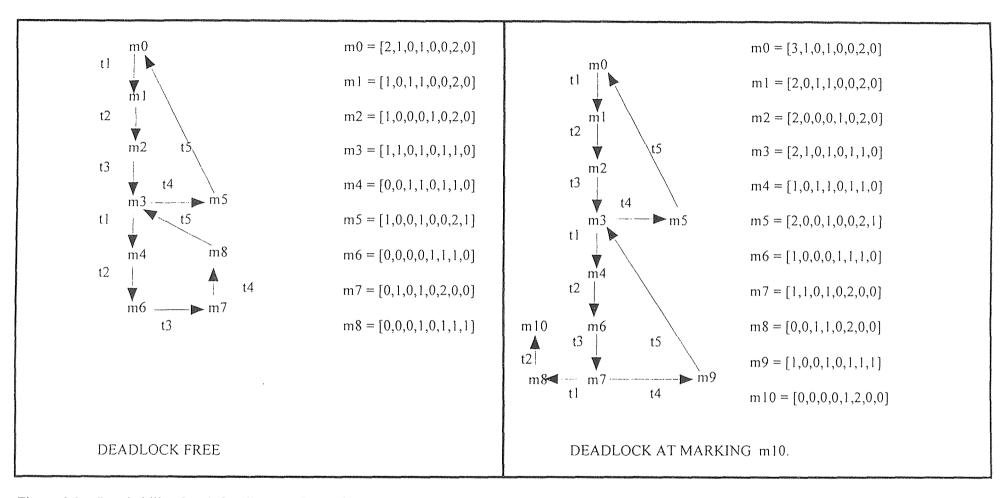

From the definition of the reachability tree the following observation can be made for the illustrative example when an initial marking is  $m_0 = (2,1,0,1,0,0,2,0)^T$  [26]. In this marking transition  $t_1$  is enabled. When  $t_1$  fires a new marking is obtained;  $m_1 =$  $(1,0,1,1,0,0,2,0)^T$ . This is a "new" marking in which transition  $t_2$  is enabled. Firing  $t_2$  in  $m_1$  results in  $m_2 = (1,0,0,0,1,0,2,0)^T$ . This is a "new" marking in which transition  $t_3$  is enabled and m<sub>1</sub> becomes an "old" marking. Firing t<sub>3</sub> in m<sub>2</sub> results in m<sub>3</sub> =  $(1,1,0,1,0,1,1,0)^{1}$ . This is a "new" marking in which transitions  $t_4$  and  $t_1$  are enabled and  $m_2$  becomes an "old" marking. Firing  $t_4$  in  $m_3$  results in  $m_5 = (1,0,0,1,0,0,2,1)^T$ . This is a "new" marking in which t<sub>5</sub> is enabled and m<sub>3</sub> becomes an "old" marking. Firing t<sub>5</sub> in m<sub>5</sub> results in  $m_0$  which is an "old" marking. At  $m_3$  firing  $t_1$  results in  $m_4 = (0,0,1,1,0,1,1,0)^T$ . This is a "new" marking in which  $t_2$  is enabled. Firing  $t_2$  in  $m_4$  results in  $m_6$  =  $(0,0,0,0,1,1,1,0)^T$ . This is a "new" marking in which transition  $t_3$  is enabled and  $m_4$ becomes an "old" marking. Firing  $t_3$  in  $m_6$  results in  $m_7 = (0,1,0,1,0,2,0,0)^T$ . This is a "new" marking in which t4 is enabled and m6 becomes an "old" marking. Firing t4 in m7 results in  $m_8 = (0,0,0,1,0,1,1,1)^T$ . This is a "new" marking in which transition t<sub>5</sub> is enabled and m<sub>7</sub> becomes an "old" marking. Firing t<sub>5</sub> in m<sub>8</sub> results in m<sub>3</sub> which is an "old" marking. Figure 2.3 shows reachability trees for deadlock free and deadlock of the illustrative example under different marking when m<sub>0</sub>(p<sub>1</sub>) is greater than m<sub>0</sub>(p<sub>7</sub>) such as  $m_0 = (2,1,0,1,0,0,2,0)^T$  and  $m_0 = (3,1,0,1,0,0,2,0)^T$  respectively.

A number of properties can be studied by using reachability tree. If each branch of tree contains only zeros and ones, then the net is safe. A transition is dead if it does not appear as an arc label in the tree. In this system all transitions are L2-Live for the above two initial marking, since it is possible to fire any transition at least k times in some firing sequence  $L(m_0)$ . Finally, reversibility property can also be observed by inspection that  $m_0$  is reachable from any marking  $m \in R(m_0)$  for  $m_0 = (2,1,0,1,0,0,2,0)^T$ . This also implies consistency. This net is not persistent since at  $m_3$  in Figure 2.3 firing  $t_1$  disable  $t_4$ .

The ordinary Petri nets do not include any concept of time. With this class of nets, it is possible only to describe the logical structure of the modeled system, but not its time evolution. Responding to the need for the temporal performance analysis of discrete-event systems, time has been introduced into Petri nets in a variety of ways. There are two fundamental types of timed Petri nets in the context of performance evaluation. These are Deterministic timed Petri nets, and Stochastic timed Petri nets.

When time delays are modeled as random variables, or probabilistic distributions are added to the transitions of deterministic timed Petri nets models for the conflict resolution, stochastic timed Petri nets models are yielded. In such models, it has become a convention to associate time delays with the transition only. When the random variables are of general distribution or both deterministic and random variables are involved, the resulting net models cannot be solved analytically for general cases. Thus simulation or approximation methods are required. The stochastic timed Petri nets in which the time delay for each transition is assumed to be stochastic and exponentially

Figure 2.3 Reachability Graph for Illustrate Example

distributed are called stochastic Petri nets (SPN) [15]. The SPN models which allow for immediate transitions, i.e., with zero time delay, are called generalized SPN (GSPN) [14]. Both models include extensions such as priority transitions, inhibitor arcs, and probabilistic arcs. These models can be converted into their equivalent Markov process representations, and analyzed analytically.

A conflict results when a place has two or more output transition and only one transition can be fire, others become disabled. When a conflict results, it has to be resolved by a mechanism, such as associating priority to transitions. Since this mechanism leads to stochastic nets the use of the deterministic timed Petri nets for performance evaluation has been restricted to the choice-free nets, which can be modeled as marked graphs [6,26].

The continuous time Markov chain is a state machine whose nodes are states or markings and links are labeled to the corresponding transitions. In a continuous time Markov chain transition rate  $a_{ij}$  is the rate of a process from state i to state j, i  $\neq$  j.  $a_{ii}$  is determined by

$$\sum_{j=1}^{m} a_{ij} = 0$$

Given the present state  $m_i$ , the conditional probability that  $m_i$  goes to  $m_j$  during time interval dt is  $a_{ij}$  dt. Also,  $1/a_{ij}$  is the expected time between i and j. From the above definition transition rate matrix

$$A = \begin{bmatrix} a_{11} & a_{12} & \cdots & a_{1m} \\ a_{21} & a_{22} & \cdots & \vdots \\ \vdots & \vdots & \ddots & \vdots \\ a_{m1} & a_{m2} & \cdots & a_{mm} \end{bmatrix}$$

Let  $\pi$  be a row vector of steady state probabilities. Then, it satisfies:

$$\pi * A = 0 \tag{1}$$

$$\sum_{i=1}^{\infty} \pi_i = 1 \tag{2}$$

For example, the transition rate matrix for the illustrative example shown in Figure 2.1 with the initial marking  $m_0 = (2,1,0,1,0,0,2y0)$  is

$$A = \begin{bmatrix} -\lambda_1 & \lambda_1 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 \\ 0 & -\lambda_2 & \lambda_2 & 0 & 0 & 0 & 0 & 0 & 0 & 0 \\ 0 & 0 & -\lambda_3 & \lambda_3 & 0 & 0 & 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & (-\lambda_4 - \lambda_5) & \lambda_4 & \lambda_5 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 & -\lambda_6 & 0 & \lambda_6 & 0 & 0 \\ \lambda_{10} & 0 & 0 & 0 & 0 & -\lambda_{10} & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 & 0 & 0 & -\lambda_7 & \lambda_7 & 0 \\ 0 & 0 & 0 & 0 & 0 & 0 & 0 & -\lambda_8 & \lambda_8 \\ 0 & 0 & 0 & \lambda_9 & 0 & 0 & 0 & 0 & -\lambda_9 \end{bmatrix}$$

By solving equations (1) and (2) steady state probabilities of the process can be solved.

To study performance using SPN the following steps are involved.

- 1. Develop a stochastic Petri net model of a system. Define the initial state, and obtain the corresponding marking;

- 2. Generate the reachability graph of the net, and obtain the set of Markov process;

- 3. Perform the analysis of the Markov model, and;

- 4. Convert the analysis results into the required performance measures.

In this thesis SPN is used for performance evaluation as given above using SPNP software.

#### CHAPTER 3

#### DEVELOPMENT OF A MODEL

To show how Petri net models can be used in performance analysis, a five sequenced work station model is used. This process can be extended into a larger system.

#### 3.1 System Description

Assume that previously sub-assembled parts are automatically loaded on to pallets and then pallets enter the system one by one. When station #1 (S1) is available the pallet is loaded on to S1. The specification of the process is as follows:

- Step 1: The pallet is marked good at S1 within time given by timer T1.

- Step 2: S1 acquires robot (R) and then the timer T2 starts. Using R, part #1 is loaded on sub-assembled part.

- Step 3: If within given amount of time given by timer T2 S1 failed to load part #1 using R the pallet is marked bad within time given by timer T3 and robot (R) is released. The pallet is released when S2 is available.

- Step 4: S2 also verifies that the pallet is marked good or bad, before it acquires R to load part #2.

- Step 5: If the pallet is marked bad S2 releases the pallet, when S3 is available.

- Step 6: If the pallet is marked good, S2 acquires the robot (R) when available to load part #2, then the timer T4 starts.

Step 7: If S2 fails to load part #2 using R in a given amount of time by timer T4 then the pallet is marked bad at S2 within time given by timer T5. The R and pallet is released when S3 is available.

Step 8: Before S3 starts it process, it also, verifies either the pallet is marked good or bad.

If the pallet is marked bad it releases the pallet when S4 is available.

Step 9: At S3 there is s dimpling machine, If the pallet is marked good, timer T6 starts.

At S3, using dimpling machine loaded part is dimpled and locked in its place.

Step 10: If Within give amount of time, S3 does not complete its job using dimpling machine, the pallet is marked bad within time given by timer T7 and dimpling machine and the pallet are released when S4 is available.

Step 11: As before S4 verifies if received pallet is good or bad, i.e., previous stations have completed their job or not. So, again if the pallet is marked bad it releases the pallet when S5 is available.

Step 12: At S4 there is a marker machine which for example marks part number and/or date code etc. If the pallet is good S4 using the marker marks the finished product within given amount of time by timer T8. When the job is completed, the pallet and marker are released when S5 is available.

Step 13: If S4 fails, the pallet is marked bad within time given by timer T9.

Step 14: Finally S5 unloads the pallet with a part marked good or bad. At S5 the pallet is verified. If it is marked good, it means that all stations have finished their jobs and finished goods enters the storage or into next stage of production. The verification and unloading of the pallet are done automatically at S5.

Step 15: Finally the pallet is released into the cycle back to S1 when it is available and cycle continues. See Figure 3.1 of a five sequenced work station system.

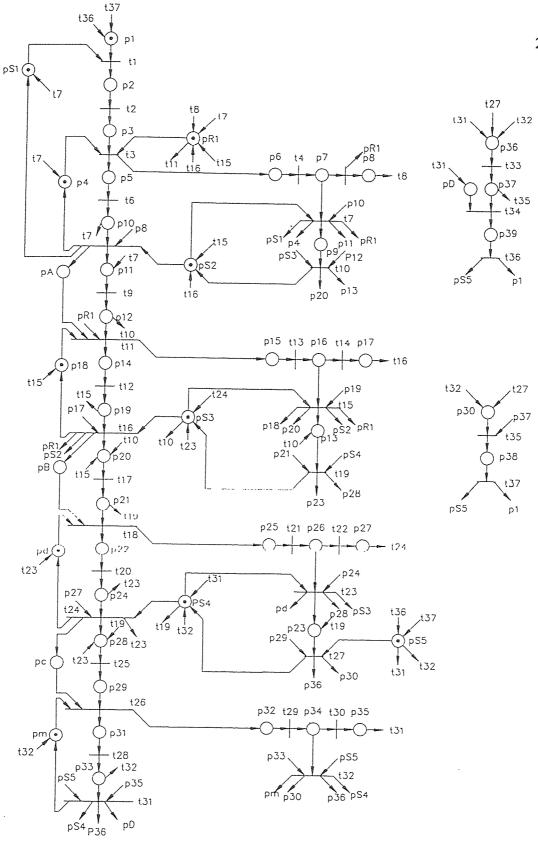

In this example stations are in sequence and the pallet is not taken out of cycle if job is failed at one station. But each station receives pallet and each of them verifies if pallet is marked good or bad before it continues with its required job. At the unloading station S5, there can be a counter to count how many pallets are good or bad for the efficiency of stations. Also, at each station one can have counter to count consecutive job failed. When the counter accumulative value equals to the preset value it shut down the station and operator is warned. The station is reset with an operator key. The unfinished product can be returned into the system for reprocessing, depending on which station has failed. The Petri net model is shown in Figure 3.4 and place designations in Table 2.

Table 2 Place Designations for SPNP program.

| p <sub>1</sub>  | Start                   | p <sub>18</sub> | Part #2                   | p <sub>35</sub> | Process Completed      |

|-----------------|-------------------------|-----------------|---------------------------|-----------------|------------------------|

| p <sub>2</sub>  | Pallet Present S1       | P <sub>19</sub> | Part#2 Load Using<br>R1   | p <sub>36</sub> | Pallet Present S5      |

| p <sub>3</sub>  | Pallet Tag Good         | p <sub>20</sub> | Pallet Present S3         | p <sub>37</sub> | Pallet Check S5        |

| p <sub>4</sub>  | Part #1                 | p <sub>21</sub> | Pallet Check S3           | P <sub>38</sub> | Bad Pallet Unload      |

| <b>p</b> ₅      | Ready to Load part #1   | p <sub>22</sub> | Good Pallet<br>Present S3 | p <sub>39</sub> | Good Pallet<br>Unload  |

| p <sub>6</sub>  | Timer S1                | p <sub>23</sub> | Bad Pallet S3             | p <sub>A</sub>  | Good Pallet from S1    |

| p <sub>7</sub>  | Wait state              | p <sub>24</sub> | Dimpling Done at S3       | рв              | Good Pallet from S2    |

| p <sub>8</sub>  | Process completed at S1 | p <sub>25</sub> | Timer S3                  | p <sub>C</sub>  | Good Pallet from S3    |

| p,              | Process Fail at S1      | p <sub>26</sub> | Wait State                | $p_{D}$         | Good Pallet from<br>S4 |

| p <sub>10</sub> | Part #1 Load Using R1   | p <sub>27</sub> | Process Completed at S3   | $p_{s1}$        | Station #1 (S1)        |

| p <sub>11</sub> | Pallet Present S2       | p <sub>28</sub> | Pallet Present S4         | p <sub>s2</sub> | Station #2 (S2)        |

| p <sub>12</sub> | Pallet Check S2         | p <sub>29</sub> | Pallet Check S4           | p <sub>s3</sub> | Station #3 (S3)        |

| p <sub>13</sub> | Bad Pallet at S2        | p <sub>30</sub> | Bad Pallet at S4          | p <sub>s4</sub> | Station #4 (S4)        |

| p <sub>14</sub> | Good Pallet Present S2  | p <sub>31</sub> | Good Pallet<br>Present S4 | $p_{s5}$        | Station #5 (S5)        |

| p <sub>15</sub> | Timer S2                | p <sub>32</sub> | Timer S4                  | p <sub>m</sub>  | Marker(ex. P/N#)       |

| p <sub>16</sub> | Wait State              | p <sub>33</sub> | Marking Done At<br>S4     | $p_d$           | Dimpling Machine       |

| p <sub>17</sub> | Process Completed       | p <sub>34</sub> | Wait State                | $p_{R1}$        | Robot #1 (R1)          |

FIGURE 3.1- FIVE SEQUENCE WORK STATION SYSTEM

## 3.2 Building a Graphical Model

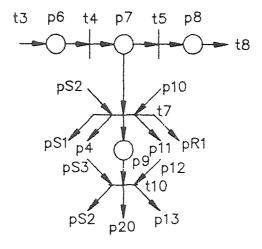

A five work station PN model is developed using a bottom-up modular approach. First, S1's process is developed then S2 - S5's. Next, the failure check module is developed for each work station. Later on five work station processes are linked in sequence. Finally, all the modules are linked to complete the system modeling. There are several different methods available to develop a graphical model given in [25].

The following method is used in the model development of the first station. Identify the processes being done at the first station. They are: a pallet being loaded into S1 and marked good, using the robot a part is loaded. For each process in order, create a place to represent its status and add a transition to show the start of a process and a transition to show the end of the process. They are connected with an output arc(s) and with an input arc(s), respectively.

For each kind of resource(s), create and label a place. If an activity place is a starting activity to require the resource(s), add input arc(s) from that resource place to the starting transition of that activity. If an activity is the ending activity to use the resource(s), add output arc(s) from the ending transition to the resource place(s). In the given system for station #1 resources are S1, robot, and part. For those resources places are  $p_{s1}$ ,  $p_{R1}$ , and  $p_{4}$  respectively. In Table 3 process places and resource places of S1 are given. Starting activities are a pallet at station #1, the pallet is marked good and using robot a part is loaded. The first activity requires S1, therefore, from  $p_{s1}$  an input arc is added to transition  $t_{1}$ .

Table 3 Place Designations for S1 Module.

| Places                | ces Processes                                        |          | Resources  |

|-----------------------|------------------------------------------------------|----------|------------|

| $p_1$                 | Pallet ready                                         | $p_{s1}$ | Station #1 |

| $p_2$                 | Pallet loaded to station 1                           | $p_{R1}$ | Robot      |

| p <sub>3</sub>        | p <sub>3</sub> Pallet marked good                    |          | Part       |

| <b>p</b> <sub>5</sub> | p <sub>5</sub> Robot is ready with part to be loaded |          |            |

| P <sub>10</sub>       | Part is being loaded                                 |          |            |

For the loading of a part using the robot an input arc is added to transition  $t_3$  from both resources places  $p_{R1}$  and  $p_4$ , respectively. Finally, the initial marking is specified.  $p_1$ ,  $p_{s1}$ ,  $p_{R1}$  and  $p_4$  are marked with one token. For example since initially a robot is available,  $m_0(p_{R1}) = 1$ . The Petri net module for the first station is shown in Figure 3.2. One difference between S1 and the other stations is that, a pallet is marked good at S1 but at the other stations a pallet is verified if it is good or bad.

Similarly, a failure check module is developed. The processes are: start timer, if timer is done, mark pallet bad else the process is completed. In this module resource(s) is not used. Therefore, only arc(s) are to show the flow of the process. Table 4 lists process places and Figure 3.3 shows the Petri net module for failure check.

Similarly, work stations S2 -S5 and their corresponding failure blocks are developed. Finally, all of them are linked to complete the system as shown in Figure 3.4 and place designation in Table 2. It is noted that links are based on the system description as given in Section 3.1.

FIGURE 3.2- STATION 1 MODULE OF PETRI NET MODEL

FIGURE 3.3-STATION 1 FAILURE MODULE OF PETRI NET MODEL

FIGURE 3.4- PETRI NET MODEL OF FIVE SEQUENCE WORK STATION

Table 4 Place Designations for S1 Failure module.

| Places         | Processes         |

|----------------|-------------------|

| P <sub>6</sub> | Timer start       |

| p <sub>7</sub> | Wait state        |

| p <sub>8</sub> | Process completed |

| p <sub>9</sub> | Pallet marked bad |

#### CHAPTER 4

#### PERFORMANCE EVALUATION OF THE SYSTEM

In order to evaluate the performance of the system, its PN model has to be analyzed. In this study SPNP software package is used for performance evaluation.

In order to run the model with the SPNP software a source code must be written. This code provides the necessary input and also generates certain output. The input consists of places along with their initial markings, transitions along with their firing rates, placement of input and outputs arcs, and any variables that the user intends to change from run to run; e.g., firing rates and failure rates.

#### 4.1 Software Packages

There are numerous software packages available for modeling and evaluating given systems. Some of the more popular packages used are SPNP, GRAMAN, SIMAN, SLAM, and SIMSCRIPT of these SIMAN, SLAM, and SIMSCRIPT are better suited for simulation. SPNP and GRAMAN were developed around and intended to be used for Petri nets. Beck and Krogh [13] have successfully utilized SIMAN to simulate their modified Petri nets models for manufacturing systems. Also, GreatSPN [8] software is powerful in the sense that it can accept various time variables, inhibitors, and random switches and has simulation capacity. SPNP (Stochastic Petri nets Package) developed by Ciardo [9] has been used by Al-Jaar and Desrochers [2] to investigate the performance

of transfer lines and production networks, also by Zhou and Leu [23] to evaluate the performance of two robotic manipulator assembly station for printed circuit boards. A UNIX based version of SPNP has been found to be appropriate tool to evaluate this five work station example. SPNP is written in C and is also available for VMS systems (VAX). The syntax and semantics are based on the C language.

### 4.2 Requirements and Terminology of SPNP

The SPNP software was used to execute the Petri nets model. Due to the complexity of the PN, the input matrix is large and occupies much memory during system execution. Also, when there are more than one pallet in the system, numerous markovian states result and hence the execution of the PN consumes much time. Hence, the model was run on SPNP with an initial marking with one token for pallet and part so that throughput and utilization of resources can be analyzed with SPNP. Example of input terminology for SPNP is described in Table 5. Details of the illustrative example and a five work stations system given in Appendix A and Appendix B respectively. Also, the output of SPNP program is given in Tables 6 - 10 and in Appendix C for the illustrative example and S4 in a five work station system, respectively.

Table 5 Terminologies for SPNP Software

| place("pl"); ** Establishes a place pl. **                                                                                                                                                                                                                                                                             |  |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| init("p1",1); ** Defines initial marking of p1 as 1. **                                                                                                                                                                                                                                                                |  |  |  |  |  |

| trans("t1"); ** Establishes a transition t1. **                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| iarc("pl","tl") ** Defines an input arc to tl from pl. **                                                                                                                                                                                                                                                              |  |  |  |  |  |

| oarc("pl","t2") ** Defines an output arc from t2 to pl. **                                                                                                                                                                                                                                                             |  |  |  |  |  |

| rateval("t1",1.0) ** Defines firing rate of t1 is 1.0. **                                                                                                                                                                                                                                                              |  |  |  |  |  |

| rateval("t2",x) ** Defines firing rate of t2 is variable x,which is entered at the beginning of the program run. **                                                                                                                                                                                                    |  |  |  |  |  |

| OUTPUT COMMANDS:  reward_type ef0() {return(rate("t1"));} /* throughput */ **  pr_expected("throughput,'t1' ",ef0);  Defines Expected throughput of transition t1. **  reward_type ef1() {return(1-mark("pR1"));}  pr_expected("utilization, 'pR1' ",ef1);  Defines Expected utilization of resources namely Robot #1. |  |  |  |  |  |

| OTHER OUTPUT FILES GENERATED BY SPNP SOFTWARE: iopt(IOP_PR_RSET,VAL_YES); If VAL_YES is specified, the program will print reachability set under ".rg" files. Which helps in analyzing deadlock marking(s) and other properties.                                                                                       |  |  |  |  |  |

#### Results of Evaluation

For each given command for output the SPNP gives corresponding output at a designated output files. For the illustrative example some of the output commands and there outputs given by the SPNP are explained below.

• (IOP\_PR\_RSET, VAL\_YES) gives the following results under ".rg" files.

Assign ascending order starting from zero to each places and transitions as given in the SPNP program. This output can be read as marking  $m_0$  being a tangible marking and having two tokens in place 0, one token in place 1, zero in place 2, one in place 3, zero in place 4, in place 5, two in place 6 and zero in place 7. If

(IOP\_PR\_FULL\_MARK, VAL\_NO) gives short form of \_reachset in which only places with tokens are given with corresponding number of tokens in each place. VAL\_YES gives long form as given above and is easy to read if SPN has a small number of places.

• (IOP\_PR\_RGRAPH, VAL\_YES) give the following results under ".rg" files.

Table 6 ".rg" File of the Illustrative Example

```

nplace = 8;

_{ntrans} = 5;

_places =

_transitions =

0: p1;

0: tl;

1: p2;

1: t2;

2: p3;

2: t3;

3: p4;

3: t4;

4: p5;

4: t5;

5: p6;

6: p7;

7: p8;

ntanmark = 9;

_nabsmark = 0;

nvanmark = 0;

nvanloop = 0;

_nentries = 10;

reachset =

#

p_1

p_2

p_3

p_4

p_5

p_6

p_7

p_8

0_t

1

1

2

l t

1

1

1

2

2_t

1

1

2

3_t

1

1

1

1

1

4_t

1

1

1

1

5_t

1

1

2

1

6_t

1

```

## Table 6 (Cont.)

|       |        |     |    |     |   |   |   |   | <br> |

|-------|--------|-----|----|-----|---|---|---|---|------|

| 7_t   | •      | 1   | :  | 1   | : | 2 | : |   |      |

| 8_t   | :      | ;   | ;  | 1   | : | 1 | 1 | 1 |      |

|       | haranh |     |    |     |   |   |   |   |      |

| _reac | hgraph |     |    |     |   |   |   |   |      |

| 0     | 1:     | 0:1 |    |     |   |   |   |   |      |

| 1     | 2:     | 1:1 |    |     |   |   |   |   |      |

| 2     | 3:     | 2:1 |    |     |   |   |   |   |      |

| 3     | 5:     | 3:1 | 4: | 0:1 |   |   |   |   |      |

| 4     | 6:     | 1:1 |    |     |   |   |   |   |      |

| 5     | 0:     | 4:1 |    |     |   |   |   |   |      |

| 6     | 7:     | 2:1 |    |     |   |   |   |   |      |

| 7     | 8:     | 3:1 |    |     |   |   |   |   |      |

| 8     | 3:     | 4:1 |    |     |   |   |   |   |      |

|       |        |     |    |     |   |   |   |   |      |

|       |        |     |    |     |   |   |   |   |      |

This output can be read as marking 0 entering marking 1 by firing transition 0 with probability 1. Also, marking 3 can go to marking 5 by firing transition 3 with probability 1 and to marking 4 by firing transition 0 with probability 1.

With IOP\_PR\_RSET and/or IOP\_PR\_RGRAPH VAL\_TANGIBLE specifies that only tangible markings must be printed in ".rg" file.

• (IOP\_PR\_MC, VAL\_YES) gives ".mc" file. It has default VAL\_CTMC, this describes the Continuous Timed Markov Chain (CTMC) derived from the SPN; the vanishing markings are absent and only numerical rates appear. The transition rate matrix is described by rows, since default is set for (IOP\_PR\_MC\_ORDER,VAL\_FROMTO) else if VAL\_TOFROM its transpose is printed in ".mc" file. The ".mc" file of the illustrative example is given in table 7.

Table 7 ".mc" File of the Illustrative Example

```

_firstindex = 0;

_nstates = 9;

nentries = 10;

order = _FROMTO;

_matrix =

1:1

2:1

1

3:1

4:1

5:1

3

4

6:1

0:1

5

6

7:1

7

8:1

8

3:1

```

This can be read as for \_matrix = 3 4:1 5:1; means that transition rate from state 3 to state 4 is 1 or to state 5 is 1. The \_TOFROM is in the following format: 4 ... 3:1 ....;

Also, these files have IOP\_METHOD that allows to set the numerical solution method for the CTMC, the default setting is steady state SOR (\_SSSOR), and other options are given in [9]. The precision can be set with FOP\_PRECISION with non-negative double value or default is 1e-06, and maximum number of iterations can be set with IOP\_ITERATIONS with non-negative int or has default value is 2000.

• (IOP\_PR\_PROB, VAL\_YES) gives ".prb" file. This file gives the steady-state probabilities for tangible markings; corresponds to the result of the CTMC solution. In this file the \_method may be changed automatically and values in it reflect the actual choice and may be different from the one declared in ".mc" file. When the maximum

number of iterations has reached, it automatically switches to Steady State Gauss-Seidel.

The ".prb" file of the illustrative example is given in Table 8.

Table 8 ".prb" File of the Illustrative Example

```

firstindex = 0;

_{nstates} = 9;

_method = _SSSOR;

precision = 0.000

iterations = 1;

_probabilities =

0:0.111

1:0.111

2:0.111

4:0.111

5:0.111

3:0.111

7:0.111

6:0.111

8:0.111

end;

```

Also, output generates ".log" file which contains the number of tangible markings, number of vanishing markings, number of arcs, number of remaining arcs after elimination of redundant arcs, number of remaining arcs after elimination of vanishing markings and solving method. This file is also, shown during the execution of SPNP program. The ".log" file of the illustrative example is given in Table 9.

Table 9 ".log" File of the Illustrative Example

The Reachability graph contains:

- 9 tangible markings

- 0 vanishing markings

- 10 arcs

#### Table 9 (Cont.)

After elimination of redundant arcs:

# of remaining arcs:

10

After elimination of vanishing markings:

# of remaining arcs:

10

Solving the Markov chain....

...Markov chain solved

Reading the reachability graph info ...

End of execution.

".out" file in Table 10 gives output request in ac\_final, Probability of each places having nonempty token, Average token in each places, Probability of enabled transitions and Average throughput of each transitions.

Table 10 ".out" File of the Illustrative Example

EXPECTED: throughput, 't3' = 0.222 EXPECTED: throughput, 't5' = 0.222 EXPECTED: utilization, 'Robot' = 0.667 EXPECTED: utilization, 'Buffer' = -0.333

#### AVERAGE:

| Dringnama | tril Ariftalianal                                  |                                                                                                                           |  |  |  |

|-----------|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Filmonemp | r fluoriembial waltokens                           |                                                                                                                           |  |  |  |

| 0.555     | 0.667                                              |                                                                                                                           |  |  |  |

| 0.333     | 0.333                                              |                                                                                                                           |  |  |  |

| 0.222     | 0.222                                              |                                                                                                                           |  |  |  |

| 0.777     | 0.777                                              |                                                                                                                           |  |  |  |

| 0.222     | 0.222                                              |                                                                                                                           |  |  |  |

| 0.555     | 0.667                                              |                                                                                                                           |  |  |  |

| 0.889     | 1.333                                              |                                                                                                                           |  |  |  |

|           | 0.555<br>0.333<br>0.222<br>0.777<br>0.222<br>0.555 | 0.333       0.333         0.222       0.222         0.777       0.777         0.222       0.222         0.555       0.667 |  |  |  |

Table 10 (Cont.)

| 7:p8      | 0.222 |             | 0.222          |

|-----------|-------|-------------|----------------|

| TRANSITIO | N     | Pr[enabled] | Av[throughput] |

| 0:t1      |       | 0.222       | 0.222          |

| 1:t2      |       | 0.222       | 0.222          |

| 2:t3      |       | 0.222       | 0.222          |

| 3:t4      |       | 0.222       | 0.222          |

| 4:t5      |       | 0.222       | 0.222          |

The Production rate (P) in the five station assembly system is taken to be small so that a result can be obtained from SPNP software. The failure rate (F) is defined as

$$F = \frac{R}{1 - R} \times P$$

where R is the rate of failure

The production rate of all the other station was constant while production rate of station in question varies. Similarly, failure rate was constant for all the stations while production rate varies for the station in question. The data has been taken for four stations and at three failure rates namely 1%,10%, 30%, also data has been taken with one pallet in the system. The data for three failure rates are given in Table 11, Table 12 and Table 13 respectively. The firing rate of transition is exponentially distributed. The time delay is random and exponentially distributed, and the resulting firing rate,  $\lambda$ , is equal to inverse of expected time delay

$$\lambda = \frac{1}{E(\tau)}$$

where  $E(\tau)$  is the average time delay. See Appendix C for the output files of S4 in a five sequence work station system.

#### 4.3 Performance Analysis of the System

The outputs requested from SPNP include station and robot utilizations, throughput of each station, as well as system production rate. The throughput of the stations S1, S2, S3, S4 and S5 are the throughput of transitions  $t_6$ ,  $t_{12}$ ,  $t_{20}$ ,  $t_{28}$  and  $t_{37}$  respectively. The system production rate is the throughput of the last station, i.e., S5. The utilization of a resource is defined as

1 - (token availability of the resource place).

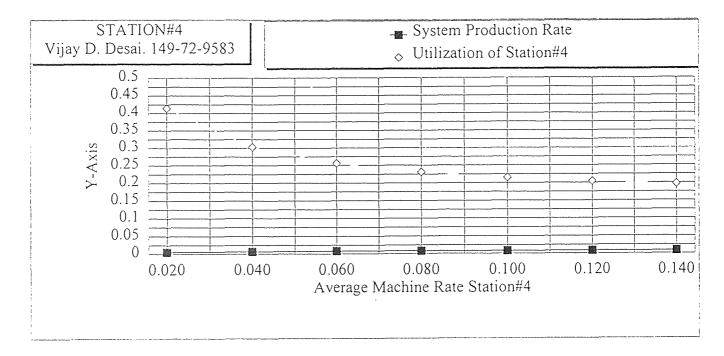

From the Table 11 and Figure 4.2 utilization of S4 is 0.214790 when production speed of the stations S1-S3 and S5 is 5; the failure rate of each stations S1-S3 and S5 is 0.1; the production speed of S4 is 0.1 and failure rate of S4 is 0.1. The token availability in place  $p_{s4}$  is 0.785210.

The following observation is made. As the average machine rate increases, the system production rate increases and the utilization of the work station decreases, until the system production rate is saturated. The average firing rate of t<sub>36</sub> gives throughput of finished goods unloaded at S5 and t<sub>37</sub> gives throughput of unfinished goods unloaded at S5.

The system production rate =

Average firing rate of

$$t_{36}$$

Average firing rate of  $t_{36}$  + Average firing rate of  $t_{37}$  × 100

The system production rate and utilization of S4 are given in Figures 4.1 - 4.3 for each failure rate of 1%, 10% and 30% respectively. As shown in Figures 4.1 - 4.3 increase in failure rate of the system reduces production rate. Thus the system efficiency decreases. Due to the production rate (P) in the five station assembly system is taken to be small significant difference in the outputs for three failure rates is not achieved.

Table 11 System Production rate and Utilization of S4 when Failure rate is 1%

| Average Machine<br>Rate S4 | Average Failure<br>Rate S4 | System<br>Production Rate | Utilization S4 |

|----------------------------|----------------------------|---------------------------|----------------|

| .020                       | .01                        | 6.437935E-03              | 4.140652E-01   |

| .040                       | .01                        | 7.663150E-03              | 3.025704E-01   |

| .060                       | .01                        | 8.475539E-03              | 2.559349E-01   |

| .080                       | .01                        | 8.453690E-03              | 2.306162E-01   |

| .100                       | .01                        | 8.626459E-03              | 2.148873E-01   |

| .120                       | .01                        | 8.743051E-03              | 2.042707E-01   |

| .140                       | .01                        | 8.826289E-03              | 1.966889E-01   |

Figure 4.1

Average Failure Rate for S4 is 1%.

Average Machine Rate is 5 and Average Failure Rate is 10% for S1, S2, S3, and S5.

Table 12 System Production rate and Utilization of S4 when Failure rate is 10%

| Average Machine<br>Rate S4 | Average Failure<br>Rate S4 | System<br>Production Rate | Utilization S4 |

|----------------------------|----------------------------|---------------------------|----------------|

| .020                       | .1                         | 6.438082E-03              | 4.140612E-01   |

| .040                       | .1                         | 7.663084E-03              | 3.025535E-01   |

| .060                       | .1                         | 8.175379E-03              | 2.558972E-01   |

| .080                       | .1                         | 8.453401E-03              | 2.305513E-01   |

| .100                       | .1                         | 8.626012E-03              | 2.147897E-01   |

| .120                       | . 1                        | 8.742420E-03              | 2.041356E-01   |

| .140                       | .1                         | 8.825454E-03              | 1.965124E-01   |

Figure 4.2

Average Failure Rate of S4 is 10%

Average Machine Rate is 5 and Average Failure is 10% for S1, S2, S3, and S5

| Table 13 System Production rate and | Utilization of S4 | when Failure | rate is 30% |

|-------------------------------------|-------------------|--------------|-------------|

|-------------------------------------|-------------------|--------------|-------------|

| Average Machine<br>Rate S4 | Average Failure<br>Rate S4 | System<br>Production Rate | Utilization S4 |

|----------------------------|----------------------------|---------------------------|----------------|

| .020                       | .3                         | 6.438044E-03              | 4.140489E-01   |

| .040                       | .3                         | 7.662883E-03              | 3.025018E-01   |

| .060                       | .3                         | 8.174898E-03              | 2.557839E-01   |

| .080                       | .3                         | 8.452544E-03              | 2.303590E-01   |

| .100                       | .3                         | 8.624704E-03              | 2.145043E-01   |

| .120                       | .3                         | 8.740601E-03              | 2.037463E-01   |

| .140                       | .3                         | 8.823076E-03              | 1.960108E-01   |

Figure 4.3

Average Failure Rate of S4 is 30%.

Average Machine Rate is 5 and Average Failure Rate is 10% for S1, S2, S3 and S5.

From the other output files of SPNP program (Appendix D) the following Petri net properties can be observed. ".log" file states that, the reachability graph contains 45 tangible markings, 0 vanishing markings and 57 arcs. Since this file does not contain any absorbing marking, the system is deadlock free. From ".rg" file, the system is found to be bounded and safe. The system is live, since for any marking  $m_0$ , it is possible to fire ultimately any transition by executing some firing sequence. The system is reversible, since marking  $m_0$  can be reached from any marking  $m_0$  (which also implies consistency.

#### CHAPTER 5

#### CONTROL OF THE SYSTEM USING PLC

In this thesis PLC is used to control the system. The application of Programmable Logic Controllers (PLCs) for system control is given in this chapter.

PLC can be defined as a specialized computer processor in a computer family. It is capable of storing instructions to implement control functions such as sequencing, timing, counting, arithmetic, data manipulation and communication.

## 5.1 History of PLC

In 1968 in order to eliminate high costs, Hydramatic Division of the General Motors Corporation replaced inflexible relay-controlled systems with PLCs which are flexible, easily maintainable, and programmable. PLCs are able to sustain in a harsh environment and can be reused in the system. Also, it provides expendability for the future. To achieve these criteria a PLC was developed. In the beginning the PLC was designed to replace relay-controlled systems which were widely used in automotive industry. In 1970's with improvement of microprocessor technology PLCs were capable of data manipulation, arithmetic and communication with other PCs and PLCs. PLCs have diagnostic indicators that aid trouble shooting and PLCs are designed in a modular form for replacement or repair of sub-assemblies. By 1971 PLCs were also being used in food and beverage, metals manufacturing and pulp and paper. CRT technology made PLC programming more

flexible and aided a trouble shooting process. Between 1975 and 1979 Hardware and Software enhancements gave PLCs more flexibility in memory capability, remote Input/Output capability, communications and fault detection. Also, a PLC reduces cost of installation and implementation of a control system. With today's technology, PLCs have developed programs that are flexible, shorter, faster and higher memory capacity. Compared with a PC-based controller, they are very expensive. However, the harsh environments still justify their extensive usage.

## 5.2 Description of a PLC

A PLC is composed of two basic sections, the CPU and Input/Output interface to the system. The CPU is composed of three components: the processor, the memory system and power supply of the system. In the operation of PLCs, Inputs/Outputs are connected to field devices which are used in the control of a process. CPU receives and processes information from field devices via control program and then updates the output devices.

The ladder diagrams are used in providing control information from the designers to the users of equipment. Since it is easy to use and interpret, it was widely accepted in the industry. Proper implementation of a control system depends on the knowledge of PLC operation, scanning and instruction programming. In PLC logic functions are programmed and can be easily changed. Relay logic implemented in PLCs is based on three basic functions (AND, OR, NOT). These functions are used either singly or in combinations to form instructions to control devices. These instructions are implemented using ladder diagram language, which is a one step translation from relay logic.

The complete ladder diagram can be thought of as being formed by individual circuits, each circuit having one output. Each of these circuits is known as a rung. A rung is the contact symbology required to control an output in the PLC. Some controllers allow a rung to have multiple outputs, but one output per rung is convention. Each rung is a combination of input conditions (symbols) connected from left to right between two vertical lines, with the symbols that represent the output at the far right. The input symbols are connected in series, parallel or some combination to obtain the desired logic.

Each symbol on the rung has a reference number, which is the address in memory where I/O status is stored. The address for given I/O can be used throughout the program as many times as required by the control logic. In relay logic, additional contacts mean additional hardware, compared to ladder logic. The address reference is dependent on the controller, but most of them are octal (base 8) or decimal (base 10) numbering.

The main function of the ladder diagram program is to control outputs and perform functional operations based on input conditions. The continuity is achieved whenever a path contains contact elements in a closed condition so that power flows from left to right. These contact elements will either close or remain closed according to the status of its reference inputs. The maximum number of ladder contact elements that can be used to program a rung is restricted by the ladder rung matrix, and its size differs among different PLC manufactures and programming device used. One of the most important rules in all PLCs is that of reverse power flow. Reverse power is not allowed in PLC logic to prevent possible sneak paths that could occur in hardwired electromechanical relay systems.

## 5.3 Description of Basics of Ladder Diagrams

The following symbols are used in translating relay control logic to contact symbolic logic.

- —] [— Normally-opened contact: Input to control logic, either external input or internal output. When evaluated by the program it is examined for its status "1". If so, the contact is closed, else it is open.

- —]/[— Normally-closed contact: Input to control logic, either external input or internal output. When evaluated by the program it is examined for its status "0" if so then contact is closed else contact will open.

- -()- Output: Represents any output that is driven by some combination of input logic. It can be connected to device or can be internal output. If any left-to-right path of a rung has all contact closed then output of the rung is energized.

Timer: There are different types of timers supplied by manufacturers. They are

1) Timer ON Delay Energize 2) Timer ON Delay De-energize 3) Timer OFF Delay

Energize and 4) Timer OFF Delay De-energize.

Also, there are two formats. Block format timer may have one or two inputs in which case one pin is control and the other is for enable/reset. If both inputs are true, then the timer block starts timing. Ladder format timer has one pin input. If it is high then timer starts. There are two registers used in the timer. One is to store the preset value and the other is to store the accumulated value. The time base is dependent on type of PLC used (e.g. 0.01 sec, 0.1 sec, 1.0 sec, etc.)

- -(L)- Latch output: A latch output remains energized, even though the status of the contacts which cause the output to energize may change. It remains latched ON until it is unlatched by an unlatch output instruction of the same reference address.

- -(U)- Unlatch output: The unlatch output instruction is programmed to reset a latched output having the same reference address. If any rung path has logic continuity to the unlatch output, the reference address is unlatched to an OFF condition.

There are other types of contact symbolic logic used in PLC program such as counter, jump to, go to subroutine, return coil, arithmetic instructions, etc. These applications and their instructions can be found in [5].

The programmable controller reads all field input devices, executes the control program and updates all field output devices. This process is called scan.

The last process of updating output is in two steps. First step is to update internal output and continue to execute the program until it has finished evaluating the control program; second step is to update output interface modules thereby the field devices. The scan time, the time it takes to implement scan, consists of the program scan time and the I/O update time. PLC manufactures generally specify the scan time based only on the amount of application memory used (e.g. 10 msec/1K of programmed memory) [5]. The remote location of I/O subsystems increases scan time. Some PLCs provide software instructions that allow the interruption of the continuous program scan in order to receive an input or update an output immediately. These immediate instructions are very useful when the PLC must react instantaneously to a critical input or output.

The power supply requirement to run PLC is usually 120VAC or 220VAC, but some controller provides PLC's to run on 24 VDC. Input supply must be connected to Isolation Transformer and through EMI filter for any fluctuation of line voltage and noise due to on/off of devices connected to PLC causing noise and power loading. If summation of the current requirements for a particular I/O configuration is greater than the total current supplied by the power supply, then the second power supply is required.

The amount of application memory is specified in terms of unit K where each K unit represents 1024 word locations. The total number of storage locations available is indicated by the memory capacity of a particular controller in the units of K. After determining the minimum memory requirements for the application, one should add 25% to 50% more memory for future changes and modifications.

The memory organization and interaction of the data table's I/O mapping and storage area helps to comprehend the functional operation of a programmable controller. Also, it helps in understanding of how the control software program is organized and developed.

In PLC the word length is two bytes, 16 bits. The starting address of control program is not very important but register address references are.

There are different types of input and output interfaces connected to a PLC. Selector switches, pushbuttons, limit switches, proximity switches, and Thumbwheel switches are example of digital or discrete type. The standard ratings for these inputs and/or outputs are 24 Volts AC/DC, 48 Volts AC/DC, 120 or 230 Volts AC/DC, TTL

level etc. Detail of these inputs and outputs can be found in [5]. Also, there are Analog I/O that can be connected to PLC [5].

#### 5.4 Development of the PLC Program

In the development of PLC program, a modular approach similar to the Petri net model is used. First, all the common rungs are written for all the stations and then these rungs are copied into files for each station. Next, individual rungs and their addresses in each station are added as per each stations job. These process are valid in a PLC, since it does not update any output until it has scanned the program completely. If input conditions are satisfied then the output contacts are made. Thus, the execution of the process is done in the actual sequence, even if the program steps are not in sequence. The PLC program is written considering many of the practical conditions such as motion of robot arms, the use of an operator key for the reset of a work station due to the machine failure.

#### 5.4.1 Ladder Logic Program for S1 Module

The portion of flow chart for the sequence of process is shown in Figure 5.1 and the PN model in Figure 3.2, the token in  $p_{s1}$  implies that S1 is ready; in ladder logic program (LLP), output B:3/1 is energized in rung 2:0. In rung 2:1 output O:3/0 is energized, when  $p_2$  has a token in the PN model. When timer T4:0 is done the pallet is marked good and output O:3/3 is energized in rung 2:6, i.e.,  $p_3$  has a token in the PN model. When a part for S1 is available in the feeder input I:1/6, I:1/6 becomes a closed contact, as in the PN model  $p_4$  has a token. Similarly, I:1/5 becomes a closed contact when robot is available

Figure 5.1 Flow Chart of Five Sequence Work Station For Ladder Logic Program

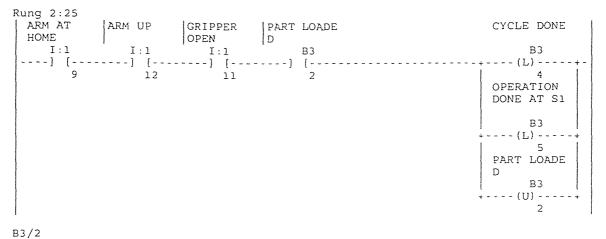

and ready or p<sub>R1</sub> has a token. Place p<sub>5</sub> having a token implies that robot is ready with the part to be loaded, and output O:3/8 is energized and latched at rung 2:20. The operation at S1 is completed when B:3/5 is energized at rung 2:25. The enabling of a transition in the PN model can be regarded as that all the input conditions are satisfied to have an output to be energized in the LLP's.

#### 5.4.2 Ladder Logic Program for S1 Failure Module