# **Copyright Warning & Restrictions**

The copyright law of the United States (Title 17, United States Code) governs the making of photocopies or other reproductions of copyrighted material.

Under certain conditions specified in the law, libraries and archives are authorized to furnish a photocopy or other reproduction. One of these specified conditions is that the photocopy or reproduction is not to be "used for any purpose other than private study, scholarship, or research." If a, user makes a request for, or later uses, a photocopy or reproduction for purposes in excess of "fair use" that user may be liable for copyright infringement,

This institution reserves the right to refuse to accept a copying order if, in its judgment, fulfillment of the order would involve violation of copyright law.

Please Note: The author retains the copyright while the New Jersey Institute of Technology reserves the right to distribute this thesis or dissertation

Printing note: If you do not wish to print this page, then select "Pages from: first page # to: last page #" on the print dialog screen

The Van Houten library has removed some of the personal information and all signatures from the approval page and biographical sketches of theses and dissertations in order to protect the identity of NJIT graduates and faculty.

#### ABSTRACT

## Design of a 320X122 MWIR-CCD PtSi:Si Imaging Radiometer with Automatic Optical Integration Time Control

### by Nathaniel Joseph McCaffrey

An infrared CCD camera system was designed and developed to operate a 320X244 Schottky-barrier IR-CCD Focal Plane Array (FPA) as an imaging radiometer. The goal of this research was to develop a reliable radiometer capable of resolving temperatures between 50 and 1000°C to within 1°C accuracy using non-contact spectral thermographic methods. To accomodate this wide dynamic range, the imager was operated in a non-interlaced format with variable optical integration times ranging from 120µsec to 122msec. Variable integration control was achieved by employing a "dump and read" timing procedure. To facilitate this operation, novel circuitry was developed for dynamically controlling the CCD waveforms to operate at the required integration time. Circuits were developed to embed critical information in the video signal to facilitate radiometric post-processing. An optoelectronically buffered digital interface was developed to connect the camera system to a Datacube processor. Additional circuitry enabled all frame rates to be displayed on an RS-170 monitor after processing. This system was designed to monitor the temperature of semiconductor wafers in Rapid Thermal Processing (RTP) reactors acting as the feedback control to the flash lamp heat sources.

## DESIGN OF A 320X122 MWIR-CCD PtSi-Si IMAGING RADIOMETER WITH AUTOMATIC OPTICAL INTEGRATION TIME CONTROL

by Nathaniel Joseph McCaffrey

A Thesis Submitted to the Faculty of New Jersey Institute of Technology in Partial Fulfillment of the Requirements for the Degree of Master of Science in Electrical Engineering

Department of Electrical and Computer Engineering May 1993 Copyright © 1993 by Nathaniel Joseph McCaffrey

ALL RIGHTS RESERVED

### APPROVAL PAGE

## Design of a 320X122 MWIR-CCD PtSi-Si Imaging Radiometer with Automatic **Optical Integration Time Control**

Nathaniel Joseph McCaffrey

Dr. Walter F. Kosonocky, Thesis Advisor Date Foundation Chair of Optoelectronics and Solid State Circuits Distinguished Professor of Electrical Engineering, Electrical and Computer Engineering, NJIT

5/6/93

Dr. Constantine N. Manikopoulos, P.É., Committee Member Associate Professor of Electrical and Computer Engineering Electrical and Computer Engineering, NJIT

5/6/93

Dr. Edwin S. H. Hou, Committee Member Assistant Professor of Electrical and Computer Engineering Electrical and Computer Engineering, NJIT

### **BIOGRAPHICAL SKETCH**

| Author:         | Nathaniel J. McCaffrey                      |

|-----------------|---------------------------------------------|

| Degree:         | Master of Science in Electrical Engineering |

| Date:           | May 1993                                    |

| Date of Birth:  |                                             |

| Place of Birth: |                                             |

### Undergraduate and Graduate Education:

- Master of Science in Electrical Engineering, New Jersey Institute of Technology, Newark, New Jersey, 1993

- Bachelor of Science in Electrical Engineering, New Jersey Institute of Technology, Newark, New Jersey, 1991

### **Publications:**

"Radiometric Infrared Focal Plane Array Imaging System for Thermographic Applications", NASA Report, NAS-18226, July, 1992.

"End Point Monitoring of Patterned Wafers During Reactive Ion Etching Using a High Resolution Infrared Camera", Proc. American Vacuum Society, Chicago, 1992. This thesis is dedicated to Kimberly for all the love and patience... (and for cutting and pasting)

### ACKNOWLEDGMENT

The author wishes to express his sincere gratitude to individuals who have provided technical support and have contributed to aspects of this thesis. Special thanks to my supervisor, Professor Walter F. Kosonocky for technical direction and project management throughout this project. With many friendly discussions and invaluable suggestions, I have learned a great deal from Dr. Kosonocky's years of experience. Special thanks are due to Professors Constantine Manikopoulous and Edwin Hou for serving as members of my committee and for many of their suggestions that have been incorporated into these designs.

The author is also grateful to the Optoelectronic Systems Group at the David Sarnoff Research Center for their many technical contributions. Special acknowledgment is due to Benjamin Esposito who has provided invaluable support in both the design and testing of this camera. Our discussions helped me to fully understand many of the complexities I had encountered. Dr. John Tower is also recognized for his management and guidance during this research.

The author appreciates the friendship and guidance from the members of the Electronic Imaging Center at NJIT including: Vipul Patel, Jitesh Shah, Michael Kaplinsky, and Jun Li.

The author wishes to acknowledge the financial support offered during my graduate career by the New Jersey Institute of Technology Foundation Chair for Optoelectronics and Solid State Circuits held by Professor Walter F. Kosonocky and also expresses his gratitude to Dr. Gary Hughes, Head of the Optoelectronics Systems Group at the David Sarnoff Research Center, for providing the facilities for this research.

vi

### TABLE OF CONTENTS

| C | Chapter Page 1 |                                       | Page |

|---|----------------|---------------------------------------|------|

| 1 | INT            | RODUCTION                             | 1    |

| 2 | INF            | RARED IMAGING                         | 3    |

|   | 2.1            | The Electromagnetic Spectrum          | 3    |

|   | 2.2            | Radiant Sources                       | 4    |

|   | 2.3            | Transfer of Radiant Flux              | 8    |

| 3 | IR L           | maging Devices                        | 13   |

|   |                | 3.1.1 Metal Semiconductor Junctions   | 13   |

|   | 3.2            | Focal Plane Array                     | 21   |

|   |                | 3.2.1 Spectral Uniformity             | 24   |

|   |                | 3.1.2 Spatial Uniformity              | 27   |

|   | 3.3            | Variable Sub-Frame Integration Time   | 32   |

|   | 3.4            | Variable Multi-Frame Integration Time | 37   |

| 4 | CAN            | IERA ELECTRONICS                      | 39   |

|   | 4.1            | Camera Head                           | 39   |

|   |                | 4.1.1 Bias Board                      | 40   |

|   |                | 4.1.2 Analog Board                    | 41   |

|   |                | 4.1.3 Pre-Process Board               | 42   |

|   |                | 4.1.4 Standard Clock Generator        | 43   |

|   | 4.2            | Variable Integration Sequencer        | 45   |

| Chapter Pag                      |      |

|----------------------------------|------|

| 5 VIDEO PROCESSOR                | . 51 |

| 5.1 Analog to Digital Conversion | . 52 |

| 5.2 Simulator Board              | . 53 |

| 5.3 Multi-Function Board         | . 56 |

| 5.3.1 Head Receiver              | . 56 |

| 5.3.2 Variable Integration Time  |      |

| with Front Panel Display         | . 56 |

| 5.3.3 Frame Count Circuitry      | . 63 |

| 5.4 Jumper Board                 | . 69 |

| 5.5 The Input/Output Board       | . 70 |

| 6 DATACUBE INTERFACE CIRCUITRY   | . 71 |

| 6.1 Datacube Input Board         | . 71 |

| 6.2 Datacube Display Board       | . 75 |

| 7 CONCLUSIONS                    | . 83 |

| A1 THE OPTICAL SYSTEM            | . 85 |

| A1.1 The Optical Setup           | . 85 |

| A1.2 Simple Lens Systems         | . 86 |

| A1.3 Optical Limitations         | . 90 |

| A1.4 Cold Shield Design          | . 94 |

| A1.5 The Experimental Setup      | . 95 |

### LIST OF TABLES

| T | Table                                                      |    |

|---|------------------------------------------------------------|----|

| 1 | Total emitted power of a wafer sized                       | 7  |

| 2 | True binary conversion from the output of the ADC 603 chip | 53 |

| 3 | Threshold levels as a percentage of full well signal.      | 58 |

| 4 | Available integration times and                            | 61 |

| 5 | Maximum time for unique time stamping                      | 64 |

| 6 | Smart Frame data-bus interface                             | 68 |

### LIST OF FIGURES

| Figure                                                            | Page |

|-------------------------------------------------------------------|------|

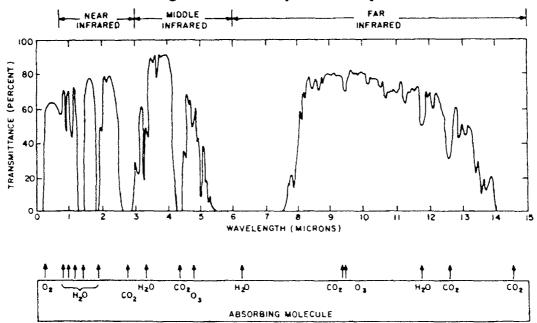

| 1 Transmission of the infrared spectrum through the atmosphere    | 3    |

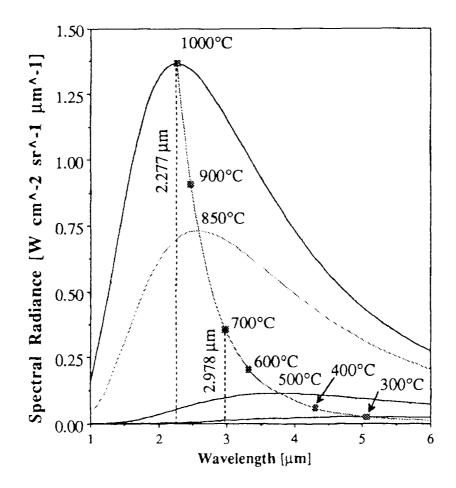

| 2 The Planck distribution and Wein displacement for MWIR signals  |      |

| for temperatures ranging from 300 to 1000°C.                      | 6    |

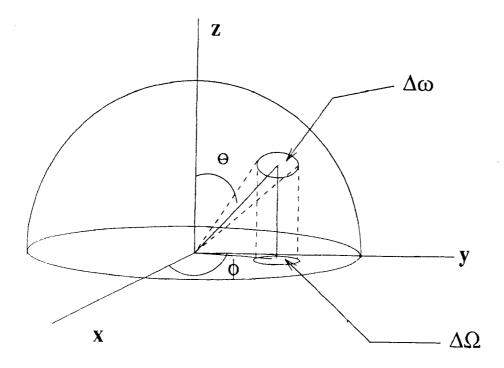

| 3 Illustration of the solid angle and projected solid angle       | 9    |

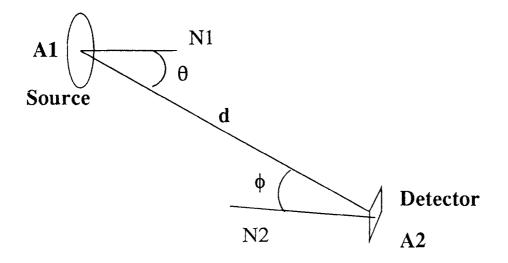

| 4 The geometrical illustration of beam throughput                 | 10   |

| 5 Energy band diagram for a PtSi Schottky Barrier Diode           | 14   |

| 6 Photon yield vs. Energy.                                        | 15   |

| 7 PtSi-Si SBD construction and operation.                         | 16   |

| 8 Responsivity plot of large area (2.5 X105 µm2) test diode       | 20   |

| 9 The 320 X 244 chip (a), and the layout of the SBD array (b)     | 23   |

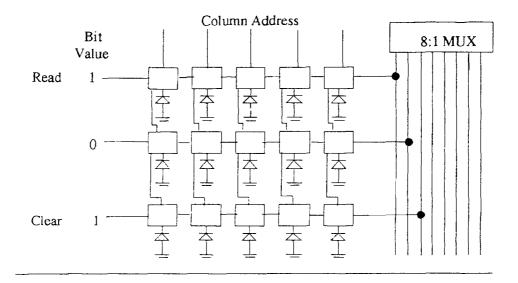

| 10 Sub-Frame optical interrogation with an IR-MOS imager.         | 24   |

| 11 Uniformity test station for PtSi detector arrays.              | 26   |

| 12 Spectral responsivity of the PtSi array for ten representative |      |

| pixels                                                            | 27   |

| 13 Procedure for obtaining two-point correction.                  | 28   |

| 14 Uniformity of corrected 640 X 480 IR-MOS FPA with              |      |

| temperature                                                       | 31   |

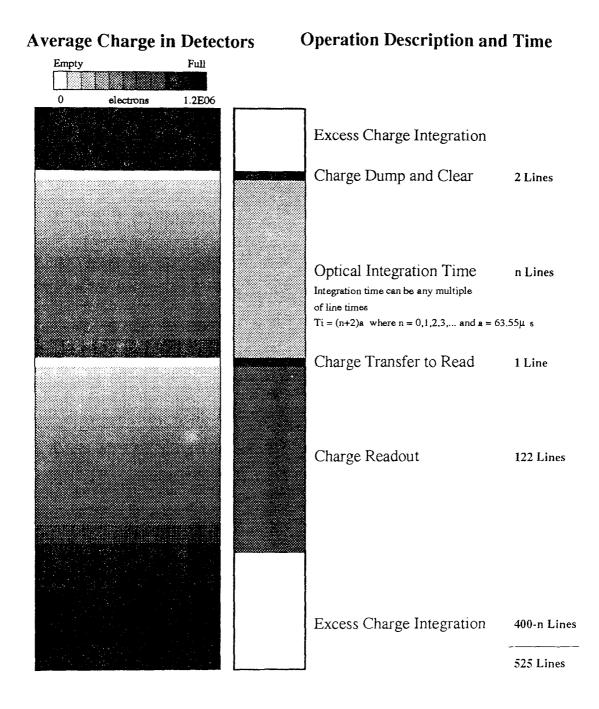

| 15 The operation of the 320 X 122 IR-CCD imager                   |      |

| for sub-frame integration.                                        | 35   |

| 16 The timing diagram for variable optical integration time       | 36   |

| 17 Multi-frame optical integration.                               | 38   |

| 18 Dewar assembly (side view)                                     | 41   |

| 19 Timing relationships for normal operation of 320 X 244 camera  | 44   |

| Figure                                                       | age  |

|--------------------------------------------------------------|------|

| 20 Measured timing signals in normal operation               | . 44 |

| 21 TRANSFER mode waveforms (measured)                        | . 47 |

| 22 READOUT mode waveforms (measured).                        | . 48 |

| 23 DUMP mode waveforms (measured).                           | . 49 |

| 24 SWEEP mode waveforms (measured)                           | . 50 |

| 25 The video processor                                       | . 51 |

| 26 Test-pattern images acquired and stored by a Sun computer | . 55 |

| 27 Variable integration calculation                          | . 59 |

| 28 Integration time decision circuitry.                      | . 60 |

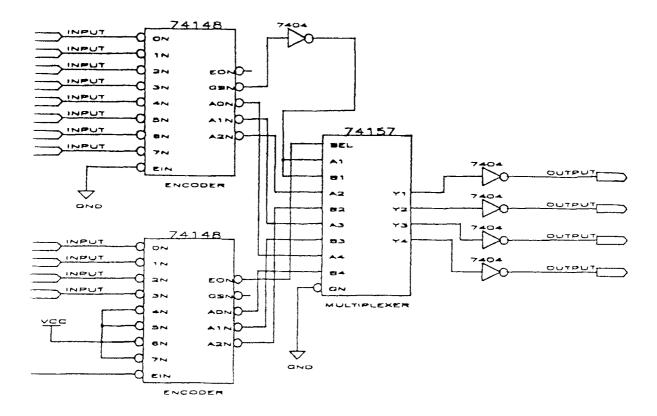

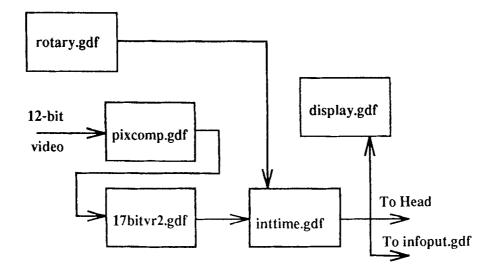

| 29 Rotary encoding circuitry                                 | . 62 |

| 30 Block diagram of variable integration time circuitry      | . 63 |

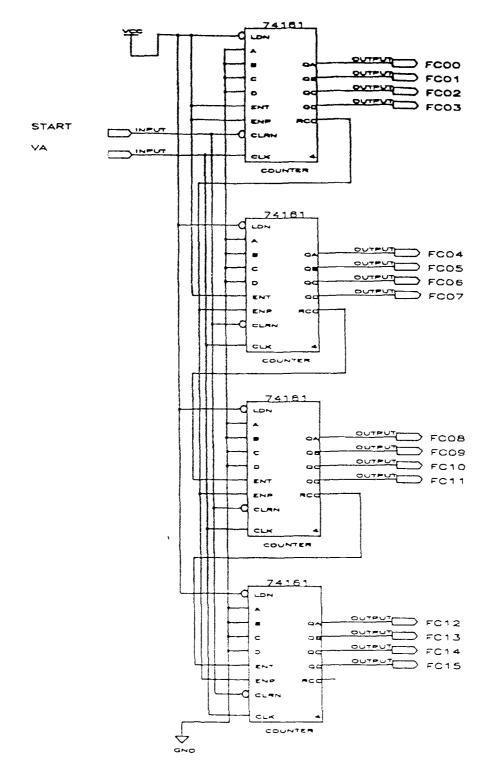

| 31 Frame count circuitry.                                    | . 65 |

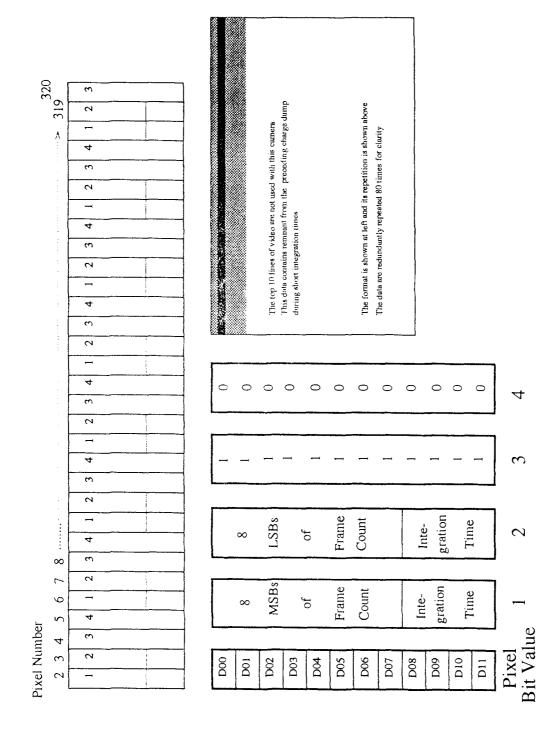

| 32 Smart Frame data encoding                                 | . 67 |

| 33 Smart Frame encoding circuitry                            | . 69 |

| 34 Datacube input board component layout                     | . 73 |

| 35 Test pattern for Datacube Input board                     | 73   |

| 36 Test pattern waveforms (measured).                        | 74   |

| 37 Datacube display board circuitry                          | . 76 |

| 38 Datacube P3 ECL system clock signals.                     | 77   |

| 39 Datacube P4 ROI synchronization signals (Even Field)      | 78   |

| 40 Ping-Pong memory operation.                               | 79   |

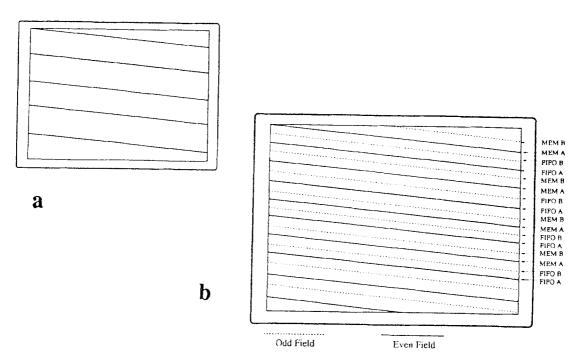

| 41 4X Scan conversion                                        | 80   |

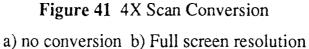

| 42 Waveforms to perform scan conversion                      | 80   |

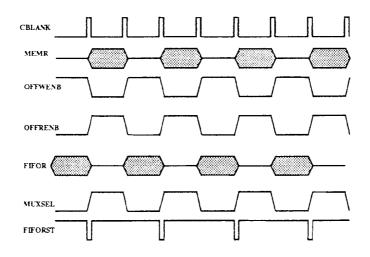

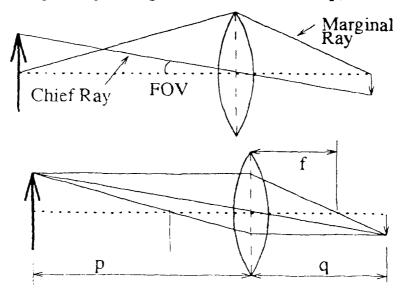

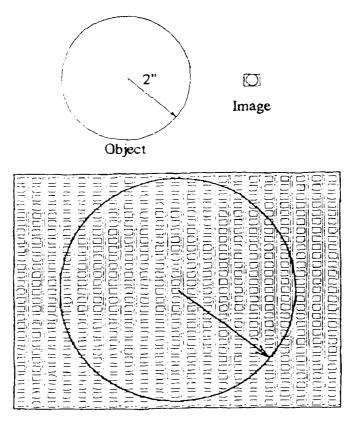

| 43 Relationship between image and working distances          | 87   |

| 44 a) Field of view and b) Image formation by ray-tracing    | 88   |

| Figure                                                            | Page |

|-------------------------------------------------------------------|------|

| 45 Scale drawing of the magnification of the wafer image          | 89   |

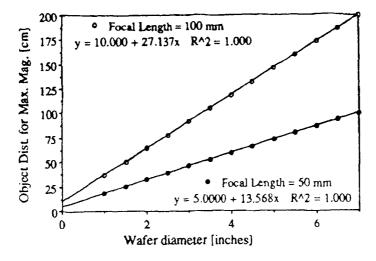

| 46 The Working distance required to obtain maximum full image vs. |      |

| wafer size for two focal lengths                                  | 90   |

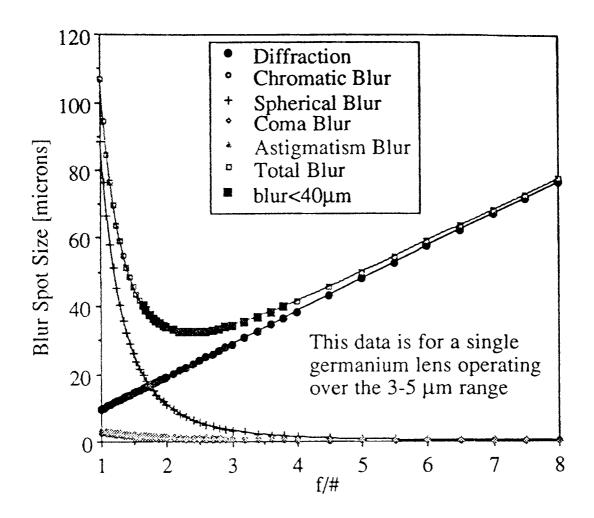

| 47 Optical aberrations vs. f/#                                    | 93   |

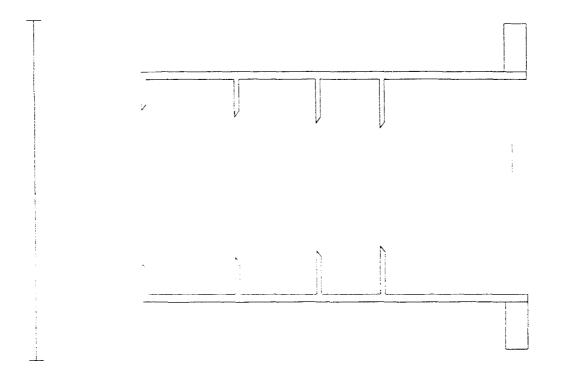

| 48 The baffle design with ray-tracing.                            | 94   |

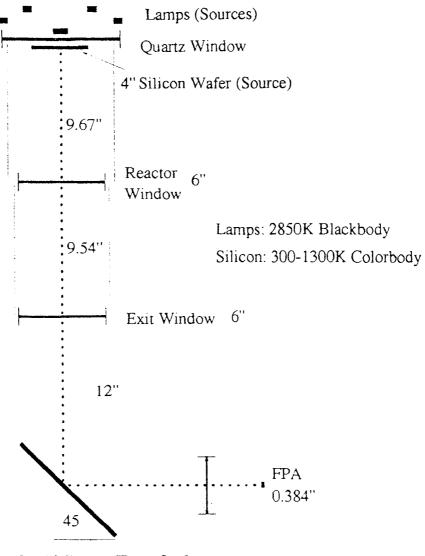

| 49 The RTP optical system.                                        | 95   |

## CHAPTER 1 INTRODUCTION

The research described in this thesis was performed at the David Sarnoff Research Center (DSRC) in Princeton, New Jersey under the direction of Dr. Walter F. Kosonocky, NJIT Foundation Chair for Optoelectronics and Solid State Circuits and supported by DARPA contract number F33615-92-C-5817 "Multi-Wavelength Imaging Pyrometry (MWIP) for Semiconductor Process Monitoring and Control". The goal of this research was to develop a reliable staring focal plane array (FPA) radiometer for non-contact spectral thermographic applications in semiconductor processing. The radiometer was required to effectively measure the temperature of a semiconductor wafer to within 1°C over the temperature range 50 to 1000°C. A 320X244 element platinum silicide (PtSi) Shottky-barrier detector FPA, developed at DSRC was chosen for this study and one-half of the vertical elements will be used in a noninterlaced format for data collection [1-2]. By employing variable integration time control ranging from 120µsec to 122ms, the effective dynamic range is improved a thousand times over the standard (single integration time) camera system.

Chapter 2 serves as an introduction to the field of infrared engineering and radiometry. Chapter 3 describes the construction and operation of the PtSi:Si imager sensors, and the dump and read procedure for sub-frame integration. Chapter 4 begins with a description of the basic camera electronics and concludes with a description of the custom timing board required for multi-integration time operation. Chapter 5 describes

1

the operation of the video processor and the functions of the multifunction board developed for this application. The interface between the camera and the Datacube computer was custom designed and its operation is explained in Chapter 6. Optical considerations for an application for this camera system are discussed in the Appendix.

The basic units of the Système International or SI consisting of the meter (m), kilogram (kg), and second (s) are used throughout the text with exception to the use of the micron ( $\mu$ m) which will be used to represent 1X10<sup>-6</sup>m.

### **CHAPTER 2**

### **2 INFRARED IMAGING**

### 2.1 The Electromagnetic Spectrum

The infrared portion of the electromagnetic spectrum spans from the millimeter wave region to the red edge of the visible spectrum. This band corresponds to wavelengths ranging from approximately 0.75 to 1000 microns. The infrared spectrum is classically divided into three regions; near infrared (NIR 0.7 to  $3\mu$ m), middle infrared (MWIR 3 to  $6\mu$ m), and far infrared (LWIR 6 to 1000 $\mu$ m). The distinctions for these three bands arise when infrared radiation is transmitted through the atmosphere. Shown in Fig. 1 is the transmittance of radiation over the infrared band with references to the molecules responsible for absorption at that wavelength. Distinct windows of high transmittivity are clearly shown.

Figure 1 Transmission of the infrared spectrum through the atmosphere.

The sensors used in the radiometer design are platinum silicide Schotkky barrier detectors (SBD). These detectors are sensitive to radiation in the MWIR band.

The mechanisms for production of MWIR radiation consist entirely of molecular vibrations in solids and liquids and vibration rotation transitions in gases. In the equilibrium state, these vibrations are caused by thermal agitation and therefore, MWIR imaging measures the emission and reflection of radiation from objects with non-zero temperatures. The emitted photon with an energy of  $hv = \Delta E_{therm}$  due to the electron-phonon interaction and subsequent electron relaxation implies that the radiant emission depends on the temperature of the object and its emissivity. For conduction and convection, the transfer of energy between two locations depends on the temperature difference to the first power. However the radiative transfer of power depends on the differences of the individual temperatures each raised to the fifth power. Imaging is then an effective measure of this radiative energy transfer and the study of radiometry concerns itself with the geometrical and spectral aspects of thermal energy transmission. This chapter will describe the basic formulae required to perform radiometric measurements. Later chapters will draw upon the formulae developed to solve problems specific to the present application.

### 2.2 Radiant Sources

The interaction of radiant energy with matter consists of reflection, transmission, and absorption. When radiation is incident on a homogeneous object, part of the radiation will be reflected at the surface while the rest will penetrate into the bulk of the body. If the body has high internal absorption, the radiation will be used to increase the internal energy of the object. To be a good absorber of incident energy, the object must have a low surface reflectivity and a high internal absorption to prevent radiation from passing through the sample.

A blackbody is an object with zero surface reflection and complete internal absorption. A blackbody radiates in a continuous fashion over a broad band of frequencies. Commercial blackbody simulators approximate ideal radiators and are used as the primary calibration standard for infrared detector testing.

According to Planck's equation, blackbody radiation is characterized by a relationship between the magnitude of the emitted intensity at each wavelength versus temperature is given by

$$L(\lambda, T) = \frac{2hc^2}{\lambda^5} \frac{1}{e^{\frac{hc}{\lambda kT}} - 1} \qquad [W \text{ m}^{-3} \text{ sr}^{-1}]$$

(1)

where h is Planck's constant, 6.6262 X 10<sup>-34</sup> Js

λ is the wavelength in meters

c is the velocity of light, 2.997 X 10<sup>8</sup> m/s

k is Boltzmann's constant, 1.3806 X 10<sup>-23</sup> J/K,

T is the absolute temperature in kelvins.

A plot of this relationship is shown in Fig. 2. The spectral radiance for temperatures of 300, 500, 850, and 1000°C is shown. The units for radiance plotted in the y-axis are in W-cm<sup>-2</sup>-sr<sup>-1</sup>· $\mu$ m<sup>-1</sup>. Also plotted is the locus of the points of maximum radiation.

This relationship is known as the Wein displacement law. It shows the maximum radiation shifts toward shorter wavelengths as the temperature of the radiator is increased.

$$\lambda_m = \frac{2898}{T} \qquad [\mu m] \qquad (2)$$

Fig. 2 shows that the peak radiation for temperatures ranging from 300-1000°C lie within the operating range of the PtSi detector response.

Figure 2 The Planck distribution and Wein displacement for MWIR signals for temperatures ranging from 300 to 1000°C.

The total power radiated per unit area of a blackbody is obtained by integrating Planck's radiation relation for all wavelengths at a given temperature, and the result is known as the Stefan-Boltzmann law:

$$M = \varepsilon \sigma T^{4}$$

where

$$\sigma = \frac{\pi^{2} k_{B}^{4}}{60\hbar^{3}c^{2}}$$

$$\sigma = 5.66961X10^{-8} W \cdot m^{-2} \cdot K^{-4}$$

(3)

In equation (3),  $\varepsilon$  is termed the total hemispherical emissivity. A perfect blackbody has an emissivity of one. A silicon wafer of six inch diameter occupies an area of:

$$A = \pi \cdot (0.0762)^2$$

$$A = 0.0182m^2$$

Table 1 lists the total power a blackbody with an area equivalent to the six inch wafer would emit for each given temperature.

| Temperature [°C]      | Total Power [W] |

|-----------------------|-----------------|

| 25 (Room Temperature) | 8.137           |

| 300                   | 111.235         |

| 500                   | 368.420         |

| 850                   | 1641.132        |

| 1000                  | 2709.806        |

Table 1 Total emitted power of a wafer sizedblackbody for certain temperatures

It is important to note that if the surroundings are at the same temperature, the object would absorb the same amount as it emits.

In many cases it is the temperature that must be determined given the radiance. Equation (1) can be rewritten as follows:

$$T = \frac{1.43883X10^4}{\lambda \cdot \ln\left[\left(\frac{1.191066X10^4}{L(\lambda)\lambda^5}\right) + 1\right]}$$

[K] (4)

### 2.3 Transfer of Radiant Flux

To correctly determine the radiometric characteristics of the camera system, a knowledge of the effective flux transferred from the source through the intervening media to the photovoltaic detector is required. Modeling the source of optical flux in terms of geometrical radiant quantities will help to predict the radiant energy transfer.

Fig. 3 shows an illustration of the differential solid angle  $\Delta \omega$ , and the differential projected solid angle  $\Delta \Omega$ . The steradian (sr) is a measure of the solid angle and is defined as the ratio of the area A on the surface of a sphere to the square of the radius. The differential solid angle is given by:

$$\Delta \omega = \frac{dA}{r^2} = \sin \theta d\theta d\phi \quad [sr] \tag{5}$$

The projected solid angle can be visualized as the projection of the solid angle area A onto the base of the hemisphere. The solid angle  $\omega$  and

Figure 3 Illustration of the solid angle and projected solid angle.

the associated projected solid angle  $\Omega$ , for a right circular cone oriented with the center on the Z-axis are given respectively by:

$$\omega = \int_0^{2\pi} d\phi = \int_0^{\Theta} \sin\theta d\theta = 2\pi (1 - \cos\Theta)$$

$$\Omega = \int_0^{2\pi} d\phi = \int_0^{\Theta} \sin\theta \cos\theta d\theta = \pi \sin^2\Theta$$

(6,7)

where  $\Theta$  is the half angle measured from the Z-axis to the cone edge.

A beam of radiant energy is defined in terms of two areas shown in Fig. 4. The areas are separated by a distance d. All the flux in the beam flows from  $A_1$  to  $A_2$ . The throughput is defined as

$$\gamma = n^2 A \Omega \tag{8}$$

where n is the index of refraction for the intervening medium.

Figure 4 The geometrical illustration of beam throughput.

Following Lambert's cosine law [6], the throughput for n=1 is given generally by

$$\gamma_1 = A_1 \cos \theta \omega_1 = A_1 \cos \theta \frac{A_2 \cos \phi}{d^2}$$

[cm<sup>2</sup> sr] (9)

This result is valid only in the limit where d is large with respect to the largest dimension of  $A_1$ . The exact relationship is given by

$$\gamma_1 = \int_{A1\omega_1} \int dA_1 \cos\theta d\omega_1 \qquad [\text{cm}^2 \text{ sr}] \qquad (10)$$

Equations (9) and (10) agree to within 1% when d is 20 times greater than the largest dimension of A<sub>1</sub>. For distances smaller than this, the integral of equation (10) needs to be solved because  $\omega_1$  is no longer independent of A<sub>1</sub>.

Flux  $(\Phi)$  is the general term used to describe a quantity that is propagated according to geometrical laws. Radiance is the most general

way of describing flux because it characterizes the beam both in position and direction.

Radiance can best be analogized to brightness in the visual spectrum. Radiance is defined as

$$L = \frac{d^2 \Phi}{\cos \theta \cdot dA \cdot d\omega} \qquad [W \, \text{cm}^{-2} \, \text{sr}^{-1}] \qquad (11)$$

where  $\theta$  represents the angle that the right circular flux cone makes with the source normal.

Emissivity is a measure of the relative response of a radiator with respect to a blackbody. Emissivity is a function of direction, wavelength, and temperature. A greybody is defined as  $\varepsilon(\lambda, T, \theta) = \text{constant} < 1$ , while a colorbody is defined as  $\varepsilon(\lambda, T, \theta) = f(\lambda, T, \theta)$ . Emissivity can be derived from the Kirchoff relations by considering an object in an isothermal cavity. If there is a temperature difference between the object and the cavity, there will be heat transfer. If the object absorbs a portion  $\alpha$  of the input exitance M that a blackbody would absorb, the emitted energy will equal the absorbed flux. Including all optical processes, the relationship

$$\alpha + \rho + \tau = 1 \tag{12}$$

is an expression of the conservation of energy where  $\rho$  is the reflectivity and  $\tau$  is the transmitivity of the material. For an opaque body where  $\tau=0$ , it is apparent that good reflectors have low emissivities. The emissivity term is used to scale radiometric equations that use blackbody models.

Calculations of the flux transfer from an extended area source to the sensor, are based on the radiometric definitions. The solid angle is measured at the sensor aperture.

The total flux is measured by spatially integrating over the entire source area, and integrating the solid angle beam the source is radiating and also the wavelength band of the response.

$$\Phi = \tau_{path} \varepsilon(\lambda, T, \theta) L(\lambda, T) \int_{\lambda} d\lambda) \int_{\omega} \cos \theta d\omega \int_{A} dA$$

$$\Phi = \varepsilon(\lambda, \theta) L(\lambda) A \Omega \tau_{path}$$

(13)

This equation is valid when the source to detector distance is 20 times greater than the length of the object, the object is isothermal, and  $\tau_{path}$ represents the aggregate transmission characteristics of the path medium. These assumptions are usually valid when a single pixel in the array is defined as the sensor. The path transmission must be found experimentally or by computer model to include effects such as molecular absorption, scattering and window/lens effects. Our system can use these assumptions for the distances used to image the semiconductor wafers. The light is transmitted through several materials and these materials need to be modeled to complete the radiometric analysis. The optical system will be further discussed in the Appendix.

### **CHAPTER 3**

### **3 IR Imaging Devices**

#### **3.1 Platinum Silicide Detectors**

In 1973 Shepherd and Yang proposed the development of infrared detector arrays based on the internal photoemission from silicon Schottky barrier diodes [7]. PtSi sensor technology matured with focal plane arrays now containing up to  $1.5 \times 10^6$  pixel elements and noise equivalent differential temperatures (NE $\Delta$ Ts) below 0.1 K. Two different imagers developed at the David Sarnoff Research Center were investigated to determine the best device for the camera design.

### 3.1.1 Metal Semiconductor Junctions

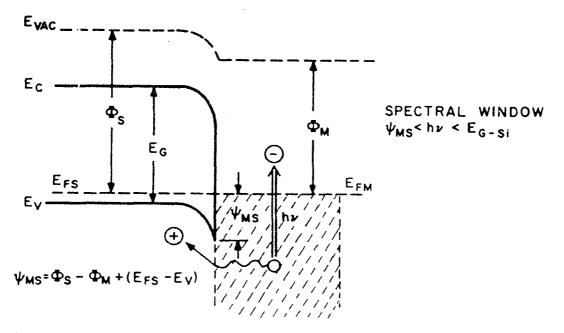

When a metal and a semiconductor are brought into intimate contact, a separation of charges at the interface forms a high resistance region devoid of mobile carriers in the semiconductor. Figure 5 shows the energy band diagram for a metal with a work function  $\phi_m$  and a p-type semiconductor with a work function  $\phi_s$  before and after contact. The gradient of the Fermi level must be invariant so the bands will bend to accommodate the disparity between the affinities of the two materials. The barrier height for holes is given by

$$\phi_b = \chi_s + E_g - \phi_m$$

$$\phi_b = 4.05 + 1.16 - 5.65 = -0.44 \, eV$$

[eV] (16)

where  $E_g$  represents the band gap of the semiconductor [8]. This represents the band bending for a PtSi Schottky barrier diode. The formation of a silicide from the metal will lower this barrier height as will the effects of image charges. The barrier height is found experimentally to be in the range of 0.16-0.23 eV.

Figure 5 Energy band diagram for a PtSi Schottky Barrier Diode

The barrier height can be verified with a variety of methods. Capacitance-voltage measurements yield both the barrier height and the donor concentration as a function of distance. The photoelectric method has proven to be the most accurate way of directly measuring  $\phi_b$  [9]. Monochromatic light in the form of filtered blackbody radiation is incident on the diode with a photon energy greater than the barrier height. The resulting photo generated current can be approximated by a Fowler equation for thermionic emission.

$$J = a \cdot \left(hv - \phi_b\right)^2 \tag{17}$$

Figure 6 Photon yield vs. Energy.

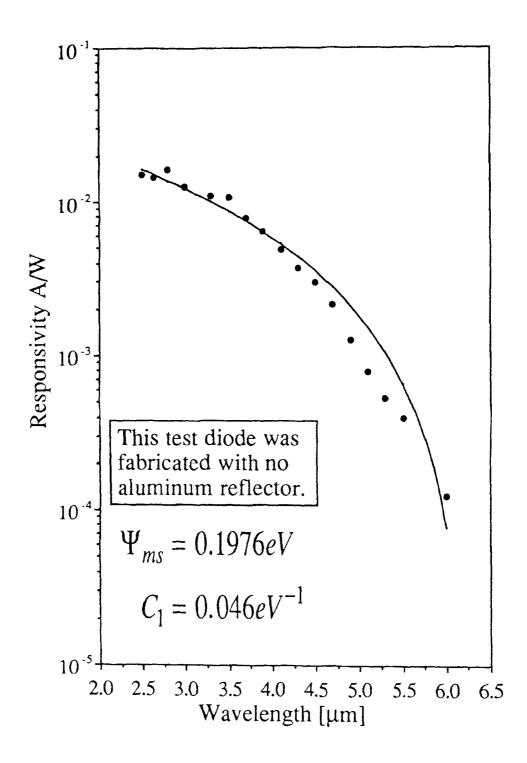

Plotting the square root of the photoresponse as a function of photon energy yields a straight line that determines the barrier height. Shown in Fig. 6 is a photon yield plot from a PtSi test diode. The measured barrier height is 0.1976 eV.

Silicides are formed by depositing a layer of metal on a clean silicon surface and a subsequent thermal annealing at the junction. This causes the metal to diffuse into the silicon and react. Thermal annealing of thin platinum films on silicon leads to formation of Pt<sub>2</sub>Si. After all the Pt is consumed, PtSi begins to form until all Pt<sub>2</sub>Si has been converted to PtSi [10].

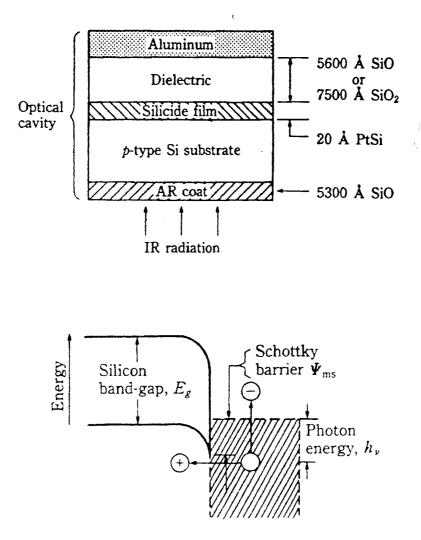

Figure 7 PtSi-Si SBD construction and operation.

The basic construction and operation of the PtSi SBD is shown in Fig. 7. The chip is illuminated from the back side and infrared radiation with photon energy less than the bandgap of silicon (1.16 eV @ 77 K) is transmitted through the silicon substrate. Thus the substrate acts as a long pass filter. Photons with energies greater than the bandgap are absorbed in

the bulk and the electrons recombine without contributing signal charge. The substrate surface is coated with an antireflection layer to increase the coupling of the IR radiation into the SBD by about 30% [3]. The photons are absorbed in the silicide layer.

Carrier momentum is conserved at the junction and carriers with sufficient kinetic energy in the normal direction to the junction can overcome the barrier potential. Holes that have surpassed the barrier ("hot" holes) are injected into the silicon substrate. The electron that is left behind contributes to a net negative charge in the silicide that is proportional to the local image irradiance. The negative charge is transferred into a CCD readout structure after a specific charge integration time as the pixel video signal. The imager responds to radiation with a spectral bandwidth of

$$\Psi_{ms} \langle hv \langle E_g \tag{18}$$

The layer of platinum that is deposited is around 9Å thick and this is followed by a 16-h anneal. The resulting active silicide layer has a thickness of about 20Å [1]. Absorbence is a function of thickness and in order to increase the efficiency, the imager used in this study is fabricated with an optical cavity placed on top of the thin silicide layer. This Fabry-Perot mirror is "tuned" to a wavelength of 4.1 $\mu$ m by separating an aluminum mirror from the silicide with a one quarter wavelength thickness layer of either SiO or SiO<sub>2</sub>. This essentially sets up a standing wave at resonance, maximizing the optical absorbency.

Responsivity [ $\Re$  A/W] is the measurement of a diode's performance to both different signal levels and different frequencies of radiation. The basic test station includes a temperature variable black body source, band pass filters to spectrally decompose the radiation, a current meter and a computer. The responsivity data set is calculated by measuring the detector output and dividing it by the input radiation flux at that wavelength.

$$\Re(\lambda, T, n) = \left[ \epsilon \left[ \frac{I \cdot d_{s-d}^2}{A_{apt} \cdot A_{det} \cdot \int_{0}^{\infty} L(\lambda, T) \cdot \tau_n(\lambda) \cdot d\lambda} \right] \right]$$

[A/W] (19)

\_ \_

where  $L(\lambda,T)$  is the spectral radiance of the black body  $\tau_n(\lambda)$  is the transmission response of filter n  $A_{apt}$  is the limiting aperture area  $A_{det}$  is the detector area  $d_{s-d}$  is the source to detector distance

\_

An enhanced responsivity test station was developed to improve the results of photo yield experiments at DSRC. Improvements included the averaging of readings till a threshold statistical deviation had been reached, the measurement of background current for each bandpass filter, and improved field stops to reduce stray leakage radiation. Shown in Fig. 8 is the measured responsivity of a large area (2.5 X10<sup>5</sup>  $\mu$ m<sup>2</sup>) test diode operating with a reverse bias of 4 volts. It should be noted that the test diode measured did not have a resonating optical cavity. The photoresponse of this device is lower than responses found experimentally with standard diodes.

The data set representing the responsivity readings can be approximated by a Fowler equation [3] as.

$$\Re = C_1 \cdot \left(1 - \frac{\Psi_{ms}\lambda}{hc}\right)^2 \tag{20}$$

where R is the responsivity in [A/W]  $C_1$  is the quantum efficiency coefficient in eV<sup>-1</sup>  $\Psi_{ms}$  is the silicide-semiconductor barrier in eV  $\lambda$  is the wavelength of the radiation in  $\mu m$ .

The yield of the detector can also be determined from the responsivity using the equation

$$Y = \sqrt{\Re} \left( \frac{hc}{\lambda} \right) \tag{21}$$

Where the straight line obtained when Y is plotted against  $E_{photon}$  determines the barrier height.

Figure 8 Responsivity plot of large area (2.5 X105  $\mu$ m<sup>2</sup>) test diode.

### 3.2 Focal Plane Array

Two imagers were analyzed to determine the best device for the camera system. The 320 X 244 IR-CCD [1-3] device can be set-up to operate in either the field or frame readout modes and utilizes charge coupled device (CCD) channels to readout charge to the output amplifier. The charge is transferred from the detectors by a universal transfer pulse. The 640 X 480 IR-MOS imager [4] was evaluated [5] to assess its usefulness in sub-frame integration. The 640 X 480 imager uses MOS transistors to readout the acquired signal from individual pixels by column and row addressing. During normal operation, the signal is read out from the detectors sequentially line by line. Therefore, the time that each line spends integration is offset from each previous line.

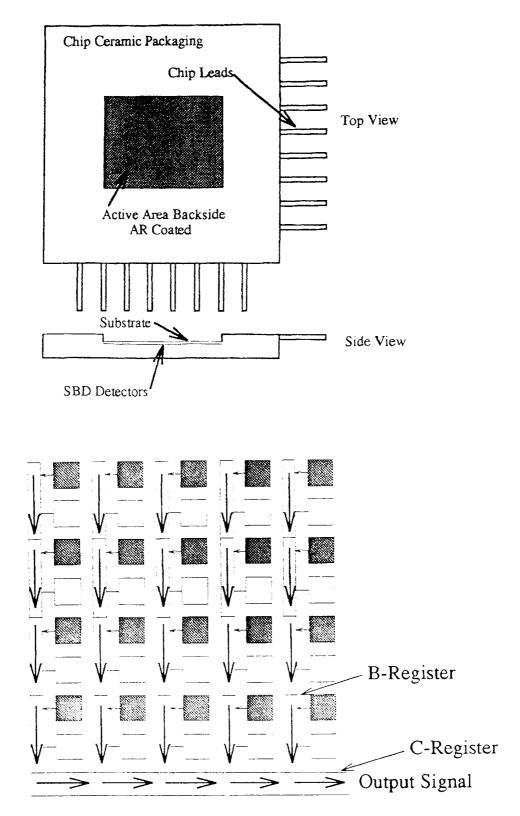

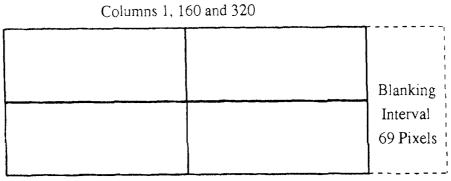

The 320X244 IR-CCD array used for this thesis occupies an active area of 504 mil X 384 mil on 40 X 40  $\mu$ m centers. The optically active area represents 43% of the total device area because detection occurs in SBDs and does not occur in the CCD channels. This differs from visible imagers where the entire array can be photo active. The imager is designed as an interline transfer with two vertical detectors interlaced to the same vertical CCD channel. The operation of two interlaced fields represents frame integration and is done so that the display will contain less flicker and is easier to view. Our application entails machine vision and field integration is the most efficient way of entering video data into the computer. Field integration involves operating the imager with one field (either half the pixels or combining fields together in the form of a double sized pixel) with the frame made up of that field. A schematic of the CCD chip and the array layout is shown on Fig. 9. As stated previously, electrical signal derived from photodetection is allowed to accumulate in the PtSi detectors for a specific charge integration time. A transfer pulse activates the overlapping surface channel CCD (SCCD) by bringing one phase of the B clocks high. The CCDs in this design are fabricated for four-phase operation. This transfers charge from the detectors into the B-registers [vertical buried channel CCDs (BCCDs)]. The B-registers are clocked downward at the line rate of  $63.5 \,\mu$ s. At the same time, the horizontal C-Registers [BCCDs connected to the B-registers at the bottom of the array] are clocked at the pixel rate and read one line of 320 pixels to the on-chip output amplifier in one line time. For a full description of the design and fabrication of the imager chip and the clock signals necessary to operate the imager see Patel [11]. For an understanding into the kinetics of charge transfer in a cryogenically cooled BCCD, see Esposito [12].

The 640 X 480 IR-MOS pixel dimensions are 24X24  $\mu$ m. The pixels are addressed using column and row registers. This allows for spatial sub-frame windowing at higher frame rates. This imager can be operated in the field or frame integration mode. The 640 X 480 imager can be operated in a sub-frame integration mode by clearing the detectors a certain time before interrogating them. IR-MOS imagers developed at DSRC contain an 8:1 MUX to reduce the line capacitance and the kTC noise associated with it. This also allows the resetting of video lines not addressed by the multiplexer. IR-MOS imagers can be reset by biasing the

Figure 9 The 320 X 244 chip (a), and the layout of the SBD array (b)

pixel transistors on the line preceding the readout line to clear the detector. The integration time is then  $T_i = n \cdot 63.55 \mu s$  where n is the number of vertical clock periods between the two lines. Using this operation the integration time can be varied from 60µs to 30ms [4]. Shown in Fig. 10 is the sub-frame integration operation of an IR-MOS imager. This method however does not measure image with the identical exposure time.

# 3.2.1 Spectral Uniformity

When employing individual pixel elements arranged in an array to perform high spatial resolution radiometry, the uniformity in the response of the pixels is essential. Measurements were made to determine the uniformity in both spectral and spatial responses of the focal plane array

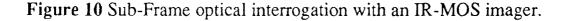

[5]. The experiments were carried out with a DSRC 640 X 480 IR-MOS imager. Figure 11 shows the test camera integrated into the primary evaluation system (additional equipment was utilized for some of the testing). The test apparatus consists of a square radiator, a filter wheel, a current picoammeter, a data acquisition unit, two video digitizers, an Apple MAC IIf x computer and *FrameGrabber* software [13]. These units are consolidated under the computer's control to work as an automated characterization system. The black body source, an Electro Optical Industries (BH2450E) large aperture radiator (with a range of 25 to 170°C), was controlled and monitored using an IEEE-488 interface. Two video digitizers were employed to convert the odd and even video fields into computer data. The test setup was controlled by a computer utilizing software developed at the David Sarnoff Research Center. FrameGrabber is a flexible, high speed, data acquisition software system developed specifically for the characterization of solid state imaging arrays. The video signal is captured and analyzed using a Macintosh graphical interface. FrameGrabber can print the captured image, generate defect lists and uniformity histograms, and calculate multiplicative correction coefficients that can be applied to any acquired frame.

Figure 11 Uniformity test station for PtSi detector arrays.

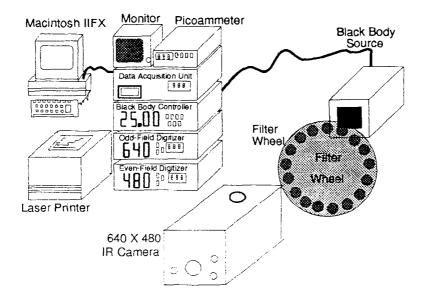

By controlling the temperature and by placing filters between the source and detector, the responsivities of individual pixels can be found. Bandpass filters with sidebands of the order ( $\pm 0.1 \mu$ m) were placed inside the dewar and a constant temperature of 150°C was maintained. Signals were acquired with the *FrameGrabber* software and 16 frames were averaged to make a composite image with reduced temporal noise effects. This image was analyzed to yield measurements of the electrical output signal for ten representative pixels chosen to represent the entire area of the FPA. The spectral responsivity has been defined as the output diode current divided by the input optical power per unit wavelength. Shown in Fig. 11 is the spectral responsivity in A/W as a function of wavelength.

Figure 12 Spectral responsivity of the PtSi array for ten representative pixels.

Also shown is the spectral response of the average pixel. The data in Fig. 12 shows that detectors have practically identical responsivities for the wavelengths of interest (3.5 to 5.5  $\mu$ m). The spectral nonuniformity is estimated to be  $\pm 1.1\%$ . Therefore, pixel to pixel nonuniformities should not vary significantly with incident power spectral density.

# 3.1.2 Spatial Uniformity

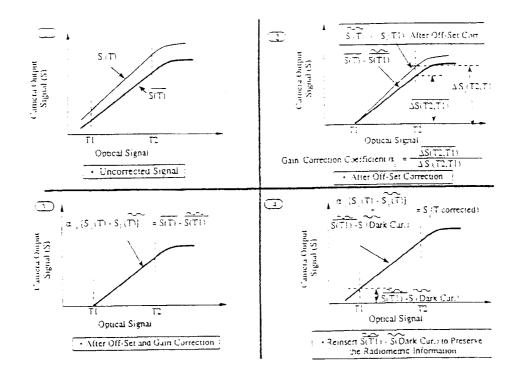

Spatial nonuniformity measures the deviation in a pixel's response to that of the average array response. When the camera is uniformly illuminated, the signal from each pixel in the array should be equal. Furthermore, any change in temperature  $\Delta T$  should induce equal changes in the pixel signal  $\Delta S$ . Due to inherent anomalies in the process of fabricating the imaging chip, nonuniformities in both the offset and slope of the pixel response are present. These nonuniformities need to be corrected for the chip to perform as a radiometer. Correcting for both the slope and offset of individual pixels in an array is called two point correction. Figure 13 shows graphically the procedure for obtaining two point correction<sup>\*</sup>. Part 1 shows the response of any arbitrary uncorrected pixel (i) and the average response of the FPA for two reference

Figure 13 Procedure for obtaining two-point correction.

\* The concept of one and/or two point uniformity correction preserving radiometric accuracy was proposed by W.F. Kosonocky prior to the summer of 1992.

temperatures  $T_1$  and  $T_2$ . The offset has been subtracted in Part 2 at the temperature  $T_1$  from all pixel responses. At this point, the only difference in pixel responses is due to their varying slopes. Gain coefficients are now

29

computed which are used to force the differential response of each pixel to be the same as that of the average pixel. This is shown in Part 3. Illustrated in Part 4, to preserve the radiometric information, the same signal due to  $T_1$  minus the dark current is added to the offset and gain corrected signal of Part 3. The reinserted offset signal can be either average array signal or a local average signal near the center of the imager.

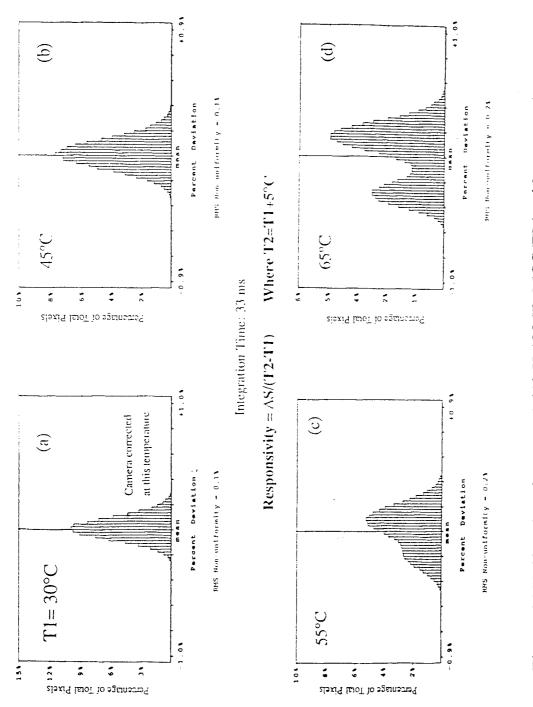

Data was acquired by the FrameGrabber program at two temperatures (T<sub>1</sub> and T<sub>2</sub>=T<sub>1</sub> + 5°C) A 20 frame average of the blackbody radiator scene was used to calculate the uniformity of the array. The mean was calculated as the average pixel amplitude of the scene. The response is the measured change in the amplitude of the pixel at the two different temperature scenes. The mean response is the average calculated response of the array. Percent deviations were calculated and the % rms nonuniformity was calculated from these deviations. Data were taken at temperatures ranging from 25 to 65°C at full frame integration. The camera used for this experiment was a camera equipped with two point correction circuitry. The camera was offset corrected while staring at the blackbody radiator to remove irregularities in the emissivity of the square radiator if any were present. Multiplicative coefficients were generated to correct for nonuniformities encountered while staring at 25°C radiation and were stored in memory. These coefficients were applied to the signals acquired at the various temperatures of this experiment.

Figure 14 illustrates the distributions of the array uniformities for the corrected camera. The histogram plot shows the percentage of pixels along the y-axis versus the percent deviation from the mean along the xaxis. The calculated mean is placed at the center of the x-axis and the number of pixels falling into equally sized bins around the mean are plotted in both directions away from the center. Bins to the left of the mean represent pixels whose displays are darker than average. Fig 14a shows the camera system behaving with high uniformity at the temperature where the coefficients were originally generated. This behavior is expected. As the signal level is increased in Figs. 14(b,c,&d), the detectors respond similarly and the deviation of the pixel response increases only slightly. Above 70°C however, as pixels begin to saturate, the nonuniformities increase dramatically. Also shown in Fig. 14d are two distinct peaks in the plot. This is thought to be due to the uneven responses of the two fields used in the interlaced mode. This deviation is small however.

## 3.3 Variable Sub-Frame Integration Time

The maximum charge storage capability of the SBD detectors is approximately one million electrons. To find the maximum flux density that will saturate the detectors at normal operation.

$$40\mu m \times 40\mu m = 1.6 \times 10^{-5} cm^{2} = A_{d}$$

$$1 \times 10^{6} \times 0.2 = 5 \times 10^{6} \frac{photons}{det} frame$$

$$\Phi_{ph} = 5 \times 10^{6} \frac{photons}{det} frame$$

This calculation assumes an average photo conversion quantum efficiency of 0.20.

$$E[eV] = hv = \frac{hc}{\lambda} = \frac{1.237}{\lambda[\mu m]}$$

$$E(4.0\,\mu m) = 0.3093\,eV$$

$$E = 4.948 \times 10^{-20} \, J/photon$$

$$N = \Phi_{ph} \div A_d = 3.125 \times 10^{11} \, photons/frame \cdot cm^2$$

$$P = N \cdot E \cdot F_{rame} R_{ate} = 4.638 \times 10^{-7} \, W/cm^2$$

This shows the maximum flux (@ 4µm) that the detector can measure without saturating is approximately 0.468  $\mu$ W/cm<sup>2</sup> · To effectively measure

radiances above this level, the absolute time that the detector "looks" at the radiation should be reduced. The detectors are continually gathering electrons so excess charge will quickly accumulate when staring at high temperature scenes. The frame readout time cannot be changed, so the time the detectors spend gathering useful data should be a fraction of the frame time. The operation of the camera with variable integration time requires the detectors be reset at a precise time before transferring the charge to be read out.

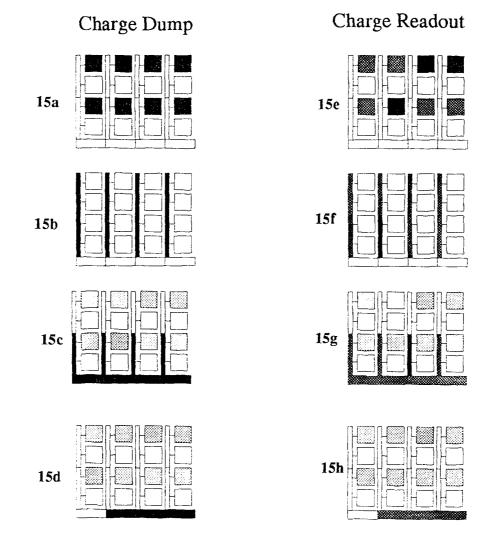

The IR-CCD imager transfers charge from all pixels to the readout simultaneously. This means that the imager essentially takes 'snapshots' of the infrared scene. This made the camera the better choice for our camera design. However, sub-frame integration with IR-CCD imagers cannot be accomplished in the same way as IR-MOS imagers because there is no way to interrogate lines or pixels, and the primary mechanism for removing charge is through the CCD channels. In the IR-MOS, each line is read out sequentially whereas in the IR-CCD readout, the pixels are transferred simultaneously with a universal transfer pulse. To implement integration time control, the charge needs to be swept out through the CCD registers. A dump-and-read procedure was developed to facilitate this clearing of excess charge [14]. To investigate the quickest and most efficient means to clear the excess charge, clocking circuits were developed to allow different frequencies to act as the master clock. The sweep out procedure begins as charge that has accumulated in the detectors from the last transfer pulse is transferred to the B-registers through a transfer pulse. The B-registers are then clocked rapidly and charge immediately saturates the C-registers that are simultaneously clearing charge through the output amplifier. The sweep out procedure is completed as the charge is cleared from all the CCD registers.

A test camera was then retrofitted with the custom clock chip and the charge was swept from the array at different rates. At 12 MHz, the charge was shown to be cleared from the array in two line times. At high illumination, the inefficiency present at this sweep rate becomes significant and increases the sweep time to five lines. The charge is cleared from the B-registers in two lines but three additional lines are required to clear the C-registers. The minimum optical integration time available for this camera is two line times or  $127\mu$ s. To insure radiometrically correct data, the first ten lines of video should be discarded at this integration time, because they contain residue charge from the inefficient sweep procedure. It is important to note that as the charge is being swept out of the CCD channels, photo-charge is accumulating in the SBD detectors. This represents the first charge of the signal data.

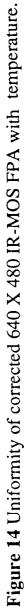

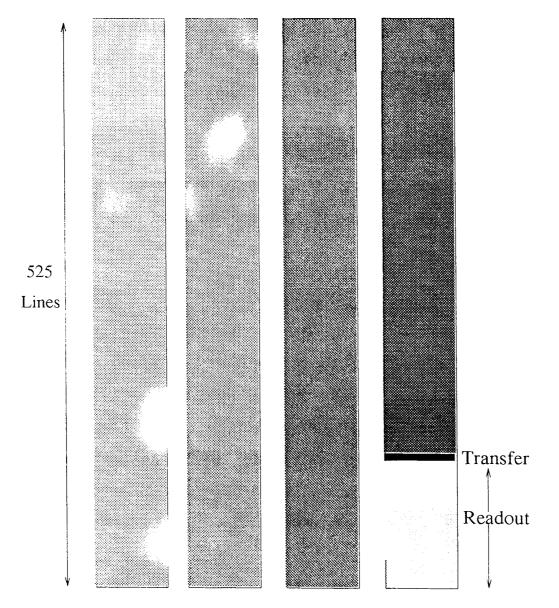

The operation of variable integration timing is shown pictorially in Fig. 15. The first frame 15a begins the sequence with the detectors fully saturated. Clearly shown are the B-registers with two SBD detectors connected to each register. With the camera operation only utilizing half vertical resolution, only one pixel will be used per vertical register. This saturation charge needs to be swept out and is transferred to the B-registers in 15b. In 15c, the charge is clocked down and out at 12MHz/16 from the horizontal register. Shown in 15d, the B-registers are cleared in 127  $\mu$ s. The C-register may contain some residue charge. During the sweep out, charge can be seen collecting in the SBDs. The integration time initialized when dump sequence began and charge was transferred to the B-registers. After the required optical integration time has integrated, the signal charge is transferred to the B-registers in 15f. The charge is then read out at video rate as shown in 15g and 15h. Dump charge for the next sweep out is seen to collect during readout. The variability of integration time can be controlled in increments of line times. The timing diagram of sub-frame optical integration time is shown in Fig. 16. A frame can be thought of as

Figure 15 The operation of the 320 X 122 IR-CCD imager for sub-frame integration.

Figure 16 The timing diagram for variable optical integration time.

525 lines. Taking into account all required timings, one variable is left. The integration time can be set to any integer of line times greater than or equal to zero. The excess dump charge integration is determined from the integration time.

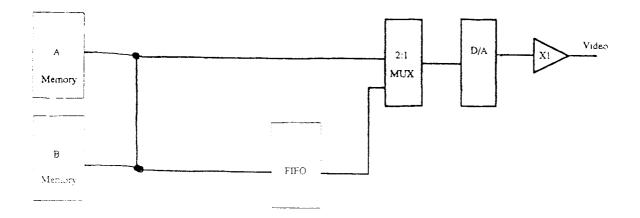

## 3.4 Variable Multi-Frame Integration Time

When imaging scenes of low temperature, the reduction in flux causes a reduction in the amount of charge signal integrated over standard 33 ms operation. This decreases the signal to noise ratio and the response of the camera deviates from linearity. To improve the radiometric performance, the optical integration time should be increased. With the understanding of sub-frame charge integration, it is easy to extend this concept to charge integration times larger than 525 lines. By suppressing the readout at the normal frame rate, the imager is allowed to integrate charge for a certain number of frames before being readout. Shown in Fig. 17 is the timing diagram for supra-frame optical integration. There is no dump procedure, only integration and readout and all charge is used in the signal. This is essential when viewing low radiance scenes. The frame rate of the camera must be decreased because the rate at which new information is generated decreases below 30 frames/s. The maximum integration time is limited by the detector shot noise as this signal is also being accumulated during integration.

# Four Frame Integration

Figure 17 Multi-frame Optical Integration.

## **CHAPTER 4**

#### **4 CAMERA ELECTRONICS**

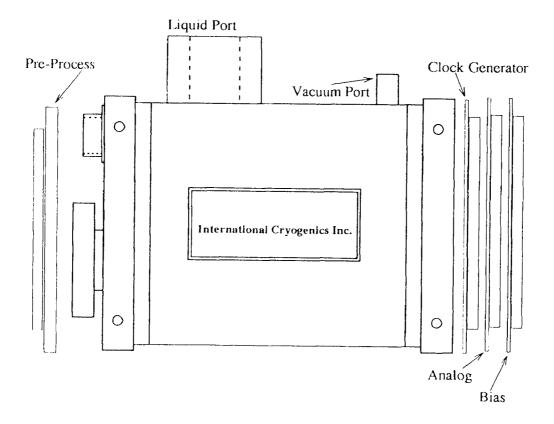

There are two separate units that comprise the total camera system, the camera head and the video processor box. The camera head electronics (with the exception of the custom sequencer board) have been built using the designs and printed circuit boards developed at the David Sarnoff Research Center. These designs are markedly different in their layout than from previous cameras developed for NJIT and described in thesis by Patel [11] and Blume [15].

# 4.1 Camera Head

The camera head consists of four printed circuit boards affixed to the minisized liquid nitrogen dewar. Also affixed to the dewar is the imager chip. The chip is placed in a vacuum chamber with a 2" silicon window to allow incident light to be imaged. The dewar holds 0.5 liters of liquid nitrogen and it is easy to calculate the approximate heat load on the system and the approximate nitrogen replacement time using the Stefan-Boltzmann relation of equation (3). Assume the imager is staring at 1000°C radiation. This radiation can be assumed to fill the sensor's hemispherical field of view,  $\gamma = \pi \cdot A_{chip}$ . Then

$$\Phi = L_{1273} \cdot \pi \cdot A_{wndw} = \sigma \cdot T^{4} \cdot A_{wndw}$$

$$\Phi = 5.67X10^{-8} \left[ W \cdot m^{-2} \cdot K^{-4} \right] \times 1273^{4} \left[ K^{4} \right] \times 10^{-4} \left[ m^{2} \cdot cm^{-2} \right] \times (2 \times 2.54)^{2} \left[ cm^{2} \right] \times \frac{\pi}{4}$$

$$\Phi = 301.8W$$

(22)

Using the heat of vaporization for liquid nitrogen of approx. 752.5 W-liter<sup>1</sup>·h<sup>-1</sup>, The sensor requires 0.4 liters of liquid nitrogen per hour to absorb the heat load in a 2 inch diameter aperture while staring at 1000°C radiation.

The four boards that make up the camera head electronics are:

- Bias Board

Clock Generator or Variable Integration

Sequencer

- Analog Board

- Pre-Process Board

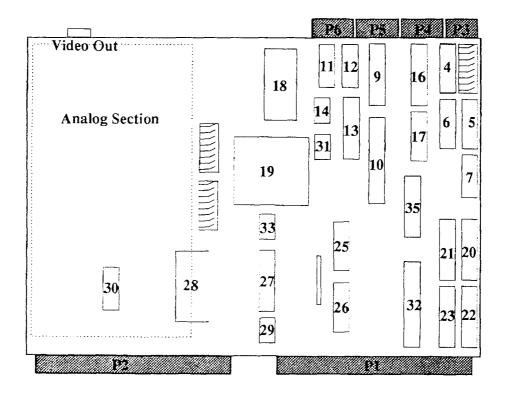

Shown in Fig. 18 is a scale drawing side view of the dewar assembly with the four boards assembled. The entire camera head measures 10.4 X 5.7 X 4.8 inches. The camera head is connected to the video processor by a 34-pin connector cable.

# 4.1.1 Bias Board

The bias board is mounted rearmost and provides back panel access to all analog chip voltage levels set by potentiometers for calibration and adjustment. Probe pins are placed next to each of the 23 potentiometers to allow for convenient connection to measurement equipment. The board has two connectors with connector 1 (60 pin) connected to the back-plane and connector 2 (60 pin) connected to the pre-process board.

# 4.1.2 Analog Board

The analog board resides in front of the bias board to the rear of the camera and provides analog signal amplification and control for transmission to the

Figure 18 Dewar Assembly (side view)

video processor unit. Synchronization pulses provided by the clock board are added to the "raw" signal to provide a composite video signal. The video signal is sent from the pre-process board and is processed by a correlated

double sampling (CDS) unit. This sampling reduces the sampling noise that occurs when more primitive sampling methods are used. For a discussion of CDS circuitry, see Romanowich [16]. Potentiometers external to the camera on its rear panel control the initial gain and offset of the camerafor RS-170 display. The analog board receives these signals and impresses gain and offset onto the sampled video. The synchronization pulses are imposed onto the video and composite video is routed to an SMA connector at the rear of the camera. This video may be used to display the image on a standard RS-170 monitor or may be sent to the video processor. Two ribbon connectors attach this board to the camera system. Connector 1 (60 pin) is connected to the back plane and Connector 2 (14 pin) is connected to the gain/offset pots.

#### 4.1.3 Pre-Process Board

The pre-process board is located at the front of the dewar, near the imager chip. The board is shaped like a horseshoe to allow for the installation of the cold shield assembly. The board is connected to the imager chip via a 22 pin hermetically sealed gold connector. The connector provides electrical access to the vacuum chamber. All input bias and clock signals as well as output pixel data are sent via this connector. Biases sent to the pre-process board from the bias board are buffered and routed to the dewar connector. Clock biases are imposed on clock signals generated in the clock board and drive the CCD imager with clock phases timed and biased for optimal performance. The output video is buffered with a low-noise buffer amplifier and the pixel data are amplified on board before being sent to the analog board. There are three ribbon connectors that are connected to the bias board. Connector 1 has 26 pins, Connector 2 and Connector 3 each contain 14 pins.

## 4.1.4 Standard Clock Generator

The standard clock generator contains a programmable gate array (PGA) that is programmed to operate the imager at 320 X 244 resolution with interlaced 30 frames/sec display. Interlaced operation is a frame integration mode [1-3] where the field rate is 60 frames/sec and alternating fields are overlapped to prevent flicker effects in the display. Flicker is a psychophysical effect and interlacing the frame accomplishes the same flicker reduction as increasing the frame rate [17]. The resulting output conforms to the RS-170 format [18], suitable for display standard NTSC compatible monitors.

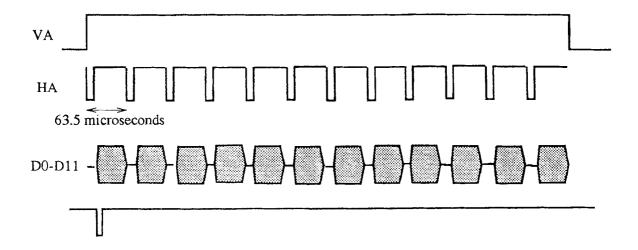

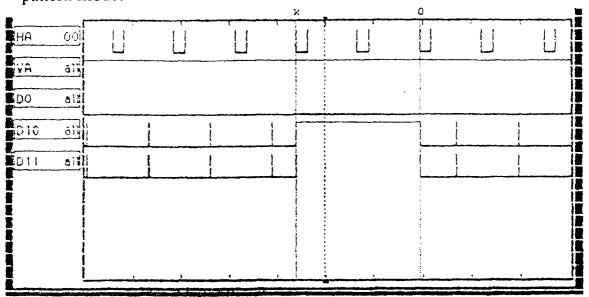

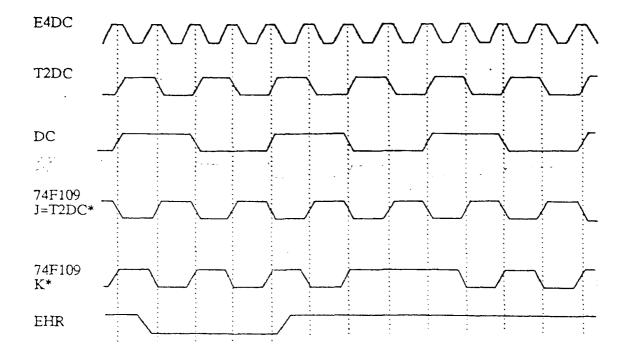

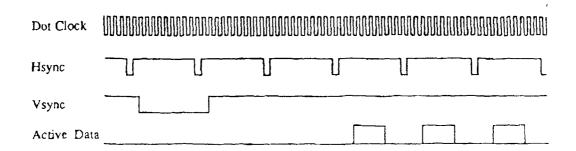

The signals generated to synchronize the processor are vertical active (VA), horizontal active (HA), system clock (CLOCK), horizontal sync (HSYNC), and camera lock (LOCK). The relationship between these signals in the standard mode of operation is shown in Fig. 19. The VA pulse is active high at the start of the frame. It is followed immediately by a falling edge of HA. HA is active high for 52  $\mu$ s after an 11.5  $\mu$ s blanking period and the rising edge of HA signals the start of a line. CLOCK is a 12 MHz signal with 50% duty cycle. The CLOCK is used to synchronize all operations. HSYNC provides a synchronization signal to create the front and back "porches" needed to run on an NTSC system. LOCK is a negative pulse one pixel wide at a rate of 30 Hz that is pulsed immediately following the rising edge of VA if present. The measured signals are shown in Fig. 20.

Figure 19 Timing Relationships for Normal Operation of 320 X 244 Camera.

Figure 20 Measured Timing Signals in Normal Operation.

This board was constructed to allow for the standard operation of the camera with full resolution video imagery. It also facilitated the testing of the camera at an early stage, and so data comparisons between existing cameras could be done. The clock generator board sits in front of the analog board, at the rear and adjacent to the dewar. Two connectors are needed to connect this board to the system. Connector 1 (60 pins) is connected to the back plane while Connector 2 (40 pin) is connected to the 34 pin cable connecting the processor and the head. All power and non-video data communication is contained in this connection. A power harness was fabricated to allow for the testing of the camera head without the need for the processor box by mimicking Connector 2 and its power pin connections. Power supply connections (banana) are marked to allow for the autonomous operation of the camera head with suitable bench power supplies.

## 4.2 Variable Integration Sequencer

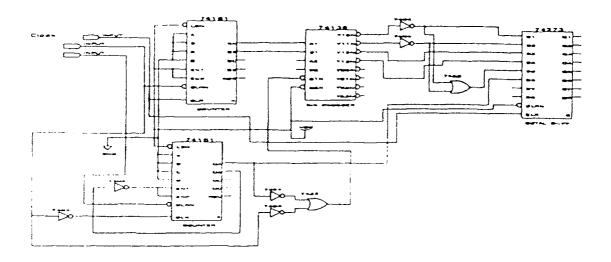

This board was custom designed for the specific application outlined in this thesis. This board receives a four-bit nibble representing the integration time suggested by the video processor box and automatically sequences the operations required to perform the dump and read procedure described in the previous chapter. There are four operating modes of the sequencer in any integration time: READOUT, DUMP, TRANSFER, and SWEEPOUT. The integration time is input to a differential receiver (SN75ALS193) and input to a XILINX (XC3042-PC84) fieldprogrammable gate array (FPGA). The array provides pulses to the standalone microsequencer (SAM) to generate the proper transfer and CCD clock pulses to perform variable integration. The XILINX FPGA provides pulses DUMP, SWEEP, and TRANS to the Altera (EPS448) SAM. The SAM is user configurable and is a function-specific programmable statemachine. The internal EPROM memory allow up to 448 unique states to be specified and contains an internal clock and a pipeline register for high speed output state transition operation. By impressing a "1" to any of the three inputs, the SAM switches to one of three modes.

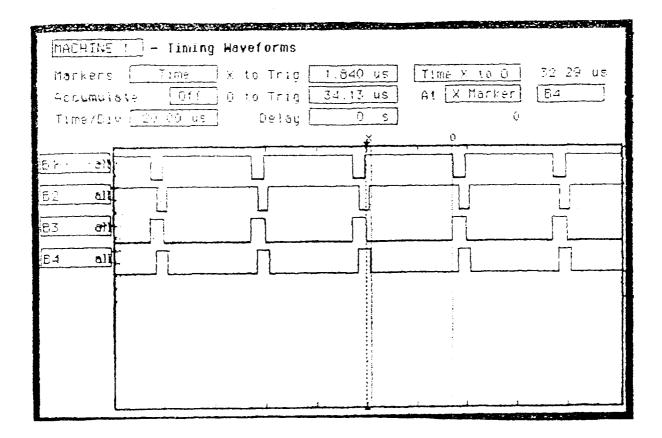

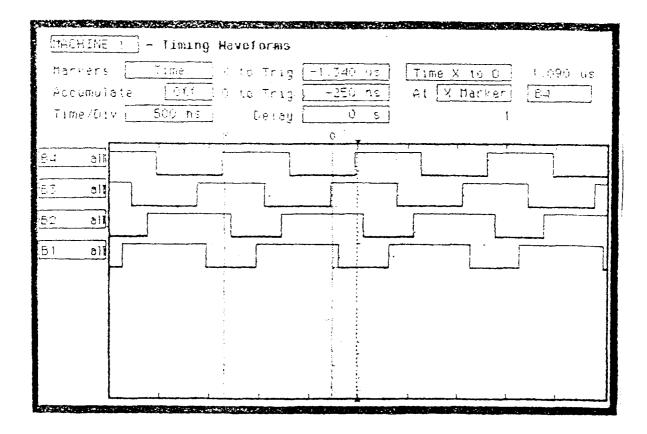

The operation of variable integration will be explained by "walking through" a sample cycle beginning with the charge transfer and ending with a high speed sweep of dump charge. If the TRANFER pin is at logic 1, the SAM will be placed in the TRANSFER mode. In the TRANSFER mode, the SAM is programmed to pulse the proper B-phase with a transfer pulse to clear the detectors and drive the contents into the B-register. The beginning of the line clears the register with 31 high speed B-clocks. The diode transfer pulse occurs after the phase between the C and B registers is set. The transfer pulse is approximately 10  $\mu$ s. The C-register is clocked during transfer to sweep out any excess charge. Shown in Fig. 21 is the general measured relationship of the clocks during transfer.

|                  | -                                        |                                         |             |              |                 |

|------------------|------------------------------------------|-----------------------------------------|-------------|--------------|-----------------|

|                  | ามส.ล                                    | A to Trig                               | 10.90 as    | Time × tc 0  | 12 <u>26</u> 37 |

|                  |                                          | 2 to Trig                               | 13.16 US    | At X Marier- |                 |

| 5:12 <u>- 19</u> | .00 us ∣                                 | Delay                                   | 5,980 us    |              |                 |

| ·····            |                                          |                                         |             | <u>.</u>     |                 |

| alt              |                                          |                                         |             |              |                 |

|                  | ากการการการการการการการการการการการการกา | ៣០.៣៣៣៣៣៣៣៣៣៣៣៣៣៣៣៣៣៣៣៣៣៣៣៣៣៣៣៣៣៣៣៣៣៣៣៣ |             |              |                 |

|                  |                                          |                                         |             |              |                 |

|                  |                                          |                                         | 1           |              |                 |

|                  |                                          |                                         |             |              |                 |

|                  |                                          |                                         |             |              |                 |

|                  |                                          |                                         |             |              |                 |

|                  |                                          |                                         | -<br>-<br>- |              |                 |

|                  |                                          |                                         |             |              |                 |

|                  |                                          |                                         |             |              |                 |

|                  |                                          |                                         | -           |              |                 |

|                  |                                          |                                         |             |              |                 |

|                  |                                          |                                         | Delay       |              | <u>- x a</u>    |

Figure 21 TRANSFER mode waveforms (measured).

If all three control pulses are at logic 0 the SAM is placed in the readout mode. In the READOUT (default) mode, the B-clocks are operated for four-phase standard operation at the line rate of 63.55  $\mu$ s. The C-clocks operate in four-phase readout at the pixel rate. Several additional C-clock pulses occur after the falling edge of HSYNC to provide for overscan. Figure 22 illustrates the clock waveforms in the READOUT mode.

Figure 22 READOUT mode waveforms (measured).

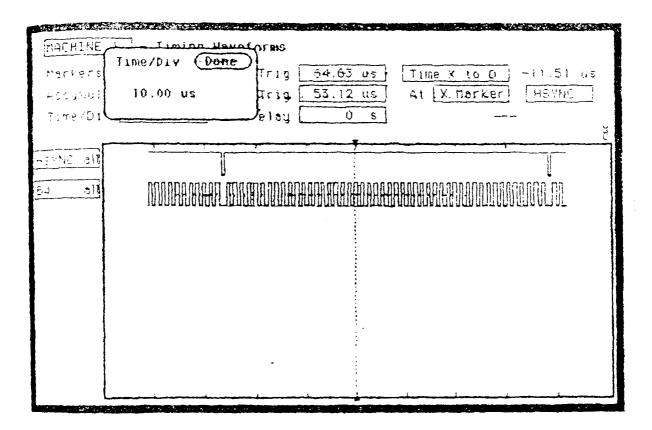

After READOUT, the detectors have been integrating dump charge. By impressing a "1" on the DUMP pin of the SAM, the DUMP operation begins. This mode is similar to the TRANSFER mode, however, there are no clear pulses for the B-register and the beginning of the line starts with a 10ms long transfer pulse. The B-clocks are run continuously at the high rate of 750 X 10<sup>3</sup> transfers/s. The C-register is also being clocked continuously including overscan. At the end of the line, the timing generator internal to the SAM checks to see the next state sequence. Fig. 23 shows the waveforms associated with the DUMP mode.

Figure 23 DUMP mode waveforms (measured).

The SWEEP mode continues the clearing of dump charge that was initiated in the DUMP operation. Both the B and C clocks are operated continuously at high speed to remove charge from the registers. Shown in Fig. 24 are the waveforms associated with the SWEEP mode of operation.

Figure 24 SWEEP mode waveforms (measured)

It should be noted that the state of the pulse applied to the SAM should be stable while HSYNC is low. The XYLINX provides the pulses in the correct sequence and at the proper time. The timing diagrams of Figs. 16 and 17 provide all the information necessary to properly time the sequence for any integration time.

# **CHAPTER 5**

# **5 VIDEO PROCESSOR**

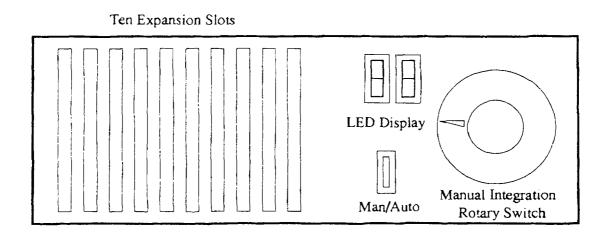

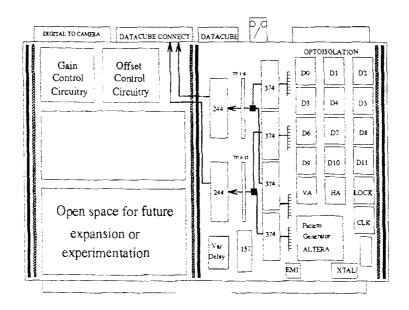

The video processor provides digital conversion and manipulation for signal processing. The video processor also provides feedback (either manual or automatic) to control the optical integration time. The main user interface is through the processor and the ports which connect the camera to other computing and control equipment is through the processor. The processor box contains all the power supplies necessary to run the processor and the camera head. The box measures 17 X 18 X 5.5 inches and contains a card cage with 10 slots to provide for adaptability and easy maintenance. PC-type edge connector cards with 102-pin Euro connectors are used and the card cage back plane is set up with the data stream running from left to right when viewed from the front. This means that the order that the cards are placed in the cage is critical. Shown in Fig. 25 is a drawing of the processor box.

Figure 25 The video processor.

While there are no necessary boards required to operate the camera, the analog to digital (ADC) board and the output board are required to operate the camera with the Datacube. Datacube is needed to provide flexible real time digital video processing capabilities. Currently there are five boards completed for implementation in the processor.

- A/D Board Test Board

- Multifunction Board Jumper Board

- I/O Board

## 5.1 Analog to Digital Conversion

The video signal that arrives at the video processor port is in sampled analog form. The pixels are discrete packages of information in analog form streaming in at approximately 6 Msamples/s. The video signal is digitized with 12-bit resolution by utilizing the Burr-Brown 10MHz 12-bit A/D converter (ADC603H). The ADC converts analog signals with a full scale range of -1.25 to +1.25 volts. The conversion is enabled by the clock pulse acting as the sample. On-board digital delay circuitry insures that the clock pulse is positioned at the center of the pixel to obtain the most accurate sampling. The data is converted into inverted two's complement form. The MSB of the data is inverted to convert the word into pure binary representation. The conversion is shown graphically in Table 2.

Therefore the data can assume 4096 discrete states with each state corresponding to a voltage change of 0.61 mV. This is the resolution of the converter board. The conversion linearity error is listed as  $\pm 0.5$  LSB [19].

| Analog Signal | Inverted 2's    | True Binary   | Decimal |

|---------------|-----------------|---------------|---------|

| Level         | Complement      | MSB           | Value   |

| + Full Scale  | 011111111111    | 111111111111  | 4096    |

| + 0.75 Scale  | 01100000000     | 111000000000  | 3584    |

| + 0.50 Scale  | 01000000000     | 1100000000000 | 3072    |

| + 0.25 Scale  | 00100000000     | 1010000000000 | 2560    |

| + 1 Bit       | 000000000001    | 1000000000001 | 2049    |

| Zero          | 000000000000000 | 1000000000000 | 2048    |

| - 1 Bit       | 111111111111    | 0111111111111 | 2047    |

| - 0.25 Scale  | 111000000000    | 011000000000  | 1536    |

| - 0.50 Scale  | 11000000000     | 010000000000  | 1024    |

| - 0.75 Scale  | 10100000000     | 00100000000   | 512     |

| - Full Scale  | 10000000000     | 000000000000  | 0       |

Table 2 True binary conversion from the output of the ADC 603 chip

The digital data is then sent to the next board in the stream but is also available and ported to the rear of the processor box as uncorrected digital video. The next board in line to process video is the multifunction board. A board was developed to simulate the A/D board and it provides test patterns for evaluation of the processor box.

#### 5.2 Simulator Board

The Simulator board resides in the same slot as the ADC board. By replacing the ADC board, the Simulator board emulates a temporally and spatially noise-free digital pixel stream. The board consists of two pattern generators and twelve 2:1 multiplexers to choose one of the two patterns. The patterns are generated from the control signals sent from the camera head (VA, HA, and CLOCK). The patterns simulate a horizontal ramp assuming all pixel values and a set of sixteen horizontal bars of multi-line width. The board allows the evaluation of the digital noise generation in the video processor, enables the investigation of the least significant bit operation as the camera noise de-stabilizes these pixel values, and allows for accurate linearity testing of processor components and computer interfaces.

The first test pattern produces a linear ramp across each line by clocking an 8-bit counter circuit at the pixel rate and applying the count as the 8-MSBs of the digital stream. The 4-LSBs are held at logic 0. The count is cleared at the beginning of each line producing a pattern that increases in intensity to column 256 and repeats to column 320. The count is disabled during ( $\overline{VA} \cup \overline{HA}$ .)

The second test pattern is generated by clocking an 8-bit counter at the line rate (HA) and applying the count to the 8-MSBs of the digital video bus. The 4-LSBs are all set to logic 1. The count is cleared at the beginning of the frame and counting is disabled during ( $\overline{VA}$ ). The pattern appears as horizontal bars increasing in intensity with each row. Shown in Fig. 26 are the actual test patterns generated by the camera and input into the Datacube system. The images were acquired and stored with a Sun computer. The images were subsequently transferred in digital format over the INTERNET computer network to another computer system and printed.

Figure 26 Test-pattern images acquired and stored by a Sun computer.

#### 5.3 Multi-Function Board

The radiometer is designed to automatically control the exposure time and relay the exposure time to the processing computer. A time base must also be generated to coordinate the data acquired from other diagnostic equipment. These functions are performed on the multifunction board. This board resides in the video processor box directly downstream from the A/D or Simulator boards.

#### 5.3.1 Head Receiver

This circuitry receives differential data transmitted from the camera head representing all timing signals generated there and transforms them into single ended TTL signals suitable for further processing. Two SN75ALS193 differential receivers are used to accept differential control signals from the camera head. These signals are input with the 12-bit data to a 16-bit latch constructed from 74ALS273 Octal D-Type flip flops. All signals are now latched on to the board with the came clock pulse and are lined up in time.

## **5.3.2** Variable Integration Time with Front Panel Display

The camera's integration time can be analogized as the exposure time in a film camera system. As the photon flux density increases, the charge saturation signal (approx.1X10<sup>6</sup> electrons) of the SBD pixels is approached. The integration time must then be reduced to provide a non saturating signal that lies in the linear response region of the camera. Equally important, if the photon flux rate decreases, the integration time must be increased to keep the signal in the linear portion of the response as well as to preserve the signal to nose ratio at a respectable level. The frame may be considered the collection of 39040 pixels and the design of a robust control circuit for the integration time must be flexible. The control scheme compares the pixel signals individually and then decides upon action after considering the state of the entire ensemble of pixels that make up the frame.

The control of the optical integration time is performed digitally for greater flexibility, lack of drift and ease in implementation. The video signal is compared against preset levels to determine the state of the pixel. This is accomplished with 74LS682 Octal Flash Comparators that output a zero whenever the P (video) inputs exceed the Q (switch) inputs. In the case of white pixels, the Q inputs are provided by an octal DIP switch wired to represent logical signals. Pixels that are out of these preset ranges are counted and compared against preset total pixel counts pre-stored onboard. The white level is set to the top eight video bits (D04 to D11), representing signals ranging from 0.36% to 99.63% of the full well signal. The Black level is set with th P inputs logically switched with an octal DIP switch to the video bit signals D03 to D10, representing signals ranging from 0.17% to 49.82% of the full well signal. The pixel counts are chosen from the top eight bits of a sixteen bit pixel counter. These thresholds are summarized in Table 3.

| Threshold   | Lowest       | Percent of | Highest      | Percent of |

|-------------|--------------|------------|--------------|------------|

| Type        | Count        | Total      | Count        | Total      |

| White Pixel | 000000001111 | 0.36%      | 111111110000 | 99.63%     |

|             | (15)         | (4095)     | (4080)       | (4095)     |

| Black Pixel | 000000000111 | 0.17%      | 011111111000 | 49.82%     |

|             | (7)          | (4095)     | (2040)       | (4095)     |

| Pixel Count | 00FFH        | 0.65%      | FF00H        | 100%       |

| (B/W)       | (255)        | (39040*)   | (65280)      | (39040)    |

Table 3 Threshold levels as a percentage of full well signal.

\* This represents the pixel count for 320X122 pixels (9880H). Setting the pixel count threshold higher than 9880H will disable the automatic integration time for black and/or white pixels.

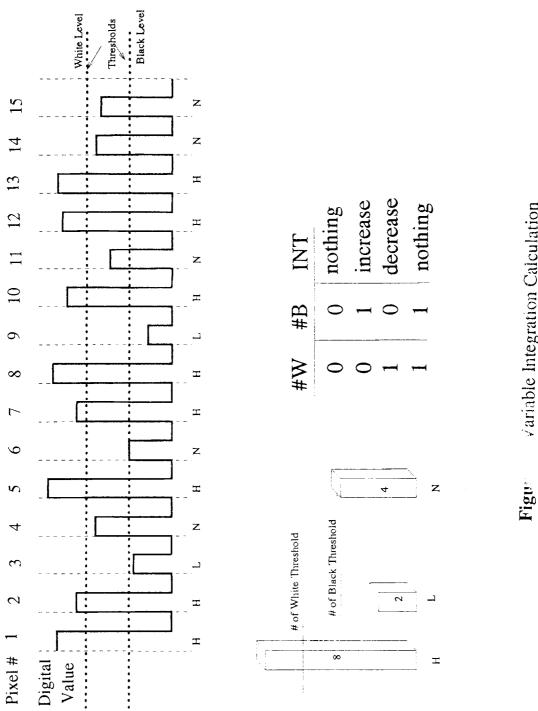

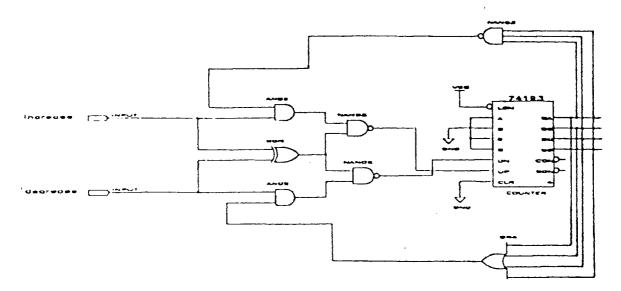

The method employed in this effort is shown symbolically in Fig. 27. The data are shown streaming from left to right with their bar heights proportional to their magnitude. Gating circuitry insures that only valid pixels are compared by enabling flash comparison only during (VA AND HA) pulses. Also shown are the black and white threshold levels which are user settable from on-board 8-pin DIP switches. Pixels that exceed the white level are tagged as high and pixels that fall below the black level are deemed low. Pixels that fall between the levels are set as neutral. These pixels are counted separately and stored in two registers (16-bit counters 74LS161). At the end of the frame, the signal  $\overline{VA}$  latches these totals (74LS274) and compares the top eight bits of the counts against the pixel count thresholds for both black and white totals. The signals TOOLITE and TOODARK are used as inputs to a combinational logic circuit that performs the operation shown in the truth table at the bottom of Fig. 27.

Variable Integration Calculation

59