# **Copyright Warning & Restrictions**

The copyright law of the United States (Title 17, United States Code) governs the making of photocopies or other reproductions of copyrighted material.

Under certain conditions specified in the law, libraries and archives are authorized to furnish a photocopy or other reproduction. One of these specified conditions is that the photocopy or reproduction is not to be "used for any purpose other than private study, scholarship, or research." If a, user makes a request for, or later uses, a photocopy or reproduction for purposes in excess of "fair use" that user may be liable for copyright infringement,

This institution reserves the right to refuse to accept a copying order if, in its judgment, fulfillment of the order would involve violation of copyright law.

Please Note: The author retains the copyright while the New Jersey Institute of Technology reserves the right to distribute this thesis or dissertation

Printing note: If you do not wish to print this page, then select "Pages from: first page # to: last page #" on the print dialog screen

The Van Houten library has removed some of the personal information and all signatures from the approval page and biographical sketches of theses and dissertations in order to protect the identity of NJIT graduates and faculty.

### ABSTRACT

### Monolithic Silicon Opto-Electro-Mechanical Light Modulator

### by Ching-Horng Wu

A Fabry-Perot light beam modulator of the reflection-type has been designed with process and performance parameters optimized. This design takes advantage of the economies of surface micromaching using silicon substrates and selected thin films. High performance with a low drive voltage are achieved using electrostatic actuation of a thin polysilicon diaphragm. The diaphragm is a novel corrugated structure which has maximum compliance and maintains planarity during actuation. In addition, the corrugationsuspension used provides an improved linearity of amplitude modulation response as a function of the actuation voltage.

A preliminary version of this device has been fabricated through a contract foundry using some industry-standard film thicknesses. The preliminary version of the device confirms the physical mask design without optimal film processing. The optimized Fabry-Perot structure is designed for operation at a wavelength of 1.3 nm. Using a thin, corrugated diaphragm of 190 nm thickness a 48.90% modulation index is obtained with an actuation voltage of 5 volts based on detailed simulation results. The final optimized device will be fabricated at NJIT at a future date.

The proposed optimized device contains a titanium-tungsten metal film deposited into a cavity of half wavelength depth and insulated from the monolithic silicon substrate. An additional quarter wavelength film of silicon nitride is deposited over the metal to increase the modulation index. In the fabrication process a 325nm sacrificial film of spinon glass is deposited to fill the cavity and form the spacer between the Fabry-Perot etalon entrance and reflecting surfaces. The optical entrance surface is obtained next in the fabrication process by depositing an infrared-transmissive film of polysilicon. The selected polysilicon thickness is 190 nm or any odd integer multiple of a half wavelength.

This device can be used as an economical light modulator in near-infrared communications and control systems. This device suitable for relatively low bandwidth applications is expected to provide cost and reliability advantages over competing torsion mirror and macro-sized modulators.

### MONOLITHIC SILICON OPTO-ELECTRO-MECHANICAL LIGHT MODULATOR

by Ching-Horng Wu

A Thesis Submitted to the Faculty of New Jersey Institute of Technology in Partial Fulfillment of the Requirements for the Degree of Master of Science in Electrical Engineering

Department of Electrical and Computer Engineering

May, 1993

$\bigcirc$  $\langle$

### **APPROVAL PAGE**

Monolithic Silicon Opto-Electro-Mechanical Light Modulator

Ching-Horng Wu

Dr. William N. Carr, Thesis Adviser Professor and Holder of Sponsored Chair in Microelectronics, NJIT

Dr. Edip Niver, Committee Member Associate Professor of Electrical Engineering, NJIT

Dr. Robert B. Marcus, Committee Member Research Professor of Applied Physics, NJIT

Dr. Farmer, Kenneth R., Committee Member Assistant Professor of Physics, NJIT

### **BIOGRAPHICAL SKETCH**

Author: Ching-Horng Wu

Degree: Master of Science in Electrical Engineering

**Date:** May 1993

### **Undergraduate and Graduate Education:**

- Master of Science in Electrical Engineering, New Jersey Institute of Technology, Newark, NJ, 1993

- Bachelor of Science in Electrical Engineering, Feng-Chia University, Taichung, Taiwan, R. O. C., 1991

Major: Electrical Engineering

To my parents

### ACKNOWLEDGMENT

The author would like to express his sincere gratitude to his supervisor, Dr. William N. Carr, for his guidance, friendship, and moral support throughout this work. Especially thanks Dr. Carr sent him to Mentor Graphics Co., San Jose, CA. taking training courses which is great helpful for this work.

Special thanks to Professor Niver, Professor Marcus, and Professor Farmer for serving as members of the committee.

The author appreciates the kindly help, suggestions and discussion from Michael Grieco, Michael Berry, Dr. Xiaoyi Gu, Chang-Joo Kim, Chao Ye, and Chao Sun.

The author also appreciates the help from MCNC labs.

And finally, the author would like to thank his parents and Pingyu Wang for their love and encouragement. He also wants to express his thanks to his grandparents for their encouragement and they both died in February, 1993.

### TABLE OF CONTENTS

| Chapter Page                                |

|---------------------------------------------|

| 1 INTRODUCTION                              |

| 1.1 Thesis Description 1                    |

| 1.2 Fabry Perot Etalon                      |

| 1.3 Silicon Micromechanics 4                |

| 1.4 Bulk Micromechanics Technology 5        |

| 1.5 Surface Micromechanics Technology 7     |

| 1.6 Cavity Micromechanical Sensor Structure |

| 2 FABRY-PEROT ETALON 12                     |

| 2.1 Principles of Operation                 |

| 2.2 Previous Work                           |

| 2.3 This Thesis Device                      |

| 3 PERFORMANCE DESIGN OF THE LIGHT MODULATOR |

| 3.1 Introduction                            |

| 3.2 Device Geometry                         |

| 3.3 Electrostatic Force Model               |

| 3.4 Optical Transmission                    |

| 3.5 Mechanics of Corrugated Diaphragm       |

| 3.6 Results and Discussion                  |

| 4 MASK DESIGN AND PROCESS PROCEDURE         |

| 4.1 Device Structure                        |

| Chapter Pag                                         | ge |

|-----------------------------------------------------|----|

| 4.2 Mask Design                                     | 51 |

| 4.3 Process Description                             | 60 |

| 5 TECHNIQUES FOR FABRICATION                        | 88 |

| 5.1 Fabrication of Cavity using a Sacrificial Layer | 88 |

| 5.2 SOG Processing                                  | 89 |

| 5.3 The Corrugated Silicon Diaphragm Structure      | 92 |

| 6 APPLICATION                                       | 94 |

| 7 CONCLUSIONS                                       | 97 |

| APPENDIX A: PHYSICAL LAYOUT FOR MCNC FOUNDRY        | 98 |

| APPENDIX B: PHYSICAL LAYOUT FOR NJIT MRC11          | 16 |

| APPENDIX C: DEVICE WITH INCREASED SENSITIVITY       | 24 |

| REFERENCES                                          | 27 |

### LIST OF TABLES

| Tables                                                                          | Page |

|---------------------------------------------------------------------------------|------|

| 4.1 Compared advantages of two metals (Al and W) according to VLSI requirements |      |

| 4.2 Properties of LPCVD Silicon Nitride                                         | 71   |

| 4.3 Properties of Aluminum and Aluminum Alloy thin films                        | 81   |

| 7.1 Compared three different designed FPI                                       | 97   |

| Figure                                                                                                                                                    | lage   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| 1.1 From Airy (1831, figure 17)                                                                                                                           | 3      |

| 1.2 Cross section of a typical sensor device formed using<br>anisotropic and selective etching techniques                                                 | 7      |

| 1.3 Anisotropic etching on [100] and [110] surface                                                                                                        | 7      |

| 1.4 The processing sequence of polysilicon cantilever and double supported beam                                                                           | 9      |

| 2.1 Multiple reflections model for analyzing the Fabry-Perot etalon                                                                                       | 15     |

| 2.2 Two successive reflections                                                                                                                            | 15     |

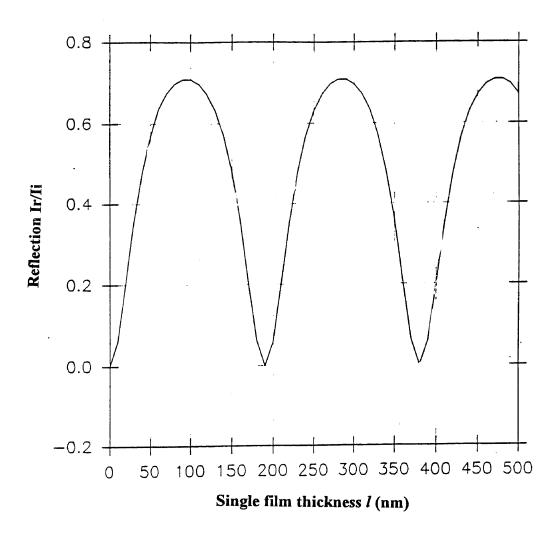

| 2.3a Transmission characteristics of a thin film                                                                                                          | 17     |

| 2.3b Reflection characteristics of a thin film                                                                                                            | 18     |

| 2.4a Calculated reflection characteristics of a Fabry-Perot etalon<br>at $\lambda$ =1300nm as a function of the etalon optical length                     | 19     |

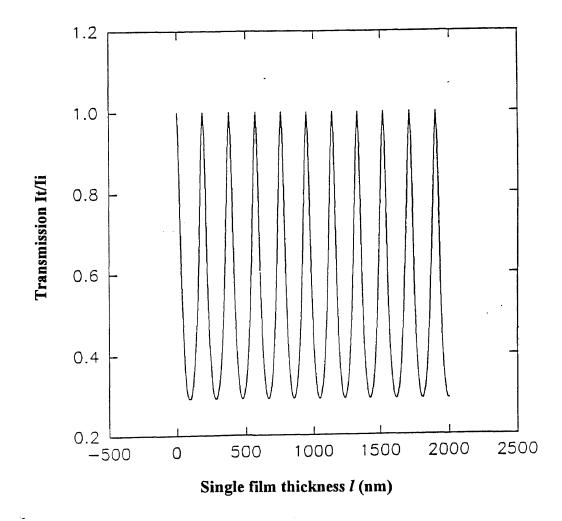

| 2.4b Calculated transmission characteristics of a Fabry-Perot etalon<br>at $\lambda$ =1300nm as a function of the etalon optical length ( 0 < l < 2000nm) | ····20 |

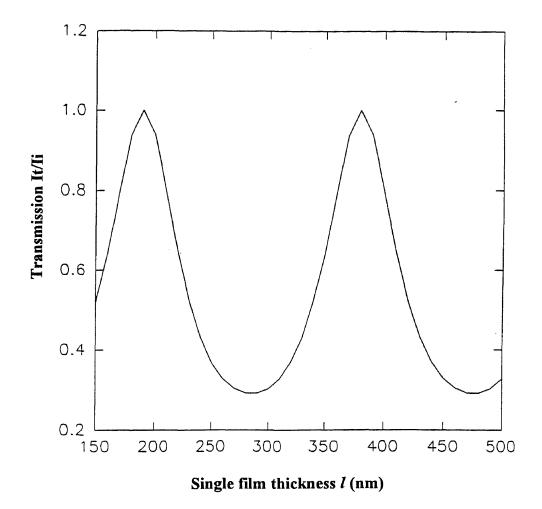

| 2.4c Calculated transmission characteristics of a Fabry-Perot etalon<br>at $\lambda$ =1300nm as a function of the etalon optical length                   | 21     |

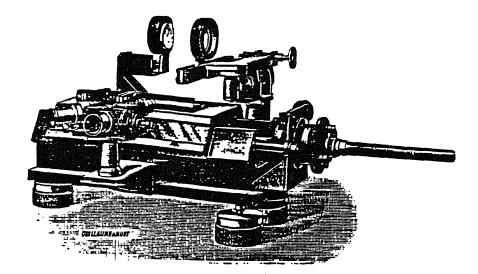

| 2.5 The highly engineered interferometer built by<br>M Jobin for Fabry and Perot are described and illustrated in 1901                                    | 23     |

| 2.6 A photograph of interference rings of the green mercury line<br>shown by Fabry and Perot in 1901                                                      | 23     |

| 2.7 A fixed etalon or standard of thickness developed by<br>Fabry and Perot for measurement on arc and solar lines                                        | 24     |

| 2.8 Interference fringes photographed by Barnes (1904) under various conditions of plate separation                                                       | 24     |

| 2.9 The original idea of this thesis device                                                                                                               | : 25   |

| 3.1 The first generation of FPI                                                                                                                           | 27     |

Figure

### Page

| 3.2 Cross-sectional schematic view of second-generation reflection type FPI           | 27  |

|---------------------------------------------------------------------------------------|-----|

| 3.3 Cross-sectional schematic view of third-generation reflection type FPI            | .28 |

| 3.4 Applied voltages vs. modulation lengths (with corrugation)                        | .34 |

| 3.5 Applied voltages vs. modulation lengths (without corrugation)                     | 34  |

| 3.6 The overall light path of this device                                             | 35  |

| 3.7 The top sandwich construction of this device                                      | 36  |

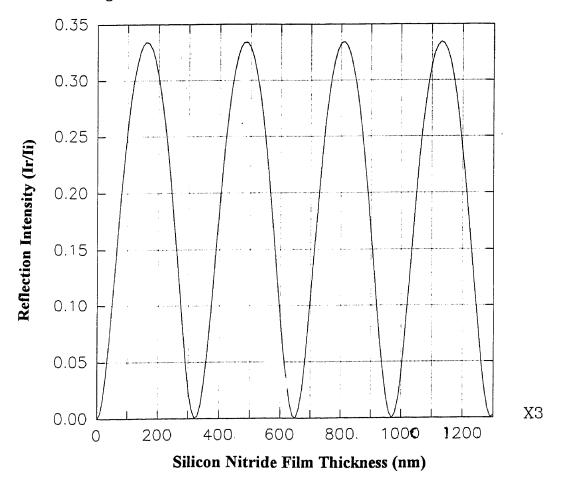

| 3.8 Light reflection intensity vs. polysilicon film thickness                         | 36  |

| 3.9 The second sandwich construction of this device                                   | 38  |

| 3.10 Reflection intensity vs. physical air gap length                                 | 39  |

| 3.11 The bottom sandwich construction of this device                                  | 40  |

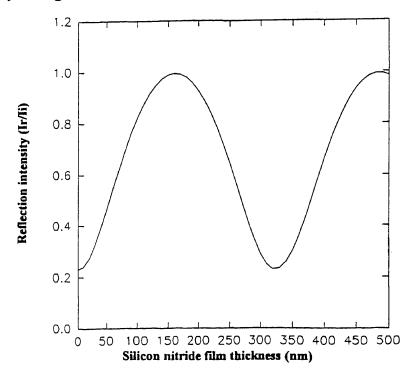

| 3.12 The reflected light intensity vs. silicon nitride thickness                      | 40  |

| 3.13 The overall effect of this device                                                | 41  |

| 3.14 The reflection light intensity vs. physical cavity height                        | 42  |

| 4.1 A top view of the full diaphragm region showing the corrugated structure          | 43  |

| 4.2 Cross-sectional schematic view of this thesis device                              | 45  |

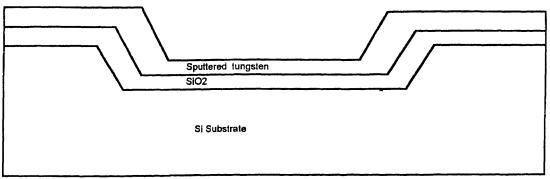

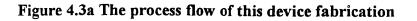

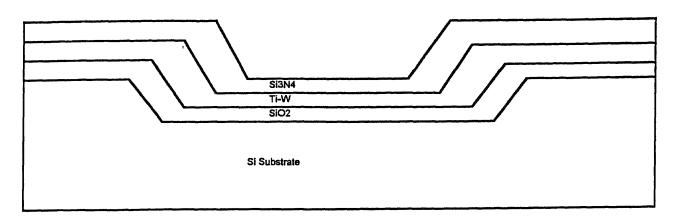

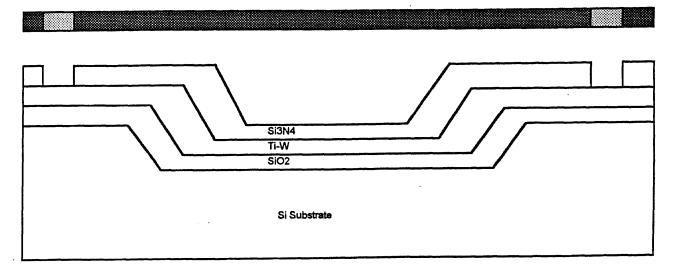

| 4.3 The process flow of this device fabrication                                       | 46  |

| 4.4 The six mask levels                                                               | 53  |

| 4.5 Device lithography generalization                                                 | 60  |

| 4.6 RIE etch defined a flat-bottom cavity                                             | 62  |

| 4.7 Deposited SiO <sub>2</sub> as an isolated layer between substrate and metal layer | 63  |

| 4.8 Growth of SiO <sub>2</sub>                                                        | 64  |

| 4.9 Sputter tungsten as a mirror surface                                              | 65  |

| Figure                                                                   | Page       |

|--------------------------------------------------------------------------|------------|

| 4.10 Optical reflectivity vs. RF power for two film thickness            | . 68       |

| 4.11 LPCVD silicon nitride                                               | . 69       |

| 4.12 The reflection light intensity vs. silicon nitride thickness        | 71         |

| 4.13 Open windows for Contact to the Buried Electrode                    | . 72       |

| 4.14 The wet process for silicon nitride                                 | . 73       |

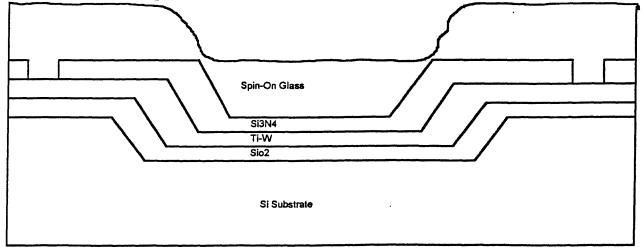

| 4.15 Spin-on glass as a sacrificial layer                                | 74         |

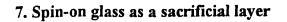

| 4.16 Planerize spin-on glass                                             | • 75       |

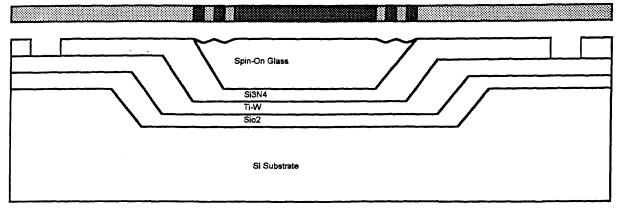

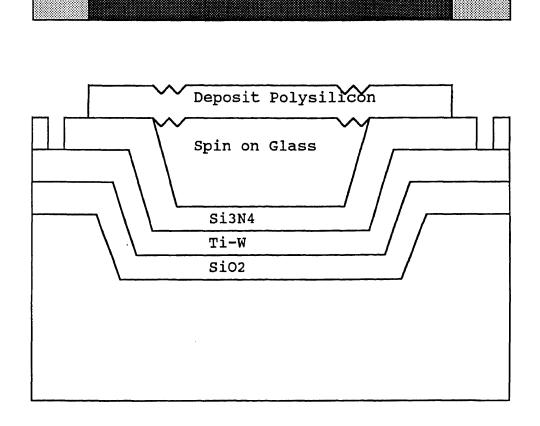

| 4.17 Deposit polysilicon                                                 | . 76       |

| 4.18 Resistivity of P-doped polysilicon                                  | . 77       |

| 4.19 Light transmission intensity vs. polysilicon layer thickness        | . 78       |

| 4.20 Light reflection intensity vs. polysilicon layer thickness          | . 78       |

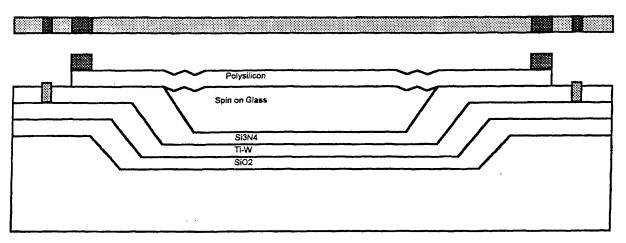

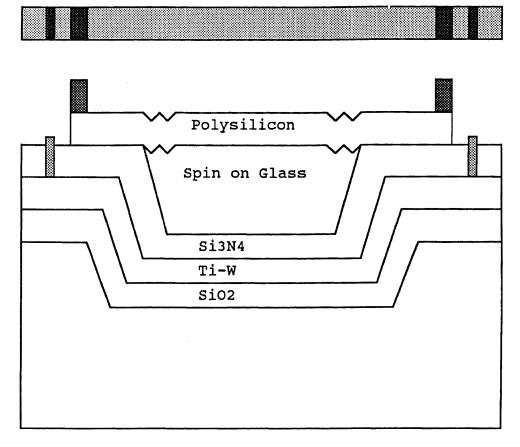

| 4.21 Pattern the polysilicon layer                                       | . 79       |

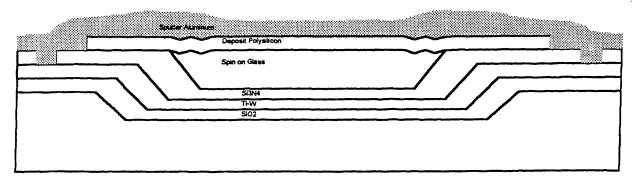

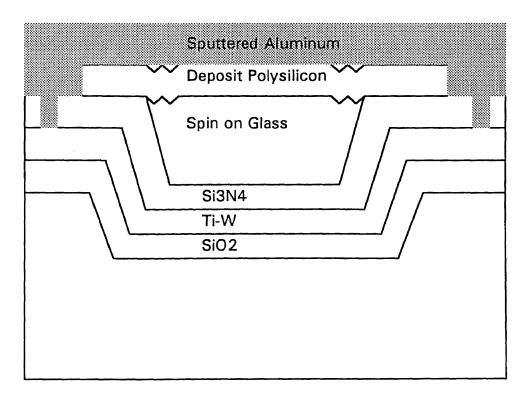

| 4.22 Sputtered Aluminum as bonding pads                                  | 81         |

| 4.23 Aluminum removal                                                    | 83         |

| 4.24 Etch small holes for the etchants coming into the cavity            | 85         |

| 4.25 Etch out of the cavity                                              | <b>8</b> 6 |

| 4.26 Two examples show that same thickness SOG with different etch holes | 87         |

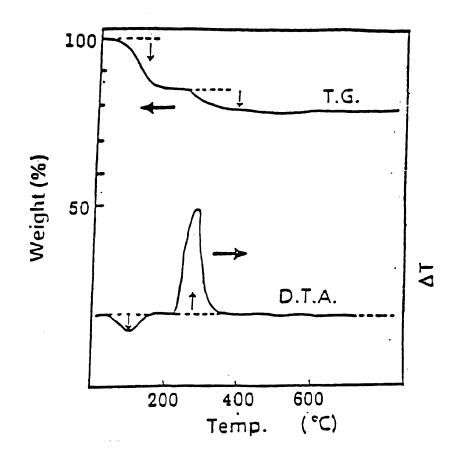

| 5.1 Differential thermal analysis of SOG                                 | 91         |

| 5.2 Etch rate comparison between LPCVD oxide and doped SOG               | 92         |

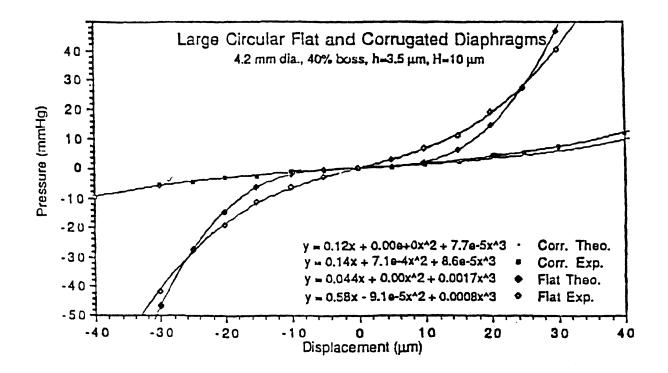

| 5.3 Deflection characteristics of flat and corrugated diaphragms         | 93         |

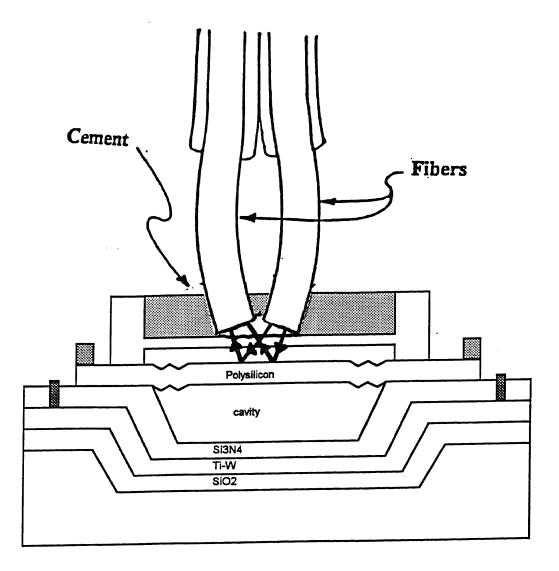

| 6.1 An application of this device                                        | 96         |

| Figure                                               | Page |

|------------------------------------------------------|------|

| A.1 Physical layout of device masks for MCNC foundry | 109  |

| B.1 Physical layout of device masks for NJITMRC      | 116  |

| C.1 A Design for optimal polysilicon film actuation  | 125  |

| C.2 A Design for optimal polysilicon film actuation  |      |

## CHAPTER ONE INTRODUCTION

#### **1.1 Thesis Description**

Optical sensing technology has developed enormously during the last decade. Particular use has been made of optical fibers not only for conveying the beams but also as the sensing elements themselves. Advances to 1982 were reviewed by Giallorenzi et al (1982) with reference to over one hundred and thirty papers. Devices for sensing various physical perturbations, including magnetic, acoustic, thermal, acceleration, rotation etc., have now been developed and are usually categorized as either amplitude or phase (interferometric) sensors. In the former class the physical perturbation acts directly to modulate the intensity of the light; such sensors are simple and reliable with a performance matching that of existing technologies. In many cases however interferometic phase sensors offer theoretically orders of magnitude improvement in sensitivity. In the most widely used sensors they are made in centimeter scale.

With the increasing requirement for high density silicon memory cells has come the need for sophisticated I/O interfaces with a high data rate, low crosstalk and high reliability. Contactless connections such as optical interconnects are a promising solution, provided that reliable transmitters and receivers can be fabricated. Reliable and cheap transmitters fabricated in silicon, and compatible with standard silicon processing remain a major problem in releasing these devices.

Structures such as GaAlAs diodes grown in silicon substrates have been fabricated, but this increases production costs. A further solution is to use hybrid structures but this increases the size of the device. The ideal solution is to fabricate a transmitter which can be fabricated in silicon and is compatible with standard processing.

Light modulators have been produced in silicon by, for example, a silicon torsional mirror [1], or a deformable mirror device [2]. However, these techniques have the

1

disadvantages of a slow response time. Fabry-Perot interferometers have been fabricated using a combination of bulk micromachining and wafer-to-wafer bonding [3]. This process resulted in a high performance device with batch fabrication capabilities. However, bulk micromaching does not lend itself to high density arrays. Surface micromachining, on the other hand , by definition leads to small size and thus easy manufacture of arrays and furthermore, these structures do not suffer from slow response time. With careful consideration of the processing yields a process which is compatible with standard silicon processing.

In this thesis, the design and processing consideration for developing a micromechanical light modulator is described.

Chapter 1 reviews the development of Fabry-Perot etalon and micromechanics, the brief history of Fabry-Perot etalon and bulk micromechanical techniques and surface microengineering, Chapter 1 also introduces the background which inspired this work. Those readers interested in the Fabry-Perot etalon theory and the design work of this novel light modulator structure may concentrate on Chapter 2. The detailed theoretically analysis is covered in Chapter 3. The detail processing and mask design are discussed in Chapter 4. Chapter 5 describes spin on glass, as a sacrificial layer and planarization material and corrugated support structure developed for cavity structure process. Chapter 6 describes application for this devices. Finally in Chapter 7, conclusions are made.

#### **1.2 Fabry-Perot Etalon**

In 1831 George Biddell Airy, Professor of Astronomy in the University of Cambridge brought out a second edition of his 'Mathematical Tracts'. For that edition he had added a chapter on 'The Planetary Theory' and one on 'The Undulatory Theory of Optics'. A direct copy of Airy's figure 17 is shown as figure 1.1. In an elegant derivation Airy calculated the retardation V of successive components of vibration as being  $2D\cos\beta$  and showed that the brightness of the reflected light was

$$\Phi_{\rm R} = 4a^2e^2\sin^2\frac{\pi V}{\lambda}(1-2e^2\cos^2\frac{\pi V}{\lambda}+e^4)^{-1}$$

and of the transmitted light was

$$\Phi_{\rm T} = {\rm a}^2 (1-{\rm e}^2)^2 [(1-{\rm e}^2)^2 + 4{\rm e}^2 \sin^2 \frac{\pi {\rm V}}{\lambda}]^{-1} - )^{-1}$$

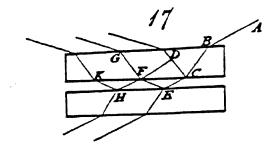

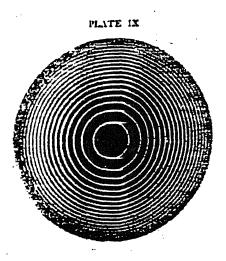

Figure 1.1 From Airy (1831, figure 17). The incident ray is shown entering along AB and experiencing successive reflections and refractions at C, E, F, H and K. The construction line FD is drawn perpendicular to the ray path CD.

In the forty years following Airy many significant advances were made in optics with contributions from most of the notable physicists of the 19th century. (For a brief review see for example the historical introduction to Principles of Optics by Born and Wolf (1975)). In December 1897 Fabry and Perot published in *Annales de Chimie et de*

Physique their paper 'On the fringes of thin silvered plates and their application to the measurement of small thicknesses of air'. They noted prophetically that these '....have led to the study of optical phenomena interesting in themselves, and to the invention of a method of measurement of small thicknesses which will doubtless be useful in other cases.' Fabry and Perot firstly pointed to the sharpness and contrast ratio of fringes arising in a thin film of air between glass plates. In an ingenious device they described a mobile plate constrained between the two plates, movements as small as  $\lambda/200$  of the tethered plate could be observed. In addition the tethered plate could itself be readjusted to a set position without the necessity of following its displacement and counting fringes.

Some idea of the increased use of Fabry-Perot interferometers is given by the list of leading centuries involved with measurement of standard wavelengths. Those topics have remained of interest to the present and , for the most part, the basic remained essentially unchanged from Fabry and Perot's day until the invention of the laser. The detail theory for the Fabry-Perot etalon will be introduced in chapter 2.1.

#### **1.3 Silicon Micromechanics**

An important and rapidly expanding area of silicon integrated circuit technology is silicon micromechanics [4]-[7]. This technology utilizes and develops silicon integrated circuit processing techniques to fabricate micromechanical structures together with electronic devices on silicon wafers. These micromechanical structures and devices when interfaced with integrated circuits and signal processing open up new opportunities for integrated sensors and robotics.

Two groups of unique processing techniques have been developed primarily for the fabrication of micromechanical sensor devices, bulk technology and surface technology. Bulk technology uses anisotropic wet chemical etching and special bonding techniques [8]-[11]. Surface technology, in contrast, uses silicon thin film technology of polysilicon, oxide, PSG, silicon nitride, metal, and special purpose film such as stress free polysilicon [12], polymer, piezoelectric films, tin-oxide films and special metal films [13].

#### **1.4 Bulk Micromechanics Technology**

The first micromechanical device was a silicon diffused element piezoresistive diaphragm made in 1962 with bulk technology [14]. The main feature of this technology is the anisotropical etching of the silicon substrate with doping dependent chemical etchants, and some special bonding techniques. This technology has been extensively investigated and it has been successfully used to micromachine complex structure. A representative example is a integrated gas chromatography system developed by Standford in 1975 [15]. This work integrated the GC system including a 1.5-m-long capillary column, a gas control valve, and a detector element on a 2-inch wafer with isotropic etching, anisotropic etching and anodical bonding of glass plate to silicon techniques.

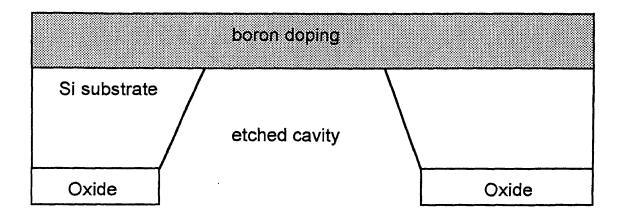

Figure 1.2 shows a cross section of a typical device formed using selective etching technology. The device could be a pressure sensor, an accelerometer, or light modulator. The wafer is to be selectively thinned from 300-500 $\mu$ m to from a diaphragm having a thickness control in the order of 1 $\mu$ m. Anisotropic etching will produce the desired lateral control. Anisotropic etchants attack the <100> and <110> directions at considerable etch rate, but attack the <111> direction at a rate typically 50 times slower. Thus, as illustrated in Figure 1.3(a), in <100> material, a cavity is formed with respect to the surface at an angle of 54.7°. In <110> material, vertical sidewall are produced [8][18].

There are three generally accepted anisotropic etching solutions for silicon: potassium hydroxide (KOH) [17], hydrazine [18], ethylene diamine-pyrocatechol-water (EDP) [19][20], and cesivm hydroxide (CsOH). While hydrazine has the distinction of not etching aluminum, it has few other advantages, tends to produce a rough surface, and can

be very dangerous to handle. It is thus not widely used. KOH is rsed in near saturated solutions (1:1 in water by weight) at  $85^{\circ}C$ . It produces a uniform etch and bright surface. This etch is preferred for shallow cavities where uniformity is important. It attacks silicon dioxide at a rate of about 60 A/min. EDP is better suited for deep etching since its oxide etch is negligible (5A/min). Also EDP produces a somewhat smoother surface compared with KOH.

In terms of vertical thickness control, the boron etch-stop technique has been developed to allow the etching process stops at desired vertical thickness [21]. This process relies on the fact that EDP essentially stops etching when the boron impurity concentration exceeds about  $5 \times 10^{19}$  cm<sup>-3</sup> in the silicon lattice.

Bonding of one substrate to another substrate is also an important technology usedd in the fabrication of this device. The most generally used techniques are eutectic bonding [22], electrostatic silicon-to-glass bonding [23], silicon to silicon fusion bonding [24] and cemented bonding.

The main problem with bulk micromachining technology is the reduced compatibility with conventional IC processing for some process steps. One of the problems occurs in masking where photoresist will etch away quickly with anisotropic etchants. Special masking layers such as silicon nitride for KOH, aluminum or Silicon dioxide for EDP have to be deposited and patterned before the etching. The other problem is the slow etch rate of anisotropic wet etching. The temperature of the tech tank must be increased to obtain resonable etch rates. For example the etch rate of silicon [100] surface in KOH at 85°C is 1 $\mu$ m/min [27]. The boron etch stop requiring a high doping level is also a major problem in some processes. The high concentration doping makes the formation of integral circuits more difficult in some instances. If the devices are formed in epitaxial material grown on the top of the etch stop layer (a boron buried layer), there are problems

Figure 1.2 Cross section of a typical sensor device formed using anisotropic and selective etching techniques

Figure 1.3a Anisotropic etching on <100> surface

Figure 1.3b Anisotropic etching on <110> surface

with epitaxial film quality and out-diffusion of boron from the buried layer.

#### **1.5 Surface Micromechanics Technology**

Recently, surface technology represented by using polycrystalline as a mechanical material is drawing more attention because this technology avoids some challenging processing difficulties of bulk technology. It provides better compatibility with standard silicon device processes, and offers new degrees of freedom for the design of integrated sensors, actuators and circuits [5][28]. Using this technology, various types of structures such as

rotating and sliding structures, gears, springs [29][30] and various applications such as micrometer [31][32] have been made.

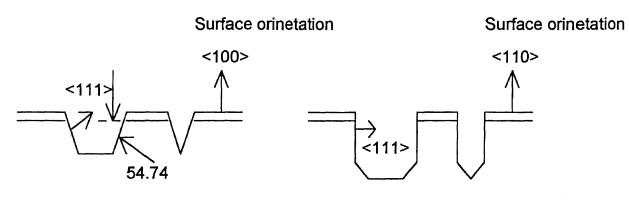

Figure 1.4 illustrates the processing sequence for fabricating a polysilicon cantilever and a double supported beam (microbridge). As shown in the figure, an oxide layer is initially grown or deposited on the silicon wafer. The first masking step opens windows in the oxide at the location the beam support areas, as shown in figure 1-3.2(a). Polysilicon is then deposited by chemical vapor deposition (CVD), and patterned by reactive ion etching in the second masking step. A lip of poly-Si is left around the perimeter of the oxide window to allow for misalignment error. If the poly-Si edge fails to overlap the oxide, then conventional RIE will erode the substrate after etch through the polysilicon layer. Immersing the wafer in buffered HF to remove all oxide and undercut the poly-Si layer. In figure 1.4(c) a free standing cantilever beam is created as illustrated. A double supported micromechanical beam (microbridge) is made by including a second oxide window, as illustrated in figure 1.4 (d) to (f).

Surface technology often uses polysilicon as a mechanical material. Silicon dioxide or phosphosilicate glass (PSG) as a sacrificial layer, and silicon nitride as an etch stop. The feature size of the micromechanical device is 1 to 2 orders of magnitude smaller than bulk technology. This technology is highly compatible with conventional processing technology. Several applications of integrating polysilicon micromechanical devices with on chip MOS circuit have reported [33][34].

Figure 1.4 The processing sequence of polysilicon cantilever and double supported beam (microbridge)

One major problem of surface technology is that as-deposited LPCVD polysilicon film tends to buckle down due to strain after sacrificial layer of oxide is removed. Special techniques are being developed to produce a smooth surfaced, stress relieved polysilicon beam. Details will be discussed in Chapter 5 as it relates to this thesis.

#### **1.6 Cavity Micromechanical Sensor Structure**

One of the major applications of micromechanical technology is the solid state sensor [33][35]. By using micromechanical technology, numerous types of sensors such as accelerometer [36][38], pressure sensor, have been made.

Most microengineered accelerometer and pressure sensors reported up to now have been made with bulk micromechanical technology. Surface microengineering alone has not been used for many sensor applications yet. Surface microengineering is an even newer field compared with bulk technology. Currently, most surface microengineering techniques are more likely planar VLSI structures. As shown in figure 1.4., the planar structure allows only thin sacrificial layers.

Up to now, all reported methods to produce cavities were using bulk micromechanical techniques. The typical methods are:

1. Using anisotropic etching of silicon bulk to form cantilever beam, etching cavity from glass plate and using special bonding techniques to bond them together [41].

Producing SiO<sub>2</sub>/Si epi/Heavy doped P+ buried layer sandwich. The silicon cavity is anisotropic etched from under the oxide to the heavily doped P+ buried layer to release the SiO<sub>2</sub> beam [42].

Those methods present processing complexity and compatible problems with conventional IC processing.

This cavity based bottom metal layer, sacrificial layer, polysilicon sensing element layer structure is a very powerful structure. It can be used to build three different types of sensor, capacitive type, mechanical resonance type or piezoresist type, if different external circuits are connected.

Discussion will be limited to the light modulator application in this thesis although other sensor types could be involved.

# CHAPTER 2 Fabry-Perot Etalon

#### 2.1 Principles of Operation

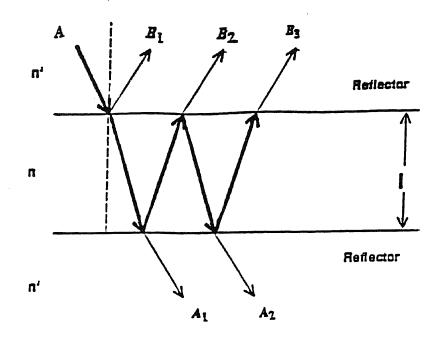

The Fabry-Perot etalon, or interferometer, named after its inventors, is a basis of this thesis. It consists of a plane-parallel plate of thickness l and index n that is immersed in a medium of index n'. Let a plane wave be incident on the etalon at an angle  $\theta'$  to the normal, as shown in Figure 2.1-1. We can treat the problem of the transmission (and reflection) of the plane wave through the etalon by considering the infinite number of partial waves produced by reflections at the two end surfaces. The phase delay between two partial waves is attributable to one additional round trip. It is given, according to Figure 4.2, by

$$\delta = \frac{4\pi n l \cos\theta}{\lambda} \qquad [2.1-1]$$

where  $\lambda$  is the vacuum wavelength of the incident wave and  $\theta$  is the internal angle of incidence. If the complex amplitude of the incident wave is taken as  $A_i$ , then the partial reflections,  $B_1, B_2$ , and so forth, are given by

$$B_1 = rA_i$$

,  $B_2 = tt'r'A_ie^{i\delta}$ ,  $B_3 = tt'r'^3A_ie^{2i\delta}$ , ....

where r is the reflection coefficient (ratio or reflected to incident amplitude),  $\infty$  is the transmission coefficient for waves incident from n' toward n, and r' and t' are the corresponding quantities for waves traveling from n toward n'. The complex amplitude of the total reflected wave is  $A_r = B_1 + B_2 + B_3...$ , or

$$A_{r} = \{r + tt'r'e^{i\delta}(1 + r'^{2}e^{i\delta} + r'^{4}e^{2i\delta} + ...)\}A_{i} \qquad [2.1-2]$$

For the transmitted wave,

$$A_1 = tt'A_i$$

,  $A_2 = tt'r'^2 e^{i\delta}A_i$ ,  $A_3 = tt'r'^4 e^{2i\delta}A_i$ , .....

where a phase factor  $exp(i\delta)$ , which corresponds to a single traversal of the plate and is common to all the terms, has been left out. Adding up the A terms, we obtain

$$A_{t} = A_{i}tt'(1 + r'^{2} e^{i\delta} + r'^{4} e^{2i\delta} + ...)$$

[2.1-3]

for the complex amplitude of the total transmitted wave. We notice that the terms within the parentheses in [2.1-2] and [2.1-3] form an infinite geometric progression; adding them, we got

$$A_{r} = \frac{(1 - e^{i\delta})\sqrt{R}}{1 - Re^{i\delta}}A_{i}$$

[2.1-4]

and

$$A_{t} = \frac{T}{1 - Re^{i\delta}} A_{i}$$

[2.1-5]

where we used the fact that r'=-r, the conservation of energy relation that applies to lossless mirrors

$$\mathbf{r}^2 + \mathbf{t}\mathbf{t'} = 1$$

as well as the definitions

$$R = r^2 = r'^2 \qquad T = tt'$$

R and T are, respectively, the fraction of the intensity reflected and transmitted at each interface and will be referred to in the following discussion as the mirrors' reflectance and transmittance. If the incident photo intensity (watts per square meter) is taken as  $A_iA_i$ , we obtain from (2.1-4) the following expression for the fraction of the incident intensity that is reflected:

$$\frac{I_r}{I_i} = \frac{A_r A_r''}{A_i A_i''} = \frac{4R \sin^2(\delta_2)}{(1-R)^2 + 4R \sin^2(\delta_2)}$$

[2.1-6]

moreover, from [2.1-5],

$$\frac{I_{t}}{I_{i}} = \frac{A_{t}A_{t}^{"}}{A_{i}A_{i}^{"}} = \frac{(1-R)^{2}}{(1-R)^{2} + 4R\sin^{2}(\delta/2)}$$

[2.1-7]

for the transmitted fraction. Our basic model contains no less mechanisms, so conservation of energy requires that  $I_t + I_r$  be equal to  $I_i$ , as is indeed the case.

Let us consider the transmission characteristics of a Fabry-Perot etalon. According to [2.1-7] the transmission is unity whenever

$$\delta = \frac{4 \pi n l \cos \theta}{\lambda} = 2 m \pi$$

, m=any integer [2.1-8]

Using [2.1-1], the condition [2.1-8] for maximum transmission can be written as

$$v_{\rm m} = m \frac{c}{2 n l \cos \theta}$$

, m=any integer [2.1-9]

where  $c = v\lambda$  is the velocity of light in vacuum and v is the optical frequency. For a fixed 1 and  $\theta$ , [2.1-9] defines the unity transmission (resonance) frequencies of the etalon. These are separated by the so-called *free spectral range*

$$\Delta v = v_{m+1} - v_m = \frac{c}{2nl\cos\theta}$$

[2.1-10]

Figure 2.1 Multiple reflections model for analyzing the Fabry-Perot etalon

Figure 2.2 Two successive reflections,  $A_1$  and  $A_2$ .

15

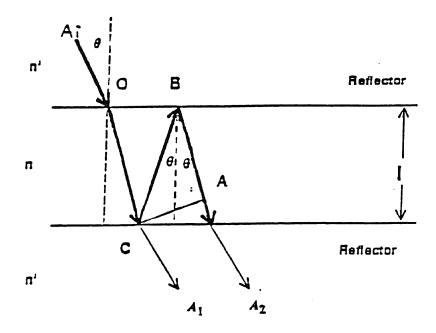

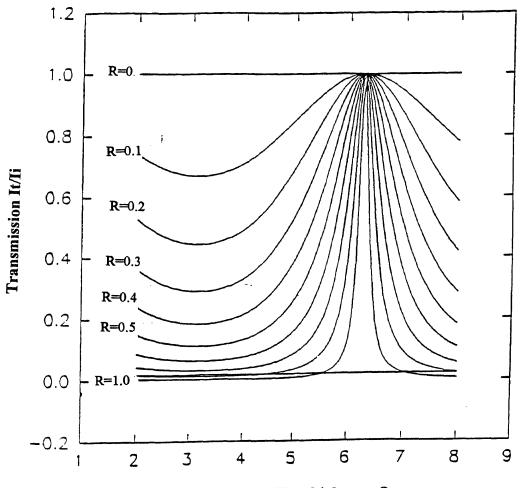

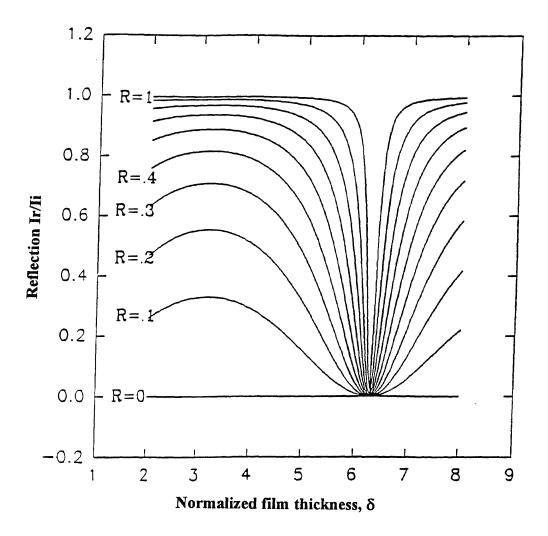

Theoretical transmission plots of a Fabry-Perot etalon are shown in Figure 2.3. The maximum transmission is unity, as stated previously. The minimum transmission, on the other hand, approaches zero as the net reflectance R approaches unity.

If we allow for the existence of losses in the etalon medium, we find that the peak transmission is less than unity. Taking the fractional intensity loss per pass as (1-A), we find that the maximum transmission T drops from unity to

$$T = \frac{I_t}{I_i} = \frac{(1-R)^2 A}{(1-RA)^2}$$

Calculated transmission plots of Fabry-Perot etalons are shown in Figure 2.4. This device geometry is given in figure 2.2. The incident optical source is normal to the interferometer surface. The bulk absorption of the device is neglected. The refraction index of the front and back surface is silicon dioxide (n=1.5).

Normalized film thickness,  $\boldsymbol{\delta}$

Figure 2.3a Transmission characteristics of a single film Plotted with equations 2.1-7a and  $\delta$  is defined by 2.1-8

Figure 2.3a Reflection characteristics of a single film Plotted with equations 2.1-6a and  $\delta$  is defined by 2.1-8

Figure 2.4a Calculated reflection characteristics of a Fabry-Perot single film etalon at 1300nm as a function of the etalon optical length with n'=1 and n=3.42 (figure 2.1). The peaks shown correspond to a change in the optical length  $\Delta(nl)=\lambda/2$ .  $(\lambda=\lambda air/3.42)$

Figure 2.4b Calculated transmission characteristics of a Fabry-Perot single film etalon at 1300nm as a function of the etalon optical length with n'=1 and n=3.42 (figure 2.1). The optical length l vary from 0 to 2000nm.

Figure 2.4c Calculated transmission characteristics of a Fabry-Perot single film etalon at 1300nm as a function of the etalon optical length with n'=1 and n=3.42 (figure 2.1). The optical length I vary from 150 to 500nm.

#### 2.2 Previous Work

In the last years of the 19th century two young French physicists at the University of Marseilles, Alfred Perot and Charles Fabry, described a novel form of interference device. This made use of interference phenomena due to waves successively reflected between two thinly silvered plane glass plates set accurately parallel. Comparable instruments of the time were the diffraction grating which had been brought to its highest pitch in the work of Rowland, and the two beam interferometer of Michelson. All these instruments, including the grating, relied on interference. However for the Fabry-Perot etalon's advantages, real and potential. is with great clarity and vigor. Within ten years all the major applications and techniques had been introduced, largely from Marseilles, and remained standard practice for over fifty years. For the reason of precisely adjust optical length, all these instruments were made very large and heavy. Some of these instruments are shown below.

By the early 1920s the Fabry-Perot interferometer had become well established in the lab. For these years the application, apart from astrophysical measurements, would be found in isotope shifts, line broadening and shift due to source conditions, and the structure of complex lines. The basic manner of use remained essentially unchanged from Fabry and Perot's day until the invention of the laser. Apart from photoelectric recording, however, it is difficult to point to anything that had not been at least envisaged by Fabry and Perot in their early work. This perhaps may stand as the highest possible tribute to their endeavors.

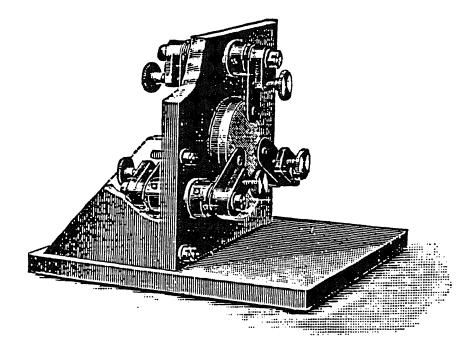

Figure 2.5 The highly engineered interferometer built by M Jobin for Fabry and Perot are described and illustrated in 1901. This is the same basic layout as the prototype instrument described in detail in 1899.

Figure 2.6 A photograph of interference rings of the green mercury line, shown by Fabry and Perot in 1901 in the *Astrophysical Journal*. The full structure of four satellite rings was lost in reproduction. This appears to be the first published record of Fabry and Perot fringes.

Figure 2.7 A fixed etalon or standard of thickness developed by Fabry and Perot for measurement on arc and solar lines.

Figure 2.8 Interference fringes photographed by Barnes (1904) under various conditions of plate separation, optical arrangement and focusing of the fringe forming lens.

# 2.3 This Thesis Device

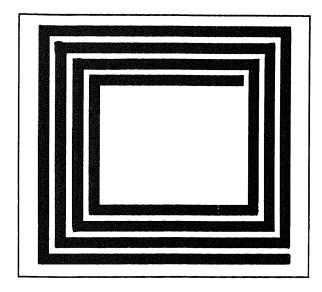

This thesis present the design and processing considerations of fabricating an optoelectronic reflection type modulator device basically apply Fabry-Perot etalon. The challenge is to make the etalon to micromachine scale and use electric to control the optical length of the interferometer.

In previous design, people use very heavy and large mechanical instrument to achieve the idea of control optical length. In these days the fast development of VLSI technology made it possible to shrink the scale of the etalon to micro. It is possible to control micro-sized gap between the two thin diaphragms by electrostatic force.

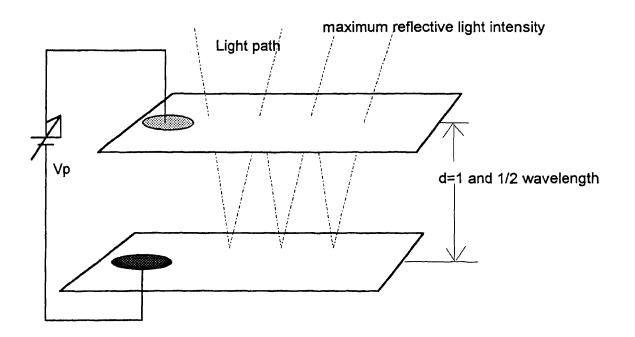

Figure 2.9 shows the basic idea of this thesis device. The detail will be illustrated in chapter 3 and chapter 4.

Figure 2.9 The original idea of this thesis device

# CHAPTER THREE PERFORMANCE DESIGN OF THE LIGHT MODULATOR

### **3.1 Introduction**

The Fabry-Perot interferometer (FPI) is an optical element consisting of two partiallyreflecting low-loss parallel mirrors separated by a gap. The optical reflection or transmission characteristic of such an element consists of a series of sharp resonant peaks. When the gap equals multiples of half wavelengths of primary and secondary reflection the transmission T is a maximum, and the reflectance is a minimum. These peaks are caused by wave interference between the two parallel plates. This device can operate in the a wide range of wavelengths.

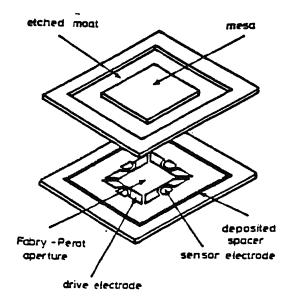

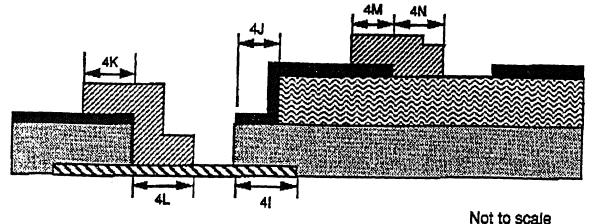

Figure 3.1 shows a first-generation microscaled FPI [45][46], consisting of a similar fixed central thick silicon diaphragm, and a moveable diaphragm. The moveable diaphragm serves as the moveable mirror. Although this device demonstrated the feasibility of applying micromachining technology for Fabry-Perot etalon, the suspension characteristics of the flat diaphragm resulted in an overall die size of about 12 mm×14 mm, much too large for fiber optic modulation. The proposed structure of this thesis uses an etch-stopped corrugated diaphragm support in place of a flat diaphragm, to obtain increased linear travel and isolation from stresses and resistance to off-axis bending. Corrugated structures can be particularly useful in providing a large vertical travel with a relatively small suspension area. These corrugations are formed by etching concentric grooves in the front surface of a wafer and diffusing an etch-stop layer into the resulting non-planar surface. After etching from the back surface, the diaphragm that is formed follows the etched contour of the front surface. By using anisotropic etch for the groove formation, the corrugations can follow any desired pattern, including circular, spiral and serpentine. In this case, the grooves have straight sides with rounded corners, surrounding

Figure 3.1 The first generation of FPI. [45][46]

a square center boss. The overall die size is 5 mm square, with a central optical cavity 1.4 mm square.

The second generation FPI [47], shown in Figure 3.2, consists of two silicon wafers, bonded together at the wafer level, and sawed into individual devices. Both wafers have highly reflective multilayer dielectric mirrors and arrays of metallic electrodes deposited on the interior devices. One wafer consists of silicon mesas surrounded by corrugated diaphragm suspensions. The other wafer has a matching set

Figure 3.2 Cross-sectional schematic view of second-generation reflection type FPI. Vertical scale exaggerated for clarity. [47]

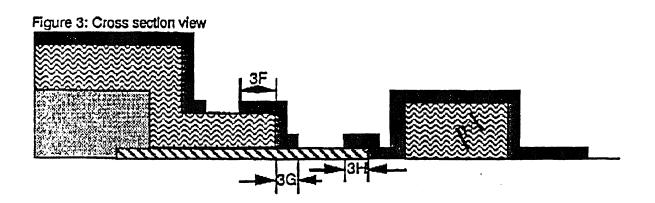

#### **3.2 Device Geometry**

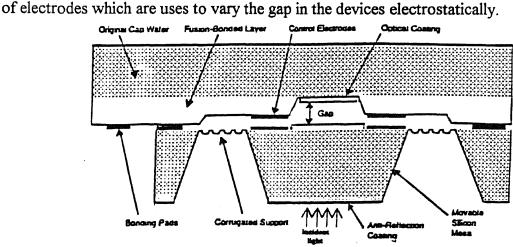

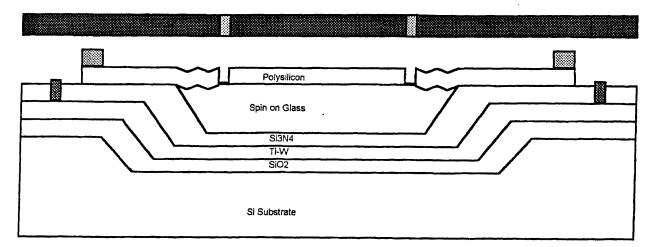

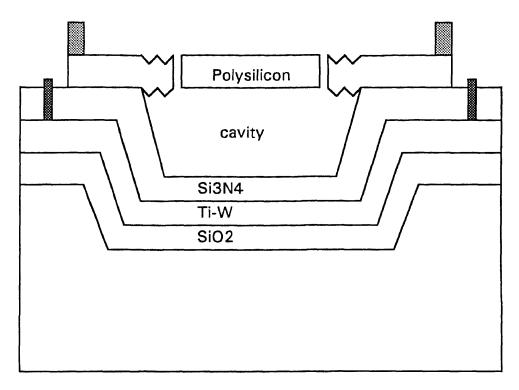

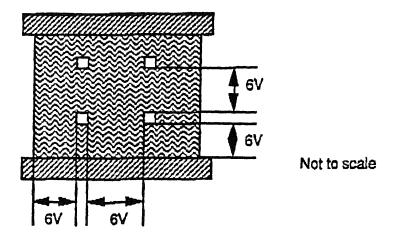

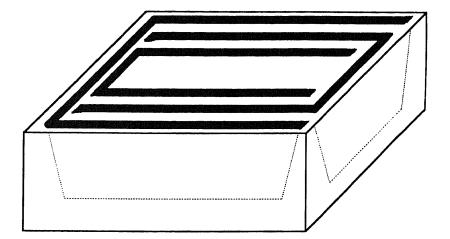

The third-generation Fabry-Perot Etalon (FPI) of this thesis, shown in Figure 3.3 is fabricated entirely on a single wafer using surface micromachining technology. It has highly reflective multilayer dielectric mirrors and arrays of metallic electrodes deposited on the interior surfaces. The top side of the cavity consists of polysilicon thin film surrounded by corrugated diaphragm suspensions. The substrate side has a matching electrode which is used in conjunction with the top electrode to vary the gap electrostatically.

# Figure 3.3 Cross-sectional schematic view of third-generation reflection type FPI. Vertical scale expanded for clarity.

This new device uses a novel technique for forming the optical gap cavity. The silicon surfaces on which the optical coatings are deposited must have high polish characteristic. This precludes the use of an etched silicon surface as the front surface of the backside mirror. The isolated layer and metallization are then deposited and patterned.

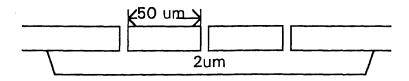

Next spin-on glass (SOG) is used as a sacrificial layer. The cap film which is a polysilicon layer is then deposited. Next, the SOG layer is sacrificially etched away to provide the desired gap of about  $0.65\mu$ m. The final step is coated with optical coatings, which increasing the transparency of light intensity. The detail process is presented in chapter 4.

The quality of the optical coating is critical to the operation of the device. The coatings must have high reflectivity to provide narrow optical bandwidth, but with very low loss to provide high peak transmittance. The reflective coatings used are multilayer dielectric mirrors made up of multiple pairs of quarter wavelength layers with high and low refractive indices. A common technique is to use a relatively low-index material, such as silicon dioxide, and a higher index metallic oxide.

## **3.3 Electrostatic Force Model**

The optical gap I is controlled by varying voltages between the two control electrodes (diaphragm cap and the substrate). The electrostatic force tends to draw the cap film towards the opposite surface reducing the cavity spacing. This motion is balanced by the elastic restoring force of the diaphragm structure. There is a pair of drive electrodes on the device. These electrodes are designed to allow not only the spacing of the cavity to be controlled, but also the parallelism of the two mirrors, maximizing the finesse of the system. Additionally, the spacing of the electrodes can be monitored capacitively. The gap between the films must be maintained to high precision. Active control of the gap is sometimes necessary to correct for the small changes in gap due by acceleration or temperature changes.

The microstructure of this device with no applied voltage has the capacitance  $C_o = \varepsilon Lb / d$  in the parallel-plate approximation neglecting fringe fields. When a potential  $V = E_z d$  is applied, a uniform pressure  $P = \frac{\varepsilon V^2}{2d^2} = \frac{\varepsilon E_Z^2}{2}$  is created which pulls the electrodes together. The film warp caused by this pressure will be discussed in section 3.5.

#### **3.4 Optical Transmission**

The transmission of a FPI is described by the Airy function

$$T = \left[1 - \frac{A}{(1-R)}\right]^2 \left\{1 + \left[\frac{4R\sin^2\left(kd\cos\theta\right)}{(1-R)^2}\right]\right\}^{-1}$$

[3.4-1]

where A= mirror absorptance, R= mirror reflectance, d= cavity gap,  $\theta$ = angle of incidence of the beam, and k=  $2\pi/\lambda$ .

The wavelength response described by the Airy function consists of a series of resonant peaks. It can be seen from equ. 3.4-1 that with  $kd=n\pi$ , and with n, the order of the interference, equal to a positive integer, the transmission for normal incidence eq. 3.4-1 becomes :

$$T_{max} = \left[1 - \frac{A}{(1 - R)}\right]^2$$

[3.4-2]

and the transmission intensity minimum between these peaks is given by

$$T_{\min} = T_{\max} \left[ \frac{(1-R)}{(1+R)} \right]^2$$

[3.4-3]

The transmission peaks are separated in wavelength by  $\Delta \lambda = \frac{\lambda^2}{(2d)}$ , and this spacing is referred to as the free spectral range (FSR). Each peak has a full width at half maximum (FWHM) bandwidth given by

$$FWHM = \frac{\lambda(1-R)}{n\pi\sqrt{R}}$$

[3.4-4]

The instrument finesse F is the ratio of the free spectral range to the FWHM linewidth.  $F_R$  is the reflection finesse given by

$$F_{\rm R} = \pi \sqrt{R} F_{\rm R} = \frac{\pi \sqrt{R}}{(1-R)}$$

[3.4-6]

An important feature of a FPI is that the free spectral range and the FWHM bandwidth can be independently controlled. For a given wavelength, the cavity gap sets

the free spectral range and the mirror reflectivity controls the bandwidth. Thus the properties of the filter can be tailored to a particular application.

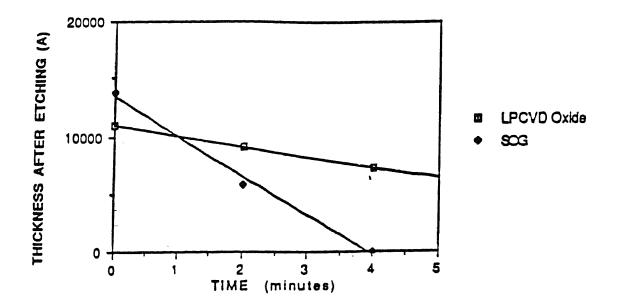

# 3.5 Mechanics of Corrugated Diaphragm

Most reported micromachined silicon diaphragms have been flat and either square or rectangular. These configuration have served well for piezoresistive pressure sensors for pressure ranges above 100 mmHg. For very low pressure ranges, however, the nonlinearity caused by membrane stresses in a square diaphragm becomes appreciable, and other, more elaborate schemes are needed. These have primarily taken the form of bossed regions on the back side of the diaphragm to concentrate stress at the periphery for piezoresistive devices or to produce piston-like travel from the central region of the diaphragm [48]-[50]. These bossed structure offer better linearity than a non-bossed structure, but the linear deflection possible from such structure is still vary small. It has been recognized for decades in the field of conventionally formed metal diaphragms that by introducing corrugations into the diaphragm structure, the linearity of a diaphragm can be increased considerably [51]. To date only a limited amount of work has been undertaken to transfer conventional corrugated diaphragm technology to micromachined silicon structures [52]. In the present work a useful technique for forming these structures is proposed modeled to increase the linearity of this device. But, however, the corrugated structure will reduce the resonant frequency.

With the introduction of corrugations into the diaphragm structure, the device performance can be improved dramatically. For shallow, sinusoidal corrugations the deflection is approximately given by [53]:

$$\frac{PR^4}{E'h^4} = a_p \frac{y}{h} + b_p \frac{y^3}{h^3}$$

[3.5-1]

where P is the applied pressure, R is the diaphram radius, h is the diaphragm thickness, E is Young's modulus, v is poisson's ratio and y is the center deflection of the diaphragm.

$$a_{p} = \frac{2(q+3)(q+1)}{3(1-\frac{\nu^{2}}{q^{2}})}$$

$$b_{p} = \frac{165(q+1)^{3}(q+3)}{q^{2}(q+4)(q+11)(2q+1)(3q+5)}$$

[3.5-2]

and

$$E' = \frac{E}{1 - v^2}$$

[3.5-3]

and for shallow, sinusoidal profiles:

$$q^{2} = 1 + 1.5 \frac{H^{2}}{h^{2}}$$

[3.5-4]

with q is the corrugation quality factor and H is the corrugation depth. Thus q varies from 1, for a flat diaphragm, to a value that approaches 1.22 times the ratio of corrugation depth to diaphragm thickness. For conventional metal corrugated diaphragms, the value of q is typically chosen to be between 10 and 30. It is clear that the coefficient  $a_p$  increases rapidly with increases in q, while the coefficient  $b_p$  decreases rapidly with increases in q. Thus the linearity of the diaphragm can be increased dramatically by providing corrugations that are as little as three times the diaphragm thickness. In this case, q=3.8, and the linear term,  $a_p$ , is increase by about a factor of four while the cubic coefficient,  $b_p$ , is reduced by a factor of over 10.

In many useful structures it is desirable to introduce a center boss into the structure. This makes the structure stiffer for a given diaphragm thickness and corrugation depth. Small deflections of a bossed, corrugated diaphragm can be expressed as:

$$\frac{\mathbf{PR}^4}{\mathbf{E'h}^4} = \mathbf{a_p}\mathbf{n_p}\frac{\mathbf{y}}{\mathbf{h}}$$

[3.5-5]

where

$$\frac{1}{n_p} = (1 - r^4) \left(1 - \frac{8qr^4 (1 - r^{q-1})(1 - r^{q-3})}{(q-1)(q-3)(1 - r^{2q})}\right)$$

[3.5-6]

and r is the ratio of boss radius to diaphragm radius. This correction is less than 20% for boss ratios less than 0.4 with values of q grater than 4. It is vary significant, however, for nearly flat diaphragms with boss ratios greater than 0.3. The influence of a boss on the cubic term is somewhat more complicated; a factor similar in magnitude to  $n_p$  can be used to modify the  $b_p$  term.

There is an additional factor that needs to be considered depending on the method of fabrication of the diaphragms. The traditional approach has been to use a heavily doped boron layer as the etch stop used to form the diaphragm. It has been shown that these etch stops introduce considerable residual tension in the resulting diaphragms. For large values of initial tension the deflection of a flat diaphragm can be represented by:

$$\frac{PR^{4}}{E'h^{4}} = \frac{4\sigma R^{2}}{Eh^{2}} (\frac{y}{h})$$

[3.5-7]

where  $\sigma$  is the initial stress. This resistance to bending due to initial stress can be added to the terms given above using the principle of superposition to given, for a flat diaphragm:

$$\frac{PR^4}{Eh^4} = \left(\frac{16}{3(1-v^2)} + \frac{4\sigma R^2}{Eh^2}\right)\frac{y}{h} + \frac{2.83}{(1-v^2)}\frac{y^3}{h^3}$$

[3.5-8]

This initial tension in very heavily doped etch stops can be very great. Chau and Wise report a 3 mm square diaphragm,  $1.7 \mu m$  thick, that is 600 times stiffer than a stress-free diaphragm. The use of an electrochemically etch-stopped diaphragm can produce a structure that has considerably less residual stress.

With this equation we get the following charts.

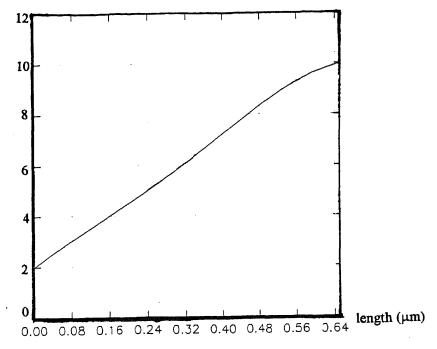

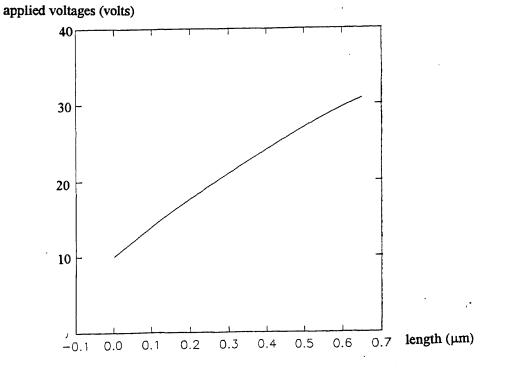

Figure 3.4 Applied voltages vs. modulated lengths (with corrugation)

Figure 3.5 Applied voltages vs. modulated lengths (without corrugation)

# 3.6 Results and Discussion

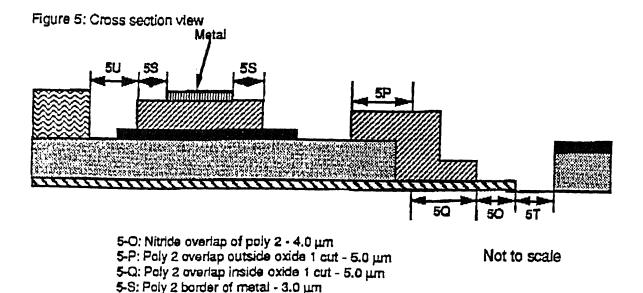

This device bases on the FPI but it is more complex than simple FPI. It is composed by five different layers. The overall effect is illustrated here.

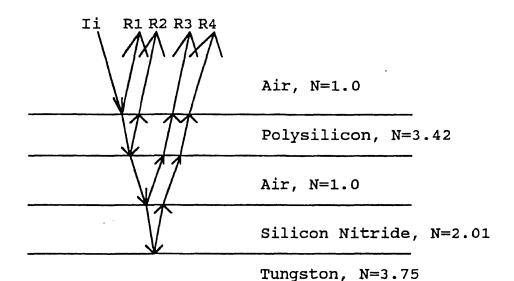

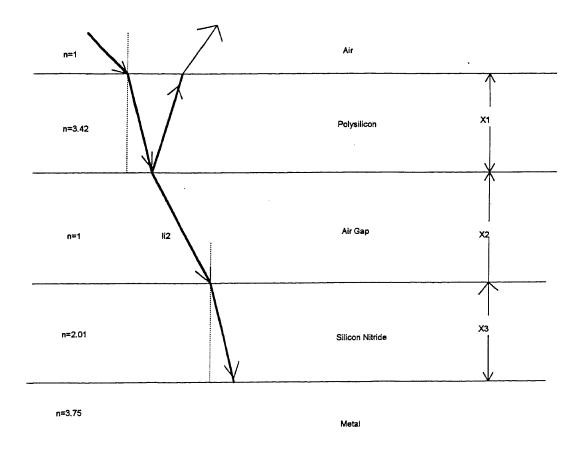

Figure 3.6 shows the main working area of this device. The light incident from air through polysilicon layer, air (cavity), and silicon nitride then reflected by tungsten film and bake through the same path again. Each layers' interface will transmit reflect light intensity.

# Figure 3.6 The overall light path of this device

We now consider the top sandwiches construction which is show in figure 3.7. This structure is a air-polysilicon-air structure.

Figure 3.7 The top sandwich construction of this device

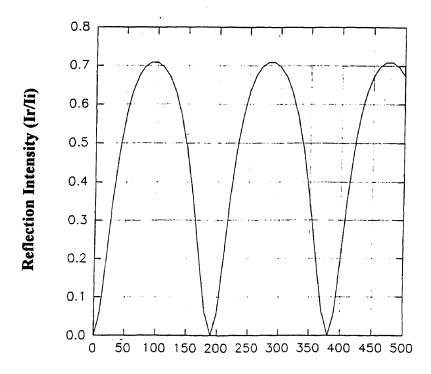

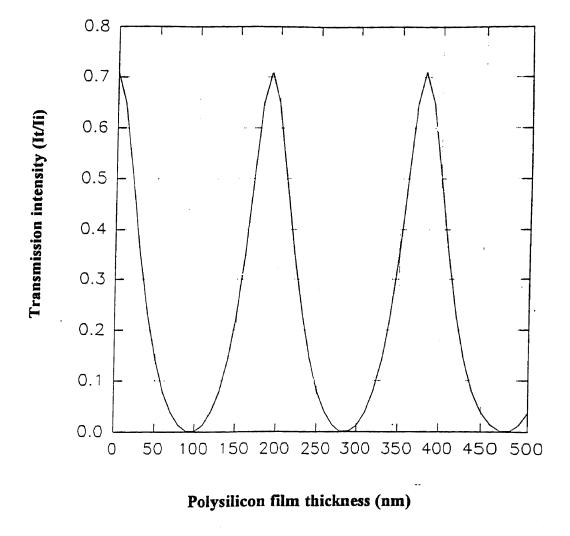

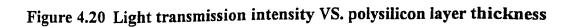

The transmission intensity of this constructure we have already discuss in chapter 2. Figure 3.8 shows the transmission characteristic. Here we pick

$$X_1 = \frac{1300 \text{ nm}}{3.42 \times 2} = 190.058 \text{ nm}$$

In this condition we can get a 98% transmission intensity, that is  $I_{i1}=I_{\Sigma A}=98\%$ Ii.

Even the processing error change the polysilicon thickness  $\pm 50$ nm. We still get 90% transmission intensition.

Figure 3.8 Reflection Intensity vs. Polysilicon Film Thickness (nm)

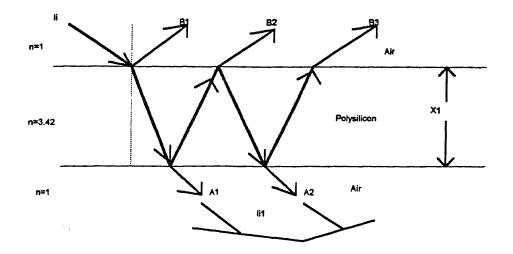

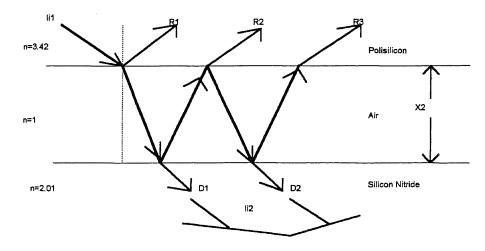

The second sandwich of this device is shown in figure 3.9. Now the complex amplitude of this incident wave is  $A_{I2}$ , then the partial reflections, R1, R2, and so forth, are given by

$$R_1 = r_1 A_{11}, \quad R_2 = t_1 t_1 r_2 A_{11} e^{i\delta}, \quad R_2 = t_1 t_1 r_2^2 r_1 A_{11} e^{2i\delta}, \dots$$

where  $r_1$  is the reflection coefficient of polysilicon interface,  $r_2$  is the reflection coefficient of air and silicon nitride interface,  $t_1$  is the transmission coefficient for waves incident from polysilicon toward air, and  $t'_1$  and  $r'_1$  are the corresponding quantities for waves traveling from air toward polysilicon. The complex amplitude of the total reflected wave is

$$A_{r} = R1 + R2 + \dots = \{r + t_{1}t_{1}r_{2}e^{i\delta}(1 + r_{1}r_{2}e^{i\delta} + r_{1}^{2}r_{2}^{2}e^{2i\delta} + \dots)\}A_{11}$$

[3.6-1]

For the transmitted wave,

$$D_1 = t_1 t_2 A_{II}, D_2 = t_1 t_2 r_1 r_2 e^{i\delta} A_{II}, D_3 = t_1 t_2 r_1^{-2} r_2^{-2} e^{2i\delta} A_{II}, \dots$$

where a phase factor  $exp(i\delta)$ , which corresponds to a single traversal of the plate and is common to all the terms, has been left out. Adding up the D terms, we obtain

$$A_{t} = A_{II}t_{I}t_{2}(1 + r_{I}'r_{2}e^{i\delta} + r_{I}'^{2}r_{2}^{2}e^{2i\delta} + ...)$$

[3.6-2]

for the complex amplitude of the total transmitted wave. We notice that the terms within the parentheses in [3.6-1] and [3.6-2] form an infinite geometric progression; adding them, we got

$$A_{r} = \frac{(1 - e^{i\delta})r_{2}}{1 - r_{1}r_{2}e^{i\delta}}A_{11}$$

[3.6-3]

and

$$A_{t} = \frac{t_{1}t_{2}}{1 - r_{1}r_{2}e^{i\delta}}A_{11}$$

[3.6-4]

where we used the fact that r'=-r.

If the incident photo intensity (watts per square meter) is taken as Ir, we obtain from (3.6-3) the following expression for the fraction of the incident intensity that is reflected:

$$\frac{I_{r}}{I_{i}} = \frac{A_{r}A_{r}^{"}}{A_{I1}A_{I1}^{"}} = \frac{4r_{1}r_{2}\sin^{2}(\delta_{2})}{(t_{1}t_{2})^{2} + 4r_{1}r_{2}\sin^{2}(\delta_{2})}$$

[3.6-5]

moreover, from [3.6-4],

$$\frac{I_{t}}{I_{i}} = \frac{A_{t}A_{t}^{"}}{A_{II}A_{II}^{"}} = \frac{(t_{1}t_{2})^{2}}{(t_{1}t_{2})^{2} + 4r_{1}r_{2}\sin^{2}(\delta/2)}$$

[3.6-6]

for the transmitted fraction. Our basic model contains no less mechanisms, so conservation of energy requires that  $I_t + I_r$  be equal to  $I_{i2}$ , as is indeed the case.

Figure 3.9 The second part construction of this device

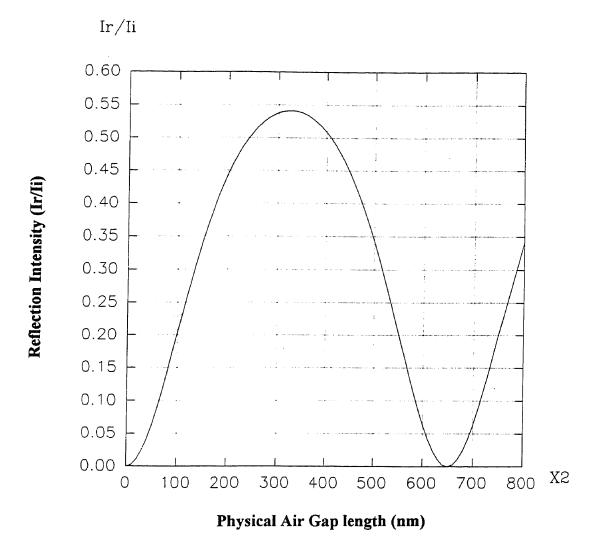

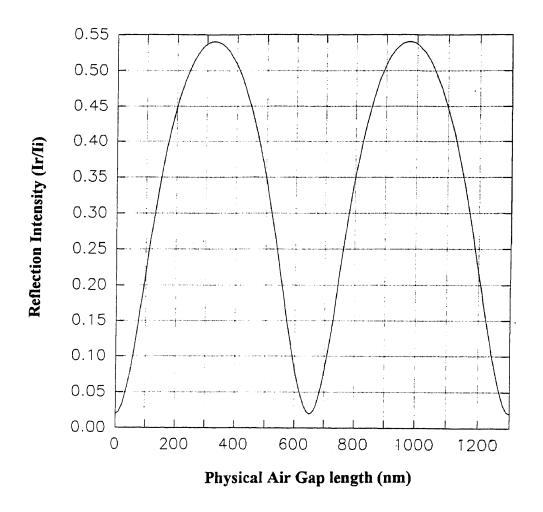

Figure 3.10 shows the reflection characteristic. With this structure, we can get a 0.53 reflection index.

Figure 3.10 Reflection Intensity vs. Physical Air Gap Length

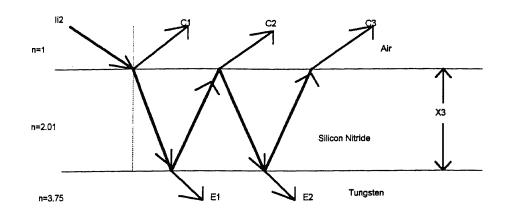

Now we discuss the bottom sandwich which is air-silicon nitride-tungsten construction. With a similar method we get figure 3.12 which shows the reflection characteristic of this construction. We choose  $X3 = \frac{1300 \text{ nm}}{2.01 \times 2} = 323.38 \text{ nm}$  to get a zero reflection.

Figure 3.11 The bottom sandwich construction of this device

Figure 3.12 Reflection Intensity vs. Silicon Nitride Thickness

Figure 3.13 shows the overall effect of this device. From the above calculations,  $I_{i1}=98\%$  I<sub>i</sub>. We can modulate Ii so that  $I_{Ri2}$  varies from 0 to 53% of  $I_{i1}$ . The reflection intensity of the bottom sandwich is properly choose so that no reflection. The overall modulation index of this device is, if we define that

$$N_{fbi} = R_{max} \% - R_{min} \%$$

then

$$N_{fbi} = (98\% \times 53\% \times 98\%)I_i - (2\%I_i) = 48.90\%$$

and the reflection intensity is about 50% of Ii.

Figure 3.13 The overall effect of this device

Figure 3.14 Total Reflection Intensity of this Device vs. Physical Length of Air Gap

# **CHAPTER 4** MASK DESIGN AND PROCESS PROCEDURE

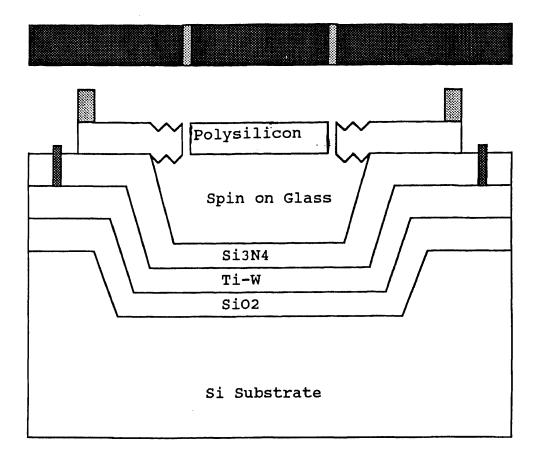

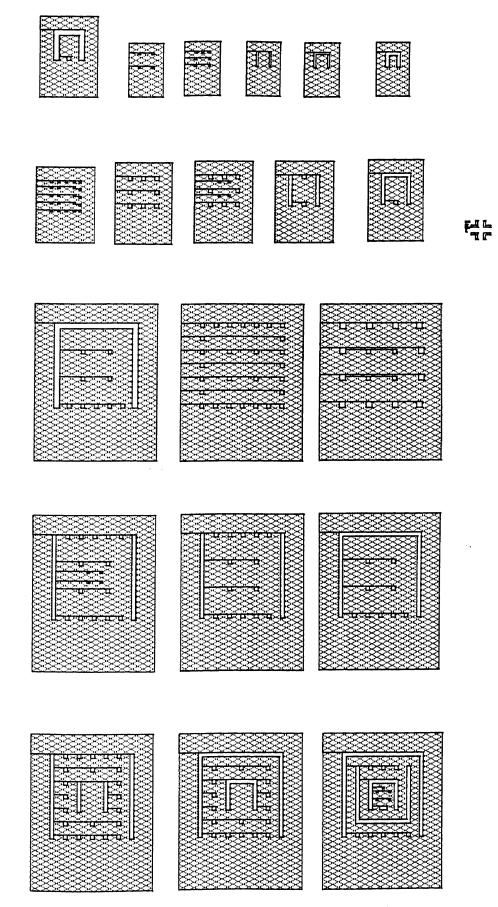

# 4-1. Device Structure

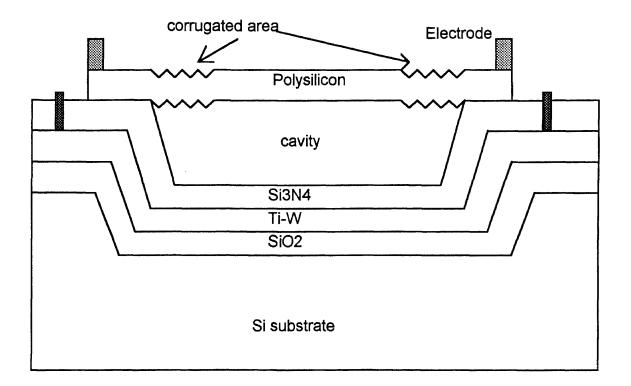

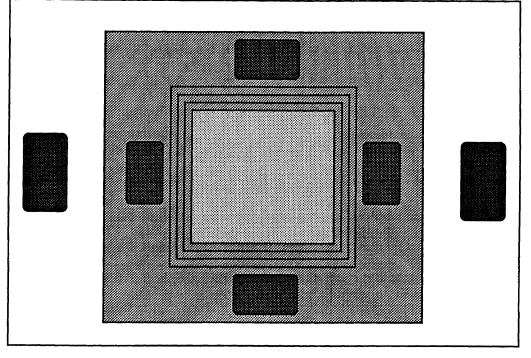

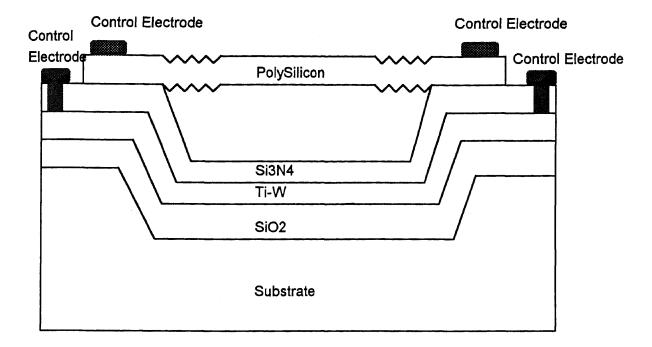

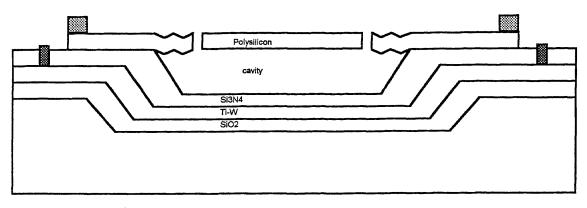

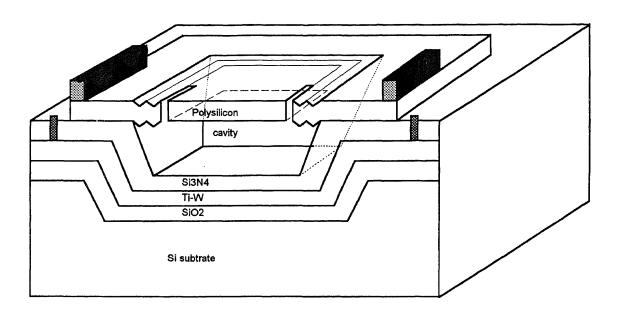

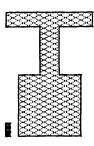

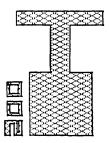

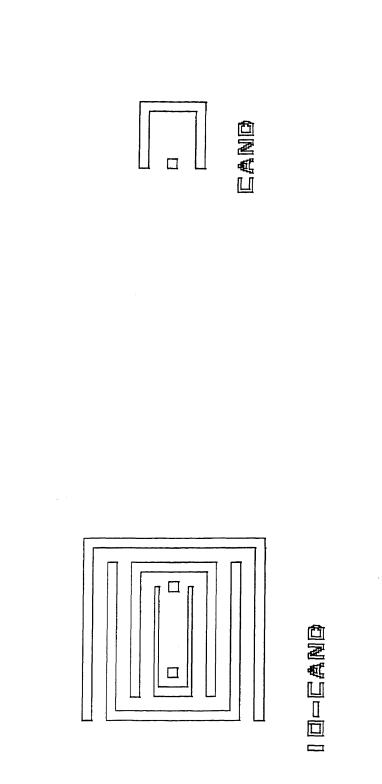

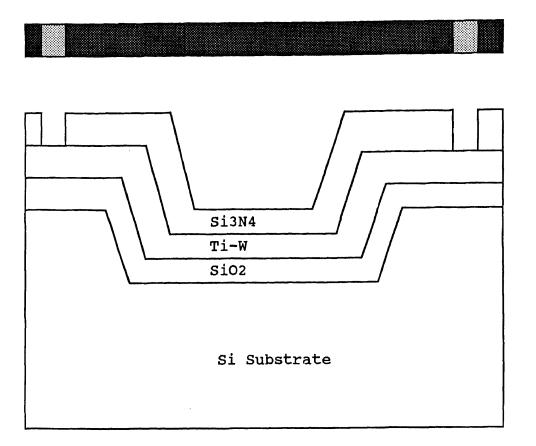

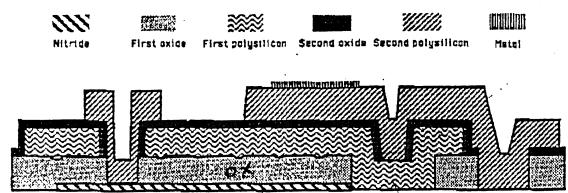

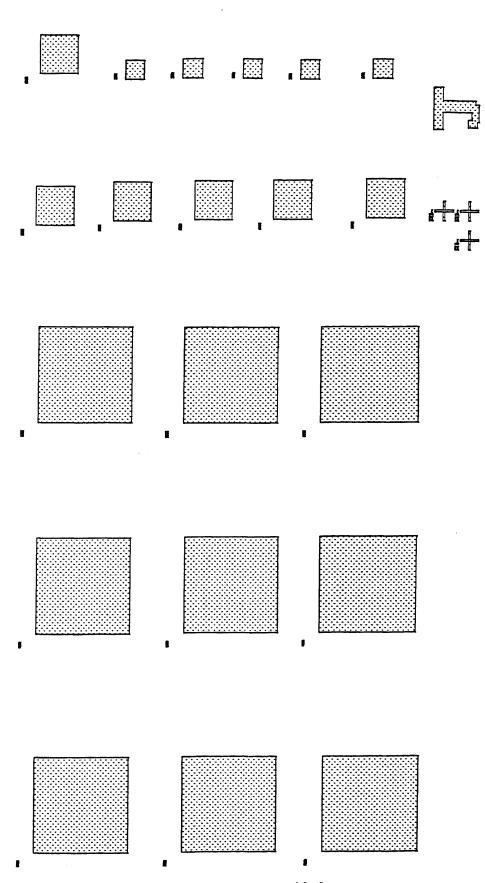

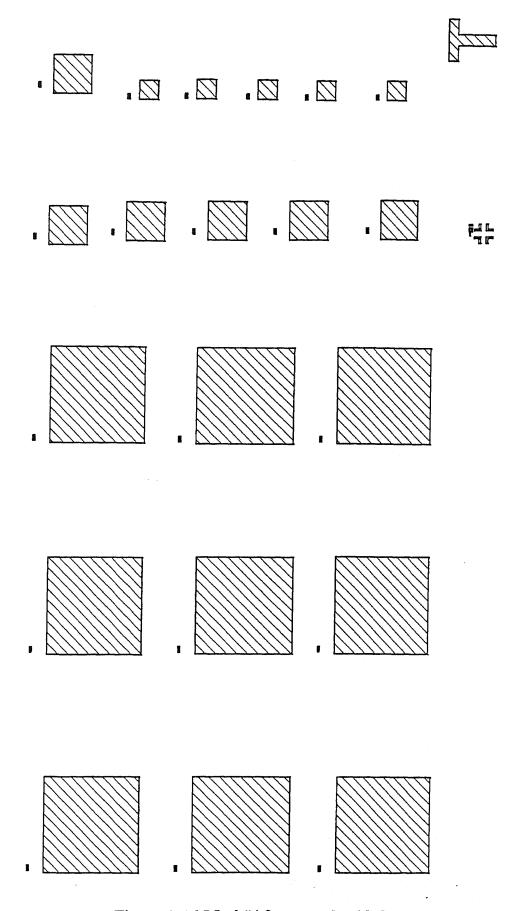

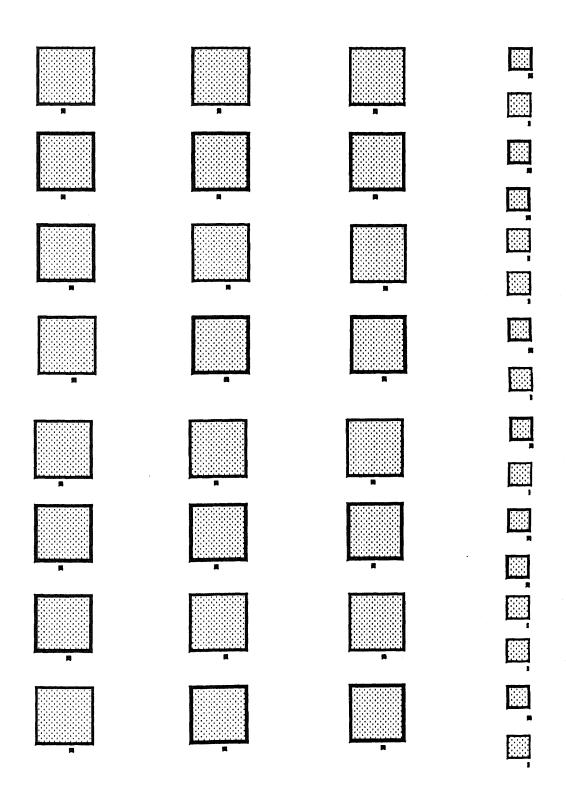

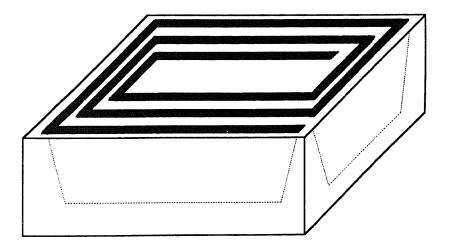

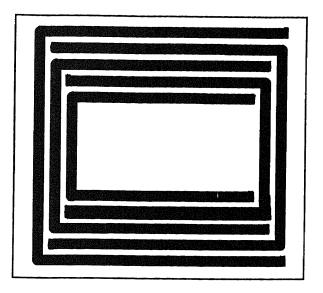

A top view of the device design in this thesis is shown in figure 4.1. In this figure the cavity underlies the diaphragm and corrugated structure. A cross section is shown in fig. 4.2. This device is fabricated within a single silicon wafer. The process uses six masks.

Diaphragm (main working area) Polysilicon

**Controlled Electrode**

**Controlled Electrode**

A top view of the full diaphragm region showing the corrugated Figure 4.1 structure

The third-generation Fably-Perot etalon (FPI) of this thesis, shown in Figure 4.1, contains a single cavity structure. It has highly reflective multilayer dielectric mirrors and metallic electrodes that are surface machined. The top side of the cavity consists of a polysilicon thin film surrounded by corrugated diaphragm suspensions. The bottom or lower side has a fixed position metal film which is used for electrostatic actuation.

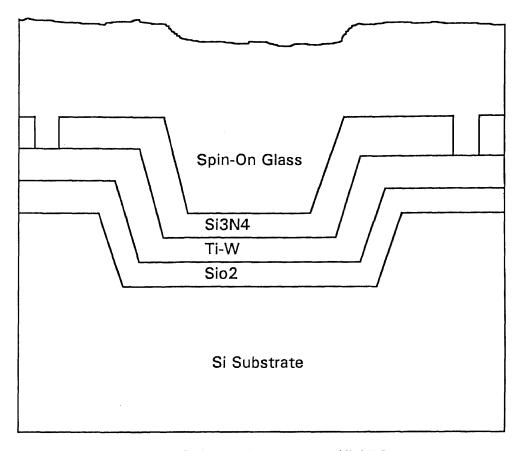

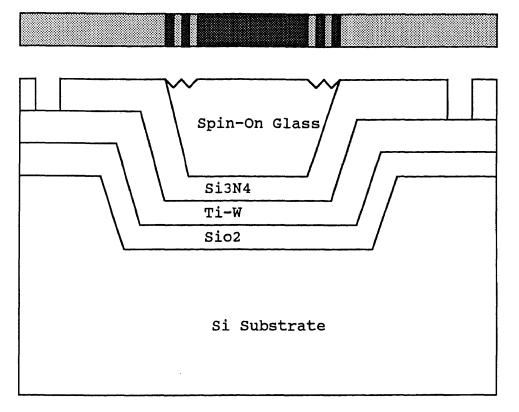

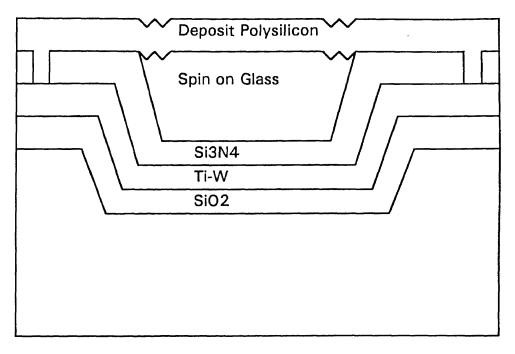

This new device uses a novel technique for forming the initial optical gap which is the depth of the cavity. The silicon surfaces on which the optical coatings are deposited must be equivalent in surface finish to unprocessed silicon wafers. This precludes the use of an etched silicon surface as the mirror surface, the isolated layer and metallization are then deposited and patterned. Spin-on glass is used as a sacrificial layer to create the cavity. The polysilicon cap film is then deposited. After that the sacrificial layer is etched down to the desired gap width of approx. 1 $\mu$ m. In the final processing step, the diaphragm is coated with optical coatings, thereby increasing the transparency for a incident light. The detail process will be discussed in chapter 4.3. Figure 4.3 shows the process flow of this device fabrication.

Figure 4.2 Cross-sectional schematic view of third-generation FPI. Vertical scale exaggerated for clarity.

.

# 1. Starting material (silicon wafer with [100] direction)

3. Deposit SiO<sub>2</sub> as an isolated layer between substrate and metal layer

4. Sputter tungsten as a mirror surface

5. LPCVD Si<sub>3</sub>N<sub>4</sub>

6. Open windows for contact to the buried electrode

# Figure 4.3b The process flow of this device fabrication

#### Mask #3 Planerize SOG

# 8. Planerize spin-on glass

# 9. Deposited polysilicon

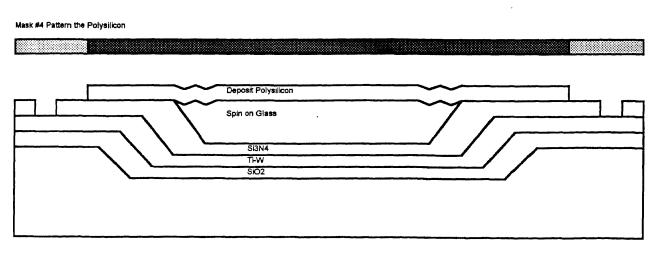

10. Pattern the polysilicon layer

Figure 4.3c The process flow of this device fabrication (cont)

# 11. Sputter Aluminum as bonding pad

Mask #5 Aluminum Removal

12. Aluminum Removal

13. Etch small holes for the etchants coming into the cavity

Figure 4.3d The process flow of this device fabrication

14. Etch out the cavity

Figure 4.3e process flow of this device fabrication

### 4-2. Mask Design

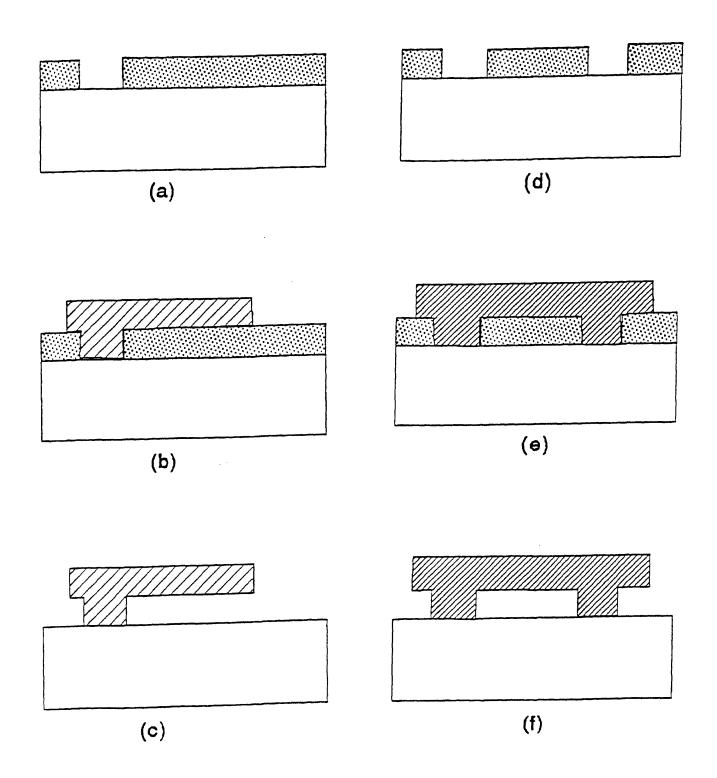

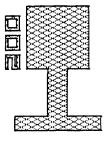

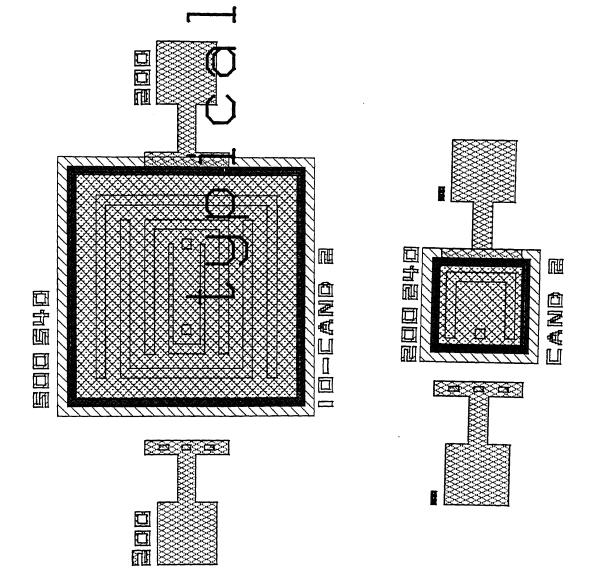

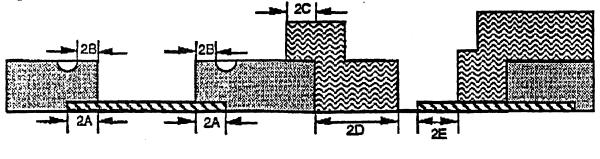

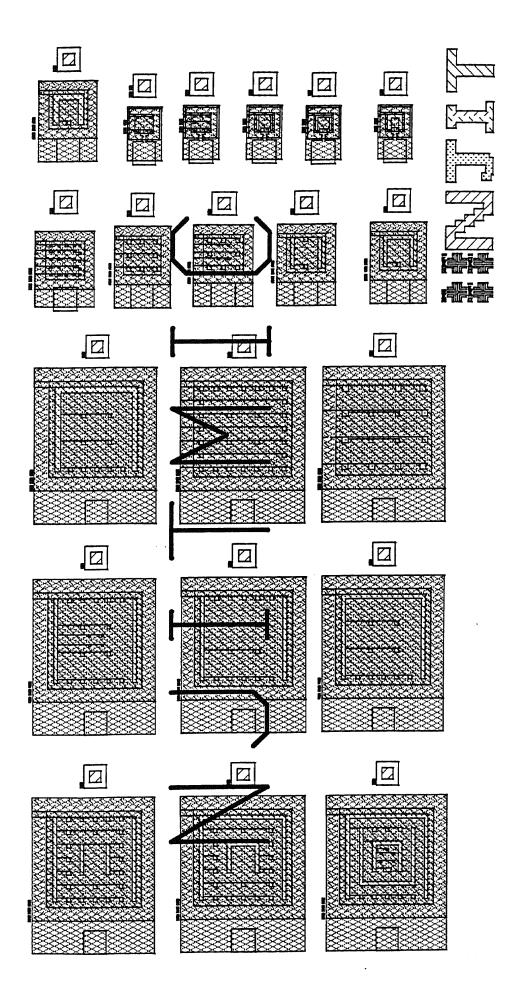

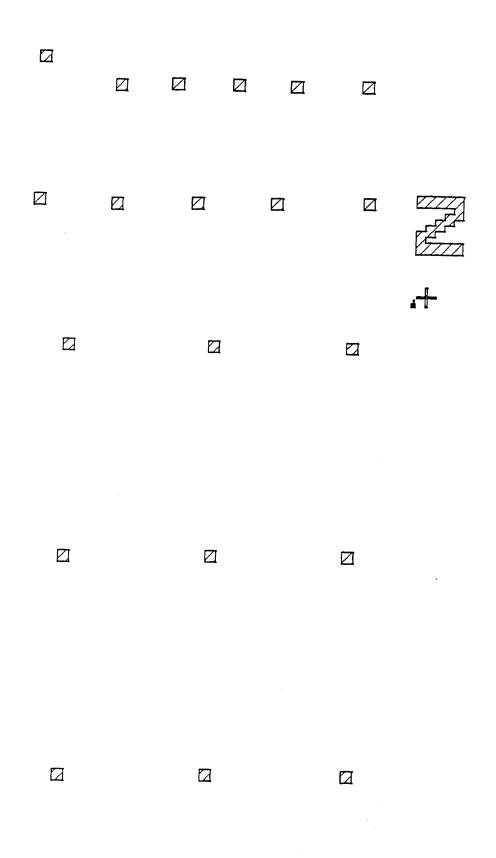

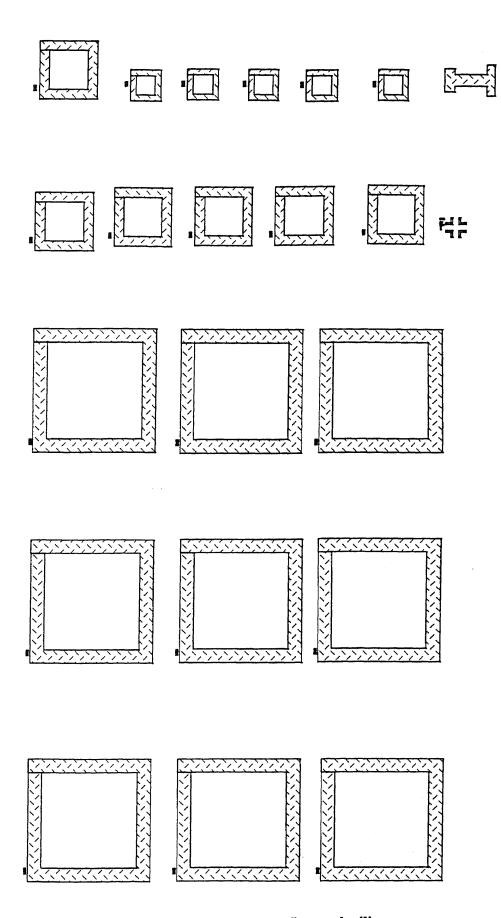

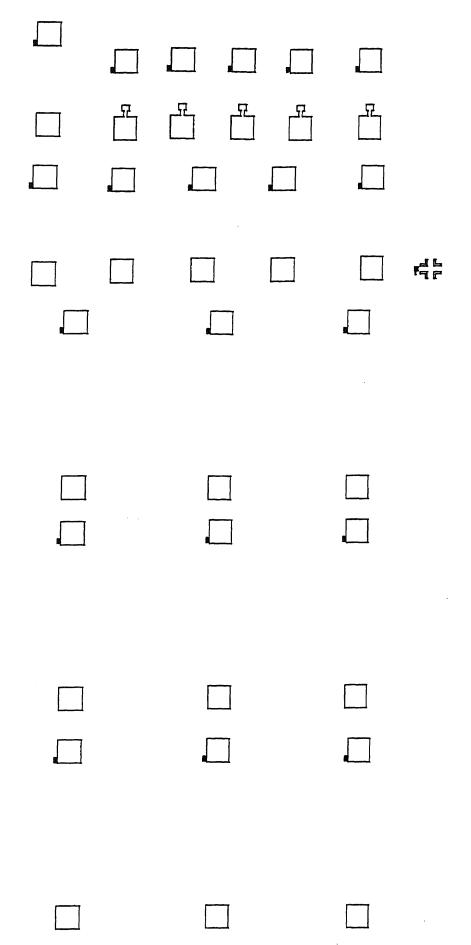

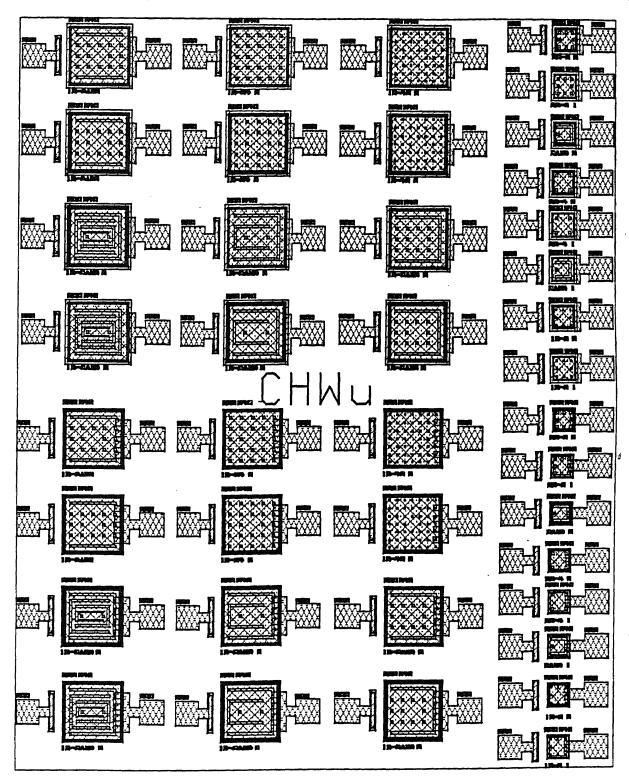

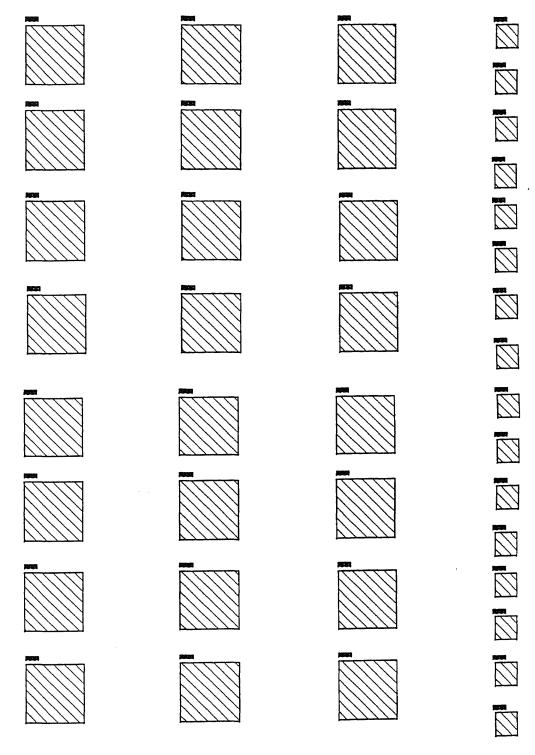

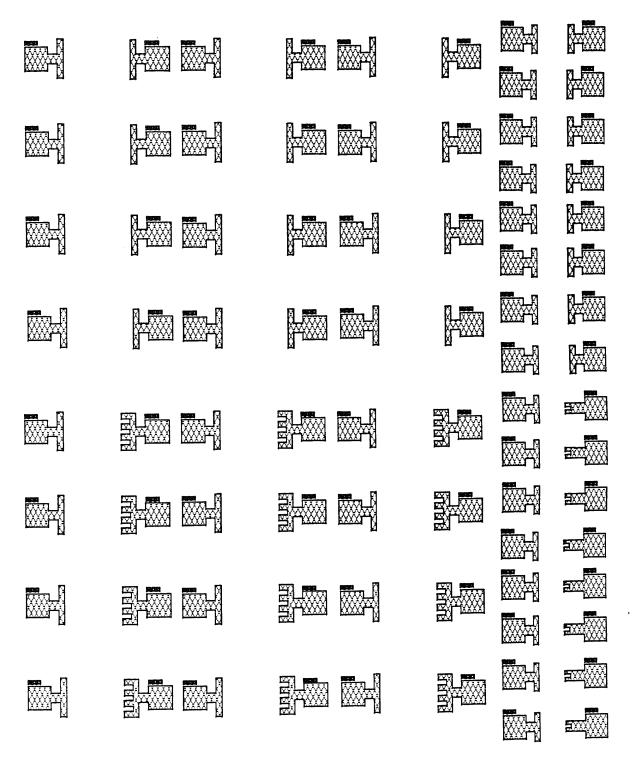

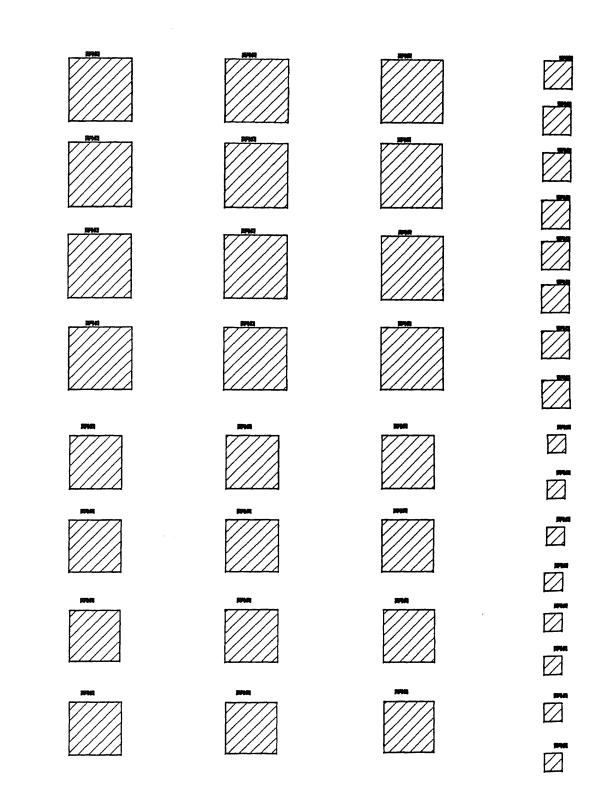

Physical layouts of the 6 mask levels are in Appendix A. Figure 4.4(a) to (f) shows the typical device mask layout.

In this third generation FPI, six masks are needed for fabrication. These mask levels are :

#### Mask #1: Define the cavity

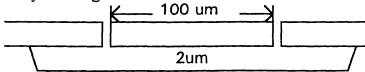

We apply this mask (figure 4.4(a)) in the very first step. The area of the cavity is the mean working area. For experimental testing, three different sizes were designed to get the best effect, they are  $100 \times 100 \ \mu\text{m}$ ,  $200 \times 200 \ \mu\text{m}$ , and  $500 \times 500 \ \mu\text{m}$ . Fields are specified for positive photoresist.

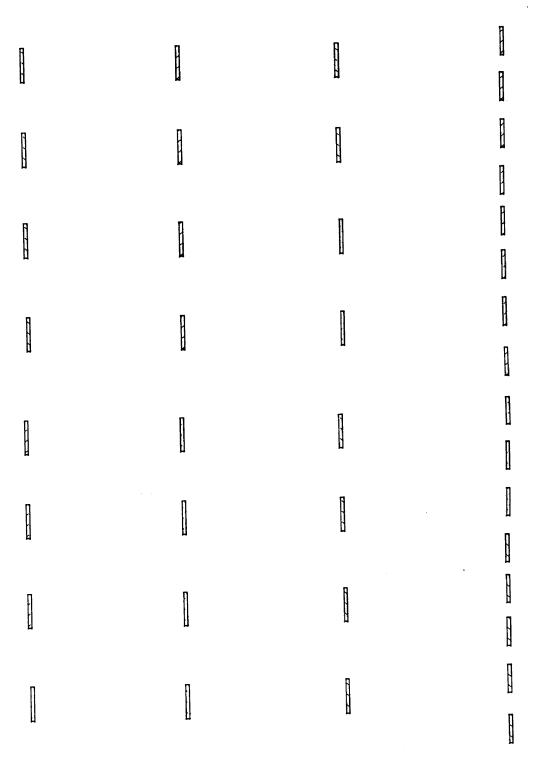

### Mask #2 Contact to the buried electrode

Two electrodes on each side of the cavity provide the electrostatic actuation. The top electrode is the cap film that is doped polysilicon film. The other side is a tungsten reflective metal film. The isolator film between these two electrodes is silicon nitride. Mask #2 is shown in figure 4.4(b) which is a light field mask.

#### Mask #3 Planerize Spin-On Glass

The cavity of this device is fabricated through a sacrificial layer process. The material which is used for the sacrificial layer is SOG. The SOG is applied by a spin-on process. The SOG will cover the entire wafer. This mask is used to remove the SOG from areas outside of the cavity. Additionally, this mask contains structures to define the corrugation of the diaphragm. Mask #3 is shown in figure 4.4(c) which is a light field mask.

Mask #4 Pattern the Polysilicon

This mask exposes the bonding pad which contacts the lower electrode. This opens the polysilicon to expose the under lying metal. Figure 4.4(d) shows mask #4 which is a dark field mask.

# Mask #5 Aluminum Removal

The device should be connect to the outside world. We use aluminum as the "wire" in the device, then use it to wire bonding. This mask is for the aluminum removal. The left area is the electrodes. They connect the electrode to the outside world. (Figure 4.4(e))

# Mask #6 Etch small hole in polysilicon

The sacrificial layer is released as a final process stop. This mask opens an etch window through the polysilicon. These holes should not be too large to effect the light reflection and transmission (or, effect the result as little as possible). Several different hole diameters and positions designs are used to get the best result. These holes also cannot be too small, otherwise the time for the cavity release will be too long. (Figure 4.4(f))

Figure 4.4(a) Mask #1 Define the cavity

Figure 4.4(c) Mask #3 Planerize Spin-on glass

Figure 4.4(d) Mask #4 Pattern the polysilicon

Figure 4.4(e) Mask #5 Aluminum removal

•

Figure 4.4(f) Mask #6 Etch small hole in polysilicon

Figure 4.3 The six mask levels combined

#### 4-3. Process Description

#### 4.3-1 Starting material

Silicon wafers oriented in the [100] crystallographic plane are used in this thesis. Prior to use silicon wafers are cleaned chemically to remove surface contamination. Commonly used are aqueous mixtures of  $NH_4OH-H_2O_2$ ,  $HCI-H_2O_2$ , and  $H_2SO_4-H_2O_2$ . Here we use  $H_2SO_4-H_2O_2$ . All of the solutions are efficient in removing metallic impurities. The ammonium hydroxide and sulfuric acid based mixtures will also remove organic contaminants, but the latter is better in this regard. These cleaning solusions leave the surface of the wafers in a hydrophilic state due to the oxidizing nature of the peroxide. In a hydrophilic state, water will wet the wafer surface (i.e., will be retained by surface tension). Since the chemically grown oxide can contain impurities from the chemicals, it is usually removed by a short immersion in dilute hydrofluoric acid. A typical cleaning sequence would be a sulfuric acid-hydrogen peroxide clean followed by the hydrofluoric acid dip, with deionized water rinses following each acid step.

#### 4.3-2 Lithography step: Mask #1 Defines Cavity

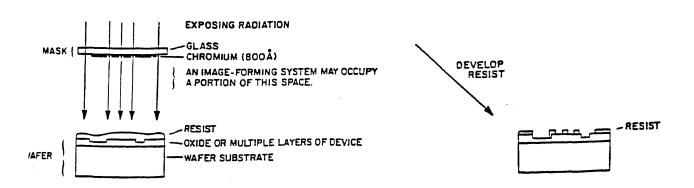

#### Figure 4.5 Device lithography generalization

Figure 4.5 illustrates schematically the lithographic process used to process wafers. The incident radiation is transmitted through the "clear" parts of the lithography mask. The circuit pattern of opaque chromium blocks some of the radiation. This type of chromium/glass mask is used with ultraviolet (UV) light.

Here we use optical lithography comprise the formation of images with visible or ultraviolet radiation in a photoresist using contact printing. For integrated circuit production the linewidth limit of optical lithography lies near 0.4  $\mu$ m, although 0.2  $\mu$ m features may eventually be printed under carefully controlled conditions.

Positive resists are used for processing this device. Positive resists have two components: a resin and a photoactive compound dissolved in a solvent. The photoactive compound is a dissolution inhibitor. When it is destroyed by exposure to light, the resin becomes more soluble in an aqueous developer solution, so higher resolution is possible with positive resists. The development process of projection printed images in positive resists has been modeled theoretically. It is an isotropic etching process. The sensitivity of most standard resists peaks in the 300 to 400 nm spectral range.

We open this window on the silicon substrate for the main working area. This cavity forms the optical path, the cap. The window's size is really depend on the application need. Three different window sizes:  $100 \times 100 \mu m^2$ ,  $200 \times 200 \mu m^2$ , and  $500 \times 500 \mu m^2$  are used for the present design.

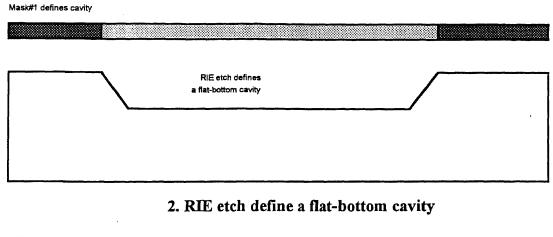

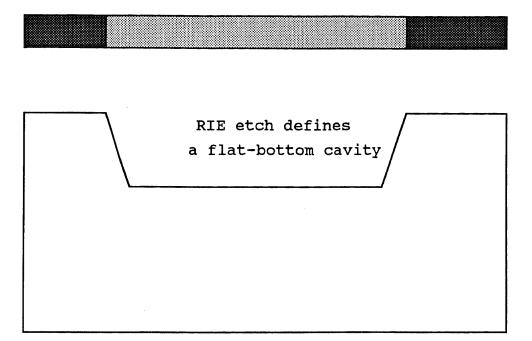

## 4.3-3 Silicon substrate etch (RIE)

Mask#1 defines cavity

Figure 4.6 RIE etch define a flat-bottom cavity

We use reactive ion etching (RIE) to define a flat-bottom cavity. RIE has three characteristics: physical (ion) and chemical, directional, and more selective than sputtering. The pressure of this etching is in the range of 100 millitorr. The term reactive ion etching is commonly used to denote processes in which plasma etching is accompanied by ionic bombardment, is actually somewhat of a misnomer. Since the etching by the reactive radicals is principally enhanced by the ionic bombardment, sometimes these processes would be described as ion-assisted etching processes.

Since this bottom act like a mirror after sputtering metal. The bottom of the cavity must be very flat. RIE provide the most uniform etching across the entire wafer to match the requirement.

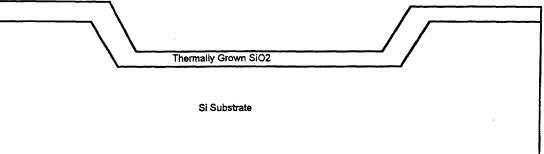

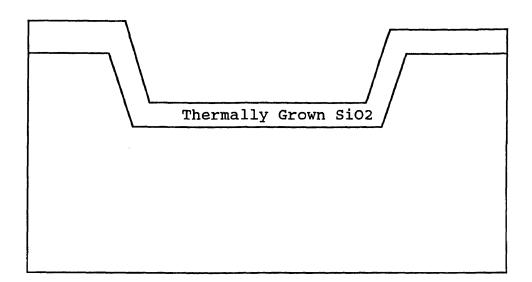

## 4.3-4 Thermally Grown Oxidation

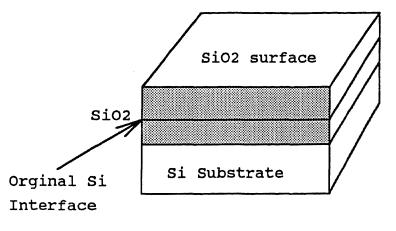

# Figure 4.7 deposit SiO<sub>2</sub> as an isolated layer between substrate and metal layer

Silicon Oxide has several uses here: to serve as a mask against implant or diffusion of dopant into silicon, to provide surface passivation, and to provide electrical isolation of next level metallization. Several techniques for forming the oxide layers have been developed, such as thermal oxidation (including rapid thermal techniques), wet anodization, vapor-phase technique [chemical vapor deposition (CVD)], and plasma anodization or oxidation. Since the interface between the oxide and the silicon requires a low-charge density level, thermal oxidation has been the preferred technique.

Because a silicon surface has a high affinity for oxygen, an oxide layer rapidly forms when silicon is exposed to an oxidizing ambient. The chemical reactions describing the thermal oxidation of silicon in oxygen or water vapor are given in equation 4.3-4(1) and 4.3-4(2), respectively.

Si (solid) +

$$O_2 \rightarrow SiO_2(solid)$$

4.3-4(1)

Si (solid) + 2H<sub>2</sub>O  $\rightarrow SiO_2(solid)$  + 2H<sub>2</sub> 4.3-4(2)

The basic process involves shared valence electrons between silicon and oxygen; the silicon-oxygen bond structure is covalent. During the course of the oxidation process, the Si-SiO<sub>2</sub> interface moves into the silicon. Its volume expands, however, so that the external SiO<sub>2</sub> surface is not coplanar with the original silicon surface. Based on the densities and molecular weights of Si and SiO<sub>2</sub>, we can show that for growth of an oxide of thickness d, a layer of silicon with a thickness of 0.44d is consumed (figure 4.8)

Figure 4.8 Growth of SiO<sub>2</sub>

Thermally grown SiO<sub>2</sub> is in thickness ranging from 60 Å to 10000 Å. For here we want 300 Å thickness for isolating the metal and substrate.

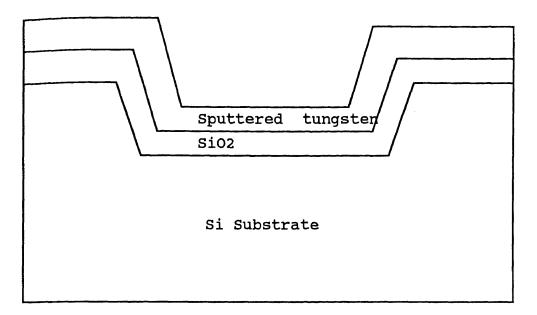

# 4.3-5 Sputtered tungsten film

Figure 4.9 Sputter tungsten as a mirror surface

4.3-5(a) Sputtering

Sputtering is a term used to describe the mechanism in which atoms are dislodged from the surface of a material by collision with plasma-produced particles. It has become the most widely utilized deposition technique for a variety of metallic films in VLSI fabrication, including aluminum, aluminum alloys, platinum, gold, titanium:tungsten and tungsten. It is also used in some applications to deposit molybdenum, Si, SiO<sub>2</sub>(silica glass), and refractory metal silicides.

We choose sputtering to deposit metal layer because of the following reasons:

a) Sputtering can be accomplished from large-area targets, which simplifies the problem of depositing films with uniform thickness over large wafers.

b) Film Thickness control is relatively easily achieved by selecting a constant

set of operating conditions and then adjusting the deposition time to react.

c) Many important film properties, such as step coverage and grain structure, can be controlled by varying the negative bias and heat applied to the substrates.

## 4.3-5(b) Tungsten film

# I. Fabrication concern

For fabrication concern, refractory films are required in contact and interconnection, where low-resistivity and thermally stable layers are particularly required. This growing requirement is a logical constant decrease of device dimensions in order to achieve higher densities and performances. For "self-aligned" technology, the use of refractory metals able to withstand the strong postime/plantation annealing (800-900 °C) without any degradation of the film integrity is a requirement of prime necessity.

The refractory metals are legitimate candidates for the above-mentioned very large scale integration (VLSI) requirements. The advantages of tungsten, in particular, are compared in Table 4.3-5 I with those of AL and summarized below:

- (i) The electrical resistivity is fairly low (W bulk resistivity: 5.6  $\mu\Omega$  cm)

- (ii) The heat resistance is intrinsically high.

- (iii) The films are readily etchable.

- (iv) The patternability is fine.

| Film characteristics               | Aluminum                       | Tungsten                     |

|------------------------------------|--------------------------------|------------------------------|

| Resistivity ( $\mu\Omega$ cm)      | 2.7 (bulk)                     | 5.6 (bulk)                   |

| Lithography resolution ( $\mu m$ ) | 1                              | 0.2                          |

| Critical linewidth (µm)            | 3                              | 0.5                          |

| Maximum temperature                |                                |                              |

| of postannealings (°C)             | 500                            | 800                          |

| Adhesion                           | very good                      | irregular                    |

| Low temperature                    | Al <sub>2</sub> O <sub>3</sub> | Low thermal                  |

| Oxidation                          | problem with etching           | stability in oxygen ambients |

Table 4.1 Compared advantages of two metals (AL and W) according to VLSI requirements.

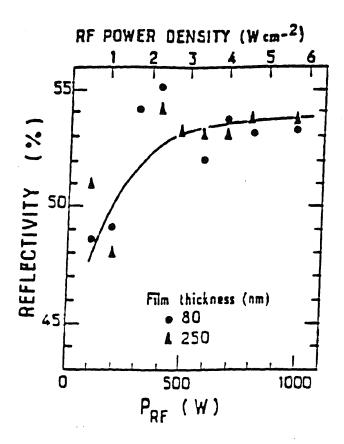

# II. Reflectivity

Figure 4.10 shows the variations of the optical reflectivity (light wavelength: 546 nm) for two W film Thickness (80 and 250 nm) in the 100-1000 W rf power range (during deposition). In each case, a strong decrease of the reflectivity is observed ~100-200 W and is particularly pronounced for the lower thicknesses. Beyond 200 W, the reflectivity tends to stabilize at a 54% upper limit, which corresponds to the following mean value of the complex refractive index:  $\tilde{N} = 3.15$  For comparison, the complex refractive index of a quasi-ideal W surface (atomically clean and well-ordered surface) is  $\tilde{N} = 3.75$  at 546 nm and the corresponding reflectivity is also 54%.

Figure 4.10 Optical reflectivity vs rf power for two film thickness (150 and 250 nm). for tungsten [56]

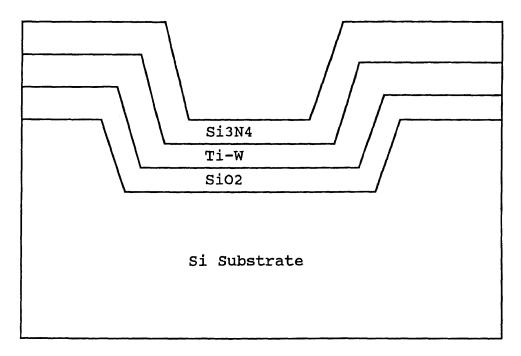

#### 4.3-6 Use low-pressure chemical vapor deposition to grow silicon nitride

# Figure 4.11 LPCVD Si<sub>3</sub>N<sub>4</sub>

Stoichiometric silicon nitride  $(Si_3N_4)$  is used for passivating the tungsten layer because it serves as an extremely good barrier to the diffusion of water and sodium. These impurities cause devise metallization to corrode or devices to become unstable. Silicon nitride is patterned and the exposed silicon substrate is oxidized. The silicon nitride oxidizes slowly and prevents the underlying silicon from oxidizing. This process of selective oxidation produces nearly planar device structures.

Silicon nitride is chemically deposited by reacting silane and ammonia at atmospheric pressure at temperatures between 700 and 900°C (That's why tungsten was selected as the metal layer) or by reacting dichlorosilane and ammonia at reduced pressure at temperatures between 700 and 800°C. The chemical reactions are

$$3SiH_4 + 4NH_3 \rightarrow Si_3N_4 + 12H_2$$

$$3SiCl_2H_2 + 4NH_3 \rightarrow Si_3N_4 + 6HCl + 6H_2$$

The reduced-pressure technique has the advantage of good uniformity and high wafer throughput.

Silicon nitride, chemically deposited at temperatures between 700 and 900°C, is an amorphous dielectric containing up to 8 atmospheric % hydrogen. The hydrogen is bonded to the nitrogen and the silicon. The amount of hydrogen depends on the deposition temperature and the ratio of reactants. More hydrogen is incorporated into the deposited film at low deposition temperatures or at high ammonia to dichlorosilane ratios. Silicon nitride deposited at low ammonia to dichlorosilane ratios contains excess silicon that decreases the electrical resistivity which is the effect we don't want.

Silicon nitride films have a refractive index of 2.01 and an etch rate in buffered hydrofluoric acid of less than 1 nm/min. Both properties are used to check the quality of deposited nitrides. Oxygen impurities in the film cause a higher etch rate. High refractive indices suggest a silicon-rich film; low indices are caused by oxygen impurities. Figure 4.3-6 shows how the refractive index changes with composition. Silicon nitride films that contain oxygen are silicon oxynitride. The composition of silicon oxynitride can vary from silicon dioxide with a refractive index of 1.46 to silicon nitride with an index of 2.01. Films that are free of oxygen but have silicon to nitrogen ratios greater than 0.75 are silicon-rich silicon nitride and have a refractive index that increases as the amount of excess silicon.

Silicon nitride has a high tensile stress, about  $1 \times 10^{10}$  dyne/cm<sup>2</sup>. Films thicker than 200 nm sometimes creak because of high stress. The resistivity of silicon nitride at room temperature is about  $10^{16}$  ohm-cm. The electrical resistivity depends on the deposit temperature, film stoichiometry, amount of hydrogen in the film, and the presence of oxygen impurities.

Table 4.2 summarizes the properties of LPCVD silicon nitride.

# Table 4.2 Properties of LPCVD silicon nitride

| Temperature (°C)                               | 700-800                            |  |  |  |

|------------------------------------------------|------------------------------------|--|--|--|

| Composition                                    | Si <sub>3</sub> N <sub>4</sub> (H) |  |  |  |

| Si/N ratio                                     | 0.75                               |  |  |  |

| Atom % H                                       | 4-8                                |  |  |  |

| Refractive Index                               | 2.01                               |  |  |  |

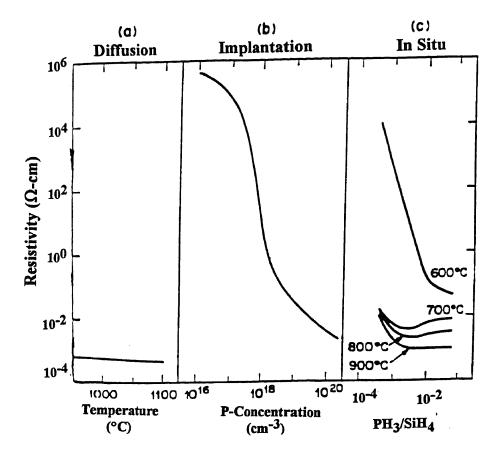

| Density(g/cm <sup>3</sup> )                    | <b>2.9-3</b> .1                    |  |  |  |