# **Copyright Warning & Restrictions**

The copyright law of the United States (Title 17, United States Code) governs the making of photocopies or other reproductions of copyrighted material.

Under certain conditions specified in the law, libraries and archives are authorized to furnish a photocopy or other reproduction. One of these specified conditions is that the photocopy or reproduction is not to be "used for any purpose other than private study, scholarship, or research." If a, user makes a request for, or later uses, a photocopy or reproduction for purposes in excess of "fair use" that user may be liable for copyright infringement,

This institution reserves the right to refuse to accept a copying order if, in its judgment, fulfillment of the order would involve violation of copyright law.

Please Note: The author retains the copyright while the New Jersey Institute of Technology reserves the right to distribute this thesis or dissertation

Printing note: If you do not wish to print this page, then select "Pages from: first page # to: last page #" on the print dialog screen

The Van Houten library has removed some of the personal information and all signatures from the approval page and biographical sketches of theses and dissertations in order to protect the identity of NJIT graduates and faculty.

3) A

# MICROPROCESSOR BASED DIGITAL LOGIC SIMULATOR,

BY

) KEVIN DRESHER

A THESIS

PRESENTED IN PARTIAL FUFILLMENT OF THE REQUIREMENTS FOR THE DEGREE

OF

MASTER OF SCIENCE IN ELECTRICAL ENGINEERING

TA

NEW JERSEY INSTITUTE OF TECHNOLOGY

This thesis is to be used only with due regard to the rights of the author. Bibliographical referces may be noted, but passages must not be copied without permission of the College and without credit being given in subsequent written or published work.

Newark, New Jersey

1980

## APPROVAL OF THESIS

Α

# MICROPROCESSOR BASED DIGITAL LOGIC SIMULATOR

BY

KEVIN DRESHER

FOR

DEPARTMENT OF ELECTRICAL ENGINEERING

NEW JERSEY INSTITUTE OF TECHNOLOGY

BY

FACULTY COMMITTEE

| APPROVED: |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|           | - Company of the Comp |

| *         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|           | And the second s |

Newark, New Jersey

1980

### AN ABSTRACT

Α

# MICORPROCESSOR BASED DIGITAL LOGIC SIMULATOR

by

Kevin Dresher

Advisor: Dr. Robert DeLucia

Submitted in Partial Fulfillment of the Requirements for The Degree of Master of Science in Electrical Engineering July 1980

It is the intent of this thesis to acquaint the reader with a tool which is available for use in the digital circuit design field. The reader is now able to totally simulate via DLS the digital logic design he creates on paper before it ever takes a hardware form. The computer program accepts a detailed description of the schematic and creates timing diagrams, loading statistics, cross references, and various lists for future documentation.

The user needs no programming knowledge and will find the requirements to run a simulation with DLS extremely user oriented. The simulation descriptions and command language are tailored to logic design applications. The format is straight forward, utilizing standard English

163056

language and logic design concepts. To code a design for simulation the designer needs only a well labeled circuit diagram, where all the inputs and outputs of each element has a label. With the addition of a few simulation parameters DLS will take the network description and form a program in memory which will recreate the operations of the digital circuit.

## Dedication

I would like to thank the people that are and were close to me for threatening me with bodily injury if I did not complete this work.

## TABLE OF CONTENTS

| Chapter |   |     | <u>Title</u>                             | Page |

|---------|---|-----|------------------------------------------|------|

| CHAPTER | 1 | WHY | ANOTHER SIMULATOR?                       | 1    |

|         |   | 1.1 | Need for Simulators                      | 1    |

|         |   | 1.2 | Levels of Simulation                     | 2    |

|         |   | 1.3 | Gate Level Simulation                    | 4    |

|         |   | 1.4 | DLS a Microprocessor<br>Based Program    | 8    |

| CHAPTER | 2 | THR | EE VALUE SIMULATION                      | 10   |

|         |   | 2.1 | Use of Ternary Algebra                   | 10   |

|         |   | 2.2 | Propagation Hazard<br>Example            | 14   |

|         |   | 2.3 | Oscillation Error<br>Example             | 16   |

|         |   | 2.4 | Don't Care Example                       | 18   |

| CHAPTER | 3 |     | LE DRIVEN SIMULATION<br>HNIQUES          | 20   |

|         |   | 3.1 | Modeling Approach                        | 20   |

|         |   | 3.2 | Table Driven Simulation Method           | 21   |

|         |   | 3.3 | Dual Table Simulation                    | 22   |

|         |   | 3.4 | Table Setups                             | 27   |

| CHAPTER | 4 | THE | DLS PROGRAM                              | 32   |

|         |   | 4.1 | DLS Program Structure                    | 32   |

|         |   | 4.2 | Source Program<br>Requirements           | 34   |

|         |   | 4.3 | The Controller/Editor                    | 37   |

|         |   | 4.4 | The Controller/Editor<br>Program Listing | 41   |

|         |   | 4.5 | The DLS Compiler                         | 53   |

|         |   | 4.6 | The Compiler Program Listing             | 66   |

|         |   | 4.7 | The DLS Executer                         | 82   |

| Chapter |   | <u>Title</u>                                       | Page |

|---------|---|----------------------------------------------------|------|

|         |   | 4.8 The Executer Program Listing                   | 90   |

|         |   | 4.9 General Purpose Routines and Memory Allocation | 112  |

| CHAPTER | 5 | USING THE DIGITAL LOGIC SIMULATOR                  | 118  |

|         |   | 5.1 Design Examples                                | 118  |

| CHAPTER | 6 | CONCLUSION                                         | 138  |

|         |   | 6.1 A Few Last Words                               | 138  |

|         |   | BTBT.TOGRAPHY                                      | 140  |

# LIST OF FIGURES

| <u>Figure</u> | <u>Title</u>                       | Page |

|---------------|------------------------------------|------|

| 1-1           | Time Delay Modeling                | 5    |

| 2-1           | Two Value Truth Table              | 11   |

| 2-2           | Combinational Hazard Detection     | 12   |

| 2-3           | Digital Latch With Hazard Example  | 15   |

| 2-4           | Oscillating Test Circuit           | 17   |

| 2-5           | Don't Care Example                 | 19   |

| 3-1           | Dual Table Operation               | 23   |

| 3-2           | OR Gate Simulation                 | 26   |

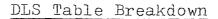

| 3 <b>-</b> 3  | DLS Table Breakdown                | 28   |

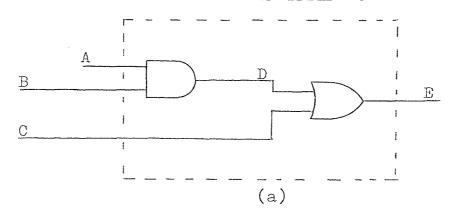

| 3-4           | Simulation Tables                  | 30   |

| 4-1           | Memory Allocation                  | 33   |

| 4-2           | Command Word Format                | 36   |

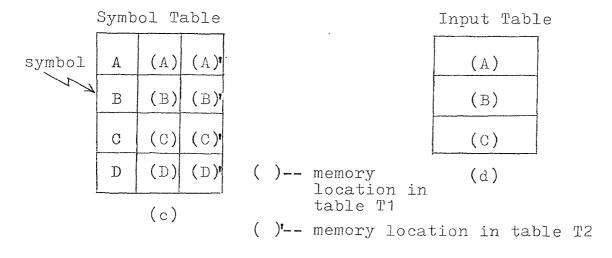

| 4-3           | Source Program Update Routine      | 38   |

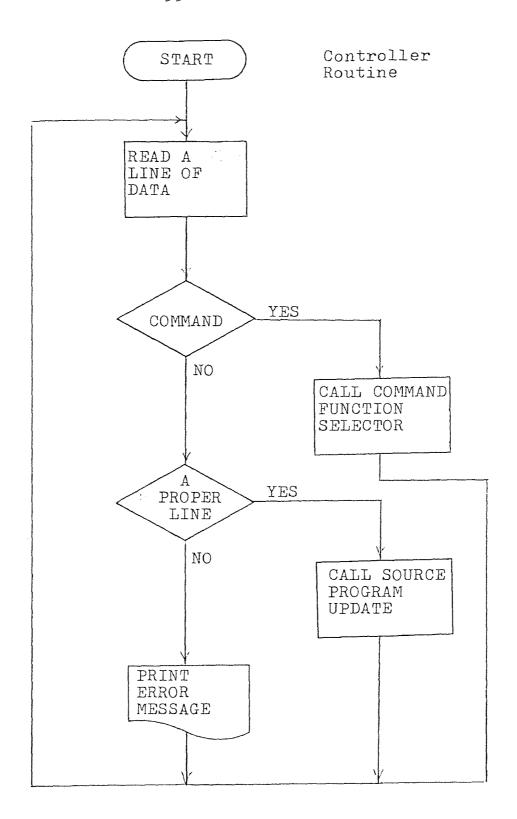

| 4-4           | Controller Routine                 | 39   |

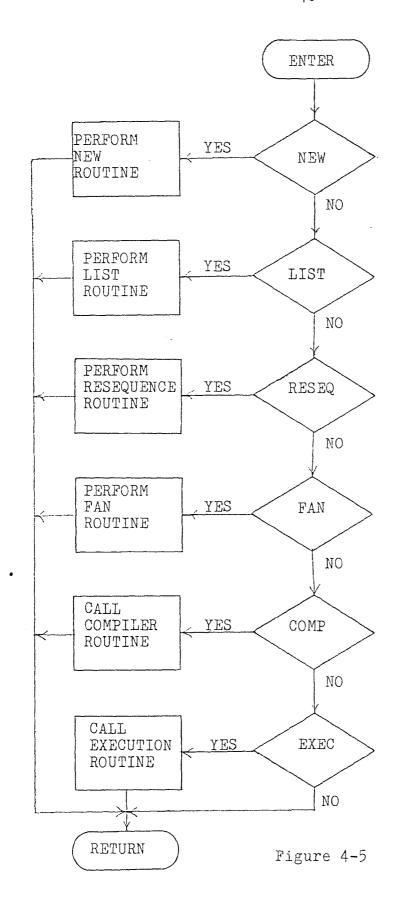

| 4-5           | Command Function Selection Routine | 40   |

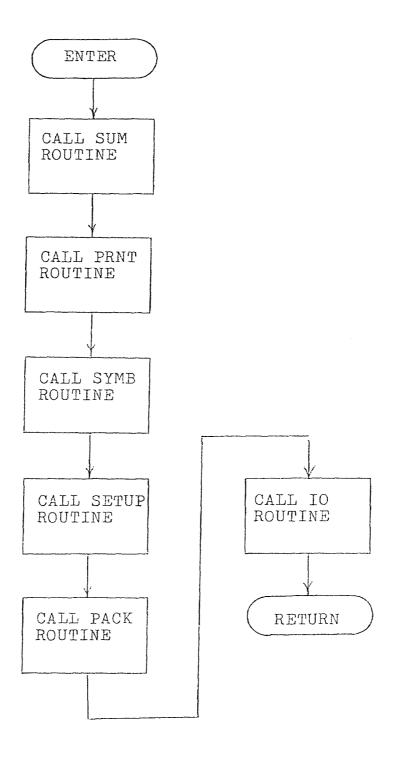

| 4-6           | Compiler Function Routine          | 54   |

| 4-7           | Sum Function Routine               | 56   |

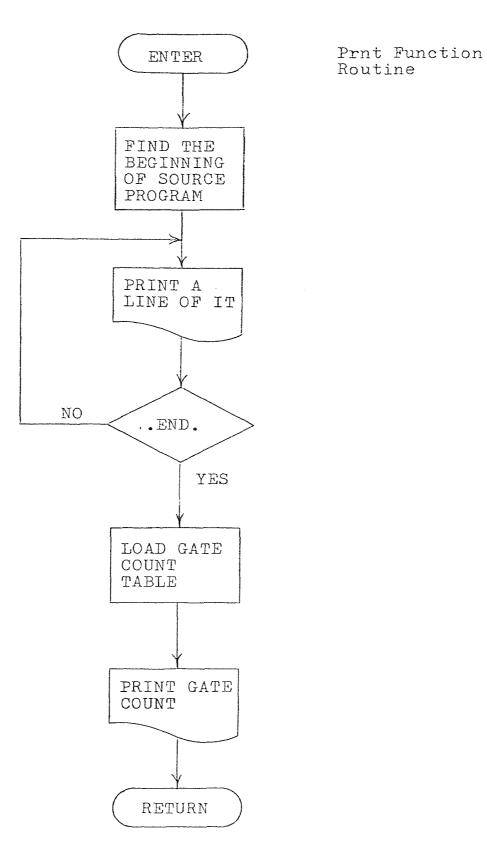

| 4-8           | Prnt Function Routine              | 57   |

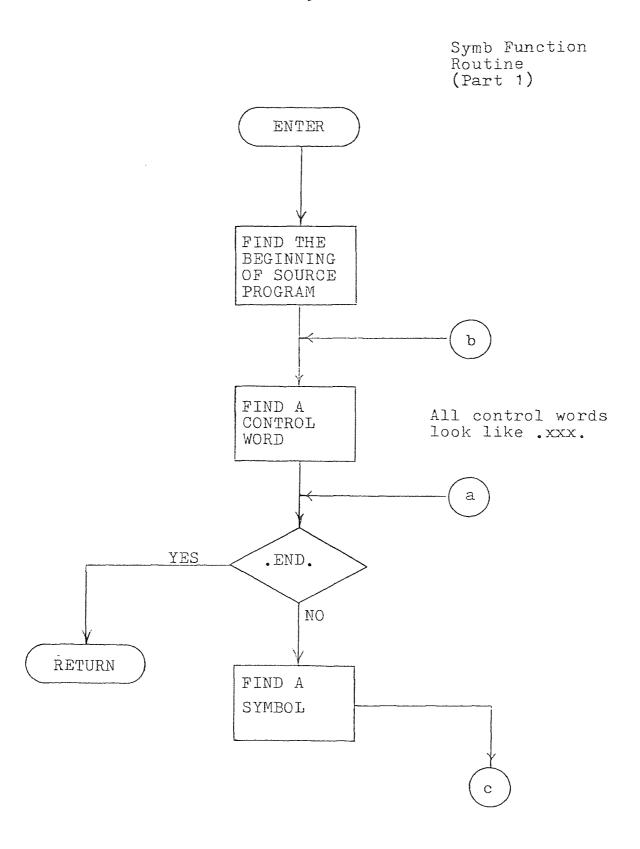

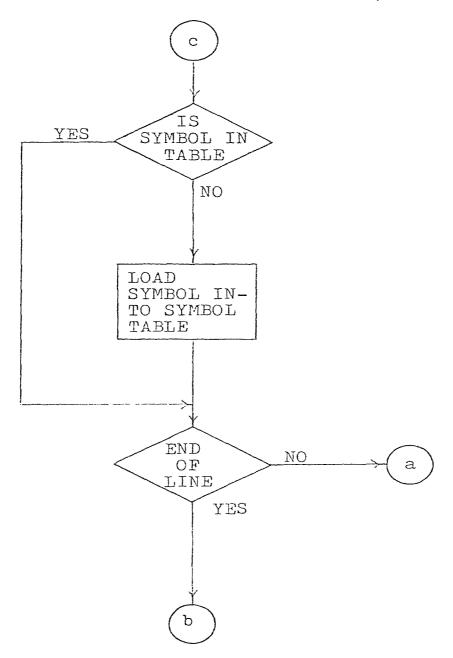

| 4-9           | Symb Function Routine              | 58   |

| 4-10          | Setup Function Routine             | 61   |

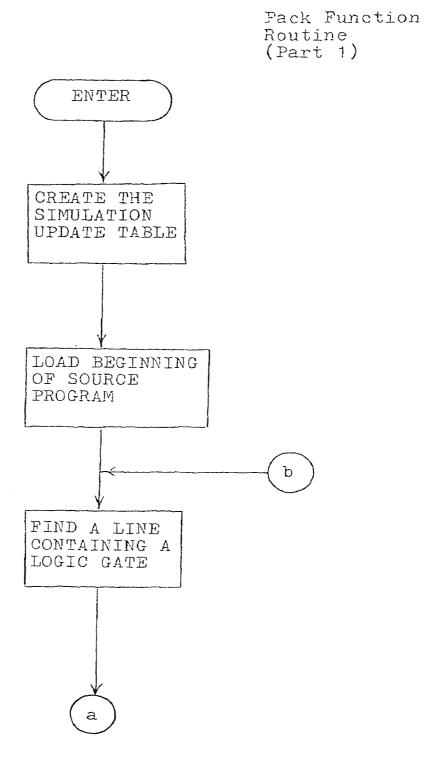

| 4-11          | Pack Function Routine              | 62   |

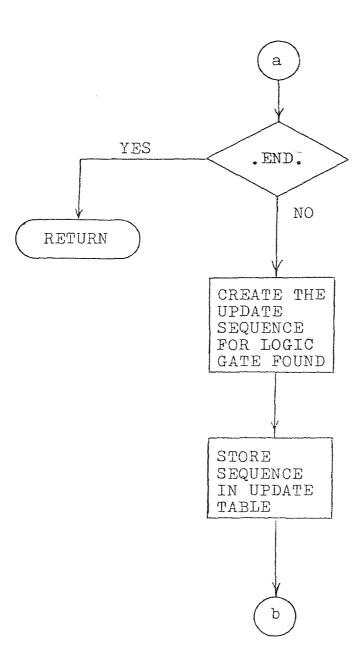

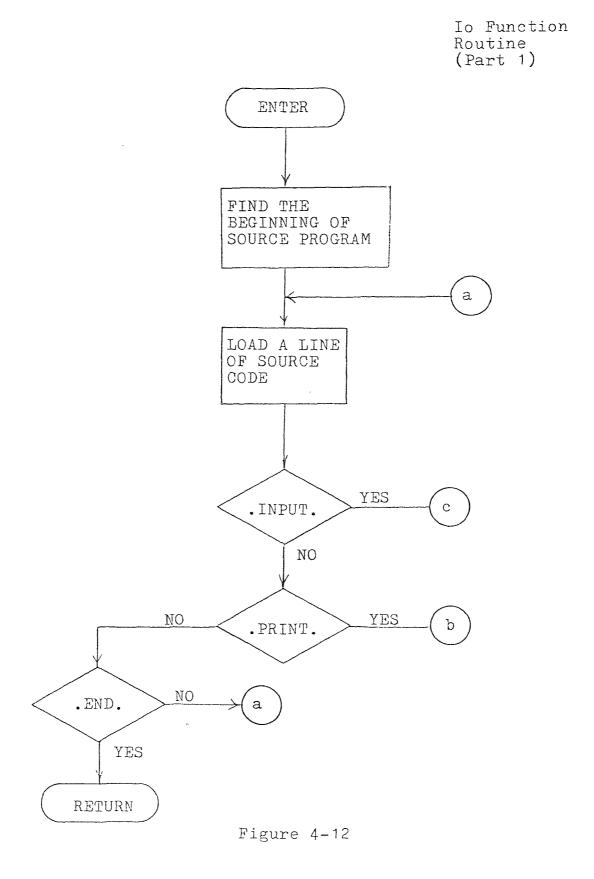

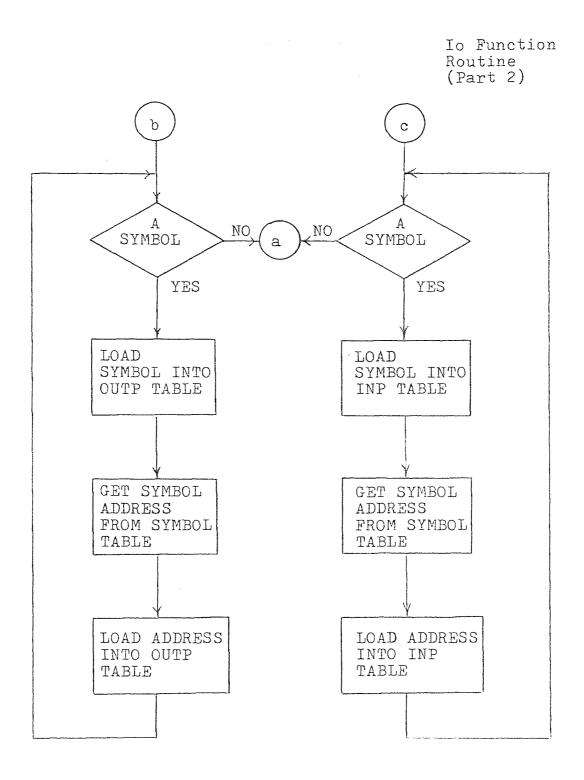

| 4-12          | Io Function Routine                | 64   |

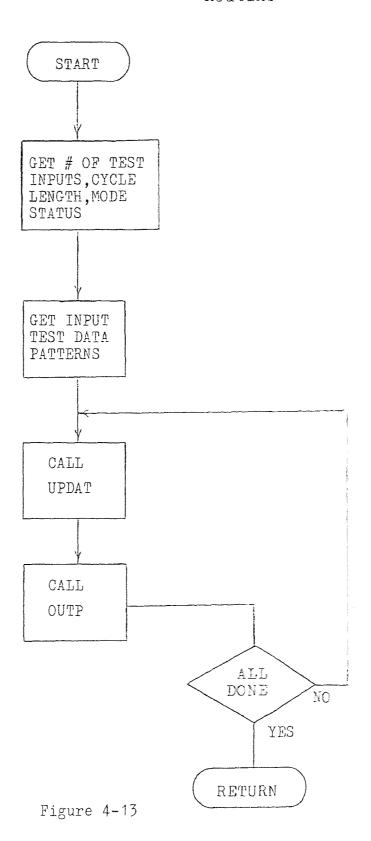

| 4-13          | Exec Function Routine              | 84   |

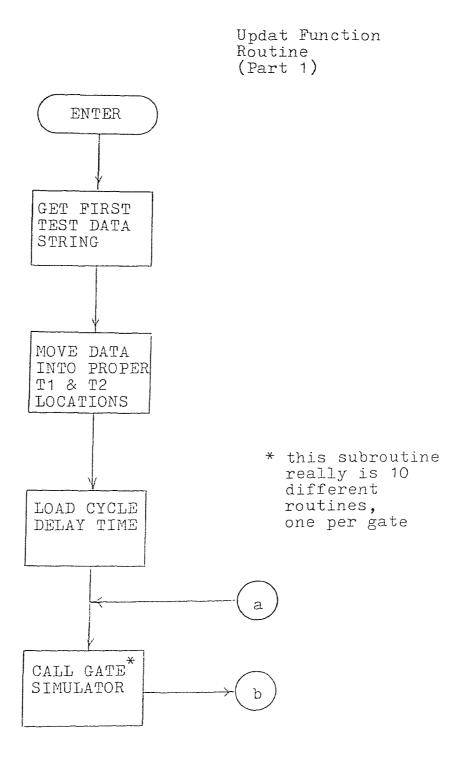

| 4-14          | Updat Function Routine             | 85   |

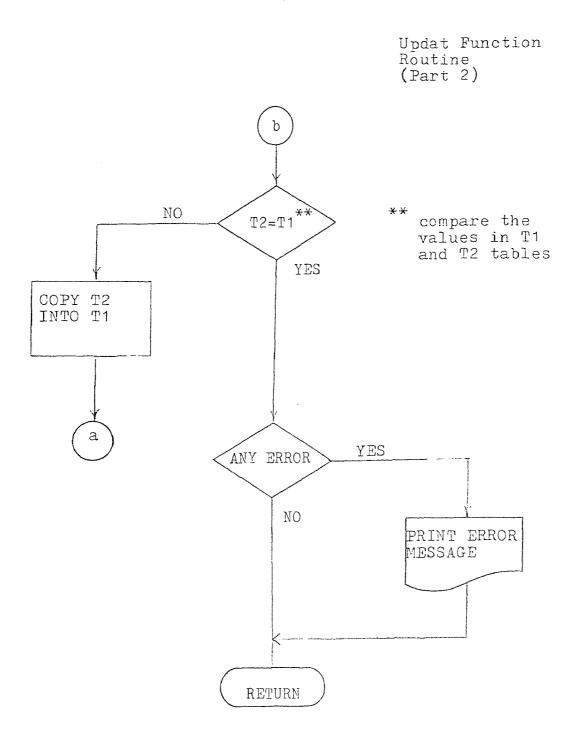

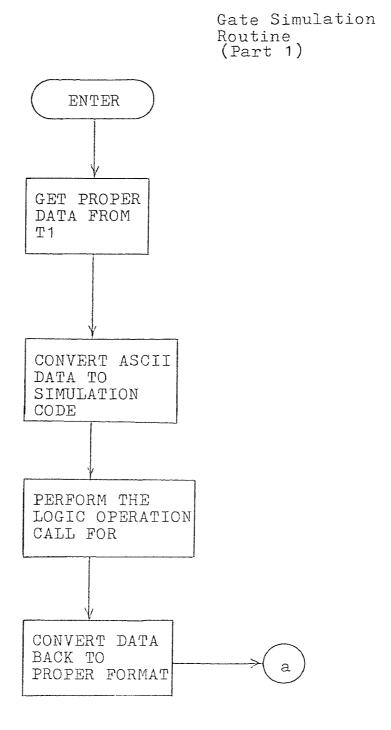

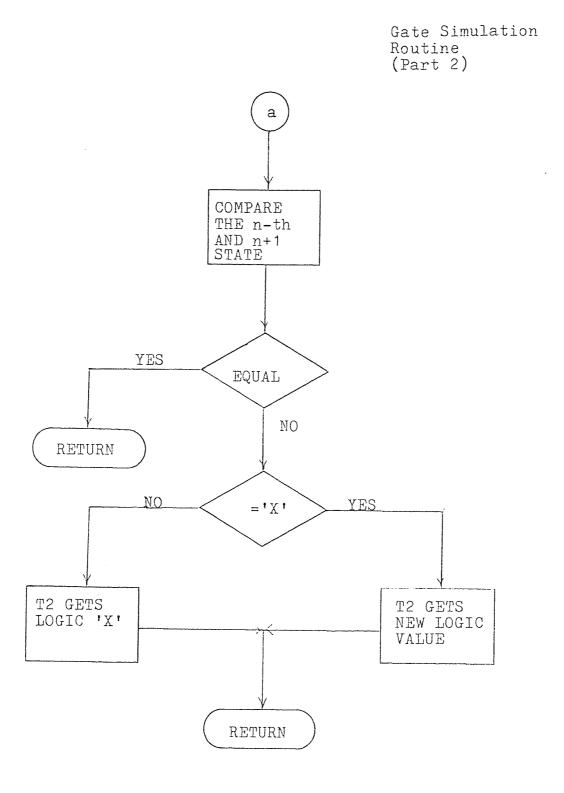

| 4-15          | Gate Simulation Routine            | 87   |

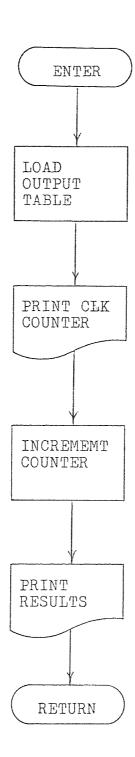

| 4-16          | Outp Function Routine              | 89   |

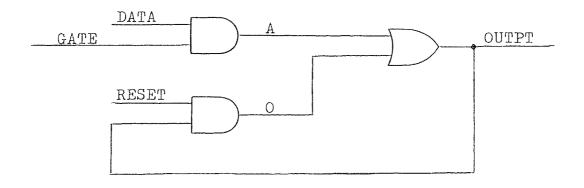

| 5-1           | Race Condition Example             | 118  |

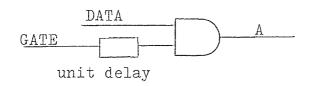

| 5 <b>-</b> 2  | Adding a Delay Block               | 120  |

| Figure | <u>Title</u>                      | Page |

|--------|-----------------------------------|------|

| 5-3    | Another Race Circuit              | 122  |

| 5-4    | Full-Adder Circuit                | 126  |

| 5-5    | Asynchronous Finite State Machine | 131  |

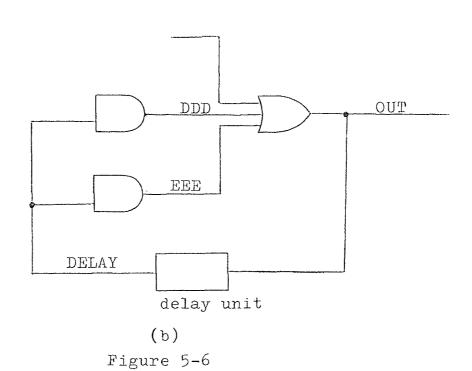

| 5-6    | Circuit with Race Condition       | 134  |

#### CHAPTER 1

#### WHY ANOTHER LOGIC SIMULATOR?

## 1.1 Need for Simulators

The use of computers to assist in the engineering of digital systems is not a new idea. Design automation schemes have been in existence since the first generation computers. The original computer systems were mainly concerned with production logistics such as generating wiring schedules and printed circuit board layouts. The logic design phase was performed manually, using intuition and experience based on the theories of switching circuits. When the MSI and LSI logic components were introduced, the design approach changed radically. The problem was one of sheer complexity. Since digital systems attained such a high level of sophistication, the old conventional design practices proved inadequate to handle these complexities. It therefore became essential to use the computer from the initial design stages.

This is done through the use of the process of simulation, whereby it is possible to model the behavior of a real system either mathematically or functionally.

Experience shows that simulation is one of the most power-ful analysis tools available to the designer. It allows the designer to make expermental designs with systems, real or proposed, where it would otherwise be impossible or impractical to do so.

Computer-Aided Design (CAD) programs were written for the purpose of simulating proposed or experimental systems. Using CAD programs, the designer could explore new ideas and techniques. As results are achieved more rapidly, inoperative designs may be eliminated immediately while positive results are open to exploration.

## 1.2 Levels of Simulation

There are four basic levels at which digital systems can be simulated. The first is known as "System Level," whereby the simulation is used to evaluate the general overall properties of a system. Elements of the system are usually complex devices, and may include buffers, memory modules, arithmetic units, and central processing units. Usually each model is characterized by a set of parameters, such as response time and capacity. System level simulation is primarly used as a means of predicting system performances.

This is followed by the type of simulation known as

<sup>&</sup>lt;sup>1</sup>M. A. Breuer, "Recent Developments in Design Automation," Computer, May/June 1972, pp. 23-35

"Register Transfer Level." At this level data flow is specified at the register level. The simulator operates upon real data, hence the functional design of the system can be evaluated.

The third type of simulation is "Gate Level Simulation." At this level the system is described by a collection of logic gates and their interconnections. Each signal line is restricted primarly to two or three values. Time is usually quantized to the point where one unit of time corresponds to one gate delay time unit.

The final type of simulation is the "Circuit Level." A logic gate circuit may consist of some interconnection of diodes, transistors, and resistors. Here each signal line is not restricted to just two or three values but rather to a quantized interval between two voltages or current levels. In addition time is quantized to a very fine degree. Transitory behavior is usually of primary interest.

Each of the last three levels employs models which are simplifications of those of the preceding level, both in quantitative terms and in terms of behavior. The set of components represented in the circuit level model of a logic gate and the circuit's finite rate of change of state, may be simplified using a gate level model into a single two state element. The state of this element would change instantaneously at discrete time intervals. Simil-

arly sets of gates may be merged together to form elements of a register transfer level model, in which state changes may occur at varing multiples of the basic gate operation time units. Circuit, gate, and register transfer level simulation models represent progressive levels of simplification of an actual system element behavior. This can be viewed as being derived from a direct translation of its electrical characteristics.

A system level simulation model represents a level of simplification of elements of a real system derived by abstraction, rather then by synthesis. Circuit level simulation employs continous time models. This differs fundamentally from those using gate level or register transfer level which employs discrete time models.

### 1.3 Gate Level Simulation

Digital Logic Simulator (DLS) is a gate level simulation program which can be used for analyzing digital logic designs. When given the initial state and the input sequence the simulator will calculate a state-time map of the logic signals.

Most of the early simulators would model gates as elements having zero induced propagation delay time.  $^2$  This

<sup>&</sup>lt;sup>2</sup>M. J. Flomenhoft and B. M. Csencsits, "A Minicomputer Based Logic Circuit Fault Simulator," <u>ASM Sigma Newsletter</u>, Vol. 4, No. 3, 1974, pp. 15-19

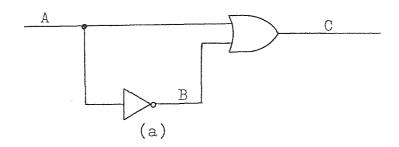

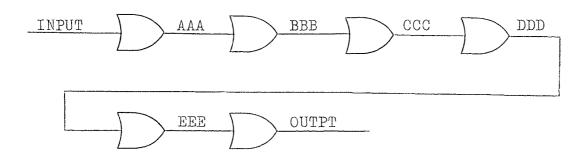

Time Delay Modeling

FIGURE 1-1

implies that the output logic level changes instanteously when the inputs change. An example is shown in Figure 1-1a which depicts a two gate circuit. In a zero delay simulator as the input signal (A) changes from a logic '1' to a logic '0,' the output signal (C) stays constant. This can be seen in Figure 1-1b.

In actuality, this circuit design would have an inherent race condition. One of the two signals being fed into the OR gate will have a propagation delay time longer than the other.

One of the goals for creating DLS was to develop a method of simulation where such hazards could be observed and corrected. DLS has two modes of operation which can show the presence of a race condition. In the first mode, each gate has a single time unit delay before the output changes corresponding to changes of the inputs. Figure 1-1c shows that when the input to the NOT gate changes from a logic '1' to a logic '0' the output signal (B) of the NOT gate is delayed for one time unit before it changes from a logic '0' to a logic '1.' This means that for one time unit both inputs to the OR gate will be at a logic '0' producing a logic '0' on the output. In the next time frame the NOT gate has propagated its signal through the gate producing a logic '1' on one of the inputs of the OR gate which produces a logic '1' on the output.

There is a difference between the simulation of a zero

and a one gate delay circuit simulation. The first simulation had a constant logic '1' on the output where the latter one had a period of time where the output dropped to a logic '0.' In digital circuit design this would be known as a glitch. Using the simulator the designer would be able to see the existence of this hazardous condition and go back to modify the circuit to remove the glitch from the design.

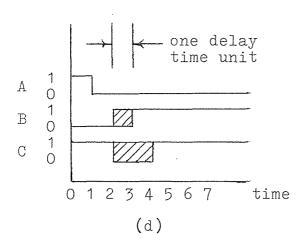

The second mode of DLS uses what is known as a three value simulator. Whenever a signal tries to change its logic level, it enters a transition state. This is a third logic state where the state is neither a logic '1' or a logic 'O.' it is unknown. Figure 1-1d shows that when the output of the NOT gate tries to change its logic level, it enters the transition state for one time unit. In the next time frame the output goes to the correct logic level. The transition state that the NOT gate produced is passed to the OR gate which produces an unknown output. The output of the OR gate will have two transition states due to the fact that in time frame two both inputs were at a logic 'O.' As the output attempts to reach a logic 'O' it is forced into the transition state for one time unit. In the third time frame one of the inputs is in the transition state which keeps the output in the transition state, the glitch.

<sup>&</sup>lt;sup>3</sup>J. S. Jephson, R. P. McQuarrie, and R. E. Vogelsberg, "A Three-Value Computer Design Verification System," <u>IBM</u> System Journal, Vol. 8, No. 3, 1969, pp. 178-189

Finally by the fifth time frame all the signals have settled out. When the results are viewed the fact would be noted that the final output had two time units in which the output is unknown. This occurrence creats a condition that is in all probability hazardous to the operation.

## 1.4 DLS a Microprocessor Based Program

One of the big differences between DLS and other simulators is that it has been implemented on a microprocessor based computer system. Most standard high-level languages, such as Fortran and Basic, are oriented to numerical computations and consequently are extremely inefficient when used for data processing operations. A more efficient approach is achieved through the use of a machine dictated assembly language. Data is usually stored in a tabular or list format. Thus a language capable of setting up data structures in list form that is capable of manipulating the items in the list is required.

DLS was written in assembly language for two reasons. The first is for its ease of handling list structured queues and secondly high-level languages, require large amounts of memory. One of the objectives for writing DLS was to create a system that occupied the smallest amount of memory space, making it possible to run on a small system. Even though assembly languages have the disadvant-

age of being specific to one type of computer, DLS was written for the 8080 microprocessor, an industry standard.

#### CHAPTER 2

#### THREE VALUE SIMULATION

## 2.1 Use of Ternary Algebra

The presence of hazards and races in combinational logic circuits may be detected by using the concept of ternary algebra. In this method a third value 'X' which assumes the value between a logic 'O' and a logic '1' is used to represent unspecified transition periods, initial conditions, oscillations, and don't know states. Basic logic gates can be redefined in terms of ternary functions using logic levels 'O,' '1,' and 'X.' Figure 2-1 shows the truth tables for the basic gates for both two and three logic state simulations.

The using of the three value method allows hazards to be detected that normally go unnoticed in a two value simulation. Figure 2-2a shows the two value simulation for several gates. When the two inputs change simultan-

<sup>&</sup>lt;sup>1</sup>M. Yoeli and S. Rinon, "Application of Ternary Algebra to the study of Static Hazards," <u>Journal of the Association for Computing Machinery</u>, Vol. 11, 1964, pp.84-97

<sup>&</sup>lt;sup>2</sup>J.S. Jephson, R. P. McQuarrie, and R. E. Vogelsberg "A Three-Value Computer Design Verification System," <u>IBM</u> System Journal, Vol.8, No.3, 1969, pp.178-189

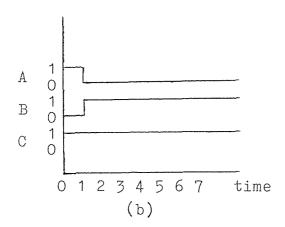

# Two Value Truth Table

|                          | I<br>N<br>1 | I<br>N<br>2      | A<br>N<br>D      | N<br>A<br>N<br>D | 0<br>R      | N<br>O<br>R | E<br>X<br>O<br>R |   |

|--------------------------|-------------|------------------|------------------|------------------|-------------|-------------|------------------|---|

| ØØ:<br>Ø1:<br>Ø2:<br>Ø3: | Ø<br>Ø<br>1 | Ø<br>1<br>Ø<br>1 | Ø<br>Ø<br>Ø<br>1 | 1<br>1<br>1<br>Ø | Ø<br>1<br>1 | 1<br>Ø<br>Ø | Ø<br>1<br>1<br>Ø | _ |

|                          |             |                  | (a               | )                |             |             |                  |   |

# Three Value Truth Table

|                                            | I<br>N<br>1                     | I<br>N<br>2                          | A<br>N<br>D                     | N<br>A<br>N<br>D                     | O<br>R            | N<br>O<br>R     | E<br>X<br>O<br>R  |  |

|--------------------------------------------|---------------------------------|--------------------------------------|---------------------------------|--------------------------------------|-------------------|-----------------|-------------------|--|

| Ø1:<br>Ø1:<br>Ø2:<br>Ø34:<br>Ø5678<br>Ø78: | Ø<br>Ø<br>1<br>1<br>1<br>X<br>X | Ø<br>1<br>X<br>Ø<br>1<br>X<br>Ø<br>1 | Ø<br>Ø<br>Ø<br>1<br>X<br>Ø<br>X | 1<br>1<br>1<br>1<br>0<br>X<br>1<br>X | Ø 1 X 1 1 X 1 X X | 1 Ø X Ø Ø X Ø X | Ø 1 X 1 Ø X X X X |  |

|                                            |                                 |                                      | <b>(</b> b                      | )                                    |                   |                 |                   |  |

Figure 2-1

## Combinational Hazard Detection

Figure 2-2

eously the output stays constant. In three value simulation when a logic level changes state first it must enter the logic 'X' state. Figure 2-2b shows that when both inputs to a gate change at the same time, for one time unit both inputs are unknown. This produces an output which is temporarily unknown. In a larger circuit design this glitch would be passed along to the rest of the circuit which could lead to a possible erroneous final output.

In addition to hazard detection the third logic level may also be used to represent "don't care" input conditions to the circuit. This makes it possible to cut down on the amount of test data required to check a given circuit. For example if it were required to simulate the reset logic of a basic register circuit. Normally this would have to be performed by applying the reset logic to the input repetitively and checking that for every possible combination of input bits the output of the register always goes to a logic 'O.' This would require 2<sup>n</sup> simulation runs, where n is the number of bits in the register. By initally setting all of the bits in the register to the logic 'X' state and then simulating the reset logic, it is possible to determine in one simulation run those stages which do not get reset to a logic 'O' state.<sup>2</sup>

<sup>&</sup>lt;sup>2</sup>Ibid., pp.179

## 2.2 Propagation Hazard Example

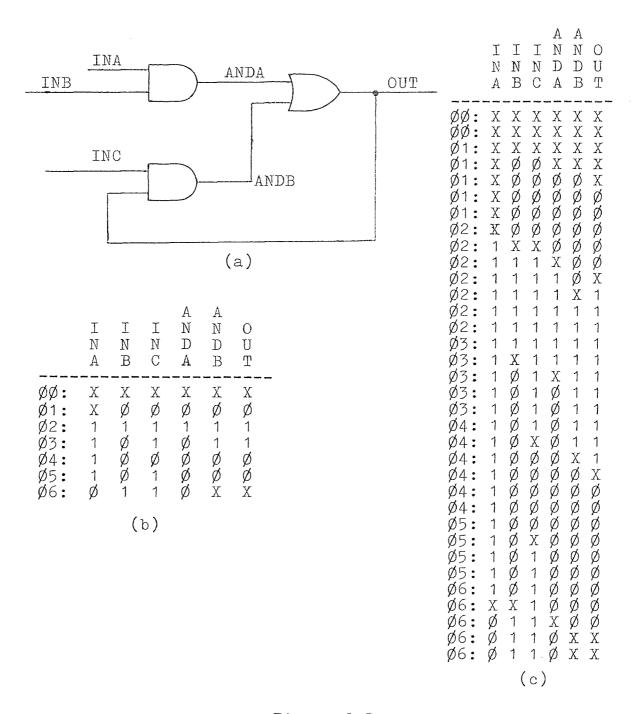

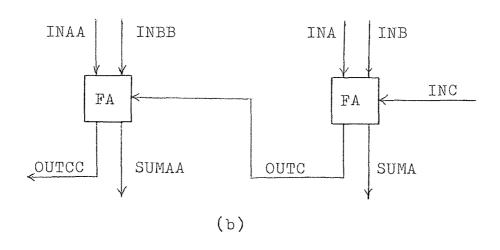

Figure 2-3a is a logic circuit which was simulated by DLS. The circuit consists of two AND gates and one OR gate. The output of the OR gate is fed back to one of the AND gates to form a type of latch. Figure 2-3b is the printout of the DLS simulation operated in the normal mode. Time frame O shows that when the three inputs are unknown the output is unknown. In time frames 1, 2, 3, 4, and 5 the circuit is put through several different test patterns. A problem occurs when the inputs (INA and INB) change their values from time frame 5 to frame 6. This simultaneous change is detected as a possible hazard to the circuit. Due to the creation of the feedback path in the circuit, the glitch is transferred through the OR gate and then back to one of the inputs. This means that the glitch causes the circuit to settle in the unknown state.

As a verification of the results DLS is rerun using the trace mode this time. Figure 2-3c is the DLS trace mode results. The critical point is time frame 6 where the two inputs change simultaneously. INA changes from a logic '1' to a logic 'X' then to the final logic '0' value. On the other hand INB changes from a logic '0' to a logic 'X' and settles to a logic '1.' For one time unit both inputs to the AND gate are unknown. This glitch is fed into the OR gate which will produce a logic 'X' which feeds

## Digital Latch With Hazard Example

Figure 2-3

this value back to the AND gate which will the produce an output of a logic 'X.' Even though the first AND gate has by this time finished changing, the original glitch has caused the output of the circuit to become latched in the unknown state.

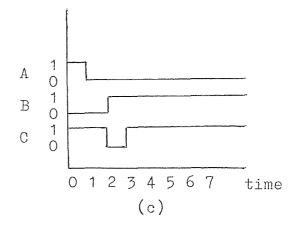

## 2.3 Oscillation Error Example

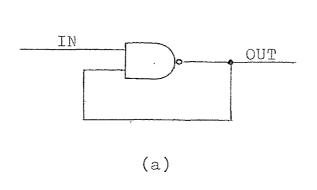

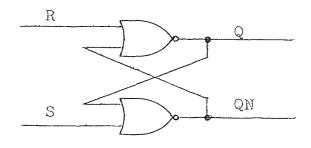

A simple example of an oscillating circuit is expressed in Figure 2-4a. This simple NAND gate has a problem when the input goes to a logic '1,' the output tries to go to a logic '0.' This is then fed back to the other input.

Now what happenes is that the output tries to go to the logic '1' state. This circuit works fine with a logic '0' on the input but whenever it goes to any other logic value the output can not find a stable state so it oscillates.

Another example is shown in Figure 2-4b. The two NOR gates are configured to form a R-S Flip Flop. Note from the results that when no initial condition is given and both inputs are at a logic 'O' the output stays unknown. This is due to the fact that DLS assigns a logic 'X' to all gates prior to the start of the simulation. This circuit operates properly up to time frame 7. Here both inputs (R and S) go to a logic '1' producing outputs (Q and QN) at a logic 'O.' The outputs are stable except by definition one is supposed to be the complement of the other.

# Oscillating Test Circuits

|                                                   | N | O<br>U<br>T                                              |

|---------------------------------------------------|---|----------------------------------------------------------|

| - Ø Ø 1 2 3 4 5 5 6 7 8 9 9 Ø Ø Ø Ø Ø Ø Ø Ø Ø Ø Ø |   | 1<br>1<br>X<br>X<br>X<br>1<br>1<br>X<br>X<br>X<br>X<br>1 |

|                                               | R                     | S | Q                     | Q<br>N                                              |  |

|-----------------------------------------------|-----------------------|---|-----------------------|-----------------------------------------------------|--|

| ØØ1:<br>ØØ2:<br>ØØ4:<br>ØØ56:<br>ØØ9Ø<br>ØØ9Ø | Ø Ø 1 X Ø Ø Ø 1 Ø 1 Ø | - | X X Ø Ø Ø 1 1 Ø X Ø X | X<br>X<br>1<br>1<br>1<br>Ø<br>Ø<br>Ø<br>X<br>1<br>X |  |

Figure 2-4

The problem occurs in this circuit when both inputs now drop from a logic '1' to a logic '0' at the same time. The circuit starts to oscillate which DLS detects in time frame 8.

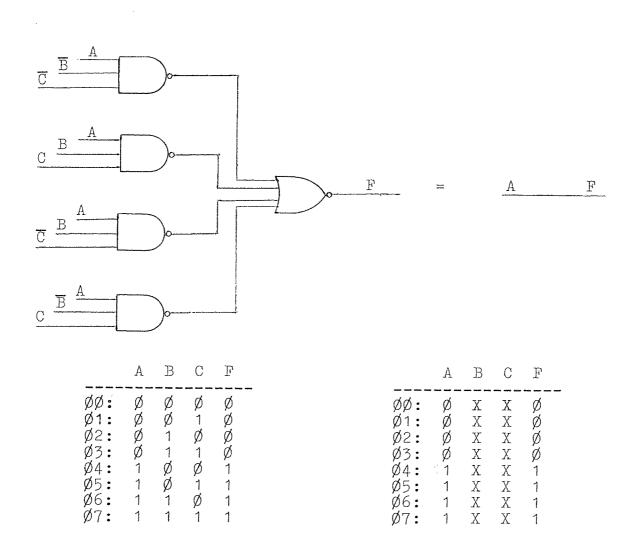

## 2.4 Don't Care Example

Figure 2-5 shows a circuit derived from the equation  $F=A\overline{BC}+A\overline{BC}+AB\overline{C}+AB\overline{C}+ABC$ , which using Boolean Algebra can be reduced to F=A. To prove this, first DLS is made to run through the nine different possible input combinations. The problem is then rerun, this time setting the values of the eliminated variables to the logic 'X' state. The two simulations produce the identical results. This example was not chosen to show reduction techniques but to show that the logic 'X' state could be used in place of don't care situations which may arise.

## Don't Care Example

Figure 2-5

### CHAPTER 3

### TABLE DRIVEN SIMULATION TECHNIQUES

## 3.1 Modeling Approach

A fundamental question is how a digital circuit is to represented or modeled by the computer. There are several ways to model a circuit, each have advantages and disadvantages. The method of digital circuit modeling is dependent upon the type of machine being used. Three important factors which must be considered are machine type, word length, and the number or language of the instruction set.

The simulation model is formed from the inputed source language statements which describe the digital circuit. These statements can either be interpreted directly and then executed or compiled into machine code which is executed later. Most of the earlier simulators were either interpretive or executed compiled code. Current simulators however, employ some form of data structure and are table driven.

For compiled code simulators each source statement

<sup>&</sup>lt;sup>1</sup>M. A. Breuer, <u>Digital System Design Automation</u>, California, Computer Science Press, Inc., 1975, pp. 237-242

generates a set of subroutines which perform the logical function required by each specific element. The simulated network is represented in the computer as a series of interconnected subroutines which evaluates the logical function of each element in the order in which they appear in the circuit. Starting at the input gates and proceding through the circuit, outputs of one gate acting as inputs to the succeeding gates until the final output gates are reached. The disadvantage of this approach is that for each element there could be about five to ten instructions required to perform the simulation. For a fairly large circuit the size of the compiled code would require a fair amount of memory. Another problem is that a compiled code is inherently a zero delay simulation and is extremely inflexible as to the extent of the types of different operations which can be performed during simulation.

## 3.2 Table Driven Simulation Method

In the table driven method, the parameters of each logic element in a circuit is stored in a tabular form. <sup>2</sup>

Each entry consists of such data as logic function, propagation delay, input sources, output values, and output destination. The source language statements are translated

M. A. Breuer, Design Automation of Digital Systems, New Jersey, Prentice-Hall, Inc., 1972, pp. 127-128

into a data structure representing the circuit. During simulation the data structure is operated on by a control program which analyzes the information in the lists in accordance with the simulator command statements to determine the flow of data and logical values in the network.

The interpreter program operates by evaluating all the elements and assessing those subroutines which are required by the program rather than having individual macros for each element. When a large circuit design is simulated the running time of the simulator could become a factor because of the sequential nature of the program and the number of instructions to be executed. In a table driven simulator for a given input pattern only a certain number of the elements will be changing their logic states. A large reduction in computation time is achieved in DLS because only those elements which are supposed to change states are evaluated.

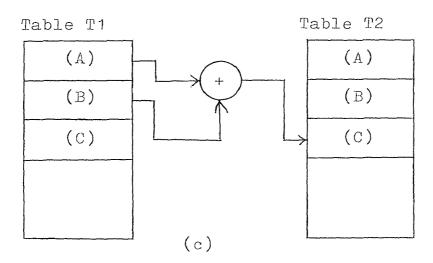

## 3.3 Dual Table Simulation

DLS contains seven tables but the heart of the program is contingent upon two of the tables. These two tables are known as T1 and T2, contain all the logic levels of the network. Each logic level is stored in one word of memory, in the case of the 8080 microprocessor a word of memory is 8 bits in length. At the beginning of the simulation run

# Dual Table Operation

Figure 3-1

both T1 and T2 contain the same information. If no initial condition is given for each element a logic 'X' is automatically assigned to the output of that element.

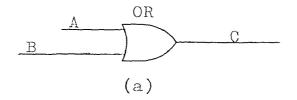

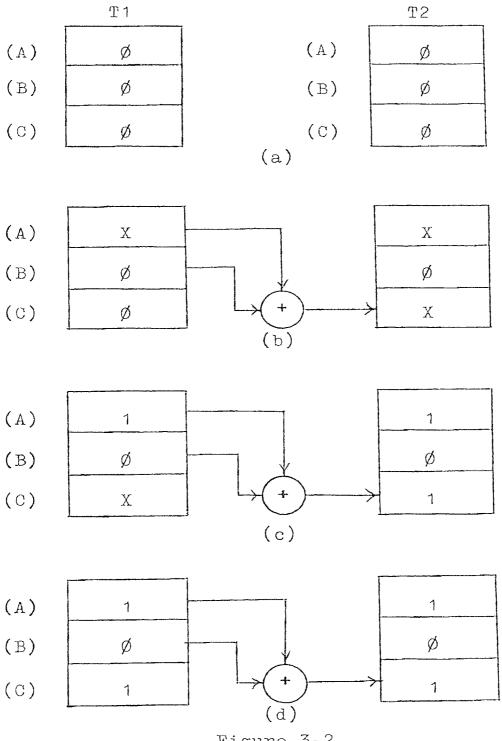

The simulation is done by taking the inputs from T1, performing the logic function called for and storing the results in T2. For example, Figure 3-1a shows a single two input one output OR gate. In DLS a line of source code to describe the gate is shown by Figure 3-1b. line tells the interpreter program the type of logic gate, the number of inputs, the input symbols, the output symbol, and any initial condition for the output symbol. program would translate this line code and assign three words of memory for T1 and T2 for this one element. Each table would have the same logic levels assigned to them at the beginning of the simulation. During the simulation the two input values would be taken from T1, operated upon and stored in the output, located in T2, as can be seen in Figure 3-1c. At this point a comparison is made between the contents in T1 and T2. If the two tables contain the identical information then the simulated circuit is said to have reached a stable state. Disagreement indicates that some of the signals are still being propagated through the circuit.

If only one table existed there would be no way to ascertain whether the network had reached a stable state, since there would be no record of the previous state. Two

tables make it possible to check the stability of the circuit. After all logical operations were performed T1 would contain the n-th state while T2 would contain the n+1 state. When comparing the n-th and n+1 states of the network it can be determined if the network had achieved a stable state.

A clarification of this analysis may be seen in the example shown by Figure 3-2, which is a simulation run of Figure 3-1a. Assume that both inputs (A and B) are at a logic 'O' and the initial condition of the output (C) is also at a logic 'O.' Figure 3-2a shows that at the start of the simulation both T1 and T2 contain the same data. Assume now that one of the inputs (A) is going to change to a logic '1,' but in a three value simulation it must for one time unit be at the transition level 'X.' The 'X' value is substituted into the (A) location in T1 and T2, then the OR operation is performed as seen in Figure 3-2b. A comparison is made between T1 and T2. Since they are not the same the operation is not yet complete, so T2 is copied over into T1. The n+1 state now becomes the n-th state and a new n+1 state must be generated. Now that the input (A) has been in the transition state for the required time it now goes to a logic '1.' Another OR operation is performed as can be seen in Figure 3-2c. Again after the operation T2 is not equal to T1 so it is copied into T1 and again another OR operation is done. This time T1 is

# OR Gate Simulation

Figure 3-2

the same as T2 so the simulation update cycle is complete, all signals have been propagated through and stability in the circuit has been achieved. Using three value simulation it took two time units to produce the correct output, but it took three time units for the circuit to be considered stable in DLS.

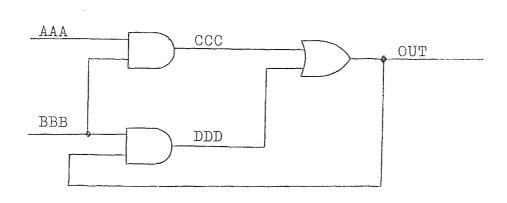

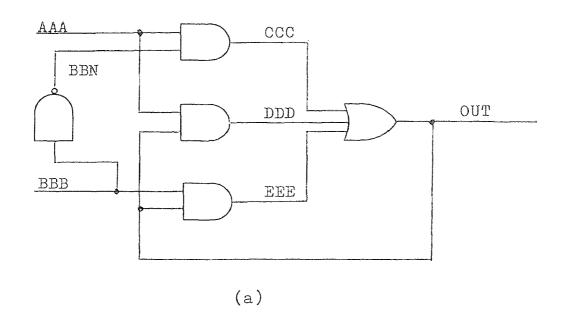

#### 3.4 Table Setups

It is the formation of the other five tables which the translator portion of DLS uses to setup the dual simulation tables. Certain information has to be extracted from the source program and broken down into the different tables. Consider Figure 3-3a which is a two element device. The enclosed area shows the portion of the circuit which will be under test. The lines extending from this area are the test inputs and the test output. Other internal signals can be monitored where applicable. To simulate this circuit using DLS the device is described by English language type statements, shown in Figure 3-3b. The program must be given the test inputs, test output, gate type, and any initial conditions.

The first thing DLS does is to scan for all symbols used in the circuit description. Figure 3-3c shows the creation of the symbol table. Each symbol, which can be up to five characters in length, is stored in the symbol

Figure 3-3

table along with its corresponding address as seen in tables T1 and T2. The symbol table is very important since all the other tables will access it to determine the locations of the symbols in table T1 and T2.

DLS then looks for certain control words for the formation of the test input table. Once DLS finds the control word, it then scans the rest of the line for symbols whose addresses can be found in the symbol table. DLS completes the operation by storing the input symbol addresses in the input table. In addition a count of the number of test inputs is maintained as shown in Figure 3-3d.

The same procedure is done in determining what points of the circuit the user wants to monitor during simulation. In this case DLS will scan for the print control word. Addresses are extracted from the symbol table and stored in the output table along with the count on the number of outputs, as seen in Figure 3-4a. For both the input and output tables, the addresses assigned are those corresponding to table T1. Since after a simulated network has reached a stable state T1 will contain the same information as T2, there would be no need to access information from T2.

The next two tables to be formed are created simultaneously. DLS scans the program looking for the logic gates. When a gate is found that gate type count will be incremented (Figure 3-4b) and then DLS will create an updating sequence table (Figure 3-4c). The update sequence for any two input

# Simulation Tables

|                                                                 |      | Gate Type | Table |  |

|-----------------------------------------------------------------|------|-----------|-------|--|

| Output Table                                                    |      | Gate Type | #     |  |

| (A)                                                             |      |           | 1     |  |

| (B)                                                             |      | OR/2      | 1     |  |

| (C)                                                             |      | NAND/2    | 0     |  |

| (E)                                                             |      | (b)       |       |  |

| (a)                                                             |      | T1        | ī     |  |

| Update Sequence                                                 | (A)  | X         |       |  |

| (A)                                                             | (B)  | X         |       |  |

| (B)                                                             | (C)  | X         |       |  |

| (D):                                                            | (D)  | Ø         |       |  |

| (D)                                                             | (E)  | 1         | (d)   |  |

| (c)                                                             |      | T2        |       |  |

| (E)'                                                            | (A)  | X         |       |  |

| (c)                                                             | (B)' | X         |       |  |

| ( ) memory location in T1 table ( ) memory location in T2 table | (C)  | X         |       |  |

|                                                                 | (D)' | Ø         |       |  |

|                                                                 | (E)  | 1         |       |  |

|                                                                 |      | (ė)       |       |  |

Figure 3-4

input device would consist of the two inputs to the gate whose addresses are located in table T1, followed by the output, whose address is located in table T2. For logic elements with four inputs and one output, the update sequence table would contain four addresses from T1 and one from T2. It should be noted that prior to simulation all symbols which were not given any initial condition are assigned a logic 'X' to their respective locations. Symbols with assigned initial conditions are inserted in both tables T1 and T2 prior to simulation.

#### CHAPTER 4

#### THE DLS PROGRAM

### 4.1 DLS Program Structure

The DLS simulator was written in a format kmown as a modular program. There are three distinct modules; controller/editor, compiler, and executor. Each module acts independent of each other but can not operate without the others. Parameters are not passed back and forth between modules but instead the controller will partition off blocks of memory where all the necessary information will reside. These blocks of data or tables have no fixed memory addresses. Also each table does not have any fixed size. Figure 4-1 shows how the memory would be allocated for a given simulation. The object file of DLS occupies the first 4K block of memory. The control program then partitions off the rest for the tables.

The source program which is the topological description in the DLS language is entered into the memory via the editor. As each line of data is taken in and stored in memory, the size of the source program increases. The control program will then alter where the next open source

# Memory Allocation

| BEGIN          |                              | 7 |      |

|----------------|------------------------------|---|------|

| START          | DLS PROGRAM (object file)    |   |      |

| NEXT<br>SYMBS  | SOURCE PROGRAM (source file) |   | = 4K |

| SYMBE<br>T1S   | SYMBOL TABLE                 |   |      |

| T1E<br>T2S     | SIMULATION<br>TABLE 1 (T1)   |   |      |

| T2E            | SIMULATION<br>TABLE 2 (T2)   |   |      |

| INP            | INPUT FILE<br>TABLE          |   |      |

| OUTP           | OUTPUT FILE<br>TABLE         |   |      |

| SIMTS<br>SIMTE | UPDATE<br>SEQUENCE TABLE     |   |      |

Figure 4-1

program location will be located in memory. If there are alterations in the source program any previously compiled network becomes void. This is because when the source program increases or decreases in size the other table addresses will not be altered, meaning source code information may overlap into the table area.

Once the network description is complete the compiler module will be called upon. The compiler takes the source program and breaks it down into the representing data structure. Once the compiler sets up the tables it is the function of the execution module to perform the simulation. The executer contains a simulation controller which calls upon the user to setup certain simulation parameters. Using these parameters plus the compiled tables the network can now be simulated.

## 4.2 Source Program Requirements

It is possible to define logic circuits in terms of Boolean equations but impractical for large complex circuits. To reflect the implemented configuration the equations would have to be derived directly from the actual circuit. Such an approach would be rather cumbersome. A better way would be based on an element description. Each element

<sup>&</sup>lt;sup>1</sup>H. J. Kahn and J. W. R. May, "The Use of Logic simulation in the Design of a Large Computer System," The Radio and Electronic Engineer, Vol. 43, No. 8 pp. 497-503

would have its inputs and output uniquely defined, making it easer to define complex compound modules. An element would consist of gate type, number of inputs, and the output. DLS uses this along with another parameter, the initial condition. This helps eliminate transients which would exist when the simulation first begins, since all logic elements which are not given an initial condition are put into the logic 'X' state.

DLS is slightly limited in the types of elements it can presently simulate. Figure 4-2a and 4-2b show the types of elements which DLS can handle. That which is in capitalized letters must be typed by the user, the lower case letters are where the user would put variable names, which can be up to five alphabetic characters in length. The initial condition is optional to the user and can be completely left out.

It is the users responsibility to inform DLS, within the source program, which logic variables are primary inputs and which are monitored outputs. A primary input is a variable whose logic level is not generated internally in the circuit but rather must be supplied externally by the user. They can be considered the test input paths. The monitored output points are those variables which the user wants to view during the simulation. The format for these operations is shown in Figure 4-2c.

The final requirement for DLS to operate is that the

## Command Word Format

```

.AND/2.

IC=___

in1, in2, out

.NAND/2.

in1,in2,out

.OR/2. in1,in2,out

.NOR/2. in1,in2,out

.EXOR/2. in1,in2,out

IC=

IC=

IC=

(a)

IC=

.AND/4.

in1, in2, in3, in4, out

in1, in2, in3, in4, out in1, in2, in3, in4, out

.NAND/4.

IC=

.OR/4.

IC=

.NOR/4.

.NOR/4. in1,in2,in3,in4,out

.EXOR/4. in1,in2,in3,in4,out

IC=

IC=

(b)

.INPUT. a1,a2,a3,...,a<sub>n</sub>

.PRINT. 61,62,63,...,bn

(c)

.END.

```

(d)

last line in the program must be as shown in Figure 4-2d. This statement informs the compiler that there is no more source code to be compiled.

## 4.3 The Controller/Editor

The controller/editor module performs two duties for DLS. Its first task is to interact with the user to determine what action DLS is to perform. The second duty is to edit the source program which the user loads into the computer via a terminal.

Each line must have a four digit identification as the first four characters. This is simular to the program language Basic. As each line comes in the source program is scanned for where the new line will go. This is done by scanning the source program for the other line indentifiers then comparing it with that of the new line. Figure 4-3 shows the flowchart depicting how the editor goes about placing a new line into memory. What must first be done is to determine if a line with the same number already exists in the source program. If it does it must first be deleted from memory. After that has been determined then the routine finds where the new line goes and puts it there.

Figure 4-4 is the controller routine flowchart. Its

Figure 4-4

Command Function Selection Routine

task is to get a line of information from the user and determine if it is a command or source data. If it is source data and it fits the proper format then the source program update routine will be implemented. If it is a command then the controller will call the command function selector routine. The function selection process is done by simply matching up the contents in the input buffer to some test patterns to determine which function is to be implemented. This process is shown in Figure 4-5.

DLS has six command functions which can be performed. Two of these commands (COMP and EXEC) will pass control over to either the compiler or the execution modules. Three of the remaining four commands are editor orientated. This entails some sort of source program manipulation. The command NEW will reset the source program memory pointers, erasing any previous source program. The command LIST will print all of the source program which had been entered by the user. The command RESEQ will resequence all the line identifiers of the source program in memory. Starting from zero for the first line and working up in steps of ten.

The sixth command FAN can not be called upon until the compiler module has been implemented. FAN will calculate the fanout (the number of connections per logic line) of the simulated network.

# 4-4 The Controller/Editor Program Listing

```

: MAIN PROGRAM

; FUNCTION

: OUTCH, GETCH, CRLF

; CALLS

; INPUTS

: BEGIN, DATA, BUFFR

; OUTFUTS

:START, LENTH

: THIS IS THE CONTROLLER AND

: DESCRIPTION

: EDITOR PROGRAM. IT PRINTS

: OUT ALL THE NECESARY TITLES

: AND INTERACTS WITH THE USER

: TO DETERMINE IF THE USER IS

: INPUTING A STRING OF DATA OR

: REQUESTING CERTAIN OPERATIONS

: TO TAKE PLACE

ì

ĵ

÷

BEGIN:

LXI

SP, BEGIN

LXI

H, DATA ; BEGINNING OF SOURCE PROGRAM

SHLD

START

LXI

H, AAZ

FRINT OUT THE PROGRAM TITLES

AA1;

MOV

AIM

INX

---(

CFI

0

JΖ

NEW

CALL

OUTCH

JMF

AA1

AA2:

DB

ODH, OAH

DB

OAH, 20H, 20H, 'DIGITAL LOGIC'

DB

' SIMULATOR', OAH, OAH, O

:EAA

CALL

CRLF

MVI

B, 54

; SETUP AN INPUT BUFFER

LXI

H, BUFFR

AA4:

MVI

M, 20H

INX

H

DCR

B

JNZ

AA4

MVI

A, '; '

CALL

DUTCH

FRINT THE PROMPT MESSAGE

LXI

H, BUFFR

MVI

B, 0

AA5:

; INFUT A STRING OF CHARACTERS

CALL

GETCH

CF. I

; TO BE INTERPERATED, OR ENDS A LINE

ODH

J Z

AAZ

DFI

18H

; CONTROL 'X' KILLS THE LINE

JZ

EAA

OPI

7FH

ITHIS BACKSPACES ONE CHARACTER IN

JNZ

AA6

; THE STRING

MOV

A, E

```

```

ORA

Α

.17

AA3

MVI

A,08H

CALL

OUTCH

DOR

В

M, 20H

MVI

DCX

H

JMP:

AA5

AA6:

MOV

M, A

; LOAD CHARACTER INTO BUFFER

INX

H

INR

B

MOV

A, B

65

CFI

; BUFFER STRING CAN ONLY BE 64

AA5

; CHARACTERS IN LENGTH

JNZ

AAZ:

LXI

HIBUFFR ; START TO INTERPERATE THE STRING

MOV

A, B

STA

LENTH

MOV

A.M

101

CP I

FIRST TO SEE IF THE LINE STARTS

JM

AA8

191+1

CF I

; WITH A DIGIT WHICH MEANS THE

JM

LINE

STRING IS DATA TO BE STORED IN

CPI

L

; THE SOURCE PROGRAM

JZ

; JUMF TO LIST ROUTINE

LIST

'N'

CFI

JZ

NEW

; JUMP TO 'NEW' ROUTINE

CF.I

1 R1

JΖ

RESER

JUMP TO 'RESEQUENCE' ROUTINE

CFI

101

JZ

COMF

JUMP TO THE COMPILER ROUTINE

'F'

CPI

JZ

EXEC

; JUMP TO THE EXECUTION ROUTINE

CPI

1F1

JΖ

FAN

JUMP TO THE FANOUT ROUTINE

AA8:

LXI

H, AA10

; IF NO MATCH EXISTS THEN

AA9;

MOV

A,M

FRINT OUT THE ERROR MESSAGE

CPI

Õ

JZ

AA3

; THEN TRY AGAIN

CALL

OUTCH

INX

H

JMF

AA9

A010:

DB

ODH, OAH, '**ERROR**', O

÷

ý

÷

ĵ

; FUNCTION

;LIST

; CALLS

: CRLF, OUTCH

; INFUTS

: NOTHING

```

```

; OUTFUTS

: NOTHING

; DESCRIPTION

:LIST PRINTS OUT THE USERS

: SOURCE PROGRAM FROM MEMORY

ż

ŷ

CALL

CRLF

LIST:

; CALL CARRAGE RETURN AND

CRLF

CALL

; LINE FEED

LHLD NEXT

; LAST BYTE OF SOURCE PROGRAM

XCHG

LHLD

START ; FIRST BYTE OF SOURCE PROGRAM

AB1:

MOV

ALL

CMP

E

AB2

JNZ

MOV

A, H

; TEST TO SEE IF THIS IS THE LAST

D

CMF

; BYTE TO BE PRINTED

JΖ

EAA

AB2:

MOV

A, M

CALL

OUTCH ; OUTPUT THE CHARACTER TO THE PRINTER

INX

Н

JMF

AB1 ; GET NEXT BYTE

ĵ

÷

; FUNCTION

: NEW

;CALLS

: NOTHING

; INFUTS

:START

:NEXT

; OUTPUTS

; DESCRIPTION

: NEW CLEARS OUT THE SOURCE

:OLD PROGRAM MEMORY BUFFER

÷

÷

ż

CRLF ; FRINT CARRAGE RETURN AND LINE FEED

CALL

NEW:

H, AC2

; PRINT THE MEMORY PROTECT MESSAGE

LXI

AC1:

MOV

A, M

CF I

Ō

AC3:

JZ

CALL

DUTCH

·INX

H

AC1

JMP

"'CLEAR MEMORY ?',O

ACZ:

DB

```

```

GET A CHARACTER FROM THE CONSOLE

AC3:

GETCH

CALL

CPI

'N'

FOR THE RESPONCE TO THE QUESTION

; N -- DON'T CLEAR THE MEMORY

JZ

EAA

7 Y 7

CFI

;Y-- CLEAR THE MEMORY

AC1-3

; ANYTHING ELSE TRY ACAIN

JNZ

LHLD

START

NEXT

SHLD

JMF'

AA3

;

; FUNCTION

RESEG

; CALLS

: NOTHING

; INFUTS

: NEXT, START, WORK

; OUTFUTS

: NOTHING

: EACH LINE OF SOURCE PROGRAM HAS

; DESCRIPTION

: A FOUR DIGIT NUMBER ASSIGNED TO

: IT, RESER WILL RESERVENCE THE

: FOUR DIGITS IN STEPS OF TEN

ż

NEXT ; GET THE FIRST AND LAST

RESEG:

LHLD

XCHG

; BYTES OF THE SOURCE PROGRAM

LHLD

START

MVI

A, 101

; SET THE LINE COUNTER TO ZERO

PUSH

14

H, WORK

LXI

MVI

B, 4

;STORE THE LINE NUMBER AWAY

ADI1:

MOV

M, A

Н

INX

R

DCR

JNZ

AD1

605

Η.

; TEST TO SEE IF THIS IS THE LAST

AD2:

MOV

A, L

CMP

Ε

; LINE HAS BEEN RESERVENCED

JNZ

EDA

MOV

A.H

CME

[t

; IF ALL DONE RETURN TO CONTROLLER

JΖ

EAA

; SCAN FOR THE BEGINNING OF A LINE

ADG:

MOV

A, M

INX

Н

CPI

OAH

AD2

JMZ

FUSH

\mathbf{D}

```

```

MVI

B, 4

D, WORK ; RESEQUENCE THIS LINE

LXI

AD4:

D

LDAX

; UPDATE RESEQUENCE COUNTER

MOV

M, A

INX

\prodI

14

INX

DCR

В

JNZ:

AD4

MVI

В,З

AD5:

DCX

D

D

LIC X

LDAX

\Gamma

INE

191+1

; COUNTER IS A DECMIAL COUNT

CPI

JP

AD7

STAX

D

AD6:

P'OF'

\mathbf{D}

EDA

JMF

A, 'O'

ADI7:

MVI

STAX

D

DCR

B

JNZ

AD5

JMF'

AD6

; FUNCTION

:LINE

; CALLS

: EXIST, FIND, OPEN, TRANS

; INPUTS

: BUFFR, LENTH

; OUTPUTS

: NOTHING

; DESCRIPTION

:LINE IS THE ROUTINE WHICH

: TAKES THE INPUT DATA STRING

: WHICH IS TEMPORALLY IN A DATA

: BUFFER AND MOVES IT TO ITS'

:PROPER LOCATION IN THE

:SOURCE PROGRAM

÷

÷

LINE:

LXI

H, BUFFR+1

B,3 ; TEST TO MAKE SURE THAT THE

MVI

AE1:

YOM

A, M

; LINE IN THE BUFFER HAS A

CFI

101

FOUR DIGIT IDENTIFIER ON IT

JM

BAA

CPI

191+1

```

```

JP

AA8

INX

H

DCR

В

JNZ

AE1

EXIST

; SEE IF THE LINE EXISTS ALREADY

CALL

; IF IT DOES DESTROY THAT LINE

LENTH

LDA

CPI

5

JM .

AA3

; FIND WHERE THE LINE SHOULD GO

CALL

FIND

CALL

OPEN

FOREN A SPACE FOR THE LINE

CALL

TRANS

; MOVE BUFFER INTO SOURCE MEMORY

JMP

EAA

ź

ź

; FUNCTION

:EXIST

: NOTHING

; CALLS

; INPUTS

: NEXT, START, BUFFR

; OUTPUTS

*NEXT

; DESCRIPTION

: EXIST EXAMINES THE FOUR DIGIT

: IDENTIFIERS IN THE TEMPORY

; BUFFER AND SEARCHES THROUGH THE

:SOURCE PROGRAM TO SEE IF A LINE

:WITH THE SAME NUMBER EXISTS. IF

: IT DOES THAT LINE WILL BE DESTROYED

EXIST:

LHLD

NEXT

; LOAD THE PARAMETERS OF THE

XCHG

* SOURCE PROGRAM

LHLD

START

; TEST TO SEE IF A COMPLETE

AC1:

MOV

A+L

CMP

E

; SEARCH HAS BEEN MADE

AG2

JNZ

YOM

A, H

CMF

\square

JNZ

AG2

RET

; LINE NOT FOUND

AG2:

MOV

A,M

INX

H

CFI

; FIND THE BEGINNING OF A LINE

DAH

JNZ

AG1

PUSH

D

PUSH

H

MVI

0,4

```

48

```

LXI

B, BUFFR ; LOAD THE FOUR DIGITS FROM BUFFER

AG3:

LDAX

B

CMP

M

; COMPARE WITH THE IDENTIFIER

JΖ

AG4

; IN THE SOURCE PROGRAM

POP

H

FOP

D

JMF'

AG1

AG4:

INX.

B

INX

H

DCR

D

JNZ

AG3

POP

14

POP

\Gamma

DCX

H

DCX

Н

PUSH

TI

F'OF'

B

PUSH

1

F'OF'

\mathbf{D}

INX

D

AC5:

LDAX

\Box

CF'I

ODH

JZ

AG6

INX

\square

YOM

A, D

; IF THE LINE IS FOUND TO BE

CMP

B

JNZ

AG5

; THE LAST LINE IN MEMORY THEN

FRESET THE NEXT BYTE TO THE

MOV

A, E

; BEGINNING OF THIS LINE

CMF

\mathbb{C}

JNZ

AG5

SHLD

NEXT

RET

AG6:

LTIAX

\Gamma

MOV

; LINE HAS BEEN FOUND DESTROY IT

M, A

INX

\Gamma_1

INX

H

; TRANSFER THE REST OF THE

MOV

A, D

; MEMORY BLOCK TO CLOSE THE

CMP

В

JNZ

AG6

; AREA WHERE THE OLD LINE WAS

MOV

A,E

CMF'

AG6

JNZ

RECALCULATED NEXT BYTE ADDRESS

SHLD

NEXT

RET

÷

```

; FUNCTION

: TRANS

```

; CALLS

: NOTHING

: BUFFR, WORK

; INFUTS

; OUTFUTS

: NOTHING

:TRANS WILL TRANSFER THE INPUT

; DESCRIPTION

:DATA STRING WHICH RESIDES IN

: THE TEMPORY BUFFER, TO THE

:SOURCE PROGRAM MEMORY

LXI

D, BUFFR ; BEGINNING OF THE BUFFER

TRANS:

LHLD

WORK

; WHERE IN MEMORY IT WILL GO

MVI

M, ODH

INX

14

MVI

M, OAH ; ATTACH THE LEADER CHARACTERS

INX

H

MVI

B,64

AF1:

LDAX

D

MOV

M, A

; TRANSFER THE BUFFER OVER

INX

Н

; TO SOURCE MEMORY

INX

I^{\dagger}

DCR

B

AF1

JNZ

RET

ĵ

÷

; FUNCTION

; FIND

; CALLS

: NOTHING

: NEXT, START, BUFFR

; INFUTS

; OUTPUTS

: WORK

; DESCRIPTION

:FIND ROUTINE SEARCHES THROUGH

:MEMORY TO FIND THE ADDRESS

ĵ

:WITHIN THE SOURCE PROGRAM

:WHERE THE NEW LINE OF DATA GOES

÷

;

FIND:

L.HLD

NEXT ; LOAD THE SOURCE PROGRAM PARAMETERS

XCHG

LHLD

START

AH1:

MOV

A, L

; CONDUCT A MEMORY SEARCH

```

```

CMP

E

AH2

JNZ

MOV

A,H

CMP

D

AH2

JNZ

XCHG

SHLD

WORK

RET.

AH2:

MOV

A, M

INX

H

CPI

;TO FIND THE BEGINNING OF A LINE

OAH

JNZ

AH1

FUSH

\Pi

PUSH

Н

MVI

D, 4

LXI

B, BUFFR ; COMPARE THE FOUR DIGIT INDENTIFIERS

AH3:

LDAX

B ; TO DETERMINE IF THE LINE IN THE

CMP

M

; BUFFER SHOULD GO BEFORE THIS

JM

AH5

; LINE IN MEMORY

JZ

AH4

F'OP

H

POP

D

JMP

AH1

AH4:

INX

R

H

INX

DCR

D

EHA

; NOT THIS LINE MOVE ON TO

JNZ

AH5:

FOP

1-1

; NEXT LINE

DCX

Н

DCX

H

FOF

\Gamma

SHLD

WORK ; FOUND WHERE IT SHOULD GO

RET

÷

÷

ź

; FUNCTION ; OPEN

; CALLS

: NOTHING

: NEXT, WORK

; INFUTS

; OUTPUTS

: NEXT

; DESCRIPTION

: OPEN IS THE ROUTINE WHICH

: OPENS A 66 BYTE STRING IN

:THE SOURCE PROGRAM TO MAKE

ROOM FOR THE INCERTION

OF THE NEW LINE OF DATA

÷

ż

```

÷

```

÷

GET THE LAST BYTE OF DATA

NEXT

OPEN:

LHLD

XCHG

; THIS IS WHERE THE DATA INCERTION

WORK

LHLD

; WILL TAKE PLACE

PUSH

Н

POP -

B

В

DCX

LXI

H, 66

DAD

D

; MOVE THE LAST BYTE OF DATA

NEXT

SHLD

A, D

; 66 BYTES LOWER

AI1:

MOV

CMP

В

JNZ

AI2

A, E

MOV

CMP

\mathbb{C}

RZ

; MOVE THE BLOCK OF DATA FROM

AIZ:

LDAX

D

; THE POINT WHERE THE INCERTED

MUA

M, A

; LINE WILL GO TO THE LAST

D

DCX

Н

; LINE, DOWN TO THE NEW NEXT LOCATION

DCX

JMP

AI1

7

; FUNCTION

:FAN

; CALLS

:CRLF, DUTCH, PRBYT

; INPUTS

:SYMBS, SIMTE, SIMTS, WORK

; OUTPUTS

* WORK

; DESCRIPTION

: FAN SEARCHES THROUGH THE

SYMBOL TABLE TO FIND EACH

:SYMBOL AND COUNT HOWMANY

:TIMES THAT SYMBOL IS USED

: IN THE NETWORK FOR COMPUTING

:THE FANOUT OF EACH LOGIC LEVEL

÷

÷

FAN:

CALL

CRLF

CALL

CRLF

LHLD

SYMBS

;START OF SYMBOL TABLE

AJO:

MVI

II, 5

AJ1:

YOM

A, M

GET A SYMBOL

```

```

/e/

; END OF SYMBOL TABLE INDICATOR

CPI

JΖ

EAA

CPI

0

JNZ

$+5

MVI

A+20H

OUTCH

; PRINT THE SYMBOL

CALL

INX

DCR

D

JNZ

AJ1

A+ ' + '

MVI

OUTCH

CALL

MOV

C, M

INX

Н

MOV

B, M

INX

H

PUSH

Н

A, 0

;STORE THE ADDRESS OF THE SYMBOL

MVI

WORK

FROM T1 TABLE IN THE WORK REGISTER

STA

SIMTE

LHLD

XCHG

LHLD

SIMTS ; LOAD SIMULATION TABLE

AJ2:

MOV

A,H

CMP

; SYMBOL TABLE SEARCH

TI

JNZ

ELA

MOV

A, L

CMP

E

JNZ

AJ3

FOP

LDA

WORK

; SEARCH DONE PRINT THE RESULTS

; OF HOW MANY TIMES THAT

CALL

FRBYT

CALL

CRLF

; SYMBOL IS USED

INX

H

H

INX

JMP

AJO

; MOVE ON TO NEXT SYMBOL

AJ3:

MOV

A, M

INX

H

CMF'

\mathsf{C}

JΖ

AJ4

; MAKE THE ADDRESS COMPARISON

INX

AJ2

JMP

AJ4:

MOV

A,M

INX

Н

CMF'

B

JNZ

AJ2

WORK

LDA

; EACH TIME A MATCH EXISTS

ADI

1

DAA

; ADD DNE TO ITS FANOUT COUNT

STA

WORK

JMF

AJ2

```

#### 4.5 The DLS Compiler

The routines which form the compiler portion of the simulator are the heart of DLS. The compiler module can be broken down into six sub-modules and it is the task of these sub-modules to create the various tables which drive the simulator.

Once the source program has been entered into memory via the controler/editor, the user issues the proper command word (COMP) which initates the execution of the compiler. The DLS compiler is unlike the standard meaning of a compiler, where the source program is broken down into another form of a program which is more easly understood by the computer. The DLS compiler does not work this way. It makes several passes over the source program extracting different pieces of information as it goes along.

Memory is partitioned off by the compiler for the formation of the tables where the extracted information will reside. For example the compiler has to know how many symbols the source program uses. This determines the size of the tables T1 and T2. The compiler must also know how many of each logic gate from the gate library are being called upon. This determines the size of the simulation update sequence tables and so on.

In the style of modular programming the compiler routine is simply a controller. Figure 4-6 is the flow-

# Compiler Function Routine

Figure 4-6

chart of the compiler routine. It performs the duty of directing the flow of the program through several routines. The six routines called upon are: SUM, PRNT, SYMB, PACK, IO, SETUP. Each of these sub-modules may have several sub-sub-modules which will be called upon.

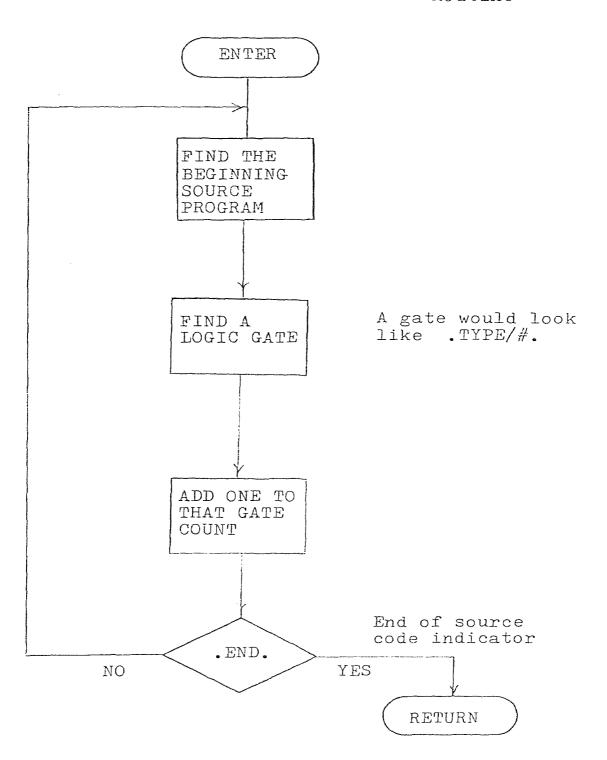

The SUM routine is assigned the task of determining how many of each type of logic gate are going to be used in the simulation. Figure 4-7 is the flowchart for this routine. There are ten types of logic gates which can be implemented by DLS. The SUM routine sets up the table which will keep track of the gate count. The routine will terminate when the end control word is encountered.

The PRNT routine does not extract any information from the source program but rather aids in error detection. PRNT prints out the source program listing along with the gate count table. The user can readily determine if all the logic gates were accounted for in the compiling. Figure 4-8 shows the flowchart for this routine.

The SYMB routine performs a major task. It scans through the source program picking out all the different symbols being used. The routine must be able to distinguish between a symbol and some other type of information. Figure 4-9 has the flowchart of this routine. To determine what is what the routine first looks for a line containing a control word. Once this has been determined and the proper lines found, SYMB will proceed with its function.

Sum Function Routine

Figure 4-7

Figure 4-8

Figure 4-9

Symb Function Routine (Part 2)

Figure 4-9

As each symbol is encountered it is run through a test to see if it already exists in the symbol table. If it is in the table the routine will move on to the next symbol. If not then this new symbol will be loaded into the table along with room for the two simulation table addresses to be assigned later. These addresses will be found once tables T1 and T2 are formed.

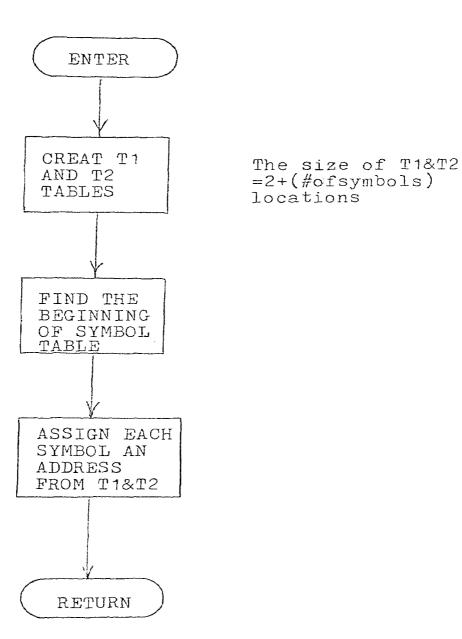

Once all the symbols have been found the next two tables can be formed. This is done by the SETUP routine, Figure 4-10. A count of the number of symbols used was kept by the last routine. The size of the two tables depends upon the number of symbols. After the beginning and end addresses of T1 and T2 are determined SETUP will go back and assign each symbol in the symbol table addresses to T1 and T2.

Now that each symbol has a place in both simulation tables and both tables have been formed, what is left is to make an update sequence. This is accomplished by the PACK routine. What this routine does is to search through the source program looking for logic gates. Each gate definition contains information related to the number of inputs. PACK then looks for the input symbols and the output symbol and gets their addresses from tables T1 and T2. It then assigns these addresses to the update sequence table. A two input gate has two locations in T1 and its output located in T2. For a four input type gate

## Setup Function Routine

Figure 4-10

Figure 4-11

Pack Function Routine (Part 2)

Figure 4-11

Figure 4-12

four of its locations are in T1 and its output is in T2. Figure 4-11 shows the flowchart for this routine.

The final sub-module of the compiler is the IO routine. It has the task of determining which variables are primary inputs and which are monitored outputs. Figure 4-12 shows this routine. This task is done by scanning through the source program looking for either INPUT or PRINT command words. When one of these is encountered each symbol which follows, along with its address of where in T1 it is located is stored in either table INP(input) or OUTP(output) depending on which command word was encountered. Once all the inputs and outputs have been stored away the compiling is complete. Control will now be passes back to the controller/editor where errors can be corrected or execution of the compiled program can take place.

## 4.6 The Compiler Program Listing

```

; FUNCTION

: COMP '

; CALLS

:SUM, PRNT, SYMB, SETUP, PACK, IO

; INPUTS

: NOTHING

; OUTPUTS

: NOTHING

: COMP IS THE COMPILER ROUTINE

; DESCRIPTION

: OF BLS. THE FUNCTION OF COMP

: IS TO DIRECT THE IMPLIMENT-

: ATION OF THE COMPILER. THERE

: ARE SIX STAGES IN THIS COMPILER

: AND COMP ACTS AS THE CONTROLLER

: IT CALLS UPON THE NECESSARY

: ROUTINES TO BREAKDOWN THE

:SOURCE PROGRAM.

COMP:

CALL.

SUM

GET THE GATE TYPE COUNT

PRNT

CALL

; PRINT NETWORK PLUS GATE COUNT

CALL

SYMB

; ASSIGN LOCATIONS TO SYMBOLS

CALL

SETUP

; SETUP SIMULATION TABLES

PACK

CALL

FPUT THE INFORMATION IN TABLES

CALL

IO

; SETUP PRIMARY INPUT & OUTPUT

JMF'

EAA

GO BACK TO EDITOR

÷

FUNCTION

: SUM

; CALLS

: FNDP + FNDCH + FNDS

; INPUTS

:START, WORK

; OUTFUTS

: WORK

SUM HAS THE TASK OF DETERM-

; DESCRIPTION

: INING HOW MANY OF THE POSSIBLE

; ELEVEN TYPES OF GATES ARE IN

:THE NETWORK, CERTAIN CHARACTERS

: ARE USED TO KEYOFF THE ROUTINE.

:FNDP- FINDS DECIMAL POINTS;

:FNDCH- FINDS AN ALPHABETIC

: CHARACTER.

```

```

SUM:

MVI

A, 11

; COUNT OF GATE TYPES

WORK

STA

LXI

H, NA2

GATE COUNT TABLE

BAO:

MVI

M, 0

; INILIZATION OF TABLE

Н

INX

DCR

A

JNZ

BAO

LXI

B, NAZ

; GATE TYPES ARE DETERMINED BY

; A STRING COMPARISON TO THE

\Gamma X I

D, BAS

BA1:

; SOURCE PROGRAM

LHLD

START

BA2:

CALL

FNDP

;LOOK FOR DECIMAL POINT

; THE CONTROL WORD

JNC

BA4

CALL

FNEICH

GET FIRST CHARACTER

PUSH

D

LDAX

n

CMF

M

; COMPARE TO TEST STRING

BAB

JNZ

; NOT FOUND CONTINUE SCAN

INX

Н

\mathbf{D}

; NEXT CHARACTER

INX

D

LDAX

CMP

M

; COMPARE NEXT CHARACTER

; IF NO MATCH TRY AGAIN

EAB

JNZ

;STILL GOOD FIND SLACH

CALL

FNDS

INX

\mathbf{D}

D

LDAX

; COMPARE # OF INPUTS

CMP

M

BAB

; NOT THE SAME KEEP LOOKING

JNZ

FNDF.

FIND END OF CONTROL WORD

CALL

FOP

D

В

; GATE COUNT

LDAX

INR

Α

; INCREMENT COUNT

В

; SAVE THE NEW COUNT

STAX

; LOOK FOR ANOTHER ONE

JMP

RA2

BA3:

FOF

\mathbf{D}

FNDP

; NO GOOD LOOK FOR NEXT ONE

CALL

PA2

JMF

; NEXT TYPE OF GATE

D

BA4:

INX