# **Copyright Warning & Restrictions**

The copyright law of the United States (Title 17, United States Code) governs the making of photocopies or other reproductions of copyrighted material.

Under certain conditions specified in the law, libraries and archives are authorized to furnish a photocopy or other reproduction. One of these specified conditions is that the photocopy or reproduction is not to be "used for any purpose other than private study, scholarship, or research." If a, user makes a request for, or later uses, a photocopy or reproduction for purposes in excess of "fair use" that user may be liable for copyright infringement,

This institution reserves the right to refuse to accept a copying order if, in its judgment, fulfillment of the order would involve violation of copyright law.

Please Note: The author retains the copyright while the New Jersey Institute of Technology reserves the right to distribute this thesis or dissertation

Printing note: If you do not wish to print this page, then select "Pages from: first page # to: last page #" on the print dialog screen

The Van Houten library has removed some of the personal information and all signatures from the approval page and biographical sketches of theses and dissertations in order to protect the identity of NJIT graduates and faculty.

# CORRELATION OF DRAIN BREAKDOWN WITH EXCESS NOISE AND OTHER SURFACE-RELATED PHENOMENA

### IN ENHANCEMENT MOSFETS

ΒY

JERRY J. RIJ

A THESIS

PRESENTED IN PARTIAL FULFILLMENT OF

### THE REQUIREMENTS FOR THE DEGREE

0F

MASTER OF SCIENCE IN ELECTRICAL ENGINEERING

### ΑT

NEWARK COLLEGE OF ENGINEERING

THIS THESIS IS TO BE USED ONLY WITH DUE REGARD TO THE RIGHTS OF THE AUTHOR. BIBLIOGRAPHICAL REFER-ENCES MAY BE NOTED, BUT PASSAGES MUST NOT BE COPIED WITHOUT PERMISSION OF THE COLLEGE AND WITHOUT CREDIT BEING GIVEN IN SUBSEQUENT WRITTEN OR PUBLISHED WORK.

> Newark, New Jersey 1973

### APPROVAL OF THESIS

## CORRELATION OF DRAIN BREAKDOWN WITH EXCESS NOISE AND OTHER SURFACE-RELATED PHENOMENA

IN ENHANCEMENT MOSFETS

ΒY

JERRY J. RIJ

FOR

DEPARTMENT OF ELECTRICAL ENGINEERING NEWARK COLLEGE OF ENGINEERING

ΒY

FACULTY COMMITTEE

APPROVED:

NEWARK, NEW JERSEY SEPTEMBER, 1973

### ABSTRACT

AN INVESTIGATION OF SEMICONDUCTOR SURFACE - RELATED PHENOMENA HAS BEEN UNDERTAKEN TO CORRELATE 1/F NOISE WITH DRAIN BREAKDOWN IN P-CHANNEL ENHANCEMENT MOSFET'S. | N -CREASES IN THE INTENSITY OF DRAIN CURRENT FLUCTUATIONS AT 10 Hz AND AT 1 KHz, PARTICULARLY AT THE HIGHER FREQUENCY, WAS OBSERVED FOLLOWING ACCELERATED LIFE-TESTING FOR THRESH-OLD VOLTAGE DRIFT. IT WAS CONCLUDED THAT MOBILE IONS NEAR THE OXIDE-SEMICONDUCTOR INTERFACE PRODUCE A SHARP INCREASE IN FAST SURFACE STATES AND THAT THESE STATES MAY BE REGARDED AS FAST TRAPPING CENTERS. IT WAS ALSO FOUND THAT THE 1/F NOISE INTENSITY CONSISTENTLY PEAKED AT THE THRESHOLD OF DRAIN BREAKDOWN AND THAT IT STEADILY DECREASED WITH FUR-THER INCREASES IN DRAIN CURRENT. OF ALL THE TRANSISTORS TESTED, THOSE WITH RELATIVELY LOW NOISE INTENSITY WERE FOUND TO EXHIBIT SHARPER BREAKDOWN CHARACTERISTICS AND HIGHER BREAKDOWN VOLTAGES WHILE THOSE TRANSISTORS WITH HIGH NOISE SHOWED SOFT BREAKDOWN CHARACTERISTICS. IT WAS THEREFORE CONCLUDED THAT LOW NOISE MOS TRANSISTORS ARE SUPERIOR TO THOSE WITH RELATIVELY HIGH NOISE AND THAT THE 1/F NOISE - DRAIN CURRENT CHARACTERISTICS MAY BE USED IN NONDESTRUCTIVE TESTING TO DETERMINE THE APPROXIMATE DRAIN BREAKDOWN VOLTAGE.

### ACKNOWLEDGEMENTS

THE AUTHOR WISHES TO EXPRESS HIS SINCERE APPRECIATION AND GRATITUDE TO THE FOLLOWING:

DR. RAJ P. MISRA WHOSE BACKGROUND IN THE FIELD OF RE-LIABILITY RESEARCH PROVIDED HELPFUL INSIGHT AND VALUABLE CRITISISM AS THE AUTHOR'S ADVISOR THROUGHOUT THIS ENDEAVOR,

DR. ROY CORNELY WHOSE EXPERIENCE AND WEALTH OF TECH-NICAL INFORMATION ADDED IMMEASUREABLY TO THE AUTHOR'S KNOW-LEDGE OF SEMICONDUCTOR PHYSICS,

DR. ROBERT MCMILLAN WHOSE EXPERIENCE AND ASSISTANCE WAS APPRECIATED WHILE TAKING THE PICTURES CONTAINED HEREIN,

AND FINALLY,

NEWARK COLLEGE OF ENGINEERING FOR PROVIDING FINANCIAL ASSISTANCE IN THE FORM OF A FELLOWSHIP DURING THE 1972-73 ACADEMIC YEAR.

IV

### TABLE OF CONTENTS

| CHAPTER |                                                                   | PAGE |

|---------|-------------------------------------------------------------------|------|

| 1       | INTRODUCTION AND THEORY OF MOSFET<br>OPERATION                    | 1    |

|         | 1.1 INTRODUCTION TO BASIC MOS DEVICES.                            | 1    |

|         | 1.2 THEORY OF MOSFET OPERATION                                    | 2    |

|         | 1.3 Previous Investigations of the<br>Saturation Phenomenon       | 11   |

|         | REFERENCES                                                        | 15   |

| 2       | FABRICATION AND PROPERTIES OF THE SI-<br>SIO2 INTERFACE           | 16   |

|         | 2.1 INTRODUCTION                                                  | 16   |

|         | 2.2 BACKGROUND INFORMATION                                        | 16   |

|         | 2.3 Previous Experimental Investiga-<br>tions                     | 25   |

|         | 2.4 INVESTIGATION OF THRESHOLD VOLTAGE<br>Drift                   | 26   |

|         | REFERENCES                                                        | 30   |

| 3       | THE SURFACE-STATE RELATED NOISE PHENOM-<br>ENA IN MOS TRANSISTORS | 32   |

|         | 3.1 INTRODUCTION                                                  | 32   |

|         | 3.2 BASIC NOISE THEORY                                            | 33   |

|         | 3.3 Previous Studies of the Excess<br>Noise Spectral Intensity    | 36   |

|         | 3.4 ELECTRICAL NOISE AND COMPONENT<br>Reliability                 | 39   |

|         | 3.5 Noise Measurements Undertaken                                 | 41   |

|         | 3.6 Experimental Results and Discussion                           | 45   |

|         | REFERENCES                                                        | 54   |

### CHAPTER

### PAGE

| 4            | CORRELATION OF 1/F NOISE WITH DRAIN<br>BREAKDOWN                                                                                                          | 56  |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|              | 4.1 INTRODUCTION                                                                                                                                          | 56  |

|              | 4.2 Theory of Electrical Breakdown at P-N Junctions                                                                                                       | 56  |

|              | 4.3 Previous Investigation of Drain<br>Breakdown                                                                                                          | 57  |

|              | 4.4 Investigation of Drain Breakdown<br>Under Conditions of Strong Channel<br>Inversion in Enhancement MOS Tran-<br>sistors                               | 61  |

|              | 4.5 Investigation of Gate-Controlled<br>Drain-Diode Breakdown Under Cutoff<br>Conditions                                                                  | 71  |

|              | REFERENCES                                                                                                                                                | 76  |

| 5            | CONCLUSION AND DISCUSSION OF RESULTS                                                                                                                      | 77  |

| APPENDIX A   | THE INFLUENCE OF DEVICE PARAMETERS ON<br>THE MOS SATURATION DRAIN CONDUCTANCE                                                                             | 81  |

|              | REFERENCES                                                                                                                                                | 86  |

| APPENDIX B   | A DERIVATION OF THE EQUATION OF THE<br>SPECTRAL INTENSITY OF THE SHORT-CIRCUIT<br>DRAIN CURRENT FLUCTUATIONS IN METAL-<br>OXIDE-SEMICONDUCTOR TRANSISTORS | 87  |

|              | REFERENCES                                                                                                                                                | 95  |

| APPENDIX C   | THRESHOLD VOLTAGE DRIFT IN P-CHANNEL<br>ENHANCEMENT MOSFETS                                                                                               | 97  |

| APPENDIX D   | EXCESS NOISE-DRAIN CURRENT MEASUREMENTS<br>AT CONSTANT GATE VOLTAGE                                                                                       | 100 |

| APPENDIX E   | DRAIN LEAKAGE CURRENT MEASUREMENTS                                                                                                                        | 107 |

| APPENDIX F   | EQUIPMENT USED IN THIS RESEARCH                                                                                                                           | 112 |

| BIBLIOGRAPHY | •••••••••••••••••                                                                                                                                         | 113 |

### LIST OF FIGURES

| FIGURE      | TITLE                                                                                                                                                                  | PAGE |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 1-1         | GEOMETRICAL CONSTRUCTION OF A P-CHANNEL<br>ENHANCEMENT MOSFET BLASED FOR CHANNEL<br>CONDUCTION                                                                         | 3    |

| 1-2         | ENERGY BAND-BENDING NEAR THE SEMICON-<br>DUCTOR SURFACE UNDER THREE CONDITIONS<br>OF GATE BIAS FOR A P-CHANNEL ENHANCE-<br>MENT MOSFET                                 | 4    |

| 1-3         | EFFECTS OF INCREASING VDS ON THE INVER-<br>SION REGION OF A P-CHANNEL ENHANCEMENT<br>MOSFET                                                                            | 7    |

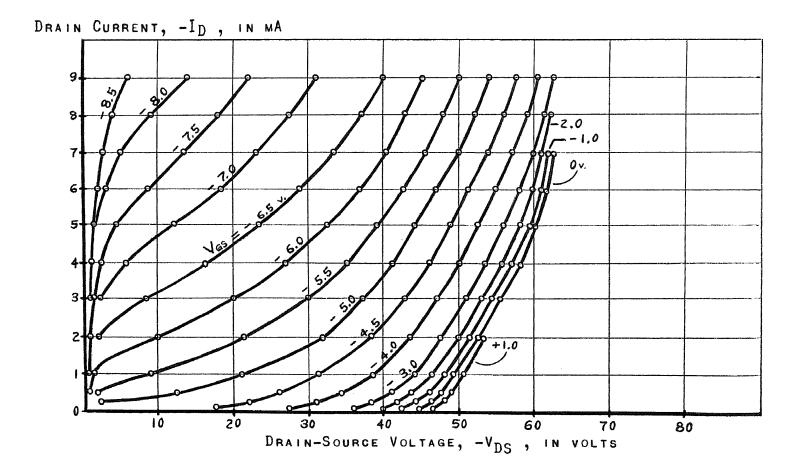

| 1 – 4       | Photograph showing the current-voltage<br>characteristics of a typical p-channel<br>enhancement MOSFET                                                                 | 10   |

| 1-5         | Scale drawing of a p-channel enhancement<br>MOSFET                                                                                                                     | 14   |

| 2-1         | Model of the SI-SIO2 interface in a p-<br>channel enhancement MOSFET showing the<br>results of ionic drift in the oxide un-<br>der the influence of an electric field. | 23   |

| 3-1         | Connection block diagram of the Quan-<br>Tech Model 327 Diode Noise Analyzer<br>modified for measuring noise voltages<br>of p-channel enhancement MOS transis-<br>tors | 42   |

| 3-2         | Comparison of mean excess noise voltage<br>for three types of p-channel enhance-<br>ment MOSFET's                                                                      | 46   |

| 3-3         | Comparison of noise voltage at 10Hz with<br>saturation drain conductance for selec-<br>ted units of type DD07P MOSFET's                                                | 48   |

| 3-4         | Comparison of noise voltage at 10Hz with<br>saturation drain conductance for selec-<br>ted units of type DD08P MOSFET's                                                | 49   |

| 3 <b>-5</b> | Comparison of noise voltage at 10Hz with<br>saturation drain conductance for selec-<br>ted units of type DD08K MOSFET's                                                | 50   |

## FIGURE TITLE

| Ρ | A | G | Е |

|---|---|---|---|

| - | - | - | - |

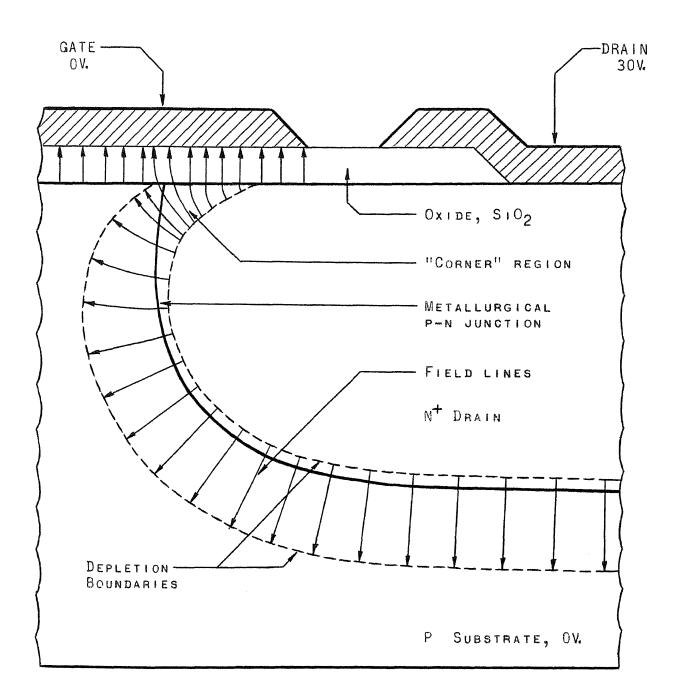

| 4-1          | Drain-portion of an n-channel enhance-<br>ment MOSFET showing the mechanism of<br>Drain-diode breakdown in the "corner"<br>region                                                  | 60  |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

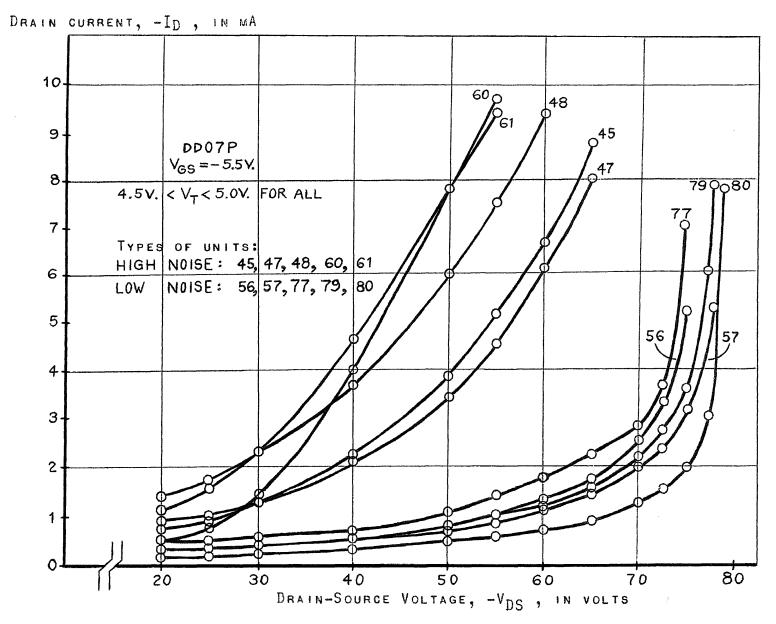

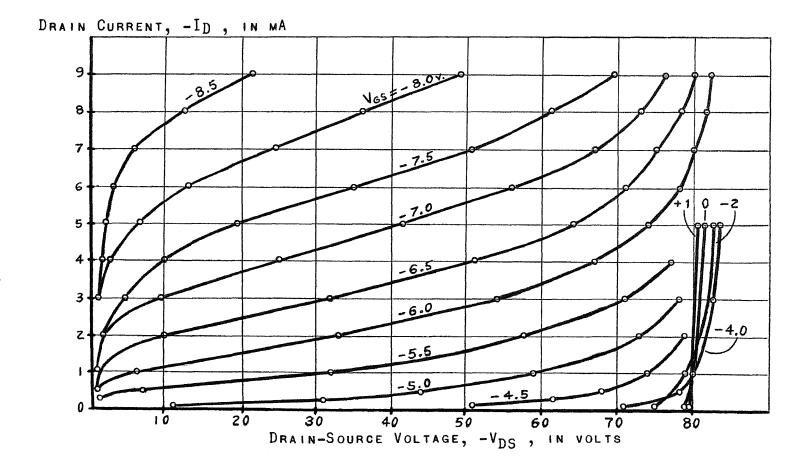

| 4 <b>-2</b>  | Drain breakdown characteristics of five<br>high- and five low-noise type DD07P<br>MOSFET's                                                                                         | 63  |

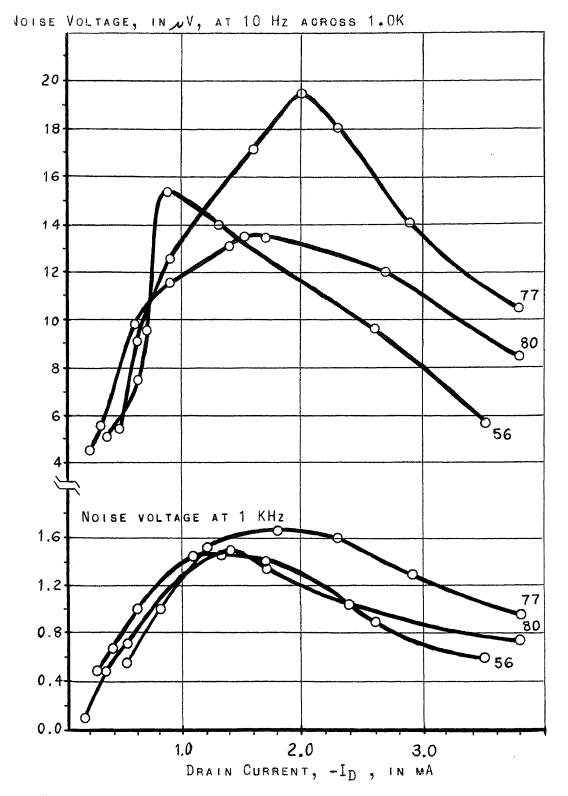

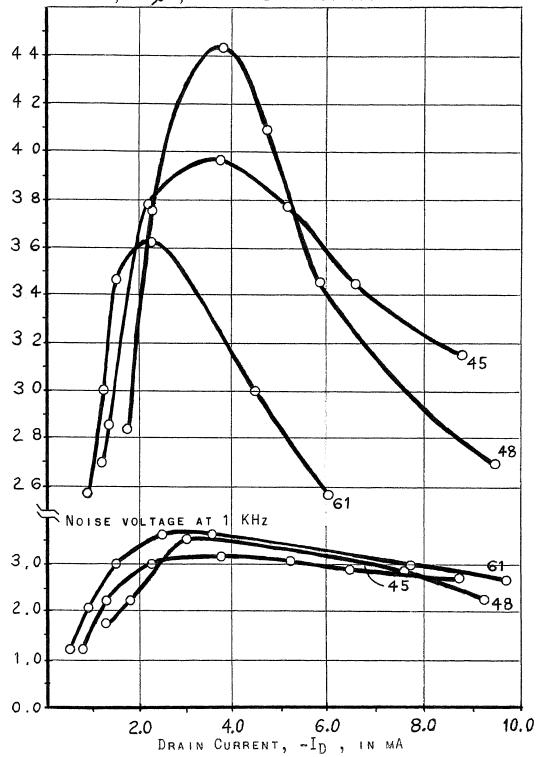

| 4-3          | Noise voltage-drain current character-<br>istics for three low noise type DD07P<br>MOSFET's                                                                                        | 66  |

| 4 <b>- 4</b> | Noise voltage-drain current character-<br>istics for three high noise type DD07P<br>MOSFET's                                                                                       | 67  |

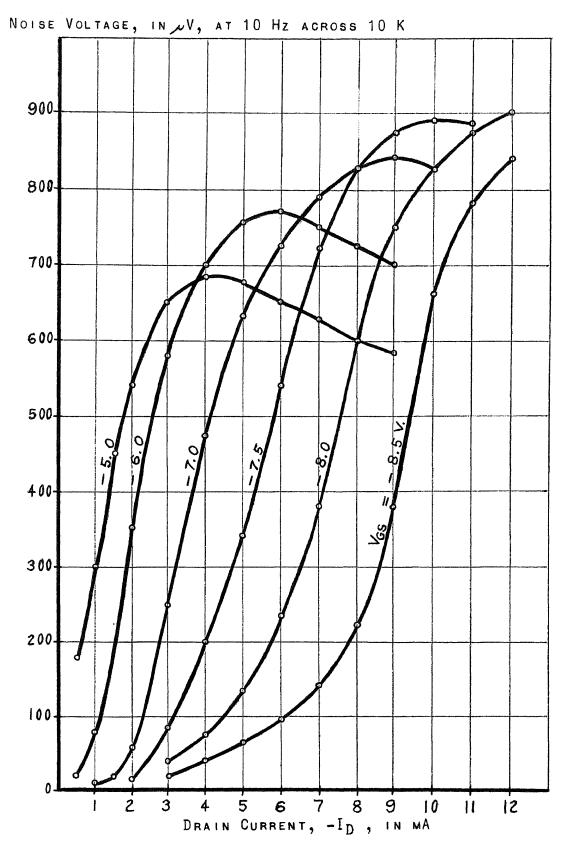

| 4-5          | Noise voltage-drain current character-<br>istics at several gate voltages for a<br>single high noise type DD07P MOSFET                                                             | 69  |

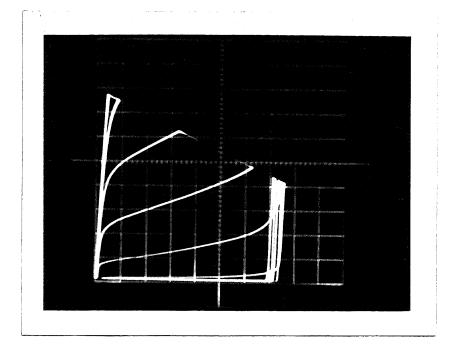

| 4-6          | Photograph showing the current-voltage<br>drain breakdown characteristics of a<br>relatively low noise p-channel enhance-<br>ment MOSFET                                           | 72  |

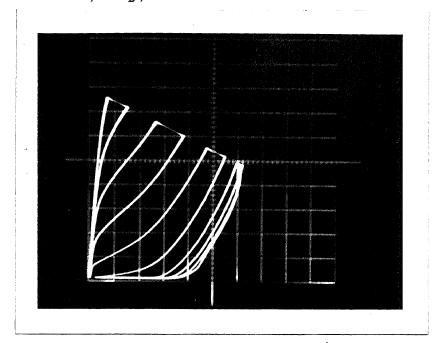

| 4-7          | Photograph showing the current-voltage<br>drain breakdown characteristics of a<br>relatively high noise p-channel enhance-<br>ment MOSFET                                          | 73  |

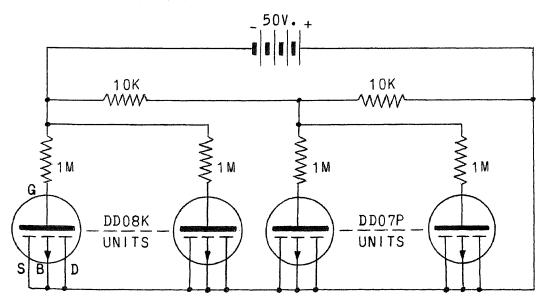

| C-1          | Connection diagram for biasing p-channel<br>MOS transistors for negative threshold<br>voltage drift                                                                                | 97  |

| D-1          | Current-voltage characteristics for a relatively low noise DD07P MOSFET                                                                                                            | 105 |

| D-2          | Current-voltage characteristics for a relatively high noise DD07P MOSFET                                                                                                           | 106 |

| E-1          | SIMPLIFIED SCHEMATIC OF A GENERAL RADIO<br>Type 1230-A DC Amplifier and Electrom-<br>eter and external DC supply used for<br>measuring IDSS of a p-channel enhance-<br>ment MOSFET | 108 |

| F-1          | Photograph showing the principal instru-<br>ments used in this research                                                                                                            | 112 |

### LIST OF SYMBOLS

| Α              | AREA OF GATE METALIZATION IN CM <sup>2</sup>                                                                                                         |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| Å              | Angstrom unit, 10 <sup>-10</sup> meters, 10 <sup>-8</sup> cm                                                                                         |

| В              | BANDWIDTH IN CYCLES PER SECOND, HERTZ, HZ                                                                                                            |

| c              | CAPTURE RATE PROBABILITY                                                                                                                             |

| ¢ <sub>s</sub> | CAPTURE RATE PROBABILITY AT THE SI-SIO <sub>2</sub> INTERFACE                                                                                        |

| С <sub>в</sub> | Impurity concentration in the substrate per cm $^3$                                                                                                  |

| Co             | Capacitance of the oxide layer in Farads/cm <sup>2</sup>                                                                                             |

| Cs             | Capacitance of the semiconductor space-charge<br>region in Farads/cm <sup>2</sup>                                                                    |

| E              | Surface-state energy in electron volts, eV                                                                                                           |

| Е <sub>в</sub> | BARRIER POTENTIAL TO BE EXCEEDED IN THE TUNNELING MECHANISM OF HOLES                                                                                 |

| Ec             | CONDUCTION-BAND ENERGY LEVEL                                                                                                                         |

| EF             | FERMI ENERGY LEVEL                                                                                                                                   |

| Ε <sub>ν</sub> | VALENCE-BAND ENERGY LEVEL                                                                                                                            |

| E,             | TRANSVERSE ELECTRIC FIELD IN THE CHANNEL DEPLETION<br>REGION BETWEEN THE EXPOP (EXTRAPOLATED PINCH-OFF<br>POINT) AND THE DRAIN-TO-SUBSTRATE JUNCTION |

| F, $f$         | FREQUENCY IN CYCLES PER SECOND                                                                                                                       |

| f <sub>T</sub> | QUASI-FERMI FUNCTION OF SURFACE STATES                                                                                                               |

| $f_{TP}$       | $1 - t_r$                                                                                                                                            |

| G              | The rate that surface states of energy E located at a distance x into the oxide layer gain holes                                                     |

| Gм             | Transconductance in ohms <sup>-1</sup> , mhos                                                                                                        |

| 9dsat          | Small-signal saturation drain conductance in ohms <sup>-1</sup>                                                                                      |

| ħ              | Planck's constant, 4.136×10 <sup>-15</sup> eV·second                                                                                                 |

|                |                                                                                                                                                      |

- *i*<sup>2</sup> *i*<sup>2</sup> MEAN SQUARED NOISE CURRENT WITH DRAIN SHORTED IN MA<sup>2</sup>/cycle

- DRAIN CURRENT

- DSAT SATURATION DRAIN CURRENT

- $I_{DSAT}$  \* SATURATION DRAIN CURRENT WHEN  $V_D = V_{DSAT}$

- DRAIN LEAKAGE CURRENT WHEN THE GATE IS RETURNED TO THE SOURCE, THE SOURCE AND SUBSTRATE ARE COM-MON, AND THE DRAIN-TO-SOURCE VOLTAGE IS 10 VOLTS

- J CURRENT DENSITY

- k BOLTZMANN'S CONSTANT, 8.617×10<sup>-5</sup>eV·°K<sup>-1</sup>

- K MATERIAL CONSTANT

- Ko Relative permittivity of SiO2, 3.54×10<sup>-13</sup>Farad/cm

- K<sub>S</sub> Relative permittivity of silicon

- kT ENERGY LEVEL, 0.0258 eV at  $T = 300^{\circ} \text{ K}$

- Length of Diffusion of surface states from the SI-SIO2 interface

- L EFFECTIVE CHANNEL LENGTH (IN THE DIRECTION OF CURRENT FLOW)

- $\Delta L$  . Length by which the conducting channel is shortened when  $V_{DS}$  exceeds  $V_{DS\,\Delta\,T}$

- M<sup>\*</sup> EFFECTIVE MASS OF A HOLE, 9.108×10<sup>-31</sup>Kg

- NA ACCEPTOR DOPING DENSITY PER CM<sup>3</sup>

- N<sub>D</sub> DONOR DOPING DENSITY PER CM<sup>3</sup>

- $N_{T}(E)$  Surface-state density of free holes and electrons in cm<sup>-3</sup>·eV<sup>-1</sup>

- h<sub>si</sub> Free electron concentration at the surface when the Fermi level is at the surface-state level

- hso STEADY-STATE VALUE OF hsi

- $h_{\tau}(\epsilon)$  Empty surface states at energy E located at a distance x from the SI-SIO<sub>2</sub> interface

- P<sup>+</sup> HEAVY P-TYPE DIFFUSION (10<sup>18</sup> to 10<sup>20</sup> cm<sup>-3</sup>)

- $P_s$  Hole density in the inverted channel in cm<sup>-3</sup>.eV<sup>-1</sup>

- $P_{s_i}$  Free hole concentration at the surface when the Fermi level is at the surface-state level

- PSO STEADY-STATE VALUE OF PSI

Q<sub>SS</sub> Surface-state charge in coulombs

9 MAGNITUDE OF ELECTRONIC CHARGE, 1.602×10<sup>-19</sup>coul

R RESISTANCE IN OHMS

- R RATE THAT SURFACE STATES OF ENERGY E LOCATED AT A DISTANCE X INTO THE OXIDE LAYER LOSE HOLES

- $S_{i(\omega)}$  Short-circuit drain current noise spectral intensity (drain current fluctuations in MOSFET's)

- $S_{p\tau(\omega)}$  Spectral intensity of the trapped hole density fluctuation

- T TEMPERATURE IN DEGREES KELVIN, °K

- V VOLUME

- VD DRAIN VOLTAGE

- VDS DRAIN-TO-SOURCE VOLTAGE

- $V_{DSAT}$  Drain voltage which causes channel pinch-off

- V<sub>FB</sub> FLAT-BAND VOLTAGE NECESSARY TO COUNTER BALANCE THE WORK FUNCTION DIFFERENCE BETWEEN THE METAL-OXIDE BARRIER ENERGY AND THE SILICON-OXIDE BAR-RIER IN AN MOS TRANSISTOR

- VG GATE VOLTAGE

- VG' EFFECTIVE GATE VOLTAGE

- V<sub>RS</sub> GATE-TO-SOURCE VOLTAGE

- VGSUB GATE-TO-SUBSTRATE VOLTAGE

- VT THRESHOLD VOLTAGE

- x DISTANCE FROM THE SI-SIO<sub>2</sub> INTERFACE

- X<sub>O</sub> THICKNESS OF THE OXIDE LAYER

- Z PARABOLIC RATE CONSTANT FOR GROWTH OF SIO2

- $\alpha$  CAPTURE RATE TIME CONSTANT

- β GAIN TERM

- $\mathfrak{F}, \mathfrak{I}, \mathfrak{O}, \mathfrak{A}$  Exponents of  $\mathbb{R}, \mathfrak{F}, \mathfrak{I}, \mathfrak{v}$  in Bell's general equation for frequency-dependent noise

- δ INFINITESIMALLY SMALL INCREMENT

- €. PERMITTIVITY OF FREE SPACE, 8.86×10<sup>-14</sup>Farad/cm

- 5,5 FIELD FRINGING FACTORS EXPERIMENTALLY FOUND TO BE 0.2 AND 0.6, RESPECTIVELY

- MOBILITY OF ELECTRONS IN CM<sup>2</sup>/VOLT.SECOND

- MOBILITY OF HOLES IN CM<sup>2</sup>/VOLT.SECOND

- *π* P1, 3.1415926

- P RESISTIVITY

- S SHAPE FACTOR, EG. CROSS-SECTION/UNIT LENGTH

- TIME CONSTANT FOR SURFACE-STATE CHARGE DENSITY FLUCTUATION

- $r_{\rm s}$  Time constant for surface states located right at the SI-SIO<sub>2</sub> interface

- ELECTROSTATIC POTENTIAL WITH REFERENCE TO THE BULK SEMICONDUCTOR MATERIAL

- $\phi_F$  ELECTROSTATIC POTENTIAL AT THE FERMI LEVEL; THE AMOUNT BY WHICH THE FERMI LEVEL IS DISPLACED FROM THE INTRINSIC LEVEL OR THE CENTER OF THE GAP (AS MEASURED IN THE BULK)

- \$\$ ELECTROSTATIC POTENTIAL AT THE SURFACE; THE AMOUNT BY WHICH THE INTRINSIC FERMI LEVEL, AT THE SURFACE, HAS BEEN CHANGED WITH RESPECT TO THE FERMI LEVEL

- ω ANGULAR FREQUENCY IN RADIANS PER SECOND

#### CHAPTER 1

### INTRODUCTION AND THEORY OF MOSFET OPERATION

#### 1.1 INTRODUCTION TO BASIC MOS DEVICES

THE BASIC METAL-OXIDE-SEMICONDUCTOR FIELD-EFFECT TRANSISTOR (MOSFET) IS COMPOSED OF TWO HEAVILY-DOPED REGIONS, THE <u>SOURCE</u> AND <u>DRAIN</u>, DIFFUSED INTO A SEMICON-DUCTOR <u>SUBSTRATE</u> AND SEPARATED BY A <u>CHANNEL</u>. AN <u>INSULA-</u> <u>TED METAL GATE</u> ABOVE THE CHANNEL MODULATES <u>MAJORITY CAR-</u> <u>RIER</u> CONDUCTION FROM THE SOURCE TO THE DRAIN BY FIELD EFFECTS.

Two types of devices are commercially available: the p-channel MOSFET (in which holes are the majority carriers) and the n-channel MOSFET (in which the majority carriers are electrons). In addition, there are two common modes of operation: the <u>enhangement-mode</u> (in which the device is normally off and channel conduction is <u>enhanced</u> by the appropriate gate voltage) and the <u>depletion-mode</u> (in which the channel normally conducts and a gate voltage <u>depletes</u> it of majority carriers). Until recently, it was custom ary to produce primarily either p-channel enhancement- or n-channel depletion-mode MOS transistors. However, complimentary MOS integrated circuits consisting of pairs of both p- and n-channel transistors on a single chip are replacing a large portion of the bipolar devices in use today.

### 1.2 THEORY OF MOSFET OPERATION

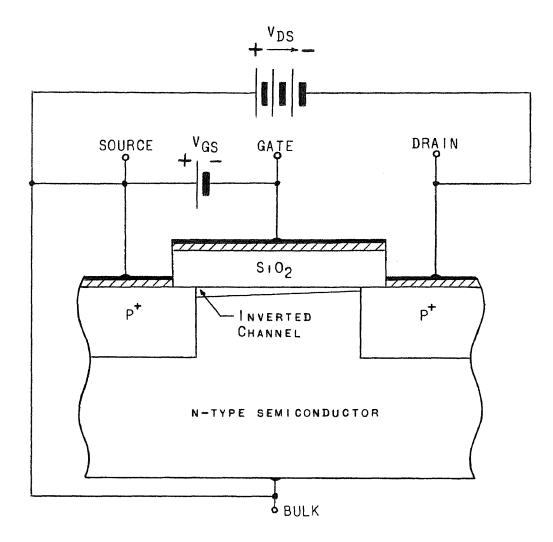

MODULATION OF CHANNEL CONDUCTION. FIGURE 1-1 SHOWS THE GEOMETRIC CONSTRUCTION OF A P-CHANNEL ENHANCEMENT -MODE MOS TRANSISTOR PROPERTLY BIASED FOR CHANNEL CONDUC-TION. SUCH DEVICES REQUIRE A SUFFICIENTLY NEGATIVE GATE VOLTAGE BEFORE THE CHANNEL BECOMES <u>INVERTED</u>. THIS THEN FORMS A P TYPE CONDUCTING PATH BETWEEN THE SOURCE AND THE DRAIN, THE CONDUCTIVITY OF WHICH IS <u>ENHANCED</u> WITH INCREAS-INGLY NEGATIVE GATE BIAS. N-CHANNEL ENHANCEMENT MOSFET'S HAVE N<sup>+</sup> SOURCE AND DRAIN REGIONS AND REQUIRE A DRAIN AND GATE BIAS OF OPPOSITE POLARITY TO THOSE OF P-CHANNEL MOS TRANSISTORS IN ORDER TO OPERATE. DEPLETION-MODE DEVICES HAVE A BUILT-IN CONDUCTING CHANNEL BENEATH THE OXIDE OF THE SAME TYPE OF MATERIAL USED FOR THEIR RESPECTIVE DRAIN AND SOURCE REGIONS.

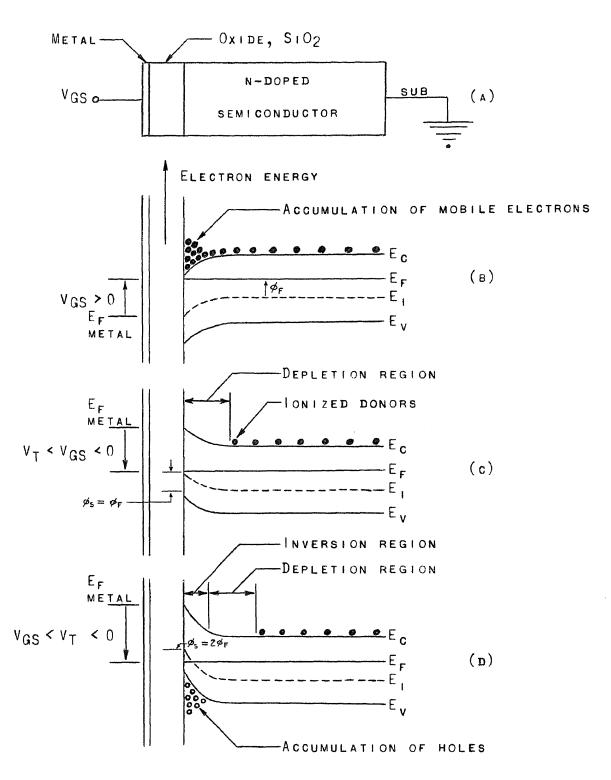

FIGURE 1-2A IS A LATERAL VIEW TAKEN IN THE CHANNEL BETWEEN THE SOURCE AND DRAIN OF A P-CHANNEL ENHANCEMENT MOSFET. V<sub>GS</sub> is the gate bias applied between the gate and source terminals. With the source and substrate at an electrical ground, there are three gate bias conditions of interest.

FIGURE 1-2B ILLUSTRATES THE SEMICONDUCTOR ENERGY BANDS and characteristic "band bending" when the applied  $V_{GS}$  is greater than zero. An abrupt difference is assumed between the oxide (SiO<sub>2</sub>) and the semiconductor substrate. The energy

FIGURE 1-1. GEOMETRICAL CONSTRUCTION OF A P-CHANNEL EN-HANCEMENT MOSFET BLASED FOR CHANNEL CONDUCTION. SUCH DEVICES HAVE ISOLATED P<sup>+</sup> SOURCE AND DRAIN DIFFUSIONS WITHIN AN N-TYPE SEMICONDUCTOR SUBSTRATE. AN OXIDE LAYER, USUALLY SIO<sub>2</sub>, IN-SULATES THE GATE FROM THE SUBSTRATE AND PASSIVATES THE SUR-FACE OF THE DRAIN AND SOURCE P-N JUNCTIONS. TERMINALS ARE PROVIDED FOR THE DRAIN, GATE, AND SOURCE AND, IN SOME CASES, A SEPARATE TERMINAL FROM THE SUBSTRATE BULK MAY ALSO BE EX-TERNALLY AVAILABLE. OTHERWISE, THE SUBSTRATE IS CONNECTED INTERNALLY TO THE SOURCE AND THE DEVICE IS THEN USUALLY IN-TENDED TO BE OPERATED WITH ONLY ONE OF THE P<sup>+</sup> REGIONS AS THE DRAIN.

FIGURE 1-2. ENERGY BAND-BENDING NEAR THE SEMICONDUCTOR SURFACE UNDER THREE CONDITIONS OF GATE BIAS FOR A P-CHANNEL ENHANCEMENT MOSFET! (B) POSITIVE  $V_{GS}$  RESULTS IN AN ELECTRON ACCUMULATION BENEATH THE OXIDE; (C) SMALL  $|-V_{GS}|$  RESULTS IN DEPLETION REGION; AND (D) LARGER  $|-V_{GS}|$  CAUSES SURFACE INVERSION AND AN ACCUMULATION OF HOLES.

#### BANDS ARE IDENTIFIED AS FOLLOWS:

- E ELECTRON ENERGY AT THE EDGE OF THE CONDUCTION BAND

- E ELECTRON ENERGY AT THE FERMI LEVEL, DEFINED AS THE ENERGY LEVEL AT WHICH "THE PROBABILITY OF OCCUPATION OF AN ENERGY STATE BY AN ELECTRON IS EXACTLY ONE-HALF."<sup>2</sup>

- E, ELECTRON ENERGY AT THE INTRINSIC FERMI LEVEL, THE FERMI LEVEL IN AN INTRINSIC SEMICONDUCTOR

- Ev Electron energy at the edge of the valence band.

A POSITIVE GATE BIAS LOWERS THE ENERGY LEVEL ASSOCI-ATED WITH THE SURFACE STATES DOWN NEAR THE FERMI LEVEL IN THE SEMICONDUCTOR MATERIAL. THE PROBABILITY OF THE STATES BEING OCCUPIED BY AN ELECTRON IS GREATLY INCREASED AND AN ELECTRON ACCUMULATION RESULTS BENEATH THE OXIDE.

FIGURE 1-2c shows the effect of applying a small negative gate bias. As the states are elevated, their probability of occupation by electrons is decreased. The channel near the oxide becomes depleted of electrons. This results in a <u>depletion region</u> which consists of mostly bound ions of impurity atoms.

WHEN THE GATE BIAS IS SUFFICIENTLY NEGATIVE, THE PRO-BABILITY OF OCCUPATION APPROCHES ZERO. ENOUGH ELECTRONS ARE THEN DISPLACED FROM THE SEMICONDUCTOR SURFACE (HEREAFTER REFERRED TO SIMPLY AS THE <u>SURFACE</u>) THAT THEY BECOME THE MIN-ORITY CARRIERS, WHILE HOLES BECOME DOMINANT. FIGURE 1-2D SHOWS A NET ACCUMULATION OF HOLES IN THE SUBSTRATE DIRECTLY BENEATH THE OXIDE. WHEREAS THE CHANNEL WAS HITHERTO COM-POSED OF N-DOPED SILICON, THE SURFACE IS NOW WITHIN AN <u>INVERSION REGION</u>, THEREBY ALLOWING A HOLE CURRENT TO FLOW FROM THE SOURCE TO THE DRAIN WHEN THE DRAIN IS BIASED AT A POTENTIAL NEGATIVE WITH RESPECT TO THE SOURCE.

The negative gate voltage which permits a current of ten microamperes to flow with an applied  $-V_{DS}$  equal to  $-V_{GS}$ is defined to be the <u>threshold voltage</u>,  $V_T$ . It is so-named because it is at this potential that the surface is at the threshold of inversion.

It is evident that the depth, and so the conductance, of the conducting channel may be easily modulated by variations in the applied gate voltage. The MOS transistor acquires its property of amplification from the fact that a relatively small variation in  $V_{\mbox{GS}}$  induces a large variation in drain current.

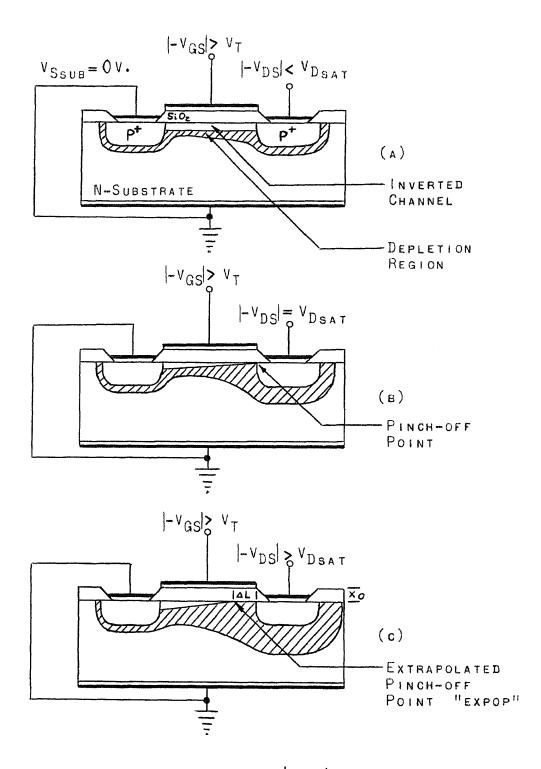

<u>Operation beyond channel pinch-off</u>. Figure 1-3a shows a cross-section of a p-channel enhancement-mode transistor with gate voltage large enough to establish a conducting channel between the source and drain. In the common-source configuration it is customary to ground the source and substrate bulk and apply a negative voltage to the drain. A small  $|-V_{DS}|$  results in the bias condition formerly illustrated in figures 1-1 and 1-2D above.

Figure 1-3. Effects of increasing  $|-V_{\rm DS}|$  on the inversion region of a p-channel enhancement MOSFET. (a) Condition with small  $|-V_{\rm DS}|$ ; (b) Pinch-off condition; and (c) Condition beyond channel pinch-off.

Since both the drain and source regions are of  $P^+$ type silicon (N<sub>A</sub> between  $10^{18}$  and  $10^{20}$  cm<sup>-3</sup>) in an n-doped semiconductor substrate (N<sub>D</sub> $\simeq 10^{15}$  cm<sup>-3</sup>), there is a natural <u>Recombination</u> process as electrons fill holes near the p-n junctions. With the drain and source heavily doped, recombination extends much further into the substrate than into either the source or the drain. This results in a <u>space-charge depletion region</u> around the source and drain junctions. Furthermore, since the substrate is electrically connected to the source, any applied  $-V_{DS}$  reverse biases the drain-to-substrate p-n junction, thereby further increasing the width of that particular depletion region.<sup>3</sup>

IF  $|-V_{DS}|$  is small compared to  $|-V_{GS}|$ , there is a linear drop in potential along the channel as hole current proceeds from the source to the drain. In this condition, the drain current  $-I_D$  (negative to indicate that the majority carriers are holes) is linearly proportional to  $|-V_{DS}|$  and the transistor is said to be operating in the <u>linear portion</u> of its I-V (current-voltage) characteristics.

It is evident that as  $|-V_{DS}|$  is increased, the difference in potential between the gate and drain terminals is lessened. Since the inversion region is dependent upon the electric field across the oxide, which is a function of the potential difference across each differential element of the oxide along the channel, the width of the inversion region is

DIRECTLY PROPORTIONAL TO THE ELECTRIC FIELD INTENSITY IN THAT PORTION OF THE OXIDE DIRECTLY ABOVE IT. CONSEQUENTLY, AS  $|-V_{DS}|$  increases, the field in the oxide at the drain-end of the channel decreases. Eventually, if  $|-V_{DS}|$  is made high enough, the field intensity is unable to support channel inversion near the drain-to-substrate junction.<sup>4</sup> Figure 1-3B illustrates this effect at the onset of channel <u>pinch-off</u>, a condition marked by essentially zero channel depth at the drain-end.<sup>\*</sup>

FIGURE 1-3c shows the effect of further increasing  $|-V_{DS}|$ . The length of the inverted channel decreases by an amount  $\Delta L$ and the <u>expop</u> (extrapolated pinch-off point at the tip of the inversion region) recedes toward the source. If the resistivity of the inverted region is averaged over its entire length, any shortening yields a decrease in channel resistance and a corresponding increase in drain current.

IF IT IS ASSUMED THAT A DIFFERENTIAL INCREASE IN DRAIN VOLTAGE BEYOND THAT REQUIRED FOR SATURATION IS ACCOMPANIED BY A DIFFERENTIAL INCREASE IN DRAIN CURRENT DUE ENTIRELY TO A DIFFERENTIAL REDUCTION IN CHANNEL LENGTH, THEN THE INSTAN-

<sup>\*</sup>Actually, the channel depth must be some finite dimension in order for drain current to flow. "Zero channel depth" is an approximation used for the convience of defining the channel pinch-off condition. Refer to sources 1969-2 and 1965-6 in the BIBLIOGRAPHY for a more detailed explanation of the saturation phenomena.

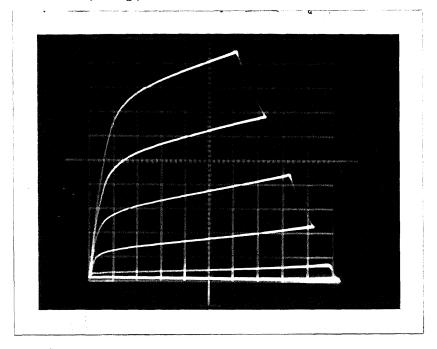

DRAIN CURRENT, -ID, 2MA/DIVISION

DRAIN VOLTAGE, -VDS, 5 VOLTS/DIVISION

Gate Voltage in one volt increments starting from  $V_{\mbox{GS}}=-6$  volts

FIGURE 1-4. PHOTOGRAPH SHOWING THE CURRENT-VOLTAGE CHARACTERISTICS OF A TYPICAL P - CHANNEL ENHANCEMENT MOSFET. The curves were taken from a Tetronix Type 527 Transistor Curve Tracer with a slight modification which allowed for Variations in applied gate voltage. TANEOUS SLOPE OF THE I-V CHARACTERISTICS IN THE SATURATION REGION YIELDS THE SMALL-SIGNAL SATURATION DRAIN CONDUCTANCE. This quantity may be expressed by the following:<sup>5</sup>

$$9_{dsat} = \frac{d | Dsat}{dV_D} = \frac{d | Dsat}{dL} \cdot \frac{dL}{dV_D}$$

1-1

FIGURE 1-4 SHOWS THE 1-V CHARACTERISTICS OF A TYPICAL P-CHANNEL ENHANCEMENT MOSFET. THE LINEAR AND SATURATION REGIONS ARE LABELED. IT IS EVIDENT THAT CHANNEL SHORTEN-ING YIELDS A FINITE OUTPUT RESISTANCE FOR MOS TRANSISTORS.

### 1.3 PREVIOUS INVESTIGATIONS OF THE SATURATION PHENOMENON

FROHMAN-BENTCHKOWSKY AND GROVE<sup>6</sup> AND OTHERS<sup>7,8</sup> Have studied MOSFET saturation conductance in terms of device parameters. Appendix A reviews the analytical analysis of the effects of oxide thickness, electric field intensity and associated fringing effects, and the semiconductor impurity concentration on drain conductance. In general, the saturation drain conductance can be expected to increase with both <u>increased oxide thickness</u> (see equation A-12) and <u>decreased impurity concentration</u> (see equation A-9) in the substrate.<sup>9</sup>

Devices which exhibit abnormally high drain conductance in the saturation region can therefore also be expected to have a thicker oxide layer, a lower substrate impurity concentration, or both. This investigation suggests that the saturation drain conductance is also a function of the surface-

STATE DENSITY AT THE OXIDE-SEMICONDUCTOR INTERFACE.

Reddi and Sah<sup>10</sup> have shown that the drain-to-source voltage required for pinch-off decreases with both increasing oxide thickness and higher bulk doping. Since small increases in the number of impurities used to dope the substrate yield great increases in the number of free carriers according to the familiar equation, <sup>11</sup>

$$h p = h_i^2 = K^2 T^3 E x P (-E_c/kT)$$

1-2

where  $E_{g} = E_{c} - E_{v} = Forbidden gap in eV$

- k = BOLTZMANN'S CONSTANT

- $K = MATERIAL CONSTANT, 3.87 \times 10^{22} \text{ for silicon}$ and 1.76×10<sup>22</sup> for germanium at 25°C

- $h = \text{Concentration of electrons per cm}^3$

- a = Concentration of holes per cm<sup>3</sup>

- $T = TEMPERATURE IN \circ K$ ,

IT IS REASONABLE TO EXPECT THAT A LARGER GATE BIAS IS NEC-ESSARY TO DEPLETE, AND FINALLY INVERT THE CHANNEL WHEN THE SUBSTRATE IMPURITY CONCENTRATION IS HIGH.

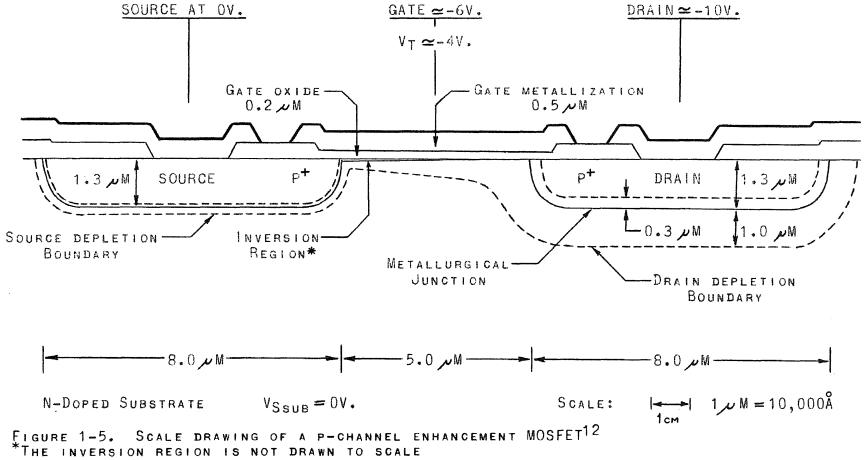

FIGURE 1-5 ILLUSTRATES A P-CHANNEL ENHANCEMENT MOSFET DRAWN TO SCALE. THE CONTOURS OF THE DEPLETION REGIONS AND THE VARIOUS DIMENSIONS APPROXIMATE THEORETICAL BOUNDARIES BASED ON CUSTOMARY IMPURITY DOPING CONCENTRATIONS AND APPLIED TERMINAL VOLTAGES. SINCE THE WIDTH OF THE INVERSION REGION IS TYPICALLY LESS THAN 100Å, CHANNEL INVERSION AND DRAIN CONDUCTANCE ARE BOTH ESSENTIALLY SURFACE EFFECTS. THEREFORE, THE CHARACTERISTICS OF THE OXIDE-SEMICONDUCTOR INTERFACE LARGELY DETERMINE THE OBSERVED PROPERTIES OF MOS TRANSIS-TORS.

SUCCEEDING CHAPTERS DISCUSS THE SI-SIO<sub>2</sub> INTERFACE IN MORE DETAIL. CORRELATIONS ARE MADE BETWEEN SURFACE-STATE DENSITY, SEMICONDUCTOR IMPURITY CONCENTRATION, AND BOTH THE EXCESS NOISE AND SATURATION DRAIN CONDUCTANCE PHENOM-ENA AND HOW THEY RELATE TO THE TYPE AND EXTENT OF DRAIN BREAKDOWN IN ENHANCEMENT-MODE MOS TRANSISTORS.

#### REFERENCES

<sup>1</sup>W. G. GOSLING, W. G. TOWNSEND AND J. WATSON, <u>FIELD</u>-<u>EFFECT ELECTRONICS</u> (New York, 1971), p. 34. Ref. 1971-4.

<sup>2</sup>A. S. GROVE, <u>PHYSICS AND TECHNOLOGY OF SEMICONDUCTOR</u> <u>Devices</u> (New York, 1967), p. 98. Ref. 1967-7.

<sup>3</sup>D. Frohman-Bentchkowsky and A. S. Grove, "Conductance of MOS Transistors in Saturation," <u>IEEE Transactions on</u> <u>Electron Devices</u> (1969), p. 110. Ref. 1969-2.

<sup>4</sup>Op. Cit., Gosling et al., p. 39.

<sup>5</sup><u>Op</u>. <u>Cit</u>., Bentchkowsky and Grove, p. 110.

6<u>1вір.</u>, рр. 108-113.

<sup>7</sup>J. A. NIELEN AND O. W. MEMELINK, "THE INFLUENCE OF THE SUBSTRATE UPON THE DC CHARACTERISTICS OF SILICON MOS TRANSISTORS," <u>Philips Research Reports</u> (1967), pp. 55-71. Ref. 1967-10.

<sup>8</sup>J. A. Guerst, "Theory of Insulated-Gate Field-Effect Transistors Near and Beyond Pinch-Off," <u>Solid-State Elec-</u> <u>tronics</u>(GB) (1966), pp. 129-42. Ref. 1966-5.

<sup>9</sup><u>Op</u>. <u>Cit</u>., Bentchkowsky and Grove, p. 110.

<sup>10</sup>V. G. K. REDDI AND C. T. SAH, "Source to Drain Resistance Beyond Pinch-Off in Metal-Oxide-Semiconductor Transistors (MOST)," <u>IEEE Transactions on Electron Devices</u>(1965), P. 140. Ref. 1965-6.

<sup>11</sup>HARRY E. STEWART, <u>ENGINEERING</u> <u>ELECTONICS</u> (BOSTON, 1969), PP. 28-29. Ref. 1969-8.

<sup>12</sup>Richard S. Cobbold, <u>Theory and Application of Field</u>-Effect Transistors (New York, 1970), p. 290. Ref. 1970-2.

#### CHAPTER 2

### FABRICATION AND PROPERTIES OF THE SI-SIO2 INTERFACE

### 2.1 INTRODUCTION

MANY OPERATING CHARACTERISTICS OF MOS FIELD-EFFECT TRANSISTORS, PARTICULARLY THOSE WHICH FUNCTION IN THE EN-HANCEMENT MODE, MAY BE TRACED DIRECTLY TO THE PROPERTIES OF THE SILICON-SILICON DIOXIDE INTERFACE. THE FOLLOWING DISCUSSIONS QUALITATIVELY INVESTIGATE THESE PROPERTIES AND REVIEW THE MECHANISMS BY WHICH THE INSULATING LAYER IS GROWN ON SILICON. EXPERIMENTAL EVIDENCE IS OFFERED TO EXPLAIN THRESHOLD VOLTAGE DRIFT IN TERMS OF A REDIS-TRIBUTION OF MOBILE IMPURITY IONS WITHIN THE OXIDE. THE MAGNITUDE OF SUCH DRIFT IS CORRELATED WITH THE INTENSITY OF DRAIN CURRENT FLUCTUATIONS AND IT IS SHOWN THAT TRAN-SISTORS WHICH EXHIBIT HIGH NOISE ALSO TEND TO SHOW HIGH THRESHOLD VOLTAGE DRIFT. MEASUREMENTS OF <sup>1</sup>DSS CONFIRMED THAT THERE IS NO MEANINGFUL CORRELATION BETWEEN LEAKAGE AT THE DRAIN P-N JUNCTION AND THRESHOLD VOLTAGE DRIFT.

### 2.2 BACKGROUND INFORMATION

<u>Growth and oxidation of silicon</u>. Crystal defects may be introduced during the growth of n- or p-doped monocrystaline silicon. Crystal defects may be thermally stress-induced near the liquid-solid interface. During epitaxial growth, vapor-phase reduction of silicon-tetrachloride introduces defects as the temperature of growth is REDUCED.

THE OVERALL REVERSIBLE CHEMICAL REACTION<sup>1</sup>

$$SICL_4 + 2H_2 \implies SI(SOLID) + 4HCL 2-1$$

SHOWS THAT HYDROCHLORIC ACID CONTAINED IN THE CARRIER GAS ENTERING THE REACTOR MAY RESULT IN REMOVAL RATHER THAN GROWTH OF SILICON.

THE COMPETING REACTION<sup>2</sup>

$$S_1CL_4 + S_1(SOLID) = 2S_1CL_2$$

2-2

SUGGESTS THAT "IF THE [SILANE] CONCENTRATION IS TOO HIGH, ETCHING OF THE SILICON WILL TAKE PLACE EVEN IN THE AB-SENCE OF A SIGNIFICANT CONCENTRATION OF HCL."<sup>3</sup> Such ETCHING DESTROYS MONO-CRYSTALLINE SURFACE PERIODICITY DUE TO LOSS OF SURFACE ATOMS. HIGH TEMPERATURES DURING THE GROWTH PROCESS ENABLES NEIGHBORING ATOMS TO EASILY MIGRATE TO REDUCE THE ENERGY LEVEL AT STRESS POINTS CAUSED BY VACANCIES. THIS INDUCES EVEN MORE LATTICE DE-FORMATION WHICH MAY LEAVE THE SUBSTRATE WITH AN EXCESS OF HIGH ENERGY STATES AS A RESULT OF WEAK OR MISSING CO-ORDINATIVE BONDS NEAR THE SEMICONDUCTOR SURFACE. IN CONTRAST WITH RELATIVELY RIGID TETRAHEDRONS OF NEAR PER-FECT CRYSTALLINE SILICON, THE HIGH ENERGY STATES MAY FACILITATE HIGHER DIFFUSIVITY OF IMPURITIES INTO THE SUBSTRATE. THERMAL OXIDATION OF SILICON MAY PROCEED BY EITHER OF TWO REACTIONS DEPENDING ON THE NATURE OF THE OXIDATION PROCESS USED:<sup>4</sup>

DRY

$$S_{1(SOLID)} + O_2 \xrightarrow{S_1O_2(SOLID)} 2-3$$

WET

$$S_{1(SOLID)} + H_{20} = S_{10} (SOLID)^{+2H_{2}} - 4$$

IT HAS BEEN SHOWN THAT SOME OF THE SURFACE EPITAXIAL SILICON IS CONSUMED DURING OXIDATION:

"From the densities and molecular weights of silicon dioxide, a layer of silicon .45  $x_0$  thick is consumed [where  $x_0$  is the net oxide thickness]. It has been demonstrated by the use of radioactive tracers that oxidation proceeds by an inward motion of the oxidizing species through the oxide layer rather than by the opposite process of the outward motion of silicon to the outer surface of the oxide."<sup>5</sup>

Accordingly, the oxidizing species must undergo three consecutive steps during oxidation: 6

1. THEY MUST BE TRANSPORTED FROM THE BULK OF THE GAS TO THE GAS-OXIDE INTERFACE;

2. THEY MUST DIFFUSE ACROSS THE OXIDE LAYER ALREADY PRESENT: AND

3. THEY MUST REACT AT THE SILICON SURFACE.

IT IS NOW CLEAR THAT OXIDE-MASKING STEPS DURING PRO-DUCTION OF MOS DEVICES INDUCE CRYSTAL STRESS WHEN THE OXIDIZING SPECIES MAKE THEIR WAY THROUGH EXISTING LAYERS OF OXIDE AND THE SEMICONDUCTOR BENEATH THEM. OTHER IONIC IMPURITIES SUCH AS SODIUM AND HYDROGEN MAY REACT WITH THE SILICON AND SILICON DIOXIDE AT THE SI-SIO<sub>2</sub> INTERFACE AND IN-TRODUCE A LARGE NUMBER OF STATES WITH ENERGY LEVELS WITHIN THE FORBIDDEN GAP. SUCH STATES ARE CALLED <u>SURFACE STATES</u> AND WILL BE SHOWN TO PLAY A VITAL PART IN NOISE PHENOMENA ASSOCIATED WITH MOS TRANSISTORS.

IT IS A WELL KNOWN FACT THAT "IN EQUILIBRIUM, THE CON-CENTRATION OF A SPECIES WITHIN A SOLID IS PROPORTIONAL TO THE PARTIAL PRESSURE OF THE SPECIES IN THE SURROUNDING GAS."<sup>7</sup> EXPERIMENTAL DATA UNDER WIDELY RANGING CONDITIONS OF TEM-PERATURE, PARTIAL PRESSURE OF OXIDENTS, AND USING EITHER OXYGEN OR WATER VAPOR AS THE OXIDIZING SPECIES CONFIRM THAT FOR LARGE TIMES T, THE THICKNESS OF THE OXIDE FILM MAY BE EXPRESSED AS<sup>8</sup>

$$x_0^2 \simeq Z \cdot T$$

2-5

HERE Z IS A PARABOLIC RATE CONSTANT FOR THE PROCESS AND IS PROPORTIONAL TO THE PARTIAL PRESSURE OF THE OXIDENT IN THE GAS AND RELATED TO BOTH THE DIFFUSIVITY AND CONCENTRATION OF THE OXIDIZING SPECIES IN THE OXIDE LAYER.

EXPERIMENTAL INVESTIGATIONS HAVE INDICATED THAT "FOR OXIDATION BOTH WITH OXYGEN AND WITH WATER VAPOR, THE OXI-DIZING SPECIES MOVING THROUGH THE OXIDE LAYER ARE APPARENTLY <u>MOLECULAR</u>."<sup>9</sup> AT LEAST ONE THEORY OF 1/F NOISE<sup>10</sup> MAKES USE OF A "SLOW RELAXATION" IN THE TRANSISTION FROM MOLECULAR

CHEMISORBED WATER TO LARGER CHEMISORBED COMPLEXES.\*

<u>Properties of the SI-SIO2 interface</u>. The siliconsilicon dioxide interface in MOS transistors may be characterized by <u>fixed surface-state charge</u> in the oxide, <u>space charges</u> within the insulating layer due to <u>mobile</u> <u>impurity ions and traps</u> ionized thermally or by radiation, and <u>surface states</u>. Each of these phenomena are treated individually in the following discussions.

1. Fixed surface-state charge. It is theorized that the unexpected existence of a fixed surface-state charge,  $Q_{SS}$ , located at or near the SI-SIO<sub>2</sub> interface is attributed to excess unreacted ionic silicon present in the oxide during the oxidation process. The characteristics of this charge have been extensively investigated by Deal et al<sup>11</sup> and have been summarized by Grove:<sup>12</sup>

IT IS FIXED AND CAN BE NEITHER CHARGED NOR DIS-CHARGED OVER A WIDE VARIATION OF BENDING OF THE SILICON ENERGY BANDS.

IT IS NOT AFFECTED UNDER CONDITIONS LEADING TO SODIUM MIGRATION IN THE OXIDE.

IT IS LOCATED WITHIN APPROXIMATELY 200Å OF THE SI-SIO2 INTERFACE.

THE CHARGE DENSITY IS NOT AFFECTED BY EITHER THE OXIDE THICKNESS OR THE TYPE AND CONCENTRATION OF IMPURITY PRESENT.

\*O. JANTSCH<sup>13</sup> AND REVESZ<sup>14</sup> HAVE SHOWN THAT THE "SLOW RELAXATION" RESULTS IN A "MODULATION OF SURFACE RECOMBINA-TION" WHICH PRODUCES DRAIN CURRENT FLUCTUATIONS IN MOSFETS. THE CHARGE IS A FUNCTION OF THE OXIDATION AND ANNEALING CONDITIONS AS WELL AS THE ORIENTA-TION OF THE SILICON CRYSTAL.

THE FIXED SURFACE-STATE CHARGE RESULTS IN A "PARA-LLEL TRANSLATION OF THE CAPACITANCE-VOLTAGE CHARACTER-ISTICS ALONG THE VOLTAGE AXIS.<sup>1115</sup> IT ALSO INCREASES THE EFFECTIVE GATE VOLTAGE BY<sup>16</sup>

$$V_{G}' = V_{G} + Q_{SS}/C_{O} \qquad 2-6$$

AND DECREASES THE FLAT-BAND VOLTAGE ACCORDING TO<sup>17</sup>

$$V_{FB} = \Phi_{MS} - Q_{SS} \left( \frac{x_0}{K_0 \epsilon_0} \right)$$

2-7

where  $V_{FB}$  is due to the difference in work functions between the metal and the semiconductor material and  $\Phi_{MS}$  is the metal-semiconductor work function difference with-out the influence of  $Q_{SS}$ .

2. Space charges due to ionic contamination. A major problem with early MOS devices has been traced to sodium contamination and ionic drift under the influence of an electric field. This causes a "rearrangement of ionic space-charge distribution in the oxide."<sup>18</sup>

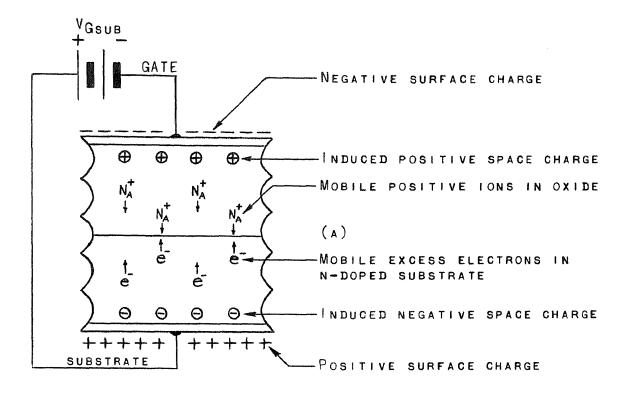

FIGURE 2-1 PRESENTS A MODEL OF THE SILICON-SILICON DIOXIDE INTERFACE WITH BIAS APPLIED AT ELEVATED TEMPERA-TURES. FIGURE 2-1A SHOWS THE APPLICATION OF A -V<sub>GSUB</sub> AND THE INDUCED CHARGES AT THE METAL-GATE AND SUBSTRATE-METAL INTERFACES. THE DIAGRAM SHOWS POSITIVE SODIUM ATOMS, REPELLED BY THE INDUCED OXIDE CHARGE AND HAVING SUFFICIENT THERMAL ENERGY TO MIGRATE TOWARD THE SUBSTRATE, DRIFTING TOWARD THE SI-SIO<sub>2</sub> INTERFACE. THIS CAUSES MOBILE ELECTRONS IN THE N-DOPED SUBSTRATE TO DRIFT TOWARD THE OXIDE AND CHANNEL REGION IN P-CHANNEL ENHANCEMENT MOSFET'S.

FIGURE 2-1B ILLUSTRATES THE FOUR RESIDUAL SPACE CHARGES WHICH REMAIN IF THE DRIFT PROCESS IS ALLOWED TO CONTINUE OVER A LONG PERIOD OF TIME. THE RESULT IS THE SAME AS IF A POSITIVE VOLTAGE IS APPLIED TO THE GATE AS WAS SHOWN IN FIGURE 1-2B. THE CHANNEL APPEARS TO BE MORE HEAVILY N-DOPED THAN BEFORE IONIC DRIFT. THE NEGATIVE GATE VOLTAGE REQUIRED FOR SURFACE INVERSION,  $V_T$ , MUST NOW BE INCREASED, THEREBY ACCOUNTING FOR APPARENT NEGATIVE THRESH-OLD DRIFT.

3. Space charges due to ionized traps. Exposure of silicon dioxide films to x-ray, gamma ray, and low-and highenergy irradiation results in the formation of electron-hole pairs. When in the presence of an electric field, the electrons and holes separate.<sup>19</sup>

Consider the model in figure 2-1 again. If a  $-V_{GS}$  is applied and, instead of heat the device is brought into contact with x-radiation, optically excited electrons drift toward the oxide and holes drift toward the semiconductor. Since the mobility of electrons in silicon dioxide is very

FIGURE 2-1. MODEL OF THE SI-SIO<sub>2</sub> INTERFACE IN A P-CHANNEL ENHANCEMENT MOSFET SHOWING THE RESULTS OF IONIC DRIFT IN THE OXIDE UNDER THE INFLUENCE OF AN ELECTRIC FIELD. (A) SODIUM IONS ARE ATTRACTED TOWARD THE SEMICONDUCTOR WHILE MOBILE ELECTRONS IN THE N-DOPED SUBSTRATE DRIFT TO-WARD THE OXIDE. (B) RESIDUAL SPACE-CHARGES IN THE OXIDE AND IN THE SEMICONDUCTOR MATERIAL. THE APPARANT HIGHER DOPING IN THE CHANNEL REGION CAUSES A NEGATIVE SHIFT IN THE THRESHOLD VOLTAGE, THE GATE VOLTAGE REQUIRED TO IN-VERT THE SEMICONDUCTOR SURFACE. LOW, MAJORITY CARRIERS IN THE N-DOPED SUBSTRATE CANNOT RECOMBINE IN THE BULK INSULATOR AT THE SI-SIO<sub>2</sub> INTERFACE. THEREFORE, THERE IS A BUILD-UP OF SPACE CHARGE IN THE OXIDE AS HOLES ARE TRAPPED NEXT TO THE SUBSTRATE.

Continued irradiation in the presence of an electric field causes a larger fraction of the total applied gate voltage to be dropped across the space charge region, thereby further increasing the electric field across the space-charge region due to the accumulation of holes. If the process is allowed to continue, the field in the rest of the oxide gradually approaches zero and a steady-state highly localized electric field condition is brought about in the oxide at the silicon-silicon dioxide interface.<sup>20</sup>

4. Fast surface states. Figure 1-2 illustrated the energy band bending which takes place in the semiconductor near: the SI-SIO<sub>2</sub> interface when the gate is held at some positive or negative potential with respect to the substrate. Due to a disruption of the periodicity of the semiconductor surface during oxidation, there are many surface energy states within the forbidden gap. Consequently, variations in the energy bands relative to the Fermi level affect the "probability of occupation of those states."<sup>21</sup>

By DEFINITION, "THOSE STATES WHOSE CHARGE CAN BE READILY EXCHANGED WITH THE SEMICONDUCTOR ARE CALLED SURFACE

STATES.<sup>1122</sup> THE PRESENCE OR ABSENCE OF ELECTRONS IN SUCH STATES IS A FUNCTION OF THE SURFACE POTENTIAL WHICH IS ITSELF A FUNCTION OF THE APPLIED GATE VOLTAGE.<sup>\*</sup>

# 2.3 PREVIOUS EXPERIMENTAL INVESTIGATIONS

Revesz<sup>23</sup> has investigated the SI-SIO<sub>2</sub> interface in enhancement MOSFET's and has shown that the silicon surface state is a <u>donor</u>, that is, positively ionized silicon provides an excess of donor electrons. During oxidation in oxygen at relatively high temperatures it is theorized that O<sup>-</sup> and O<sup>--</sup> consume electrons as they diffuse into the silicon substrate. Revesz has concluded that oxidation in water vapor involves significantly more surface states than does oxidation in oxygen alone and that the oxidation rate is increased while the density of free states is reduced.<sup>24</sup>

IT IS WELL KNOWN THAT STATES HAVE A MUCH GREATER PROB-ABILITY OF EXISTING AT DISLOCATIONS AND BOUNDARY IMPERFEC-TIONS THAN ANYWHERE ELSE AND THAT THEY GIVE RISE TO THE FIXED SURFACE-STATE CHARGE PHENOMENON IN THE OXIDE. IT HAS BEEN THEORIZED THAT DONOR ELECTRONS PRESENT IN THIS MANNER ACT AS <u>RECOMBINATION CENTERS</u>, ENABLE THE DIFFUSION OF SUCH

<sup>\*</sup>SURFACE-STATE FLUCTUATIONS RESULTING IN VARIATIONS IN SURFACE POTENTIAL MODULATE CHANNEL CONDUCTANCE WHICH IN TURN CAUSES VARIATIONS IN DRAIN CURRENT. THESE DRAIN CUR-RENT FLUCTUATIONS MAY BE OBSERVED AS NOISE.

IMPURITIES AS HIGHLY MOBILE SODIUM ION, Na<sup>+</sup>, Hydrogen ION,  $H^+$ , and other <u>acceptors</u> which may be present.<sup>25</sup>

WHEN THE SEMICONDUCTOR SURFACE OF A P-CHANNEL ENHANCE-MENT MOSFET IS INVERTED, THE FREE HOLE CONCENTRATION IS VERY LARGE WHILE THE FREE ELECTRON DENSITY IS NEGLIGIBLE. SINCE IONIZED SILICON, SI<sup>+3</sup> and SI<sup>+4</sup>, IS ALSO AN ACCEPTOR, IT HAS BEEN THEORIZED THAT THE SURFACE STATES IN P-CHANNEL DEVICES ARE ALMOST EXCLUSIVELY <u>FAST TRAPPING CENTERS</u> IN THE CONDUC-TION CHANNEL.<sup>\*</sup>

## 2.4 INVESTIGATION OF THRESHOLD VOLTAGE DRIFT

EXPERIMENTAL METHOD. IN ORDER TO QUANTITATIVELY IN-VESTIGATE THE MAGNITUDE OF THRESHOLD VOLTAGE DRIFT DUE TO IONIC CONTAMINATION IN THE INSULATING LAYER AND IN ORDER TO CORRELATE SUCH DRIFT WITH EXCESS NOISE AND OTHER SURFACE-RELATED PHENOMENA, LIFE-TESTING OF SEVERAL ENHANCEMENT MOSFET'S WAS UNDERTAKEN.

A LARGE NUMBER OF MEDIUM CONDUCTANCE P-CHANNEL FIELD-EFFECT TRANSISTORS WERE OBTAINED. \*\* THESE DEVICES WERE

\*Such other chemisorbed species as H<sub>2</sub>O<sup>+</sup> may also be considered fast trapping centers. O. Jantsch claims they figure prominently in the production of excess noise in MOS transistors. See reference 1967-8 for more details.

\*\* THE DEVICES WERE MANUFACTURED BY AMERICAN MICRO-SYS-TEMS, INC. OF SANTA CLARA, CALIFORNIA AND WERE PART OF JOINT RELIABILITY STUDIES UNDERTAKEN BY NEWARK COLLEGE OF ENGIN-EERING AND PICATINNY ARSENAL DURING THE YEARS 1968-72. PURPORTED TO BE DESIGNED PRIMARILY FOR "LINEAR WIDEBAND AMPLIFIERS AND HIGH SPEED SWITCHING AND COMMUTATING APPLI-CATIONS." THEY FEATURED A HIGH GAIN-BANDWIDTH PRODUCT, TYPICALLY 195MHZ, AND A THRESHOLD VOLTAGE RANGE OF FROM -3.5 TO -5.5V. Two CONFIGURATIONS AND THREE TYPES WERE AVAILABLE: TYPE DDO?P UNITS HAD A BUILT-IN ZENER DIODE VOLTAGE LIMITER BETWEEN THE GATE AND THE SUBSTRATE WHILE TYPES DDO8P AND DD08K HAD NO SUCH GATE PROTECTION. ALL WERE FOUR LEAD TRANSISTORS (ONE LEAD FOR THE DRAIN, GATE, SOURCE AND SUBSTRATE BULK) AND HERMETICALLY SEALED IN OR-DINARY TO-72 METAL CANS. THERE WERE NO SIGNIFICANT DIF-FERENCES IN THE CONSTRUCTION OF THE THREE TYPES OF MOSFET'S.

TWENTY DEVICES, TEN EACH OF TYPES DD07P AND DD08K, WERE SELECTED FOR LIFE-TESTING FOR THRESHOLD VOLTAGE DRIFT ON THE BASIS OF THEIR LOW FREQUENCY NOISE INTENSITY.\* ACCORDINGLY, FIVE HIGH- AND FIVE LOW-NOISE UNITS WERE SELECTED FROM EACH OF THE TWO TYPES.

Teflon sockets were used to connect all transistors with common drain, source, and substrate. All type DD07P devices were biased with  $V_{\rm GS}=-25V$ . and all type DD08K units had -50V. on the gate. The complete assembly was wired inside an oven latter maintained at 130±5°C for 500 hours.

<sup>\*</sup>Noise measurements were made at 10Hz. and at 1KHz., both with a bandwidth of 1 cycle. The noise measurements are detailed in section 3.5.

EXPERIMENTAL RESULTS AND DISCUSSION. APPENDIX C LISTS THE PERCENTAGE NEGATIVE THRESHOLD VOLTAGE DRIFT,  $\% \Delta V_T$ , FOR ALL TWENTY UNITS TESTED. TYPE DD07P TRANSISTORS EXHIBITED RANGES OF DRIFT OF FROM 1.75 TO 2.66 PERCENT AND FROM 3.16 TO 7.15 PERCENT FOR LOW- AND HIGH-NOISE UNITS, RESPECTIVELY. RANGES OF 6.88 TO 9.11 AND 11.5 TO 23.6 PERCENT DRIFT WERE OBSERVED FOR THE LOW- AND HIGH+ NOISE TYPE DD08K UNITS.

It is apparant that threshold voltage drift is directly proportional to the electric field across the oxide, as evidenced by the higher percent drift for those units which were blased at the higher gate voltage. Statistical analysis confirmed that the type DD08K units exhibited substantial  $\Delta V_T$  while drift in the DD07P transistors was very small.

OF PARTICULAR IMPORTANCE WAS THE FACT THAT HIGHER THRESHOLD VOLTAGE DRIFT WAS OBSERVED IN THE HIGH NOISE UNITS THAN IN THOSE WITH LOW NOISE INTENSITY. IT WAS THEREFORE CONCLUDED THAT THERE IS A DEFINITE CORRELATION BETWEEN 1/F NOISE AND THRESHOLD VOLTAGE DRIFT AND THAT, FOR P-CHANNEL ENHANCEMENT MOSFET'S, IONIC DRIFT IN THE OXIDE DEFINITELY AFFECTS THE SEMICONDUCTOR SURFACE.

<sup>\*</sup>Previous investigations showed that the type DD08K devices exhibited unusually high  $\Delta V_T$ . It was therefore of particular importance that such high drift units also be included in this investigation.

<sup>&</sup>lt;sup>\*\*</sup>Chapter 3 shows that 1/F noise is a surface-related phenomena and that ionic Drift increases the surface-state density.

APPENDIX E DESCRIBES THE PROCEDURES USED TO MEASURE THE SHORT-CIRCUIT DRAIN LEAKAGE CURRENT (WITH ZERO GATE BIAS) AND LISTS THE RESULTS OBTAINED BOTH BEFORE AND AFTER LIFE-TESTING FOR THRESHOLD VOLTAGE DRIFT. IT WAS FOUND THAT THE LEAKAGE CURRENT INCREASED BY A FACTOR OF FROM THREE TO FOUR BUT THAT THIS WAS INSUFFICIENT TO CONCLUDE THAT A SIGNIFICANT AMOUNT OF DRAIN JUNCTION DEGRADATION HAD TAKEN PLACE AFTER 500 HOURS OF BIAS AT 130±5°C.

Furthermore, since there was no significant difference between the amount by which  $I_{DSS}$  increased for units having either relatively high or relatively low noise, it was concluded that drain leakage was not a factor which results in the production of drain current fluctuations. Also, since the increase in leakage for transistors which showed appreciable threshold voltage drift was similar to that for units which exhibited only a small amount of drift, it was concluded that there is no correlation between  $I_{DSS}$ and threshold voltage drift and the mechanism of ionic drift at the Si-SiO<sub>2</sub> interface which produces the drift.

## REFERENCES

<sup>1</sup>A. S. GROVE, <u>Physics and Technology of Semiconductor</u> <u>Devices</u> (New York, 1967), p. 8. Ref. 1967-7. <sup>2</sup><sub>ІВІД</sub>., р. 9. <sup>3</sup> | ВІД., Р. 9. <sup>4</sup> Івір., р. 22. <sup>5</sup> IBID. P. 23. <sup>6</sup>Івір., р. 24. <sup>7</sup>IBID., PP. 24-25. <sup>8</sup>Івір., р. 27. <sup>9</sup><u>Івір</u>., р. 28. <sup>10</sup>O. JANTSCH, "A THEORY OF 1/F NOISE AT SEMICONDUCTOR SURFACES," <u>Solid-State Electronics</u>(GB) (1968), pp. 267-72. Ref. 1968-8. <sup>11</sup>B. E. DEAL, E.H. SNOW, AND A.S. GROVE, "PROPERTIES OF THE SILICON—SILICON DIOXIDE SYSTEM," <u>Semiconductor Products</u> <u>AND Solid State Technology</u> (1966), pp. 25-33. Ref. 1966-4. 120P. CIT., GROVE, P. 342. <sup>13</sup>Op. CIT., O. JANTSCH, P. 268. <sup>14</sup>Akos G. Revesz, "The Defect Structure of Grown Silicon Dioxide Films," <u>IEEE Transactions on Electron Devices</u> (1964), PP. 97-101. ŘEF. 1964-3. <sup>15</sup><u>Op</u>. <u>Cit</u>., Grove, p. 342. <sup>16</sup>D. FROHMAN-BENTCHKOWSKY AND A. S. GROVE, "CONDUCTANCE OF MOS TRANSISTORS IN SATURATION," <u>IEEE TRANSACTIONS ON</u> <u>ELECTRON DEVICES</u> (1969), p. 110. Ref. 1969-2. <sup>17</sup><u>Ор. Сіт</u>., Grove, р. 345. <sup>18</sup>Івід., р. 338. <sup>19</sup>Івір., р. 340.

20 IBID. PP. 341-2.

<sup>21</sup><u>IBID</u>., P. 282. <sup>22</sup><u>IBID</u>., P. 283. <sup>23</sup><u>OP</u>. <u>Cit</u>., Revesz, p. 98. <sup>24</sup><u>IBID</u>., P. 98. <sup>25</sup><u>OP</u>. <u>Cit</u>., O. Jantsch, p. 268.

## CHAPTER 3

# THE SURFACE-STATE RELATED NOISE PHENOMENA

## IN MOS TRANSISTORS

#### 3.1 INTRODUCTION

IN THE ABSENCE OF EXTERNALLY APPLIED POWER, VIRTUALLY ALL RESISTIVE ELEMENTS MAY BE THOUGHT OF AS NOISE GENERA-TORS. HOWEVER, MOS TRANSISTORS ARE UNIQUE IN THAT THEY PRODUCE AN EXCEPTIONALLY HIGH INTENSITY OF <u>EXCESS NOISE</u> WHEN POWER IS APPLIED. THIS NOISE HAS BEEN SHOWN TO BE DIRECTLY PROPORTIONAL TO CURRENT DENSITY AND INVERSELY PROPORTIONAL TO THE FREQUENCY AT WHICH IT IS DETECTED.<sup>1</sup> FURTHERMORE, NUMEROUS INVESTIGATIONS HAVE SHOWN THAT THIS "1/F" NOISE IS STRONGLY DEPENDENT UPON THE GENERAL SURFACE CONDITIONS AT THE SILICON-SILICON DIOXIDE INTERFACE IN MOS TRANSISTORS AND ON THE SURFACE STATE DENSITY IN PARTICULAR.

THE FOLLOWING DISCUSSIONS PRESENT A BRIEF BACKGROUND ON THE MAJOR TYPES OF ELECTRICAL NOISE WITH PARTICULAR EM-PHASIS ON LOW FREQUENCY EXCESS NOISE INTENSITY AND ITS USE IN AN ANALYSIS OF COMPONENT RELIABILITY. EXPERIMENTAL RE-SULTS ARE THEN PRESENTED WHICH QUALITATIVELY CORRELATE SUR-FACE-STATE RELATED 1/F NOISE INTENSITY WITH THE SURFACE-STATE DENSITY, SEMICONDUCTOR IMPURITY CONCENTRATION, AND OBSERVED DIFFERENCES IN SATURATION DRAIN CONDUCTANCE BE-TWEEN HIGH- AND LOW-NOISE ENHANCEMENT MOSFET'S.

## 3.2 BASIC NOISE THEORY

ELECTRICAL NOISE MAY BE DEFINED AS SPURIOUS, UNWANTED SIGNALS WHICH ARE RANDOM IN NATURE AND WHICH TEND TO BE APERIODIC. NOISE MAY BE NAMED FOR ITS APPARANT CAUSE AND EFFECT (IE. THERMAL EXCITATION, RANDOM RECOMBINATION, OR RANDOM COLLISIONS) OR BY ITS FREQUENCY DOMAIN (EG. LOW-FREQUENCY NOISE). ACCORDINGLY, THERE ARE THREE MAJOR TYPES OF NOISE COMMONLY FOUND IN ELECTRICAL COMPONENTS, EACH OF WHICH IS DISCUSSED INDIVIDUALLY BELOW.

THERMAL (JOHNSON) NOISE. THE RANDOM VELOCITIES OF CARRIERS BETWEEN COLLISIONS CONSTITUTES CURRENTS WHICH CAUSE A FLUCTUATING VOLTAGE TO APPEAR ACROSS THE TERMINALS OF ANY RESISTANCE R. FOR MOS TRANSISTORS, THE NYQUIST RELATION<sup>2</sup>

$$\overline{V}^2 = 4kTR\Delta f \qquad 3-1$$

EXPRESSES THE MEAN-SQUARED NOISE VOLTAGE IN TERMS OF THE TOTAL DRAIN-TO-SOURCE RESISTANCE, THE ABSOLUTE TEMPERATURE, AND THE BANDWIDTH IN CYCLES PER SECOND.

THE SPECTRAL INTENSITY OF THERMAL NOISE IS "WHITE," THAT IS, ITS MAGNITUDE IS PRACTICALLY UNIFORM WITH RESPECT TO FREQUENCY. CONSEQUENTLY, THE LARGER THE INCLUDED BAND-WIDTH, THE GREATER WILL BE THE INTENSITY OF NOISE MEASURED. ALL PRACTICAL ELECTRONIC COMPONENTS POSSESS A FINITE RESIS-TANCE WHICH CONTRIBUTES THERMAL NOISE. SHOT NOISE. DIRECT CURRENTS IN SEMICONDUCTOR MATER-IALS ARE BY WAY OF A CONTINUOUS PROCESS OF DISSOCIATION AND RECOMBINATION IN A SPASMODIC "JERKY" FASHION. THIS RESULTS IN INSTANTANEOUS CURRENT FLUCTUATIONS, THE MEAN-SQUARED VALUE OF WHICH IS GIVEN BY<sup>3</sup>

$$\overline{i}^2 = 29 \mathrm{I}\Delta f \qquad 3-2$$

where I is the direct current measured,  $\mathscr{G}$  is the carrier charge, and  $\Delta f$  is the included bandwidth.

Previous investigations<sup>4,5,6</sup> have shown that shot noise is essentially white for low frequencies. It may be considered independent of frequency over the range of interest for MOSFET operation.

Excess (1/F. MODULATION, FLICKER) NOISE. THE ORIGIN OF EXCESS NOISE IS "THOUGHT TO LIE IN SEMICONDUCTOR CRYSTAL IMPERFECTIONS AND SURFACE EFFECTS."<sup>7</sup> By passivating silicon Devices with silicon dioxide to reduce the role of surface states, defects are necessarily introduced at the SI-SIO<sub>2</sub> interface. The presence of fast surface states at the semiconductor surface leads to a fluctuation of surface charge in MOS transistors and may produce surface-state related noise which may be observed in Either one or both the gate and the drain circuit in MOSFET's. Bell<sup>8</sup> has proposed two mechanisms which result in observed excess noise in MOS devices: 1. <u>Gate noise</u><sup>\*</sup> due to fluctuations in total surface charge as carriers move to and from the oxide, and

2. <u>Drain current fluctuations</u>\*\* resulting from variations in channel conductance as a result of variations in V<sub>GS</sub> due to the charge fluctuations which produce gate noise.

Bell offers the following generalized expression for frequency-dependent noise:<sup>9</sup>

$$\frac{V^2B}{B} = K(J^{\theta}R^{\eta}v^{\lambda}s/f^{\eta})B \qquad 3-3$$

where B = BANDWIDTH in cycles per second

J = CURRENT DENSITY K = MATERIAL CONSTANT R = RESISTANCE IN OHMS S = SHAPE FACTOR V = VOLUME 7 + 8 = 2 to balance the equation in time B = 2 to balance the equation in charge

\*For any  $\Delta Q$  into the oxide from the semiconductor, there must be a  $\Delta Q$  of opposite polarity onto the gate and vice versa. This leads to gate charge fluctuation which is observed as a noise voltage in the gate circuit.

<sup>\*\*</sup>Variations of charge between the Depletion Region, the inversion region, and the surface states alters the instantaneous value of  $V_{\rm GS}$ . Recall from section 1.2 that the channel conductance, and therefore the Drain current, is easily modulated by variations in gate voltage. Hence the observed drain current fluctuations in MOS transistors. THE GENERAL EXPRESSION MAY BE SIMPLIFIED TO<sup>10</sup>

$$\frac{V^{2}B}{R} = K(J^{2}R^{2-\eta}v^{1-\varkappa}s/f)B \qquad 3-4$$

where  $x = (\gamma - 1)/3$ . For an exact 1/F spectrum, let  $\gamma = 1$ , 1-x = 1, 2- $\eta = 1$ , and let s be an area/unit length. Then The product R.s is in units of resistivity,  $\rho$ .

The noise power density for a 1/F spectral intensity (in which B is one cycle at an angular frequency of  $\omega$ ) may be stated as<sup>11</sup>

$$P_{N(\omega)} = K(J^2 q V/f) d\omega \qquad 3-5$$

WHICH IS DIRECTLY PROPORTIONAL TO THE DC POWER APPLIED (AND THE CURRENT DENSITY SQUARED) AND INVERSELY PROPOR-TIONAL TO FREQUENCY.\*

# 3.3 PREVIOUS STUDIES OF THE EXCESS NOISE SPECTRAL INTENSITY

SURFACE-STATE RELATED 1/F NOISE HAS BEEN ATTRIBUTED TO A MODULATION OF SURFACE RECOMBINATION. THIS REASONING IS BASED ON McWhorter's<sup>12</sup> theory of trapping centers at the SILICON-SILICON DIOXIDE INTERFACE:

1. THE INTRODUCTION OF TRAPPING CENTERS INTO THE SEMICONDUCTOR MATERIAL RESULTS IN A "DIRECT CHANGE IN CURRENT DUE TO A CHANGE IN THE NUMBER OF FREE CARRIERS AND AN INDIRECT CHANGE IN CURRENT DUE TO A CHANGE IN THE NUMBER OF TRAPPED CARRIERS."13

\*1/F NOISE IS USUALLY MASKED BY THERMAL NOISE AT ALL FREQUENCIES ABOVE 20KHZ AND THEREFORE MUST BE OBSERVED AT RELATIVELY LOW FREQUENCIES FOR TRUE 1/F DEPENDENCE. 2. THE RANDOM OCCUPANCY OF SURFACE STATES BY BROWNIAN MOTION "MODULATES THE SURFACE POTEN-TIAL, WHICH CAUSES A <u>FLUCTUATION IN SURFACE</u> <u>RECOMBINATION VELOCITY</u> AND A <u>MODULATION OF THE</u> <u>FREE CARRIER DENSITY</u> IN THE SPACE-CHARGE REGION NEAR THE SILICON SURFACE."<sup>14</sup>

3. SINCE THE DRIFT OF CHARGED CARRIERS CONSTI-TUTES A DIFFUSION CURRENT, ANY FLUCTUATION IN THE FREE CARRIER DENSITY NECESSARILY INDICATES A "FLUCTUATION IN DIFFUSION CURRENT."<sup>15</sup>

THE 1/F NOISE CAN THEN BE EXPLAINED BY "CONDUCTION CHANNEL CHARGE DENSITY FLUCTUATION CAUSED BY THE MODULA-TION OF SURFACE POTENTIAL DUE TO THE RANDOM OCCUPANCY OF SURFACE STATES"<sup>16</sup> which supports the theory of Drain CURRENT FLUCTUATIONS PUT FORTH BY BELL.

Since the Life-time of the fast surface states is typically about 10<sup>-9</sup> second, the recombination noise produced is of very high frequency. The observed low-frequency noise must therefore be a <u>modulation of surface</u> Recombination.<sup>17</sup>

Heiman and Warfield<sup>18</sup> have estimated that surface states are located within about 20Å from the the  $SI-SIO_2$ interface. Since the oxide thickness in MOS transistors is typically 600-2000Å (and since the oxide thickness must be orders of magnitude greater than the inversion layer), the resident distance of surface states is negligibly small and the <u>1/F</u> noise may be considered a surface phenomenon. Hsu<sup>19</sup> has analytically predicted the noise spectral intensity of low-frequency excess noise in p-channel enhancement MOSFET's and a review of his derivation is included in Appendix B. The <u>spectral intensity of the short</u>-<u>circuit drain current fluctuations</u> is given by<sup>20</sup>

$$S_{i(\omega)} = \left[\frac{g G_{M}}{A C_{0}}\right]^{2} \frac{4 k T A N_{T}(E) \gamma_{s}}{\alpha} (e^{\alpha \ell} - 1) \qquad 3-6 A$$

FOR  $\omega \gamma_{s} e^{\alpha \ell} \ll 1$

$$S_{i}(\omega) = \left[\frac{g^{G}G}{AC_{0}}\right]^{2} \frac{kTAN_{T}(E)}{\alpha f} \qquad 3-6B$$

FOR  $\omega \gamma_{s} \ll 1 \ll \omega \gamma_{s} e^{\alpha \ell}$

$$S_{i(\omega)} = \left[\frac{\varphi G_{M}}{AC_{0}}\right]^{2} \frac{4kTAN_{T}(E)}{\alpha \omega^{2} \gamma_{s}} (1 - e^{-\alpha \ell}) \qquad 3-6c$$

FOR  $1 \ll \omega \gamma_{s}$

where A = Effective area of the gate in cm<sup>2</sup>  $C_{O} = \frac{K_{O} \epsilon_{O}}{x_{O}} \text{ is the oxide capacitance}$   $G_{M} = \frac{\partial I_{D}}{\partial V_{G}} | \text{ is the MOST transconductance}$   $K = B_{O} \text{ transformed} \text{ for } V_{D} = \text{constant}$   $k = B_{O} \text{ transformed} \text{ to be 20Å}$   $N_{T}(E) = D_{E} \text{ nsity of trapped surface states per unit}$   $K = A_{B} \text{ solute temperature in } K$   $\gamma_{S} = T_{I} \text{ ime constant of surface states located at}$   $\omega = A_{N} \text{ solutar frequency in Rad/sec.}$

AND WHERE  $\alpha$  is experimentally determined to be 2×10<sup>8</sup> cm<sup>-1</sup> and exp( $\alpha \ell$ ) = 10<sup>17</sup>.<sup>21</sup>

From the above expressions it is apparant that very Low frequency noise is independent of frequency, a true 1/F spectral intensity is found only within the range of  $(2\pi\gamma_{\rm s}e^{\alpha\ell})^{-1}$  to  $(2\pi\gamma_{\rm s})^{-1}$  (a range theoretically predicted to be about 17 orders of magnitude), and that noise at higher frequencies has a  $1/F^2$  dependence.

OF PARTICULAR INTEREST IS THE DEPENDENCE OF NOISE INTENSITY ON THE SURFACE-STATE DENSITY. SINCE ONLY THOSE STATES "WITHIN  $\pm 2kT$  from the surface-state Fermi level contribute noise to the device, if the surface states are arbitrarily distributed in energy, the value  $N_T(E)$  represents the surface-state density within  $\pm 2kT$  of the Fermi level."<sup>22</sup> Processes which introduce states into this range of energy therefore result in an increase in the number of surface states and may be observed by an increase in noise intensity.

#### 3.4 ELECTRICAL NOISE AND COMPONENT RELIABILITY

AN EXCEPTIONALLY HIGH NOISE INTENSITY MAY BE REGARDED AS AN INDICATION OF SOME ABNORMALITY IN AN ELECTRICAL DEVICE. THOSE DEVICES EXHIBITING HIGH NOISE CHARACTERISTICS MAY THEREFORE BE CLASSIFIED AS POTENTIAL <u>RELIABILITY RISKS</u>. NOISE MEASUREMENTS ARE THEREFORE A <u>RELIABILITY TOOL</u> USED TO COMPARE DEVICES WITH AN ACCEPTED STANDARD.

ANY MECHANISM WHICH "FOCUSES" OR "FUNNELS" A SIGNIFI-CANT AMOUNT OF CURRENT THROUGH A SMALL CROSS-SECTION RESULTS IN A HIGH LOCALIZED CURRENT DENSITY AND ACCOMPANYING LOCAL-IZED HEATING IN A DEVICE. DEFECTS IN THE CRYSTAL STRUCTURE AT P-N JUNCTIONS, CRACKS, FLAWS, OR INCLUSIONS IN THE SEMI-CONDUCTOR MATERIAL MAY LEAD TO "CURRENT FUNNELING" AND HIGH 1/F NOISE INTENSITY.<sup>23</sup>

SINCE ENHANCEMENT MOSFET'S CONDUCT THROUGH A RELATIVELY NARROW INVERSION REGION AT THE SEMICONDUCTOR SURFACE, ALL DRAIN CURRENT IS CONCENTRATED WITHIN AN EXTREMELY LIMITED PORTION OF THE CHANNEL. AT EVEN MODERATE CURRENT LEVELS, SUCH DEVICES POSSESS AN INHERENTLY HIGH CURRENT DENSITY NEAR THE SI-SIO<sub>2</sub> INTERFACE (WHERE INCLUSIONS SUCH AS SIO<sub>2</sub> MOLECULES ARE PRESENT) AND CONSEQUENTLY EXHIBIT MUCH HIGHER 1/F NOISE INTENSITY THAN BIPOLAR TRANSISTORS.

THEREFORE, UNUSUALLY HIGH NOISE UNITS MAY BE ELIMINATED FROM PRODUCTION BATCHES IN ANTICIPATION OF A CORRESPONDINGLY HIGH FAILURE RATE PROBABILITY DUE TO HIGH CURRENT DENSITY. FURTHERMORE, THE RELATIVE 1/F NOISE INTENSITY SHOULD BE AN EXCELLENT INDICATOR OF SURFACE CONDITIONS PRESENT IN EACH DEVICE AND THE SURFACE-STATE DENSITY IN PARTICULAR. THIS REASONING WAS APPLIED TO ALL ANALYISES OF NOISE PHENEMENA ENCOUNTERED IN THIS RESEARCH AND WAS ONE OF THE REASONS IT WAS THOUGHT THAT NOISE MEASUREMENTS WOULD BE BENEFICIAL IN A STUDY OF BREAKDOWN IN ENHANCEMNENT MOSFET'S.

### 3.5 NOISE MEASUREMENTS UNDERTAKEN

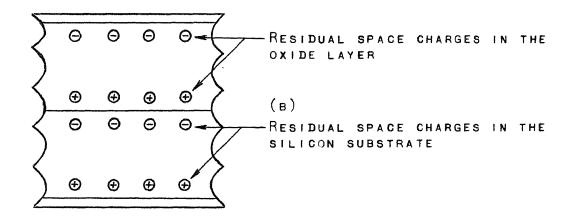

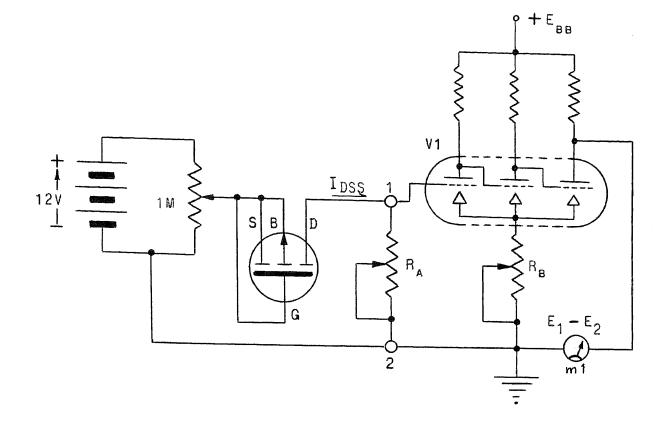

DESCRIPTION OF EQUIPMENT. NOISE MEASUREMENTS WERE PERFORMED USING THE QUAN-TECH MODEL 327 DIODE NOISE ANALYZER. FIGURE 3-1 SHOWS THE INTERNAL CONNECTION BLOCK DIAGRAM AND EXTERNAL GATE SUPPLY OF SUCH AN INSTRUMENT MODIFIED FOR USE WITH P-CHANNEL ENHANCEMENT MOSFET'S.

THE DEVICE CONSISTED OF A BUILT-IN VARIABLE DC SUPPLY, A SHIELDED TEST JIG AND SOCKET, CURRENT-LIMITING RESISTORS, A BROADBAND AMPLIFIER FOR AMPLIFYING THE NOISE VOLTAGE ACROSS A SINGLE, SELECTED, FIXED RESISTOR, TWO ACTIVE FIL-TERS RESONANT AT TEN HERTZ AND ONE KILOHERTZ WITH A BAND-WIDTH OF ONE CYCLE EACH, AND ANALOG OUTPUTS WHICH READ AT THE APPROPRIATE FREQUENCY IN RMS VOLTS.

NICKEL-CADMIUM BATTERIES WERE USED TO BIAS THE GATE OF EACH MOSFET UNDER TEST IN ORDER TO MINIMIZE NOISE INTRO-DUCED INTO THE GATE CIRCUIT WHICH MIGHT IN TURN CAUSE UN-DESIREABLE DRAIN CURRENT FLUCTUATIONS.

ALL NOISE MEASUREMENTS WERE CONDUCTED WITHIN A SHIELDED ROOM AT A TEMPERATURE OF ABOUT 25°C AND NOT MORE THAN 30% HUMIDITY.

EXPERIMENTAL METHOD. THE P-CHANNEL MOSFET'S UNDER TEST WERE INDIVIDUALLY CONNECTED WITH SOURCE AND SUBSTRATE TO THE MAIN POWER SUPPLY POSITIVE TERMINAL, DRAIN TO THE NEGATIVE TERMINAL, AND GATE TO THE EXTERNAL VARIABLE SUPPLY.

FIGURE 3-1. CONNECTION BLOCK DIAGRAM OF THE QUAN-TECH Model 327 Diode Noise Analyzer modified for measuring Noise voltages of p-channel enhancement MOS transistors.<sup>24</sup>

THE MAIN DC SUPPLY AND THE CURRENT-LIMITING RESISTORS PROVIDED CONTINUOUS VARIATION OF EITHER  $-V_{DS}$  or  $-I_D$ . With use of the external gate supply, noise voltages<sup>\*</sup> could be obtained anywhere on the MOSFET I-V characteristics.

APPROXIMATELY 80 TRANSISTORS WERE SELECTED FROM A LARGE BATCH OF P-CHANNEL MOSFET'S.<sup>\*\*</sup> All devices were FIRST SCREENED FOR PROPER OPERATION UP TO AND SLIGHTLY BE-YOND THE THRESHOLD OF DRAIN BREAKDOWN. THEN, 25 TRANSIS-TORS OF EACH TYPE WERE SELECTED FOR ACTUAL NOISE MEASURE-MENTS.

Noise voltages were obtained at 10Hz and at 1KHz with all units biased at a constant  $V_{\rm GS}$  of -5.5 volts and four different values of drain voltage: -3V., -10V., -20V., and at -25V. This permitted noise voltages to be made in both the linear and saturation regions of operation for each unit. The data provided a profile of the mean noise voltage and standard deviation as a function of drain voltage for each type of transistor.

\*\*Section 2.4 described the types DD07P, DD08P, and DD08K P-CHANNEL ENHANCEMENT MOSFET'S USED IN THIS RESEARCH. THOSE DEVICES ON WHICH NOISE MEASUREMENTS WERE MADE WERE SELECTED AT RANDOM FROM A BATCH ESTIMATED TO BE OVER 300 UNITS.

<sup>\*</sup>Actual Drain current fluctuations were computed from the measured noise voltages by dividing the observed quantity by the known, fixed resistance across which it appeared. The noise intensity (of drain current fluctuations) was then the square of the calculated noise current at a specified operating point.

Using the built-in voltmeter and ammeter on the Quan-Tech noise measuring instrument, saturation drain conductance measurements were made at an operating point of -5.5V. on the gate and  $V_{\rm DS} = -20V$ . The relative noise voltage at 10Hz was correlated with the drain conductance for each individual transistor.

On the basis of the relative noise intensity at ten cycles, the five highest and five lowest noise transistors of types DD07P and DD08K were selected for life-testing for threshold voltage drift. Noise voltage versus drain current measurements at constant gate voltage were made before and after 500 hours of bias<sup>\*</sup> at  $130 \pm 5^{\circ}$ C.

Noise voltage versus drain current characteristics at several gate voltages were plotted for three high- and three low-noise transistors of type DD07P. A curve tracer was used to visually verify the plotted I-V characteristics.

All noise, current, and voltage measurements were checked and rechecked to ensure accurate readings. A <u>Fluke Model</u> <u>8000A Digital Voltmeter</u> was used to determine the precise threshold voltage for each transistor as well as for purposes of double checking the voltage readings on the Quan-Tech instrument.

<sup>\*</sup>Type DD07P units were biased at  $V_{\rm GS}=-25V.$  while type DD08K units were biased at  $V_{\rm GS}=-50V.$  The drain, source, and substrate bulk were common for both types of devices.

#### 3.6 EXPERIMENTAL RESULTS AND DISCUSSION

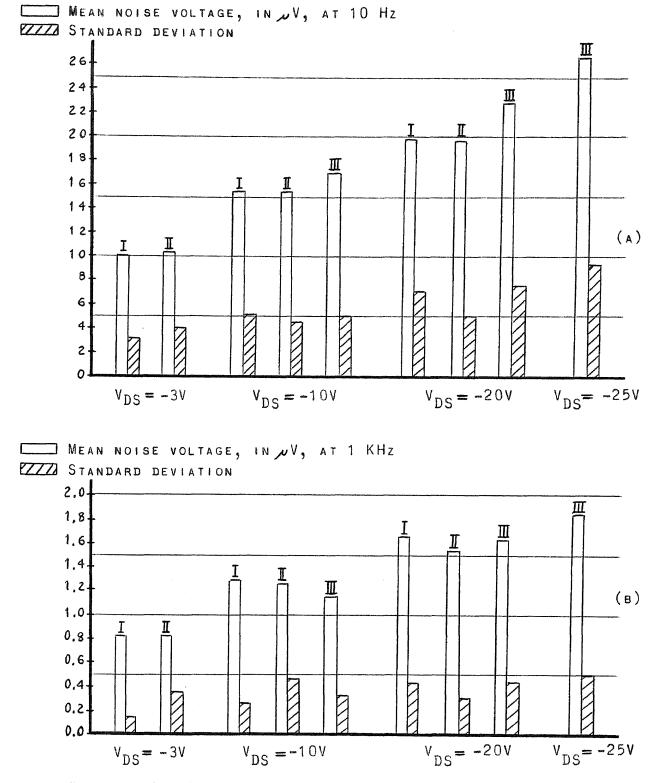

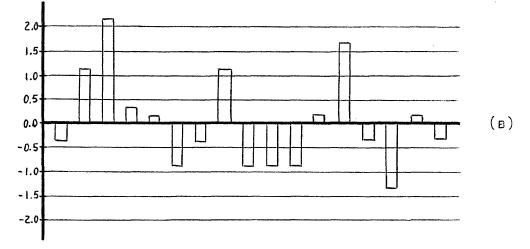

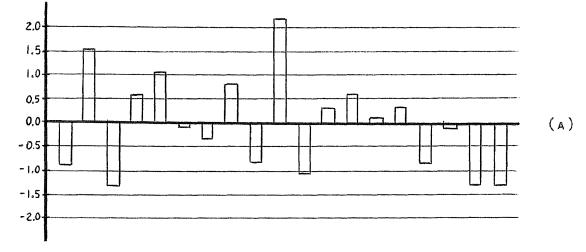

<u>COMPARISON OF NOISE INTENSITIES</u>. FIGURE 3-2 REPRE-SENTS THE NOISE VOLTAGE PROFILE OF THREE SETS OF DEVICES AS A FUNCTION OF DRAIN VOLTAGE BEFORE LIFE-TESTING FOR THRESHOLD VOLTAGE DRIFT. FIGURE 3-2A SHOWS THE MEAN AND STANDARD DEVIATION OF NOISE VOLTAGES AT TEN CYCLES WHILE FIGURE 3-2B GIVES THE CORRESPONDING INFORMATION AT ONE-THOUSAND CYCLES.<sup>\*</sup>

IT WAS NOT THE INTENTION OF THIS RESEARCH TO ESTAB-LISH THE EXACT FREQUENCY DEPENDENCE OF EXCESS NOISE IN MOS TRANSISTORS. THIS HAS BEEN DONE BEFORE AND IS READILY AVAILABLE IN THE LITERATURE.<sup>25,26,27</sup> Rather, it may be concluded that the low frequency excess noise intensity was found to be approximately inversely proportional to the frequency at which it was measured <u>before</u> threshold voltage drift. The 1/F noise theory developed earlier therefore applies to all subsequent discussions regarding the noise intensity of the devices tested.

<sup>\*</sup>The figures represent RMS noise voltage in microvolts at two frequencies. Comparisons of mean noise intensities between any two types of devices or between two frequencies for the same device must reflect the ratio of the squares of the noise voltage readings used. Example: Compare the mean noise intensity of type DD08P at 10Hz and VDS =-3V. and at the same drain voltage and 1KHz. In the first case the mean noise voltage was  $10 \times 10^{-6}V$ . And in the second it was approximately  $0.82 \times 10^{-6}V$ . The ratio of the square of the first reading to that of the second shows that the noise intensity at ten cycles was in fact more that 100 times that at one kilohertz.

FIGURE 3-2. COMPARISON OF MEAN EXCESS NOISE VOLTAGE FOR THREE TYPES OF P-CHANNEL ENHANCEMENT MOSFET'S. MEASUREMENTS WERE MADE AT FOUR DRAIN VOLTAGES WITH CONSTANT VGS OF -5.5V. TYPEI: DD08P TYPEII: DD08K TYPE III: DD07P

As expected, the noise voltage was found to increase with increasing drain voltage when the gate was held at a constant potential. Increasing V<sub>DS</sub> in this manner also increases the drain current which flows in a channel of fairly constant dimensions. The approximate 1/F frequency dependence was found to hold for both the linear and saturation regions of operation.

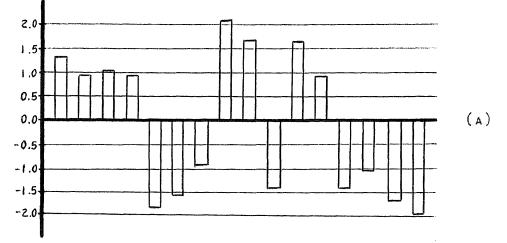

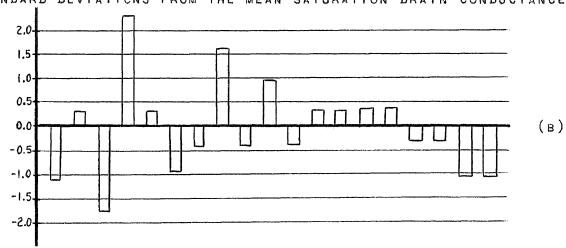

FIGURES 3-3 THROUGH 3-5 COMPARE MEAN NOISE VOLTAGE at 10Hz with saturation drain conductance at  $V_{DS} = -10V$ . and  $V_{GS} = -5.5V$ . For the three types of units tested. Two observations are immediately apparant:

1. THERE WAS A WIDE RANGE OF RELATIVE NOISE INTENSITY WITHIN EACH GROUP OF MOSFET'S, AND

2. IN EVERY CASE, THOSE UNITS HAVING A HIGH NOISE IN-TENSITY SHOWED A CORRESPONDINGLY HIGHER SATURATION DRAIN CONDUCTANCE THAN DID THE LOW-NOISE UNITS.

Two THEORIES ARE OFFERED TO EXPLAIN THE CORRELATION BETWEEN 1/F NOISE INTENSITY AND SATURATION DRAIN CONDUC-TANCE.

#### 1. VARIATIONS OF SEMICONDUCTOR IMPURITY CONCENTRATION.

Recall from section 1.2 that high saturation drain conductance is synonymous with relatively thick oxide layers and/or low substrate impurity concentrations. Under the condition of <u>uniform oxidation</u> with <u>low surface-state den-</u>

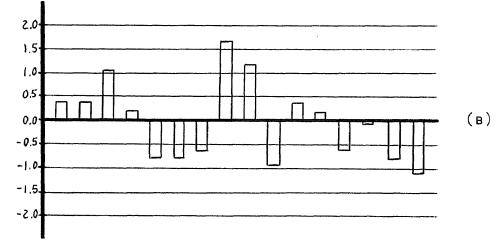

STANDARD DEVIATIONS FROM THE MEAN NOISE VOLTAGE AT 10 Hz

UNIT NO. 'S: 45 47 48 54 56 57 59 60 61 70 72 75 77 78 79 80

Figure 3-3. Comparison of noise voltage at 10Hz with saturation drain conductance for selected units of type DD07P MOSFET's. VDS = -20volts and VGS = -5.5volts.

STANDARD DEVIATIONS FROM THE MEAN NOISE VOLTAGE AT 10 Hz

STANDARD DEVIATIONS FROM THE MEAN SATURATION DRAIN CONDUCTANCE

Figure 3-4. Comparison of noise voltage at 10Hz with saturation drain conductance for selected units of type DD08P MOSFET's.  $V_{\rm DS}=-20\,\text{volts}$  and  $V_{\rm GS}=-5.5\,\text{volts}$ .

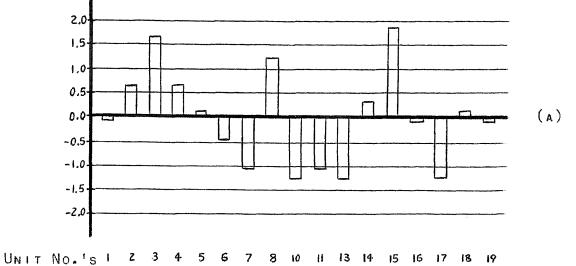

STANDARD DEVIATIONS FROM THE MEAN NOISE VOLTAGE AT 10 Hz

UNIT NO. 'S 101 102 103 104 105 106 107 109 110 111 112 113 114 115 116 118 119 120 121

STANDARD DEVIATIONS FROM THE MEAN SATURATION DRAIN CONDUCTANCE

Figure 3-5. Comparison of noise voltage at 10Hz with saturation drain conductance for selected units of type DD08K MOSFET's.  $V_{DS} = -20$  volts and  $V_{GS} = -5.5$  volts.